(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I675004 B

(45)公告日：中華民國 108 (2019) 年 10 月 21 日

(21)申請案號：104105678

(51)Int. Cl. : **C01G15/00 (2006.01)**

**H01L29/24 (2006.01)**(30)優先權：2014/02/21 日本 2014-032192

2014/05/09 日本 2014-098071

2014/06/13 日本 2014-122792

2014/06/26 日本 2014-131834

2014/10/27 日本 2014-218310(71)申請人：日商半導體能源研究所股份有限公司 (日本) SEMICONDUCTOR ENERGY

LABORATORY CO., LTD. (JP)

日本(72)發明人：下村明久 SHIMOMURA, AKIHISA (JP)；山根靖正 YAMANE, YASUMASA (JP)；

佐藤裕平 SATO, YUHEI (JP)；石山貴久 ISHIYAMA, TAKAHISA (JP)；岡崎健

一 OKAZAKI, KENICHI (JP)；川鍋 千穂 KAWANABE, CHIHO (JP)；太田將志

OOTA, MASASHI (JP)；石原典隆 ISHIHARA, NORITAKA (JP)

(74)代理人：林志剛

(56)參考文獻：

JP 2013-201429A

審查人員：李明達

申請專利範圍項數：22 項 圖式數：89 共 335 頁

(54)名稱

半導體膜、電晶體、半導體裝置、顯示裝置以及電子裝置

(57)摘要

本發明提供一種半導體膜、電晶體、半導體裝置、顯示裝置以及電子裝置。本發明提供一種氧化物半導體膜，使用束徑的半寬度為 1nm 的電子線在使氧化物半導體膜的位置與電子線的位置相對地移動時對氧化物半導體膜的被形成面進行照射，由此觀察到氧化物半導體膜具有的多個電子繞射圖案，多個電子繞射圖案具有在彼此不同的觀察地點觀察的 50 個以上的電子繞射圖案，第一電子繞射圖案與第二電子繞射圖案所占的比率之和為 100%，第一電子繞射圖案所占的比率為 90% 以上，第一電子繞射圖案包括表示 c 軸朝向大致垂直於氧化物半導體膜的被形成面的方向的觀察點，第二電子繞射圖案包括不具有對稱性的觀察點或配置為如圓圈那樣的觀察區域。

Favorable electrical characteristics are given to a semiconductor device. Furthermore, a semiconductor device having high reliability is provided. One embodiment of the present invention is an oxide semiconductor film having a plurality of electron diffraction patterns which are observed in such a manner that a surface where the oxide semiconductor film is formed is irradiated with an electron beam having a probe diameter whose half-width is 1 nm. The plurality of electron diffraction patterns include 50 or more electron diffraction patterns which are observed in different areas, the sum of the percentage of first electron diffraction patterns and the percentage of second electron diffraction patterns accounts for 100 %, the first

electron diffraction patterns account for 90 % or more, the first electron diffraction pattern includes observed points which indicates that a c-axis is oriented in a direction substantially perpendicular to the surface where the oxide semiconductor film is formed.

指定代表圖：

圖 1A

# 發明專利說明書

(本說明書格式、順序，請勿任意更動)

## 【發明名稱】(中文/英文)

半導體膜、電晶體、半導體裝置、顯示裝置以及電子裝置

Semiconductor film, transistor, semiconductor device, display device, and electronic appliance

## 【技術領域】

[0001] 本發明關於係一種物體、方法或製造方法。或者，本發明關於係一種製程 (process) 、機器 (machine) 、產品 (manufacture) 或組成物 (composition of matter)。尤其是，本發明關於係一種半導體裝置、顯示裝置、發光裝置、蓄電裝置、記憶體裝置、它們的驅動方法或它們的製造方法。

[0002] 注意，在本說明書等中，半導體裝置是指能夠藉由利用半導體特性而工作的所有裝置。電晶體、半導體電路是半導體裝置的一個方式。另外，算術裝置、記憶體裝置、攝像裝置、電光裝置、發電裝置（包括薄膜太陽能電池、有機薄膜太陽能電池等）及電子裝置有時包括半導體裝置。

## 【先前技術】

[0003] 在非專利文獻 1 中，描述以

$In_{1-x}Ga_{1+x}O_3(ZnO)_m$  (  $x$  滿足  $-1 \leq x \leq 1$  ,  $m$  為自然數 ) 表示的同系物 ( homologous phase ) 的存在。此外，描述同系物的固溶區域 ( solid solution range ) 。例如，描述  $m=1$  的情況下的同系物的固溶區域在  $x$  為  $-0.33$  至  $0.08$  的範圍內，並且  $m=2$  的情況下的同系物的固溶區域在  $x$  為  $-0.68$  至  $0.32$  的範圍內。

[0004] 作為具有尖晶石型的結晶結構的化合物，已知有以  $AB_2O_4$  (  $A$  及  $B$  為金屬元素 ) 表示的化合物。在非專利文獻 1 中示出  $In_xZn_yGa_zO_w$  的例子，並且記載有在  $x$  、  $y$  及  $z$  具有  $ZnGa_2O_4$  附近的組成，即  $x$  、  $y$  及  $z$  具有  $(x, y, z) = (0, 1, 2)$  附近的值的情況下，容易形成或混合尖晶石型的結晶結構。

[0005] 使用半導體材料構成電晶體的技術受到關注。該電晶體被廣泛地應用於積體電路 ( IC ) 、影像顯示裝置 ( 簡單地記載為顯示裝置 ) 等電子裝置。作為可以用於電晶體的半導體材料，矽類半導體材料被廣泛地周知，而作為其他材料，氧化物半導體受到關注。

[0006] 例如，公開了作為氧化物半導體使用氧化鋅或  $In\text{-}Ga\text{-}Zn$  氧化物半導體來製造電晶體的技術 ( 參照專利文獻 1 及專利文獻 2 ) 。

[0007] 近年來，隨著電子裝置的高功能化、小型化或輕量化，對高密度地集成有被微型化的電晶體等半導體元件的積體電路的要求提高。

[0008]

[專利文獻 1]日本專利申請公開第 2007-123861 號公報

[專利文獻 2]日本專利申請公開第 2007-96055 號公報。

[0009]

[非專利文獻 1]M. Nakamura, N. Kimizuka, and T. Mohri, "The Phase Relations in the  $In_2O_3$ - $Ga_2ZnO_4$ - $ZnO$  System at 1350 °C", J. Solid State Chem., 1991, Vol.93, pp.298-315。

### 【發明內容】

[0010] 本發明的一個方式的目的之一是使半導體裝置具有良好的電特性。或者，本發明的一個方式的目的之一是提供一種可靠性高的半導體裝置。

[0011] 或者，本發明的一個方式的目的之一是提供一種特性偏差少的良好的電晶體。或者，本發明的一個方式的目的之一是提供一種包括具有良好的保持特性的記憶元件的半導體裝置。或者，本發明的一個方式的目的之一是提供一種適合於微型化的半導體裝置。或者，本發明的一個方式的目的之一是提供一種縮小電路面積的半導體裝置。或者，本發明的一個方式的目的之一是提供一種具有新穎結構的半導體裝置。

[0012] 注意，這些目的的記載不妨礙其他目的的存在。本發明的一個方式並不需要實現所有上述目的。另

外，說明書、圖式以及申請專利範圍等的記載中顯然存在上述目的以外的目的，可以從說明書、圖式以及申請專利範圍等的記載中獲得上述目的以外的目的。

[0013] 本發明的一個方式是一種氧化物半導體膜，其中，使用束徑的半寬度為 1nm 的電子線在使氧化物半導體膜的位置與電子線的位置相對地移動的同時對氧化物半導體膜的被形成面進行照射，由此觀察到氧化物半導體膜具有的多個電子繞射圖案，多個電子繞射圖案具有在彼此不同的觀察地點觀察的 50 個以上的電子繞射圖案，多個電子繞射圖案的方向不同，第一電子繞射圖案所占的比率為 90% 以上，並且，第一電子繞射圖案包括表示 c 軸朝向大致垂直於氧化物半導體膜的被形成面的方向的觀察點。

[0014] 或者，本發明的一個方式是一種氧化物半導體膜，其中，使用束徑的半寬度為 1nm 的電子線在使氧化物半導體膜的位置與電子線的位置相對地移動的同時對氧化物半導體膜的被形成面進行照射，由此觀察到氧化物半導體膜具有的多個電子繞射圖案，多個電子繞射圖案具有在彼此不同的觀察地點觀察的 50 個以上的電子繞射圖案，多個電子繞射圖案的方向不同，在 50 個以上的電子繞射圖案中第一電子繞射圖案所占的比率與第二電子繞射圖案所占的比率之和為 100%，第一電子繞射圖案所占的比率為 90% 以上，第一電子繞射圖案包括表示 c 軸朝向大致垂直於氧化物半導體膜的被形成面的方向的觀察點，並

且，第二電子繞射圖案包括不具有對稱性的觀察點或配置為如圓圈那樣的（環狀的）觀察區域。

[0015] 或者，本發明的一個方式是一種氧化物半導體膜，其中，使用束徑的半寬度為  $1\text{nm}$  的電子線在使氧化物半導體膜的位置與電子線的位置相對地移動的同時對氧化物半導體膜的被形成面進行照射，由此觀察到氧化物半導體膜具有的多個電子繞射圖案，在多個電子繞射圖案中，彼此不同的觀察地點觀察的 50 個以上的電子繞射圖中的第一電子繞射圖案所占的比率為 100%，第一電子繞射圖案包括表示  $c$  軸朝向大致垂直於氧化物半導體膜的被形成面的方向的觀察點，並且，多個電子繞射圖案的方向不同。

[0016] 在上述結構中，觀察到第二電子繞射圖案的區域較佳為包含奈米晶的氧化物半導體膜。

[0017] 或者，本發明的一個方式是一種包含  $\text{In}$ 、以  $M$  表示的元素及  $\text{Zn}$  的氧化物半導體膜，其中，以  $M$  表示的元素選自鋁、鎵、釔和錫中的至少一個， $\text{In}$ 、 $M$  及  $\text{Zn}$  的原子個數比滿足  $\text{In} : M : \text{Zn} = x : y : z$ ，並且， $x$ 、 $y$  及  $z$  在以  $\text{In}$ 、元素  $M$  及  $\text{Zn}$  的三個元素為頂點的平衡狀態圖中具有由依次連接第一座標 ( $x : y : z = 2 : 2 : 1$ )、第二座標 ( $x : y : z = 23 : 27 : 25$ )、第三座標 ( $x : y : z = 8 : 12 : 35$ )、第四座標 ( $x : y : z = 4 : 0 : 7$ )、第五座標 ( $x : y : z = 2 : 0 : 3$ )、第六座標 ( $x : y : z = 7 : 1 : 8$ )、第七座標 ( $x : y : z = 15 : 5 : 8$ ) 以及上述第一座標的線段

圍繞的範圍內的原子個數比。

[0018] 在上述結構中，較佳的是，氧化物半導體膜藉由濺射法並使用包含 In、以 M 表示的元素及 Zn 的靶材而形成，以 M 表示的元素選自鋁、鎵、鈦和錫中的至少一個，靶材所包含的 In、M 及 Zn 的原子個數比滿足  $In : M : Zn = a : b : c$ ，並且，a、b 及 c 在以 In、元素 M 及 Zn 的三個元素為頂點的平衡狀態圖中具有由依次連接第一座標 ( $a : b : c = 2 : 2 : 1$ ) 、第二座標 ( $a : b : c = 23 : 27 : 25$ ) 、第三座標 ( $a : b : c = 1 : 2 : 9$ ) 、第四座標 ( $a : b : c = 1 : 0 : 3$ ) 、第五座標 ( $a : b : c = 2 : 0 : 3$ ) 、第六座標 ( $a : b : c = 7 : 1 : 8$ ) 、第七座標 ( $a : b : c = 10 : 4 : 7$ ) 以及上述第一座標的線段圍繞的範圍內的原子個數比。

[0019] 或者，本發明的一個方式是一種包含 In、Ga 及 Zn 的氧化物半導體膜，其中，In、Ga 及 Zn 的原子個數比滿足  $In : Ga : Zn = x : y : z$ ，並且，x、y 及 z 在以 In、Ga 及 Zn 的三個元素為頂點的平衡狀態圖中具有由依次連接第一座標 ( $x : y : z = 2 : 2 : 1$ ) 、第二座標 ( $x : y : z = 23 : 27 : 25$ ) 、第三座標 ( $x : y : z = 8 : 12 : 35$ ) 、第四座標 ( $x : y : z = 4 : 0 : 7$ ) 、第五座標 ( $x : y : z = 2 : 0 : 3$ ) 、第六座標 ( $x : y : z = 7 : 1 : 8$ ) 、第七座標 ( $x : y : z = 15 : 5 : 8$ ) 以及上述第一座標的線段圍繞的範圍內的原子個數比。

[0020] 或者，本發明的一個方式是一種包括如上所

記載的氧化物半導體膜的半導體裝置。

[0021] 或者，本發明的一個方式是一種在通道區域中包括如上所記載的氧化物半導體膜的電晶體。

[0022] 在上述結構中，較佳的是，半導體裝置還包括第二氧化物膜及第三氧化物膜，其中，氧化物半導體膜接觸於第二氧化物膜的頂面，並且，第三氧化物膜接觸於氧化物半導體膜的頂面。另外，在上述結構中，第三氧化物膜較佳為接觸於第二氧化物膜的側面、氧化物半導體膜的側面及頂面。此外，在上述結構中，氧化物半導體膜所包含的氧化物的電子親和力較佳為大於第二氧化物膜所包含的氧化物及第三氧化物膜所包含的氧化物的電子親和力。

[0023] 或者，本發明的一個方式是一種包括第一氧化物膜及接觸於第一氧化物膜的第二氧化物膜的半導體裝置，其中，第一氧化物膜包含銦、元素 M 及鋅，第一氧化物膜所包含的銦、元素 M 及鋅的原子個數比滿足銦：元素 M：鋅 =  $x_a : y_a : z_a$ ，並且， $x_a$ 、 $y_a$ 、 $z_a$  及  $\alpha$  滿足  $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 1$  且  $-0.33 \leq \alpha \leq +0.08$ 、 $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 2$  且  $-0.68 \leq \alpha \leq +0.32$ 、 $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 3$  且  $-1 \leq \alpha \leq +0.46$ 、 $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 4$  且  $-1 \leq \alpha \leq +0.54$  以及  $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 5$  且  $-1 \leq \alpha \leq +0.72$  中的任一個。

[0024] 或者，本發明的一個方式是一種包括第一氧化物膜及接觸於第一氧化物膜的第二氧化物膜的半導體裝

置，其中，第一氧化物膜包含銦、元素 M 及鋅，第一氧化物膜所包含的銦、元素 M 及鋅的原子個數比滿足銦：元素 M：鋅 =  $x_a : y_a : z_a$ ，第二氧化物膜包含銦、元素 M 及鋅，第二氧化物膜所包含的銦、元素 M 及鋅的原子個數比滿足銦：元素 M：鋅 =  $x_b : y_b : z_b$ ， $x_a$ 、 $y_a$  及  $z_a$  在以銦、元素 M 及鋅的三個元素為頂點的平衡狀態圖中具有由依次連接第一座標 ( $x_a : y_a : z_a = 8 : 14 : 7$ )、第二座標 ( $x_a : y_a : z_a = 2 : 5 : 7$ )、第三座標 ( $x_a : y_a : z_a = 51 : 149 : 300$ )、第四座標 ( $x_a : y_a : z_a = 46 : 288 : 833$ )、第五座標 ( $x_a : y_a : z_a = 0 : 2 : 11$ )、第六座標 ( $x_a : y_a : z_a = 0 : 0 : 1$ )、第七座標 ( $x_a : y_a : z_a = 2 : 2 : 1$ ) 以及上述第一座標的線段圍繞的範圍內的原子個數比，並且， $x_b$ 、 $y_b$  及  $z_b$  在以銦、元素 M 及鋅的三個元素為頂點的平衡狀態圖中具有由依次連接第一座標 ( $x_b : y_b : z_b = 2 : 2 : 1$ )、第二座標 ( $x_b : y_b : z_b = 23 : 27 : 25$ )、第三座標 ( $x_b : y_b : z_b = 8 : 12 : 35$ )、第四座標 ( $x_b : y_b : z_b = 4 : 0 : 7$ )、第五座標 ( $x_b : y_b : z_b = 2 : 0 : 3$ )、第六座標 ( $x_b : y_b : z_b = 7 : 1 : 8$ )、第七座標 ( $x_b : y_b : z_b = 10 : 4 : 7$ ) 以及上述第一座標的線段圍繞的範圍內的原子個數比。

[0025] 在上述結構中，較佳的是，半導體裝置包括第一電晶體，並且，第二氧化物膜具有用作第一電晶體的通道區域的功能。此外，在上述結構中， $x_b$  及  $y_b$  較佳為滿足  $x_b > y_b$ 。另外，在上述結構中，第一氧化物膜的電子

親和力較佳為小於第二氧化物膜的電子親和力。此外，在上述結構中，較佳的是，半導體裝置包括接觸於第二氧化物膜的第三氧化物膜，並且，第三氧化物膜的電子親和力較佳為小於第二氧化物膜的電子親和力。

[0026] 在上述結構中， $x_a$ 、 $y_a$ 、 $z_a$  及  $\alpha$  較佳為滿足  $x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 1$  且  $-0.33 \leq \alpha \leq +0.08$ 、

$x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 2$  且  $-0.68 \leq \alpha \leq +0.32$ 、

$x_a : y_a : z_a = (1-\alpha) : (1+\alpha) : 3$  且  $-1 \leq \alpha \leq +0.46$ 、 $x_a :$

$y_a : z_a = (1-\alpha) : (1+\alpha) : 4$  且  $-1 \leq \alpha \leq +0.54$  以及  $x_a :$

$y_a : z_a = (1-\alpha) : (1+\alpha) : 5$  且  $-1 \leq \alpha \leq +0.72$  中的任一個。

[0027] 在上述結構中， $x_b$ 、 $y_b$ 、 $z_b$  及  $\beta$  較佳為滿足  $x_b : y_b : z_b = (1-\beta) : (1+\beta) : 1$  且  $-0.33 \leq \beta \leq +0.08$ 、

$x_b : y_b : z_b = (1-\beta) : (1+\beta) : 2$  且  $-0.68 \leq \beta \leq +0.32$ 、

$x_b : y_b : z_b = (1-\beta) : (1+\beta) : 3$  且  $-1 \leq \beta \leq +0.46$ 、 $x_b :$

$y_b : z_b = (1-\beta) : (1+\beta) : 4$  且  $-1 \leq \beta \leq +0.54$  以及  $x_b :$

$y_b : z_b = (1-\beta) : (1+\beta) : 5$  且  $-1 \leq \beta \leq +0.72$  中的任一個。

[0028] 根據本發明的一個方式，可以使半導體裝置具有良好的電特性。另外，可以提供一種可靠性高的半導體裝置。

[0029] 另外，可以提供一種特性偏差少的良好的電晶體。另外，可以提供一種包括具有良好的保持特性的記憶元件的半導體裝置。另外，可以提供一種適合於微型化

的半導體裝置。另外，可以提供一種縮小電路面積的半導體裝置。另外，可以提供一種具有新穎結構的半導體裝置。注意，這些效果的記載不妨礙其他效果的存在。本發明的一個方式並不需要實現所有上述效果。另外，說明書、圖式以及申請專利範圍等的記載中顯然存在上述效果以外的效果，可以從說明書、圖式以及申請專利範圍等的記載中獲得上述效果以外的效果。

### 【圖式簡單說明】

[0030] 在圖式中：

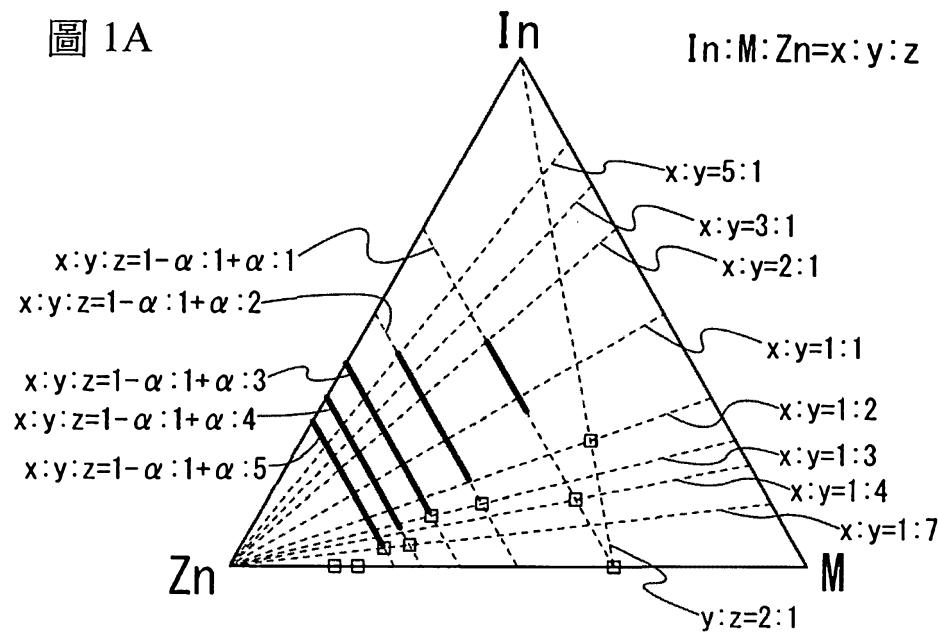

圖 1A 和圖 1B 是說明根據本發明的一個方式的氧化物膜的原子個數比的圖；

圖 2A 和圖 2B 是說明根據本發明的一個方式的氧化物膜的原子個數比的相圖；

圖 3A 和圖 3B 是說明相圖的圖；

圖 4 是說明根據本發明的一個方式的靶材的原子個數比的相圖；

圖 5A 至圖 5C 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 6A 和圖 6B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 7A 和圖 7B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 8A 和圖 8B 是示出根據本發明的一個方式的電晶

體的一個例子的圖；

圖 9A 至圖 9D 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 10A 和圖 10B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 11A 至圖 11C 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 12A 和圖 12B 是根據本發明的一個方式的電路圖；

圖 13A 至圖 13C 是示出根據本發明的一個方式的半導體裝置的一個例子的圖；

圖 14A 至圖 14C 是示出根據本發明的一個方式的半導體裝置的一個例子的圖；

圖 15A 至圖 15D 是示出根據本發明的一個方式的半導體裝置的一個例子的圖；

圖 16A 至圖 16E 是示出根據本發明的一個方式的半導體裝置的製造方法的圖；

圖 17A 至圖 17D 是示出根據本發明的一個方式的半導體裝置的製造方法的圖；

圖 18A 至圖 18C 是示出根據本發明的一個方式的半導體裝置的製造方法的圖；

圖 19A 和圖 19B 是示出根據本發明的一個方式的半導體裝置的製造方法的圖；

圖 20A 是示出根據本發明的一個方式的電晶體的一部

分的能帶結構的圖，圖 20B 是說明導通時的電流的路徑的圖；

圖 21A 至圖 21C 是氧化物半導體的剖面 TEM 影像及局部的傅立葉變換影像；

圖 22A 至圖 22D 是示出氧化物半導體膜的奈米束電子繞射圖案的圖及示出穿透式電子繞射測定裝置的一個例子的圖；

圖 23A 至圖 23C 是示出利用穿透式電子繞射測定的結構分析的一個例子的圖及平面 TEM 影像；

圖 24A 至圖 24D 是根據實施方式的電路圖；

圖 25 是根據實施方式的 RF 標籤的結構實例；

圖 26 是根據實施方式的 CPU 的結構實例；

圖 27 是根據實施方式的記憶元件的電路圖；

圖 28A 至圖 28C 是根據實施方式的顯示裝置的俯視圖及電路圖；

圖 29A 至圖 29F 是根據實施方式的電子裝置；

圖 30A 至圖 30F 是根據實施方式的 RF 標籤的使用例子；

圖 31A 至圖 31C 是示出靶材的原子個數比和氧化物半導體膜的原子個數比的關係的圖；

圖 32 示出氧化物半導體膜的 SIMS 分析結果；

圖 33A 和圖 33B 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 34A 和圖 34B 示出氧化物半導體膜的 TDS 分析結

果；

圖 35A 和圖 35B 示出氧化物半導體膜的 TDS 分析結果；

圖 36A 至圖 36D 示出根據本發明的一個方式的氧化物半導體膜的 XRD 評價結果；

圖 37A 和圖 37B 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 38A 和圖 38B 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 39A 和圖 39B 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 40A 和圖 40B 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 41A 至圖 41D 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 42A 至圖 42D 示出氧化物半導體膜的剖面 TEM 觀察結果；

圖 43A 和圖 43B 示出氧化物半導體膜的平面 TEM 觀察結果；

圖 44A 和圖 44B 是示出氧化物半導體膜的 CAAC 比率的圖；

圖 45 示出氧化物半導體膜的電子繞射圖案；

圖 46 示出氧化物半導體膜的電子繞射圖案；

圖 47 示出氧化物半導體膜的電子繞射圖案；

- 圖 48 示出氧化物半導體膜的電子繞射圖案；

- 圖 49 示出氧化物半導體膜的電子繞射圖案；

- 圖 50 示出氧化物半導體膜的電子繞射圖案；

- 圖 51 示出氧化物半導體膜的電子繞射圖案；

- 圖 52 示出氧化物半導體膜的電子繞射圖案；

- 圖 53 示出氧化物半導體膜的電子繞射圖案；

- 圖 54 示出氧化物半導體膜的電子繞射圖案；

- 圖 55 示出氧化物半導體膜的平面 TEM 觀察結果；

- 圖 56A 至圖 56C 示出氧化物半導體膜的電子繞射圖案；

- 圖 57A 和圖 57B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

- 圖 58A 和圖 58B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

- 圖 59A 和圖 59B 示出氧化物半導體膜的剖面 TEM 觀察結果；

- 圖 60 是根據實施方式的半導體裝置的電路圖；

- 圖 61 是說明 In-Ga-Zn 氧化物中的氧的移動路徑的圖；

- 圖 62A 至圖 62C 是示出根據本發明的一個方式的電晶體的一個例子的圖；

- 圖 63A 和圖 63B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

- 圖 64A 和圖 64B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

- 圖 65A 至圖 65D 是示出根據本發明的一個方式的電

晶體的一個例子的圖；

圖 66A 和圖 66B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 67A 和圖 67B 是示出根據本發明的一個方式的電晶體的一個例子的圖；

圖 68A 至圖 68C 是示出根據本發明的一個方式的氧化物半導體膜的 XRD 評價結果；

圖 69A 至圖 69C 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 70 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 71A 和圖 71B 示出氧化物半導體膜的 CPM 評價結果；

圖 72 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 73 是示出電晶體的臨界值變化的圖；

圖 74 是示出電晶體的臨界值變化的圖；

圖 75 是示出電晶體的臨界值變化的圖；

圖 76A 和圖 76B 是示出電晶體的  $Vg$ - $Id$  特性的計算結果的圖；

圖 77A 和圖 77B 是示出根據本發明的一個方式的電晶體的剖面照片；

圖 78 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 79 是示出電晶體的  $Vd$ - $Id$  特性的圖；

圖 80A 至圖 80C 示出根據本發明的一個方式的氧化物的 XRD 評價結果；

圖 81A 至圖 81D 示出根據本發明的一個方式的氧化

物的 XRD 評價結果；

圖 82A 和圖 82B 示出根據本發明的一個方式的氧化物的平面 TEM 觀察結果；

圖 83A 和圖 83B 示出根據本發明的一個方式的氧化物的平面 TEM 觀察結果；

圖 84A 和圖 84B 示出根據本發明的一個方式的氧化物的平面 TEM 觀察結果；

圖 85A 和圖 85B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 86A 和圖 86B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 87A 和圖 87B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 88A 和圖 88B 是示出電晶體的  $Vg$ - $Id$  特性的圖；

圖 89A 和圖 89B 是示出電晶體的  $Vg$ - $Id$  特性的圖。

## 【實施方式】

[0031] 參照圖式對實施方式進行詳細的說明。注意，本發明不侷限於以下說明，而所屬技術領域的普通技術人員可以很容易地理解一個事實就是其方式及詳細內容在不脫離本發明的精神及其範圍的情況下可以被變換為各種各樣的形式。因此，本發明不應該被解釋為僅侷限於以下所示的實施方式所記載的內容中。

[0032] 注意，在下面說明的發明結構中，在不同的圖式中共同使用相同的元件符號來表示相同的部分或具有相同功能的部分，而省略反復說明。此外，當表示具有相同功能的部分時有時使用相同的陰影線，而不特別附加元

件符號。

[0033] 注意，在本說明書所說明的各個圖式中，有時為了明確起見，誇大表示各構成要素的大小、層的厚度或區域。因此，本發明的一個方式並不限於圖式中的比例。

[0034] 另外，在本說明書等中使用的“第一”、“第二”等序數詞是為了方便識別構成要素而附的，而不是為了在數目方面上進行限定的。

[0035] 注意，例如當導電性充分低時，有時即使表示為“半導體”也具有“絕緣體”的特性。此外，“半導體”和“絕緣體”的境界不太清楚，因此有時不能精確地區別。由此，有時可以將本說明書所記載的“半導體”換稱為“絕緣體”。同樣地，有時可以將本說明書所記載的“絕緣體”換稱為“半導體”。

[0036] 電晶體是半導體元件的一種，可以進行電流或電壓的放大、控制導通或非導通的開關動作等。本說明書中的電晶體包括 IGFET (Insulated Gate Field Effect Transistor：絕緣閘場效電晶體) 和薄膜電晶體 (TFT：Thin Film Transistor)。

[0037] 另外，根據情況或狀態，可以互相調換“膜”和“層”。例如，有時可以將“導電層”調換為“導電膜”。另外，有時可以將“絕緣膜”調換為“絕緣層”。

[0038]

## 實施方式 1

在本實施方式中，說明本發明的一個方式的氧化物半導體。

[0039] 在此，氧化物半導體例如是包含銦的氧化物半導體。在氧化物半導體包含銦時，例如其載子移動率（電子移動率）提高。另外，氧化物半導體較佳為包含元素 M。元素 M 較佳為鋁、鎵、鈷或錫等。作為可用作元素 M 的其他元素，有硼、矽、鈦、鐵、鎳、鍆、鈷、鋯、鋁、鎵、鎵、鎵、鎵、鎵、鎵等。注意，作為元素 M 有時也可以組合多個上述元素。元素 M 例如是與氧的鍵能高的元素。元素 M 例如是與氧的鍵能高於銦的元素。或者，元素 M 例如是具有增大氧化物半導體的能隙的功能的元素。此外，氧化物半導體較佳為包含鋅。當氧化物半導體包含鋅時，有時容易晶化。

[0040]

### [氧化物半導體膜的結構]

以下說明氧化物半導體膜的結構。

[0041] 氧化物半導體膜大致分為非單晶氧化物半導體膜和單晶氧化物半導體膜。非單晶氧化物半導體膜包括 CAAC-OS ( C-Axis Aligned Crystalline Oxide Semiconductor : c 軸配向結晶氧化物半導體 ) 膜、多晶氧化物半導體膜、微晶氧化物半導體膜以及非晶氧化物半導體膜等。

[0042] 首先，說明 CAAC-OS 膜。

[0043] CAAC-OS 膜是包含呈 c 軸配向的多個結晶部的氧化物半導體膜之一。

[0044] 藉由利用穿透式電子顯微鏡（TEM：Transmission Electron Microscope）觀察 CAAC-OS 膜的明視野像及繞射圖案的複合分析影像（也稱為高解析度 TEM 影像），可以確認到多個結晶部。另一方面，藉由高解析度 TEM 也觀察不到結晶部與結晶部之間的明確的邊界，即晶界（grain boundary）。因此，在 CAAC-OS 膜中，不容易發生由晶界引起的電子移動率的下降。

[0045] 根據從大致平行於樣本面的方向觀察的 CAAC-OS 膜的高解析度剖面 TEM 影像可知在結晶部中金屬原子排列為層狀。各金屬原子層具有反映形成 CAAC-OS 膜的面（也稱為被形成面）或 CAAC-OS 膜的頂面的凸凹的形狀並以平行於 CAAC-OS 膜的被形成面或頂面的方式排列。

[0046] 另一方面，當從大致垂直於樣本面的方向觀察 CAAC-OS 膜的高解析度平面 TEM 影像時，可以確認到在結晶部中金屬原子排列為三角形狀或六邊形狀。但是，在不同的結晶部之間金屬原子的排列沒有規律性。

[0047] 在本說明書中，“平行”是指兩條直線形成的角度為-10°以上且 10°以下的狀態。因此，也包括該角度為-5°以上且 5°以下的狀態。“大致平行”是指兩條直線形成的角度為-30°以上且 30°以下的狀態。另外，“垂直”是指兩條直線形成的角度為 80°以上且 100°以下的狀

態。因此也包括  $85^\circ$  以上且  $95^\circ$  以下的角度的狀態。“大致垂直”是指兩條直線形成的角度為  $60^\circ$  以上且  $120^\circ$  以下的狀態。

[0048] 在本說明書中，六方晶系包括三方晶系和菱方晶系。

[0049] 圖 21A 是 CAAC-OS 膜的剖面的高解析度 TEM 影像。另外，圖 21B 是進一步放大圖 21A 的剖面的高解析度 TEM 影像，其中，為便於理解而突出顯示原子排列。

[0050] 圖 21C 是圖 21A 中的 A-O-A' 之間的由圓圈包圍的區域（直徑大致為  $4\text{nm}$ ）的局部性的傅立葉變換影像。在圖 21C 所示的各區域中可以確認到 c 軸配向性。另外，A-O 間的 c 軸方向不同於 O-A' 間的 c 軸方向，由此可知 A-O 間的晶粒不同於 O-A' 間的晶粒。另外，可知在 A-O 之間，c 軸的角度以  $14.3^\circ$ 、 $16.6^\circ$ 、 $26.4^\circ$  等而逐漸地連續變化。同樣地，可知在 O-A' 之間，c 軸的角度以  $-18.3^\circ$ 、 $-17.6^\circ$ 、 $-15.9^\circ$  等而逐漸地連續變化。

[0051] 另外，在 CAAC-OS 膜的電子繞射圖案中，觀察到呈現配向性的斑點（亮點）。例如，在使用例如為  $1\text{nm}$  以上且  $30\text{nm}$  以下的電子束獲得的 CAAC-OS 膜的頂面的電子繞射圖案（也稱為奈米束電子繞射圖案）中，觀察到斑點（參照圖 22A）。

[0052] 由剖面的高解析度 TEM 影像及平面的高解析度 TEM 影像可知，CAAC-OS 膜的結晶部具有配向性。

[0053] 注意，CAAC-OS 膜所包含的結晶部幾乎都可以容納在一個邊長小於  $100\text{nm}$  的立方體內。因此，有時包括在 CAAC-OS 膜中的結晶部能夠容納在一邊短於  $10\text{nm}$ 、短於  $5\text{nm}$  或短於  $3\text{nm}$  的立方體。但是，有時包含在 CAAC-OS 膜中的多個結晶部聯結，從而形成一個大結晶區域。例如，在平面的高解析度 TEM 影像中有時會觀察到  $2500\text{nm}^2$  以上、 $5\mu\text{m}^2$  以上或  $1000\mu\text{m}^2$  以上的結晶區域。

[0054] 使用 X 射線繞射 (XRD : X-Ray Diffraction) 裝置對 CAAC-OS 膜進行結構分析。例如，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的 CAAC-OS 膜時，在繞射角 ( $2\theta$ ) 為  $31^\circ$ 附近時常出現峰值。由於該峰值來源於  $\text{InGaZnO}_4$  結晶的 (009) 面，由此可知 CAAC-OS 膜中的結晶具有 c 軸配向性，並且 c 軸朝向大致垂直於 CAAC-OS 膜的被形成面或頂面的方向。

[0055] 另一方面，當利用從大致垂直於 c 軸的方向使 X 射線入射到樣本的 in-plane 法分析 CAAC-OS 膜時，在  $2\theta$ 為  $56^\circ$ 附近時常出現峰值。該峰值來源於  $\text{InGaZnO}_4$  結晶的 (110) 面。在此，將  $2\theta$ 固定為  $56^\circ$ 附近並在以樣本面的法線向量為軸 ( $\phi$  軸) 旋轉樣本的條件下進行分析 ( $\phi$  掃描)。當該樣本是  $\text{InGaZnO}_4$  的單晶氧化物半導體膜時，出現六個峰值。該六個峰值來源於相等於 (110) 面的結晶面。相對於此，當該樣本是 CAAC-OS 膜時，即使在將  $2\theta$ 固定為  $56^\circ$ 附近的狀態下進行  $\phi$  掃描也

不能觀察到明確的峰值。

[0056] 由上述結果可知，在具有 c 軸配向的 CAAC-OS 膜中，雖然 a 軸及 b 軸的方向在不同結晶部之間不規律，但是 c 軸都朝向平行於被形成面或頂面的法線向量的方向。因此，在上述剖面的高解析度 TEM 影像中觀察到的排列為層狀的各金屬原子層相當於與結晶的 ab 面平行的面。

[0057] 注意，結晶部在形成 CAAC-OS 膜或進行加熱處理等晶化處理時形成。如上所述，結晶的 c 軸朝向平行於 CAAC-OS 膜的被形成面或頂面的法線向量的方向。由此，例如，當 CAAC-OS 膜的形狀因蝕刻等而發生改變時，結晶的 c 軸不一定平行於 CAAC-OS 膜的被形成面或頂面的法線向量。

[0058] 另外，在 CAAC-OS 膜中，c 軸配向的晶化部的分佈不一定要均勻。例如，當 CAAC-OS 膜的結晶部是由 CAAC-OS 膜的頂面附近的結晶成長而形成時，有時頂面附近的 c 軸配向的結晶部比例會高於被形成面附近的結晶度。另外，在添加有雜質的 CAAC-OS 膜中，添加有雜質的區域變質而有時 CAAC-OS 膜中的 c 軸配向結晶部所占的比例根據區域而不同。

[0059] 注意，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的 CAAC-OS 膜時，除了在  $2\theta$ 為  $31^\circ$ 附近的峰值之外，有時還在  $2\theta$ 為  $36^\circ$ 附近觀察到峰值。 $2\theta$ 為  $36^\circ$ 附近的峰值意味著 CAAC-OS 膜的一部分中含有不具有 c

軸配向的結晶，例如典型為尖晶石型結晶結構。較佳的是，在 CAAC-OS 膜中在  $2\theta$  為  $31^\circ$  附近時出現峰值而在  $2\theta$  為  $36^\circ$  附近時不出現峰值。

[0060] CAAC-OS 膜是雜質濃度低的氧化物半導體膜。雜質是指氫、碳、矽、過渡金屬元素等氧化物半導體膜的主要成分以外的元素。尤其是，某一種元素如矽等與氧的鍵合力比構成氧化物半導體膜的金屬元素與氧的鍵合力強，該元素會奪取氧化物半導體膜中的氧，從而打亂氧化物半導體膜的原子排列，導致結晶性下降。另外，由於鐵或鎳等的重金屬、氫、二氧化碳等的原子半徑（或分子半徑）大，所以若包含在氧化物半導體膜內，則會打亂氧化物半導體膜的原子排列，導致結晶性下降。注意，包含在氧化物半導體膜中的雜質有時成為載子陷阱或載子發生源。

[0061] 另外，CAAC-OS 膜是缺陷態密度低的氧化物半導體膜。例如，氧化物半導體膜中的氧缺陷有時成為載子陷阱，或因俘獲氫而成為載子發生源。

[0062] 將雜質濃度低且缺陷態密度低（氧缺陷量少）的狀態稱為“高純度本質”或“實質上高純度本質”。在高純度本質或實質上高純度本質的氧化物半導體膜中載子發生源少，所以可以降低載子密度。在此，說明將該氧化物半導體膜用於電晶體的情況。使用該氧化物半導體膜的電晶體很少具有負臨界電壓的電特性（也稱為常開啟特性）。在高純度本質或實質上高純度本質的氧化物

半導體膜中載子陷阱少。因此，使用該氧化物半導體膜的電晶體的電特性變動小，於是成為高可靠性電晶體。另外，被氧化物半導體膜的載子陷阱俘獲的電荷的釋放需要長時間，有時像固定電荷那樣動作。因此，使用雜質濃度高且缺陷態密度高的氧化物半導體膜的電晶體的電特性有時不穩定。雜質及氧缺陷少的 CAAC-OS 膜是載子密度低的氧化物半導體。明確而言，可以使用載子密度小於  $8 \times 10^{11}/\text{cm}^3$ 、較佳為小於  $1 \times 10^{11}/\text{cm}^3$ 、更佳為小於  $1 \times 10^{10}/\text{cm}^3$ 、且是  $1 \times 10^{-9}/\text{cm}^3$  以上的氧化物半導體。將這樣的氧化物半導體稱為高純度本質或實質上高純度本質的氧化物半導體。CAAC-OS 膜的雜質濃度和缺陷態密度低。即，CAAC-OS 膜可以說是具有穩定的特性的氧化物半導體。

[0063] 另外，在使用 CAAC-OS 膜的電晶體中，起因於可見光或紫外光的照射的電特性的變動小。

[0064] 接下來，對多晶氧化物半導體膜進行說明。

[0065] 在多晶氧化物半導體膜的高解析度 TEM 影像中，可以觀察到晶粒。例如在高解析度 TEM 影像中，多晶氧化物半導體膜中含有的晶粒的粒徑尺寸大多為 2nm 以上且 300nm 以下、3nm 以上且 100nm 以下或 5nm 以上且 50nm 以下。另外，在多晶氧化物半導體膜的高解析度 TEM 影像中，有時觀察到晶界。

[0066] 多晶氧化物半導體膜包含多個晶粒，並且，在該多個晶粒之間結晶定向有時不同。另外，使用 XRD

裝置對多晶氧化物半導體膜進行結構分析。例如，當利用 out-of-plane 法分析包括  $\text{InGaZnO}_4$  結晶的多晶氧化物半導體膜時，有時在  $2\theta$  為  $31^\circ$  或  $36^\circ$  等附近時出現峰值。

[0067] 由於多晶氧化物半導體膜具有高結晶性，因此有時具有高電子移動率。所以，使用多晶氧化物半導體膜的電晶體具有高場效移動率。注意，有時在多晶氧化物半導體膜中，雜質偏析在晶界。另外，多晶氧化物半導體膜的晶界成為缺陷能階。多晶氧化物半導體膜的晶界有可能成為載子陷阱或載子發生源，因此有時與使用 CAAC-OS 膜的電晶體相比，使用多晶氧化物半導體膜的電晶體的電特性變動大，而成為可靠性低的電晶體。

[0068] 接下來，說明微晶氧化物半導體膜。

[0069] 在高解析度 TEM 影像中，微晶氧化物半導體膜包括能夠確認到結晶部的區域以及不能夠明確地確認到結晶部的區域。微晶氧化物半導體膜中含有的結晶部的尺寸大多為  $1\text{nm}$  以上且  $100\text{nm}$  以下或  $1\text{nm}$  以上且  $10\text{nm}$  以下。尤其是，將具有尺寸為  $1\text{nm}$  以上且  $10\text{nm}$  以下或  $1\text{nm}$  以上且  $3\text{nm}$  以下的微晶的奈米晶 (nc : nanocrystal) 的氧化物半導體膜稱為 nc-OS (nanocrystalline Oxide Semiconductor : 奈米晶氧化物半導體) 膜。另外，例如在 nc-OS 膜的高解析度 TEM 影像中，有時難以明確地確認到晶界。

[0070] nc-OS 膜在微小區域（例如  $1\text{nm}$  以上且  $10\text{nm}$  以下的區域，特別是  $1\text{nm}$  以上且  $3\text{nm}$  以下的區域）中其

原子排列具有週期性。另外，nc-OS 膜在不同的結晶部之間觀察不到晶體配向的規律性。因此，在膜整體上觀察不到配向性。所以，有時 nc-OS 膜在某些分析方法中與非晶氧化物半導體膜沒有差別。例如，在藉由利用使用其束徑比結晶部大的 X 射線的 XRD 裝置的 out-of-plane 法對 nc-OS 膜進行結構分析時，檢測不出表示結晶面的峰值。另外，在對 nc-OS 膜進行使用其束徑比結晶部大（例如，50nm 以上）的電子射線的電子繞射（也稱為選區電子繞射）時，觀察到類似於光暈圖案的繞射圖案。另一方面，在對 nc-OS 膜進行使用其束徑近於或小於結晶部的電子射線的奈米束電子繞射時，觀察到斑點。另外，在 nc-OS 膜的奈米束電子繞射圖案中，有時觀察到如圓圈那樣的（環狀的）亮度高的區域。在 nc-OS 膜的奈米束電子繞射圖案中，還有時觀察到環狀的區域內的多個斑點（參照圖 22B）。

[0071] nc-OS 膜是其規律性比非晶氧化物半導體膜高的氧化物半導體膜。因此，nc-OS 膜的缺陷態密度比非晶氧化物半導體膜低。但是，nc-OS 膜在不同的結晶部之間觀察不到晶體配向的規律性。所以，nc-OS 膜的缺陷態密度比 CAAC-OS 膜高。

[0072] 因此，nc-OS 膜有時具有比 CAAC-OS 膜高的載子密度。載子密度高的氧化物半導體膜有時具有高電子移動率。所以，使用 nc-OS 膜的電晶體有時具有較高的場效移動率。此外，因為 nc-OS 膜有時具有比 CAAC-OS 膜

高的缺陷態密度，所以有時具有較多的載子陷阱。因此，與使用 CAAC-OS 膜的電晶體相比，使用 nc-OS 膜的電晶體的電特性變動大，而成為可靠性低的電晶體。注意，因為 nc-OS 膜即使包含較多的雜質也可以形成，所以與 CAAC-OS 膜相比容易形成，從而有時根據用途較佳為使用 nc-OS 膜。因此，有時能夠高生產率地製造具有使用 nc-OS 膜的電晶體的半導體裝置。

[0073] 接著，對非晶氧化物半導體膜進行說明。

[0074] 非晶氧化物半導體膜是具有無序的原子排列並不具有結晶部的氧化物半導體膜。其一個例子為具有如石英那樣的無定形態的氧化物半導體膜。

[0075] 在使用高解析度 TEM 觀察的非晶氧化物半導體膜的影像中，觀察不到結晶部。

[0076] 使用 XRD 裝置對非晶氧化物半導體膜進行結構分析。當利用 out-of-plane 法分析時，檢測不到表示結晶面的峰值。另外，在對非晶氧化物半導體膜進行電子繞射時，觀察到光暈圖案。另外，在對非晶氧化物半導體膜進行奈米束電子繞射時，觀察不到斑點，而觀察到光暈圖案。

[0077] 非晶氧化物半導體膜是以高的濃度包含氫等雜質的氧化物半導體膜。此外，非晶氧化物半導體膜是其缺陷態密度高的氧化物半導體膜。

[0078] 雜質濃度高且缺陷態密度高的氧化物半導體膜是載子陷阱或載子發生源多的氧化物半導體膜。

[0079] 因此，非晶氧化物半導體膜有時具有比 nc-OS 膜更高的載子密度。所以，使用非晶氧化物半導體膜的電晶體容易具有常導通電特性。因此，有時可以將非晶氧化物半導體膜適用於需要常導通電特性的電晶體。非晶氧化物半導體膜具有較高的缺陷態密度，因此有時具有較多的載子陷阱。由此，與使用 CAAC-OS 膜或 nc-OS 膜的電晶體相比，使用非晶氧化物半導體膜的電晶體的電特性變動大，而成為可靠性低的電晶體。

[0080] 接著，對單晶氧化物半導體膜進行說明。

[0081] 單晶氧化物半導體膜是雜質濃度低且缺陷態密度低（氧缺陷少）的氧化物半導體膜。所以，可以降低載子密度。因此，使用單晶氧化物半導體膜的電晶體很少具有常導通電特性。另外，由於單晶氧化物半導體膜具有較低的雜質濃度和較低的缺陷態密度，因此有時具有很少的載子陷阱。因此，使用單晶氧化物半導體膜的電晶體的電特性變動小，而成為可靠性高的電晶體。

[0082] 為了形成單晶，例如能夠以大約 1000°C 以上的高溫度進行焙燒。另一方面，CAAC-OS 膜能夠以室溫至 500°C 左右的低溫度形成，所以在產業上是較佳的。

[0083] 注意，氧化物半導體膜的缺陷越少其密度越高。此外，氧化物半導體膜的結晶性越高其密度越高。另外，當氧化物半導體膜中的氫等雜質的濃度越低其密度越高。單晶氧化物半導體膜的密度比 CAAC-OS 膜高。此外，CAAC-OS 膜的密度比微晶氧化物半導體膜高。另

外，多晶氧化物半導體膜的密度比微晶氧化物半導體膜高。此外，微晶氧化物半導體膜的密度比非晶氧化物半導體膜高。

[0084] 此外，氧化物半導體膜有時具有呈現 nc-OS 膜與非晶氧化物半導體膜之間的物性的結構。將具有這種結構的氧化物半導體膜特別稱為 amorphous-like 氧化物半導體 (a-like OS : amorphous-like Oxide Semiconductor) 膜。

[0085] 在使用高解析度 TEM 觀察的 a-like OS 膜的影像中，有時觀察到空洞（也稱為空隙）。此外，在使用高解析度 TEM 觀察的 a-like OS 膜的影像中，有明確地確認到結晶部的區域及確認不到結晶部的區域。a-like OS 膜有時因 TEM 觀察時的微量的電子照射而產生晶化，由此觀察到結晶部的生長。另一方面，在良好的 nc-OS 膜中，幾乎觀察不到因 TEM 觀察時的微量的電子照射而產生晶化。

[0086] 此外，a-like OS 膜及 nc-OS 膜的結晶部的大小的測量可以使用高解析度 TEM 影像進行。例如， $\text{InGaZnO}_4$  的結晶具有層狀結構，在 In-O 層之間具有兩個 Ga-Zn-O 層。 $\text{InGaZnO}_4$  的結晶的單位晶格具有三個 In-O 層和六個 Ga-Zn-O 層的一共九個層在 c 軸方向上重疊為層狀的結構。因此，這些彼此相鄰的層之間的間隔與 (009) 面的晶格表面間隔（也稱為 d 值）大致相等，從結晶結構分析求出其值為  $0.29\text{nm}$ 。因此，著眼於高解析

度 TEM 影像的晶格條紋，在晶格條紋的間隔為  $0.28\text{nm}$  以上且  $0.30\text{nm}$  以下的區域，每個晶格條紋都被認為是對應於  $\text{InGaZnO}_4$  的結晶的 a-b 面。

[0087] 另外，氧化物半導體膜的密度有時根據結構而不同。例如，當已知某個氧化物半導體膜的組成時，藉由以與該組成相同的組成中的單晶的密度與其進行比較，可以估計該氧化物半導體膜的結構。例如，相對於單晶的密度，a-like OS 膜的密度為 78.6% 以上且小於 92.3%。例如，相對於單晶的密度，nc-OS 膜的密度和 CAAC-OS 膜的密度都為 92.3% 以上且小於 100%。注意，難以形成其密度相對於單晶的密度小於 78% 的氧化物半導體膜。

[0088] 使用具體例子對上述內容進行說明。例如，在原子個數比滿足  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$  的氧化物半導體膜中，具有菱方晶系結構的單晶  $\text{InGaZnO}_4$  的密度為  $6.357\text{g/cm}^3$ 。因此，例如，在原子個數比滿足  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$  的氧化物半導體膜中，a-like OS 膜的密度為  $5.0\text{g/cm}^3$  以上且小於  $5.9\text{g/cm}^3$ 。另外，例如，在原子個數比滿足  $\text{In} : \text{Ga} : \text{Zn} = 1 : 1 : 1$  的氧化物半導體膜中，nc-OS 膜的密度和 CAAC-OS 膜的密度為  $5.9\text{g/cm}^3$  以上且小於  $6.3\text{g/cm}^3$ 。

[0089] 注意，有時不存在相同組成的單晶。此時，藉由以任意比例組合組成不同的單晶，可以算出相當於所希望的組成的單晶的密度。根據組成不同的單晶的組合比例使用加權平均計算所希望的組成的單晶的密度即可。注

意，較佳為儘可能減少所組合的單晶的種類來計算密度。

[0090] 注意，氧化物半導體膜例如可以是包括非晶氧化物半導體膜、a-like OS 膜、微晶氧化物半導體膜和 CAAC-OS 膜中的兩種以上的疊層膜。

[0091] 如上所述，CAAC-OS 膜在產業上也是較佳的。另外，由於與多晶及微晶相比起因於晶界的載子散射小，所以有不容易發生載子移動率的降低的優點。此外，因為 CAAC-OS 膜是缺陷態密度低的氧化物半導體膜且載子陷阱少，所以使用 CAAC-OS 膜的電晶體成為電特性的變動小且可靠性高的優良的電晶體。

[0092] 在此，CAAC-OS 膜有時具有多個結構。在 CAAC-OS 膜具有多個結構時，有時藉由利用後述的奈米束電子繞射可以進行結構分析。在此，將 c 軸配向的多個結晶部稱為 CAAC 結構。另外，將在 CAAC-OS 膜中代表性地觀察到的繞射圖案，即呈現 c 軸配向的繞射圖案，稱為 CAAC 結構的繞射圖案。例如，c 軸配向的多個結晶部即具有 CAAC 結構的 CAAC-OS 膜在使用奈米束電子繞射的情況下有時觀察到 CAAC 結構的繞射圖案之外的繞射圖案。例如，有時觀察到與 nc-OS 膜同樣的繞射圖案，即 nc 結構的繞射圖案，有時觀察到尖晶石型結晶結構的繞射圖案。如此，在氧化物半導體膜具有多個結構的情況下，例如在這些結構與觀察到 CAAC-OS 膜的繞射圖案的區域之間的邊界增大載子的散射，而導致載子移動率的降低。此外，由於考慮到邊界部容易成為雜質的移動路徑且

容易俘獲雜質，所以有增大 CAAC-OS 膜的雜質濃度的擔憂。

[0093]

[奈米束電子繞射]

接著，說明奈米束電子繞射。在氧化物半導體膜具有多個結構時，有時藉由利用奈米束電子繞射可以進行結構分析。

[0094] 圖 22C 示出一種穿透式電子繞射測量裝置，包括：電子槍室 610；電子槍室 610 下的光學系統 612；光學系統 612 下的樣本室 614；樣本室 614 下的光學系統 616；光學系統 616 下的觀察室 620；設置於觀察室 620 的拍攝裝置 618；以及觀察室 620 下的膠片室 622。以朝向觀察室 620 內部的方式設置拍攝裝置 618。另外，該穿透式電子繞射測量裝置也可以不包括膠片室 622。

[0095] 另外，圖 22D 示出圖 22C 所示的穿透式電子繞射測量裝置內部的結構。在穿透式電子繞射測量裝置內部中，從設置在電子槍室 610 的電子槍發射的電子藉由光學系統 612 照射到配置在樣本室 614 中的物質 628。穿過物質 628 的電子藉由光學系統 616 入射到設置在觀察室 620 內部的螢光板 632 中。在螢光板 632 中，藉由呈現對應於所入射的電子的強度的圖案，可以測量穿透式電子繞射圖案。

[0096] 因為拍攝裝置 618 朝向螢光板 632 地設置，所以可以拍攝呈現於螢光板 632 的圖案。穿過拍攝裝置

618 的透鏡的中間部及螢光板 632 的中間部的直線和螢光板 632 所形成的角度例如為  $15^\circ$  以上且  $80^\circ$  以下、 $30^\circ$  以上且  $75^\circ$  以下或  $45^\circ$  以上且  $70^\circ$  以下。該角度越小，由拍攝裝置 618 拍攝的穿透式電子繞射圖案的應變越大。但若預先得知該角度，則能夠校正所得到的穿透式電子繞射圖案的應變。另外，有時也可以將拍攝裝置 618 設置在膠片室 622。例如，也可以以與電子 624 的入射方向相對的方式將拍攝裝置 618 設置在膠片室 622 中。在此情況下，可以從螢光板 632 的背面拍攝應變少的穿透式電子繞射圖案。

[0097] 樣本室 614 設置有用來固定作為樣本的物質 628 的支架。支架具有使穿過物質 628 的電子透過的結構。例如，支架也可以具有在 X 軸、Y 軸、Z 軸等上移動物質 628 的功能。支架的移動功能例如具有在  $1\text{nm}$  以上且  $10\text{nm}$  以下、 $5\text{nm}$  以上且  $50\text{nm}$  以下、 $10\text{nm}$  以上且  $100\text{nm}$  以下、 $50\text{nm}$  以上且  $500\text{nm}$  以下、 $100\text{nm}$  以上且  $1\mu\text{m}$  以下等的範圍內移動的精度即可。至於這些範圍，根據物質 628 的結構設定最適合的範圍即可。

[0098] 接著，說明使用上述穿透式電子繞射測量裝置測量物質的穿透式電子繞射圖案的方法。

[0099] 例如，如圖 22D 所示，藉由改變物質中的奈米束的電子 624 的照射位置（進行掃描），可以確認到物質的結構逐漸地產生變化的狀況。此時，若物質 628 是 CAAC-OS 膜，則可以觀察到圖 22A 所示的繞射圖案。或者，若物質 628 是 nc-OS 膜，則可以觀察到圖 22B 所示的

具有亮點的環狀繞射圖案。

[0100] 如圖 22A 所示，在 CAAC-OS 膜的繞射圖案中，例如觀察到位於六邊形的頂點的斑點。藉由改變 CAAC-OS 膜的照射位置（進行掃描），觀察到該六邊形方向不同而逐漸地旋轉的狀態。旋轉的角度具有某些寬度。

[0101] 或者，藉由改變照射位置（進行掃描），觀察到 CAAC-OS 膜的繞射圖案以 c 軸為中心而逐漸地旋轉的狀態。這是例如也可以說 a 軸和 b 軸形成的面旋轉。

[0102]

[CAAC 比率]

在此，即使物質 628 是 CAAC-OS 膜，有時也部分地觀察到與 nc 結構等同樣的繞射圖案。因此，有時可以在一定範圍內觀察到 CAAC 結構的繞射圖案的區域的比例（也稱為 CAAC 比率或 CAAC 化率）表示 CAAC-OS 膜的優劣。在此，CAAC 比率較佳為 90% 以上，更佳為 95% 以上，進一步較佳為 97% 以上且 100% 以下。

[0103] 以下說明 CAAC-OS 膜的 CAAC 比率的評價方法。隨機選擇測量點，取得穿透式電子繞射圖案，而算出相對於所有測量點的數量的觀察到 CAAC 結構的繞射圖案的測量點的數量的比率。在此，測量點的數量較佳為 50 點以上，更佳為 100 點以上。

[0104] 作為隨機選擇測量點的方法，例如可以直線狀地掃描照射位置，按每個相等間隔的時間取得繞射圖

案。藉由掃描照射位置，可以確認具有 CAAC 結構的區域與其他區域的邊界等，所以是較佳的。

[0105] 作為一個例子，對具有剛進行成膜之後（表示為 as-sputtered）的 CAAC-OS 膜或在包含氧的氛圍中以 450°C 進行加熱處理之後的 CAAC-OS 膜的各樣本的頂面一邊進行掃描一邊得到穿透式電子繞射圖案。在此，一邊以 5nm/秒鐘的速度進行掃描 60 秒鐘一邊觀察繞射圖案，且每隔 0.5 秒鐘將觀察到的繞射圖案轉換為靜態影像，從而導出 CAAC 比率。注意，作為電子線使用束徑為 1nm 的奈米束。另外，對六個樣本進行同樣的測量。並且，利用六個樣本的平均值算出 CAAC 比率。

[0106] 此外，較佳為在因 TEM 影像的觀察或電子繞射的測量等而照射電子線時結晶結構不變化。例如，在利用日本日立高新技術公司（Hitachi High-Technologies Corporation）製造的 H-9000NAR 的情況下，例如加速電壓較佳為 300kV 以下，例如電子線的累積照射量（電流密度 × 時間）較佳為  $1 \times 10^7 e^-/nm^2$  以下。另外，例如較佳為使用 TEM 影像等確認：結晶結構在照射前後沒有由於例如 TEM 影像的觀察等而顯著地變化。

[0107] 圖 23A 示出各樣本的 CAAC 比率。剛進行成膜之後的 CAAC-OS 膜的 CAAC 比率為 75.7%（非 CAAC 比率為 24.3%）。另外，進行 450°C 的加熱處理之後的 CAAC-OS 膜的 CAAC 比率為 85.3%（非 CAAC 比率為 14.7%）。由此可知，與剛進行成膜之後相比，450°C 的加

熱處理之後的 CAAC 比率較高。也就是說，可知高溫（例如 400°C 以上）下的加熱處理降低非 CAAC 比率（提高 CAAC 比率）。另外，在進行低於 500°C 的加熱處理時也可以得到具有高 CAAC 比率的 CAAC-OS 膜。

[0108] 在此，與 CAAC 結構不同的繞射圖案的大部分是 nc 結構的繞射圖案。另外，在測量區域中觀察不到與非晶氧化物半導體膜同樣的繞射圖案。由此可知，藉由加熱處理，具有 nc 結構的區域受到相鄰的區域的結構的影響而重新排列，並 CAAC 化。

[0109] 圖 23B 及圖 23C 是剛進行成膜之後及 450°C 的加熱處理之後的 CAAC-OS 膜的平面 TEM 影像。藉由對圖 23B 和圖 23C 進行比較，可知 450°C 的加熱處理之後的 CAAC-OS 膜的性質更均勻。也就是說，可知藉由高溫的加熱處理提高 CAAC-OS 膜的性質。

[0110] 藉由採用這種測量方法，有時可以對具有多種結構的氧化物半導體膜進行結構分析。

[0111] 例如，當對 CAAC-OS 膜進行剖面 TEM 觀察時，可以說 CAAC 比率越高，金屬原子有規律地排列為層狀的區域越大。雖然在後面的實施例中詳細地描述，但是例如在對 CAAC 比率不同的兩個 CAAC-OS 膜進行剖面 TEM 觀察時，有時在 CAAC 比率更大的膜中增大金屬原子有規律地排列為層狀的區域。圖 59A 示出對 CAAC 比率約為 90% 的 CAAC-OS 膜的剖面進行觀察的結果，圖 59B 示出對 CAAC 比率約為 98% 的 CAAC-OS 膜的剖面進

行觀察的結果。在圖 59A 和圖 59B 中以線表示的區域示出金屬原子有規律地排列為層狀的區域。在有規律地排列的區域之間有時存在排列不明確的區域，有時 CAAC-OS 膜的 CAAC 比率越高，不明確的區域越少。

[0112] 在此，考慮到如下情況：在進行奈米束電子繞射的情況下，CAAC-OS 膜部分具有 CAAC 結構之外的結構的區域，例如觀察到 nc 結構的繞射圖案的區域或者觀察到尖晶石型結晶結構的繞射圖案的區域。在此情況下，在觀察到 CAAC 結構的繞射圖案的區域與觀察到其他結構的繞射圖案的區域之間的邊界，例如有時增大載子的散射而導致載子移動率的下降。此外，由於考慮到邊界部容易成為雜質的移動路徑且容易俘獲雜質，所以有增大 CAAC-OS 膜的雜質濃度的擔憂。

[0113] 尤其是，在具有其他結構的區域為具有尖晶石型結晶結構的區域的情況下，有時在具有與 CAAC 結構的區域之間觀察到明確的邊界，因此有時在其邊界部中由於載子的散射等而電子移動率下降。另外，在 CAAC-OS 膜上形成導電膜的情況下，有時導電膜所包含的元素如金屬等擴散到尖晶石型結晶結構的區域與其他區域之間的邊界。在具有尖晶石型結晶結構的膜中，有時膜中的雜質濃度如氫濃度上升，例如有可能考慮到在晶界部分中氫等雜質被俘獲。因此，CAAC-OS 膜尤其較佳為不包含尖晶石型結晶結構或者尖晶石型結晶結構較少。

[0114]

## [原子個數比]

考慮到氧化物半導體膜包含銦、元素 M 及鋅的情況。在此，元素 M 較佳為鋁、鎵、鈷或錫等。作為可用作元素 M 的其他元素，有硼、矽、鈦、鐵、鎳、鎗、鈷、鎔、鋁、鑭、鈰、釤、鉻、鎢等。注意，作為元素 M 有時也可以組合多個上述元素。參照圖 1A 至圖 2B 說明氧化物半導體膜所包含的銦、元素 M 及鋅的原子個數比  $x : y : z$  的較佳的範圍。

[0115] 在此，使用圖 3A 和圖 3B 說明各元素的原子個數比。圖 3A 及圖 3B 示出以 X、Y 及 Z 為頂點的正三角形以及作為座標點的例子的座標點 R (4 : 2 : 1)。在此，各頂點分別表示元素 X、Y 及 Z。各個原子個數比越近於各頂點越高，越遠於各頂點越低。如圖 3A 所示，各個原子個數比被表示為座標點與三角形的頂點的對邊之間的垂線的長度。例如，元素 X 被表示為座標點與頂點 X 的對邊即邊 YZ 之間的垂線 21 的長度。因此，在圖 3A 和圖 3B 所示的座標 R 中，元素 X、元素 Y 及元素 Z 的原子個數比表示垂線 21、垂線 22 及垂線 23 的長度的比例，即  $x : y : z = 4 : 2 : 1$ 。另外，將經過頂點 X 和座標點 R 的直線與邊 YZ 交叉的點稱為  $\gamma$ 。此時，在將線  $Y\gamma$  的長度與線  $\gamma Z$  的長度的比例設定為  $Y\gamma : \gamma Z$  的情況下，滿足  $Y\gamma : \gamma Z = (\text{元素 Z 的原子個數}) : (\text{元素 Y 的原子個數})$ 。

[0116] 如圖 3B 所示，劃經過座標點 R 並分別與三角形的三個邊分別平行的三條直線。此時，使用三條直線與

三個邊的交點， $x$ 、 $y$  及  $z$  可以如圖 3B 所示。

[0117] 圖 1A 至圖 2B 示出氧化物半導體膜所包含的銦、元素  $M$  及鋅的原子個數比的範圍。在此，圖 1A 至圖 2B 示出元素  $M$  為 Ga 的例子。注意，圖 1A 至圖 2B 不記載氧的原子個數比。

[0118] 例如，如非專利文獻 1 所記載，已知在包含銦、元素  $M$  及鋅的氧化物中存在以  $InMO_3(ZnO)_m$  ( $m$  為自然數) 表示的同源相 (同系列)。在此，考慮到元素  $M$  為 Ga 的情況的例子。在圖 1A 和圖 1B 中以粗直線表示的區域是已知例如在將  $In_2O_3$ 、 $Ga_2O_3$  及  $ZnO$  的粉末以圖 1A 和圖 1B 所示的區域的比例混合並以  $1350^{\circ}C$  的溫度焙燒的情況下有可能為單一相的固溶區域的區域。此外，在圖 1A 和圖 1B 中以四邊形的符號表示的座標已知具有容易混合尖晶石型結晶結構的組成。

[0119] 例如，作為具有尖晶石型結晶結構的化合物，已知  $ZnGa_2O_4$  等以  $ZnM_2O_4$  表示的化合物。例如，在非專利文獻 1 中，記載了：在如圖 1A 和圖 1B 所示具有  $ZnGa_2O_4$  附近的組成，即  $x$ 、 $y$  及  $z$  具有近似於 ( $x : y : z$ ) = (0 : 1 : 2) 的值的情況下，容易形成或混合尖晶石型結晶結構。

[0120] 在此，氧化物半導體膜較佳為 CAAC-OS 膜。在 CAAC-OS 膜中尤其較佳為不包含尖晶石型結晶結構。為了提高載子移動率較佳為提高 In 的含有率。在包含銦、元素  $M$  及鋅的氧化物半導體中，重金屬的 s 軌域主

要有助於載子傳導，並且，藉由增加銻的含有率來增加 s 軌域的重疊，由此銻的含有率多的氧化物的移動率比銻的含有率少的氧化物高。因此，藉由將銻含量高的氧化物用於氧化物半導體膜，可以提高載子移動率。

[0121] 因此，氧化物半導體膜所包含的銻、元素 M 及鋅的原子個數比  $x : y : z$  例如較佳為在圖 1B 所示的區域 11 的範圍內。在此，區域 11 是具有依次連接第一座標 K ( $x : y : z = 8 : 14 : 7$ ) 、第二座標 L ( $x : y : z = 2 : 5 : 7$ ) 、第三座標 M ( $x : y : z = 51 : 149 : 300$ ) 、第四座標 N ( $x : y : z = 46 : 288 : 833$ ) 、第五座標 O ( $x : y : z = 0 : 2 : 11$ ) 、第六座標 P ( $x : y : z = 0 : 0 : 1$ ) 、第七座標 Q ( $x : y : z = 1 : 0 : 0$ ) 以及上述第一座標 K 的範圍內的原子個數比的區域。注意，區域 11 包括線上的座標。

[0122] 藉由將  $x : y : z$  設定為圖 1B 所示的區域 11，在奈米束電子繞射圖案時可以使尖晶石型結晶結構沒有觀察到或儘可能減少觀察到的比率。由此，可以獲得優良的 CAAC-OS 膜。另外，因為能夠減少 CAAC 結構與尖晶石型結晶結構之間的境界的載子散射等，所以在將氧化物半導體膜用於電晶體的情況下，可以實現場效移動率高的電晶體。另外，可以實現可靠性高的電晶體。

[0123] 在此，為了提高氧化物半導體膜的 CAAC 比率，較佳為提高鋅的原子個數比。在圖 1A 至圖 2B 中，以虛線表示銻、元素 M 及鋅的原子個數比  $x : y : z$  滿足如下算式（1）的範圍。

[0124]

[算式 1]

$$x:y:z = (1-\alpha):(1+\alpha):m \quad (-1 \leq \alpha \leq 1) \quad (1)$$

[0125] 在此，圖 1A 至圖 2B 示出  $m=1, 2, 3, 4, 5$  的情況。圖 1A 和圖 1B 所示的粗線表示已知例如在元素 M 為鎵的情況下 In-Ga-Zn 氧化物有可能為單一相的固溶區域的區域。例如，藉由將 In-Ga-Zn 氧化物的原子個數比設定為有可能為固溶區域的範圍，有時可以提高 CAAC 比率。有可能為固溶區域的範圍有在相對於銦與鎵的原子個數之和提高鋅的原子個數比時擴大的傾向。因此，藉由相對於銦與鎵的原子個數之和提高鋅的原子個數比，有時可以提高氧化物半導體膜的 CAAC 比率。

[0126] 在此，圖 1A 和圖 1B 所示的粗線的區域即有可能為固溶區域的範圍在  $m=1$  至  $5$  的情況下以如下算式 (2) 至算式 (6) 表示。

[0127]

[算式 2]

$$x:y:z = (1-\alpha):(1+\alpha):1 \quad (-0.33 \leq \alpha \leq +0.08) \quad (2)$$

[0128]

[算式 3]

$$x:y:z = (1-\alpha):(1+\alpha):2 \quad (-0.68 \leq \alpha \leq +0.32) \quad (3)$$

[0129]

[算式 4]

$$x:y:z = (1-\alpha):(1+\alpha):3 \quad (-1 \leq \alpha \leq +0.46) \quad (4)$$

[0130]

[算式 5]

$$x:y:z = (1-\alpha):(1+\alpha):4 \quad (-1 \leq \alpha \leq +0.54) \quad (5)$$

[0131]

[算式 6]

$$x:y:z = (1-\alpha):(1+\alpha):5 \quad (-1 \leq \alpha \leq +0.72) \quad (6)$$

[0132] 因此，為了提高氧化物半導體膜的 CAAC 比率，較佳為將氧化物半導體膜所包含的銦、元素 M 及鋅的原子個數比  $x:y:z$  設定為圖 2A 所示的區域 12 的範圍，更佳為設定為圖 2B 所示的區域 13 的範圍。在此，由於區域 12 及區域 13 都包括在區域 11 中，因此，可以使氧化物半導體膜的尖晶石型結晶結構的區域沒有觀察到或減少觀察到的區域，所以是較佳的。

[0133] 在此，區域 12 是具有依次連接第一座標 A ( $x:y:z=2:2:1$ ) 、第二座標 B ( $x:y:z=23:27:25$ ) 、第三座標 C ( $x:y:z=8:12:35$ ) 、第四座標 D ( $x:y:z=4:0:7$ ) 、第五座標 E ( $x:y:z=2:0:3$ ) 、第六座標 F ( $x:y:z=7:1:8$ ) 、第七座標 G ( $x:y:z=15:5:8$ ) 以及上述第一座標 A 的範圍內的原子個數比的區域。注意，區域 12 包括線上的座標。

[0134] 此外，區域 13 是具有依次連接第一座標 H ( $x:y:z=35:20:22$ ) 、第二座標 I ( $x:y:z=7:4:11$ ) 、第三座標 J ( $x:y:z=5:1:6$ ) 、第四座標 U ( $x:y:z=25:10:14$ ) 以及上述第一座標 H 的範圍內的

原子個數比的區域。注意，區域 13 包括線上的座標。例如，藉由提高銦的原子個數比，可以提高載子移動率，所以是較佳的。例如， $x$  較佳為  $y$  的 1.75 倍以上。

[0135] 在區域 12 及區域 13 的範圍內， $x$ 、 $y$  及  $z$  滿足算式 (1) 或算式 (2) 至算式 (6) 的關係的情況下，尤其 CAAC 比率得到提高，所以是更佳的。在此， $x$ 、 $y$  及  $z$  例如也可以包括滿足算式 (1) 至算式 (6) 的關係的值的  $\pm 10\%$  左右的誤差。例如，在  $(x : y : z) = (x_1 : y_1 : z_1)$  滿足算式 (1) 的情況下， $x$ 、 $y$  及  $z$  的值較佳為  $0.9 \times x_1 \leq x \leq 1.1 \times x_1$ 、 $0.9 \times y_1 \leq y \leq 1.1 \times y_1$  以及  $0.9 \times z_1 \leq z \leq 1.1 \times z_1$ 。

[0136] 根據本發明的一個方式，能夠實現 CAAC 比率高的氧化物半導體膜。就是說，能夠實現品質良好的 CAAC-OS 膜。此外，根據本發明的一個方式，可以實現觀察到尖晶石型結晶結構的區域沒有或極少的 CAAC-OS 膜。在此，CAAC 比率較佳為 95% 以上，更佳為 97% 以上且 100% 以下。

[0137] 當利用濺射法形成氧化物半導體膜時，形成之後的膜的原子個數比有時與靶材的原子個數比不一致。尤其是，形成之後的膜中的鋅的原子個數比有時小於靶材中的鋅的原子個數比。明確而言，該膜中的鋅的原子個數比有時為靶材中的鋅的原子個數比的 40% 以上且 90% 以下左右。在此，所使用的靶材較佳為多晶。

[0138] 在此，描述關於銦、鎵及鋅對靶材的原子個

數比與藉由濺射法得到的氧化物半導體膜的原子個數比的關係進行調查的結果。表 1 示出所使用的靶材的原子個數比以及藉由濺射法得到的氧化物半導體膜的原子個數比。

[0139]

[表 1]

| 靶材的原子個數比 In : Ga : Zn | 膜的原子個數比 |      |      |

|-----------------------|---------|------|------|

|                       | In      | Ga   | Zn   |

| 1 : 1 : 1             | 1       | 0.99 | 0.66 |

| 1 : 1 : 1.2           | 1       | 0.98 | 0.84 |

| 1 : 1 : 1.5           | 1       | 0.92 | 1.04 |

| 1 : 3 : 2             | 1       | 2.89 | 1.24 |

| 1 : 3 : 4             | 1       | 3.02 | 2.56 |

| 1 : 3 : 6             | 1       | 3.06 | 4.19 |

| 3 : 1 : 2             | 3       | 0.98 | 1.40 |

| 3 : 1 : 3             | 3       | 1.01 | 2.30 |

[0140] 作為成膜條件，將氬及氧用作成膜氣體，並將氧流量比設定為 33%。在此氧流量比是指以氧流量  $\div$  ( 氧流量 + 氬流量 )  $\times 100[\%]$  表示的量。此外，壓力為 0.4Pa 至 0.7Pa，基板溫度為 200°C 至 300°C，電源功率為 0.5kW ( DC ) 。

[0141] 藉由 ICP-MS ( Inductively Coupled Plasma Mass Spectrometry，電感耦合電漿質譜分析法) 對使用各個原子個數比的靶材得到的氧化物半導體膜的各元素的濃度進行評價。圖 31A 至圖 31C 示出靶材的原子個數比與鋅的殘留率的關係。圖 31A 至圖 31C 中的數字表示靶材的銦 : 鎮 : 鋅的原子個數比，縱軸表示鋅的殘留率。在此

說明鋅的殘留率。將藉由成膜得到的膜的鋅的原子個數比除以銦、鎵及鋅的原子個數比的和的值稱為  $Zn$  (Film)。另外，將靶材的鋅的原子個數比除以靶材的銦、鎵及鋅的原子個數比的和的值稱為  $Zn$  (Target)。在此，將鋅的殘留率定義為以  $A = Zn(Film) \div Zn(Target) \times 100[\%]$  表示的值。圖 31A 的橫軸表示靶材的相對於鎵的原子個數比的鋅的原子個數比 ( $Zn/Ga$ )，圖 31B 的橫軸表示靶材的相對於銦的原子個數比的鎵的原子個數比 ( $Ga/In$ )，圖 31C 的橫軸表示靶材的相對於銦的原子個數比的鋅的原子個數比 ( $Zn/In$ )。各個圖式的縱軸表示鋅的殘留率  $A$ 。

[0142] 由圖 31A 至圖 31C 可知，藉由濺射法得到的氧化物半導體膜的鋅的殘留率大致在 50% 以上且 90% 以下的範圍內。就是說，可知與靶材的原子個數比相比鋅大幅度地減少。另外，由表 1 所記載的銦及鎵的原子個數比可知，與鋅相比，銦及鎵從靶材的原子個數比幾乎沒有變化。此外，例如在靶材的相對於鎵的鋅的原子個數比 ( $Zn/Ga$ ) 為 1 的情況下，鋅的殘留率  $A$  大約為 66%，在 2 的情況下  $A$  大約為 74%，在 3 的情況下  $A$  大約為 83%。

[0143] 由圖 31A 可知，在靶材的相對於鎵的鋅的原子個數比 ( $z/y$ ) 與鋅的殘留率之間有良好的關係。就是說，相對於鎵的鋅的量越少，殘留率越低。

[0144] 在此，在氧化物半導體膜的銦、鎵及鋅的原子個數比  $x$ 、 $y$  及  $z$  滿足算式 (1) 的情況下，有時可以進

一步提高氧化物半導體膜的 CAAC 比率。

[0145] 作為滿足算式 (1) 的原子個數比的例子，考慮到  $x : y : z = 4 : 2 : 3$ 、 $x : y : z = 1.1 : 2.9 : 6$ 、 $x : y : z = 1 : 2 : 3$  這三個例子。

[0146] 例如，藉由採用  $x : y : z = 4 : 2 : 3$ ，可以使銻的原子個數比增加到鎵的 2 倍，由此可以提高銻的含有率。因此，有時能夠獲得高移動率。

[0147] 例如，藉由採用  $x : y : z = 1.1 : 2.9 : 6$ ，可以滿足算式 (1) 並在有可能呈現在圖 1A 和圖 1B 中以粗線表示的固溶區域的範圍內，由此有時能夠獲得高 CAAC 比率，所以是較佳的。此外，藉由減少銻的含有率，可以減少電子親和力。例如，因為具有  $x : y : z = 1.1 : 2.9 : 6$  的原子個數比的氧化物半導體膜的銻的含有率比具有區域 12 或區域 13 的原子個數比的氧化物半導體膜低，所以可以使電子親和力較小。

[0148] 同樣地，例如，藉由採用  $x : y : z = 1 : 2 : 3$ ，可以滿足算式 (1) 並在有可能為固溶區域的範圍內，由此有時能夠獲得高 CAAC 比率，所以是較佳的。此外，因為具有  $x : y : z = 1 : 2 : 3$  的原子個數比的氧化物半導體膜的銻的含有率比具有區域 12 或區域 13 的原子個數比的氧化物半導體膜低，所以可以使電子親和力較小。

[0149] 將靶材的銻、鎵及鋅的原子個數比設定為  $a$ 、 $b$  及  $c$ 。由圖 31A 至圖 31C 可知，鋅的殘留率  $A$  與  $b$  及  $c$  滿足以如下算式 (7) 表示的近似式。

[0150]

[算式 7]

$$A[\%] = \{0.0811 \times (c/b) + 0.5825\} \times 100 \quad (7)$$

[0151] 由此，如果假定銦及鎵的殘留率為 100%，則在使用  $In : Ga : Zn = a : b : c$  的靶材藉由濺射法形成氧化物半導體膜的情況下，所得到的氧化物半導體膜滿足原子個數比  $x : y : z = a : b : \{0.0811 \times (c/b) + 0.5825\} \times c$ 。

[0152] 在此，在使所得到的氧化物半導體膜的銦、鎵及鋅滿足原子個數比  $x : y : z = 4 : 2 : 3$  的情況下，靶材的鋅的原子個數比  $c$  滿足如下算式 (3) 即可。注意， $a = x = 4$ 、 $b = y = 2$ 、 $z = 3$ 。

[0153]

[算式 8]

$$3 = \{0.0811 \times (c/2) + 0.5825\} \times c \quad (8)$$

[0154] 算式 (8) 為  $c$  的 2 次方程式，求出其解是 4.0234 及 -18.3883。由於在此負值不適合，所以為了滿足  $x : y : z = 4 : 2 : 3$  而滿足  $a : b : c = 4 : 2 : 4$  即可。

[0155] 同樣地，為了滿足  $x : y : z = 1.1 : 2.9 : 6$  而滿足  $a : b : c = 1.1 : 2.9 : 7.6$  即可，為了滿足  $x : y : z = 1 : 2 : 3$  而滿足  $a : b : c = 1 : 2 : 4$  即可。

[0156] 另外，例如，為了得到圖 2A 和圖 2B 所示的區域 12 的氧化物半導體膜，靶材中的鋅的原子個數比較佳為多於圖 2A 和圖 2B 所示的區域 12。在此，將靶材所包含的銦、元素 M 及鋅的原子個數比設定為  $a : b : c$ 。在

此，為了將藉由濺射法得到的氧化物半導體膜的銨、元素 M 及鋅的原子個數比設定為  $x : y : z$ ，在  $c/b$  為 1 的情況下，例如使  $c/(a+b+c)$  的值成為  $z/(x+y+z)$  的大約 1.5 倍 ( $100 \div 66 = 1.51$ ) 即可，在  $c/b$  為 2 的情況下，例如使  $c/(a+b+c)$  的值成為  $z/(x+y+z)$  的大約 1.35 倍 ( $100 \div 74 = 1.35$ ) 即可，在  $c/b$  為 3 的情況下，例如使  $c/(a+b+c)$  的值成為  $z/(x+y+z)$  的大約 1.20 倍 ( $100 \div 83 = 1.20$ ) 即可。

[0157] 藉由將氧化物半導體膜的原子個數比設定為區域 12 的範圍，可以進一步提高 CAAC 比率，所以是較佳的。

[0158] 因此，為了獲得 CAAC 比率更高的氧化物半導體膜，如果靶材的原子個數比滿足  $c/b \geq 2$ ，則例如使  $c/(a+b+c)$  的值成為  $z/(x+y+z)$  的大約 1.4 倍即可。明確而言，靶材的原子個數比例如較佳為滿足圖 4 所示的區域 14 的範圍內的值。在此，區域 14 是具有依次連接第一座標 A ( $a : b : c = 2 : 2 : 1$ )、第二座標 B ( $a : b : c = 23 : 27 : 25$ )、第三座標 S ( $a : b : c = 2 : 4 : 15$ )、第四座標 T ( $a : b : c = 2 : 0 : 5$ )、第五座標 E ( $a : b : c = 2 : 0 : 3$ )、第六座標 F ( $a : b : c = 7 : 1 : 8$ )、第七座標 G ( $a : b : c = 15 : 5 : 8$ ) 以及上述第一座標 A 的範圍內的原子個數比的區域。注意，區域 14 包括線上的座標。

[0159] 在此，作為本發明的一個方式的氧化物半導體膜也可以層疊多個膜。另外，多個膜的每一個的 CAAC

比率也可以彼此不同。此外，被層疊的多個膜中的至少一層的膜的 CAAC 比率例如較佳為高於 90%，更佳為 95% 以上，進一步較佳為 97% 以上且 100% 以下。

[0160] 在此，說明氧化物半導體膜的膜密度。

[0161]

[膜密度評價結果]

CAAC-OS 膜包含 c 軸配向的多個結晶部，並且觀察不到結晶部與結晶部之間的明確的邊界，從而可以得到緻密的膜。對藉由濺射法作為靶材使用原子個數比為 In : Ga : Zn = 1 : 1 : 1 的 In-Ga-Zn 氧化物形成的 CAAC-OS 膜以及使用原子個數比為 In : Ga : Zn = 2 : 1 : 3 的 In-Ga-Zn 氧化物形成的 CAAC-OS 膜的膜密度進行評價，其密度都大約為  $6.3 \text{ g/cm}^3$ 。在後面的實施例中描述詳細的條件。採用氧流量比為 33%，成膜時的基板溫度為 200°C 以上且 300°C 以下的條件。膜密度藉由 X 射線反射率 (XRR : X-Ray Reflectivity) 法而被求出。

[0162] 另一方面，根據氧化物半導體膜的形成條件而可以得到膜密度低的膜。此外，隨著膜密度的下降，有時可以得到包含所謂的空洞的膜。在此空洞例如是指密度極低的區域或空間。這樣的膜的結晶性低，有時容易俘獲雜質，而難以得到良好的電晶體特性。

[0163] 在此，說明空洞多的膜的膜密度。例如，藉由使用濺射法，採用氧流量比低的條件，並以低基板溫度進行成膜，有時形成空洞多的膜。藉由採用表 2 所示的條

件並利用濺射法，形成氧化物半導體膜。作為靶材，使用原子個數比為  $In : Ga : Zn = 1 : 1 : 1$  的  $In-Ga-Zn$  氧化物。作為電源，使用 RF 電源。

[0164]

[表 2]

| 電源功率 | 氣體流量         |                          | 基板溫度<br>[°C] | 壓力<br>[Pa] |

|------|--------------|--------------------------|--------------|------------|

|      | Ar<br>[sccm] | O <sub>2</sub><br>[sccm] |              |            |

| 條件 C | 100W         | 98                       | 2            | 室溫         |

| 條件 D | 100W         | 98                       | 2            | 室溫         |

[0165] 表 2 所示的條件 C 的成膜率為  $0.48\text{nm}/\text{分}$ ，條件 D 的成膜率為  $1.78\text{nm}/\text{分}$ 。

[0166] 表 3 是對使用表 2 所示的條件 C 及條件 D 形成的氧化物半導體膜的膜密度進行測量的結果。

[0167]

[表 3]

|      | 膜密度<br>[g/cm <sup>3</sup> ] |

|------|-----------------------------|

| 條件 C | 5.57                        |

| 條件 D | 6.10                        |

[0168] 條件 C、條件 D 都示出膜密度低的傾向。可以認為：這是因為氧流量比低即 2%，且成膜溫度低。此外，在與條件 D 相比成膜壓力高的條件 C 中，示出膜密度更低的結果。

[0169]

[膜中氫濃度]

接著，圖 32 示出採用條件 C 及條件 D 形成的氧化物半導體膜的膜中氫濃度。在條件 C 中得到氫濃度顯著高的結果。

[0170] 圖 33A 和圖 33B 示出採用條件 C 及條件 D 形成的氧化物半導體膜的觀察剖面 TEM 影像的結果。圖 33A 是採用條件 C 的膜的剖面 TEM 影像，圖 33B 是採用條件 D 的膜的剖面 TEM 影像。在條件 C 中觀察到膜稀疏的部分，所謂的空洞。以虛線圍繞觀察到空洞的區域的一個例子而示出。

[0171] 圖 34A 和圖 34B 示出採用條件 C 及條件 D 形成的氧化物半導體膜的 TDS ( Thermal Desorption Spectroscopy：熱脫附譜分析法) 分析結果。圖 34A 和圖 34B 示出分子量=18 時的釋放量。圖 34A 是採用條件 C 的膜的結果，圖 34B 是採用條件 D 的膜的結果。在採用膜密度低的條件 C 形成的氧化物半導體膜中，顯著地觀察到 TDS 分析的分子量=18 時的釋放，由此可以認為  $H_2O$  即水的釋放。就是說，可以認為水分的吸附多的膜。

[0172] 為了詳細地調查水分的吸附，對採用條件 C 形成的氧化物半導體膜進行 TDS 分析，將該氧化物半導體膜放在平均溫度  $24^\circ C$  且平均濕度  $61^\circ C$  的大氣中 24 小時，然後再次進行 TDS 分析。圖 35A 和圖 35B 示出其結果。圖 35A 示出第一次的分析結果，圖 35B 示出放在大

氣之後的分析結果即第二次的分析結果。在第二次分析中，再次觀察到起因於分子量 18 的峰值。由此可知，因第一次 TDS 分析而氧化物半導體膜中的水分被釋放，之後在大氣中再次吸附水分。就是說，可以說密度低且包含空洞的膜容易吸附水分。

[0173]

### 實施方式 2

在本實施方式中，對使用作為本發明的一個方式的氧化物半導體的電晶體的一個例子進行說明。

[0174] 在使用習知的矽、鎗及其化合物的電晶體中，尤其在具有微小的通道長度的元件中，為了抑制短通道效應而較佳為增強閘極電場，為了增強閘極電場而較佳為進行閘極絕緣膜的薄膜化。

[0175] 另一方面，使用氧化物半導體膜的電晶體是以電子為多數載子的積累型電晶體。由此，該電晶體與具有  $pn$  接面的反轉型電晶體相比作為短通道效應之一的 DIBL (Drain-Induced Barrier Lowering，汲極導致的能障降低) 的影響小。換言之，使用氧化物半導體膜的電晶體具有對短通道效應的耐性。

[0176] 因為使用氧化物半導體膜的電晶體對短通道效應的耐性高，所以與使用矽等的習知的電晶體相比可以使閘極絕緣膜增厚。例如，在通道長度及通道寬度為 50nm 以下的微型電晶體中也可以使用 10nm 左右的厚閘極絕緣膜。在此，藉由使閘極絕緣膜增厚，可以減少寄生電

容。由此，有時可以提高電路的動態特性。此外，藉由使閘極絕緣膜增厚，有時減少洩漏電流並降低耗電量。

[0177] 由於隨著通道長度的微型化而使漏電場增強，所以在使用矽等的習知的電晶體中，尤其在具有微型的通道長度的情況下明顯看出熱載子劣化導致的可靠性的下降。另一方面，在氧化物半導體中，能帶間隙大（例如，包含銦、鎵及鋅的氧化物半導體的能帶間隙為 2.5eV 以上），不容易激發電子，電洞的有效質量大。由此，與習知的使用矽等的電晶體相比，有時不容易發生突崩潰（avalanche breakdown）等。因此，例如有時可以抑制起因於突崩潰的熱載子劣化等。

[0178] 藉由使閘極絕緣膜增厚，可以提高閘極絕緣膜的耐壓，由此能夠以更高閘極電壓驅動電晶體。此外，藉由抑制熱載子劣化，能夠以高汲極電壓驅動電晶體而不使通道長度增加。因此，可以在輸入高電壓的電路中提高電晶體的可靠性的同時使通道長度縮小，從而能夠提高電路的集成度。

[0179] 另外，在使用本質或實質上本質的氧化物半導體膜的電晶體中，當源極電極與汲極電極間的距離充分小時，受源電場及漏電場的影響導帶底的能量變低，導帶底的能量與費米能階接近。將該現象稱為 Conduction Band Lowering Effect（導帶降低效應，CBL 效應）。由於 CBL 效應而以  $V_g$ - $I_d$  特性上的 0V 附近的低閘極電壓開始流過汲極電流，因此有時能夠降低電晶體的驅動電壓。

[0180] 在此，作為氧化物半導體膜，較佳為使用 CAAC-OS 膜。CAAC-OS 膜的 CAAC 比率較佳為高。藉由提高 CAAC 比率，例如可以減小電晶體的載子散射的影響，因此可以獲得高的場效移動率。此外，因為可以減小晶界的影響，所以可以降低電晶體的導通特性的偏差。因此，可以得到可靠性高的半導體裝置。另外，藉由使用偏差小的電晶體而減小驅動電壓，可以減少耗電量。另外，例如可以實現缺陷密度低的 CAAC-OS 膜。可以實現雜質少的 CAAC-OS 膜。藉由減少缺陷密度，例如可以實現極低的關閉電流特性。

[0181]

[使用氧化物半導體膜的電晶體]

參照圖 5A 至圖 5C 說明使用氧化物半導體膜的電晶體的一個例子。

[0182] 圖 5A 示出電晶體 100 的俯視圖。圖 5B 示出沿著圖 5A 所示的點劃線 X-X' 的剖面，圖 5C 示出沿著圖 5A 所示的點劃線 Y-Y' 的剖面。圖 5A 至圖 5C 所示的電晶體 100 包括：半導體層 101；導電層 104a 及導電層 104b；半導體層 101 上的閘極絕緣膜 102；以及隔著閘極絕緣膜 102 重疊於半導體層 101 的閘極電極 103。以覆蓋電晶體 100 的方式設置有絕緣膜 112 及絕緣膜 113。電晶體 100 還可以包括導電層 105。在此，如圖 5A 至圖 5C 所示，電晶體 100 較佳為設置在基板 50 上。此外，也可以在基板與電晶體 100 之間包括接觸於基板 50 的頂面的絕

緣膜 51 以及接觸於絕緣膜 51 的頂面的絕緣膜 114。在圖 5A 至圖 5C 中，半導體層 101 與絕緣膜 114 的頂面接觸。在基板 50 與絕緣膜 114 之間也可以不設置絕緣膜。

[0183] 半導體層 101 也可以以單層形成，如圖 5A 至圖 5C 所示，較佳為以半導體層 101a、半導體層 101b 及半導體層 101c 的疊層結構形成。在此情況下，圖 5A 至圖 5C 所示的電晶體 100 包括：半導體層 101a；接觸於半導體層 101a 的頂面的半導體層 101b；接觸於半導體層 101b 的頂面並在重疊於半導體層 101b 的區域隔開的導電層 104a 及導電層 104b；接觸於半導體層 101b 的頂面的半導體層 101c；半導體層 101c 上的閘極絕緣膜 102；以及隔著閘極絕緣膜 102 及半導體層 101c 重疊於半導體層 101b 的閘極電極 103。半導體層 101a 設置在絕緣膜 114 與半導體層 101b 之間。半導體層 101c 設置在半導體層 101b 與閘極絕緣膜 102 之間。導電層 104a 及導電層 104b 接觸於半導體層 101b 的頂面及半導體層 101c 的底面。

[0184] 導電層 104a 及導電層 104b 具有用作源極電極或汲極電極的功能。另外，也可以對導電層 105 施加比源極電極低的電壓或比源極電極高的電壓而使電晶體的臨界電壓向正方向或負方向變動。例如，藉由使電晶體的臨界電壓向正方向變動，有時即便閘極電壓為 0V 也能夠實現電晶體成為非導通狀態（關閉狀態）的常關閉（normally-off）。注意，施加到導電層 105 的電壓既可為可變，又可為恆定。在施加到導電層 105 的電壓為可變

的情況下，也可以使控制電壓的電路與導電層 105 連接。另外，導電層 105 也可以與閘極電極 103 連接。

[0185] 作為設置在電晶體中的導電層 104a 及導電層 104b，可以使用鎢、鈦、鋁、銅、鉬、鉻或鉭或者其合金等容易與氧鍵合的導電材料。其結果，半導體層 101 所包含的氧與導電層 104a 及導電層 104b 所包含的導電材料鍵合，在半導體層 101 中形成氧缺陷區域。另外，有時在半導體層 101 中混入形成導電層 104a 及導電層 104b 的導電材料的構成元素的一部分。其結果，第一低電阻區域及第二低電阻區域形成在半導體層 101 中的與導電層 104a 及導電層 104b 接觸的區域附近。由於第一低電阻區域及第二低電阻區域的導電性高，所以可以降低半導體層 101 與導電層 104a 及導電層 104b 之間的接觸電阻，因此可以增大電晶體的通態電流 (on-state current)。

[0186] 另外，第一低電阻區域及第二低電阻區域的端部也可以與導電層 104a、導電層 104b 的端部大致一致。或者，第一低電阻區域及第二低電阻區域的端部位於導電層 104a 及導電層 104b 的端部的內側。當在半導體層 101 中形成第一低電阻區域及第二低電阻區域時，通道長度是半導體層 101 和閘極絕緣膜 102 之間的介面上的第一低電阻區域及第二低電阻區域之間的距離。

[0187] 作為半導體層 101b，較佳為使用電子親和力比半導體層 101a 及半導體層 101c 大的氧化物。例如，作為半導體層 101b，使用電子親和力比半導體層 101a 及半

導體層 101c 大 0.07eV 以上且 1.3eV 以下，較佳為大 0.1eV 以上且 0.7eV 以下，更佳為大 0.15eV 以上且 0.4eV 以下的氧化物。注意，電子親和力是指真空能階與導帶底的能量之間的差異。

[0188] 藉由作為半導體層 101b 使用電子親和力大於半導體層 101a 及半導體層 101c 的氧化物，在對閘極電極施加電場時，在半導體層 101a、半導體層 101b 和半導體層 101c 中的電子親和力較大的半導體層 101b 中形成通道。在此，藉由在半導體層 101b 中形成通道，例如通道形成區域從與閘極絕緣膜 102 之間的界面遠離，由此可以減小與閘極絕緣膜之間的界面的散射的影響。因此，可以提高電晶體的場效移動率。在此，因為半導體層 101b 與半導體層 101c 如後面所述構成元素相同，所以幾乎沒有發生界面散射。

[0189] 此外，在使用氧化矽膜、氧氮化矽膜、氮氧化矽膜或氮化矽膜等作為閘極絕緣膜的情況下，包含在閘極絕緣膜中的矽有可能混入氧化物半導體膜中。如果矽混入氧化物半導體膜中，則會導致氧化物半導體膜的結晶性下降、載子移動率下降等。因此，為了降低形成有通道的半導體層 101b 的雜質濃度，例如矽濃度，較佳為在半導體層 101b 與閘極絕緣膜之間設置半導體層 101c。由於同樣的理由，為了降低從絕緣膜 114 擴散雜質的影響，較佳為在半導體層 101b 與絕緣膜 114 之間設置半導體層 101a。

[0190] 半導體層 101b 例如是包含銦的氧化物半導體。在半導體層 101b 包含銦時，例如其載子移動率（電子移動率）提高。另外，半導體層 101b 較佳為包含元素 M。元素 M 較佳為鋁、鎵、釔或錫等。作為可用作元素 M 的其他元素，有硼、矽、鈦、鐵、鎳、鎗、釔、鋯、鋁、鑭、鈰、釤、鉻、鎢等。注意，作為元素 M 有時也可以組合多個上述元素。元素 M 例如是與氧的鍵能高的元素。元素 M 例如是與氧的鍵能高於銦的元素。或者，元素 M 例如是具有增大氧化物半導體的能隙的功能的元素。此外，半導體層 101b 較佳為包含鋅。當氧化物半導體包含鋅時，有時容易晶化。

[0191] 作為半導體層 101b 例如使用能隙大的氧化物。半導體層 101b 的能隙例如是 2.5eV 以上且 4.2eV 以下，較佳為 2.7eV 以上且 3.7eV 以下，更佳為 2.8eV 以上且 3.3eV 以下。

[0192] 在此，作為半導體層 101b，較佳為使用 CAAC-OS 膜。藉由使用 CAAC-OS 膜，能夠實現載子散射小且場效移動率高的電晶體。另外，較佳為提高半導體層 101b 的 CAAC 比率。例如，CAAC 比率較佳為 90% 以上，更佳為 95% 以上，進一步較佳為 97% 以上且 100% 以下。

[0193] 接著，說明半導體層 101a 及半導體層 101c。例如，半導體層 101a 及半導體層 101c 是包含一種或多種構成半導體層 101b 的除了氧之外的元素的氧化物半導

體。因為半導體層 101a 及半導體層 101c 包含一種或多種構成半導體層 101b 的除了氧之外的元素，所以不容易在半導體層 101a 與半導體層 101b 的介面以及半導體層 101b 與半導體層 101c 的介面處形成界面能階。

[0194] 在此，半導體層 101a 及半導體層 101c 較佳為使用 CAAC-OS 膜。

[0195] 例如，藉由將包括 c 軸配向的多個結晶部的 CAAC-OS 膜用作半導體層 101a，層疊在其上的半導體層 101b 在與半導體層 101a 之間的介面附近也可以形成具有良好的 c 軸配向的區域。

[0196] 此外，藉由提高 CAAC-OS 膜的 CAAC 比率，例如可以進一步減少缺陷。例如，可以減少具有尖晶石型結構的區域。例如，可以降低載子的散射。例如，可以形成對雜質具有高阻擋性的膜。因此，藉由提高半導體層 101a 及半導體層 101c 的 CAAC 比率，在與形成有通道的半導體層 101b 之間形成良好的介面，由此可以將載子散射抑制為小。另外，能夠抑制雜質混入到半導體層 101b 並減少半導體層 101b 的雜質濃度。

[0197] 在此，圖 20A 示出能帶結構。圖 20A 示出真空能階（記為“vacuum level”）、各層的導帶底的能量（記為“Ec”）以及價帶頂（記為“Ev”）。

[0198] 在此，在半導體層 101a 與半導體層 101b 之間有時存在半導體層 101a 和半導體層 101b 的混合區域。此外，在半導體層 101b 與半導體層 101c 之間有時存在半

導體層 101b 和半導體層 101c 的混合區域。混合區域的介面態密度低。因此，在半導體層 101a、半導體層 101b 及半導體層 101c 的疊層體具有各層之間的介面附近的能力連續地變化（也稱為連接結合）的能帶結構。

[0199] 注意，圖 20A 示出半導體層 101a 的  $E_c$  與半導體層 101c 的  $E_c$  相同的情況，但是也可以相互不同。例如，半導體層 101c 的  $E_c$  也可以具有比半導體層 101a 的  $E_c$  高的能量。

[0200] 此時，電子不是在半導體層 101a 及半導體層 101c 中而主要在半導體層 101b 中移動（參照圖 20B）。如上所述，藉由降低半導體層 101a 與半導體層 101b 的介面處的介面態密度、半導體層 101b 與半導體層 101c 的介面處的介面態密度，在半導體層 101b 中妨礙電子移動的情況減少，從而可以提高電晶體的通態電流。

[0201] 如圖 5B 所示，半導體層 101b 的側面與導電層 104a 及導電層 104b 接觸。此外，如圖 5C 所示，可以由閘極電極 103 的電場電圍繞半導體層 101b（將導電體的電場電圍繞半導體的電晶體結構稱為圍繞通道（surrounded channel, s-channel）結構）。因此，有時在整個半導體層 101b 中（塊內）形成通道。在 s-channel 結構中可以使大電流流在電晶體的源極-汲極間，可以提高導通時的電流（通態電流）。

[0202] 由於可以得到高的通態電流，因此 s-channel 結構可以說是適合於微型電晶體的結構。包括微型電晶體

的半導體裝置可以具有高集成度及高密度。例如，電晶體的通道長度較佳為 40nm 以下，更佳為 30nm 以下，進一步較佳為 20nm 以下，並且，電晶體的通道寬度較佳為 40nm 以下，更佳為 30nm 以下，進一步較佳為 20nm 以下。

[0203] 注意，例如，通道長度是指在電晶體的俯視圖中，半導體（或在電晶體處於開啟狀態時，在半導體中電流流動的部分）與閘極電極重疊的區域或形成有通道的區域中的源極（源極區域或源極電極）與汲極（汲極區域或汲極電極）之間的距離。另外，在一個電晶體中，通道長度在所有區域中不一定為相同。換言之，一個電晶體的通道長度有時不侷限於一個值。因此，在本說明書中，通道長度是形成通道的區域中的任一個值、最大值、最小值或平均值。

[0204] 例如，通道寬度是指半導體（或在電晶體處於開啟狀態時，在半導體中電流流動的部分）與閘極電極重疊的區域或形成有通道的區域中的源極與汲極相對的部分的長度。另外，在一個電晶體中，通道寬度在所有區域中不一定為相同。換言之，一個電晶體的通道寬度有時不侷限於一個值。因此，在本說明書中，通道寬度是形成有通道的區域中的任一個值、最大值、最小值或平均值。

[0205] 另外，在有的電晶體結構中，有時形成有通道的區域中的實際上的通道寬度（下面稱為實效通道寬度）不同於電晶體的俯視圖所示的通道寬度（下面稱為外

觀上的通道寬度）。例如，在具有立體結構的電晶體中，有時因為實效通道寬度大於電晶體的俯視圖所示的外觀上的通道寬度，所以不能忽略其影響。例如，在具有立體結構的微型電晶體中，有時形成在半導體側面中的通道區域的比例大於形成在半導體頂面中的通道區域的比例。在此情況下，形成有通道的實際上的實效通道寬度大於俯視圖所示的外觀上的通道寬度。

[0206] 在具有立體結構的電晶體中，有時難以藉由實測來估計實效通道寬度。例如，為了根據設計值估計實效通道寬度，需要一個假設，即已知半導體的形狀。因此，當半導體的形狀不確定時，難以正確地測定實效通道寬度。

[0207] 因此，在本說明書中，有時將在電晶體的俯視圖中半導體與閘極電極重疊的區域中的源極與汲極相對的部分的長度，即外觀上的通道寬度稱為“圍繞通道寬度（SCW：Surrounded Channel Width）”。此外，在本說明書中，在簡單地描述為“通道寬度”時，有時是指圍繞通道寬度或外觀上的通道寬度。或者，在本說明書中，在簡單地描述為“通道寬度”時，有時是指實效通道寬度。注意，藉由對剖面 TEM 影像等進行分析等，可以決定通道長度、通道寬度、實效通道寬度、外觀上的通道寬度、圍繞通道寬度等的值。

[0208] 另外，在藉由計算求得電晶體的場效移動率或每個通道寬度的電流值等時，有時使用圍繞通道寬度來

計算。在此情況下，該值有時不同於使用實效通道寬度計算的值。

[0209] 在此，雖然圖 5A 至圖 5C 示出作為氧化物半導體層疊半導體層 101a、半導體層 101b 及半導體層 101c 的三層的例子，但是也可以將氧化物半導體的單層用於電晶體 100。此外，也可以採用不具有半導體層 101a、半導體層 101b 和半導體層 101c 中的一個或兩個的結構。

[0210] 半導體層 101a、半導體層 101b 及半導體層 101c 較佳為至少包含銦。另外，在半導體層 101a 是 In-M-Zn 氧化物的情況下，在 In 和 M 的總和為 100atomic% 時，較佳的是：In 為低於 50atomic%，M 為 50atomic% 以上，更佳的是：In 為低於 25atomic%，M 為 75atomic% 以上。此外，在半導體層 101b 是 In-M-Zn 氧化物的情況下，在 In 和 M 的總和為 100atomic% 時，較佳的是：In 為 25atomic% 以上，M 為低於 75atomic%，更佳的是：In 為 34atomic% 以上，M 為低於 66atomic%。此外，在半導體層 101c 是 In-M-Zn 氧化物的情況下，在 In 和 M 的總和為 100atomic% 時，較佳的是：In 為低於 50atomic%，M 為 50atomic% 以上，更佳的是：In 為低於 25atomic%，M 為 75atomic% 以上。另外，半導體層 101c 也可以使用與半導體層 101a 相同的種類的氧化物。

[0211] 注意，銦鎵氧化物的電子親和力小，其氧阻擋性高。因此，例如半導體層 101c 也可以包含銦鎵氧化物。鎵原子的比率 [Ga / (In+Ga)] 例如為 70% 以上，較佳

為 80% 以上，更佳為 90% 以上。

[0212] 在此，作為半導體層 101b，使用電子親和力比半導體層 101a 及半導體層 101c 大 0.07eV 以上且 1.3eV 以下，較佳為大 0.1eV 以上且 0.7eV 以下，更佳為大 0.15eV 以上且 0.4eV 以下的氧化物。

[0213] 為了獲得具有高的 CAAC 比率的更優良的 CAAC-OS 膜，例如在半導體層 101b 包含銦、元素 M 及鋅的情況下，銦、元素 M 及鋅的原子個數比  $x : y : z$  較佳為實施方式 1 所示的圖 2A 和圖 2B 的區域 12 的範圍內的值，更佳為區域 13 所示的範圍內的值。

[0214] 半導體層 101a、半導體層 101b 及半導體層 101c 較佳為不包含尖晶石型結晶結構或者尖晶石型結晶結構很少。另外，半導體層 101a、半導體層 101b 及半導體層 101c 較佳為 CAAC-OS 膜。

[0215] 在此，作為更具體的例子，考慮到半導體層 101a、半導體層 101b 及半導體層 101c 分別為包含銦、元素 M 及鋅的氧化物的情況。在此，將半導體層 101a 的銦、元素 M 及鋅的原子個數比設定為銦：元素 M：鋅  $= x_a : y_a : z_a$ 。同樣地，將半導體層 101b 的銦、元素 M 及鋅的原子個數比設定為銦：元素 M：鋅  $= x_b : y_b : z_b$ ，將半導體層 101c 的銦、元素 M 及鋅的原子個數比設定為銦：元素 M：鋅  $= x_c : y_c : z_c$ 。

[0216] 半導體層 101a 及半導體層 101c 較佳為不包含尖晶石型結晶結構或者尖晶石型結晶結構很少。因此，

$x_a : y_a : z_a$  及  $x_c : y_c : z_c$  例如較佳為在圖 1B 的區域 11 的範圍內。作為半導體層 101b，較佳為使用電子親和力比半導體層 101a 及半導體層 101c 大的氧化物。

[0217] 由此， $x_a : y_a : z_a$  及  $x_c : y_c : z_c$  例如較佳為在區域 11 的範圍內，且其電子親和力較佳為小於半導體層 101b。

[0218] 在此，為了使半導體層 101b 的電子親和力大於半導體層 101a 及半導體層 101c，例如較佳為使半導體層 101b 的錫的含有率大於半導體層 101a 及半導體層 101c。例如，較佳為滿足  $x_b / (x_b + y_b + z_b) > x_a / (x_a + y_a + z_a)$  及  $x_b / (x_b + y_b + z_b) > x_c / (x_c + y_c + z_c)$ 。

[0219] 或者，較佳的是，半導體層 101a 例如在區域 11 的範圍內且滿足  $x_a \leq 2y_a$ 。此外，更佳的是，半導體層 101c 例如在區域 11 的範圍內且滿足  $x_c \leq y_c$ 。

[0220] 同樣地，較佳的是，半導體層 101c 例如在區域 11 的範圍內且滿足  $x_c \leq 2y_c$ 。此外，更佳的是，半導體層 101c 例如在區域 11 的範圍內且滿足  $x_c \leq y_c$ 。

[0221] 就是說，半導體層 101a 較佳為具有依次連接座標 K (8 : 14 : 7)、座標 L (2 : 5 : 7)、座標 M (51 : 149 : 300)、座標 N (46 : 288 : 833)、座標 O (0 : 2 : 11)、座標 P (0 : 0 : 1)、座標 A (2 : 2 : 1) 以及上述座標 K 的範圍內的原子個數比。

[0222] 半導體層 101c 較佳為具有依次連接座標 K (8 : 14 : 7)、座標 L (2 : 5 : 7)、座標 M (51 : 149 :

300)、座標 N (46: 288: 833)、座標 O (0: 2: 11)、座標 P (0: 0: 1)、座標 A (2: 2: 1) 以及上述座標 K 的範圍內的原子個數比。

[0223] 半導體層 101a 及半導體層 101c 較佳為具有依次連接座標 K (8: 14: 7)、座標 L (2: 5: 7)、座標 M (51: 149: 300)、座標 N (46: 288: 833)、座標 P (0: 0: 1)、座標 C (8: 12: 25)、座標 B (23: 27: 25)、座標 A (2: 2: 1) 以及上述座標 K 的範圍內的原子個數比。

[0224] 注意，當電晶體具有 s-channel 結構時，在整個半導體層 101b 中形成有通道。因此，半導體層 101b 的厚度越大，通道區域越大。即，半導體層 101b 越厚，越能夠提高電晶體的通態電流。例如，半導體層 101b 具有其厚度為 20nm 以上，較佳為 40nm 以上，更佳為 60nm 以上，進一步較佳為 100nm 以上的區域即可。注意，半導體裝置的生產率有時會下降，因此，例如，半導體層 101b 具有其厚度為 300nm 以下，較佳為 200nm 以下，更佳為 150nm 以下的區域即可。

[0225] 此外，為了提高電晶體的通態電流，半導體層 101c 的厚度越小越佳。例如，半導體層 101c 具有其厚度為低於 10nm，較佳為 5nm 以下，更佳為 3nm 以下的區域即可。另一方面，半導體層 101c 具有阻擋構成相鄰的絕緣體的氧之外的元素（氬、矽等）侵入形成有通道的半導體層 101b 中的功能。因此，半導體層 101c 較佳為具有

一定程度的厚度。例如，半導體層 101c 具有其厚度為 0.3nm 以上，較佳為 1nm 以上，更佳為 2nm 以上的區域即可。另外，為了抑制從閘極絕緣膜 102 等釋放的氧向外擴散，半導體層 101c 較佳為具有阻擋氧的性質。

[0226] 此外，為了提高可靠性，較佳為使半導體層 101a 變厚並使半導體層 101c 變薄。例如，半導體層 101a 具有其厚度例如為 10nm 以上，較佳為 20nm 以上，更佳為 40nm 以上，進一步較佳為 60nm 以上的區域即可。藉由將半導體層 101a 形成為厚，可以拉開從相鄰的絕緣體和半導體層 101a 的介面到形成有通道的半導體層 101b 的距離。注意，因為半導體裝置的生產率可能會下降，所以半導體層 101a 具有其厚度例如為 200nm 以下，較佳為 120nm 以下，更佳為 80nm 以下的區域即可。

[0227] 當氧化物半導體膜含有多量的氫時，有時起因於氫而形成施體能階。其結果，導致電晶體的臨界電壓向負向漂移。因此，較佳為藉由在形成氧化物半導體膜之後進行脫水化處理（脫氫化處理），從氧化物半導體膜中去除氫或水分以使其儘量不包含雜質來實現高度純化。

[0228] 另外，有時氧化物半導體膜中的氧也因脫水化處理（脫氫化處理）而被減少。因此，為了填補因對氧化物半導體膜的脫水化處理（脫氫化處理）而增加的氧缺陷，較佳為將氧添加到氧化物半導體膜。在本說明書等中，有時將對氧化物半導體膜供應氧的處理稱為加氧化處理，或者，有時將使氧化物半導體膜的氧含量超過化學計

量組成的處理稱為過氧化處理。

[0229] 如上所述，藉由進行脫水化處理（脫氫化處理）從氧化物半導體膜去除氫或水分，並進行加氧化處理以填補氧缺陷，可以得到被 i 型（本質）化的氧化物半導體膜或極其接近於 i 型而實質上呈 i 型（本質）的氧化物半導體膜。注意，“實質上本質”是指：在氧化物半導體膜中，來自於施體的載子極少（近於零），載子密度為  $1 \times 10^{17}/\text{cm}^3$  以下， $1 \times 10^{16}/\text{cm}^3$  以下， $1 \times 10^{15}/\text{cm}^3$  以下， $1 \times 10^{14}/\text{cm}^3$  以下， $1 \times 10^{13}/\text{cm}^3$  以下。

[0230] 如此，具備 i 型或實質上呈 i 型的氧化物半導體膜的電晶體可以實現極為優良的關態電流特性。例如，可以將使用氧化物半導體膜的電晶體處於關閉狀態時的汲極電流在室溫（25°C 左右）下設定為  $1 \times 10^{-18}\text{A}$  以下，較佳為  $1 \times 10^{-21}\text{A}$  以下，更佳為  $1 \times 10^{-24}\text{A}$  以下，或者，可以將汲極電流在 85°C 的溫度下設定為  $1 \times 10^{-15}\text{A}$  以下，較佳為  $1 \times 10^{-18}\text{A}$  以下，更佳為  $1 \times 10^{-21}\text{A}$  以下。注意，“電晶體處於關閉狀態”是指：在採用 n 通道型電晶體的情況下，閘極電壓充分小於臨界電壓的狀態。明確而言，在閘極電壓比臨界電壓小 1V 以上、2V 以上或 3V 以上時，電晶體成為關閉狀態。

[0231] 在此，藉由元件模擬計算因電晶體的半導體的形狀不同而產生的電特性的差異。圖 65A 至圖 65D 示出用於計算的電晶體的模型。注意，將 Synopsys 公司製造的 Sentaurus 用於計算。

[0232] 圖 65A 及圖 65B 是包括疊層結構的半導體層的電晶體 60a 的剖面結構。圖 65A 是通道長度方向的剖面圖，圖 65B 的通道寬度方向的剖面圖。

[0233] 電晶體 60a 包括：與基板（未圖示）的頂面接觸的絕緣膜 61；與絕緣膜 61 的頂面接觸的半導體層 62；與半導體層 62 的頂面接觸的半導體層 63；與半導體層 63 的頂面接觸並在重疊於半導體層 63 的區域隔開的導電層 65s 及導電層 65d；與半導體層 63 的頂面接觸的半導體層 66；半導體層 66 上的絕緣膜 67；以及隔著絕緣膜 67 重疊於半導體層 63 的閘極電極 68。半導體層 63 中的與導電層 65s、65d 接觸的區域包括低電阻層 64s、64d。絕緣膜 67 用作閘極絕緣膜。導電層 65s、65d 用作源極電極或汲極電極。以覆蓋電晶體 60a 的方式設置有絕緣膜 69。

[0234] 圖 65C 及圖 65D 是包括單層結構的半導體層的電晶體 60b 的剖面結構。圖 65C 是通道長度方向的剖面圖，圖 65D 的通道寬度方向的剖面圖。

[0235] 電晶體 60b 包括：與基板（未圖示）的頂面接觸的絕緣膜 61；與絕緣膜 61 的頂面接觸的絕緣膜 72；與絕緣膜 72 的頂面接觸的半導體層 63；與半導體層 63 的頂面接觸並在重疊於半導體層 63 的區域隔開的導電層 65s 及導電層 65d；與半導體層 63 的頂面接觸的絕緣膜 76；絕緣膜 76 上的絕緣膜 67；以及隔著絕緣膜 67 重疊於半導體層 63 的閘極電極 68。半導體層 63 中的與導電

層 65s、65d 接觸的區域包括低電阻層 64s、64d。絕緣膜 67 及絕緣膜 76 具有用作閘極絕緣膜的功能。以覆蓋電晶體 60b 的方式設置有絕緣膜 69。

[0236] 以下示出用於計算的條件。在電晶體 60a、60b 中，通道長度  $L$  為 60nm，通道寬度為 60nm，半導體層 63 的長度  $L_1$  為 140nm，通道長度方向上的導電層 65s、65d 重疊於閘極電極 68 的長度為 20nm。絕緣膜 61 的相對介電常數為 4.1，厚度為 400nm。導電層 65s、65d 的功函數為 4.6eV。絕緣膜 67 的相對介電常數為 4.1，厚度為 10nm。閘極電極 68 的功函數為 5.0eV。

[0237] 表 4 示出電晶體 60a、60b 的半導體層 63 的條件。

[0238]

[表 4]

|               |                              |

|---------------|------------------------------|

| 成分比           | IGZO(In : Ga : Zn=1 : 1 : 1) |

| 電子親和力         | 4.6 eV                       |

| $E_g$         | 3.2 eV                       |

| 相對介電常數        | 15                           |

| 施體密度          | 6.60E-09 $\text{cm}^{-3}$    |

| 施體密度(66s,66d) | 5.00E+18 $\text{cm}^{-3}$    |

| 電子移動率         | 10 $\text{cm}^2/\text{Vs}$   |

| 電洞移動率         | 0.01 $\text{cm}^2/\text{Vs}$ |

| $N_C$         | 5.00E+18 $\text{cm}^{-3}$    |

| $N_V$         | 5.00E+18 $\text{cm}^{-3}$    |

| 膜厚            | 15 nm                        |

[0239] 此外，在電晶體 60a 中，作為半導體層 62、66，使用 In-Ga-Zn 氧化物 (In : Ga : Zn=1 : 3 : 2)，半

導體層 62、66 的電子親和力為  $4.3\text{eV}$ ，能帶間隙為  $3.7\text{eV}$ ，相對介電常數為 15，施體密度為  $6.6 \times 10^{-9}$  個/ $\text{cm}^3$ ，電子移動率為  $0.1\text{cm}^2/\text{Vs}$ ，電洞移動率為  $0.01\text{cm}^2/\text{Vs}$ ， $N_c$  及  $N_v$  分別為  $5 \times 10^{18}$  個/ $\text{cm}^3$ 。另外，半導體層 62 的厚度為  $20\text{nm}$ ，半導體層 66 的厚度為  $5\text{nm}$ 。

[0240] 在電晶體 60b 中，絕緣膜 72、76 的電子親和力為  $0.9\text{eV}$ ，能帶間隙為  $9\text{eV}$ ，相對介電常數為 15。絕緣膜 72 的厚度為  $20\text{nm}$ ，絕緣膜 76 的厚度為  $5\text{nm}$ 。

[0241] 在電晶體 60a 的半導體層 66 與絕緣膜 67 之間設置電子陷阱。在電晶體 60b 的半導體層 63 與絕緣膜 76 之間設置電子陷阱。因為電子陷阱的分佈  $f$  是正態分佈，所以可以根據算式 9 而被求出。

[0242]

[算式 9]

$$f = N_0 \exp\left(-\frac{(E - E_0)^2}{2E_s^2}\right) \quad (9)$$

注意，在算式 9 中， $N_0$  為電子俘獲的最大密度， $E_0$  為導帶底的能量， $E$  為從導帶底向價帶分佈的電子俘獲的能量， $E_s$  為電子俘獲的偏差的大小。在此，在  $N_0 = 1.7 \times 10^{13}/\text{eVcm}^2$ ， $E_0 = 0\text{eV}$ ， $E_s = 0.1\text{eV}$  的條件下進行計算。

[0243] 圖 76A 示出電晶體 60a 的  $V_g$ - $I_d$  特性的計算結果，圖 76B 示出電晶體 60b 的  $V_g$ - $I_d$  特性的計算結果。

在圖 76A 和圖 76B 中，橫軸示出閘極電壓  $V_g$ ，第一縱軸示出汲極電流  $I_d$ ，第二縱軸示出場效移動率。實線示出不設置有電子陷阱的電晶體的計算結果，虛線示出設置有電子陷阱的電晶體的計算結果。細線示出汲極電壓  $V_d=0.1\text{V}$  時的計算結果，粗線是汲極電壓  $V_d=1\text{V}$  時的計算結果。

[0244] 如圖 76B 所示，當在半導體層 63 與絕緣膜 76 之間的界面設置電子俘獲時，通態電流下降。然而，如圖 76A 所示，當在半導體層 66 與絕緣膜 67 之間的界面設置電子陷阱時，通態電流幾乎沒有下降。在疊層結構的半導體層中，半導體層 63 是電子親和力大於半導體層 62 及半導體層 66 的氧化物。在對閘極電極施加電場時，通道形成在半導體層 62、半導體層 63、半導體層 66 中電子親和力最大的半導體層 63 中。由於通道從半導體層 66 與絕緣膜 67 之間的界面遠離，所以在通道中可以減小半導體層 66 與絕緣膜 67 之間的界面的電子陷阱的影響。因此，能夠抑制電晶體的通態電流的下降。另外，能夠抑制電晶體的臨界電壓的變動，而可以提高電晶體的可靠性。

[0245] 在本實施方式中，描述本發明的一個方式。或者，在其他實施方式中，描述本發明的一個方式。但是，本發明的一個方式不侷限於此。例如，雖然作為本發明的一個方式示出使用包含氧化物半導體的電晶體的情況的例子，但是本發明的一個方式不侷限於此。根據情況，本發明的一個方式也可以使用不包含氧化物半導體的電晶體。或者，根據情況，本發明的一個方式也可以使用包含

與氧化物半導體不同的半導體材料的電晶體。作為這樣的電晶體，本發明的一個方式例如也可以使用包含 Si（矽）、Ge（鍺）、SiGe（矽鍺）、GaAs（鎵砷）、碳化矽、氮化物半導體、化合物半導體或有機半導體等的電晶體。作為半導體的結晶性，根據情況，也可以使用非晶半導體、微晶半導體、多晶半導體、單晶半導體等。此外，雖然作為本發明的一個方式示出以固定的原子比包含固定的原子的半導體的例子，但是本發明的一個方式不侷限於此。根據情況，本發明的一個方式也可以使用以不與固定的原子比一致的比率包含原子的半導體。

[0246] 本實施方式的至少一部分可以與本說明書所記載的其他實施方式適當地組合而實施。

[0247]

### 實施方式 3

以下，對本發明的一個方式的使用氧化物半導體的電晶體的結構及半導體裝置進行說明。

[0248]

#### [電晶體的變形例]

使用氧化物半導體的電晶體 100 不侷限於實施方式 2 所示的圖 5A 至圖 5C 的結構。例如，電晶體 100 也可以具有圖 6A 和圖 6B 所示的結構。圖 6A 及圖 6B 與圖 5A 至圖 5C 之間的不同之處在於導電層 104a 及導電層 104b 的形狀。在圖 5B 所示的剖面中，導電層 104a 及導電層 104b 與半導體層 101a 的側面、半導體層 101b 的側面及

半導體層 101b 的頂面接觸。在圖 6A 中，導電層 104a 及導電層 104b 與半導體層 101b 的頂面接觸，並且導電層 104a 的端部及導電層 104b 的端部與半導體層 101b 的端部大致一致。另外，圖 6B 示出穿過圖 6A 所示的點劃線 A-B 且垂直於圖 6A 的面的剖面。

[0249] 另外，電晶體 100 也可以具有圖 66A 和圖 66B 所示的結構。圖 66A 及圖 66B 與圖 6A 及圖 6B 之間的不同之處主要在於：在圖 66A 及圖 66B 中，不對絕緣膜 114 的表面進行平坦化。

[0250] 此外，電晶體 100 也可以具有圖 7A 和圖 7B 所示的結構。圖 7A 及圖 7B 與圖 5A 至圖 5C 之間的不同之處在於閘極絕緣膜 102 及半導體層 101c 的形狀。在圖 5B 及圖 5C 中，閘極絕緣膜 102 及半導體層 101c 的端部與閘極電極 103 的端部大致一致。另一方面，在圖 7A 及圖 7B 中，閘極絕緣膜 102 及半導體層 101c 的端部位於閘極電極 103 的端部的外側。此外，圖 7B 示出穿過圖 7A 所示的點劃線 A-B 且垂直於圖 7A 的面的剖面。

[0251] 另外，電晶體 100 也可以具有圖 8A 和圖 8B 所示的結構。在圖 5A 至圖 5C 中，半導體層 101c 與導電層 104a 及導電層 104b 的頂面接觸，而在圖 8A 和圖 8B 中，半導體層 101c 與導電層 104a 及導電層 104b 的底面接觸。此外，圖 8B 示出穿過圖 8A 所示的點劃線 A-B 且垂直於圖 8A 的面的剖面。藉由採用這種結構，當形成構成半導體層 101a、半導體層 101b 及半導體層 101c 的各膜

時，可以以不接觸於大氣的方式連續地進行成膜，所以可以降低各膜之間的介面缺陷。

[0252] 另外，如圖 67A 和圖 67B 所示，電晶體 100 也可以具有層 119a 及層 119b。

[0253] 作為層 119a 及層 119b，例如可以使用透明導電體、氧化物半導體、氮化物半導體或氫氮化物半導體。作為層 119a 及層 119b，例如可以使用包含銻、錫及氬的層、包含銻及鋅的層、包含銻、鎢及鋅的層、包含錫及鋅的層、包含鋅及鎵的層、包含鋅及鋁的層、包含鋅及氟的層、包含鋅及硼的層、包含錫及鎢的層、包含錫及氟的層或包含鈦及鉻的層等。另外，這些層也可以包含氬、碳、氮、矽、鍺或氬。

[0254] 層 119a 及層 119b 也可以具有使可見光線透過的性質。另外，層 119a 及層 119b 也可以具有藉由反射或吸收可見光線、紫外線、紅外線或 X 射線而不使它們透過的性質。藉由具有這種性質，有時可以抑制雜散光導致的電晶體的電特性變動。

[0255] 另外，作為層 119a 及層 119b，有時較佳為使用不在與半導體層 101b 等之間形成肖特基能障的層。由此，可以提高電晶體的導通特性。

[0256] 另外，作為層 119a 及層 119b，有時較佳為使用具有比導電層 104a 及導電層 104b 高的電阻的層。此外，作為層 119a 及層 119b，有時較佳為使用具有比電晶體的通道低的電阻的層。例如，可以將層 119a 及層 119b

的電阻率設定為  $0.1\Omega\text{cm}$  以上且  $100\Omega\text{cm}$  以下、 $0.5\Omega\text{cm}$  以上且  $50\Omega\text{cm}$  以下或  $1\Omega\text{cm}$  以上且  $10\Omega\text{cm}$  以下。藉由將層 119a 及層 119b 的電阻率設定在上述範圍內，可以緩和通道與汲極之間的邊界部中的電場集中。因此，可以降低電晶體的電特性變動。另外，也可以降低起因於從汲極產生的電場的穿通電流。因此，也可以在通道長度短的電晶體中實現良好的飽和特性。注意，在源極和汲極不調換的電路結構中，有時較佳為僅配置層 119a 和層 119b 中的一個（例如，位於汲極一側的層）。

[0257] 另外，電晶體 100 也可以具有圖 9A 至圖 9D 所示的結構。此外，圖 9B 示出穿過圖 9A 所示的點劃線 A-B 且垂直於圖 9A 的面的剖面。圖 9A 至圖 9D 與圖 5A 至圖 5C 之間的不同之處在於：圖 9A 至圖 9D 不具有導電層 104a 及導電層 104b。在此，如圖 9C 所示，電晶體 100 也可以具有低電阻層 171a 及低電阻層 171b。低電阻層 171a 及低電阻層 171b 較佳為具有用作源極區域或汲極區域的功能。此外，也可以對低電阻層 171a 及低電阻層 171b 添加雜質。藉由添加雜質，可以降低半導體層 101 的電阻。作為雜質，例如較佳為添加選自氬、硼、碳、鎂、鋁、矽、磷、鈣、銨、鈦、釔、鉻、鎳、鐵、鈷、鎳、鎵、鎵、鎵、鎵、鎵、鎵中的一種以上。低電阻層 171a 及低電阻層 171b 是例如在半導體層 101 中包含  $5 \times 10^{19}\text{atoms/cm}^3$  以上，較佳為  $1 \times 10^{20}\text{atoms/cm}^3$  以上，更佳為

$2 \times 10^{20}$  atoms/cm<sup>3</sup> 以上，進一步較佳為  $5 \times 10^{20}$  atoms/cm<sup>3</sup> 以上的上述雜質元素的區域。圖 9D 是圖 9C 中的區域 324 的放大圖。

[0258] 另外，有時可以在這種電阻低的區域中俘獲雜質諸如不需要的氫等。藉由在低電阻層中俘獲不需要的氫，可以降低通道區域的氫濃度，而獲得電晶體 100 的良好的特性。

[0259] 此外，電晶體 100 也可以具有圖 10A 和圖 10B 所示的結構。圖 10A 及圖 10B 與圖 9A 至圖 9D 之間的不同之處在於半導體層 101c 和閘極絕緣膜 102 的形狀。在圖 9A 及圖 9B 中，閘極絕緣膜 102 的端部與閘極電極 103 的端部大致一致，半導體層 101c 位於閘極電極 103 的端部的外側。在圖 10A 及圖 10B 中，半導體層 101c 和閘極絕緣膜 102 的端部位於閘極電極 103 的端部的外側且半導體層 101c 與半導體層 101a 及半導體層 101b 的側面接觸。另外，圖 10B 示出穿過圖 10A 所示的點劃線 A-B 且垂直於圖 10A 的面的剖面。

[0260] 另外，雖然在圖 6A 至圖 10B 所示的結構中說明以接觸於半導體層 101b 的方式設置有半導體層 101a 及半導體層 101c 的結構，但是也可以採用不設置半導體層 101a 和半導體層 101c 中的一個或兩個的結構。

[0261] 此外，如圖 11A 至圖 11C 所示，電晶體 100 也可以具有閘極電極 103 隔著閘極絕緣膜 102 設置在半導體層 101 的下側的結構。圖 11A 及圖 11B 分別示出電晶

體 100 的俯視圖及剖面圖。圖 11A 是電晶體 100 的俯視圖，圖 11B 是沿著圖 11A 的點劃線 A-B 的剖面圖，並且圖 11C 是沿著圖 11A 的點劃線 C-D 的剖面圖。另外，在圖 11A 中，為了明確起見，省略基板 50、閘極絕緣膜 102、保護膜 25 等。圖 11A 至圖 11C 所示的電晶體 100 包括：設置在基板 50 上的閘極電極 103；形成在基板 50 及閘極電極 103 上的閘極絕緣膜 102；隔著閘極絕緣膜 102 重疊於閘極電極 103 的半導體層 101；以及接觸於半導體層 101 的導電層 104a 及導電層 104b。此外，在閘極絕緣膜 102、半導體層 101、導電層 104a 及導電層 104b 上形成保護膜 25。

[0262] 另外，保護膜 25 接觸於與半導體層 101 中的接觸於閘極絕緣膜 102 的面相反一側的面。就是說，保護膜 25 接觸於與半導體層 101 中的形成通道的區域相反一側的面（以下，稱為背後通道區域），由此具有保護半導體層 101 的背後通道區域的功能。

[0263] 在此，保護膜 25 例如可以是兩層以上的疊層。另外，保護膜 25 較佳為具有其氧含量超過化學計量組成且藉由加熱使氧的一部分脫離的膜。作為保護膜 25，例如可以使用氧化矽膜、氧氮化矽膜、氮化矽膜等。

[0264] 另外，如圖 62A 至圖 62C 所示，電晶體 100 也可以在保護膜 25 上具有電極 126。

[0265] 此外，電晶體 100 也可以具有圖 63A 和圖 63B 所示的結構。在此，圖 11A 至圖 11C 以及圖 62A 至

圖 62C 所示的電晶體 100 是通道蝕刻型電晶體，而圖 63A 和圖 63B 所示的電晶體 100 是通道保護型電晶體。

[0266] 在此，對通道蝕刻型電晶體的製程進行說明。藉由作為通道蝕刻型電晶體的半導體層 101 使用 CAAC-OS 膜，即使當進行用來形成一對導電層 104a 及導電層 104b 的蝕刻時半導體層 101 被露出，由於半導體層 101 的結晶性高而不容易受到蝕刻的損傷，由此也可以獲得良好的電晶體特性。藉由使用通道蝕刻型電晶體，可以使結構簡化。因此，例如可以降低電晶體的製造所需要的的成本。

[0267] 另外，因為 CAAC-OS 膜不具有晶界，所以用作銅的障壁膜。例如，可以認為：在將銅用於導電層 104a 及導電層 104b 時，CAAC-OS 膜防止導電層 104a 及導電層 104b 所包含的銅擴散到電晶體的通道區域。

[0268] 圖 63A 所示的電晶體 100 包括：設置在基板 50 上的閘極電極 103；形成在基板 50 及閘極電極 103 上的閘極絕緣膜 102；隔著閘極絕緣膜 102 重疊於閘極電極 103 的半導體層 101；閘極絕緣膜 102 及半導體層 101 上的絕緣膜 127；以及在該絕緣膜的開口部中接觸於半導體層 101 的一對導電層 104a 及導電層 104b。

[0269] 另外，如圖 63B 所示的電晶體 100，也可以包括：形成在半導體層 101 上的絕緣膜 128；以及其端部形成在絕緣膜 128 上且接觸於半導體層 101 的一對導電層 104a 及導電層 104b。

[0270] 當形成一對導電層 104a 及導電層 104b 時，圖 63A 和圖 63B 所示的電晶體 100 的半導體層 101 都被絕緣膜 127 或 128 覆蓋，由此半導體層 101 不受到進行用來形成一對導電層 104a 及導電層 104b 的蝕刻時的損傷。並且，藉由使絕緣膜 127、128 為包含氮且缺陷量少的氧化物絕緣膜，能夠製造電特性變動得到抑制且可靠性得到提高的電晶體。

[0271] 另外，圖 63A 和圖 63B 所示的電晶體 100 也可以具有如圖 62A 至圖 62C 所示的保護膜 25 或電極 126。

[0272]

[結構實例 1]

圖 12A 是本發明的一個方式的半導體裝置的電路圖的一個例子。圖 12A 所示的半導體裝置包括：電晶體 100；電晶體 130；電容元件 150；佈線 BL；佈線 WL；佈線 CL；佈線 SL；以及佈線 BG。

[0273] 在電晶體 130 中，源極和汲極中的一個與佈線 BL 電連接，另一個與佈線 SL 電連接，閘極與電晶體 100 的源極和汲極中的一個及電容元件 150 的一個電極電連接。在電晶體 100 中，源極和汲極中的另一個與佈線 BL 電連接，閘極與佈線 WL 電連接。電容元件 150 的另一個電極與佈線 CL 電連接。另外，佈線 BG 與電晶體 100 的第二閘極電連接。此外，將電晶體 130 的閘極、電晶體 100 的源極和汲極中的一個與電容元件 150 的一個電

極之間的節點稱為節點 FN。

[0274] 在圖 12A 所示的半導體裝置中，當電晶體 100 處於導通狀態（開啟狀態）時，對應於佈線 BL 的電位的電位施加到節點 FN。另外，當電晶體 100 處於非導通狀態（關閉狀態）時，具有保持節點 FN 的電位的功能。就是說，圖 12A 所示的半導體裝置具有記憶體裝置的記憶單元的功能。另外，當圖 12A 所示的半導體裝置具有與節點 FN 電連接的液晶元件或有機 EL（Electroluminescence：電致發光）元件等顯示元件時，可以將其用作顯示裝置的像素。

[0275] 可以根據施加到佈線 WL 或佈線 BG 的電位控制電晶體 100 的導通狀態、非導通狀態的選擇。另外，可以根據施加到佈線 WL 或佈線 BG 的電位控制電晶體 100 的臨界電壓。藉由作為電晶體 100 使用關態電流小的電晶體，可以長期間地保持非導通狀態下的節點 FN 的電位。因此，可以降低半導體裝置的更新頻率，所以可以實現耗電量小的半導體裝置。另外，作為關態電流小的電晶體的一個例子，可以舉出使用氧化物半導體的電晶體。

[0276] 另外，佈線 CL 被施加參考電位、接地電位或任意的固定電位等恆電位。此時，電晶體 100 的外觀上的臨界電壓根據節點 FN 的電位變動。根據外觀上的臨界電壓的變動而電晶體 130 的導通狀態、非導通狀態變化，由此可以作為資料讀出保持在節點 FN 中的電位的資訊。

[0277] 另外，為了使保持在節點 FN 中的電位以 85

°C 保持 10 年 ( $3.15 \times 10^8$  秒)，較佳的是，每電容  $1\text{fF}$  的關態電流值及電晶體的每通道寬度  $1\mu\text{m}$  的關態電流值小於  $4.3\text{yA}$  (攸安培 (yoctoampere)： $1\text{yA}$  為  $10^{-24}\text{A}$ )。此時，節點 FN 的電位的允許變動較佳為  $0.5\text{V}$  以內。此外，在  $95^\circ\text{C}$  下，上述關態電流較佳為小於  $1.5\text{yA}$ 。在本發明的一個方式的半導體裝置中，障壁膜的下層的氫濃度充分得到降低，其結果，其上層的使用氧化物半導體的電晶體可以實現這種極低的關態電流。

[0278] 另外，藉由增加電容，可以在節點 FN 中更長時間地保持電位。就是說，可以延長保持時間。

[0279] 藉由將圖 12A 所示的半導體裝置配置為矩陣狀，可以構成記憶體裝置（記憶單元陣列）。

[0280] 圖 13A 至圖 13C 示出能夠實現圖 12A 所示的電路的半導體裝置的剖面結構的一個例子。另外，圖 13B 示出穿過圖 13A 所示的點劃線 A-B 且垂直於圖 13A 的面的剖面。此外，圖 13C 示出穿過圖 13A 所示的點劃線 C-D 且垂直於圖 13A 的面的剖面。

[0281] 半導體裝置包括電晶體 130、電晶體 100 及電容元件 150。電晶體 100 設置在電晶體 130 的上方，在電晶體 130 與電晶體 100 之間至少設置有一層以上的障壁膜。另外，也可以形成多個障壁膜。

[0282] 在圖 13A 至圖 13C 中，作為電晶體 100 使用圖 7A 和圖 7B 所示的電晶體結構。

[0283] 電晶體 130 包含第一半導體材料。另外，電

晶體 100 包含第二半導體材料。雖然第一半導體材料和第二半導體材料可以為相同的材料，但是較佳為不同的半導體材料。

[0284] 作為可以用作第一半導體材料或第二半導體材料的半導體，例如可以舉出：矽、鍺、鎵、砷等半導體材料；包含矽、鍺、鎵、砷、鋁等的化合物半導體材料；有機半導體材料；或氧化物半導體材料等。

[0285] 在此，對作為第一半導體材料使用單晶矽且作為第二半導體材料使用氧化物半導體的情況進行說明。

[0286]

[第一電晶體]

電晶體 130 設置在半導體基板 131 上，並且包括：半導體基板 131 的一部分的半導體層 132；閘極絕緣膜 134；閘極電極 135；以及用作源極區域或汲極區域的低電阻層 133a 及低電阻層 133b。

[0287] 電晶體 130 可以為 p 通道型或 n 通道型，可以根據電路結構或驅動方法使用適當的電晶體。

[0288] 半導體層 132 的形成通道的區域或其附近的區域、用作源極區域或汲極區域的低電阻層 133a 及低電阻層 133b 等較佳為包含矽類半導體等半導體，更佳為包含單晶矽。另外，也可以使用包含 Ge (鍺)、SiGe (矽鍺)、GaAs (砷化鎵)、GaAlAs (鎵鋁砷) 等材料形成。也可以使用具有晶格畸變的矽。此外，電晶體 130 也可以是使用 GaAs 和 GaAlAs 等的 HEMT (High Electron

Mobility Transistor：高電子移動率電晶體）。

[0289] 另外，電晶體 130 也可以包括用作 LDD (Lightly Doped Drain：輕摻雜汲極) 區域的區域 176a 和區域 176b。

[0290] 在低電阻層 133a 及低電阻層 133b 中，除了應用於半導體層 132 的半導體材料之外，還包含磷等賦予 n 型導電性的元素或硼等賦予 p 型導電性的元素。

[0291] 作為閘極電極 135，可以使用包含磷等賦予 n 型導電性的元素或硼等賦予 p 型導電性的元素的矽等半導體材料、金屬材料、合金材料或金屬氧化物材料等導電材料。尤其是，較佳為使用同時實現耐熱性和導電性的鎢或鉑等高熔點材料，尤其較佳為使用鎢。

[0292] 在此，也可以使用如圖 15C 及圖 15D 所示的電晶體 190 代替電晶體 130。圖 15D 示出穿過圖 15C 所示的點劃線 E-F 且垂直於圖 15C 的面的剖面。在電晶體 190 中，形成通道的半導體層 132 (半導體基板的一部分) 具有凸形狀，沿著其側面及頂面設置有閘極絕緣膜 134 及閘極電極 135。另外，在電晶體之間設置有元件分離層 181。因為利用半導體基板的凸部，所以這種電晶體 190 被稱為 FIN 型電晶體。另外，也可以以與凸部的上部接觸的方式具有用作用來形成凸部的遮罩的絕緣膜。此外，雖然在此示出對半導體基板的一部分進行加工來形成凸部的情況，但是也可以對 SOI (Silicon on Insulator：絕緣層上覆矽) 基板進行加工來形成具有凸形狀的半導體層。

[0293] 以覆蓋電晶體 130 的方式依次層疊有絕緣膜 136、絕緣膜 137 及絕緣膜 138。

[0294] 在半導體裝置的製程中，絕緣膜 136 用作用來使添加到低電阻層 133a 及低電阻層 133b 的賦予導電性的元素活化的保護膜。如果不需要則可以不設置絕緣膜 136。

[0295] 當將矽類半導體材料用於半導體層 132 時，絕緣膜 137 較佳為包含含有氫的絕緣材料。藉由將含有氫的絕緣膜 137 設置在電晶體 130 上而進行加熱處理，由絕緣膜 137 中的氫終結半導體層 132 中的懸空鍵，由此可以提高電晶體 130 的可靠性。

[0296] 絝緣膜 138 用作使起因於設置在其下層的電晶體 130 等產生的步階平坦化的平坦化層。為了提高絕緣膜 138 的頂面的平坦性，其頂面也可以藉由利用 CMP (Chemical Mechanical Polishing：化學機械拋光) 法等平坦化處理被平坦化。

[0297] 另外，也可以在絕緣膜 136、絕緣膜 137、絕緣膜 138 中埋入有與低電阻層 133a 或低電阻層 133b 等電連接的插頭 140、與電晶體 130 的閘極電極 135 電連接的插頭 139 等。

[0298]

[電容元件]

在電晶體 130 與電晶體 100 之間設置有障壁膜 111。如圖 13A 至圖 13C 所示，障壁膜可以是單層或多層。

[0299] 障壁膜 111 具有抑制水及氫從障壁膜 111 的下層擴散到其上層的功能。另外，障壁膜 111 的氧透過性較佳為低。此外，障壁膜 111 也可以具有用來將設置在障壁膜 111 的上方的電極或佈線與設置在其下方的電極或佈線電連接的開口或插頭。在此，“抑制水及氧的擴散”是指例如與一般用作絕緣膜的氧化矽等相比，不容易使水及氫擴散或者水及氫的透過性低的情況。此外，“氧透過性低”是指與一般用作絕緣膜的氧化矽等相比，氧的透過性低的情況。

[0300] 與障壁膜 111 同樣，作為絕緣膜 112 較佳為使用水或氫不容易擴散的材料。另外，尤其是，作為絕緣膜 112 較佳為使用不容易使氧透過的材料。此外，絕緣膜 112 也可以是兩層以上的疊層結構。在此情況下，例如使絕緣膜 112 具有兩層的疊層結構，例如可以將氧化矽、氮氧化矽、氮氧化矽、氮化矽、氧化鋁、氮氧化鋁、氮氧化鋁、氮化鋁等用於下層。另外，與障壁膜 111 同樣，較佳為將水或氫不容易擴散的材料用於上層。此外，設置在下層的絕緣膜作為與後面說明的絕緣膜 114 同樣的藉由加熱使氧脫離的絕緣膜，可以採用隔著閘極絕緣膜 102 從半導體層 101 的上側也供應氧的結構。

[0301] 藉由由包含不容易使氧透過的材料的絕緣膜 112 覆蓋半導體層 101，可以抑制氧從半導體層 101 釋放到絕緣膜 112 的上方。再者，可以使從絕緣膜 114 脫離的氧封閉在絕緣膜 112 的下側，所以可以增大可能供應到半

導體層 101 的氧量。

[0302] 另外，藉由設置不容易使水或氫透過的絕緣膜 112，可以抑制從外部混入對氧化物半導體來說是雜質的水或氫，而電晶體 100 的電特性變動得到抑制，因此可以實現可靠性高的電晶體。

[0303] 另外，也可以在絕緣膜 112 的下側設置與絕緣膜 114 同樣的藉由加熱使氧脫離的絕緣膜，藉由閘極絕緣膜 102 從半導體層 101 的上側也供應氧。

[0304] 在此，較佳的是，在障壁膜 111 的下層中儘量降低氫或水等。或者，較佳為抑制氣體的釋放。氫或水對氧化物半導體來說有可能成為引起電特性變動的主要原因。另外，雖然可以由障壁膜 111 抑制氫或水從障壁膜 111 的下層擴散到上層，但是氫或水有時藉由設置在障壁膜 111 中的開口或插頭等會擴散到上層。

[0305] 為了降低位於障壁膜 111 的下層的各層所包含的氫或水，或者為了抑制氣體的釋放，較佳的是，在形成障壁膜 111 之前，或者剛在障壁膜 111 中形成用來形成插頭的開口之後，進行用來去除障壁膜 111 的下層所包含的氫或水或者用來抑制氣體的釋放的加熱處理。只要構成半導體裝置的導電膜等的耐熱性或電晶體的電特性不發生劣化，加熱處理的溫度越高越好。明確而言，例如可以將其設定為 450°C 以上，較佳為 490°C 以上，更佳為 530°C 以上，但是也可以設定為 650°C 以上。較佳的是，在惰性氣體氛圍下或減壓氛圍下進行 1 小時以上，較佳為 5 小時

以上，更佳為 10 小時以上的加熱處理。另外，加熱處理的溫度可以考慮到位於障壁膜 111 的下方的佈線或電極的材料的耐熱性而決定，例如當該材料的耐熱性低時，可以在 550°C 以下、600°C 以下、650°C 以下或 800°C 以下的溫度下進行加熱處理。另外，只要進行這種加熱處理至少一次以上即可，而較佳為進行多次。

[0306] 在設置在障壁膜 111 的下層的絕緣膜中，藉由熱脫附譜分析（也稱為 TDS 分析）測量的基板表面溫度為 400°C 下的氫分子的脫離量為基板表面溫度為 300°C 下的氫分子的脫離量的 130% 以下，較佳為 110% 以下。或者，藉由 TDS 分析測量的基板表面溫度為 450°C 下的氫分子的脫離量為基板表面溫度為 350°C 下的氫分子的脫離量的 130% 以下，較佳為 110% 以下。

[0307] 另外，障壁膜 111 本身所包含的水或氫也較佳為得到減少。或者，較佳為抑制氣體的釋放。例如，作為障壁膜 111，較佳為使用藉由 TDS 分析測量的基板表面溫度為 20°C 至 600°C 的範圍內的氫分子 ( $M/z=2$ ) 的脫離量低於  $2 \times 10^{15}$  個/ $\text{cm}^2$ ，較佳為低於  $1 \times 10^{15}$  個/ $\text{cm}^2$ ，更佳為低於  $5 \times 10^{14}$  個/ $\text{cm}^2$  的材料。或者，作為障壁膜 111，較佳為使用藉由 TDS 分析測量的基板表面溫度為 20°C 至 600°C 的範圍內的水分子 ( $M/z=18$ ) 的脫離量低於  $1 \times 10^{16}$  個/ $\text{cm}^2$ ，較佳為低於  $5 \times 10^{15}$  個/ $\text{cm}^2$ ，更佳為低於  $2 \times 10^{12}$  個/ $\text{cm}^2$  的材料。

[0308] 另外，在作為電晶體 130 的半導體層使用單

晶矽的情況下，該加熱處理可以兼作由氫終結矽的懸空鍵的處理（也稱為氫化處理）。藉由氫化處理，電晶體 130 的閘極絕緣膜或形成於障壁膜 111 的下層的其他絕緣膜所包含的一部分氫脫離並擴散到第一電晶體的半導體層中，而使矽中的懸空鍵終結，由此可以提高第二電晶體的可靠性。

[0309] 作為障壁膜 111，例如可以使用包含氧化鋁、氧化鉻、氧化鉭、氧化鋯、鋯鈦酸鉛（PZT）、鈦酸鋰（ $\text{SrTiO}_3$ ）或（Ba，Sr） $\text{TiO}_3$ （BST）等所謂的高介電常數（high-k）材料的絕緣膜的單層或疊層。另外，例如也可以對這些絕緣膜添加氧化鋁、氧化鉻、氧化鋯、氧化鋆、氧化矽、氧化鈦、氧化鎢、氧化釔、氧化鋯、氧化鎵。此外，也可以對這些絕緣膜進行氮化處理形成氮化膜。還可以在上述絕緣膜上層疊氧化矽、氮化矽或氮化矽。尤其是，氧化鋁具有對水或氫的優良的阻擋性，所以是較佳的。

[0310] 作為障壁膜 111，除了不容易使水或氫透過的材料的層之外，也可以使用包含其他絕緣材料的層的疊層。例如，也可以使用包含氧化矽或氮化矽的層、包含金屬氧化物的層等的疊層。

[0311] 另外，作為障壁膜 111，較佳為使用不容易使氧透過的材料。上述材料是不但對氫、水而且對氧也具有優良的阻擋性的材料。藉由使用這種材料，可以抑制當對絕緣膜 114 進行加熱時被釋放的氧擴散到障壁膜 111 的下

層。其結果，可以增大可能從絕緣膜 114 被釋放而供應到電晶體 100 的半導體層的氧量。

[0312] 如此，降低位於障壁膜 111 的下層的各層所包含的氫或水的濃度，或者藉由抑制氣體的釋放且設置障壁膜 111 抑制氫或水擴散到電晶體 100 中。因此，可以使絕緣膜 114 或構成電晶體 100 的各層中的氫及水的含量極低。例如，可以將絕緣膜 114、電晶體 100 的半導體層 101 或閘極絕緣膜 102 所包含的氫的濃度降低到低於  $5 \times 10^{18} \text{ cm}^{-3}$ ，較佳為低於  $1 \times 10^{18} \text{ cm}^{-3}$ ，更佳為低於  $3 \times 10^{17} \text{ cm}^{-3}$ 。

[0313] 藉由上述結構，也可以在第一電晶體和第二電晶體中都可以實現高可靠性，由此可以實現可靠性極高的半導體裝置。

[0314] 以夾著障壁膜 111 的方式設置有導電層 151、導電層 152a 及導電層 152b，由此形成電容元件 150。插頭 140、導電層 251 與電晶體 100 的導電層 104b 電連接。導電層 151 與電晶體 100 的導電層 104a 電連接。導電層 151、導電層 143 及導電層 251 以填充在絕緣膜 115 中的開口部的方式形成。

[0315] 以覆蓋障壁膜 111、導電層 152a、導電層 152b 及導電層 105 等的方式設置有絕緣膜 114。

[0316] 絶緣膜 114 的頂面較佳為藉由利用 CMP 法等的平坦化處理被平坦化。

[0317] 另外，絕緣膜 114 較佳為包含氧化物。尤其

是，較佳為包含藉由加熱使一部分氧脫離的氧化物材料。較佳為使用其氧含量超過化學計量組成的氧化物。當作為第二半導體材料使用氧化物半導體時，從絕緣膜 114 脫離的氧供應到氧化物半導體，可以減少氧化物半導體中的氧缺陷。其結果，可以抑制第二電晶體的電特性變動，而可以提高可靠性。

[0318] 另外，作為絕緣膜 114，較佳為使用藉由加熱使一部分氧脫離的氧化物材料。作為藉由加熱使氧脫離的氧化物材料，較佳為使用其氧含量超過化學計量組成的氧化物。在其氧含量超過化學計量組成的氧化物膜中，藉由加熱使一部分氧脫離。其氧含量超過化學計量組成的氧化物膜是在熱脫附譜分析中，換成為氧原子的氧的脫離量為 $1.0 \times 10^{18} \text{ atoms/cm}^3$  以上，較佳為 $3.0 \times 10^{20} \text{ atoms/cm}^3$  以上的氧化物膜。注意，上述 TDS 分析時的膜的表面溫度較佳為 100°C 以上且 700°C 以下或 100°C 以上且 500°C 以下。

[0319] 例如，作為這種材料，較佳為使用包含氧化矽或氧氮化矽的材料。另外，也可以使用金屬氧化物。作為金屬氧化物，可以使用氧化鋁、氧氮化鋁、氧化鎵、氧氮化鎵、氧化鈦、氧氮化鈦、氧化鉻、氧氮化鉻等。注意，在本說明書中，“氧氮化矽”是指在其組成中氧含量多於氮含量的材料，而“氮氧化矽”是指在其組成中氮含量多於氧含量的材料。

[0320] 另外，為了使絕緣膜 114 含有過剩氧，也可以對絕緣膜 114 引入氧而形成含有過剩氧的區域。例如，

對成膜之後的絕緣膜 114 引入氧（至少包含氧自由基、氧原子、氧離子中的任一個）而形成包含過剩氧的區域。作為氧的引入方法，可以使用離子植入法、離子摻雜法、電漿浸沒離子佈植技術、電漿處理等。

[0321]

[第二電晶體]

在絕緣膜 114 的上部設置有電晶體 100 的半導體層 101。

[0322] 電晶體 110 包括：接觸於絕緣膜 114 的頂面的半導體層 101；導電層 104a 及導電層 104b；半導體層 101 上的閘極絕緣膜 102；以及隔著閘極絕緣膜 102 重疊於半導體層 101 的閘極電極 103。另外，以覆蓋電晶體 100 的方式設置有絕緣膜 112、絕緣膜 113 及絕緣膜 116。此外，電晶體 100 也可以具有用作第二閘極電極的導電層 105。

[0323] 另外，半導體層 101 也可以以單層形成，如圖 13A 至圖 13C 所示，較佳為以半導體層 101a、半導體層 101b 及半導體層 101c 的疊層結構形成。圖 13A 至圖 13C 所示的電晶體 100 包括：半導體層 101a；接觸於半導體層 101a 的頂面的半導體層 101b；接觸於半導體層 101b 的頂面並在重疊於半導體層 101b 的區域隔開的導電層 104a 及導電層 104b；接觸於半導體層 101b 的頂面的半導體層 101c；半導體層 101c 上的閘極絕緣膜 102；以及隔著閘極絕緣膜 102 及半導體層 101c 重疊於半導體層 101b

的閘極電極 103。另外，圖 13A 至圖 13C 所示的電晶體 100 包括用作第二閘極電極的導電層 105。導電層 105 也可以與構成電容元件 150 的一部分的導電層 152a 及導電層 152b 同時形成。半導體層 101a 設置在絕緣膜 114 與半導體層 101b 之間。半導體層 101c 設置在半導體層 101b 與閘極絕緣膜 102 之間。導電層 104a 及導電層 104b 接觸於半導體層 101b 的頂面及閘極絕緣膜 103c 的底面。

[0324] 另外，以覆蓋電晶體 100 的方式設置有絕緣膜 112、絕緣膜 113 及絕緣膜 116。

[0325] 在此，作為半導體層 101b 較佳為使用氧化物半導體。藉由加熱從絕緣膜 114 脫離的氧供應到半導體層 101b，由此可以降低半導體層 101b 中的氧缺陷。其結果，例如可以抑制電晶體 100 的電特性變動，而提高可靠性。

[0326] 下面，對半導體層 101b 為 In-Ga-Zn 氧化物時的結晶性與氧透過性的關係進行說明。

[0327] 藉由計算來求得 In-Ga-Zn 氧化物的結晶中的起因於過剩氧（氧）遷移的能障。在計算中，使用根據密度泛函理論的平面波基第一原理計算軟體 VASP (Vienna ab-initio simulation package)。注意，作為泛函數，使用 GGA-PBE。另外，將平面波截止能量設定為 400eV。此外，藉由 PAW (Projector Augmented Wave：投影綴加波) 法將內殼層電子的效果反映在計算結果中。

[0328] 在此，在圖 61 所示的 In-Ga-Zn 氧化物的結晶

中，計算出過剩氧（氧）在遷移路徑 1、遷移路徑 2、遷移路徑 3 和遷移路徑 4 之中哪個路徑比較容易遷移。

[0329] 另外，遷移路徑 1 是鍵合於與三個銻原子以及一個鋅原子鍵合的氧的過剩氧（氧）鍵合到相鄰的與三個銻原子以及一個鋅原子鍵合的氧的路徑。此外，遷移路徑 2 是鍵合於與三個銻原子以及一個鎵原子鍵合的氧的過剩氧（氧）穿過包含銻及氧的層而鍵合到相鄰的與三個銻原子以及一個鋅原子鍵合的氧的路徑。另外，遷移路徑 3 是鍵合於與兩個鎵原子以及一個鋅原子鍵合的氧的過剩氧（氧）鍵合到相鄰的與兩個鋅原子以及一個鎵原子鍵合的氧的路徑。此外，遷移路徑 4 是鍵合於與兩個鎵原子以及一個鋅原子鍵合的氧的過剩氧（氧）穿過包含鎵、鋅及氧的層而鍵合到相鄰的與三個銻原子以及一個鎵原子鍵合的氧的路徑。

[0330] 在將超越每單位時間的擴散的能障  $E_a$  的頻率作為擴散頻率  $R$  時， $R$  可以以下面所示的算式來表示。

$$[0331] R = v \cdot \exp[-E_a / (k_B T)]$$

[0332] 另外， $v$  表示擴散原子的熱振動數， $k_B$  表示波茲曼常數， $T$  表示絕對溫度。以表 5 表示對  $v$  施加  $10^{13} [1/\text{sec}]$  作為德拜頻率時的  $350^\circ\text{C}$  及  $450^\circ\text{C}$  下的擴散頻率  $R$ 。

[0333]

[表 5]

|        | 能障<br>[eV] | 擴散頻率 R [1/sec]       |                      |

|--------|------------|----------------------|----------------------|

|        |            | 350°C                | 450°C                |

| 遷移路徑 1 | 0.50       | $9.0 \times 10^8$    | $3.3 \times 10^9$    |

| 遷移路徑 2 | 1.97       | $1.2 \times 10^{-3}$ | $1.9 \times 10^{-1}$ |

| 遷移路徑 3 | 0.53       | $5.2 \times 10^8$    | $2.0 \times 10^9$    |

| 遷移路徑 4 | 0.56       | $3.0 \times 10^8$    | $1.3 \times 10^9$    |

[0334] 如表 5 所示，穿過包含銦及氧的層的遷移路徑 2 的能障比其他遷移路徑高。這示出在 In-Ga-Zn 氧化物的結晶中，過剩氧（氧）不容易在 c 軸方向上遷移。即，示出在如 CAAC-OS 等，結晶具有 c 軸配向性且 c 軸朝向大致垂直於被形成面或頂面的方向的情況下，過剩氧（氧）不容易在大致垂直於被形成面或頂面的方向上遷移。

[0335] 因此，在將過剩氧供應到半導體層 101b 的情況下，可以從與垂直於被形成面或頂面的方向稍微偏離的方向供應氧。例如，在形成半導體層 101b 之後，從其側面供應氧即可。

[0336] 另外，例如在半導體層 101a 上層疊半導體層 101b 的情況下，在半導體層 101a 的頂面，即與半導體層 101b 的介面不容易產生過剩氧的移動。因此，可以抑制供應到半導體層 101b 的氧的釋放。與此同樣，在半導體層 101b 上層疊半導體層 101c 的情況下，在半導體層 101b 與半導體層 101c 的介面不容易產生過剩氧的移動，

可以抑制氧從半導體層 101b 被釋放。另一方面，氧從半導體層 101b 的側面有可能容易被釋放，所以如圖 5A 至圖 5C 所示那樣，較佳為由半導體層 101c 覆蓋半導體層 101b 的側面。或者，如圖 6A 和圖 6B 所示那樣，較佳為由絕緣膜 112 覆蓋半導體層 101b 的側面，或者隔著閘極絕緣膜 102 由閘極電極 103 等覆蓋半導體層 101b 的側面。

[0337] 另外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）設置在半導體層 101b（和/或半導體層 101a）等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）。

[0338] 另外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）與半導體層 101b（和/或半導體層 101a）等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）接觸。此外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）與半導體層 101b（和/或半導體層 101a）等半導體層的至少一部分（或全部）接觸。

[0339] 另外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）與半導體層 101b（和/或半導體層 101a）等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）電連接。此外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）與半導體層 101b（和/或半導體層 101a）等半導體層的至少一部分（或全部）電連接。

[0340] 另外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）的附近。此外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的至少一部分（或全部）的附近。

[0341] 另外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）的橫方向上。此外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的至少一部分（或全部）的橫方向上。

[0342] 另外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的表面、側面、頂面和/或底面的至少一部分（或全部）的斜上方。此外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的至少一部分（或全部）的斜上方。

[0343] 另外，導電層 104a (和/或導電層 104b) 的至少一部分（或全部）設置在半導體層 101b (和/或半導體層 101a) 等半導體層的表面、側面、頂面和/或底面的至

少一部分（或全部）的上方。此外，導電層 104a（和/或導電層 104b）的至少一部分（或全部）設置在半導體層 101b（和/或半導體層 101a）等的半導體層的至少一部分（或全部）的上方。

[0344] 半導體層 101 也可以在通道形成區域中包含矽類半導體等半導體。尤其是，半導體層 101 較佳為包含能帶間隙比矽寬的半導體。較佳的是，半導體層 101 包含氧化物半導體。藉由使用能帶間隙比矽寬且載子密度小的半導體材料，可以降低電晶體的關閉狀態（off-state）時的電流，所以是較佳的。

[0345] 藉由作為半導體層使用上述材料，可以實現電特性變動得到抑制的可靠性高的電晶體。

[0346] 能夠適用於半導體層的氧化物半導體的較佳的方式例如可以參照實施方式 1 所示的氧化物半導體。

[0347] 注意，在本說明書等中，實質上本質是指氧化物半導體層的載子密度低於  $1 \times 10^{17}/\text{cm}^3$ 、低於  $1 \times 10^{15}/\text{cm}^3$  或低於  $1 \times 10^{13}/\text{cm}^3$  的狀態。藉由使氧化物半導體層高純度本質化，可以對電晶體賦予穩定的電特性。

[0348] 導電層 104a 和導電層 104b 中的一個用作源極電極，另一個用作汲極電極。

[0349] 導電層 104a 及導電層 104b 使用鋁、鈦、鉻、鎳、銅、釔、鎔、鉬、銀、鉭和鎢等金屬或以這些元素為主要成分的合金以單層結構或疊層結構形成。例如，可以舉出包含矽的鋁膜的單層結構、在鈦膜上層疊鋁膜的

兩層結構、在鎢膜上層疊鋁膜的兩層結構、在銅-鎂-鋁合金膜上層疊銅膜的兩層結構、在鈦膜上層疊銅膜的兩層結構、在鎢膜上層疊銅膜的兩層結構、依次層疊鈦膜或氮化鈦膜、鋁膜或銅膜以及鈦膜或氮化鈦膜的三層結構、以及依次層疊鋁膜或氮化鋁膜、鋁膜或銅膜以及鋁膜或氮化鋁膜的三層結構等。另外，也可以使用包含氧化鋁、氧化錫或氧化鋅的透明導電材料。

[0350] 作為閘極絕緣膜 102，例如使用氧化矽、氮氧化矽、氮氧化矽、氧化鋁、氧化鉻、氧化鎵、Ga-Zn 類金屬氧化物、氮化矽等即可，並以疊層或單層的結構設置。

[0351] 此外，作為閘極絕緣膜 102 也可以使用矽酸鉻 ( $\text{HfSiO}_x$ )、添加有氮的矽酸鉻 ( $\text{HfSi}_x\text{O}_y\text{N}_z$ )、添加有氮的鋁酸鉻 ( $\text{HfAl}_x\text{O}_y\text{N}_z$ )、氧化鉻等 high-k 材料。

[0352] 另外，作為閘極絕緣膜 102 可以使用氧化鋁、氧化鎂、氧化矽、氮氧化矽、氧化鎵、氧化鋯、氧化鉻、氧化鉻、氧化鋯、氧化鑭、氧化釤、氧化鉻和氧化鋁等氧化物絕緣膜、氮化矽、氮氧化矽、氮化鋁和氮氧化鋁等氮化物絕緣膜或者混合上述材料的膜。

[0353] 另外，與絕緣膜 114 同樣，作為閘極絕緣膜 102 較佳為使用其氧含量超過化學計量組成的氧化物絕緣膜。

[0354] 此外，藉由將特定的材料用於閘極絕緣膜，可以在特定的條件下使閘極絕緣膜俘獲電子而提高臨界電壓。例如，如氧化矽及氧化鉻的疊層膜那樣，作為閘極絕

緣膜的一部分使用氧化鉻、氧化鋁、氧化鉬等電子俘獲能階多的材料，在更高溫度（比半導體裝置的使用溫度或保管溫度高的溫度、或者  $125^{\circ}\text{C}$  以上且  $450^{\circ}\text{C}$  以下，典型的是  $150^{\circ}\text{C}$  以上且  $300^{\circ}\text{C}$  以下）下，將閘極電極的電位保持為高於源極電極或汲極電極的電位的狀態 1 秒以上，典型的是 1 分鐘以上，電子從半導體膜向閘極電極移動，其一部分被電子俘獲能階俘獲。

[0355] 像這樣，使電子俘獲能階俘獲電子的電晶體的臨界電壓向正一側漂移。藉由控制閘極電極的電壓可以控制電子的俘獲量，由此可以控制臨界電壓。另外，俘獲電子的處理在電晶體的製造過程中進行即可。

[0356] 例如，在形成與電晶體的源極電極或汲極電極連接的佈線金屬之後、前製程（晶圓處理）結束之後、晶圓切割製程之後或者封裝之後等發貨之前的任一個步驟進行俘獲電子的處理即可。不管在上述哪一種情況下，都較佳為在該處理之後不將電晶體放置在  $125^{\circ}\text{C}$  以上的溫度下 1 小時以上。

[0357] 閘極電極 103 例如可以使用選自鋁、鉻、銅、鉻、鈦、鉬、鎢中的金屬、以上述金屬為成分的合金或組合上述金屬元素的合金等而形成。另外，也可以使用選自錳、鎔中的一個或多個的金屬。此外，也可以使用以摻雜有磷等雜質元素的多晶矽為代表的半導體、鎳矽化物等矽化物。另外，閘極電極 103 可以具有單層結構或兩層以上的疊層結構。例如，可以舉出包含矽的鋁膜的單層結

構、在鋁膜上層疊鈦膜的兩層結構、在氮化鈦膜上層疊鈦膜的兩層結構、在氮化鈦膜上層疊鎢膜的兩層結構、在氮化鉭膜或氮化鎢膜上層疊鎢膜的兩層結構以及依次層疊鈦膜、該鈦膜上的鋁膜和其上的鈦膜的三層結構等。此外，也可以使用組合鋁與選自鈦、鉭、鎢、鋁、鉻、釤、銠中的一種或多種的合金膜或它們的氮化膜。

[0358] 另外，閘極電極 103 也可以使用銻錫氧化物、包含氧化鎢的銻氧化物、包含氧化鎢的銻鋅氧化物、包含氧化鈦的銻氧化物、包含氧化鈦的銻錫氧化物、銻鋅氧化物、添加有氧化矽的銻錫氧化物等透光導電材料。此外，也可以採用上述透光導電材料與上述金屬的疊層結構。

[0359] 另外，可以在閘極電極 103 和閘極絕緣膜 102 之間設置 In-Ga-Zn 類氧氮化物半導體膜、In-Sn 類氧氮化物半導體膜、In-Ga 類氧氮化物半導體膜、In-Zn 類氧氮化物半導體膜、Sn 類氧氮化物半導體膜、In 類氧氮化物半導體膜、金屬氮化膜 (InN、ZnN 等) 等。由於上述膜具有 5eV 以上，較佳為 5.5eV 以上的功函數，且該值比氧化物半導體的電子親和力大，所以可以使使用氧化物半導體的電晶體的臨界電壓向正方向漂移，從而可以實現所謂常關閉特性的切換元件。例如，在使用 In-Ga-Zn 類氧氮化物半導體膜的情況下，使用氮濃度至少高於半導體層 101，具體為 7at.% (原子百分比) 以上的 In-Ga-Zn 類氧氮化物半導體膜。

[0360] 與障壁膜 111 同樣，作為絕緣膜 112 較佳為使用水或氫不容易擴散的材料。另外，尤其是，作為絕緣膜 112 較佳為使用不容易使氧透過的材料。

[0361] 藉由由包含不容易使氧透過的材料的絕緣膜 112 覆蓋半導體層 101，可以抑制氧從半導體層 101 釋放到絕緣膜 112 的上方。再者，可以使從絕緣膜 114 脫離的氧封閉在絕緣膜 112 的下側，所以可以增大可能供應到半導體層 101 的氧量。

[0362] 另外，藉由設置不容易使水或氫透過的絕緣膜 112，可以抑制從外部混入對氧化物半導體來說是雜質的水或氫，而電晶體 100 的電特性變動得到抑制，因此可以實現可靠性高的電晶體。

[0363] 另外，也可以在絕緣膜 112 的下側設置與絕緣膜 114 同樣的藉由加熱使氧脫離的絕緣膜，藉由閘極絕緣膜 102 從半導體層 101 的上側也供應氧。

[0364] 另外，如圖 13B 所示，藉由在電晶體的通道寬度方向上的剖面中閘極電極 103 與半導體層 101b 的頂面及側面對置，不但在半導體層 101b 的頂面附近，而且在側面附近也形成通道，實效的通道寬度增大，可以增高開啟狀態下的電流（通態電流）。尤其是，在半導體層 101b 的寬度極小（例如，50nm 以下，較佳為 30nm 以下，更佳為 20nm 以下）的情況下，形成通道的區域擴散到半導體層 101b 的內部；因此，越微型化，越有助於通態電流。

[0365] 以上是對電晶體 100 的說明。

[0366] 覆蓋電晶體 100 的絕緣膜 116 用作覆蓋其下層的凹凸形狀的平坦化層。另外，絕緣膜 113 也可以具有形成絕緣膜 116 時的保護膜的功能。如果不需要，則可以不設置絕緣膜 113。

[0367] 在絕緣膜 112、絕緣膜 113 及絕緣膜 116 中埋入有與導電層 104b 或導電層 104a 電連接的插頭 321、插頭 322、插頭 123。

[0368] 在絕緣膜 116 的上部設置有與插頭 322 電連接的佈線 124 等。

[0369] 在此，圖 13A 所示的佈線 124 相當於圖 12A 和圖 12B 所示的佈線 BL。與此同樣，圖 13B 所示的佈線 166 相當於佈線 BG。另外，雖然未圖示，但是與圖 13A 至圖 13C 所示的閘極電極 103 連接的佈線相當於佈線 WL。此外，與導電層 152a 及導電層 152b 連接的佈線相當於佈線 CL。另外，與電晶體 130 的低電阻層 133b 連接的佈線相當於佈線 SL。此外，包括電晶體 130 的閘極電極 135、用作電容元件 150 的第一電極的導電層 151 及電晶體 100 的導電層 104a 的節點相當於圖 12A 所示的節點 FN。

[0370] 另外，如圖 13A 至圖 13C 所示，也可以在包含氫的絕緣膜 136 上設置包含與障壁膜 111 同樣的材料的絕緣膜 137 的結構。藉由採用這種結構，可以有效地抑制殘留在包含氫的絕緣膜 136 中的水或氫擴散到上方。此

時，較佳為在形成絕緣膜 137 之前以及在形成絕緣膜 137 之後且形成障壁膜 111 之前一共進行用來去除水或氫的加熱處理 2 次以上。

[0371] 作為佈線 124、佈線 166 等佈線的材料，可以使用金屬材料、合金材料或金屬氧化物材料等導電材料。尤其是，較佳為使用同時實現耐熱性和導電性的鎢或鉬等高熔點材料，尤其較佳為使用鎢。

[0372] 另外，作為導電層 151、導電層 152a、導電層 152b、導電層 251、導電層 143 等導電層、插頭 123、插頭 139、插頭 140、插頭 164、插頭 165 等的插頭的材料，可以使用金屬材料、合金材料或金屬氧化物材料等導電材料。尤其是，較佳為使用同時實現耐熱性和導電性的鎢或鉬等高熔點材料，尤其較佳為使用鎢。另外，也可以使用氮化鈦、鈦等的材料和其他材料的疊層。例如，藉由使用氮化鈦或鈦，可以提高與開口部的密接性。導電層 151、導電層 152a、導電層 152b、導電層 251、導電層 143 等導電層、插頭 123、插頭 139、插頭 140、插頭 164、插頭 165 等插頭以埋入在絕緣膜的方式設置，各頂面較佳為被平坦化。

[0373] 因為本發明的一個方式的半導體裝置包括電晶體 130 以及位於電晶體 130 的上方的電晶體 100，所以藉由層疊它們可以縮小元件所占的面積。再者，藉由設置在電晶體 130 與電晶體 100 之間的障壁膜 111，可以抑制存在於其下層的水或氫等雜質擴散到電晶體 100 一側。並

且，隔著該障壁膜 111 設置其一部分用作第一電極的導電層 151 及其一部分用作第二電極的導電層 152a 及導電層 152b 來形成電容元件 150，因此可以容易製造電容元件 150 而不另行追加用來製造電容元件 150 的製程。

[0374]

[結構實例 2]