(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5019859号

(P5019859)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G02F 1/1343 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 550

GO2F 1/133 525

GO2F 1/1343

GO9G 3/20 611E

請求項の数 12 (全 26 頁) 最終頁に続く

(21) 出願番号

特願2006-328223 (P2006-328223)

(22) 出願日

平成18年12月5日 (2006.12.5)

(65) 公開番号

特開2008-139764 (P2008-139764A)

(43) 公開日

平成20年6月19日 (2008.6.19)

審査請求日

平成21年11月5日 (2009.11.5)

(73) 特許権者 598172398

ソニーモバイルディスプレイ株式会社

愛知県知多郡東浦町大字緒川字上舟木50

番地

(74) 代理人 100092152

弁理士 服部 毅巖

(72) 発明者 渡辺 賢哉

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 堀部 修平

最終頁に続く

(54) 【発明の名称】 液晶装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶層に基板面方向の電界を印加して液晶分子の配向制御を行う、第1の画素電極および第2の画素電極を備える横電界方式の液晶素子と、

各画素回路に設けられ、データ線を経由して書き込まれた第1の電圧または第2の電圧を電圧供給端に出力するメモリ回路と、

各画素回路に設けられ、前記メモリ回路の前記電圧供給端と基準電源電位とに接続され、前記電圧供給端から供給される前記第1の電圧または前記第2の電圧を、前記液晶素子の前記第1の画素電極および前記第2の画素電極のうちの一方に供給すると共に、他方に前記基準電源電位の電圧を供給し、前記電圧供給端から供給される前記第1の電圧または前記第2の電圧を前記第1の画素電極または前記第2の画素電極のいずれに供給するかを切り換えることにより、前記液晶素子に印加される電圧を反転させる印加電圧反転回路と、

、

を有する液晶装置。

## 【請求項 2】

請求項1に記載の液晶装置であって、

前記印加電圧反転回路は、

前記電圧供給端と、前記基準電源電位との間に、該電圧供給端から順に直列に接続され、切換制御信号に応じて一方がオンのとき他方がオフする第1および第2のスイッチ素子と、

前記電圧供給端と、前記基準電源電位との間に、該電圧供給端から順に直列に接続され、前記切換制御信号に応じて一方がオンのとき他方がオフする第3および第4のスイッチ素子と、を有し、

前記第1および第2のスイッチ素子の共通接続点に前記第1の画素電極が接続され、前記第3および第4のスイッチ素子の共通接続点に前記第2の画素電極が接続されると共に、

前記第1および第4のスイッチ素子を選択的にオンさせるか、あるいは、前記第2および第3のスイッチ素子を選択的にオンさせるかを、前記切換制御信号によって制御する液晶装置。

**【請求項3】**

10

請求項2に記載の液晶装置であって、

前記第1、第2、第3および第4のスイッチ素子の各々は、同一導電型のトランジスタによって構成され、

前記切換制御信号は、前記第1および第4スイッチ素子を制御する第1のクロック信号と、前記第2および第3スイッチ素子を制御する前記第1のクロック信号と逆相の第2のクロック信号と、を有する液晶装置。

**【請求項4】**

請求項2または請求項3に記載の液晶装置であって、

前記切換制御信号の電圧レベルは、前記第1および第3の各トランジスタを十分にオンさせるに足る電圧レベルに設定され、前記メモリ回路の前記電圧供給端から供給される前記第1の電圧は、前記液晶素子の前記第1または第2の画素電極に、電圧値が低下することなく印加される液晶装置。

20

**【請求項5】**

請求項2～請求項4のいずれかに記載の液晶装置であって、

前記印加電圧反転回路は、

前記切換制御信号の電圧レベルが変化するタイミングにおいて、前記メモリ回路の前記電圧供給端からの電圧供給を遮断するスイッチ素子を、さらに有する液晶装置。

**【請求項6】**

請求項2から請求項5のいずれかに記載の液晶装置であって、

前記液晶装置は、PWM (Pulse Width Modulation) 駆動によって階調重み付けされるデジタル駆動方式の液晶装置であり、前記切換制御信号は、前記デジタル駆動のためのタイミングパルスに基づいて得られる液晶装置。

30

**【請求項7】**

請求項1～請求項6のいずれかに記載の液晶装置であって、

前記メモリ回路および前記印加電圧反転回路における前記基準電源電位は、前記画素回路内の共通の電源配線を介して供給される液晶装置。

**【請求項8】**

請求項1～請求項7のいずれかに記載の液晶装置であって、

前記メモリ回路は、1ビットデータを保持するSRAM型のメモリセルである液晶装置。

40

**【請求項9】**

請求項1～請求項8のいずれかに記載の液晶装置であって、

前記横電界方式の液晶素子は、IPS (In-Plane Switching) 方式の液晶素子である液晶装置。

**【請求項10】**

請求項1～請求項9のいずれかに記載の液晶装置であって、

前記液晶装置は反射型の液晶装置であり、

前記メモリ回路および前記印加電圧反転回路は、光を反射する材料からなる前記第1および第2の画素電極の下側の素子形成領域に配設される液晶装置。

**【請求項11】**

50

請求項 1 ~ 請求項 10 のいずれかに記載の液晶装置であって、前記印加電圧反転回路は、前記液晶素子に画像を表示しているときに、所定のタイミングで、前記液晶素子の前記第 1 および第 2 の電極の電圧を反転させる液晶装置。

【請求項 12】

請求項 1 ~ 請求項 11 のいずれかに記載の液晶装置を搭載した電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶装置、アクティブマトリクス基板および電子機器に関する。

【背景技術】

【0002】

反射型液晶装置は、例えば、携帯電話端末、ノート型パーソナルコンピュータ、反射型プロジェクタ等の電子機器に搭載されている。反射型液晶装置は、例えば、データ線、走査線、トランジスタ等のスイッチ素子、電荷蓄積容量、およびアルミニウム等の反射型の画素電極を備えたガラスまたはシリコン等の基板と、透明導電膜からなる対向電極等を備えたガラス等の基板との間に液晶層を挟持した構成をもつ。画素電極が反射型であるため、画素電極の下側にトランジスタ等のスイッチ素子を設けることができ、解像度を高めた場合でもパネルの開口率が低下せず、高解像度と高輝度を両立することが比較的容易である。

【0003】

但し、保持容量によって画素電圧を保持するアナログ方式の画素回路を用いた場合には、時間の経過と共に、保持容量の電圧値が低下することから、表示画像の明度やコントラストの変動が生じ得る。

【0004】

この問題を解決するために、各画素の反射型画素電極の下側に 1 ピットのメモリセルを配設した液晶装置が提案されている（例えば、特許文献 1 参照）。このようなメモリセルを各画素に備えた液晶装置においては、メモリセルによりデータ線からの画像信号がラッシュされ、その信号が各画素の液晶層に印加される。メモリセルは、新たな信号が書き込まれるまで前の信号を保持している。したがって、例えば、静止画像をメモリに退避した後に別の静止画像を表示し、その後、退避してあった静止画像を再び表示する、というような表示切換えを、簡単かつ効率的に行うことができる。また、画素電圧をデジタル化することにより、クロストーク等による表示品質の劣化が起きにくいといった効果も得ることができる。

【0005】

また、液晶に直流電圧が印加されることによって、いわゆる焼き付き（液晶分子の配向が特定方向に揃うことによる表示画像の劣化現象）が生じるのを防止するためには、液晶に印加する電圧の極性を、周期的に反転することが有効である（例えば、特許文献 2 参照）。

【0006】

また、各画素にメモリセルを備えた液晶装置における、液晶に印加する電圧を反転させるための回路構成は、例えば、特許文献 3 および特許文献 4 に記載されている。これらの文献に記載される技術は、液晶の一方の電極に与える電圧と、対向電極（共通電極）に与える電圧の極性を周期的に反転させる点で共通している。なお、特許文献 3 の技術では、S R A M から得られる相補信号のいずれを液晶に供給するかを、トランジスタのオン／オフによって切換えている。また、特許文献 4 に記載される技術では、液晶に印加される電圧を反転させたときにオフセットが生じると焼き付きの原因となることから、光センサから得られる応答波形がフィールド毎に等しくなるように対向電極（共通電極）に与える電圧のオフセット電圧を微調整している。

【0007】

また、液晶装置の一形態として、液晶層に基板面方向の電界を印加して液晶分子の配向

10

20

30

40

50

制御を行う方式（以下、横電界方式と称する。）のものが知られており、液晶に電界を印加する電極の形態によりIPS（In-Plane Switching）方式、FFS（Fringe-Field Switching）方式等と呼ばれる（例えば、特許文献5参照）。横電界方式の液晶は、水平な液晶分子を横方向に回転させることによって光の透過状態を制御する。液晶分子の垂直方向の傾きが発生しないため、視野角による輝度変化／色変化が少ない。したがって、横電界方式の液晶は、高視野角特性と高品質な発色性が必要なときに利用される。

【特許文献1】特開平8-286170号公報

【特許文献2】特開平5-303077号公報

【特許文献3】特開2005-148453号公報

【特許文献4】特開2005-25048号公報

【特許文献5】特開2001-337339号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

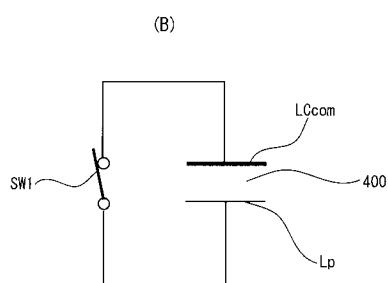

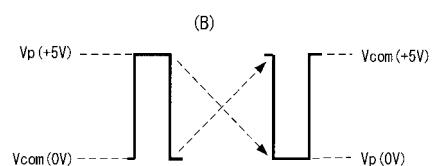

液晶の焼き付きを防止するためには、直流電圧が液晶に長時間にわたって印加されることを防止する必要がある。図13は、液晶装置における焼き付き防止のために必要な動作を示す図であり、（A）は液晶に電圧を印加する場合の動作を示す図であり、（B）は液晶に電圧を印加しない場合の動作を示す図である。図13では、液晶層に基板面に垂直に電界が印加されるタイプの液晶（例えば、TN液晶）が用いられる。

【0009】

図13（A）に示すように、液晶400に電圧が印加される場合には、焼き付き防止のために、例えば周期的に、液晶に印加する電圧の極性を反転させる。すなわち、図中のX1, X2の各端子に印加する電圧の極性が周期的に切換えられる。なお、液晶400は、下部電極Lpと、上部電極（共通電極）LCcomと、を有する。

【0010】

また、図13（B）に示すように、液晶400に電圧が印加されない場合の焼き付き防止には、下部電極Lpと、上部電極（共通電極）LCcomとをショートして等電位とし、直流オフセットを生じさせないようにすることが重要である。なお、図13（B）では、便宜上、スイッチSW1を用いて液晶の両電極をショートさせているが、実際には、各電極に同じ電圧を印加することによって、液晶400の両極のショート状態を実現する。

【0011】

しかし、各画素にメモリ回路を備える液晶装置において、図13（A），（B）に模式的に記載されるような理想的な動作（焼き付き防止のための極性反転動作や両極のショート動作）を実現することは、現実には困難である。

【0012】

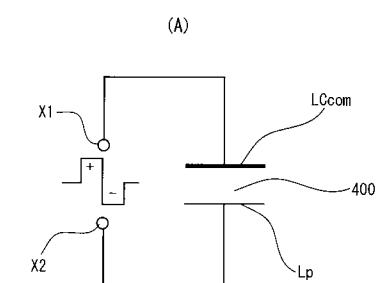

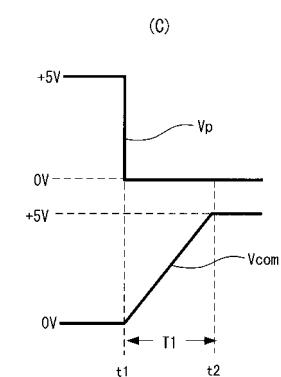

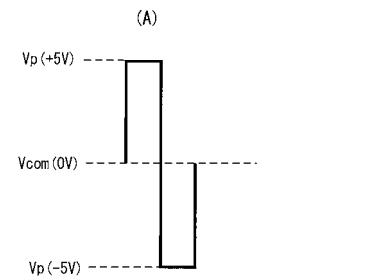

図14（A）～（C）は、各画素回路にメモリ回路を備える液晶装置における、液晶の両極の電圧を反転させる際の問題点を説明するための図である。

【0013】

液晶の両極の電圧を反転させる様としては、図14（A）に示すように、対向電極（共通電極）LCcomの電圧（Vcom）を固定し、下部電極Lpの電圧（Vp）の極性を反転する方法と、図14（B）に示すように、下部電極Lpと共通電極LCcomの各電圧（VpおよびVcom）を同時に入れ替える方法がある。なお、図14（A）～（C）では、液晶に印加する電圧は“5V”と“0V”としている。

【0014】

図14（A）に示す方法をとれば、対向電極（共通電極）LCcomの電位（Vcom=0V）を変化させる必要がないため便利であるが、下部電極Lpの電圧（Vp）をVcomに対して相対的に変化させる必要があるため、結果的に負電源を使用する必要が生じる。各画素に備わる各メモリ回路を負電源で動作させることは現実的ではないため、メモリ回路を用いる液晶装置では、図14（A）の方式は採用できない。

【0015】

10

20

30

40

50

そこで、図14(B)のように、下部電極Lpと共に共通電極LCcomの各電圧(VpおよびVcom)を同時に入れ替える方法を採用せざるを得ない。この場合、問題となるのは、対向電極(共通電極)LCcomは、液晶装置の全画素に共通する電極であるため、基板間に挟持される液晶層の全体が負荷容量として機能し、したがって、電圧の変化が遅いということである。

#### 【0016】

つまり、図14(C)に示すように、下部電極Lpについては、1画素単位の電極であるため負荷が軽い。したがって、液晶の両極の電圧の反転時(時刻t1)には、下部電極Lpの電圧(Vp)は速やかに変化する。これに対し、対向電極(共通電極)LCcomの電圧(Vcom)の変化は、負荷が重いために遅くなり、図14(C)に示すように、遷移期間T1(時刻t1～t2)を経て電圧が切り換わる。したがって、結果的に、遷移期間T1においては、液晶に印加される電圧は時間経過と共に徐々に変化することになり、これに伴う液晶の透過率の変化は、その変化が遅いために人の目につきやすく、よってフリッカ(視覚的なちらつき)が生じやすい。10

#### 【0017】

また、図14(B)のような電圧反転制御を行うためには、VpとVcomの各々を、別々の制御回路によって個別に制御する必要があり、回路構成が複雑化するのは否めない。

#### 【0018】

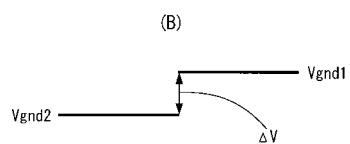

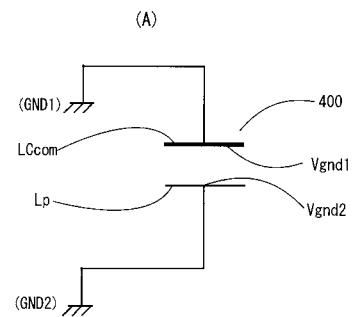

図15(A), (B)は、各画素回路にメモリ回路を備える液晶装置における、液晶の両極をショート状態(同電位状態)とする場合の問題点を説明するための図である。図15(A)に示すように、液晶400の両電極(Lp, LCcom)には、別々の回路(配線)から接地電位(GND1, GND2)が与えられる。しかし、別々の回路(配線)経由で各電極に与えられる各接地電位(GND1, GND2)は、電圧レベルの変動が各々独立に生じるために、相対的に差が生じる場合がある。20

#### 【0019】

また、液晶の各電極(Lp, LCcom)は2次元の広がりをもつたため、その電圧(Vp, Vcom)は面内ではらつき、これによって、各画素の両極に、直流オフセットが生じる場合もある。

#### 【0020】

したがって、結果的に、図15(B)に示すように、液晶400の各画素の両極に直流オフセット電圧(V)が生じる場合がある。なお、図中のVgnd1, Vgnd2は、面内ばらつきを考慮した各画素の両極の電圧を示す。このような直流オフセット電圧Vは、焼き付きの原因となる。30

#### 【0021】

このように、各画素にメモリ回路を備えた液晶装置において、フリッカを発生させることなく、焼き付け防止のための印加電圧の反転を行うこと、ならびに直流オフセットを発生しない、完全なショート状態を実現することは困難である。また、液晶の各電極(Lp, LCcom)の電圧を個別に制御する必要があるため、制御のための回路構成が複雑化する。40

#### 【0022】

本発明は、このような考察に基づいてなされたものであり、その目的は、簡単な回路構成ならびに簡単な制御によって、フリッカを抑制しつつ印加電圧の高精度の反転を実現して焼き付けを防止し、また、液晶に電圧を印加しないときに、直流オフセットを生じさせることなく両極のショートを実現することにある。

#### 【課題を解決するための手段】

#### 【0023】

本発明の液晶表示装置の一態様では、液晶層に基板面方向の電界を印加して液晶分子の配向制御を行う、第1の画素電極および第2の画素電極を備える横電界方式の液晶素子と、各画素回路に設けられ、データ線を経由して書き込まれた第1の電圧または第2の電圧

を電圧供給端に出力するメモリ回路と、各画素回路に設けられ、メモリ回路の電圧供給端と基準電源電位とに接続され、電圧供給端から供給される第1の電圧または第2の電圧を、液晶素子の第1の画素電極および第2の画素電極のうちの一方に供給すると共に、他方に基準電源電位の電圧を供給し、電圧供給端から供給される第1の電圧または第2の電圧を第1の画素電極または第2の画素電極のいずれに供給するかを切り換えることにより、液晶素子に印加される電圧を反転させる印加電圧反転回路と、を有する。

#### 【0024】

横電界方式の液晶は、液晶を挟む2つの基板のうちの一方の基板側に、1画素に対応した2つの電極が配置される構造をもち、TN液晶のように、全画素に共通した共通電極(LCcom)を用いる場合に比べて負荷容量が小さい(すなわち、横電界方式の液晶の各画素の負荷容量は一画素に相当する容量のみである)。したがって、液晶に印加する電圧を反転する場合において、各電極の電圧は共に、速やかに変化する。本発明では、横電界方式の液晶のこのような特性に着目して、横電界方式の液晶を積極的に採用する。また、メモリ回路を電圧供給源としてのみ機能させ、液晶に印加される電圧の反転は、専用の印加電圧反転回路により実現するという、電圧供給と電圧反転の各機能を完全に分離した新規な画素回路構成を採用する。印加電圧反転回路は、メモリ回路の電圧供給端から供給される第1または第2の電圧(例えば、"1"または"0"に対応した"5V(VDD)"または"0V(GND)"の電圧)を電源電圧として動作する。すなわち、印加電圧反転回路は、メモリ回路の電圧供給端から供給される電源電圧(第1または第2の電圧)と、基準電源電位(グランド)との間で動作し、そして、メモリ回路から供給される電圧(第1または第2の電圧)ならびに基準電源電圧(グランド)の各々を、横電界方式の液晶の第1および第2の画素電極のいずれに供給するかを(つまり、各電圧の供給経路を)切り換える。つまり、電圧の供給経路を切り換えるだけであり、電圧源自体は共通のため、電圧の反転前と反転後の電圧値自体には何も変動がなく、正確な電圧の極性反転が実現する。また、液晶の面内ばらつきによって、各画素における電圧レベルが若干変動したとしても、上述のとおり各画素における電圧源自体は共通であり、その画素内では、電圧の反転前と反転後の電圧値自体には何も変動がなく、したがって、各画素において直流オフセットは発生しない。また、電圧の供給経路を切り換えるだけであるため、第1および第2の画素電極の各々に供給する電圧レベルの切り替えを、簡単な回路により同時に実現することができる。従来のように、共通Vcomと下部電極の電圧Vpを別個の回路で制御し、各電圧を高精度に調整し、かつ、各電圧の切り換えタイミングの同期をとる必要はなくなる。横電界方式の液晶は、上述のとおり各電極の電圧変化が速やかに行われ、高速応答が可能であるため、従来のような電圧の遷移期間において液晶の透過率が徐々に変化していくというような現象が生じにくく、フリッカが抑制される。また、仮に、液晶の透過率が時間的に変化したとしても、その変化が速いために、人間の目には認識されにくく、この点でもフリッカが抑制される。また、印加電圧反転回路の基準電源電圧が、例えばグランドレベルであるとき、メモリ回路から供給する電圧を0Vとすれば、液晶の両電極に印加される電圧は、共に正確に0Vとなり、液晶への電圧印加がない場合のショート状態が実現され、この際、直流オフセットは生じない。

#### 【0025】

また、本発明の液晶装置の他の態様では、印加電圧反転回路は、電圧供給端と、基準電源電位との間に、該電圧供給端から順に直列に接続され、切換制御信号に応じて一方がオンのとき他方がオフする第1および第2のスイッチ素子と、電圧供給端と、基準電源電位との間に、該電圧供給端から順に直列に接続され、切換制御信号に応じて一方がオンのとき他方がオフする第3および第4のスイッチ素子と、を有し、第1および第2のスイッチ素子の共通接続点に第1の画素電極が接続され、第3および第4のスイッチ素子の共通接続点に第2の画素電極が接続されると共に、第1および第4のスイッチ素子を選択的にオンさせるか、あるいは、第2および第3のスイッチ素子を選択的にオンさせるかを、切換制御信号によって制御する。

#### 【0026】

10

20

30

40

50

印加電圧反転回路の具体的な回路構成例を明らかとしたものである。メモリ回路の電圧供給端と基準電源電位（一般にはグランド）との間に2つのスイッチ素子を直列に接続し、かつ、そのような2つのスイッチ素子の組が二組あり、各組は並列に設けられ、そして、各組の2つのスイッチ素子の共通接続点が、液晶の第1および第2の画素電極に電気的に接続される。そして、一方の組の一方のスイッチ素子がオンしてメモリ回路からの電圧を液晶に供給するときは、他方の組の一方のスイッチ素子がオンして、基準電源電位（グランド）を液晶に供給するように制御し、同様に、他方の組の他方のスイッチ素子がオンしてメモリ回路からの電圧を液晶に供給するときは、一方の組の他方のスイッチ素子がオンして、基準電源電位（グランド）を液晶に供給するように制御する。

このような4つのスイッチ素子の同期的な切換制御は、切換制御信号を用いて簡単に実現することができる。例えば、逆相のクロック信号を用いれば、一方のスイッチ素子をオンし、他方のスイッチ素子を同時にオフするというような制御も簡単に行うことができる。また、最小限の素子にて構成されるため、これ以上簡単化することができないコンパクトな回路が実現される。

#### 【0027】

また、本発明の液晶装置の他の態様では、第1、第2、第3および第4のスイッチ素子の各々は、同一導電型のトランジスタによって構成され、切換制御信号は、第1および第4スイッチ素子を制御する第1のクロック信号と、第2および第3スイッチ素子を制御する第1のクロック信号と逆相の第2のクロック信号と、を有する。

#### 【0028】

各スイッチ素子が同一導電型のトランジスタ（MOSトランジスタ、バイポーラトランジスタを含む）からなり、第1～第4のトランジスタのオン／オフは、相補的なクロック（互いに逆相のクロック）によって制御されることを明らかとしたものである。メモリ回路から供給される電圧は、第1～第4の各MOSトランジスタのソースまたはドレインに直接に印加されるが、各MOSトランジスタのソース／ドレイン間の耐圧はかなり高いため、耐圧の問題は生じない。また、メモリ回路と印加電圧反転回路は直結されている（例えば、上述の特許文献4に開示されるように、液晶への電圧供給バスに、MOSトランジスタのゲート／ソース経路が存在しない）ため、メモリ回路および印加電圧反転回路の高レベル側の電源電圧の値は同じでよく、（印加電圧反転回路を構成する4つのトランジスタのゲート電位は画素アレイ外部からの信号～CLK、/CLKによって供給されるため、任意の電圧（SRAMから供給されるVDDの電圧がVthドロップしないVDD+Vthといった電圧）を供給することができる。特許文献4に開示されている技術では、SRAMからの供給電圧をVDD+Vthとする必要があるため、SRAMを構成する各トランジスタを高耐圧トランジスタで構成する必要があるのに対して、本発明では、SRAMを構成するトランジスタとして、高耐圧トランジスタを使用せずとも、VDD電圧を印加電圧反転回路を構成するトランジスタを介して液晶に印加できる点で優位である。なお、本発明の場合、印加電圧反転回路を構成するトランジスタのゲートには、CLK、/CLKとして（VDD+Vth）といった高電圧が印加されるが、一般にトランジスタのS/D（ソース／ドレイン）耐圧よりもゲート耐圧の方が耐圧性が優れており、特に問題はない。また、トランジスタのS/D耐圧を高耐圧化しようとした場合には、トランジスタの構造自体を高耐圧に適した構造にする必要があり、なおかつトランジスタのS/Dサイズが大きくなってしまうという問題が生じやすいが、ゲート耐圧を高耐圧化する場合には、ゲート酸化膜厚を厚くするだけで高耐圧化が可能であり、実現が容易である。また、印加電圧反転回路に用いている4つのトランジスタは、VDDまたはGND電位を液晶へ印加することを目的としているため、トランジスタのサイズ（W/L）は任意のサイズで良い。但し、液晶への充電時間、放電時間を等しくする場合には、4つのトランジスタサイズを等しくしておくことが望ましい。このように、本発明では、メモリ回路を構成するトランジスタや印加電圧反転回路を構成するトランジスタを高耐圧トランジスタとする必要がなく、コンパクトな画素回路を形成することができ、デバイスの製造プロセスが複雑化することもない。また、相補的なクロック信号は、デジタル回路では汎用的に用いられるもの

10

20

30

40

50

であり、生成が容易である。

**【0029】**

また、本発明の液晶装置の他の態様では、切換制御信号の電圧レベルは、第1および第3の各トランジスタを十分にオンさせるに足る電圧レベルに設定され、メモリ回路の電圧供給端から供給される第1の電圧は、液晶素子の第1または第2の画素電極に、電圧値が低下することなく印加される。

**【0030】**

メモリ回路から例えば、5V (VDD) の電源電圧が印加電圧反転回路に供給されるとする。ここで、印加電圧反転回路にて電圧ドロップが生じると、液晶には5V (VDD) に満たない不十分な電圧しか印加できないことになり電圧の利用効率が低下する。しかし、メモリ回路からの電圧を液晶に供給する働きをする第1および第3のMOSトランジスタが十分にオンすれば、メモリ回路からの電圧 (5V = VDD) はそのまま液晶に供給されることになり問題は生じない。このことは、第1～第4の各トランジスタが例えばNMOSトランジスタであるとき、第1および第3のNMOSトランジスタのゲートを、(5V (VDD) + 閾値電圧 (Vth)) 以上の電圧レベルの制御信号によって駆動することによって実現される。VDDを超える電圧は、例えば、ブートストラップ回路を用いて電源電圧を昇圧することによって簡単に得ることができるため、上述のようなNMOSトランジスタのゲート駆動方法の実現に際し、特に問題はない。

**【0031】**

また、本発明の液晶装置の他の態様では、印加電圧反転回路は、切換制御信号の電圧レベルが変化するタイミングにおいて、メモリ回路の電圧供給端からの電圧供給を遮断するスイッチ素子を、さらに有する。

**【0032】**

印加電圧反転回路を構成する直列接続された2つのトランジスタのオン／オフが切り換わる途中には各トランジスタが同時にオンする状態が生じ、このときに貫通電流が流れる。そこで、貫通電流が生じるタイミングでスイッチ素子をオフし、メモリ回路からの電圧（電流）の供給を遮断し、貫通電流が流れるのを、確実に防止できるようにしたものである。

**【0033】**

また、本発明の液晶装置の他の態様では、液晶装置は、PWM (Pulse Width Modulation) 駆動によって階調重み付けされるデジタル駆動方式の液晶装置であり、切換制御信号は、デジタル駆動のためのタイミングパルスに基づいて得られる。

**【0034】**

液晶のデジタル駆動方式（PWM駆動方式であり、1フレームをサブフィールド分割して各サブフィールドにおける液晶のオン／オフを制御することから、サブフィールド駆動とも呼ばれることがある）では、各サブフレームにおける液晶のオン／オフを決定するために、タイミング回路によるタイミングパルスの生成が必須である。印加電圧反転回路に供給される制御信号（相補的なクロック信号）は、そのタイミングパルスをそのまま援用して、あるいは、そのタイミングパルスを分周あるいは遅倍することによって、簡単に生成することができる。よって、本発明では、制御信号を生成するための特別な回路（専用の回路）が不要であり、したがって、回路構成（システム構成）を簡素化することができる。

**【0035】**

また、本発明の液晶装置の他の態様では、メモリ回路および印加電圧反転回路における基準電源電位は、画素回路内の共通の電源配線を介して供給される。

**【0036】**

液晶の両極をショートするときには、メモリ回路から供給される電圧（例えば0V）を液晶の一方の電極に供給し、印加電圧反転回路の基準電源電位（例えば0V）を液晶の他方の電極に供給する。このとき、メモリ回路の接地配線および印加電圧反転回路の接地配線が画素回路内で共通であれば、仮に、液晶の面内ばらつき等によって電圧レベル（0V

10

20

30

40

50

)に変動が生じたとしても、双方の電位が同様に変動するため、結果的に、液晶の両電極に印加される電圧レベルの相対的な電位差は生じない。よって、液晶に電圧を印加しないときには、高精度のショート状態が実現され、直流オフセットが生じず、したがって焼き付きが生じる心配がない。

【0037】

また、本発明の液晶装置の他の態様では、メモリ回路は、1ビットデータを保持するS R A M型のメモリセルである。

【0038】

S R A Mセルとしては、フリップフロップの負荷を高抵抗（例えばイオン打ち込みで形成される抵抗）で形成する高抵抗型S R A Mセル、負荷も含めてM O Sトランジスタで構成するフルC M O S型セルが含まれ、さらに、複数のインバータを用いてフリップフロップを形成するラッチ型セルも含まれる。

10

【0039】

また、本発明の液晶装置の他の態様では、横電界方式の液晶素子は、I P S (In-Plane Switching) 方式の液晶素子である。

【0040】

横電界方式の液晶として、使用実績のあるI P S液晶を使用するものである。

【0041】

また、本発明の液晶装置の他の態様では、液晶装置は反射型の液晶装置であり、メモリ回路および印加電圧反転回路は、光を反射する材料からなる第1および第2の画素電極の下側の素子形成領域に配設される。

20

【0042】

反射型液晶の場合、画素電極の下部に素子形成領域を設けることができる。本発明の印加電圧反転回路は簡素化された構成となっているため、画素電極の下部の空スペースに、メモリ回路および印加電圧反転回路を配置することは、むずかしいことではない。したがって、画素回路の占有面積を大きくすることなく、本発明にかかる画素回路を形成することが可能である。

【0043】

また、本発明の液晶装置の他の態様では、印加電圧反転回路は、液晶素子に画像を表示しているときに、所定のタイミングで、液晶素子の第1および第2の電極の電圧を反転させる。

30

【0044】

液晶の印加電圧をどのようなタイミングで反転させるかは、使用する液晶の特性に応じて適宜、決定される。焼き付きを防止するためには、例えば、1フレーム毎（あるいは、数フレーム毎）に液晶の両電極に印加される電圧の極性を反転するのが望ましい。

【0046】

液晶層が接続される前の、アクティブマトリクス基板自体の構成を明らかとしたものである。

【0047】

また、本発明の電子機器は、本発明の液晶装置を搭載する。

40

【0048】

本発明の液晶装置は、例えば、携帯電話のサブパネル、低消費電力のノート型パソコン、反射型プロジェクタ等の電子機器に搭載することが可能である。電圧反転に伴う静止画のフリッカが抑制されるため、高画質の画像を表示できる。また、直流オフセットの発生が低減されて焼き付きが生じにくくことから、表示画像の画質の経時的な劣化も生じにくい。

【0049】

本発明によれば、簡単な回路構成ならびに簡単な制御によって、フリッカを抑制しつつ印加電圧の高精度の反転を実現することができ、また、液晶に電圧を印加しないときは、直流オフセットを生じさせないショート状態を実現することができる。

50

**【発明を実施するための最良の形態】****【0050】**

次に、本発明の実施形態について、図面を参照して説明する。

**【0051】**

(第1の実施形態)

まず、1画素の基本構成について説明する。

**【0052】**

(1画素の基本構成)

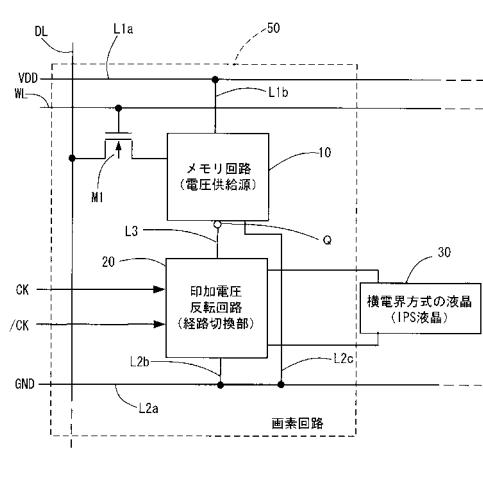

図1は、本発明の液晶装置における1画素の構成を示す図である。図1に示すとおり、1画素は、画素回路50と、横電界方式の液晶(ここではIPS液晶とする。但し、これに限定されるものではない)30と、を含んで構成される。

10

**【0053】**

横電界方式の液晶は、液晶層に基板面方向の電界を印加して液晶分子の配向制御を行う方式の液晶であり、液晶に電界を印加する電極の形態によりIPS(In-Plane Switching)方式、FFS(Fringe-Field Switching)方式等と呼ばれるものが知られている。横電界方式の液晶は、液晶を挟む2つの基板のうちの一方の基板側に、1画素に対応した2つの電極が配置される構造をもち、TN液晶のように、全画素に共通した共通電極(LCCoM)を用いる場合に比べて負荷容量が小さい(すなわち、横電界方式の液晶の各画素の負荷容量は一画素に相当する容量のみである)。したがって、液晶に印加する電圧を反転する場合において、各電極の電圧は共に、速やかに変化する。本発明では、横電界方式の液晶のこのような特性に着目し、負荷を軽減して両電極の電圧変化を速めるために、横電界方式の液晶を積極的に採用する。

20

**【0054】**

なお、IPS液晶装置の構造については、図7および図8を用いて後述する。図8から明らかなように、IPS液晶装置は、第1および第2の画素電極(光反射性の材料からなる)218a, 218bが、同一の基板側に近接して配置されており、かつ、電界Eは、基板の面方向に水平に印加される。

**【0055】**

また、画素回路50は、ゲートが走査線(WL)に接続され、一端(ソースまたはドレイン)がデータ線(DL)に接続された画素選択トランジスタ(NMOSトランジスタ)M1と、電圧供給源として機能するメモリ回路10と、液晶の両極に印加する電圧を反転するための印加電圧反転回路(経路切換部)20と、を有する。

30

**【0056】**

メモリ回路10は、第1の電源配線(L1a)を介して与えられる高レベル側電源電圧(VDD:5V)と、第2の電源配線(L2a)を介して与えられる接地電位(GND)との間で動作する。このメモリ回路10には、データ線(DL)を経由して、黒/白に対応する2値電圧(例えば、第1の電圧:VDD(5V), 第2の電圧:GND(0V))が書き込まれる。このメモリ回路10は、書き込まれた電圧(VDDまたはGND)を、印加電圧反転回路20に電源電圧として供給する働きをし、液晶に印加する電圧の反転には関与しない。

40

**【0057】**

印加電圧反転回路(経路切換部)20は、メモリ回路10の電圧供給端(Q)と、基準電源電位(GND)との間に接続されている。印加電圧反転回路20は、メモリ回路10から供給されるVDD(5V)を、高レベル側電源電圧として動作する。低レベル側電源電圧(GND)は、第2の電源配線(L2a)を経由して与えられる。この印加電圧反転回路20には、互いに逆相の相補クロック(経路切換のための切換制御信号)CK, /CKが入力され、この相補クロックCK, /CKの電圧レベルが反転するタイミングで、液晶への電圧供給経路が切り換えられる。

**【0058】**

図1において、L1bは、第1の電源配線(L1a)の電源電位VDDを、メモリ回路

50

10に供給するための配線である。また、L<sub>2b</sub>は、第2の電源配線(L<sub>2a</sub>)の電源電位GNDを、印加電圧反転回路20に供給するための配線である。また、L<sub>2c</sub>は、第2の電源配線(L<sub>2a</sub>)の電源電位GNDを、メモリ回路10に供給するための配線である。また、L<sub>3</sub>は、メモリ回路10の電圧供給端(Q)から出力される2値電圧(VDD, GND)を、印加電圧反転回路20に供給するための配線である。

#### 【0059】

メモリ回路10に接地電位を供給する接地配線と、印加電圧反転回路20に接地電位を供給する接地配線は、画素回路50内において共通である。つまり、接地配線(L<sub>2a</sub>, L<sub>2b</sub>, L<sub>2c</sub>)は共通の接地配線であり(つまり、別系統の接地配線ではなく)、したがって、メモリ回路10から供給される接地電位(0V)と、印加電圧反転回路20の基準電源電位(GND)としての接地電位(0V)とは常に一致し、相対的な電位差が生じない(すなわち、一方が変動すれば他方も同様に変動するため相対的な電位差は常に生じない)ということである。このことは、印加電圧反転回路20から液晶30の両極に0Vを与えて、液晶30をショート状態とするときに、直流オフセットが発生しないことを意味している。

#### 【0060】

##### (メモリセルの構成例)

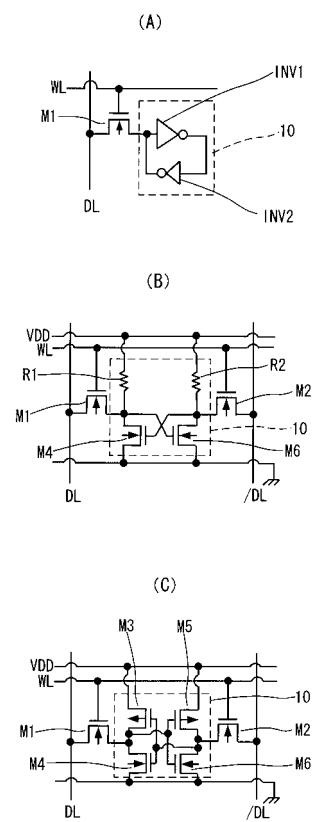

図2(A)～(C)は、図1に示されるメモリ回路(メモリセル)10の回路構成例を示す図である。いずれもSRAM(スタティク・ランダムアクセスメモリ)型のメモリセルである。

10

20

#### 【0061】

図2(A)のメモリセル(ラッチ型メモリセル)では、駆動能力が大きいインバータINV1と、駆動能力が小さいインバータINV2と、によって、1ビットのデータを保持するためのフリップフロップが構成される。

#### 【0062】

図2(B)のメモリセル(高抵抗型メモリセル)は、2つのトランジスタ(M1, M2)と、フリップフロップを構成するN MOSトランジスタM4, M6と、負荷抵抗R1, R2と、で構成される。データ線としては、相補信号を供給する2本のデータ線(DL, /DL)が設けられる。

30

#### 【0063】

図2(C)のメモリセルは、フルCMOS構成のメモリセルである。図2(B)のメモリセルと基本的な構成は同じである。但し、フリップフロップの負荷は、PMOSトランジスタM3, M5により構成される。データ線としては、相補信号を供給する2本のデータ線(DL, /DL)が設けられる。

#### 【0064】

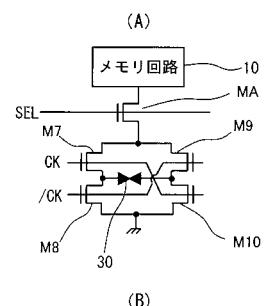

##### (画素回路の構成)

図3は、画素回路50の具体的な回路構成の一例を示す回路図である。図3では、メモリ回路10として、図2(C)に示される、フルCMOS構成のメモリセルが使用されている。

40

#### 【0065】

また、印加電圧反転回路20は、メモリ回路10の電圧供給端(Q)と基準電源電位(GND)との間に直列に接続された、第1および第2のスイッチ素子としてのN MOSトランジスタ(M7, M8)と、同じく、メモリ回路10の電圧供給端(Q)と基準電源電位(GND)との間に直列に接続された、第3および第4のスイッチ素子としてのN MOSトランジスタ(M9, M10)と、により構成される。

#### 【0066】

第1および第2のスイッチ素子としてのN MOSトランジスタ(M7, M8)の共通接続点(c)と、第3および第4のスイッチ素子としてのN MOSトランジスタ(d)の共通接続点(d)の各々に、横電界方式の液晶(IPS液晶素子)30の第1および第2の

50

電極（図8の参照符号218a, 218b）が接続される。

【0067】

そして、第1および第4のスイッチ素子としてのN MOSトランジスタ（M7, M10）のゲートには、切換制御信号としてのクロック信号（CK）が入力され、このクロック信号（CK）によって、N MOSトランジスタ（M7, M10）が同期してオンするか、あるいはオフするかが制御される。

【0068】

同様に、第2および第3のスイッチ素子としてのN MOSトランジスタ（M8, M9）のゲートには、切換制御信号としての、CKとは逆相のクロック信号（/CK）が入力され、このクロック信号（/CK）によって、N MOSトランジスタ（M8, M9）が同期してオンするか、あるいはオフするかが制御される。

【0069】

すなわち、N MOSトランジスタ（M7, M8）は、メモリ回路10の電圧供給端（Q）と基準電源電位（GND）との間に直列に接続された一組のトランジスタである。同様に、第3および第4のトランジスタ（M9, M10）も、メモリ回路10の電圧供給端（Q）と基準電源電位（GND）との間に直列に接続された一組のトランジスタである。そして、各組のトランジスタ（M7およびM8, M9とM10）は、メモリ回路10の電圧供給端（Q）と基準電源電位（GND）との間に並列に接続されているという関係にある。各組の2つのN MOSトランジスタの共通接続点（c, d）が、液晶素子30の第1および第2の画素電極（図8の参照符号218a, 218b）に電気的に接続される。

【0070】

そして、一方の組の一方のトランジスタ（ここでは、第1のN MOSトランジスタ（M7）とする）がオンして、メモリ回路10からの電圧を液晶素子30の一方の電極（図8の218a）に供給するときは、他方の組の一方のN MOSトランジスタ（ここでは、第4のトランジスタM10）がオンして、基準電源電位（グランド）を液晶素子30の他方の電極（図8の218b）に供給する。

【0071】

同様に、他方の組の他方のトランジスタ（すなわち、第3のN MOSトランジスタ（M9））がオンして、メモリ回路10からの電圧を液晶素子30の一方の電極（図8の218a）に供給するときは、一方の組の他方のN MOSトランジスタ（すなわち、第2のトランジスタM8）がオンして、基準電源電位（グランド）を液晶素子30の他方の電極（図8の218b）に供給する。

【0072】

また、先に説明したように、メモリ回路10の接地電位および印加電圧反転回路20の接地電位は、共通の接地配線（L2（具体的にはL2a, L2b, L2c））を介して供給される。これによって、液晶素子30の両電極（218a, 218b）の各々に接地電位が供給されるときには、その電圧レベルに相対的な差がなく、直流オフセットが発生せず、焼き付き現象が生じる心配がない。

【0073】

また、図3の回路では、メモリ回路10から供給される電圧は、印加電圧反転回路20を構成する上側のN MOSトランジスタ（M7, M9）の一端（ソースまたはドレイン）に直接に印加される。一般に、MOSトランジスタのソース／ドレイン間の耐圧は、ゲート・ソース間の耐圧に比べて高いため、耐圧の問題は特に生じない。

【0074】

また、図3の画素回路の場合、メモリ回路10と印加電圧反転回路20は直結されており、例えば、上述の特許文献4に開示されるように、液晶への電圧供給バスに、MOSトランジスタのゲート／ソース経路が存在するような接続形態となっていない。よって、メモリ回路10および印加電圧反転回路20の高レベル側の電源電圧（VDD）の値は同じでよく（すなわちVDDは共に5V）、よって、各回路（10, 20）を構成するMOSトランジスタ（M1～M10）のサイズを同じにすることができる。例えば、メモリ回路1

10

20

30

40

50

0を構成するトランジスタ（M1～M5）を高耐圧トランジスタとする必要もない。

#### 【0075】

また、相補的なクロック信号（CK, /CK）は、デジタル回路では汎用的に用いられるものであり、生成が容易である。特に、PWMを用いたデジタル階調駆動で使用されるタイミングパルスに基づいて、相補クロック（CK, /CK）を得ることは容易である。

#### 【0076】

また、図3の画素回路では、メモリ回路10から供給されるVDD（5V）は、そのまま印加電圧反転回路20の高レベル側の電源電圧となり、そして、そのVDD（5V）はそのまま液晶素子30の一方の電極（図8の218a）に供給されるのが、電圧の利用効率からみて望ましい。これを実現するためには、NMOSトランジスタ（M7, M9）のソース・ドレイン間で電圧ドロップが発生しないことが条件となり、このためには、第1および第3のNMOSトランジスタ（M7, M9）が十分にオンすることができるゲート電圧を供給すればよい。

#### 【0077】

具体的には、第1および第3のNMOSトランジスタ（M7, M9）のゲートを、（5V（VDD）+ 閾値電圧（Vth））以上の電圧レベルの制御信号（CKあるいは/CK）によって駆動すればよい。CKあるいは/CKを、VDDを超える電圧に昇圧することはそれほどむずかしいことではない。例えば、ブーストストラップ回路を用いて電源電圧（VDD）を昇圧することによって簡単に得ることができるため、上述のようなNMOSトランジスタのゲート駆動方法の実現に際し、特に問題はない。

#### 【0078】

（印加電圧反転回路の基本的な動作）

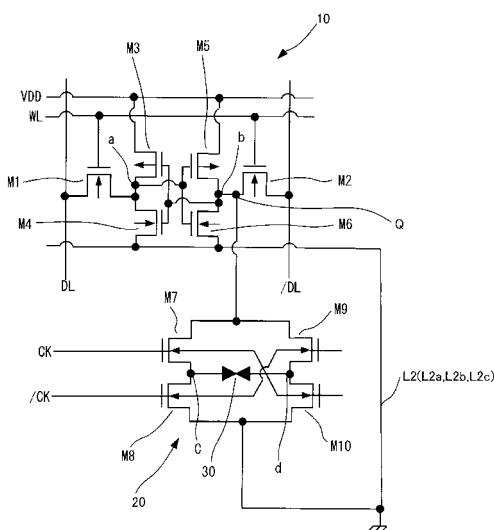

図4（A）～（C）は、印加電圧反転回路による、液晶に印加する電圧の極性反転動作を説明するための図である。図4では、便宜上、液晶素子30は容量として示している。

#### 【0079】

図4（A）は、印加電圧反転回路20に、液晶素子30を接続した状態を示している。図4（B）では、第1および第4のNMOSトランジスタ（M7, M10）がオンし、太線で示されるような経路で、液晶素子30の両電極に電圧が印加される。図4（C）では、第2および第3のNMOSトランジスタ（M8, M9）がオンし、太線で示されるような経路で、液晶素子30の両電極に電圧が印加される。

#### 【0080】

図4（B）の状態では、メモリ回路10から供給される電圧は、液晶素子30の上側の電極に印加され、基準電源電位（GND）は、液晶素子30の下側の電極に印加されている。これに対し、図4（C）の状態では、メモリ回路10から供給される電圧は、液晶素子30の下側の電極に印加され、基準電源電位（GND）は、液晶素子30の上側の電極に印加されている。このように、電圧印加経路を切換えることによって、液晶素子30に印加される電圧を高速に切換えることができる。

#### 【0081】

また、図4（B）, (C)から明らかなように、電圧印加経路が切り換わっているだけであり、液晶素子30に印加される電圧の電圧源（ソース）には何ら変化がない。すなわち、液晶素子30に印加される電圧は、メモリ回路10から供給される電圧と、印加電圧反転回路20の基準電源電位（GND）であり、このことは、図4（A）, (B)の各状態において共通している。したがって、極性反転の前後で電圧値がばらつくことがなく、正確な極性反転が担保され、かつ、そのような電圧反転を簡単に行うことができる。

#### 【0082】

従来のように、下部電極と対向電極（共通電極）の電圧（Vp, Vcom）を個別に制御し、両電圧のレベルを高精度に調整し、かつ、各電圧の印加タイミングを合わせるといった面倒な制御は本実施形態の回路では、一切必要ない。

#### 【0083】

（メモリ回路および印加電圧反転回路の具体的な動作）

10

20

30

40

50

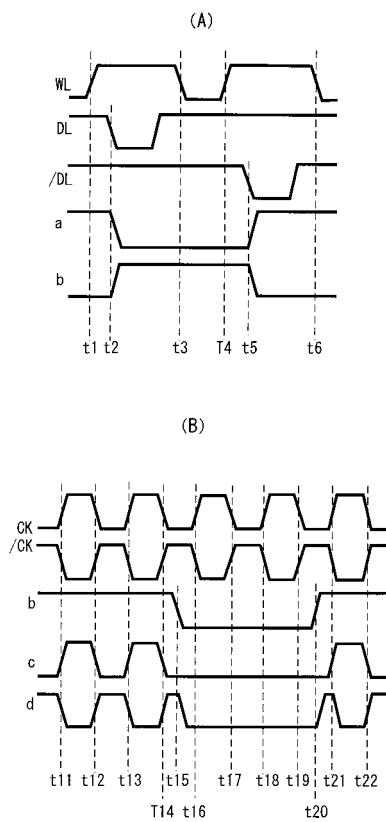

図5は、図3の画素回路の動作タイミングを示すタイミング図であり、(A)はメモリ回路の動作を示すタイミング図であり、(B)は、印加電圧反転回路の動作を示すタイミング図である。

#### 【0084】

まず、図5(A)を参照してメモリ回路10の動作を説明する。時刻t1において走査線WLがローレベルからハイレベルに変化し、時刻t2において、データ線DLの電位がハイレベルからローレベルに変化する。これに対応して、図3のa点(SRAMの出力点)の電圧はハイレベルからローレベルに変化し、b点(SRAMの他の出力点:メモリ回路の電圧供給端Qとして機能する)の電圧はローレベルからハイレベルに変化する。

#### 【0085】

時刻t3において、走査線WLはローレベルとなり、その後、時刻t4に再びハイレベルに変化し、時刻t5において、データ線(/DL)の電位がハイレベルからローレベルに変化する。これに対応して、図3のa点(SRAMの出力点)の電圧はローレベルからハイレベルに変化し、b点(SRAMの他の出力点:メモリ回路の電圧供給端Qとして機能する)の電圧はハイレベルからローレベルに変化する。

#### 【0086】

次に、印加電圧反転回路20の動作について説明する。図5(B)に示すように、相補クロック(CK, /CK)の電圧レベルは周期的に電圧レベルが反転する。クロックCKがハイレベルの期間(t11~t12, t13~t14, t16~t17, t18~t19, t21~t22)においては、図4(B)に太線で示される経路で液晶素子30に電圧が印加される。このとき、c点の電位は、b点(すなわち、メモリ回路10の電圧供給端Q)の電位となり、d点の電位は基準電源電位(接地電位:GND)となる。

#### 【0087】

一方、クロック(/CK)がハイレベルの期間(t12~t13, t14~t16, t17~t18, t19~t21)においては、図4(C)に太線で示される経路で液晶素子30に電圧が印加される。このとき、d点の電位は、b点(すなわち、メモリ回路10の電圧供給端Q)の電位となり、c点の電位は基準電源電位(接地電位:GND)となる。

#### 【0088】

そして、b点(すなわち、メモリ回路10の電圧供給端Q)の電位は、図5(B)に示されるように、時刻t15においてハイレベルからローレベルに変化し、時刻t20においてローレベルからハイレベルに変化する。

#### 【0089】

このように、c点およびd点の電位は、相補クロック(CK, /CK)の電圧レベルと、そのときのb点の電圧レベルによって決定され、したがって、図5(B)に示されるおりの変化を示す。

#### 【0090】

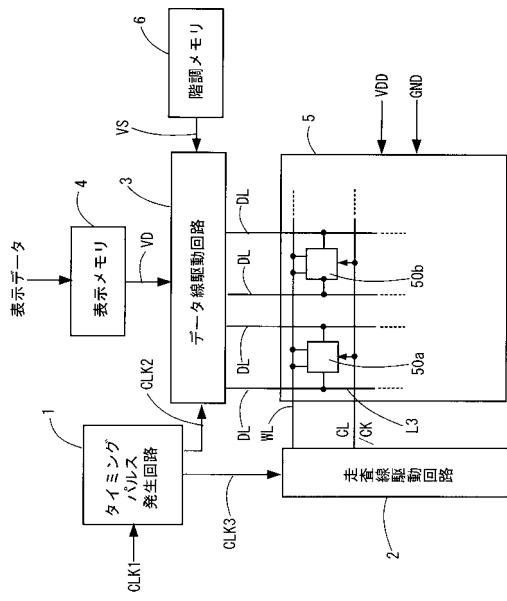

##### (液晶装置の全体構成)

図6は、本発明の液晶装置の全体構成の一例を示すブロック図である。図6の液晶装置では、デジタル階調駆動方式として、等間隔サブフィールド駆動(1フィールド期間を等間隔のサブフィールドに分割し、各サブフィールドにおける液晶素子20のオン/オフを制御する方式)が採用される(但し、これに限定されるものではない)。

#### 【0091】

図6の液晶装置は、PWMを用いた駆動によって256階調の階調表示を行うもので、画素数が $1024 \times 768$ 、1度にデータを送ることができる1ライン当たりの画素数が128であり、等間隔サブフィールドによって表示パネルが駆動される。

#### 【0092】

図示されるように、液晶装置は、タイミングパルス発生回路1と、走査線駆動回路2と、データ線駆動回路3と、表示メモリ4と、複数の画素回路(50a, 50b, ...)が含まれる画像表示領域5と、階調メモリ6と、を有している。

10

20

30

40

50

## 【0093】

タイミングパルス発生回路1は、基本クロックパルスCLK1に基づいて水平同期信号、垂直同期信号、サブフィールドタイミングパルス、走査線駆動パルス等のタイミングパルス(CLK2, CLK3)を生成し、走査線駆動回路2およびデータ線駆動回路3へ出力する。

## 【0094】

走査線駆動回路2は、上述した走査線駆動パルスのタイミングにおいて各走査線(WL)に順次”H(ハイ)”レベルの信号を出力する。また、この走査線駆動回路2は、各画素回路(50a, 50b, ..., 50z)に含まれる印加電圧反転回路20に供給するための相補クロック信号(CK, /CK)も出力する。

10

## 【0095】

表示メモリ4は、外部から供給される表示データが一時記憶されるメモリであり、画像表示領域5の画素数と同数の記憶スロットを有し、1フィールド分の表示データが一時記憶される。表示データは、例えば、表示輝度の階調を示す8ビットの階調データであり、「0」～「255」の値をとる。例えば、「0」は黒色を表し、「255」は白色を表す。表示メモリ4から読み出された表示データVDは、データ線駆動回路3に供給される。

## 【0096】

また、階調メモリ6は、表示データに対応するサブフィールド番号が予め記憶されたメモリであり、各表示データに対応したサブフィールド番号が記憶されている。階調メモリ6から読み出されるデータVSは、データ線駆動回路3に供給される。

20

## 【0097】

データ線駆動回路3は、走査線毎に表示メモリ4から表示データVDを読み出し、読み出した表示データVDを上述した階調メモリ6の内容によってサブフィールド番号に変換する。そして、走査線駆動パルス、サブフィールドタイミングパルスおよび上述したサブフィールド番号に基づいて各画素を駆動する。

## 【0098】

各画素回路(50a, 50b, ..., 50z)に含まれる印加電圧反転回路20に供給される相補クロック信号(CK, /CK)は、タイミングパルス生成回路1から出力される各種のタイミングパルス(CLK2, CLK3)に基づいて、すなわち、それらのタイミングパルス(CLK2, CLK3)をそのまま援用して、あるいは、そのタイミングパルスを周波あるいは遅倍することによって、簡単に生成することができる。よって、図6の液晶装置では、制御信号(CK, /CK)を生成するための特別な回路(専用の回路)が不要であり、したがって、回路構成(システム構成)を簡素化することができる。

30

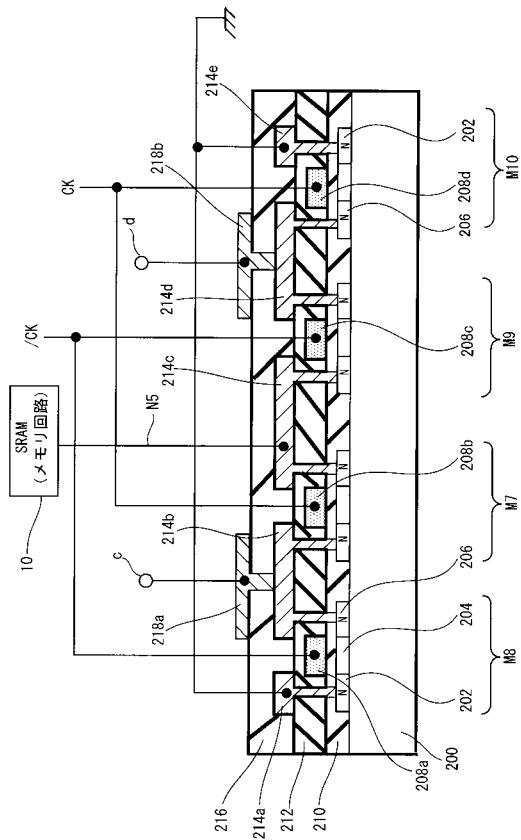

## 【0099】

## (横電界方式の液晶素子のデバイス構造)

図7は、本発明のアクティブマトリクス基板の要部の断面構造を示す図である。図7では、主として、アレイ基板200上に集積された印加電圧反転回路20を構成する4つのトランジスタ(M8～M10)の断面構造を記載している。但し、メモリ回路(SRAM)10も同様にアレイ基板200上に形成される。なお、図7では、遮光膜や配向膜は省略されている。

40

## 【0100】

図7に示されるように、アレイ基板200上に、パターニングされた多結晶シリコン層204が形成され、その多結晶シリコン層204に選択的に不純物を導入することによって、ソース/ドレイン(202, 206)が形成されている。多結晶シリコン層204を埋め込むようにゲート絶縁膜210が形成され、そのゲート絶縁膜210上に、多結晶シリコンからなるゲート電極(208a～208d)が形成されている。

## 【0101】

ゲート電極(208b, 208d)には、クロック(CK)が供給され、ゲート電極(208a, 208c)には、クロック(CK)とは逆相のクロック(/CK)が供給される。

50

**【0102】**

ゲート電極（208a～208d）上には第1の層間絶縁膜（212）が形成され、この第1の層間絶縁膜（212）には選択的にコンタクトホールが形成される。光を反射する導電性材料（アルミニウム等の金属材料）からなる電極（214a～214e）は、コンタクトホールを介してソース／ドレイン（202，206）に接続される。

**【0103】**

電極（214a，214e）には基準電源電位（基準電源電位）としての接地電位（GND）が与えられる。また、電極214cにはメモリ回路（SRAM）10が接続される。メモリ回路（SRAM）10からは、配線N5を経由して、2値電圧（第1および第2の電圧：VDDとGND）が供給される。

10

**【0104】**

電極（214a～214e）上には第2の層間絶縁膜216が形成され、この第2の層間絶縁膜216には選択的にコンタクトホールが設けられる。第1および第2の画素電極（218a，218b）は各々、そのコンタクトホールを経由して下側に位置する電極（214b，214d）に接続される。この第1および第2の画素電極（218a，218b）は、図3のc点、d点に相当し、この第1および第2の電極（218a，218b）によって、液晶素子30に電圧が印加される。

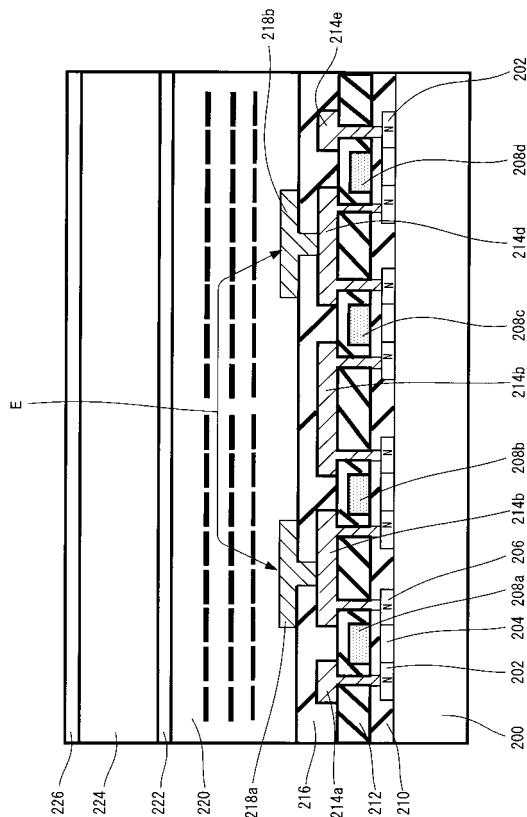

**【0105】**

図8は、図7に示されるアクティブマトリクス基板を用いた液晶装置（横電界方式の液晶装置）の断面構造を示す断面図である。図示されるように、図7のアクティブマトリクス基板と対向基板224によって液晶層220が挟持される。参照符号222は、カラーフィルタ層であり、参照符号226は偏光板である。

20

**【0106】**

液晶層220には、図中の矢印のように、基板面に水平に電界Eが印加され、液晶分子は、基板面と平行な状態を保ったまま回転し、これによって、液晶層220の光透過率が変化する。図8に示される横電界方式の液晶装置（IPS液晶装置）は、2つの画素電極（218a，218b）がアレイ基板200側に近接して設けられ、したがって電極の引き出しが容易であり、また、共通電極（LCcom）を使用しないために負荷容量が小さく（1画素相当の液晶容量のみが負荷となる）、画素電極（218a，218b）の双方の電圧は速やかに変化する。したがって、焼き付き防止のための、液晶の印加電圧の反転動作を高速に行うことができ、このことがフリッカの低減に寄与する。

30

**【0107】****（第2の実施形態）**

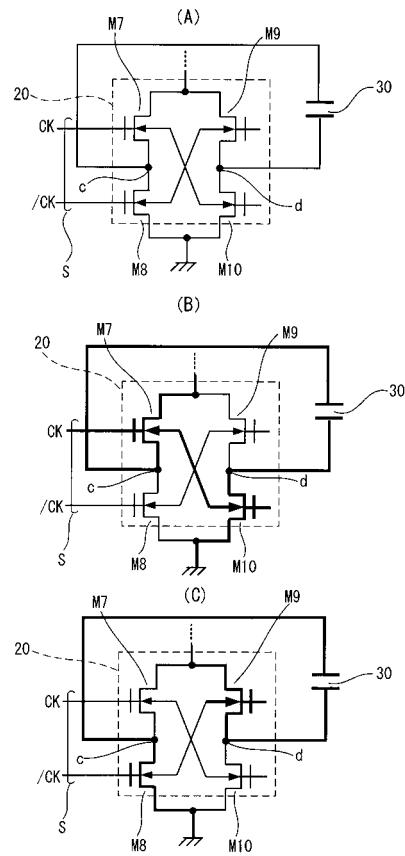

本実施形態では、印加電圧反転回路20における貫通電流（Ipeak）を抑制する回路構成について説明する。

**【0108】**

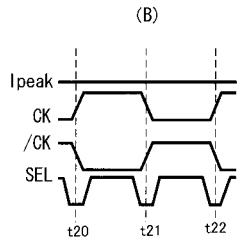

図9は、貫通電流（Ipeak）を抑制する手段をもつ印加電圧反転回路の回路構成と動作を説明するための図であり、（A）は回路構成を示す回路図であり、（B）は（A）の回路の動作を示すタイミング図であり、（C）は貫通電流を抑制する手段を持たない比較例の回路における動作を示すタイミング図である。図9において、前掲の図と共通する部分には同じ参照符号を付してある。

40

**【0109】**

図3に示される印加電圧反転回路20は、メモリ回路20の電圧供給端（Q）と基準電源電位との間に、2つのMOSトランジスタ（M7とM8，M9とM10）が直列接続された構成をもち、各MOSトランジスタは相補的にオン／オフする。各MOSトランジスタのオン／オフが切り換わる途中には各トランジスタが同時オンする状態が生じ、このときに貫通電流が流れるのは否めない。この貫通電流は、基準電源電位（GND）を揺らし、このことが回路動作に悪影響を与える可能性がないとは言えない。

**【0110】**

すなわち、図9（C）のように、相補クロック（CK，/CK）の電圧レベルが変化す

50

るタイミング（時刻  $t_{20}$ ,  $t_{21}$ ,  $t_{22}$ ）において、2つのMOSトランジスタ（M7とM8, M9とM10）が同時オン状態となり、貫通電流（Ipeak）が生じる。

#### 【0111】

そこで、図9（A）の回路では、メモリ回路10と、直列接続されたMOSトランジスタ（M7とM8, M9とM10）との間に貫通電流防止トランジスタ（スイッチ素子：MA）を設け、この貫通電流防止トランジスタ（MA）のオン／オフを、タイミング信号（SEL）によって制御するようにした。図9の回路では、貫通電流防止トランジスタ（MA）はNMOSトランジスタである。

#### 【0112】

貫通電流防止トランジスタ（MA）を、貫通電流が生じ得るタイミング（つまり、相補クロックCK, /CKの電圧レベルが変化するタイミング）にてオフさせることによって、メモリ回路10からの電圧（電流）の供給が停止し、したがって、貫通電流（Ipeak）が流れることが確実に防止される。

#### 【0113】

すなわち、図9（B）に示すように、貫通電流防止トランジスタ（MA）をオフするためのタイミング信号（SEL）は、相補クロック（CK, /CK）の電圧レベルが変化するタイミング（時刻  $t_{21}$ ,  $t_{22}$ ,  $t_{23}$ ）においてローレベルとなる。したがって、貫通電流防止トランジスタ（MA）はオフし、メモリ回路10から4つのトランジスタ（M7～M10）への電圧（電流）供給が遮断される。よって、貫通電流（Ipeak）が流れることが確実に防止される。

#### 【0114】

##### （第3の実施形態）

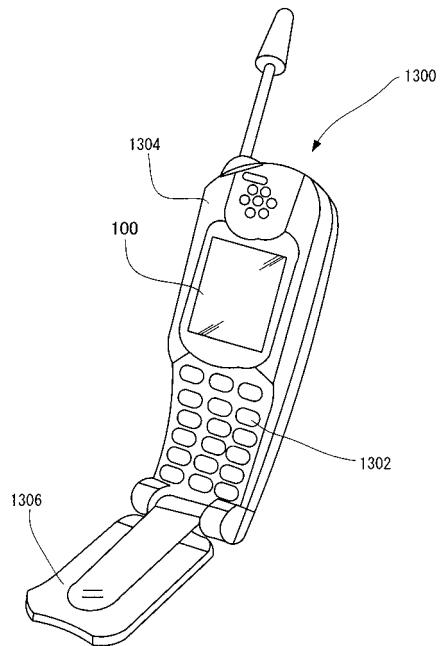

次に、本発明の液晶装置（横電界方式の液晶を用いた、SRAM付きの反射型液晶装置）を搭載した電子機器について説明する。

#### 【0115】

##### （サブパネルを備える携帯端末）

図10は、サブパネルを備える携帯端末（携帯電話端末、PDA端末、持ち運び可能なパソコン用コンピュータを含む）の斜視図である。図10の携帯端末1300は携帯電話端末であり、図示されるように、上部筐体1304と、この上部筐体1304の内面に設けられたサブパネル100と、下部筐体1306と、操作キー1302と、を備える。なお、下部筐体1306の外面にはメインパネルが設けられているが、図10ではメインパネルは図示されない。

#### 【0116】

サブパネル100は、本発明の液晶装置（横電界方式の液晶を用いた、SRAM付きの反射型液晶装置）を用いて構成される。SRAMに画像を保持できるため、例えば、サブパネル10の画像表示を一旦、終了し、メインパネル（不図示）の表示に移行し、その後、サブパネル1の表示を復活させるような場合に、保持されているデータを読み出すだけで画像の再表示が可能である。

#### 【0117】

また、横電界方式の液晶（IPS液晶）を使用するため、発色性かつ高視野角の高画質の画像表示が可能である。また、液晶に印加される電圧の理想的な反転と、電圧が印加されない時の液晶の両極の理想的なショートとによって直流オフセットが発生しないことから、表示画像の経時的な劣化も低減される。また、液晶に印加する電圧の極性反転が常に対称的に、かつ高速に行われることから、フリッカが発生せず、画質の低下が生じない、という効果も得られる。また、サブパネルとしてバックライトが不要な反射型液晶を使用するため、電池寿命を延ばすことができる。

#### 【0118】

##### （低消費電力の携帯情報端末）

図11は、本発明の液晶装置を用いた携帯情報端末（PDA, パーソナルコンピュータ, ワードプロセッサ等）の斜視図である。携帯情報端末1200は、上部筐体1206およ

10

20

30

40

50

び下部筐体 1204 と、キーボード等の入力部 1202 と、本発明の反射型液晶装置を用いた表示パネル 100 と、を有する。この携帯情報端末においても、上述の携帯端末と同様の効果が得られる。

#### 【0119】

(反射型プロジェクタ)

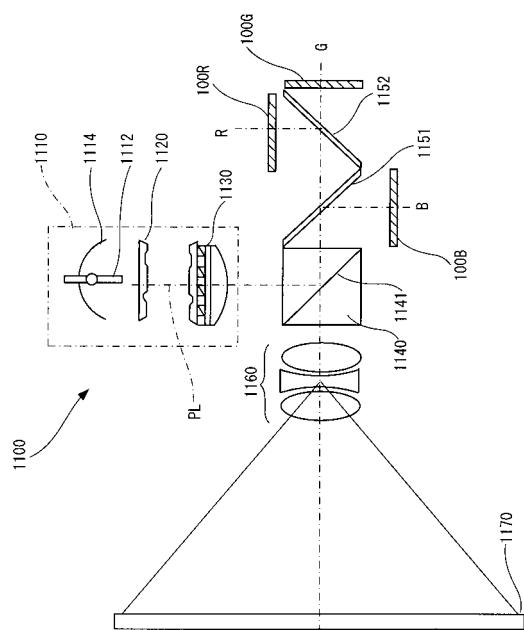

図 12 は、本発明の反射型液晶装置を光変調器として用いたプロジェクタ(投射型表示装置)の要部の概略構成を示す図である。図示されるように、プロジェクタ 1100 は、偏光照明装置 1110 と、投射光学系 1160 と、偏光ビームスプリッタ 1140(偏光光束反射面 1141 を含む)と、ダイクロイックミラー 1151, 1152 と、RGB の各色に対応した、光変調器としての本発明の反射型液晶装置(100R, 100G, 100B)と、を有する。

10

#### 【0120】

図示されるように、偏光照明装置 1110 がシステム光軸 PL に沿って配置されている。この偏光照明装置 1110 において、ランプ 1112 からの出射光は、リフレクタ 1114 による反射で略平行な光束となって、第 1 のインテグレータレンズ 1120 に入射する。これにより、ランプ 1112 からの出射光は、複数の中間光束に分割される。この分割された中間光束は、第 2 のインテグレータレンズを光入射側に有する偏光変換素子 1130 によって、偏光方向が略々揃った一種類の偏光光束(s 偏光光束)に変換されて、偏光照明装置 1110 から出射されることとなる。

20

#### 【0121】

偏光照明装置 1110 から出射された s 偏光光束は、偏光ビームスプリッタ 1140 の s 偏光光束反射面 1141 によって反射される。この反射光束のうち、青色光(B)の光束がダイクロイックミラー 1151 の青色光反射層にて反射され、反射型の液晶装置 100B によって変調される。また、ダイクロイックミラー 1151 の青色光反射層を透過した光束のうち、赤色光(R)の光束は、ダイクロイックミラー 1152 の赤色光反射層にて反射され、反射型の液晶装置 100R によって変調される。

20

#### 【0122】

一方、ダイクロイックミラー 1151 の青色光反射層を透過した光束のうち、緑色光(G)の光束は、ダイクロイックミラー 1152 の赤色光反射層を透過して、反射型の液晶装置 100G によって変調される。

30

#### 【0123】

このようにして、液晶装置 100R、100G、100B によってそれぞれ色光変調された赤色、緑色、青色の光は、ダイクロイックミラー 1152、1151、偏光ビームスプリッタ 1140 によって順次合成された後、投射光学系 1160 によって、スクリーン 1170 に投射される。この携帯情報端末においても、上述の効果が得られる。

#### 【0124】

以上、本発明を実施形態に基づいて説明したが、本発明は実施形態に限定されるものではなく、種々、変形や応用が可能である。例えば、印加電圧反転回路を構成するトランジスタ(スイッチ素子)としては、バイポーラトランジスタを使用することもできる。メモリ回路としては、SRAM 以外のメモリを使用することもできる。また、本明細書における「横電界方式の液晶」は、液晶層に加わる電界が基板面と水平である、種々の駆動方式の液晶を広く含む。

40

#### 【0125】

以上説明したように、本発明の各実施形態によれば、例えば、以下の主要な効果を得ることができる。但し、本発明の液晶装置が、以下に記載のすべての効果を同時に生じさせる必要はなく、下記の効果の列挙が、本発明の不当な限定の根拠とされることはない。

(1) 横電界方式の液晶を積極的に採用して駆動負荷を軽減し、これによって、液晶の両電極の速やかな電圧変化を可能とし、また、電圧供給と電圧反転の各機能を完全に分離した新規な画素回路構成を採用することによって、例えば、相補的なクロック(CK, /CK)によって、高速かつ高精度の印加電圧の反転を実現することができる。したがって、

50

フリッカが抑制され、高画質の画像表示が可能である。

(2) 印加電圧反転回路は、メモリ回路からの電源電圧( V D D , G N D )および印加電圧反転回路自体の基準電源電圧( G N D )の、液晶への供給経路を切り換えるだけである。したがって、液晶に印加する電圧の電圧源自体は常に共通であり、電圧の反転前と反転後の電圧値自体には何も変動がなく、したがて、正確な電圧の極性反転が実現する。また、液晶の面内ばらつきによって、各画素における電圧レベルが若干変動したとしても、その画素内では、電圧の反転前と反転後の電圧値自体には何も変動がなく、したがって、各画素において直流オフセットは発生しない。したがって、焼き付きが生じず、経時的な画像劣化が生じない。

(3) また、電圧の供給経路を切り換えるだけであるため、第1および第2の画素電極の各々に供給する電圧レベルの切り替えを、簡単な回路により同時に実現することができる。従来のように、共通 V c o m と下部電極の電圧 V p を別個の回路で制御し、各電圧を高精度に調整し、かつ、各電圧の切り換えタイミングの同期をとる必要はなくなり、制御方式が簡素化される。

(4) また、印加電圧反転回路の基準電源電圧が、例えばグランドレベルであるとき、メモリ回路から供給する電圧を 0 V とすれば、液晶の両電極に印加される電圧は、共に正確に 0 V となり、液晶への電圧印加がない場合のショート状態が実現され、この際、直流オフセットは生じない。したがって、焼き付きが生じず、経時的な画像劣化が生じない。

(5) また、印加電圧反転回路は、例えば、メモリ回路の電圧供給端と基準電源電位との間に設けられる 4 個のスイッチ素子( 第1 ~ 第4 のトランジスタ )によって構成することができ、各スイッチ素子の同期的な切換制御は、例えば、相補的なクロック( C K , / C K )を用いて簡単に実現することができる。また、印加電圧反転回路は、最小限の素子にて構成されるため、これ以上簡単化することができないコンパクトな回路が実現される。

(6) また、メモリ回路および印加電圧反転回路の高レベル側の電源電圧の値は同じでよく、よって、各回路を構成する M O S トランジスタのサイズを同じにすることができる、例えば、メモリ回路を構成するトランジスタを高耐圧トランジスタとする必要もない。

(7) また、印加電圧反転回路を駆動する相補的なクロック信号( C K , / C K )は、デジタル回路では汎用的に用いられるものであり、特に、デジタル階調駆動( P W M 駆動)におけるタイミングパルスを援用等することによって、簡単に得ることができる。したがって、御信号を生成するための特別な回路( 専用の回路 )が不要であり、したがって、回路構成( システム構成 )を簡素化することができる。

(8) また、メモリ回路からの電圧を液晶に供給する働きをする第1および第3の M O S トランジスタ( M 7 , M 9 )のゲートに、( V D D + 閾値電圧( V t h ) )以上の制御電圧を与えて十分にオンさせることによって、メモリ回路からの電圧( 5 V = V D D )はそのまま液晶に供給されることになり、電圧ドロップが生じない。

(9) 印加電圧反転回路における貫通電流を防止するためのスイッチ素子を設け、貫通電流が生じるタイミングでスイッチ素子をオフすることによって、貫通電流の発生を確実に防止することができる。

(10) また、メモリ回路の接地配線および印加電圧反転回路の接地配線が画素回路内で共通とすることによって、仮に、液晶の面内ばらつき等によって電圧レベル( 0 V )に変動が生じたとしても、双方の電位が同様に変動するため、結果的に、液晶の両電極に印加される電圧レベルの相対的な電位差は生じず、液晶に電圧を印加しないときには、高精度のショート状態が実現され、直流オフセットが生じず、焼き付きが生じる心配がない。

(11) また、反射型液晶の場合、画素電極の下部に素子形成領域を設けることができる。本発明の印加電圧反転回路は簡素化された構成となっているため、画素電極の下部の空スペースに、メモリ回路および印加電圧反転回路を配置することは、むずかしいことではない。したがって、画素回路の占有面積を大きくすることなく、本発明にかかる画素回路を形成することができる。

(12) 本発明の液晶装置は、例えば、携帯電話のサブパネル、低消費電力のノート型パソコン、ソーラーパネル、反射型プロジェクタ等の電子機器に搭載することが可能であり、

10

20

30

40

50

この場合、電圧反転に伴う静止画のフリッカが抑制されるため、高画質の画像を表示できる。また、直流オフセットの発生が低減されて焼き付きが生じにくうことから、表示画像の画質の経時的な劣化も生じにくい。

#### 【0126】

本発明は、簡単な回路構成ならびに簡単な制御によって、フリッカを抑制しつつ印加電圧の高精度の反転を実現することができ、また、液晶に電圧を印加しないときは、直流オフセットを生じさせないショート状態を実現することができるという効果を奏し、したがって、経時変化が少ない高機能な液晶装置（特に、反射型の液晶装置）として有用である。また、本発明の液晶装置は、例えば、携帯電話のサブパネル、低消費電力の携帯情報機器（パソコン用コンピュータ等）、反射型プロジェクタ等の電子機器に搭載することができ、これによって、電子機器の高機能化が達成される。10

#### 【図面の簡単な説明】

#### 【0127】

【図1】本発明の液晶装置における1画素の構成を示す図である。

【図2】(A)～(C)は、図1に示されるメモリ回路（メモリセル）10の回路構成例を示す図である。

【図3】画素回路50の具体的な回路構成の一例を示す回路図である。

【図4】(A)～(C)は、印加電圧反転回路による、液晶に印加する電圧の極性反転動作を説明するための図である。

【図5】図3の画素回路の動作タイミングを示すタイミング図であり、(A)はメモリ回路の動作を示すタイミング図であり、(B)は、印加電圧反転回路の動作を示すタイミング図である。20

【図6】本発明の液晶装置の全体構成の一例を示すプロック図である。

【図7】本発明のアクティブマトリクス基板の要部の断面構造を示す図である。

【図8】図7に示されるアクティブマトリクス基板を用いた液晶装置（横電界方式の液晶装置）の断面構造を示す断面図である。

【図9】貫通電流（Peak）を抑制する手段をもつ印加電圧反転回路の回路構成と動作を説明するための図であり、(A)は回路構成を示す回路図であり、(B)は(A)の回路の動作を示すタイミング図であり、(C)は貫通電流を抑制する手段を持たない比較例の回路における動作を示すタイミング図である。30

【図10】サブパネルを備える携帯端末（携帯電話端末、PDA端末、持ち運び可能なパソコン用コンピュータを含む）の斜視図である。

【図11】本発明の液晶装置を用いた携帯情報端末（PDA、パソコン用コンピュータ、ワードプロセッサ等）の斜視図である。

【図12】本発明の反射型液晶装置を光変調器として用いたプロジェクタ（投射型表示装置）の要部の概略構成を示す図である。

【図13】液晶装置における焼き付き防止のために必要な動作を示す図であり、(A)は液晶に電圧を印加する場合の動作を示す図であり、(B)は液晶に電圧を印加しない場合の動作を示す図である。図13では、液晶層に基板面に垂直に電界が印加されるタイプの液晶（例えば、TN液晶）が用いられる。40

【図14】(A)～(C)は、各画素回路にメモリ回路を備える液晶装置における、液晶の両極の電圧を反転させる際の問題点を説明するための図である。

【図15】(A)，(B)は、各画素回路にメモリ回路を備える液晶装置における、液晶の両極をショート状態（同電位状態）とする場合の問題点を説明するための図である。

#### 【符号の説明】

#### 【0128】

1 タイミングパルス発生回路、2 走査線駆動回路、3 データ線駆動回路、

4 表示メモリ、5 複数の画素回路を含む画像表示領域、6 階調メモリ、

10 メモリ回路（2値電圧の電圧供給源、例えばSRAM）、

20 印加電圧反転回路（経路切換部）、

10

20

30

40

50

30 横電界方式の液晶素子(IPS液晶素子)、50 画素回路、

VDD 高レベル電源電位(高レベル電源電圧)、

GND 基準電源電位(基準電源電圧)、WL 走査線、DL, /DL データ線、

M1, M2 トランジスターゲート、

M3 ~ M6 フリップフロップを構成するトランジスタ

M7 ~ M10 印加電圧反転回路を構成するトランジスタ

Q メモリ回路の電圧供給端、

L2a, L2b, L2c 共通の基準電源電位(GND)配線

CK, /CK 印加電圧反転のための相補クロック

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図 1 5】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 4 1 A |

| G 0 9 G | 3/20 | 6 1 2 J |

(56)参考文献 特開2002-175051(JP,A)

特開2004-191574(JP,A)

特開2005-258416(JP,A)

特開平09-189897(JP,A)

特開2004-021163(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |