(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6126212号

(P6126212)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

(51) Int.Cl.

H01L 21/822 (2006.01)

H01L 27/04 (2006.01)

H01L 27/06 (2006.01)

F 1

H01L 27/04

H01L 27/06H

311C

請求項の数 20 (全 17 頁)

(21) 出願番号 特願2015-515170 (P2015-515170)

(86) (22) 出願日 平成25年5月30日 (2013.5.30)

(65) 公表番号 特表2015-524169 (P2015-524169A)

(43) 公表日 平成27年8月20日 (2015.8.20)

(86) 國際出願番号 PCT/US2013/043244

(87) 國際公開番号 WO2013/181328

(87) 國際公開日 平成25年12月5日 (2013.12.5)

審査請求日 平成28年4月19日 (2016.4.19)

(31) 優先権主張番号 61/653,225

(32) 優先日 平成24年5月30日 (2012.5.30)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/901,772

(32) 優先日 平成25年5月24日 (2013.5.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】集積回路における双方向E S D保護のための装置及び方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板と静電気放電(E S D)保護回路とを含む集積回路であって、

前記E S D保護回路が、

第1の端子と、

第2の端子と、

前記第1の端子と前記第2の端子との間に並列に結合される複数のスイッチレッグと、

を含み、

前記複数のスイッチレッグが第1のスイッチレッグと第2のスイッチレッグとを含み、

前記第1のスイッチレッグが、

第1の電流供給ノードとしてのアノードと第1の電流収集ノードとしてのカソードとを

有するシリコン制御整流器(S C R)を含む第1の電流スイッチであって、前記第1の電

流供給ノードが前記第1の端子に電気的に結合される、前記第1の電流スイッチと、

第2の電流供給ノードと第2の電流収集ノードとを含む第2の電流スイッチであって、

前記第2の電流供給ノードが前記第2の端子に電気的に結合され、前記第2の電流収集ノ

ドが前記第1のスイッチレッグの前記第1の電流収集ノードに結合され、前記第2の電

流収集ノードが、前記第2のスイッチレッグ内の第3及び第4の電流収集ノードからの電

気的結合がない、前記第2の電流スイッチと、

を含む、集積回路。

## 【請求項2】

10

20

請求項 1 に記載の集積回路であって、

前記第 2 の電流スイッチが、第 2 のシリコン制御整流器 (SCR) であり、前記第 2 の電流供給ノードが、前記第 2 の SCR のアノードであり、前記第 2 の電流収集ノードが、前記第 2 の SCR のカソードである、集積回路。

【請求項 3】

請求項 1 に記載の集積回路であって、

前記第 1 及び第 2 の電流スイッチが、第 1 及び第 2 の金属酸化物半導体 (MOS) ランジスタであり、前記第 1 及び第 2 の電流供給ノードが、前記第 1 及び第 2 の MOS ランジスタのソースノードであり、前記第 1 及び第 2 の電流収集ノードが、前記第 1 及び第 2 の MOS ランジスタのドレインノードである、集積回路。

10

【請求項 4】

請求項 1 に記載の集積回路であって、

前記第 1 及び第 2 の電流スイッチが、第 1 及び第 2 のバイポーラトランジスタであり、前記第 1 及び第 2 の電流供給ノードが、前記第 1 及び第 2 のバイポーラトランジスタのエミッタノードであり、前記第 1 及び第 2 の電流収集ノードが、前記第 1 及び第 2 のバイポーラトランジスタのコレクタノードである、集積回路。

【請求項 5】

請求項 1 に記載の集積回路であって、

前記第 2 の端子が前記集積回路の接地ノードに電気的に接続される、集積回路。

【請求項 6】

20

請求項 1 に記載の集積回路であって、

前記第 2 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が 30 ボルト上回って上昇するときにトリガするように構成され、

前記第 1 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が 30 ボルト下回って下降するときにトリガするように構成される、集積回路。

【請求項 7】

請求項 1 に記載の集積回路であって、

前記第 2 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が第 1 の電圧振幅上回って上昇するときにトリガするように構成され、

前記第 1 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が第 2 の電圧振幅下回って下降するときにトリガするように構成され、前記第 2 の電圧振幅が前記第 1 の電圧振幅の 5 ボルト以内である、集積回路。

30

【請求項 8】

請求項 1 に記載の集積回路であって、

前記第 2 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が第 1 の電圧振幅上回って上昇するときにトリガするように構成され、

前記第 1 の電流スイッチが、前記第 2 の端子に対して前記第 1 の端子の電位が第 2 の電圧振幅下回って下降するときにトリガするように構成され、前記第 2 の電圧振幅が前記第 1 の電圧振幅とは少なくとも 10 ボルト異なるようになっている、集積回路。

【請求項 9】

40

請求項 1 に記載の集積回路であって、

前記第 1 の電流スイッチが、前記スイッチレッグの各々における別々のトリガ構成要素によって個別にトリガするように構成される、集積回路。

【請求項 10】

請求項 1 に記載の集積回路であって、

前記第 1 の電流スイッチが、前記第 1 の電流スイッチの各々に接続された共通のトリガ構成要素によってトリガするように構成される、集積回路。

【請求項 11】

集積回路を形成する方法であって、

半導体材料を含む基板を提供するステップと、

50

E S D 保護構成要素の複数のスイッチレッグを同時に形成するステップであって、前記複数のスイッチレッグの各スイッチレッグの第1の電流スイッチの第1の電流供給ノードとしてのシリコン制御整流器(S C R)のアノードを形成するステップと、

前記複数のスイッチレッグの各スイッチレッグの前記第1の電流スイッチの第1の電流收集ノードとしての前記S C Rのカソードを形成するステップと、

前記複数のスイッチレッグの各スイッチレッグの第2の電流スイッチの第2の電流供給ノードを形成するステップと、

前記複数のスイッチレッグの各スイッチレッグの前記第2の電流スイッチの第2の電流收集ノードを形成するステップと、

を含む、前記E S D 保護構成要素の複数のスイッチレッグを同時に形成するステップと

、前記第1の電流供給ノードを前記E S D 保護構成要素の第1の端子に電気的に結合する第1の相互接続を形成するステップと、

前記第2の電流供給ノードを前記E S D 保護構成要素の第2の端子に電気的に結合する第2の相互接続を形成するステップと、

前記第2の電流收集ノードの各々が前記第2の電流收集ノードの他からの電気的結合がなく、前記第1の電流收集ノードの各々が前記第1の電流收集ノードの他からの電気的結合がないように、各々が、前記第1の電流收集ノードを対応するスイッチレッグの対応する第2の電流收集ノードに結合する、複数の電流收集相互接続を形成するステップと、

を含む、方法。

10

【請求項12】

入出力(I/O)端子と、

接地端子と、

前記I/O端子と前記接地端子との間に結合される双方向静電気放電(E S D)デバイスと、

を含む集積回路であって、

前記双方向E S Dデバイスが、

前記I/O端子に結合される第1の電流スイッチであって、前記I/O端子に結合される第1のソースノードと、電流收集ノードに結合される第1のドレインノードとを有する第1のN M O Sデバイスを含む、前記第1の電流スイッチと、

30

前記第1の電流スイッチと前記I/O端子とに結合される第1のトリガであって、前記第1のN M O Sデバイスの第1のゲートノードと前記I/O端子との間に結合される第1のツエナーダイオードと、前記第1のN M O Sデバイスの前記第1のゲートノードと前記接地端子との間に結合される第1のバイアスダイオードとを含む、前記第1のトリガと、

前記接地端子と前記第1の電流スイッチとに結合される第2の電流スイッチであって、前記接地端子に結合される第2のソースノードと、前記電流收集ノードに結合される第2のドレインノードとを有する第2のN M O Sデバイスを含む、前記第2の電流スイッチと、

、前記第2の電流スイッチと前記接地端子とに結合される第2のトリガと、

を含む、集積回路。

40

【請求項13】

請求項12に記載の集積回路であって、

前記第1のトリガが、前記I/O端子と前記接地端子との間の電位差が所定の閾値より下に降下するときにのみ前記電流收集ノードから前記I/O端子へ電流を運ぶために、前記第1の電流スイッチをトリガする、集積回路。

【請求項14】

請求項12に記載の集積回路であって、

前記第2のトリガが、前記I/O端子と前記接地端子との間の電位差が所定の閾値を超えて上昇するときにのみ前記電流收集ノードから前記接地端子に電流を運ぶために、前記第2の電流スイッチをトリガする、集積回路。

50

## 【請求項 15】

請求項 12 に記載の集積回路であって、

前記第 2 のトリガが、

前記第 2 の N M O S デバイスの第 2 のゲートノードと前記接地端子との間に結合される

第 2 のツエナーダイオードと、

前記第 2 の N M O S デバイスの前記第 2 のゲートノードと前記 I / O 端子との間に結合

される第 2 のバイアスダイオードと、

を含む、集積回路。

## 【請求項 16】

入出力 ( I / O ) 端子と、

接地端子と、

前記 I / O 端子と前記接地端子との間に結合される双方向静電気放電 ( E S D ) デバイ

スと、

を含む集積回路であって、

前記双方向 E S D デバイスが、

前記 I / O 端子に結合される第 1 の電流スイッチと、

前記第 1 の電流スイッチと前記 I / O 端子とに結合される第 1 のトリガと、

前記接地端子と前記第 1 の電流スイッチとに結合される第 2 の電流スイッチと、

前記第 2 の電流スイッチと前記接地端子とに結合される第 2 のトリガと、

を含み、

前記第 1 の電流スイッチが、前記 I / O 端子に結合される第 1 のアノードと電流収集ノードに結合される第 1 のカソードとを有する第 1 のシリコン制御整流器 ( S C R ) を含み、

前記第 1 のトリガが、前記第 1 のカソードと前記 I / O 端子との間に結合される第 1 の抵抗器を含み、

前記第 2 の電流スイッチが、前記接地端子に結合される第 2 のアノードと前記電流収集ノードに結合される第 2 のカソードとを有する第 2 の S C R を含み、

前記第 2 のトリガが、前記第 2 のカソードと前記接地端子との間に結合される第 2 の抵抗器を含む、集積回路。

## 【請求項 17】

入出力 ( I / O ) 端子と、

接地端子と、

前記 I / O 端子と前記接地端子との間に結合される双方向静電気放電 ( E S D ) デバイ

スと、

を含む集積回路であって、

前記双方向 E S D デバイスが、

前記 I / O 端子に結合される第 1 のエミッタノードと第 1 の電流収集ノードに結合され

る第 1 のコレクタノードとを有する第 1 の N P N トランジスタと、

前記第 1 の N P N トランジスタの第 1 のベースノードに結合される第 1 のアノードと前記 I / O 端子に結合される第 1 のカソードとを有する第 1 のダイオードと、

前記接端子に結合される第 2 のエミッタノードと前記第 1 の電流収集ノードに結合される第 2 のコレクタノードとを有する第 2 の N P N トランジスタと、

前記第 2 の N P N トランジスタの第 2 のベースノードに結合される第 2 のアノードと前記接端子に結合される第 2 のカソードとを有する第 2 のダイオードと、

前記 I / O 端子に結合される第 3 のエミッタノードと第 2 の電流収集ノードに結合される第 3 のコレクタノードとを有する第 3 の N P N トランジスタと、

前記第 3 の N P N トランジスタの第 3 のベースノードに結合される第 3 のアノードと前記 I / O 端子に結合される第 3 のカソードとを有する第 3 のダイオードと、

前記接端子に結合される第 4 のエミッタノードと前記第 2 の電流収集ノードに結合される第 4 のコレクタノードとを有する第 4 の N P N トランジスタと、

10

20

30

40

50

前記第4のNPNトランジスタの第4のベースノードに結合される第4のアノードと前記接地端子に結合される第4のカソードとを有する第4のダイオードと、

を含む、集積回路。

【請求項18】

入出力(I/O)端子と、

接地端子と、

前記I/O端子と前記接地端子との間に結合される双方向静電気放電(ESD)デバイスと、

を含む集積回路であって、

前記双方向ESDデバイスが、

10

前記I/O端子に結合されるソースと第1の電流収集ノードに結合されるドレインとを有する第1のNMOSトランジスタと、

前記接地端子に結合されるソースと前記第1の電流収集ノードに結合されるドレインとを有する第2のNMOSトランジスタと、

前記I/O端子に結合されるソースと第2の電流収集ノードに結合されるドレインとを有する第3のNMOSトランジスタと、

前記接地端子に結合されるソースと前記第2の電流収集ノードに結合されるドレインとを有する第4のNMOSトランジスタと、

前記I/O端子に結合されるソースと第3の電流収集ノードに結合されるドレインとを有する第5のNMOSトランジスタと、

20

前記接地端子に結合されるソースと前記第3の電流収集ノードに結合されるドレインとを有する第6のNMOSトランジスタと、

前記第1、第3及び第5のNMOSトランジスタのゲートと前記I/O端子とに結合される第1のトリガと、

前記第2、第4及び第6のNMOSトランジスタのゲートと前記接地端子とに結合される第2のトリガと、

を含み、

前記第1及び第2のNMOSトランジスタが前記I/O端子と前記接地端子との間に第1の放電パスを作り、

前記第3及び第4のNMOSトランジスタが前記第1の放電パスに並列に独立に第2の放電パスを作り、

30

前記第5及び第6のNMOSトランジスタが前記第1及び第2の放電パスに並列に独立に第3の放電パスを作る、集積回路。

【請求項19】

請求項18に記載の集積回路であって、

前記第1のトリガが、前記I/O端子と前記第1、第3及び第5のNMOSトランジスタのゲートとの間に結合される第1のツエナーダイオードと、前記接地端子と前記第1、第3及び第5のNMOSトランジスタのゲートとの間に結合される第1のバイアスダイオードとを含む、集積回路。

【請求項20】

40

請求項19に記載の集積回路であって、

前記第2のトリガが、前記接地端子と前記第2、第4及び第6のNMOSトランジスタのゲートとの間に結合される第2のツエナーダイオードと、前記I/O端子と前記第2、第4及び第6のNMOSトランジスタのゲートとの間に結合される第2のバイアスダイオードとを含む、集積回路。

【発明の詳細な説明】

【技術分野】

【0001】

本願は集積回路に関し、より具体的には静電気放電(ESD)保護を含む集積回路に関する。

50

## 【背景技術】

## 【0002】

集積回路における静電気放電（E S D）保護デバイスは、正電圧及び負電圧の両イベントから提供し得る。E S D保護デバイスにとって、E S Dイベントにおいて大電流を短絡できること、及び持続的なE S Dイベントにおいて電流密集なしに保護を提供できることも、望ましい場合がある。E S D保護デバイスの望ましいサイズを維持しながら、これらの機能を提供することは問題となり得る。

## 【発明の概要】

## 【0003】

集積回路が、複数の並列スイッチレッグ（switch leg）を有する双方向E S D保護デバイスを含む。各スイッチレッグは、背中合わせ構成で第2の電流スイッチと直列に結合された第1の電流スイッチを含む。第1の電流スイッチは、第1の極性E S Dイベントにおいて第2の電流スイッチに対して安定器機能を提供し、第2の電流スイッチは、第2の、反対の極性E S Dイベントにおいて第1の電流スイッチに対して安定器機能を提供する。第1の電流スイッチの各インスタンスの第1の電流供給ノードが、E S D保護デバイスの第1の端子に結合される。第2の電流スイッチの各インスタンスの第2の電流供給ノードが、E S D保護デバイスの第2の端子に結合される。第1の電流スイッチの各インスタンスの第1の電流収集ノードが、第2の電流スイッチの各対応インスタンスの第2の電流収集ノードに結合される。第1の電流スイッチの各インスタンスの第1の電流収集ノードには、第1の電流スイッチの他のインスタンスの第1の電流収集ノードへのいかなる電気的結合もなく、同様に、第2の電流スイッチの各インスタンスの第2の電流収集ノードには、第2の電流スイッチの他のインスタンスの第2の電流収集ノードへのいかなる電気的結合もない。

10

20

## 【図面の簡単な説明】

## 【0004】

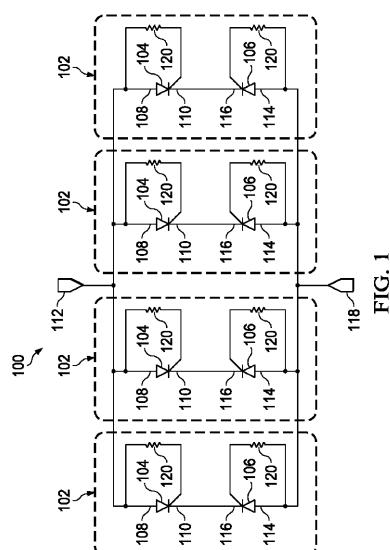

【図1】集積回路に含まれる例示の双方向静電気放電（E S D）保護デバイスの回路概略図である。

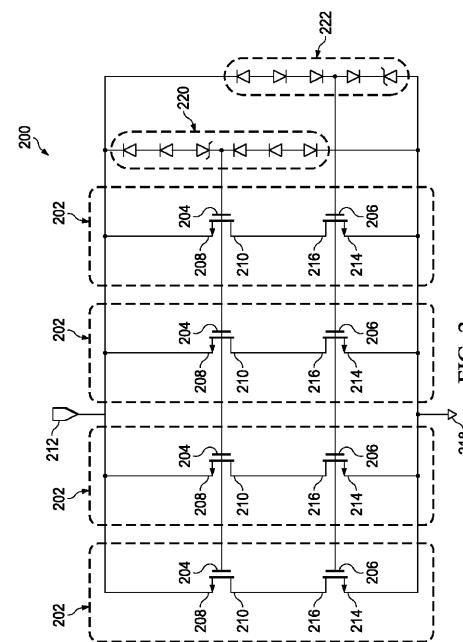

【図2】集積回路に含まれる例示の双方向静電気放電（E S D）保護デバイスの回路概略図である。

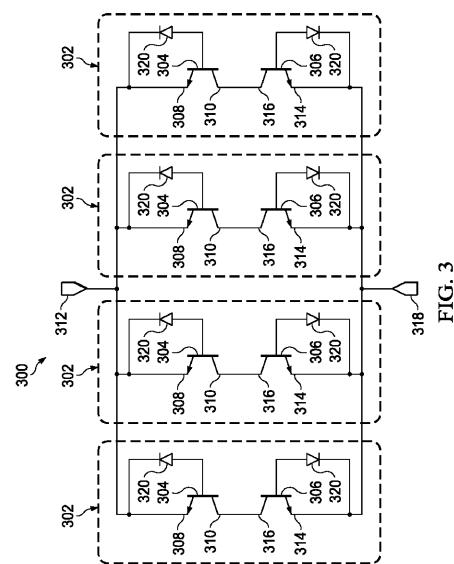

【図3】集積回路に含まれる例示の双方向静電気放電（E S D）保護デバイスの回路概略図である。

30

## 【0005】

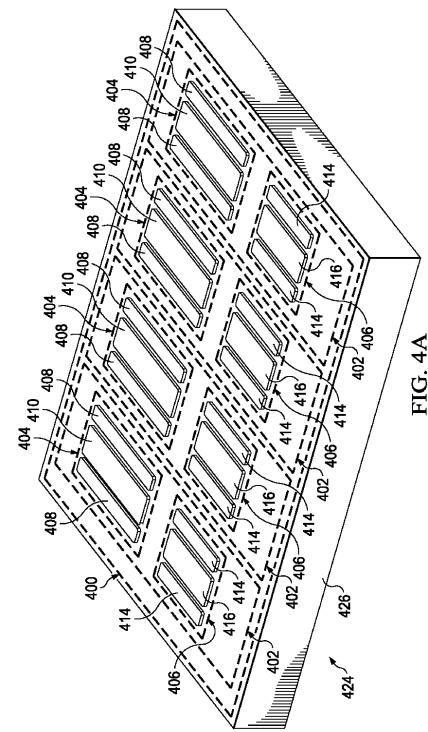

【図4 A】製造の連続段階で示される、例示の双方向E S D保護デバイスを含む集積回路の斜視図である。

【図4 B】製造の連続段階で示される、例示の双方向E S D保護デバイスを含む集積回路の斜視図である。

【図4 C】製造の連続段階で示される、例示の双方向E S D保護デバイスを含む集積回路の斜視図である。

## 【0006】

【図5】第1の電流スイッチ及び第2の電流スイッチがシリコン制御整流器（S C R）である、例示の双方向E S D保護デバイスを含む集積回路の断面図である。

40

## 【0007】

【図6】第1の電流スイッチ及び第2の電流スイッチがnチャネルドレイン拡張M O Sトランジスタである、例示の双方向E S D保護デバイスを含む集積回路の断面図である。

## 【0008】

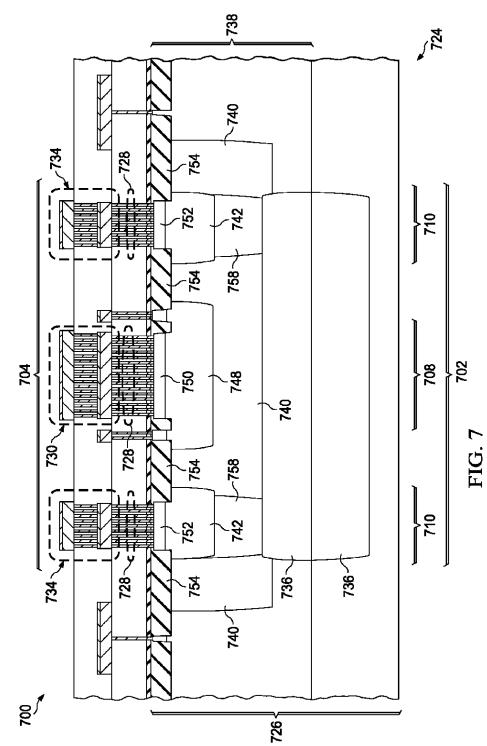

【図7】第1の電流スイッチ及び第2の電流スイッチがN P Nバイポーラトランジスタである、例示の双方向E S D保護デバイスを含む集積回路の断面図である。

## 【発明を実施するための形態】

## 【0009】

集積回路が、並列の複数のスイッチレッグを有する双方向E S D保護デバイスを含む。

50

各スイッチレッグは、背中合わせ構成で第2の電流スイッチと直列に結合された第1の電流スイッチを含む。第1の電流スイッチは、第1の極性E S Dイベントにおいて第2の電流スイッチに対して安定器機能を提供し、第2の電流スイッチは、第2の、反対の極性E S Dイベントにおいて第1の電流スイッチに対して安定器機能を提供する。第1の電流スイッチの各インスタンスの第1の電流供給ノードが、E S D保護デバイスの第1の端子に結合される。第2の電流スイッチの各インスタンスの第2の電流供給ノードが、E S D保護デバイスの第2の端子に結合される。第1の電流スイッチの各インスタンスの第1の電流収集ノードが、第2の電流スイッチの各対応インスタンスの第2の電流収集ノードに結合される。第1の電流スイッチの各インスタンスの第1の電流収集ノードには、第1の電流スイッチの他のインスタンスの第1の電流収集ノードへのいかなる電気的結合もなく、同様に、第2の電流スイッチの各インスタンスの第2の電流収集ノードには、第2の電流スイッチの他のインスタンスの第2の電流収集ノードへのいかなる電気的結合もない。

#### 【0010】

第1の電流スイッチ及び/又は第2の電流スイッチは、例えば、シリコン制御整流器(S C R)、金属酸化物半導体(M O S)トランジスタ、及び/又はバイポーラトランジスタのインスタンスであり得る。第1の電流スイッチは、各スイッチレッグにおける別々のトリガ構成要素によって個別にトリガされ得るか、又は、各第1の電流スイッチに接続された共通のトリガ構成要素によってトリガされ得る。同様に、第2の電流スイッチは、各スイッチレッグにおける別々のトリガ構成要素によって、又は共通のトリガ構成要素によってトリガされ得る。第2の電流スイッチは、第2の端子に対して第1の端子の電位が30ボルト上回って上昇するときトリガするように構成され得る。同様に、第1の電流スイッチは、第2の端子に対して第1の端子の電位が30ボルト下回って下降するときトリガするように構成され得る。第1の電流スイッチ及び第2の電流スイッチは、互いに5ボルト以内の電圧振幅でトリガするように構成され得る。「電圧振幅」という用語は電圧の絶対値を指すものと理解され、電圧振幅は常に正の数である。代わりに、第1の電流スイッチ及び第2の電流スイッチは、互いに少なくとも10ボルト差の電圧振幅でトリガするように構成され得、例えば、第1の電流スイッチは50ボルトの電圧振幅でトリガするように構成され得、第2の電流スイッチは35ボルトの電圧振幅でトリガするように構成され得る。

#### 【0011】

図1～図3は、集積回路内の例示の双方向E S D保護配置を示す。

#### 【0012】

図1は、複数の並列スイッチレッグ102を含む双方向E S D保護回路100を示す。各スイッチレッグ102は第1の電流スイッチ104を含み、これは本例ではS C R 104である。各スイッチレッグ102はさらに第2の電流スイッチ106を含み、これは本例では、背中合わせ構成で、対応する第1の電流スイッチ104と直列に結合されたS C R 106である。

#### 【0013】

各第1の電流スイッチ104は、S C R 104のアノード108である第1の電流供給ノード108と、S C R 104のカソード110である第1の電流収集ノード110とを有する。第1の電流スイッチ104の各第1の電流供給ノード108は、双方向E S D保護デバイス100の第1の端子112に結合される。

#### 【0014】

同様に、各第2の電流スイッチ106は、S C R 106のアノード114である第2の電流供給ノード114と、S C R 106のカソード116である第2の電流収集ノード116とを有する。第2の電流スイッチ106の各第2の電流供給ノード114は、双方向E S D保護デバイス100の第2の端子118に結合される。

#### 【0015】

第1の電流スイッチ104の各第1の電流収集ノード110は、同じ並列スイッチレッグ102内の第2の電流スイッチ106の対応する第2の電流収集ノード116に結合さ

10

20

30

40

50

れ、背中合わせ構成を提供する。第1の電流スイッチ104の各第1の電流収集ノード110には、第1の電流スイッチ104の他の第1の電流収集ノード110のいずれへの電気的結合もなく、第2の電流スイッチ106の各第2の電流収集ノード116には、第2の電流スイッチ106の他の第2の電流収集ノード116のいずれへの電気的結合もない。

【0016】

第1の電流スイッチ104及び第2の電流スイッチ106は、1つ又は複数のトリガ構成要素によってオンにされ得る。第1の電流スイッチ104及び第2の電流スイッチ106の各インスタンスは、図1に示されるように別々のトリガ構成要素120を有し得る。他のトリガ構成要素が本例の範囲内にある。第1の端子112は、回路100を含む集積回路の入力／出力端子に接続され得る。第2の端子118は、集積回路の接地ノードに接続され得る。

【0017】

集積回路の動作の間、配置100での正極性ESDイベントが、第2の端子118に対して正である第1の端子112における電圧過渡を提供する。第2の電流スイッチ106のうちの1つが、トリガし得、電流の導通を開始し得る。同じスイッチレッグ102内の対応する第1の電流スイッチ104は、導通している第2の電流スイッチ106に対して安定を与える。導通している第2の電流スイッチ106が電流を導通すると、導通している第2の電流スイッチ106を介する電圧降下が、第2の電流スイッチ106の導通していないインスタンスを介する電圧降下に比して減少する。第2の電流スイッチ106の第2の電流収集ノード116の各々には、第2の電流スイッチ106の他の第2の電流収集ノード116のいずれに対する電気的結合もないため、導通している第2の電流スイッチ106を介する電圧降下の減少は、導通していない第2の電流スイッチ106を介する電圧降下を減少させることはなく、導通していない第2の電流スイッチ106のインスタンスは、トリガされ得、電流の導通を独立して開始し得る。

【0018】

同様に、デバイス100での負極性ESDイベントが、第2の端子118に対して負である第1の端子112における電圧過渡を提供する。第1の電流スイッチ104のうちの1つが、トリガし得、電流の導通を開始し得る。同じスイッチレッグ102内の対応する第2の電流スイッチ106は、導通している第1の電流スイッチ104に対して安定を与える。第1の電流スイッチ104の第1の電流収集ノード110の各々には、第1の電流スイッチ104の他の第1の電流収集ノード110のいずれに対する電気的結合もないため、導通していない第1の電流スイッチ104のインスタンスが、トリガされ得、電流の導通を独立して開始し得る。

【0019】

このような動作モードは、第2の電流スイッチ106によるより均一な導通を提供し、第2の電流スイッチ106の如何なる単一インスタンスを介する電流密集をも防ぐため、有利である。したがってデバイス100は、高電流容量と持続的ESDイベントからの保護とを提供する。

【0020】

図2は、電流スイッチにMOSトランジスタを用いる、別の例示の双方向ESD保護手法を示す。保護デバイス200は、複数の並列スイッチレッグ102を含む。各スイッチレッグ102は、本例ではnチャネルMOSトランジスタ204である第1の電流スイッチ204を含む。各スイッチレッグ202は更に第2の電流スイッチ206を含み、これは、本例ではnチャネルMOSトランジスタ206であり、背中合わせ構成で、対応する第1の電流スイッチ204と直列に接続される。

【0021】

各第1の電流スイッチ204は、nチャネルMOSトランジスタ204のソースノード208である第1の電流供給ノード208と、nチャネルMOSトランジスタ204のドレインノード210である第2の電流収集ノード210とを有する。第1の電流スイッチ

10

20

30

40

50

204の各第1の電流供給ノード208は、デバイス200の第1の端子212に結合される。同様に、各第2の電流スイッチ206は、nチャネルMOSトランジスタ206のソースノード214である第2の電流供給ノード214と、nチャネルMOSトランジスタ206のドレインノード216である第2の電流収集ノード216とを有する。第2の電流スイッチ206の各第2の電流供給ノード214は、デバイス200の第2の端子218に結合され、第2の端子218は、本例ではデバイス200を含む集積回路の接地ノードである。

#### 【0022】

第1の電流スイッチ204の各第1の電流収集ノード210は、同じ並列スイッチレッグ202内の第2の電流スイッチ206の対応する第2の電流収集ノード216に結合され、背中合わせ構成を提供する。第1の電流スイッチ204の各第1の電流収集ノード210には、第1の電流スイッチ204の他の第1の電流収集ノード210のいずれに対する電気的結合もなく、第2の電流スイッチ206の各第2の電流収集ノード216には、第2の電流スイッチ206の他の第2の電流収集ノード216のいずれに対する電気的結合もない。本例において、第1の電流スイッチ204は、第1の電流スイッチ204のnチャネルMOSトランジスタ204のゲートノードのすべてのインスタンスに接続される、第1のトリガ構成要素220によってトリガされる。第1のトリガ構成要素220は、第1の電流スイッチ204のゲートノードに所望のトリガレベルを提供するために、図2に示されるように、ツエナーダイオードと1つ又は複数の順方向バイアス及び逆方向バイアスの信号ダイオードとを含み得る。同様に、本例では、第2の電流スイッチ206は、第2の電流スイッチ206のnチャネルMOSトランジスタ206のゲートノードのすべてのインスタンスに接続される、第2のトリガ構成要素222によってトリガされる。第2のトリガ構成要素222は、第1のトリガ構成要素220と同様の構造を有し得、第1のトリガ構成要素220とは異なる電圧でトリガするように構成され得る。他のトリガ構成、例えばレジスタネットワーク、が本例の範囲内にある。

#### 【0023】

集積回路の動作の間、デバイス200での正極性ESDイベントが、第2のトリガ構成要素222に、第2の電流スイッチ206のnチャネルMOSトランジスタ206のゲートノードにオン状態バイアスを印加させる。第2の電流スイッチ206のうちの1つが、最初にオンとなり、電流の導通を開始する。同じスイッチレッグ202内の対応する第1の電流スイッチ204は、導通している第2の電流スイッチ206に安定を提供する。導通している第2の電流スイッチ206が電流を導通すると、導通している第2の電流スイッチ206を介する電圧降下が、第2の電流スイッチ206の導通していないインスタンスを介する電圧降下に比して減少する。第2の電流スイッチ206の第2の電流収集ノード216の各々には、第2の電流スイッチ206の他の第2の電流収集ノード216のいずれに対する電気的結合もないため、導通している第2の電流スイッチ206を介する電圧降下の減少は、導通していない第2の電流スイッチ206を介する電圧降下を減少させることはなく、導通していない第2の電流スイッチ206のインスタンスが、オンとなり得、電流の導通を独立して開始し得る。同様に、双方向ESD保護デバイス300での負極性ESDイベントが、正極性ESDイベントと同様の利点を備えて、必要な変更を施して処理されて、高電流容量と持続的ESDイベントからの保護とを提供する。

#### 【0024】

図3は、電流スイッチのためのバイポーラトランジスタを有する、別の例の双方向ESD保護デバイス300を示す。デバイス300は複数の並列スイッチレッグ302を含む。各スイッチレッグ302は第1の電流スイッチ304を含み、これは本例ではNPNバイポーラトランジスタ304である。各スイッチレッグ302は更に第2の電流スイッチ306を含み、これは本例ではNPNバイポーラトランジスタ306であって、背中合わせ構成で、対応する第1の電流スイッチ304と直列に接続される。

#### 【0025】

各第1の電流スイッチ304は、NPNバイポーラトランジスタ304のエミッタノード

10

20

30

40

50

ド 3 0 8 である第 1 の電流供給ノード 3 0 8 と、N P N バイポーラトランジスタ 3 0 4 の収集ノード 3 1 0 である第 1 の電流収集ノード 3 1 0 とを有する。第 1 の電流スイッチ 3 0 4 の各第 1 の電流供給ノード 3 0 8 は、デバイス 3 0 0 の第 1 の端子 3 1 2 に結合される。同様に、各第 2 の電流スイッチ 3 0 6 は、N P N バイポーラトランジスタ 3 0 6 のエミッタノード 3 1 4 である第 2 の電流供給ノード 3 1 4 と、N P N バイポーラトランジスタ 3 0 6 の収集ノード 3 1 6 である第 2 の電流収集ノード 3 1 6 とを有する。第 2 の電流スイッチ 3 0 6 の各第 2 の電流供給ノード 3 1 4 は、デバイス 3 0 0 の第 2 の端子 3 1 8 に結合され、第 2 の端子 3 1 8 は、配置 3 0 0 を含む集積回路の接地ノードであり得る。

## 【 0 0 2 6 】

第 1 の電流スイッチ 3 0 4 の各第 1 の電流収集ノード 3 1 0 は、同じ並列スイッチレッグ 3 0 2 内の第 2 の電流スイッチ 3 0 6 の対応する第 2 の電流収集ノード 3 1 6 に結合され、背中合わせ構成を提供する。第 1 の電流スイッチ 3 0 4 の各第 1 の電流収集ノード 3 1 0 には、第 1 の電流スイッチ 3 0 4 の他の第 1 の電流収集ノード 3 1 0 のいずれに対する電気的結合もなく、第 2 の電流スイッチ 3 0 6 の各第 2 の電流収集ノード 3 1 6 には、第 2 の電流スイッチ 3 0 6 の他の第 2 の電流収集ノード 3 1 6 のいずれに対する電気的結合もない。第 1 の電流スイッチ 3 0 4 及び第 2 の電流スイッチ 3 0 6 は、1 つ又は複数のトリガ構成要素によってオンにされ得る。第 1 の電流スイッチ 3 0 4 及び第 2 の電流スイッチ 3 0 6 の各インスタンスは、図 3 に示されるように別々のトリガ構成要素 3 2 0 を有し得る。他のトリガ構成要素が本例の範囲内にある。

## 【 0 0 2 7 】

保護デバイス 3 0 0 での正極性 E S D イベント及び負極性 E S D イベントの間の集積回路の動作は、図 1 及び図 2 に関して説明した同じ利点を備えて、変更すべきところは変更して処理されて、高電流容量と持続的 E S D イベントからの保護とを提供する。

## 【 0 0 2 8 】

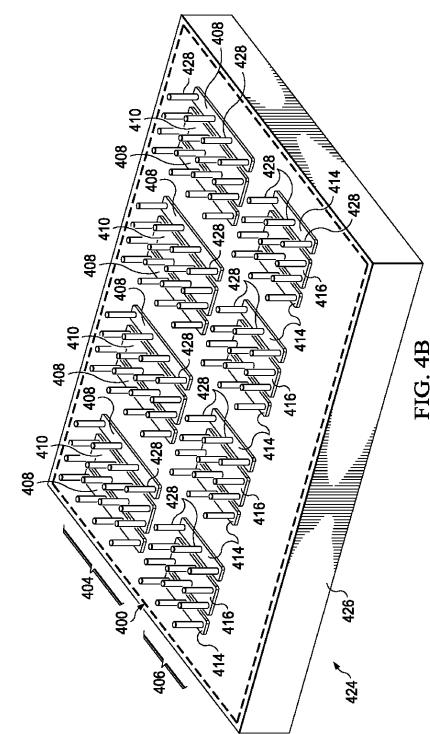

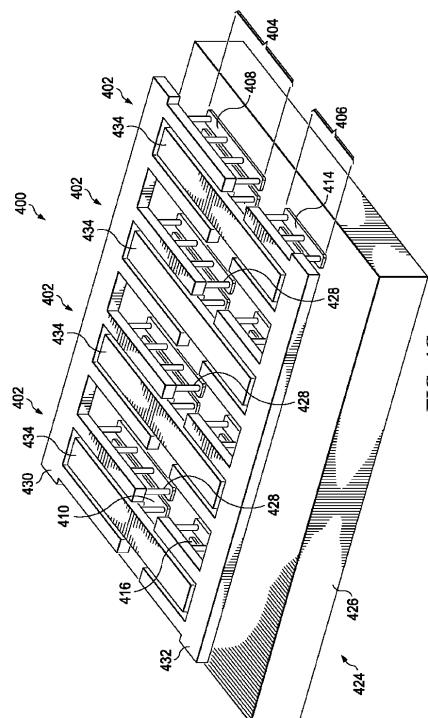

図 4 A ~ 図 4 C は、例示の双方向 E S D 保護回路を含む集積回路を製造する際のステップを示す。図 4 A は、半導体材料を含む基板 4 2 6 上に形成された集積回路 4 2 4 を示す。集積回路と共に組み込まれる双方向 E S D 保護デバイス 4 0 0 が、複数の並列スイッチレッグ 4 0 2 を含む。各スイッチレッグ 4 0 2 は、第 1 の電流スイッチ 4 0 4 及び第 2 の電流スイッチ 4 0 6 を含む。

## 【 0 0 2 9 】

各第 1 の電流スイッチ 4 0 4 は、第 1 の電流供給ノード 4 0 8 及び第 1 の電流収集ノード 4 1 0 を有する。同様に、各第 2 の電流スイッチ 4 0 6 は、第 2 の電流供給ノード 4 1 4 及び第 2 の電流収集ノード 4 1 6 を有する。

## 【 0 0 3 0 】

図 4 B は、集積回路 4 2 4 上に形成されたコンタクト 4 2 8 を示す。コンタクト 4 2 8 は、第 1 の電流スイッチ 4 0 4 の第 1 の電流供給ノード 4 0 8 及び第 1 の電流収集ノード 4 1 0 との電気的接続、並びに、第 2 の電流スイッチ 4 0 6 の第 2 の電流供給ノード 4 1 4 及び第 2 の電流収集ノード 4 1 6 との電気的接続を成す。

## 【 0 0 3 1 】

コンタクト 4 2 8 は、二酸化ケイ素及び窒化ケイ素のプレメタル誘電体 ( P M D ) ( premetal dielectric ) 層などの、誘電体層を介して形成され得る。コンタクト 4 2 8 は、反応性イオンエッチ ( R I E ) プロセスを用いて P M D 層を介してコンタクトホールをエッチングすること、それぞれ、スパッタプロセス及び原子層堆積 ( A L D ) プロセスを用いてチタン及び窒化チタンのライナを形成すること、コンタクトホールを充填するように化学気相蒸着 ( C V D ) プロセスを用いてライナ上にタングステン層を形成すること、並びに、エッチバック又は化学機械研磨 ( C M P ) プロセスを用いて P M D 層の頂部表面からタングステン及びライナを除去することによって形成され得る。

## 【 0 0 3 2 】

図 4 C は、コンタクト 4 2 8 上に形成された金属相互接続を示す。金属相互接続のうちの第 1 の相互接続 4 3 0 が、コンタクト 4 2 8 を介して第 1 の電流スイッチ 4 0 4 の第 1

10

20

30

40

50

の電流供給ノード 408 への電気的接続を成す。第 1 の相互接続 430 は、E S D 保護デバイス 400 の第 1 の端子に電気的に結合される。

【 0033 】

金属相互接続のうちの第 2 の相互接続 432 が、コンタクト 428 を介して第 2 の電流スイッチ 406 の第 2 の電流供給ノード 414 への電気的接続を成す。第 2 の相互接続 432 は、デバイス 400 の第 2 の端子に電気的に結合される。

【 0034 】

金属相互接続の複数の電流収集相互接続 434 が、第 1 の電流スイッチ 404 の第 1 の電流収集ノード 410 への及び第 2 の電流スイッチ 406 の第 2 の電流収集ノード 416 への電気的接続を成し、そのため、各スイッチレッグ 402 内の第 1 の電流スイッチ 404 の第 1 の電流収集ノード 410 は、同じスイッチレッグ 402 内の第 2 の電流スイッチ 406 の第 2 の電流収集ノード 416 に電気的に結合される。各電流収集相互接続 434 には、異なるスイッチレッグ 402 内の電流収集相互接続 434 のインスタンスへの電気的接続はない。

10

【 0035 】

金属相互接続は、アルミニウムメタライゼーションプロセスを用いて、コンタクト及び P M D 層上に、例えばチタニウムタンゲステン又は窒化チタンなどの、接着性金属の層を形成すること、接着性金属の層上に、例えば数パーセントのチタン、銅、及び / 又はケイ素を伴うアルミニウムなどの、スパッタされたアルミニウムの層を形成すること、並びに、スパッタされたアルミニウムの層上に、窒化チタンなどの反射防止金属の層を形成することによって形成され得る。金属相互接続のための領域を覆うように、反射防止金属の層の上にエッチマスクが形成される。エッチマスクは、フォトリソグラフィプロセスによって形成されるフォトレジストを含み得るか、又は無機ハードマスク材料を含み得る。R I E プロセスが、エッチマスクによって露出される反射防止金属の層、スパッタされたアルミニウムの層、及び接着性金属の層を除去し、金属相互接続が残る。

20

【 0036 】

代わりに、金属相互接続は、銅ダマシンメタライゼーションプロセスを用いて、コンタクト 428 及び P M D 層の上に層間誘電体 ( I L D ) 層を形成することによって形成されてもよい。金属相互接続のために画定された領域において、I L D 層内にトレンチが通常 50 ~ 150 ナノメートル深さでエッチングされる。通常は、物理気相蒸着、原子層堆積、又は化学気相蒸着によって、トレンチの底部及び側部上に窒化タンタルなどのライナ金属の層が形成される。通常はスパッタリングによって、ライナ金属上に銅のシード層が形成される。その後、通常は電気めっきによって、トレンチが銅で充填される。銅及びライナ金属は、C M P 及びエッチプロセスによって I L D 層の頂部表面から除去され、金属相互接続が残る。

30

【 0037 】

双方向 E S D 保護デバイス 400 の抵抗を低減するために、第 1 の電流スイッチ 404 の各第 1 の電流収集ノード 410 に、第 1 の電流スイッチ 404 の他の第 1 の電流収集ノード 410 のいずれに対する電気的結合もなく、第 2 の電流スイッチ 406 の各第 2 の電流収集ノード 416 に、第 2 の電流スイッチ 406 の他の第 2 の電流収集ノード 416 のいずれに対する電気的結合もないように、金属相互接続の付加的なレベルが、第 1 の相互接続 430 、第 2 の相互接続 432 、及び / 又は電流収集相互接続 434 の上に形成され得る。

40

【 0038 】

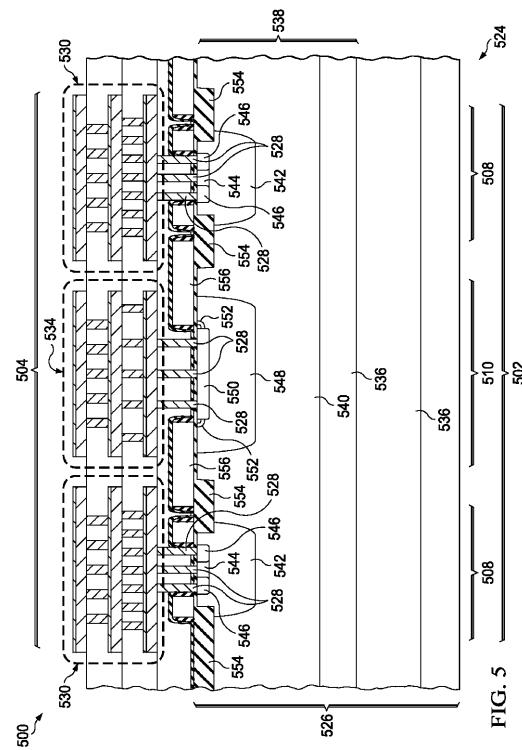

図 5 は、第 1 の電流スイッチ及び第 2 の電流スイッチが S C R である、例示の双方向 E S D 保護デバイスを含む集積回路を示す。集積回路 524 は、半導体材料を含む基板 526 上に形成される。図 5 は、スイッチレッグ 502 内の、S C R 504 である第 1 の電流スイッチ 504 を介した、デバイス 500 の断面を示す。スイッチレッグ 502 の第 2 の電流スイッチが、同様のプロセスシーケンスによって形成され得る。

【 0039 】

50

例えば基板 526 の既存の頂部領域に n 型ドーパントを注入することによって、基板 526 内に n 型埋め込み層 536 が形成され、その後、埋め込み層 536 の上に半導体材料のエピタキシャル層 538 を形成する、熱駆動及びエピタキシャル成長プロセスが続く。埋め込み層 536 はエピタキシャル層 538 内まで延在する。基板 526 は埋め込み層 536 及びエピタキシャル層を含む。例えば n 型ドーパントをイオン注入し、それに続いて熱駆動オペレーションを実行することによって、埋め込み層 536 の上の基板内に深い n 型ウェルが形成される。

【 0040 】

S C R 504 のアノード 508 である、第 1 の電流スイッチ 504 の第 1 の電流供給ノード 508 が、深い n 型ウェル 540 内に形成される浅い n 型ウェル 542 と、浅い n 型ウェル 542 内に形成される n 型ボディコンタクト領域 544 と、n 型ボディコンタクト領域 544 近傍の浅い n 型ウェル 542 内に形成される p 型アノードコンタクト領域 546 とを含む。 10

【 0041 】

S C R 504 のカソード 510 である、第 1 の電流スイッチ 504 の第 1 の電流収集ノード 510 が、深い n 型ウェル 540 内に形成される浅い p 型ウェル 548 と、浅い p 型ウェル 548 内に形成される n 型カソードコンタクト領域 550 と、n 型カソードコンタクト領域 550 に近接する浅い p 型ウェル 548 内に形成される p 型ボディコンタクト領域 552 とを含む。 20

【 0042 】

アノード 508 からカソード 510 への漏れ経路を抑制するために、基板 526 の頂部表面にフィールド酸化物 554 が形成され得る。深い n 型ウェル 540 及び浅い p 型ウェル 548 に重なって基板 526 の上にゲート 556 が形成される。ゲート 556 は S C R 504 をトリガするためにバイアスされ得る。 20

【 0043 】

基板 526 の上にコンタクト 528 及び金属相互接続が形成される。金属相互接続のうちの第 1 の相互接続 530 が、コンタクト 528 を介して S C R 504 のアノード 508 への電気的接触を成す。第 1 の相互接続 530 は、双方向 E S D 保護デバイス 500 の第 1 の端子に電気的に結合される。金属相互接続の電流収集相互接続 534 が、S C R 504 のカソード 510 への及び同じスイッチレッグ 502 内の第 2 の電流スイッチの第 2 の電流収集ノードへの電気的接続を成す。電流収集相互接続 534 には、異なるスイッチレッグ内の電流収集相互接続の他のインスタンスへの電気的接続はない。 30

【 0044 】

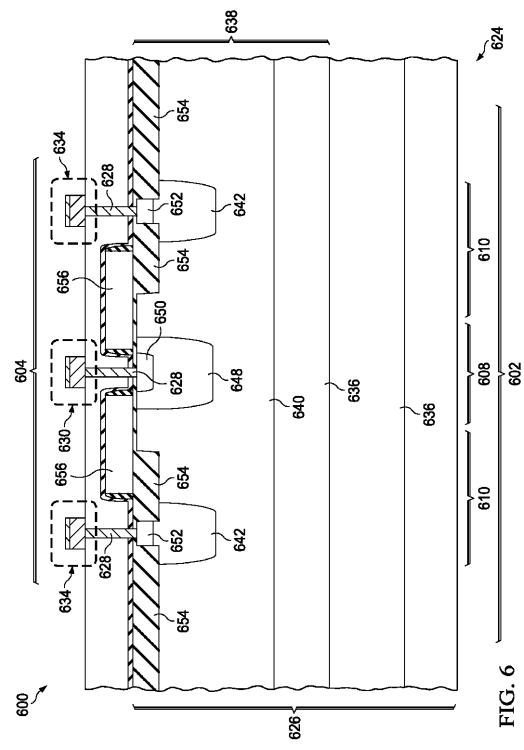

図 6 は、第 1 の電流スイッチ及び第 2 の電流スイッチが n チャネルドレイン拡張 M O S トランジスタである、例示の双方向 E S D 保護デバイスを含む集積回路を示す。集積回路 624 は、半導体材料を含む基板 626 内及び基板 626 上に形成される。図 6 は、スイッチレッグ 602 内の、ドレイン拡張 M O S トランジスタ 604 である第 1 の電流スイッチ 604 を介した、デバイス 600 の断面を示す。スイッチレッグ 602 の第 2 の電流スイッチが、同様のプロセスシーケンスによって形成され得る。 40

【 0045 】

例えば図 5 に関して説明したように、n 型埋め込み層 636 が基板 626 内に形成され、深い n 型ウェル 640 が埋め込み層 636 の上の基板内に形成される。M O S トランジスタ 604 のソースノード 608 である、第 1 の電流スイッチ 604 の第 1 の電流供給ノード 608 が、深い n 型ウェル 640 内に形成される浅い p 型ウェル 648 と、浅い p 型ウェル 648 内に形成される n 型ソース領域 650 とを含む。 40

【 0046 】

M O S トランジスタ 604 のドレインノード 610 である、第 1 の電流スイッチ 604 の第 1 の電流収集ノード 610 が、深い n 型ウェル 640 内に形成される浅い n 型ウェル 642 と、浅い n 型ウェル 642 と浅い p 型ウェル 648 との間の深い n 型ウェル 640 の一部と、浅い n 型ウェル 642 内の n 型ドレインコンタクト領域 652 とを含む。 50

## 【0047】

n型ドレインコンタクト領域652からn型ソース領域650への漏れ経路を抑制するために、基板626の頂部表面にフィールド酸化物654が形成され得る。深いn型ウェル640及び浅いp型ウェル648に重なって基板626の上にゲート656が形成される。ゲート656はMOSトランジスタ604をトリガするためにバイアスされ得る。

## 【0048】

基板626の上にコンタクト628及び金属相互接続が形成される。金属相互接続のうちの第1の相互接続630が、コンタクト628を介してMOSトランジスタ604のソースノード608への電気的接触を成す。第1の相互接続630は、双方向ESD保護デバイス600の第1の端子に電気的に結合される。金属相互接続の電流収集相互接続634が、MOSトランジスタ604のドレインノード610への及び同じスイッチレッグ602内の第2の電流スイッチの第2の電流収集ノードへの電気的接続を成す。収集相互接続634には、異なるスイッチレッグ内の電流収集相互接続の他のインスタンスへの電気的接続はない。

10

## 【0049】

図7は、第1の電流スイッチ及び第2の電流スイッチがNPNバイポーラトランジスタである、例示の双方向ESD保護デバイスを含む集積回路を示す。集積回路724は、半導体材料を含む基板726内及び基板726上に形成される。図7は、スイッチレッグ702内の、NPNバイポーラトランジスタ704である第1の電流スイッチ704を介した、デバイス700の断面を示す。スイッチレッグ702の第2の電流スイッチが、同様のプロセスシーケンスによって形成され得る。

20

## 【0050】

例えば図5に関して説明したように、n型埋め込み層736が基板726内に形成される。埋め込み層736への電気的接続を成すために、基板726内に深いn型シンカ758が形成される。深いn型シンカ758は、例えばn型ドーパントを基板726の頂部領域内に注入すること、及びそれに続く熱駆動によって、形成され得る。深いn型ウェル740が、例えば図5に関して説明したように、埋め込み層736の上の基板内に形成される。バイポーラトランジスタ704のベース領域を提供する浅いp型ウェル748が、深いn型ウェル740内に形成される。

30

## 【0051】

バイポーラトランジスタ704のエミッタノード708である、第1の電流スイッチ704の第1の電流供給ノード708が、浅いp型ウェル748内に形成されるn型エミッタ領域750を含む。

## 【0052】

バイポーラトランジスタ704の収集ノード710である、第1の電流スイッチ704の第1の電流収集ノード710が、深いn型シンカ758の上に形成される浅いn型ウェル742と、浅いn型ウェル742内のn型コレクタコンタクト領域752とを含む。

## 【0053】

n型ドレインコレクタ領域752からn型エミッタ領域750への漏れ経路を抑制するために、基板726の頂部表面にフィールド酸化物754が形成され得る。基板726の上にコンタクト728及び金属相互接続が形成される。金属相互接続のうちの第1の相互接続730が、コンタクト728を介してバイポーラトランジスタ704のエミッタノード708への電気的接続を成す。第1の相互接続730は、双方向ESD保護デバイス700の第1の端子に電気的に結合される。金属相互接続の電流収集相互接続734が、バイポーラトランジスタ704の収集ノード710への及び同じスイッチレッグ702内の第2の電流スイッチの第2の電流収集ノードへの電気的接続を成す。収集相互接続734には、異なるスイッチレッグ内の電流収集相互接続の他のインスタンスへの電気的接続はない。

40

## 【0054】

当業者であれば、本発明の特許請求の範囲内で、説明した例示の実施形態に対する改変

50

が成され得ること、及び、多くの他の実施形態が可能であることを理解されよう。

【図1】

FIG. 1

【図2】

FIG. 2

【 図 3 】

318

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図4C】

FIG 1C

【 図 5 】

【 図 6 】

【図7】

---

フロントページの続き

(72)発明者 アクラム エイ サルマン

アメリカ合衆国 75025 テキサス州 プラノ, エルジャー ドライブ 2304

(72)発明者 ファルザン ファルビズ

アメリカ合衆国 75204 テキサス州 ダラス, ダブリュー ブールバード 537, シティプレイス 2901

(72)発明者 アン マーガレット コンカノン

アメリカ合衆国 94301 カリフォルニア州 パロ アルト, エヴァレット アヴェニュー 418

(72)発明者 ジャンルカ ボセッリ

アメリカ合衆国 75093 テキサス州 プラノ, チャネル アイル ドライブ 5305

審査官 宇多川 勉

(56)参考文献 米国特許出願公開第2008/0013231(US, A1)

特開2002-261241(JP, A)

特開昭60-103658(JP, A)

特開平08-064773(JP, A)

特開2008-034524(JP, A)

特開2009-218296(JP, A)

特開2013-172092(JP, A)

特開2008-098479(JP, A)

特表2013-531890(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04

H01L 27/06