## (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2005-506690 (P2005-506690A)

(43) 公表日 平成17年3月3日(2005.3.3)

(51) Int.C1.7

$\mathbf{F} \mathbf{I}$

テーマコード (参考)

HO1L 25/10 HO1L 25/11 HO1L 25/14

$\mathbf{z}$

HO1L 25/18

#### 審查請求 未請求 予備審查請求 未請求 (全 85 頁)

(33) 優先権主張国 米国(US)

(71) 出願人 504142411

テッセラ, インコーポレイテッド

アメリカ合衆国カリフォルニア州95134, サン・ノゼ, オーチャード・ドライヴ

3099

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(72) 発明者 プリューグハウプト, エル・エリオット

アメリカ合衆国カリフォルニア州9502 3, ロス・ガトス, モンクレア・ロード

252

最終頁に続く

(54) 【発明の名称】積層パッケージ

## (57)【要約】

積層チップアセンブリが、誘電体層(20)上に実装さ れたチップ(58)と、誘電体層の周辺領域に端子(2 2) が配置されたチップのコンタクトを相互接続する誘 電体層上のトレース(38)とを有する個々のユニット (56)を含む。トレース(38a、38e)の少なく ともいくつかが、チップセレクトコンタクトをチップセ レクト端子に接続するマルチブランチトレースである。 ユニットは、上下に積層され、異なるユニットの対応す る端子が、はんだボール(78)または他の伝導性部品 によって互いに接続されて、垂直方向バスを形成する。 積層前に、個々のユニットのマルチブランチトレースは 、個々のブランチ(50)を破断することによって、選 択的に切断されて、異なるユニットにあるチップのチッ プセレクトコンタクトを異なるチップセレクト端子に接 続した状態にすることにより、これらのチップを異なる 垂直方向バスに接続する。個々のユニットは、薄いもの であることが望ましく、互いに直接に隣接して、積層体 内のチップからの熱伝達が良好な高さの低いアセンブリ が得られる。

20

30

40

50

#### 【特許請求の範囲】

## 【請求項1】

(a)複数のユニットと、

各ユニットは、(i)少なくとも1つのチップセレクトコンタクトおよび複数の他のコンタクトを有する半導体チップと、(ii)複数のチップセレクト端子と、複数の他の端子と、前記チップのコンタクトと前記端子との間に電気的に接続されて、回路パネル上または回路パネル中に延びるトレースとを有する回路パネルとを含み、

ここで、各チップセレクトコンタクトに電気的に接続された前記トレースが、前記セレクトコンタクトに接続された共通セクションと前記チップセレクト端子の異なる端子に接続された複数のブランチとを含むマルチプランチトレースであり、前記各マルチプランチトレースの、全ブランチよりも少ない少なくとも 1 つのブランチに切断部があることによって、前記チップセレクト端子のすべてよりも少ない端子に前記セレクトコンタクトが接続され、

ここで、前記ユニットが、重ね合わされたユニットの積層体になるよう互いに上下に配置 されており、

(b)複数の垂直方向バスを形成するように、前記積層体において前記ユニットの端子を相互接続する垂直方向導体と

を含み、

異なるユニットの前記チップセレクト端子が、前記垂直方向バスに接続され、前記マルチブランチトレースにある前記切断部が、異なるユニットの前記チップセレクトコンタクトが前記垂直方向バスの異なるバスに電気的に接続されるように配設される半導体チップアセンブリ。

#### 【請求項2】

前記各ユニットにおいて、前記各マルチブランチトレースの1つを除くすべてのブランチに切断部があることによって、各チップセレクトコンタクトが、前記ユニットの1つのみの前記チップセレクト端子に接続されるものである請求項1に記載の半導体アセンブリ。

#### 【請求項3】

異なるユニットの前記チップとトレースと端子とは互いに同一のものであるが、前記ユニットの異なるユニットが、異なるユニットの前記チップセレクトコンタクトが前記ユニットの前記回路パネル上の異なる端子に接続されるように切断された異なるブランチを有する点において異なっている請求項1に記載の半導体アセンブリ。

#### 【請求項4】

異なるユニットの対応する端子が上下に配置される請求項3に記載の半導体アセンブリ。

### 【請求項5】

前記積層体にある前記同一のユニットが最下ユニットを含み、該最下ユニットの前記端子が外部基板への相互接続用に露出される請求項3に記載の半導体アセンブリ。

### 【請求項6】

前記積層体にある前記同一ユニットが最下ユニットを含み、前記アセンブリが前記最下ユニットの下にあるトランスレータをさらに含み、前記トランスレータが前記垂直バスに接続されたコンタクトパッドと該コンタクトパッドに接続された端子とを有し、前記トランスレータの前記端子が外部基板への接続用に露出される請求項3に記載の半導体アセンブリ。

## 【請求項7】

前記積層体にある前記同一ユニットが最下ユニットを含み、前記アセンブリが前記最下ユニットの下にある追加のユニットをさらに含み、前記追加ユニットが半導体チップと外部基板への接続用に露出された端子を有する回路パネルとを含み、前記追加ユニットの前記端子が前記積層体にある前記同一ユニットの前記端子とは異なるパターンに配置され、前記追加ユニットの前記端子の少なくともいくつかが前記垂直方向バスに電気的に接続され、前記追加ユニットの前記端子の少なくともいくつかが前記追加ユニットの前記チップに

電気的に接続される請求項2に記載の半導体アセンブリ。

#### 【請求項8】

前記各ユニットの前記回路パネルが、前記トレースと前記端子とを構成する電気的に伝導性の材料の層を1つだけ含む請求項1に記載の半導体アセンブリ。

#### 【請求項9】

前記各ユニットの前記回路パネルが、厚みが約100μm未満の誘電体層を含む請求項8に記載の半導体アセンブリ。

## 【請求項10】

前記 1 つのユニットの前記チップが前記ユニットの誘電体層と前記ユニットの隣接するユニットの誘電体層との間に配置され、前記誘電体層の対応する表面間の垂直方向の距離が前記ユニットにある前記半導体チップの厚みよりも大きい 2 5 0 μm以下である請求項 9 に記載の半導体アセンブリ。

#### 【請求項11】

前記ユニットの隣接するユニットにある対応する機構間の垂直方向の間隔距離が、各チップの厚みよりも大きい 2 5 0 μ m 以下である請求項 1 0 に記載の半導体アセンブリ。

#### 【請求項12】

前記各ユニットの前記回路パネルが少なくとも1つの切断孔がある誘電体層を含み、前記切断部が前記切断孔に形成されるものである請求項1に記載の半導体アセンブリ。

## 【請求項13】

前記各ユニットの前記回路パネルが、エッジと、前記エッジの1つ以上から内向きに延びる1つ以上のノッチとを有し、前記切断部が前記ノッチに形成されるものである請求項1 に記載の半導体アセンブリ。

### 【請求項14】

前記各ユニットの前記端子が、前記回路パネルの第1のエッジに隣接して配置された端子の第1の外側の列を含み、前記端子の第1の外側の列が、前記第1のエッジから離れた第1の内側境界を画定し、前記ブランチの少なくともいくつかが、前記第1の内側境界を越えて外向きに延びた外側部分を有し、前記ノッチの少なくとも1つが、少なくとも1つの前記外側部分に少なくとも1つの切断部を画定するものである請求項13に記載の半導体アセンブリ。

## 【請求項15】

前記各ユニットの前記端子が、前記ユニットの前記回路パネルの第1のエッジに隣接して配置された端子の第1の外側の列を含み、前記第1のエッジが、前記第1のエッジの残りから外向きに延びる少なくとも1つの突出部を有し、前記ブランチの少なくとも1つが、前記突出部へと延びる請求項13に記載の半導体アセンブリ。

## 【請求項16】

前記各ユニットの前記回路パネルが実質的に平坦であり、前記各回路パネルの前記突出部が前記回路パネルの平面から垂直方向に突出するものである請求項15に記載の半導体チップアセンブリ。

## 【請求項17】

半導体チップアセンブリの製造方法であって、

(a) 少なくとも1つのチップセレクトコンタクトおよび複数の他のコンタクトを有する少なくとも1つの半導体チップと、複数のチップセレクト端子、複数の他の端子、および前記端子に接続された回路パネル上または回路パネル内に延びるトレースを有する回路パネルとを各々が含む複数のユニットを積層するステップであって、前記各パネルの少なくとも1つのトレースが、複数のチップセレクト端子に関連付けられたマルチブランチトレースであり、該マルチブランチトレースの各々が、共通セクションと、前記チップセレクト端子の異なる端子に接続された複数のブランチとを含み、各ユニットにある前記少なくとも1つのチップの前記コンタクトを前記ユニットにある前記回路パネルのトレースに接続することによって、前記マルチブランチトレースの共通セクションに各チップセレクトコンタクトを接続するステップと、

30

10

20

50

( b ) 各マルチブランチトレースの前記共通セクションが、前記マルチブランチトレースに関連付けられた前記チップセレクト端子のすべてより少ない端子に接続されるように、前記マルチブランチトレースの前記ブランチを選択的に切断するステップと、

(c) 垂直方向バスを形成するように、異なるユニットの端子を互いに相互接続するステップとを含み、異なるユニットにあるチップの前記チップセレクト端子が前記垂直方向バスの異なるバスに接続されるように、前記選択的に切断するステップおよび前記相互接続するステップが実行されるものである半導体チップアセンブリの製造方法。

### 【請求項18】

前記回路パネルが、前記選択的に切断するステップの前に互いに同一のものである請求項 17に記載の方法。

【請求項19】

前記積層ステップが、異なるユニットにある回路パネルの対応する端子を互いに位置合わせすることを含む請求項18に記載の方法。

【請求項20】

前記選択的に切断するステップが、前記各マルチブランチトレースの前記共通セクションが前記トレースを担持する前記回路パネルの 1 つのセレクト端子だけに接続されるように実行されるものである請求項 1 7 に記載の方法。

【請求項21】

前記ユニットを形成するステップをさらに含み、前記ユニットを形成する前記ステップが、ツールを用いて前記トレースに前記チップを接続することを含み、前記選択的に切断するステップが、前記ツールを前記マルチブランチトレースの前記ブランチと係合することによって実行されるものである請求項17に記載の方法。

【請求項22】

チップを回路パネルに接続することによって、前記ユニットを形成するステップをさらに 含み、前記選択的に切断するステップが、前記ユニットを形成する前記ステップの後に実 行されるものである請求項17に記載の方法。

【請求項23】

前記選択的に切断するステップが、前記積層ステップと同じ施設において実行される請求項17に記載の方法。

【請求項24】

前記選択的に切断するステップの前に、前記ユニットが、同一のチップと、同一の端子と、前記チップのコンタクトと端子との間の同一の接続とを含む請求項17に記載の方法。

【請求項25】

前記選択的に切断するステップの前に、相互に交換可能な部品として、前記ユニットを取り扱いストックするステップをさらに含む請求項 2 4 に記載の方法。

【請求項26】

複数のユニットの前記回路パネルが連続的または半連続的なシートの部分であるように前記ユニットを与えるステップと、前記シートから前記回路パネルを切り離すステップとをさらに含み、前記選択的に切断するステップが前記切り離しステップと同時に実行されるものである請求項17に記載の方法。

【請求項27】

前記選択的に切断するステップの前に、前記回路パネルが前記回路パネルを通って延びる切断開口を有し、前記マルチプランチトレースの前記プランチが前記切断開口にわたって延び、前記選択的に切断するステップが前記切断開口においてマルチブランチトレースのプランチを破断することを含む請求項17に記載の方法。

【請求項28】

前記選択的に切断するステップが、前記マルチブランチトレースの領域を除去すると同時に、前記切り離し領域の下にある前記回路パネルの部分を除去することによって、マルチプランチトレースのブランチを切り離すことを含む請求項17に記載の方法。

【請求項29】

50

10

20

30

前記除去ステップが、エッジにおいて前記回路のパネルの部分を除去することを含む請求項28に記載の方法。

#### 【請求項30】

( a ) 複数のユニットを含み、各ユニットが、

( i ) 前面上にコンタクトを有する半導体チップと、

(ii)中央領域および周辺領域を有する回路パネルとを含み、前記パネルが、第1および第2の表面を有する誘電体層と、前記中央領域にある前記第1および第2の表面間に延びる少なくとも1つのボンドウィンドウと、前記周辺領域にある前記第1および第2の表面間に延びる複数の端子孔とを含み、前記各パネルが、該端子孔に位置合わせあされた複数の端子パッドと前記パネルに沿って水平方向に延びる複数のトレースとを規定する単一の金属化層を含み、前記チップが、前記中央領域にある前記パネルの表面の方へ前記チップの前記前面を対面させて配置され、前記チップの前記コンタクトが、前記少なくとも1つのボンドウィンドウにおいて前記パネルの前記トレースに接続され、

前記ユニットが、1つのユニットにおけるチップの背面が次の隣接するユニットにある誘電体層の表面に対面するように、積層体に互いに重なり合わされ、前記ユニットが前記トレースによって占められた前記中央領域の少なくとも部分に互いに担持され、前記ユニットの前記端子が互いに整列され、

(b)前記ユニットの端子と、前記パネルの前記端子孔を通って隣接するユニットの接続端子との間に配置された複数の伝導性集合体を含むものである半導体チップアセンブリ。

### 【請求項31】

各ユニットにある前記トレースが、前記ユニットにある前記誘電体層の前記第 1 の表面に沿って延び、各ユニットにある前記チップの前記前面が、前記ユニットにある前記誘電体層の前記第 2 の表面に対面するものである請求項 3 0 に記載の半導体チップアセンブリ。

#### 【請求項32】

前記ユニットの少なくともいくつかが、前記ユニットの前記トレースの上にある熱伝達層を含み、前記ユニットが、前記熱伝達層を通して互いに担持されるものである請求項31 に記載の半導体チップアセンブリ。

#### 【請求項33】

前記熱伝達層の少なくともいくつかが、前記ボンドウィンドウにわたって延び、前記ボンドウィンドウにわたって前記領域において実質的に平坦である請求項32に記載の半導体チップアセンブリ。

## 【請求項34】

前記ボンドウィンドウを少なくとも部分的に充填するカプセル封入材をさらに含む請求項3 % に記載の半導体チップアセンブリ。

### 【請求項35】

前記回路パネルの各々が前記トレースと一体形成された複数のリードを含み、前記リードが前記回路パネルの前記少なくとも 1 つのボンドウィンドウ内へと延びる請求項 3 0 に記載の半導体チップアセンブリ。

## 【請求項36】

( a ) 複数のユニットと、

ここで、各ユニットは、

( i ) 前面上にコンタクトを有する半導体チップと、

(ii)中央領域および周辺領域を有する回路パネルと、ここで、前記パネルは、第1および第2の表面を有する誘電体層と、前記中央領域にある前記第1および第2の表面間に延びる少なくとも1つのボンドウィンドウと、前記周辺領域にある前記第1および第2の表面間で露出された複数の端子パッドと、前記パネルに沿って水平方向に延びる複数のトレースとを含み、前記チップは、前記中央領域にある前記誘電体層の前記第2の表面の方へ前記チップの前記前面を対面させて配置され、前記チップの前記コンタクトは、前記少なくとも1つのボンドウにおいて前記パネルの前記トレースに接続されており、(iii)前記少なくとも1つのボンドウィンドウにあるカプセル封入材と、ここで、該

20

30

40

カプセル封入材が、前記誘電体層の前記第1の表面と実質的に同一平面上にある表面を規定しており、

を含み、

前記ユニットは、1つのユニットにおけるチップの背面が次の隣接するユニットにある誘電体層の表面に対面するように、積層体に互いに重なり合わされ、前記ユニットは、前記トレースによって占められた前記中央領域の少なくとも部分に互いに担持され、前記ユニットの前記端子は、互いに整列されており、

(b)前記ユニットの端子と、互いに隣接するユニットの接続端子との間に配置された複数の導電性集合体と

を含んでなる半導体チップアセンブリ。

【請求項37】

前記各誘電体層の厚みが、約100μm未満である請求項36に記載の半導体チップアセンブリ。

【請求項38】

前記 1 つのユニットの前記チップが、前記ユニットの誘電体層と前記ユニットの隣接するユニットの誘電体層との間に配置され、前記誘電体層の対応する表面間の垂直方向の距離が、前記ユニットにおける前記半導体チップの厚みより大きい 2 5 0 μ m 以下である請求項 3 6 に記載の半導体チップアセンブリ。

【請求項39】

前記ユニットの隣接するユニットにある対応する機構間の垂直方向の間隔距離が、各チップの厚みより大きい250μm以下である請求項36に記載の半導体チップアセンブリ。

【請求項40】

前記各ユニットが、前記少なくとも1つのボンドウィンドウおよび前記ユニットの前記カプセル封入材の上にある実質的に平坦な熱伝達層をさらに含む請求項36に記載の半導体チップアセンブリ。

【請求項41】

交換可能な半仕上げユニットの製造過程集合体であって、前記各ユニットが、少なくとも1つのチップセレクトコンタクトおよび複数の他のコンタクトを有する少なくとも1つのキップと、複数のチップセレクト端子、複数の他の端子、および前記端子に接続れた回路パネル上または回路パネル内に延びるトレースを有する回路パネルとを含み、前記各パネルの少なくとも1つのトレースが、共通セクションと前記チップセレクト端子の異なる端子に接続された複数のブランチとを有するマルチブランチトレースでありのチップの前記コンタクトが、前記ユニットにある前記少なくとも1つのチップの前記コンタクトが、前記ユニットにあるマルチブランチトレースの前記共通セクションに接続され、前記ユニットが、同一の端子、および前記チップのコンタクトと端子との間の同一の接続を含み、前記ロニットが、前記ユニットの対応する端子を互いに接続させて、上下に積層するようにされた製造過程集合体。

【請求項42】

複数の前記ユニットの前記回路パネルが、共通のシートの部分である請求項 4 1 に記載のユニットの製造過程集合体。

【請求項43】

前記シートが、前記トレースおよび前記端子を画定する金属性の層を 1 つだけ含む請求項4 1 に記載のユニットの製造過程集合体。

【請求項44】

前記各回路パネルが、厚みが100μm未満の誘電体層を含む請求項43に記載のユニットの製造過程集合体。

【発明の詳細な説明】

【技術分野】

[0001]

50

10

20

30

(7)

本発明は、電子回路の作製に用いることができる。

### 【背景技術】

#### [00002]

半導体チップは、典型的に、比較的に大きな前面および背面と小さなエッジ表面とを備えた、薄く平坦なものである。チップは、前面上にコンタクトを有する。チップは、典型的に、外部回路との接続に適した端子を有するパッケージングされたチップとして与えられる。パッケージングされたチップは、典型的に、平坦な本体の形のものである。通常、パッケージングされたチップは、回路基板の表面上にアレイ状に配設される。回路基板は、回路基板の表面に平行な水平方向に延びる、通常、「トレース」と呼ばれる導電体を有するとともに、トレースに接続されたコンタクトパッドまたは他の導電性部品を有する。パッケージングされたチップには、回路基板の表面に対面する端子担持面が実装され、各パッケージングされたチップ上の端子は、回路基板のコンタクトパッドに電気的に接続される。

## [ 0 0 0 3 ]

典型的に、このようにして、メモリチップが実装される。パッケージングされていないというにして、メモリチップが実装される。パッケージングされていたというにいていた。 1 以上のセレクトコンタクトに適切な信号が適用されなければ、ッケージングされたは、ッケーコンタクトに適切な信号が適用されなければ、ッケージングされたメモリチップは、データは接続されたデータはでは、データのように接続されたデータはは、アレクトに接続されたデータがされたメモリチップは接続されたデータにおいて、カーの対グされたメモリチップは接続されたデータにおいて、カーに対してが、1 の対のの固対のプロがでが、1 のができるとになるのがでは、できるにはい、逆のチップに関連するとになるに対してのチップにデータを書き込むにより、できるのに組み立てることができる。このような回路は、従来のケージを用いることになり、容易に組み立てることができるに対して同一のチップパッケージを用いる。

#### [0004]

従来の構成において、回路基板の理論上の最小面積は、個々のチップパッケージの端子担持表面のすべてを総計した面積に等しい。実際には、回路基板は、この理論上の最小値よりわずかに大きいはずである。回路基板上のトレースは、典型的に、大きな長さとインピーダンスとを有するため、トレースに沿って信号を伝播させるためには、かなりの時間が必要である。これは、回路の動作速度を制限してしまう。

## [0005]

これらの欠点を解消するために、さまざまなアプローチが提案されてきている。このようなアプローチのうちの1つは、共通するパッケージにおいて、複数のチップを上下に「積層(stack)」することである。パッケージ自体は、回路基板のコンタクトパッドに接続された垂直方向に延びる導体を有する。パッケージ内の個々のチップは、これらの垂直に延びる導体に接続される。チップの厚みが水平方向の寸法よりも実質的に小さされている。例えば、積層パッケージの構、では、同数のチップを接続するために要求されている。例えば、積層パッケージの構、米国特許第5,861,666号公報と、米国特許第5,198,888号公報と、米国特許第6,072,233号公報と、米国特許第6,072,233号公報と、米国特許第6,072,233号公報と、米国特許のいくつかの実施形態に示されている積層パッケージは、その各々が単ーチップとユニット端子を有するによって作製される。各ユニットはよいて、チップのコンタクトはユニット端子に接続される。ユニットは上下に積層される。

30

20

50

30

40

50

各ユニットのユニット端子は、他のユニットの対応するユニット端子に接続される。接続されたユニット端子は、バスとも呼ばれる積層パッケージの垂直方向導体を形成する。

#### [0006]

しかしながら、個々の選択接続を有する回路を積層パッケージが備えると、複雑性がさら に増してしまう。垂直方向導体が、さまざまなユニットの端子を介して延びているため、 チップのコンタクトと積層体にある各ユニットのユニット端子との間の相互接続は、特有 の垂直方向導体への接続を与えるために異なるものであるべきである。例えば、選択信号 を伝えるための4つの垂直方向バスを有する4チップ積層体において、最下部ユニットが 、バス番号1の部分を形成するユニット端子に接続されたチップのセレクトコンタクトを 有し、次のユニットが、バス番号2を形成する端子に接続されたチップの対応するセレク トコンタクトを有し、以下のユニットも同様に有する場合がある。このようにユニットを カスタマイズする必要があると、製造プロセスの複雑性が増してしまう。例えば、米国特 許 第 4 , 9 5 6 , 6 9 4 号 公 報 に は 、 各 ユ ニ ッ ト に 中 間 端 子 セ ッ ト を 備 え た チ ッ プ キ ャ リ ヤを有するユニットが記載されている。これらの中間端子は、チップ上のコンタクトに接 続され、ユニットの端子にも接続される。相互接続はワイヤボンドによって作られる。ワ イヤボンドのパターンはユニットごとに異なる。この構成では、本質的に、比較的に大き なチップキャリヤが必要であるため、コストおよびパッケージの容積(bulk)が増大する ,さらに、製造業者は、多数の異なるワイヤボンドユニットを取り扱い、ストックしなけ ればならない。 S u g a n o らの米国特許第5 , 1 9 8 , 8 8 8 号公報では、さまざまな ユニットにおいて個別化されたチップキャリヤが使用されている。これらのチップキャリ ヤは、セレクトコンタクトと関連する端子とに対して異なる相互接続パターンを規定する いくつかのリードを有する。この場合においても、製造プロセスのコストおよび複雑性が 増大する。米国特許第6,268,649号公報および米国特許第6,072,233号 公報でも、同様にカスタマイズされたユニットが使用されている。積層パッケージにおい てカスタマイズされたユニットを与えることに関連するコストの削減および複雑性の低減 が望まれる。

## [0007]

また、小型の積層パッケージを提供し、積層体内のチップから外部環境、例えば、回路基板やパッケージの上部にある熱スプレッダへの熱伝達が良好な積層パッケージを提供することが望まれる。さらに、容易に入手可能な機器と容易に製造可能な構成部品とを用いて、このようなパッケージを提供することが望まれる。

## 【発明の開示】

### [0008]

本 発 明 の 1 つ の 態 様 に よ り 、 複 数 の ユ ニ ッ ト を 組 み 込 ん だ 半 導 体 チ ッ プ ア セ ン ブ リ が 提 供 される。各ユニットは、少なくとも1つのセレクトコンタクトと複数の他のコンタクトと を有する半導体チップを含むことが望ましく、複数のチップセレクト端子と複数の他の端 子とともに、パネル上またはパネルに延びるトレースを有する回路パネルも含む。トレー スは、チップのコンタクトと端子との間に電気的に接続される。チップの各チップセレク トコンタクトに電気的に接続されたトレースは、チップのセレクトコンタクトに接続され た共通のセクション(section)と、回路パネル上のチップセレクト端子の異なるものに 接続された複数のブランチとを含むマルチブランチトレース(multi-branch trace)である ことが望ましい。アセンブリにおいて、望ましくは、少なくとも1つのブランチであるが 、このような各マルチブランチトレースのブランスのすべてより少ないブランチに切断部 があることにより、セレクトコンタクトは、パネル上のチップセレクト端子のすべてより 少ないものに接続され、最も好ましくは、各チップセレクトコンタクトは、ユニットのパ ネルの1つのみのチップセレクト端子に接続される。ユニットは、重なり合ったユニット の積層体になるよう互いに上下に設けられる。アセンブリは垂直方向導体をさらに含み、 垂直方向導体の各々は、互いに積層体内のユニットの対応する端子を接続して、複数の垂 直方向バスを形成する。マルチブランチトレースと切断されたブランチとにより与えられ る個々のユニット内での選択的な接続により、異なるユニットにあるチップのチップセレ

30

40

50

クトコンタクトは、垂直方向バスの異なるものに電気的に接続される。この構成により、個々のチップに伝達されなければならないチップセレクト信号と他の信号との選択的なルート決定が得られる。各チップ上の残りのコンタクトは、他のユニットにあるチップ上の対応するコンタクトと並列接続されるため、さまざまなチップの残りのコンタクトに信号を並列して伝達することができる。これにより、要求される選択的なルート決定が得られる。

#### [0009]

最も好ましくは、積層体にある異なるユニットのチップとトレースと端子とは、異なるユニットの異なるチップセレクトコンタクトが、このようなユニットの回路パネル上の異なる端子に接続されるように切断されたマルチブランチトレースの異なるブランチをユニットの異なるものが有することを除いて同一のものである。最も好ましくは、各ユニットの回路パネルは、約100μmの厚みより薄いことが望ましい誘電体層を含む。ユニットの隣接するいくつかの機構または要素(features)の間隔に対応する垂直方向の間隔距離は、約250μm以下であり、好ましくは、各ユニットのチップの厚みよりも大きい約200μmである。したがって、アセンブリの全高(overall height)は比較的に低い。

#### [0010]

各回路パネルにある誘電体層が切断孔または開口を有していてもよく、マルチブランチトレースのブランチにある切断部がこのような切断孔に形成されていてもよい。 典型的には、プロセスの後段階において、ユニットの製造時またはブランチの切断時に、切断孔を誘電体層に形成することができる。 ある構成において、各ユニットの回路パネルはエッジを有し、切断孔は1つ以上のエッジから内向きに延びるノッチの形で与えられる。 このようなユニットの端子は、回路パネルのエッジに隣接して設けられた外側の列を含んでいてもよく、マルチブランチトレースのブランチは、端子の外側の列へ外向きに延びるか、またはそれを越える部分を有していてもよい。この場合には、ノッチが端子の外側の列を越えて内向きに延びる必要がないため、マルチブランチリードの切断部を容易に形成することができる。

## [ 0 0 1 1 ]

本発明のさらなる態様により、半導体チップできるむ。この場合もと、本各コーマンプリの製造方法が提供される。本名コーマンプリの製造方法は、複数のユニットを与えるステップを含む。このタクトとを有ったとを有ったとを有ってといったは、少なくともも1つの半導体チップを含む。フタクトと他のコンタクトと他の出るととも1つの半導体チップを含むことがリセレクト端子の四位のカースとを有ってのセクションとを消費を含む。これを含まれたパネルトに近びのトレースとを含むマルチンタクトはないのでは、大きなのでは、大きなのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大きないのでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大き、はいるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないるでは、大きないない。

## [0012]

選択的に切断するステップは、異なるユニットにあるチップのチップセレクト端子が、垂直方向バスの異なるものに接続されるように実行されることが望ましい。マルチブランチトレースを選択的に切断するステップの前に、ユニットは互いに実質的に同一のものであることが最も好ましい。ユニットの形成中または形成後の任意の時にマルチブランチトレースを選択的に切断するステップを実行することができる。ある構成において、ユニットを与えるステップは、サーモソニックボンディングツールなどのツールを用いてチップをトレースに接続することを含み、ブランチを選択的に切断するステップは、同一の処理動

30

50

作の一環として、同じツールをブランチに関与させることにより実行される。

### [0013]

別の構成において、ブランチを選択的に切断するステップは、例えば、積層ステップの直前のように、後に実行される。したがって、相互に交換可能な部品として取り扱われストックされうる実質的に同一の部品としてユニットが与えられてもよい。この場合も、さまざまなユニットの誘電体層は、誘電体層を通って延びる切断開口を含んでもよく、マルチブランチトレースのブランチは、切断ステップの前に、これらの切断開口にわたって延びてもよい。ブランチを選択的に切断するステップは、これらの切断開口でブランチを破断することを含みうる。この代わりに、例えば、各マルチブランチトレースの小さな領域とこれらの領域の下にある誘電体層の部分とを除去することによって、例えば、トレースのブランチを破断しながら回路パネルをパンチングして切断開口を形成することによって、ブランチが破断されると同時に切断開口が形成されていてもよい。

#### [0014]

ユニットは、互いに実質的に同一のものであり、ブランチを切断するステップを含むステップまで互いに交換可能な部品としての取り扱いが可能であるため、商業上でのユニットの取り扱いおよびストック(stock)が実質的に単純化される。例えば、ユニットは、ベア半導体チップを取り扱い、ベア半導体チップを個々のユニットの回路パネルに実装するようにされたチップパッキング工場で製造できる。積層動作は、パッキングされたチップを回路基板に表面実装するように適応されたツールおよび機器を有する回路基板スタッフィング工場において実行することができる。実際、積層動作は、アセンブリを回路基板に実装すると同時に実行することができる。例えば、ユニットは積層可能であり、さまざまなユニットを接合するはんだボールは、積層体の底部ユニットを回路基板に接合するはんだボールがリフロー接合されると同時に、リフロー接合することができる。

#### [ 0 0 1 5 ]

本発明のさらなる態様により、上述したように積層プロセスおよびアセンブリにおいて使用可能で交換可能な半仕上げユニット(semi-finished unit)である仕掛りあるいは製造過程中の集合体(in-process collection)が提供される。

#### [0016]

本発明のさらなる態様において、追加の半導体チップアセンブリが提供される。本発明のこの態様によるチップアセンブリが、複数のユニットをさらに含み、各ユニットは路内ではいる。本発明の上にコンタクトを有する半導体チップを含み、中央領域において第1および第2の表面と、中央領域において第1および第2の表面に正延びると、パネルは、第1および第2の両方の表面に露出される。パネルは、誘電体層は含み、端子は第1および第2の両方の表面に露出される。はは、誘電体層は周辺領域において第1および第2の表面間に延びる複数の端子をさらに含み、端子は第1および第2の表面間に延びる複数の端子を引し、端子に対し、ボールの表面の方へ対面するように設けられ、チップの司面が少においてパネル上のトレースに接続される。1つのユニットははにおいてパネルとを有ける。1つのコンタクトは、とも1つのボンドウにおいてパネル上のトレースに接続される。1つのユニットにあるチップの背面が次に隣接するユニットにある誘電体層の表面の方へ対面するように、中央領域の少なくとも一部分において互いに支えあっていることが最も好ましい。複数の導電性集合体(conductive mass)が、ユニットの端子間に設けられ、隣接するユニットの端子を互いに接続する。

## [0017]

1つの構成において、各ユニットのトレースはそのユニットにある誘電体層の第1の表面に沿って延びており、各ユニットにあるチップの前面はそのユニットにある誘電体層の第2の表面の方に対面する。このタイプのチップアセンブリにおいて、ユニットの少なくともいくつかがこのようなユニットのトレース上にある熱伝達層を含むことが望ましく、これらのユニットは熱伝達層(heat transfer layer)を介して互いに支えあう。したがって、このような各ユニットの熱伝達層は、次の隣接ユニットにあるチップの背面と隣接す

20

30

40

50

ることが望ましい。これらのユニットの熱伝達層は、これらのユニットの誘電体層にあるボンドウィンドウにわたって延びていることが望ましく、少なくとも、ボンドウィンドウ にわたって延びている領域において実質的に平坦である。このようなユニットは、ボンドウィンドウを少なくとも部分的に充填するカプセル封入材をさらに含むことが望ましい。製造中、カプセル封入材が誘電体層を越えて突出しないようにするためにカプセル封入材を閉じ込めるマスキング層として熱伝達層が作用してもよい。以下にさらに記載するように、平坦な熱伝達層により、ユニットが互いに密接して係合して、隣接するユニット間の、独り接触を良好にすることができるようになる。これらの機構は、アセンブリの高さを低くすることに貢献し、アセンブリ内のチップからの放熱を効果的に促進させる。

#### [ 0 0 1 8 ]

本発明のさらなる態様によるアセンブリにおいて熱伝達層が存在してもよいし省略されて もよいが、カプセル封入材は、誘電体層の第 1 の表面と実質的に同一平面上にあるか、こ のような表面に対して窪みが作られた表面を規定する。熱伝達層が省略される場合には、 各ユニットの誘電体層は、次の隣接ユニットにあるチップの背面上に直接に支持されてい てもよい。

#### [0019]

本発明の上記および他の目的と特徴と利点とは、添付の図面を参照しながら、以下に示す好適な実施形態の詳細な記載からさらに容易に明らかになるであろう。

【発明を実施するための最良の形態】

### [0020]

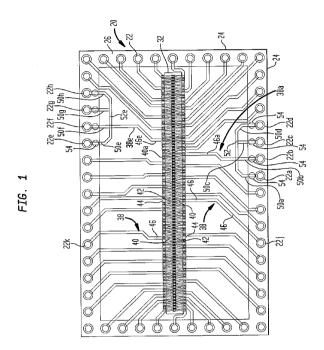

本発明の1つの実施形態によるパッケージは、各々が回路パネルの形をした複数のパッケージ部品20を用いる。このような各回路パネルは、約25~100μmの厚みであり、最も好ましくは25~75μmの厚みである、強化または非強化ポリイミドやBT樹脂等の層のような薄い可撓性の誘電体テープの形をした誘電体層を含みうる。この代わりに、各パネルは、例えば、FR-4またはFR-5基板等の繊維ガラス強化エポリスなどの誘電体を含みうる。パネルは、パネルのエッジ24に隣接したパネルの周辺領域するの列に設けられた多数の端子22を有する。図示した実施形態において、端子列が、マの4つのエッジに沿って設けられる。しかしながら、端子は、エッジのすべてよりののでありに関けられることができる。各端子22は、(図1に示す表面のように)パネルの第1の表面上の銅または他の適切な金属材料からなる平坦で比較的に薄いディスクの形をしているのでありうる。図2に最良に示すように、パネルは、端子22に位置合わせされ貫通してでありうる。図2に最良に示すように、パネルの第1の表面26とそれに対向する第2の表面30との間に広がっている。

## [ 0 0 2 1 ]

各パネル20は、パネルの中央に隣接して延びる細長いボンドウィンドウ32をさらに有する。パネルは、多数のリード36をさらに有する。各リードは、パネルの第1の表面32に沿って延びるトレース38と、ボンドウィンドウにわたってトレースから突出するトレースと一体形成された接続セクション40とを含む。図1に示すような組み立てられていない状態において、各接続セクションは、ボンドウィンドウの反対のトレース38の側から突出するアンカセクション44に、折り曲げ可能な部品42によって接続される。トレースとアンカ部分とは、ボンドウィンドウの長さに沿って延びる列に配設される。トレースとアンカ部分とは、ボンドウィンドウの長さに沿って延びる列に配設される。異なるトレースが、ボンドウィンドウの対向する側に延びるため、接続セクション40のいドウィンドウに突出する。トレースとそれらの接続セクションとの構成は、実質的に、米国特許の大・489,749号公報に示すようなものであってもよく、これを引用することにより本明細書の一部をなすものとする。

#### [ 0 0 2 2 ]

端子22は、第1のセレクト端子セット22A~22Dと、第2のセレクト端子セット2 2E~22Hとともに、本願明細書において、例えば、端子22Jおよび22K等の非セ

30

40

50

レクト端子と呼ばれる他の端子を含む。各トレース38は、接続セクション40に隣接し、そこに接続された共通のセクション46を含む。トレースのいくつかは、非セレクト端子に接続される。これらのトレースは、関連する端子、例えば、端子22Jおよび22Kまで延びる共通のセクション46を有するため、このような各トレースの共通セクション46は非セレクト端子に直接接続される。

#### [0023]

セレクト端子に関連付けされたこれらのトレース38は、マルチプランチトレース50である。このような各マルチプランチトレースは、共通のセクション46に接続され、、関ース38Aは、セレクト端子22Aに接続されたプランチ50Aと、セレクト端子22Aに接続されたプランチ50Aと、セレクト端子22Aに接続されたプランチ50Cと、セレクト端子22Cに接続されたプランチ50Cと、セレクト端子220に接続されたプランチ50Dとを含む。トレース38Aは、共通のセクション46Aに対して交差して延び、共通のセクションときまだ、端子222E~22日日は、マルチプランチ50E~50日のであり、同様のプランチ50E~50日のたり・カムでか記セクション52Eを有し、プランチ50E~50日のでは、トレースの共通のセクション46Eとその接続セクション40Eとに接続される。ル20の誘電体は、各マルチプランチトレース38のプランチ50に位置合わせされた切断孔54を有するため、このような各プランチは、切断孔にわたって延びる。切断孔は、セレクト端子22A、22Bなどに隣接して設けられる。

#### [0024]

トレースおよび接続セクションを含む端子およびリードは、パネルの第1の表面上の金属要素(metallic feature)の単一層として形成される。これらの金属要素の厚みは、約30μm未満であることが望ましく、典型的には、約5~25μm、例えば、約20μmである。任意選択的に、薄い接着層(図示せず)が、誘電体層20と金属層との間に設けれていてもよい。また、この接着層も、実行可能な限り薄いものでなければならず、カーカーのが望ましい。端子およびトレースは、テープ自動ボンディングテープとの製造において使用される従来のプロセスによって、例えば、銅または他の金属層とのパネルを形成する誘電体材料とを含むラミネートをエッチングして金属層の一部分を除することによって形成することができる。この代わりに、端子およびトレースは、無電解メッキおよび/または電気メッキなどの堆積プロセスによって形成することができる。ボンドウィンドウと端子に関連付けられた穴と切断孔とは、誘電体材料をエッチングするか、または除去することによって形成されていてもよい。

## [ 0 0 2 5 ]

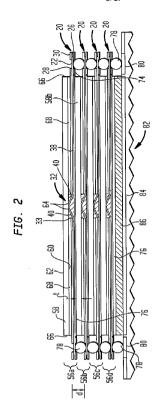

積層チップアセンブリは、複数のユニット56を含む(図2)。特に明記しない限り、各ユニット56は、積層体にある他の各ユニット56と同一のものである。このような各ユニットは、図1を参照して上述したようなパネルまたはチップキャリヤ20と、そのパネルに関連付けられたチップ58とを含む。このような各チップは、前面またはコンタクト支持表面60および背面62を有する。各チップの前面60は、チップの中央に隣接りた列に配設されたコンタクト64を有する。また、チップは、前面および背面62の境界を定めるエッジ66を有する。(前面60と背面62との間の寸法である)チップの厚み t は、典型的には、チップの他の寸法よりも実質的に小さい。例えば、典型的なチップは、厚みが約100~500ミクロンであり、(前面および背面の平面での)水平方向の寸法が約0.5cm以上でありうる。チップの前面60は、関連付けされたパネル20の第2の表面30の方へ対面する。

## [0026]

チップと各ユニットのパネルとの間に、接着層 6 8 が設けられる。接着層 6 8 は、ボンドウィンドウに位置合わせされた孔を規定する。組み立て時にチップとパネルとの間に液体またはジェル材料を適用することによって、または、層間に小さな弾性部品アレイなどの多孔層を与え、例えば、米国特許第 5 , 6 5 9 , 9 5 2 号公報および米国特許第 5 , 8 3

4 , 3 3 9 号 公 報 の い く つ か の 実 施 形 態 に お い て 教 示 さ れ た よ う な 層 に 流 動 可 能 な 材 料 を 注入することによって、接着層68を与えることができ、引用することにより本明細書の 一部をなすものとする。しかしながら、1つ以上の固体パッドまたは半固体パッドが、最 終 製 品 の 所 望 の 接 着 層 と 実 質 的 に 同 じ 水 平 方 向 の 広 が り を も つ よ う に 、 接 着 層 が 与 え ら れ る。これらのパッドは、組み立て中に、チップとパネルとの間に配置される。例えば、チ ップがパネルと並置される前に、パネルまたはチップに対してパッドを予め組み立てても よい。このような固体パッドまたは半固体パッドは、チップおよびパネルに対して非常に 正確に配置することができる。これにより、パッドエッジの公称位置と端子との間に小さ な隙間しかない場合であっても、パッドが端子22を覆わないようにされる。このような パッドは、未硬化層または部分的な硬化層と、例えば、米国特許第6,0303,856 号に記載されるような他の接着促進機構を含んでよく、この内容全体を引用することによ り本願明細書の一部をなすものとする。この代わりにまたはさらに、片面または両面上の 流動可能な接着薄層をパッドに設けることができ、この層は、米国特許第5,548,0 9 1 号公報に記載されるように非均一の層であってもよく、この内容全体を引用すること により本願明細書の一部をなすものとし、これによって、組み立て中に、層におけるガス の取り込みが防止される。接着層 6 8 は、例えば、厚みが約 1 0 ~ 1 2 5 μ m であり、最 も好ましくは、約25~75μmであるように、実現可能な限り薄いものであることが望 ましい。

[0027]

各ユニットのチップ58は関連付けられたパネルの中央領域に位置合わせされるため、コ ン タ ク ト 6 4 の 列 は パ ネ ル の ボ ン ド ウ ィ ン ド ウ 3 2 に 位 置 合 わ せ さ れ る 。 各 リ ー ド の 接 続 セクション40は、チップのコンタクト64に接続される。このプロセスの間に、各リー ドの接続セクションは、リードの折り曲げ可能なセクション42を破断することによって リードのアンカセクション44から取り外される。このプロセスは、前述した米国特許 第5,489,749号公報に記載されているように実行することができ、熱、サーモソ ニック、または超音波ボンディングツール等のツール(図示せず)を、各接続セクション に位置合わせされたパネルのボンドウィンドウへと進めることによって、ツールが接続セ クションを獲得してそれを適切なコンタクトに係合させることができるように実行されて よい。各リード(図1)にあるトレース38の共通のセクション46は、接続セクション 4 0 によって、チップ上のコンタクトに接続される。コンタクトおよび接続セクションの 構 成 は 、 マ ル チ ブ ラ ン チ ト レ ー ス 3 8 A お よ び 3 8 E の 共 通 セ ク シ ョ ン 4 6 A お よ び 4 6 E が、チップ上のセレクトコンタクト、すなわち、積層体にある他のチップのすべてにあ る対応するコンタクトと並列接続されないチップのコンタクトに接続される。他のトレー スの共通セクションは、非セレクトコンタクト、すなわち、積層体にある他のチップの対 応するコンタクトと並列接続されるチップのコンタクトに接続される。

[0028]

各ユニット56は、パネルの周辺領域にあるトレースおよび端子の上にあるはんだマスク層70(図2)をさらに含む。はんだマスク層は、端子22に位置合わせされた孔をする。従来のプロセスによって、コンフォーマル(conformal)なコーティングまたはシートとしてはんだマスク層を適用することができる。各ユニットは、トレース38上にあるパネルの中央領域にあるパネルのの表面26とをさらに含む。以下にさらに記載するように、熱伝達層は、積層体の次のが接ていたが可能ながリースなどの材料から、または、組み立て中、変形可能なおいら、またはが可能な材料、例えば、熱可塑性材料や未硬化または、熱伝達層がが態は他の反応性樹脂から、熱伝達層を形成してもよい。望ましくは、熱伝達層は、持てあり、したがって、互いのさまざまなトレースを電気的に短絡しない。熱伝達層を形成してもよいため、チップ58に位置合わせされたはんだマスク層と一体形成してもよいため、チップ58に位置合わせされたはんだマスク層と一体形成してもよいたの中央部分が熱伝達層を形成する。

[0029]

50

40

20

熱伝達層をはんだマスク層と一体形成したとしても、熱伝達層をはんだマスク層と別々に形成したとしても、例えば、その厚みは、約40μm以下、望ましくは約30μm以下であるように、実行可能な限り薄いことが望ましい。トレースの上にあるコーティングの領域における約5~20μmの厚みと、トレース間に位置する領域にある約10~40μmの厚みのコンフォーマルなコーティングとして、一体形のはんだマスク層および熱伝達層が与えられていてもよい。このようなコーティングは、わずか約5~20μmの厚みをユニットの全厚に追加する。図2に示すように、熱伝達層またははんだマスク層の中央部分は、誘電体層の孔32にまたがっている。熱伝達層またははんだマスク層の中央部分は、実質的に平坦であることが好ましく、誘電体層20から実質的に隆起しない。

## [0030]

カプセル封入材33を孔32に設けることができ、カプセル封入材33がリードの接続セクション40を取り囲む。カプセル封入材は、接着層68から分離されていてもよく、米国特許第6,232,152号公報(以下、「'152特許」とよぶ)および米国特許のとよぶ)の大き、カウに関系では、大き、834,339号公報(以下、「'339特許」とよぶ)に開示された技術を用いるように、その内容全体を引用することにより本願明細書の一実施形態に対する。'152特許および'339特許に教示されたいくつかの好適な実施形のとする。'152特許および'339特許に教示されたいくつかの好適な実施形のよって、全体でき、チップのエッジでに開けたいたは、活動でき、チップのエッジでこののチャネルを規定することができ、チップのエッジでに、大きによっての代わりに、上述しおいて、大きでは、大りにカウには、活動可能な材料によって、全体的または部分的に接きるのではれかのプロセスにおいて、熱伝達層76(または、内側熱伝達およびはんだマスク層、が誘電体層のボンドウィンドウを被覆するため、カプセル封入材は、誘電体層の第1の表面76を越えて突出することができない。

### [0031]

各ユニットの組み立て中に、マルチブランチトレースの共通セクションから、それらの特定のブランチに関連付けされた端子を切断するように、名マルチブランチを除り上している。各マルチブランチをなり、これたセレクションに接続されたセレクトでである。カールは、リースの共通セクションに接続されたセレクトでを1つのみ残すことが好ましい。破断することができる。ツールは、リーであっているできる。ツールは、リーであっているできる。ツールは、リーであっているできる。ツールは、リーであっているできる。できるものと同じものでできるいとにボンディング動作を実行するために使用たないもクションチに与えてもののではよいの残りよりも弱い折り曲げで対した強いをブランチに与えてもののではよいのでがありよりも弱い折り曲がある。ブランチはパネル20の誘電体ののではがあり、取断された端部は接着層に埋め込まれた状態になる。この代わりに、ブランチの破断された端部は接着層に埋め込まれた状態になる。この代わりに、でもよい。断された端部は、チップの表面上の誘電体保護層(図示せず)に接触していてもよい。

## [ 0 0 3 2 ]

異なるユニットが、破断ステップの後、端子に接続されたブランチの異なるものを有する。例えば、図2に示す4ユニットアセンブリにおいて、最上ユニット56Aは、セット22A~22Dの端子22Aにのみ接続されたマルチブランチトレース38Aの共通セクション46Aを有し、セット22E~22Hの端子22Eにのみ接続されたトレース38Eの共通セクション46Eを有していてもよい。次のユニット56Bにおいて、共通セクション46Eが端子22Fに接続される。次のユニット56Cは、端子22Cおよび22Gのそれぞれに接続されたセクション46Aおよび46Eを有するのに対して、最下ユニット56Dは、端子22Dおよび22Hに接続された同一の共通セクションを有する。

10

20

30

30

40

50

[0033]

ユニットは、図2に示すように、上下に積層されたものである。各端子22は、はんだボ ール78を介して次の隣接ユニットの対応する端子に接続される。はんだボール78は、 さまざまなユニットの対応する端子を垂直方向の伝導性バスに接合する伝導性部品として 作用する。例えば、各ユニットの端子22J(図1)が、他のユニットの対応する端子2 2」と同一の垂直バス上に接続される。各はんだボールは、はんだマスク層74にある孔 を通る1つのユニットの端子と、そのユニットにあるパネル20の誘電体層にある孔28 を通る他のユニットの端子と接触する。最下ユニット56D以外の各ユニット上の熱伝達 層76(または、組み合わせられた熱伝達およびはんだマスク層、このような組み合わせ 層が用いられる場合に)は、積層体にある次の下側のユニットにあるチップの背面62と 密接に接触する。組み立て中に、はんだボールは、部分的または完全に溶解されるか、 リフロー接合」される。パネルのはんだマスク層74および誘電体層によって、リフロー 動作中に、トレース38の長さに沿ったはんだの広がりが防止される。密接な接触を確保 するために、組み立てプロセス中に熱伝達層76を一時的に軟化させてもよい。この代わ り に 、 硬 化 性 エ ポ キ シ の よ う に 、 最 初 は 軟 ら か く ま た は 流 動 可 能 な 材 料 か ら 熱 伝 達 層 が 形 成される場合には、次の下側のアセンブリのチップと密接に接触させた後に、組み立て中 に熱伝達層を硬化させてもよい。

[0034]

積層体の組み立て前に、個々のユニットは、端子の位置に対応するコンタクトを有するテストソケットにおいてテストすることができる。典型的に、はんだボールは、各ユニットの端子に接合されることにより、パネルの第1の表面26から突出し、ユニットが適所にあるはんだボールを用いてテストされる。例えば、テストソケットは、はんだボールを係合するようにされた開口を有していてもよい。ユニットのすべてが同一のパターンの端子およびはんだボールを有するため、単一のテストソケットは、ユニットのすべてをテストするために使用することができる。

[0035]

その結果として得られるパッケージを、従来の表面実装技術を用いて、回路基板に組み立てることができる。特に、最下ユニット56Dのはんだボール78を、図2に示す回路板82のコンタクトパッド80とでできる。したが態にはいることができる。した状態に対した状態にされる。最下ユニット56Dの熱伝達層76は、例えば、大きな熱パッケージの一路といる。最下ユニット56Dの熱伝達層76は、例えば、次かケージの一部といると接触した状態にされていてもよい。金属板86が、パッケージの一部といてもよい。この金属板86が設けられていてもよい。はんだボールがコンタクトパッド84にリフロー接合されるように、会に金属板がパッド84にリフロー接合されるように、金属板またはデッケー接がはのであった。この代わりに、最下ユニットの熱伝達層が省略されていてもよい。

[0036]

完成したパッケージには多数の利点がある。上述したように、異なるユニットにあるチップのセレクトコンタクトは、異なるセレクト端子に接続されることにより、異なる垂直方向バスに接続される。これらのバスに関連付けられた回路基板のコンタクトパッドに選択信号をルート決定することによって、1つのみのユニットのチップにあるセレクトコンタクトに選択信号を適用することができる。相互接続されたはんだパッドによって形成された垂直方向バスは、非常に短く、低電気インピーダンスを備える。また、トレースは、比較的に低いインピーダンスの経路を与える。典型的なトレースは、約5ナノヘンリー以下のインダクタンスを有する。さらに、回路基板のコンタクトパッドとパッケージにあるのコンタクトとの間の信号伝播遅延とほぼ同じである。ユニットは、片

30

40

50

側のみに伝導性の機構を有する「単一金属(single-metal)」回路パネルを用いて、経済的に作製することができる。パッケージ全体の高さは、個々のチップの厚みによって部分的に決定される高さを有する。一例にすぎないが、各々が約125ミクロンの厚みのチップを有する4つのユニットを組み込んだ1つのパッケージの全高は、約1.5mmである

## [0037]

パッケージの全厚が小さい理由は、積層体にある隣接するチップ間の間隔を決定するチップ以外の部品の厚みが部分的に小さいことによる。上述したように、このようなユニットのチップに位置合わせされた各ユニットの中央領域内に、ユニットは、接着層68とリードまたはトレース38と熱伝達層またははんだマスク層とを含み、任意選択的に誘電体とリードを形成する金属との間のさらなる接着層のみを含むことが望ましい。隣接するユニットの対応する機構間の距離 d、例えば、ユニット56Aにおける誘電体層20の第2の表面30と、ユニット56Bにおける誘電体層の対応する表面との間の距離 d は、これらの層間に配置されたチップ58Bの厚み t と、各ユニットの中央部分を構成する前述した層の総計厚みとを合計したものに等しい。最も好ましくは、隣接するユニット間の距離 d は、チップの厚み t と約250μm以下、より好ましくは約200μm以下の厚みを合計したものに等しい。最小の高さを備えるようにさまざまな層が選択される場合には、さらに小さな距離 d を達成することができる。

#### [0038]

熱 伝 達 層 ま た は 組 み 合 わ せ た は ん だ マ ス ク 層 お よ び 熱 伝 達 層 が 実 質 的 に 平 坦 で あ る た め 、 チップの背面と良好に密接した接触が可能となる。これにより、全高を低くすることと、 ユニット間の熱伝達を良好にすることとの両方が達成される。積層体の中央にあるユニッ トのチップに広がる熱は、積層体の上部または底部を介して、積層体の上部または底部か ら、環境への熱伝達、例えば、回路基板82または周囲大気に隣接するユニットへの熱伝 達によって消失させることができる。良好な熱伝達を確保して最小の全高を与えるために 、各ユニットの中央領域が、積層およびリフロー動作中に、次の隣接するユニットにある チップと密接して接触するようにされる。また、はんだボールの表面張力効果によって与 えられる自己整合作用を用いて、積層およびリフロープロセス中に、水平方向に互いにユ ニットが位置合わせされることを確保することも望まれる。はんだボールの高さが、リフ ロー接合前に約10~15μmの公称間隔 (nominal clearance) を備えるように選択さ れた場合には、リフロー接合されると、はんだボールが互いにユニットを最初に位置合わ せし、加えて、はんだがユニットを互いに隣接させるように崩壊することになる。この代 わりにまたは加えて、確実に隣接するようにリフロー中にユニットを押圧してもよく、適 切 な 取 り 付 け ま た は ロ ボ ッ ト シ ス テ ム 、 例 え ば 、 ロ ボ ッ ト 視 覚 構 成 部 品 ( robot ic vision component)を装備したシステムを用いて、ユニットを互いに位置合わせしてもよい。

## [0039]

上述した組み立て方法の一変形例において、ユニットは、マルチブランチトレースのプランチ50を破断することなく作製することができる。これらのユニットは、互いにおが可能を基板との組み立て前に交換可能な部品として取り扱いおより破断される。ブランチは、望ましくは、組み立て直前に、別々の動作により破断される。だがって、ブランチを選択的に切断するステップは、ユニットを積層である。ブランチを選択的に切断するステップは、ユニットを積層である。カードの接続セクションを接合するのに必要とされる同じ程度を要求せずで、ストップとして1つのみのタイプのユニットを取り扱ってストックすることができる。によって、取り扱いおよび分配が単純化される。したがフェンチを破断して全によって、取り扱いおよび分配が単純化される。がカースと端子とによって、東明細書において使用する場合、「同一」という用語は、任意の製造された物品に必ず生じる各ユニットのばらつきにかかわらず、チップとトレースと端子との公称の構成をさす。

20

30

50

[0040]

積層およびブランチ破断の動作は、望ましくは、パッケージングされた半導体チップと、モジュールと、他の構成部品とを回路基板に取り付けるようにされた生産工場において実行され、当業界において「基板充填(board stuffing)」と一般に呼ばれている動作である。表面実装技術を用いる基板充填工場は、構成部品を取り扱い、回路基板に配置するための設備と、はんだを溶融するか、または構成部品と回路基板のコンタクトとの間の接合材料を活性化させるために、構成部品が載せられた回路基板を一時的に加熱するためのリフロー設備とを一般に装備している。積層動作は、回路パネルに部品を取り付けるために使用される実質的に同じ技術および手順を用いて、実行することができる。ブランチを破断する最初の追加動作のみしか要求されない。

[0041]

さらなる別の変形例において、積層動作は、基板への積層体の組み立てと同時に実行することができる。すなわち、個々のユニットは、回路基板上に上下に積層され、基板上の適所に一時的に保持されて、例えば、一時的なクランプ取り付け、重力、ユニット間の接着、端子の融剤、またはこれらのいくつかの組み合わせによって保持することができる。このような組み立て状況において、最下ユニット 5 6 d に関連付けられたはんだボールまたは伝導性部品 7 8 は、回路基板のコンタクトパッドの上にあり、外側ユニットのはんだボールは、積層体にある次の下側のユニットの端子の上にある。積層後、全積層体および回路パネルは、最下はんだボールを回路基板のコンタクトパッドに融合し、他のユニットのはんだボールを隣接するユニットの端子に融合できるリフロー動作を受ける。このリフロー動作は、他の構成部品を基板に取り付けるために使用されるリフロー動作とともに実行されうる。

[0042]

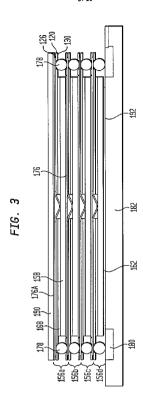

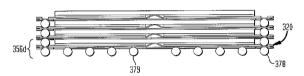

図3に示す本発明のさらなる実施形態によるパッケージでは図1および図2の実施形態に類似しているが、異なる点は、ユニット156が各ユニットに組み込まれたチップ158がユニットの最下部の方へ配置されるのに対して、各ユニットの回路パネルまたはパッケージ部品120がそのユニットのチップの上方に配置されるように逆転していることである。また、各ユニットに関連付けられたはんだボール178は、パネルの第1またはチップと離れた側126上ではなく、パネルの第2またはチップに面した側130上に配置される。別の方法で述べると、この構成において、はんだボールは、チップと同じパネルの側に配置される。この構成によって、完成したアセンブリの全高さが低くなる。

[0043]

最上ユニットの熱伝達層176Aを接触させて、最上ユニット156Aに熱スプレッダ1 9 0 が取り付けられる。金属または他の熱伝導性材料から熱スプレッダ 1 9 0 を形成する ことができ、熱を周囲へと逃がすためのリブやフィン(図示せず)等の機構を熱スプレッ ダ 1 9 0 に組み込むことができる。また、熱スプレッダは、スプレッダと回路基板との間 の 熱 伝 達 を 促 進 す る た め に 、 回 路 基 板 1 8 2 の 方 へ パ ッ ケ ー ジ の エ ッ ジ に 隣 接 し て 下 向 き に延びる壁を有してもよい。最上ユニット156Aの第1またはチップから離れた表面1 26上に設けられた熱伝達層176は、このようなユニットにあるパネル120の表面お よびトレース156と密接に適合する。上述したように、この層は、最上ユニットのトレ ースとスプレッダとの間に電気的絶縁を維持するための誘電体層でありうる。この代わり にまたは加えて、最上ユニットのはんだマスク層174は、トレースに電気的絶縁を与え るために、トレースにわたってパネルの中央領域内に広がっていてもよい。他のユニット のパネルの中央領域にわたって、同様の熱伝導層176が与えられる。この場合にも、は んだマスク層または他の誘電体層は、熱伝導層が導電性のものであれば、トレースを絶縁 するために使用することができる。図1および図2に関して上述したように、これらの熱 伝導層は、積層体におけるさまざまなユニット間の密接な接触および熱伝達を促進する。 これによって、積層体の内側ユニットからの熱放出が高められる。

[0044]

チップと同じテープ側上に、はんだボール178が設けられる場合には、はんだボールは

30

40

50

、2001年8月22日に出願され、同時係属中の本願と同一の譲受人に譲渡された米国特許出願第60/314,042号(以下、「'042特許出願」とよぶ)と、同日の優先日を主張したPCT国際特許出願第PCT/US02/26805号とに開示されているような補強層(図示せず)によって、すべてまたは部分的に取り囲まれてよく、これらの内容全体を引用することにより本願明細書の一部をなすものとする。'042特許出願に開示されているように、流動可能な材料、例えば、チップとユニットのパネル間に注入された接着層168を形成するエポキシまたはカプセル封入材等のエポキシまたはカプセル封入材によって、補強層を形成することができる。補強層は、組み立て中に取り扱いやすいように、補強層がパネルを強化する場合には、パネルの周辺に向かって延びて、はんだボールを取り囲むことが望ましい。この層は、チップによって示される領域を越えて中央領域の外側に配置されるため、積層体の高さを増加させることはない。

[0045]

最下ユニット156Dにあるチップの背面162は、回路基板182の方に対面する。背面162は、回路基板に物理的に取り付けられて、チップの背面と基板との間に設けられた熱層192によって、回路基板とさらに密接な熱伝達状態になるよう配置されていてもよい。伝導性の充填剤を有するジェルもしくはグリースなどの熱伝導性材料から、または、最下ユニットのはんだボールがリフロー接合されて、端子を回路基板のコンタクトパッド180に取り付けるときにリフロー接合されるはんだから、このような熱伝達層を形成してもよい。

[0046]

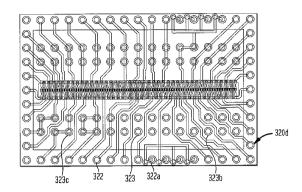

図4および図5の実施形態は、図1および図2を参照して上述した実施形態に類似しているが、異なる点は、最下ユニットのパネルまたはチップキャリヤ320に、追加の「ダミー」端子323が設けられていることである。この場合にも、端子およびトレースののすべては、単一の金属層の部品として設けられている。ダミー端子323は、最下ユニット356Dにあるパネル320Dの中央領域にわたって延びるアレイに配置される。また周のパネルは、図1を参照して上述したセレクト端子および非セレクト端子に対応、まるのパネルは、図1を参照して上述したセレクト端子上に設けられるのと同様に、対応ではが一ル379がダミー端子上に設けられる。これらのはんだボールは、パッケージが回路を板上に実装されるときに、最下ユニットと回路基板との間の熱導体として見がが回路を入れていてもよい。この構成において、トレース338は、ダミー端子の周りにルーティングされる。この代わりにまたは加えて、参照番号323Cに示すように、ダミー端子トレースに接続することができる。これによって、ダミー端子が占める領域を通るトレースのルーティングが可能になるため、パネル上のトレースのレイアウトが単純化される

[0047]

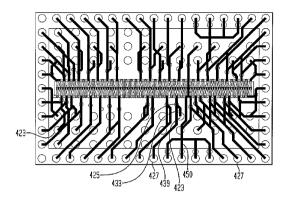

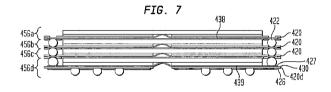

図6および図7に示す実施形態において、最下ユニット456Dを除くすべてのユニット456のパネル420は、図1および図2を参照して上述したパネルと同一のものである。最下ユニットのパネル420Dは、パネルの第2またはチップに対面する側上の金属要素層(layer of metallic feature)430と、第1またはチップと離れた側上の別の金属要素層とを有する、いわゆる、「2金属(two metal)」パネルである。チップに対面する側430上の金属要素層は、積層体にある他のパネルの端子422およびトレース438に対応する、周辺端子425およびトレース439を含む。これらの端子およびトレース438に対応する、周辺端子425およびトレース439を含む。これらの端子およびトレースを含む。パネルの第1またはチップと離れた側426上の金属要素層は、パネルの中央領域上に延びる直線グリッドに配置された基板接続端子423のアレイを含む。また、この金属層は、基板接続端子423からビア(via)425へと延びる追加のトレース433を含む。ビア425は、パネルを通って延びる孔と、これらの孔を通って延びるビアライナ(via liner)などの金属構造(metallic structure)とを含む。さらなるトレース433が、ビア内の金属要素によって、トレース439に接続される。回路基板にパッケージが実装される

30

50

と、基板接続端子423は、回路基板のコンタクトパッドに接続されるので、トレース439および周辺端子425を回路基板に接続する。これによって、周辺端子425および他のパネルの対応する端子422から形成された垂直バスと回路基板のコンタクトパッドとが接続される。このアプローチの一変形例において、マルチブランチトレースの各ブランチ450に別のビア425を設けて、別の相互接続トレース433と基板接続端子423とにリンクしてもよい。

[0048]

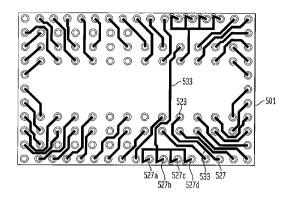

図8および図9の実施形態は、ユニット556のすべてにおいて、図1および図2を参照 して上述したパネルと同一のパネル520を用いる。しかしながら、端子522D、55 6 D は、回路パネルに直接接続されず、したがって、このユニットの端子には、下向きに 突出するはんだボールが設けられない。さらなる回路パネルまたはトランスレータ501 は、パネル520Dのチップから離れた表面または第1の表面の上にある。トランスレー タ は 、 図 6 お よ び 図 7 を 参 照 し て 上 述 し た 基 板 接 続 端 子 4 2 3 の パ タ ー ン に 類 似 し た グ リ ッドのようなパターンに配置された基板接続端子523を有する。また、トランスレータ は、さまざまなユニットのパネル上にある端子522のパターンに対応したパターンにあ る周辺端子527と、接続端子523および周辺端子527を相互接続する接続端子53 3 とを有する。トランスレータの周辺端子が周辺端子 5 2 2 D と整列されるように、トラ ンスレータは最下ユニットのパネルに並置される。したがって、さまざまなパネル520 上の整列された周辺端子の各セットによって規定された各垂直方向バスが、トランスレー タの1つの周辺端子527に接続されるので、回路基板上の1つのコンタクトパッドと電 気的に接続される。この構成により、単一の金属部品のみを有する回路基板上に実装する ための標準的またはグリッドのような端子パターンを有する構造を作製することができる ようになる。次の下側のユニットのはんだボール578がリフロー接合されるときに、最 下ユニットの端子522Dをトランスレータの周辺端子527にはんだ接合してもよい。 一変形例において、トランスレータは、さまざまなユニット上のセレクト端子と関連付け られたバスに最終的に接続される周辺端子 5 2 7 A ~ 5 2 7 D に関連付けられた別の基板 接続端子523への別の接続を含みうる。これにより、セレクト端子に接続された各バス が、回路基板上の固有のコンタクトパッドに接続されることになる。

[0049]

[ 0 0 5 0 ]

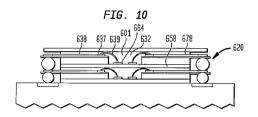

図 1 0 に示すパッケージは図 3 に示すパッケージに類似しているが、異なる点は、パネル6 2 0 のトレース 6 3 8 がチップ 6 5 8 上のコンタクト 6 6 4 に接合するための一体形成された接続セクションを有さないことである。その代わりに、トレースは、ボンドウィンドウ 6 3 2 に隣接したボンディングパッド 6 3 7 で終端する。これらのボンディングパッドとチップのコンタクト 6 6 4 との間には、ワイヤボンド 6 3 9 が設けられる。また、図

20

30

40

50

10のパッケージは、4つのユニットではなく2つのユニットしか含まない。前述した構造の任意のものに対して、より多くの数および奇数の数のユニットを使用することもできる。また、ワイヤ接合されたユニットは逆向きに用いられることができる、すなわち、図1および図2を参照して上述したように、各ユニットのチップはユニットのパネルの上方に配置される。そして、カプセル封入材601がワイヤボンドを被覆する。ユニットの残りの上にある熱伝導性の層678とエンドキャップを一体にすることができる。

[0051]

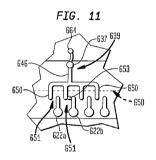

さらなる変形例(図11)において、マルチブランチトレース639は、チップコンタク ト664へ接続するようにされた共通のセクション646を有する。したがって、共通セ ク シ ョ ン は 、 コ ン タ ク ト へ の ワ イ ヤ ボ ン ド 接 続 と と も に 使 用 す る た め の ボ ン デ ィ ン グ パ ッ ド 6 3 7 を有するか、または、コンタクトに直接接合することができる接続セクションを 有してもよい。トレースのブランチ650は、最初に作製されるとき、共通セクション6 46からさまざまなセレクト端子622への破断されていない連続経路に延びていない。 むしろ、各ブランチは、ギャップ651とともに最初に作製される。例えば、1つのブラ ン チ の ギ ャ ッ プ 6 5 1 に わ た っ て 短 い ワ イ ヤ ボ ン ド 6 5 3 を 適 用 す る こ と に よ っ て 、 こ れ ら の ギ ャ ッ プ を 選 択 的 に 塞 ぐ こ と が で き る 。 追 加 の ワ イ ヤ ボ ン ド が さ ら な る 複 雑 性 お よ び インピーダンスを導入して周囲のパネルの平面の上方にあってもよいので、この実施形態 はあまり好ましくない。望ましくは、(図11の破線で示す)チップ658によって占め られる領域の外側にある回路パネルの周辺領域にブランチのギャップが配置されることに よって、ギャップにわたって延びるワイヤボンド653は、チップによって占められる領 域の外側にあるようにする。したがって、1つのユニットにある突出ワイヤボンドとこの ような突出ワイヤボンドにわたって任意に適用されうるカプセル封入材とが、このユニッ トにあるチップと並んで垂直方向にまたは次の隣接するユニットにチップに沿って突出し てもよいため、積層アセンブリの全高を増加させることがない。

[0052]

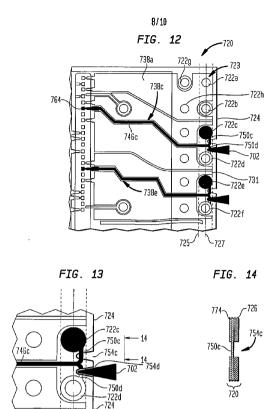

本発明のさらなる実施形態によるユニット(図12)は、上述した部品に一般的に類似し、上側に配置され多数のリード738に接続された多数の端子722を有する回路パネルまたは誘電体部品720を含む。端子は、回路パネルの第1のエッジ724に隣接して延びる端子722A~722Fを組み込む第1の外側の列723を含む。この端子の列は、内側の境界を規定する。端子722は、例えば、エッジ724からさらに離れて配置された端子722Gおよび722Hなどの追加の端子とともに、回路パネルの他の部品上の他の端子(図示せず)とを含みうる。第1の外側の列723は、回路パネルの第1のエッジ724から最も離れた端子のエッジにある内側の境界725と、中心線726と、エッジ724に最も近いエッジにある外側の境界731とを規定する。

[0053]

端子722Cおよび722Dは、チップセレクトコンタクト764へ接続するようにされた共通セクション746Cとともに、共通セクションに接続されたブランチ750Cおよび750Dを有するマルチブランチリード738Cに関連付けられたチップセレクト端子70セットを形成する。ブランチ750Dは、共通セクションをチップセレクト端子722Lに接続するのに対して、ブランチ750Dは、共通セクション746Cを別のチップフレクト端子722Dに接続する。図13に最良に示すように、ブランチ750Cおよ、ブランチは、約1mm以内、好ましくは第1のエッジ724の付近まで延びる。望ましくは、ブランチは、約1mm以内、好ましくは第1のエッジ724の約0.5mm以内であり、最10月は、第1のエッジの約200ミクロン以内まで延びる。ブランチで配置され、この列の外側境界731付近にあるこの列の中央線727から外向きに配置され、この列の外側境界731付近にあるこの列の中央線727から外向きに配置される。回路パネル720は、第1のエッジ724から内向きに延びるノッチの形をした切断開口754Cおよび754Dを有する。

[0054]

図14に最良に示すように、回路パネル720は、回路パネルの最下または内側表面を規

定する構造的な誘電体層726と、リードおよび端子ひいてはブランチ750Cを含む単一の金属要素層と、はんだマスク層774とを含む。ベース誘電体層726およびはんだマスク層774は、ブランチ750Cが切断開口をまたがるように、切断開口またはノッチ754において切断される。ノッチ754Cおよび754Dは、エッジ724からブランチ750Cおよび750Dの方へわずかにそれらを越えて内向きに延びる。ブランチがエッジの付近に配置されるため、ノッチは、エッジから回路パネル内まで遠くに延びている必要はない。望ましくは、ノッチは、パネル内に、約1.5mm未満、より望ましくは約1.0mm未満になるよう延びる。ブランチ750Dおよび切断開口またはノッチ754Dに、同じ構造が設けられる。

## [0055]

このようにして、ツールをノッチ内へと挿入し、例えば、(図12および図13の)パン チ 7 0 2 を ノッチ内へと挿入することによって、ブランチ 7 5 0 は、選択的に破断するこ とができる。回路パネルの平面に垂直な方向または平面に平行な方向にパンチを移動させ てもよい。パンチに密接に適合するような形状の開口を有する整合ダイを回路パネルの下 方に設けることができ、ダイと係合するようにノッチを通って下方にパンチを移動して、 プロセスにおいてブランチリードを破断させてもよい。 したがって、リード738Cの共 通セクション 7 4 6 C が、端子 7 2 2 C および 7 2 2 D のいずれかまたは両方に選択的に 接続されるか、またはいずれにも接続されないように、ブランチ750Cまたは750D を選択的に遮ることができる。さらなるマルチブランチリード738E(図12)は、チ ップセレクト端子722Eおよび722Fの同様の対と関連付けられ、ブランチの同様の 構造およびブランチに関連付けられた同様のノッチを有する。また、図12に示すように 、 例 え ば 、 リ ー ド 7 3 8 A 等 の リ ー ド の い く つ か が 、 2 つ 以 上 の 端 子 7 2 2 A お よ び 7 2 2 日に関連付けられ、これらの端子に永久的に接続される。また、リード7 3 8 A は、回 路パネル720上の著しく大きな領域を覆う広く平坦な構造である。さらに、端子のいく つかはリードに接続されない。例えば、端子の対称的なパターン、ひいては仕上げアセン ブリにある垂直方向導体の対称的な構造を与えるように、このような接続されていない端 子を設けてもよい。また、さまざまなユニットに加えて、アセンブリは、積層体の最上部 、または、実際には、積層体内の任意の場所に配置された追加の電気的部品を含みうる。 接続されていない端子によって形成される追加の垂直方向導体は、これらの部品まで延び る追加の導体として作用することができる。

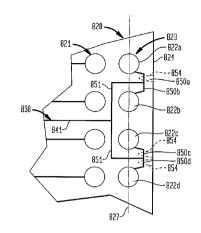

## [0056]

図15に部分的に示すユニットは、第1のエッジ824と、エッジ824に沿って、この ようなエッジに平行に延びる外側端子823の第1の列とを有するとともに、第1の外側 の列の内側に配置された端子の追加の列821とを有する回路パネル820を有する。マ ルチブランチリード838は、共通セクション846と、セレクト端子822A、822 B、 8 2 2 C、 および 8 2 2 D にそれぞれ延びるブランチ 8 5 0 A、 8 5 0 B、 8 5 0 C 、 お よ び 8 5 0 D と を 有 す る 。 ブ ラ ン チ 8 5 0 は 、 中 間 セ ク シ ョ ン 8 5 1 に よ っ て 共 通 セ クション 8 4 6 に接続される。このような 1 つの中間セクションはブランチ 8 5 0 A およ び850Bと共通セクション846に接続されるのに対し、他の中間セクションはブラン チ 8 5 0 C お よ び 8 5 0 D を 共 通 セ ク ショ ン に 接 続 さ れ る 。 こ の 場 合 も 、 ブ ラ ン チ 8 5 0 は、端子の第1の外側の列823の中央線827を越えて外向きにすべてまたは部分的に 延びる。しかしながら、最初に製造されるとき、および、チップとともに半仕上げユニッ トにおいて接続されるときには、回路パネルは切断開口を有していない。その代わりに、 (図15の破線で示す)ノッチ854を形成し、このようなノッチ形成中にブランチを破 断することによって、ブランチ850が選択的に切断される。例えば、ブランチが切断さ れる予定のノッチ854を形成するが他の位置にノッチを形成しないように、パンチによ って選択的に回路パネルが切断されてもよい。例えば、図15に示すパターンにノッチ8 54が形成されれば、ブランチ850Bは切断されていない状態に維持され、したがって . セレクト端子822Bはリード838の共通部分846に接続された状態であるが、残 りのセレクト端子は切断されることになる。上述したように、積層前に、そして最も望ま

10

20

30

40

30

40

50

しくは、例えば、回路基板スタッフィング工場において積層が実行される場所と同じ工場 において、この動作が実行されることが望ましい。

#### [0057]

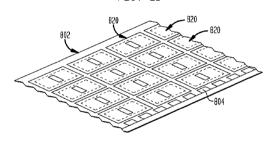

図16に示すように、大きなシートの部分として、多数のユニットを与えることができる 。したがって、個々のユニットの回路パネルを形成する誘電体層の1つ以上は、シートま たはテープ802の全体を通って延びる連続的または半連続的な誘電体層の部分を形成す る。シートまたはテープには、スプロケット孔804などの従来の位置合わせ機構を設け てもよい。明確に示すために、図16に、個々のユニット820を形成する回路パネルの 境界を描いているが、この段階では、隣接するユニット間に物理的な境界画定がないこと を認識されたい。ユニットをシート802に接続したまま、個々のユニットの回路パネル に半導体チップを組み立てることによって、上述したようにユニットが組み立てられる。 この段階では、ユニットのすべては互いに実質的に同一である。これらの同一のユニット のアセンブリは、シートの形での取り扱いおよびストックが可能である。個々のユニット は、望ましくは、積層動作の直前に、シートから切り離される。切断動作中に、そのユニ ットのノッチの所望のパターンに対応するパターンで(図 1 5 の)ノッチ 8 5 4 が各ユニ ットに形成される。異なるユニットに形成されたノッチは、異なるパターンで形成される 。例えば、各ユニットを隣接するユニットから切断するように矩形状のブレード部分80 8を有し、個々のノッチを切断し、個々のブランチ850(図15)を切り離すようにさ れた歯810をダイ806は有する。歯810は、図15に示すパターンにブランチを切 り離すようにされる。したがって、ブランチ850Aを切り離すように歯810Aが設け られ、ブランチ 8 5 0 C および 8 5 0 D を切り離すように、同様の歯 8 1 0 C および 8 1 0 D が 設けられる。しかしながら、ブランチ 8 0 5 B に対応する場所 8 1 2 には、歯が設 けられないため、このブランチは切り離されない。テープから他のユニットを切断するた めに使用されるダイは、異なる歯パターンを有する。テープからユニットを切り離すと同 時に、使用されるブランチを切り離すために、他の構成を使用することができる。個々の ユニットをテープから切断するために、さらに、ブランチを切り離すために、例えば、水 噴射、レーザ、または他の切断デバイスを使用してもよい。上述した他の実施形態にも、 同様の構成を使用することができる。例えば、ブランチに関連付けられた予め形成された 切断開口を有する構造において、ユニットをシートから切り離すために使用されるツール は、このような切断開口内に通り、ブランチを切り離すようにされた突出を有してよい。 さらなる代替において、さまざまなユニットが、望ましくは、個々のユニットをシートか ら切り離す直前に、さまざまなユニットをシートに接続されたまま実行することができる 。任意選択的に、細長いテープの形でシートが与えられてもよい。

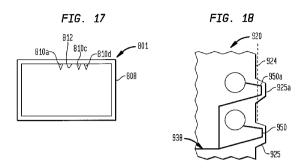

## [0058]

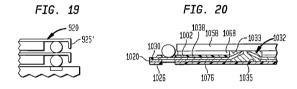

さらなる別の変形例において、回路パネル920は、このようなエッジから外向きに延びる突出部925を有するエッジ924を有する。マルチブランチリード938は、突出部に外向きに延びるブランチ950を有する。個々のブランチは、1つ以上の突出部を切り離すことによって、例えば、ブランチ950aを切断するように突出部925Aを切り離すことによって切断することができる。この動作は、突出部が取り付けられた状態にあるレセスを有するダイまたはブレードを用いて実行することができる。完成した積層アセンブリにおいて、残りの突出部925は、図19の参照番号925′に示すように、回路パネルの平面から屈曲することができるため、突出部は、アセンブリの水平方向の広がりを実質的に増すことがない。

## [0059]

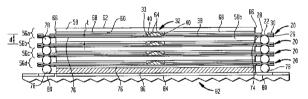

上述した特徴の多数の変形例および組み合わせは、本発明から逸脱することなく利用することができる。例えば、さまざまな回路パネルは、グラウンドまたはパワープレーンなどの追加の機構または追加のトレース層を含みうる。各パネルのトレースおよび他の伝導性機構は、チップから離れた第1の側ではなく、パネルの第2またはチップに面した側上に配置することができる。例えば、図20に示すように、誘電体層1020は、誘電体層1020の第2またはチップに面した側1030上にトレース1038を有する。はんだマ

30

40

50

ス ク 層 1 0 7 6 に 加 え て 、 第 2 の 側 1 0 3 0 上 の ト レ ー ス に わ た っ て 追 加 の は ん だ マ ス ク 層1002を設けてもよく、これは、ユニットの熱伝達または熱層としても作用する。こ の場合には、開口内1034内のカプセル封入材は、誘電体層の第1の表面1026と同 一平面上か、またはこのような表面に対してくぼみが作られた表面1035を有するため 、 第 1 の 表 面 は 実 質 的 に 平 坦 で あ る 。 一 変 形 例 に お い て 、 第 1 の 表 面 上 の は ん だ マ ス ク 層 1 0 7 6 を、カプセル封入材を導入した後に除去してもよい。この場合には、誘電体層 1 0 2 0 は、ユニットの熱または熱伝達層として作用し、積層体における次の下側のチップ と隣接する。さらなる変形例において、誘電体層の第2またはチップに面する側上にある はんだマスク層1002を、省略して、接着層1068と一体にしてもよい。また、各ユ ニットは 2 つ以上のチップを含みうる。さまざまなユニットに含まれたチップは、メモリ チップや、例えば、DRAM、フラッシュ、ROM、PROM、またはEEPROMチッ プでありうる。また、本発明は、例えば、プロセッサまたは特定用途向けの集積回路(A SIC)等のほかのチップをパッケージングする際に用いることもできる。また、「セレ クト」端子は、メモリアレイに一般に使用される「チップセレクト」などの信号を伝達す る必要はなく、すなわち、積層体内の1以上の特定のチップにルート決定されることが望 ましい任意の信号を伝達することができる。熱拡張による応力を緩和するために、各ユニ ットのユニット端子がそのユニットのチップに対して動かせるよう接着層とリードとパネ ルとを配設させてもよい。また、熱伝達層によって、隣接するユニットが相対的に移動可 能であってもよい。さらに、積層アセンブリは、実質的に上述したようなユニットに加え て、1つ以上の非同一ユニットを含みうる。例えば、積層体の異なるユニットは、異なる チップを含みうる。さらなる別の変形例において、各ユニットはある方向に配置されたチ ップを有する構造において上述した機構が使用可能であり、チップの背面はこのようなユ ニットの誘電体層に隣接し、コンタクト担持前面は誘電体層から離れて対面する。このよ うな実施形態において、コンタクトは、ワイヤボンドまたは他の導体によってトレースに 接続することができる。このような実施形態において、各チップの前面または前面の上に あるカプセル封入材の層が、次の隣接するユニットの誘電体層に隣接していてもよい。

[0060]

上述した実施形態において、さまざまなユニットを互いに接続し、垂直方向の導体を形成する伝導性部品は、従来のはんだボールである。この代わりに、他の伝導性部品を用いてもよい。例えば、いわゆる「ソリッドコアはんだボール(solid core solder ball)」を使用することができる。ソリッドコアはんだボールは、融点が比較的に高い材料から形成されたコアと、融点温度がコアの融点温度よりも低いはんだとを含む。さらなる他の伝導性部品を、伝導性ポリマー組成の集合体から形成することができる。

[0061]

上述した特徴の上記および他の変形例および組み合わせを利用できるため、好適な実施形態の上述した記載は、本発明を限定するものではなく、例示するものとして解されるべきものである。

【図面の簡単な説明】

[0062]

- 【図1】本発明の1つの実施形態において使用される回路パネルの平面図である。

- 【図2】図1の回路パネルを用いた積層パッケージの立面図である。

- 【図3】回路基板と組み合わせた本発明のさらなる実施形態による積層パッケージの断面図である。

- 【図4】図1に類似しているが、本発明のさらなる実施形態による回路パネルを示す図である。

- 【 図 5 】 図 2 に類似しているが、 図 4 の回路パネルを用いた積層パッケージを示す図である。

- 【図 6 】本発明のさらなる別の実施形態において使用される回路パネルの平面図である。

- 【図7】図6の回路パネルを用いて作製された積層パッケージの断面図である。

- 【図8】本発明のさらなる実施形態において使用されるトランスレーションパネルの平面

図である。

- 【図9】図8のトランスレーションパネルを用いたパッケージの断面図である。

- 【図10】本発明のさらなる実施形態による積層パッケージの断面図である。

- 【図11】本発明の別の実施形態によるパッケージ部品の一部分の部分図である。

- 【図12】本発明のさらなる実施形態によるパッケージの部分平面図である。

- 【図13】図12に示すユニットを拡大した部分平面図である。

- 【図14】図13の線14・14に沿って切り取った部分断面立面図である。

- 【図15】本発明のさらなる別の実施形態による回路パネルの部分平面図である。

- 【図16】図15の回路パネルを用いて形成された複数のユニットを含む仕掛りあるいは 製造過程中の集合体の部分斜視図である。

- 【図17】図15および図16の回路パネルおよびユニットとともに使用可能な切断ツールの立面図である。

- 【図18】本発明のさらなる別の実施形態による回路パネルの部分平面図である。

- 【図19】図18の回路パネルから形成されたアセンブリの部分立面図である。

- 【図20】本発明のさらなる別の実施形態によるユニットの部分断面図である。

## 【国際公開パンフレット】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

# (43) International Publication Date 17 April 2003 (17.04.2003)

**PCT**

WO 03/032370 A2

| (51) | International Patent Classification : | HVIL           | (81) |

|------|---------------------------------------|----------------|------|

| (21) | International Application Number:     | PCT/US02/32251 |      |

(22) International Filing Date: 9 October 2002 (09.10.2002) (25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 60/328,038 9 October 2001 (09.10.2001) US (71) Applicant: TESSERA, INC. [US/US]; 3099 Orchard Drive, San Jose, CA 95134 (US).

(72) Inventors: PFLUGHAUPT, L., Elliott; 252 Montclair Road, Los Gatos, CA 95023 (US). GIBSON, David; 910 Alwater Road, Lake Cowego, OR 97034 (US), KIM, Young: 21067 Red Fir Court, Cupertino, CA 95014 (US). MITCHELL, Craig, S.; 1530 Ramita Court, San Jose, CA 95128 (US).

(74) Agents: MILLET, Marcus, J. et al.; Lemer, David, Littenberg, Krumholz & Mentlik, LLP, 600 South Avenue West, Westfield, NJ 07090 (US).

To two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Grantle.

Designated States (national): All, AG, Al., AM, AT, All, AZ, BA, BB, BG, BR, BY, BZ, CA, CII, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GII, GM, IIR, III, DI, II, IN, IS, PK, EK, GK, PK, RZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PI., PT, RO, RU, SD, SE, SG, SI, SK, SI, TI, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, ST, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RK, TJ, TLM), European patent (AI, BL, BG, CH, CY, CZ, DL, DK, EL, ES, J4, JR, GB, GR, III, TT, LU, MC, NI, PT, SE, SK, TR), CAPT patent (BT, BL, CP, GC, L, CM, GA, GN, GQ, GW, MI., MR, NR, SN, TD, TG).

#### Published:

ushout international search report and to be republished upon receipt of that report

ance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: STACKED PACKAGES

**A**2

(57) Abstract: A stacked chip assembly includes individual units (56) having chips (58) mounted on dielectric layers (20) and traces (38) on the dielectric layers interconnecting the contacts of the chips with terminals (22) disposed in peripheral regions of the dielectric layers. At least some of the traces (38a, 38e) are multi-branched traces which connect chip select contacts to chip select terminals. The units are stacked one above the other with corresponding terminals of the different units being connected to one another by solder balls (78) or other conductive elements so as to form vertical buses. Prior to stacking, the multi-branched traced of the individual units are selectively interrupted, as by breking the individual arbranches (90), so as to leave disect contact of 0 chips in different units connected to different chips select terminals and thereby connect these chips to different vertical buses. The individual units desirably are thin and directly abut one another so as to provide a low-height assembly with good heat transfer from chips within the stack.

PCT/US02/32251

#### STACKED PACKAGES

BACKGROUND ART

Semiconductor chips typically are thin and flat, with relatively large front and rear surfaces and small edge The chips have contacts on their front surfaces. Typically, chips are provided as packaged chips having terminals suitable for connection to an external circuit. Packaged chips typically are also in the form of flat bodies. Ordinarily, the packaged chips are arranged in an array on a 10 surface of a circuit board. The circuit board has electrical conductors, normally referred to as "traces" extending in horizontal directions parallel to the surface of the circuit board and also has contact pads or other electrically conductive elements connected to the traces. The packaged 15 chips are mounted with their terminal-bearing faces confronting the surface of the circuit board and the terminals on each packaged chip are electrically connected to the contact pads of the circuit board.

Memory chips typically are mounted in this manner. An 20 unpackaged memory chip typically has numerous data contacts and one or a few select contacts. The chip is arranged to ignore data or commands appearing at the data terminals unless the appropriate signals are applied to the select contact or contacts. A conventional packaged memory chip has data 25 terminals connected to the data contacts and has select terminals connected to the select contacts. In a conventional system, numerous identical packaged memory chips can be connected in an array with the corresponding data terminals of the various packaged chips connected to common traces and with 30 the select terminals of the various chips connected to unique conductors, so that each conductor is associated with one, and only one, chip. Data can be written onto an individual chip by supplying the data on the common traces and by applying a selection signal on the unique trace associated with the 35 particular chip where the data is to be written. The remaining

PCT/US02/32251

chips will ignore the data. The reverse process is employed to read data from a particular chip. Such a circuit can be built readily using the conventional horizontal chip array and using identical chip packages for all of the chips in the array.

In the conventional arrangement, the theoretical minimum area of the circuit board is equal to the aggregate areas of all of the terminal-bearing surfaces of the individual chip packages. In practice, the circuit board must be somewhat larger than this theoretical minimum. The traces on the circuit board typically have significant length and impedance so that appreciable time is required for propagation of signals along the traces. This limits the speed of operation of the circuit.

Various approaches have been proposed for alleviating 15 these drawbacks. One such approach is to "stack" plural chips one above the other in a common package. The package itself has vertically-extending conductors that are connected to the contact pads of the circuit board. The individual chips within the package are connected to these vertically-extending 20 conductors. Because the thickness of a chip is substantially smaller than its horizontal dimensions, the internal conductors can be shorter than the traces on a circuit board that would be required to connect the same number of chips in a conventional arrangement. Examples of stacked packages are shown, for 25 example, in U.S. Patents 5,861,666; 5,198,888; 4,956,694; 6,072,233; and 6,268,649. The stacked packages shown in certain embodiments of these patents are made by providing individual units, each including a single chip and a package element having unit terminals. Within each unit, the contacts 30 of the chip are connected to the unit terminals. The units are stacked one atop the other. Unit terminals of each unit are connected to the corresponding unit terminals of other units. The connected unit terminals form vertical conductors of the stacked package, also referred to as buses.

PCT/US02/32251

However, providing a circuit with individual select connections in a stacked package introduces additional complexities. Because the vertical conductors extend through the terminals of the various units, the interconnections between the contacts of the chip and the unit terminals of each unit in the stack should be different in order to provide connections to unique vertical conductors. For example, in a four-chip stack having four vertical buses for carrying selection signals, the bottom unit may have a select contact of 10 its chip connected to a unit terminal that forms part of bus number 1; the next unit may have a corresponding select contact of its chip connected to a terminal that forms bus number 2; and so on. This need for customization of the units adds complexity to the manufacturing process. For example, U.S. 15 Patent 4,956,694 describes units having chip carriers with a set of intermediate terminals in each unit. These intermediate terminals are connected to the contacts on the chip and are also connected to the terminals of the unit. interconnections are made by wire bonds. The pattern of wire 20 bonds differs from unit to unit. This arrangement inherently requires a relatively large chip carrier, which adds to the cost and bulk of the package. Moreover, the manufacturer must handle and stock multiple different wire bonded units. Sugano et al., U.S. Patent 5,198,888, uses individualized chip 25 carriers in the various units. These chip carriers have leads defining different interconnect patterns for the select contacts and the associated terminals. This, again, adds to the cost and complexity of the manufacturing process. U.S. Patents 6,268,649 and 6,072,233 use customized units as well. 30 It would be desirable to reduce the cost and complexity associated with providing customized units in a stacked package.

It would also be desirable to provide a compact stacked package and to provide a stacked package with good heat 35 transfer from the chips within the stack to the external

PCT/US02/32251

environment as, for example, to the circuit board or to a heat spreader overlying the top of the package. Further, it would be desirable to provide such a package using readily-available equipment and using components that can be fabricated readily. 5 SUMMARY OF INVENTION

One aspect of the invention provides semiconductor chip assemblies incorporating a plurality of units. Each unit desirably includes a semiconductor chip having at least one select contact and a plurality of other contacts and also 10 includes a circuit panel having a plurality of chip select terminals and a plurality of other terminals, as well as traces extending on or in the panel. The traces are electrically connected between the contacts of the chip and the terminals. The trace electrically connected to each chip select contact of 15 the chip desirably is a multi-branched trace including a common section connected to the select contact of the chip and also including a plurality of branches connected to different ones of the chip select terminals on the circuit panel. In the assembly, desirably at least one branch, but less than all of 20 the branches of each such multi-branch trace, have an interruption therein so that the select contact is connected to less than all of the chip select terminals on the panel and most preferably so that each chip select contact is connected to only one chip select terminal of the panel in the unit. The 25 units are disposed one above the other in a stack of superposed units. The assembly further includes vertical conductors, each connecting the corresponding terminals of the units in the stack to one another so as to form a plurality of vertical buses. Due to the selective connections within individual 30 units provided by the multi-branch traces and interrupted branches, the chip select contacts of chips in different units are electrically connected to different ones of the vertical buses. This arrangement provides selective routing of chip select signals and other signals which must be conveyed to 35 individual chips. The remaining contacts on each chip are

PCT/US02/32251

connected in parallel with corresponding contacts on chips in other units so that signals can be conveyed to the remaining contacts of the various chips in parallel. This provides the required selective routing.

5 Most preferably, the chips, traces and terminals of different units in the stack are identical to one another, except that different ones of the units have different branches of their multi-branch traces interrupted so that different chip select contacts of different units are connected to different to terminals on the circuit panels of such units. Most preferably, the circuit panel of each unit includes a dielectric layer, desirably less than about 100 µm thick. The vertical spacing distance between corresponding features in adjacent ones of the units desirably is no more than about 250 µm and preferably no more than about 200 µm greater than the thickness of the chip in each unit. The assembly, thus, has a relatively low overall height.

The dielectric layer in each circuit panel may have a disconnection aperture or opening, and the interruptions in the 20 branches of the multi-branch traces may be formed at such disconnection apertures. The disconnection apertures can be formed in the dielectric layers when the units are manufactured or when the branches are interrupted, typically at a later stage in the process. In one arrangement, the circuit panel of 25 each unit has edges, and the disconnection apertures are provided in the form of notches extending inwardly from one or more of the edges. The terminals of such a unit may include an outer row disposed adjacent to an edge of the circuit panel and the branches of the multi-branch traces may have portions 30 extending outwardly to or beyond the outer row of terminals. In this instance, the notches need not extend inwardly beyond the outer row of terminals, so that the interruptions in the multi-branch leads can be formed readily.

A further aspect of the invention provides methods of 35 making a semiconductor chip assembly. A method according to

PCT/US02/32251

this aspect of the invention includes the step of providing a plurality of units. Here again, each unit desirably includes at least one semiconductor chip having at least one chip select contact and a plurality of other contacts and also includes a 5 circuit panel having chip select terminals, other terminals and traces extending on or in the panel connected to the terminals. As discussed above, at least one trace of each panel desirably is a multi-branch trace including a common section and plural branches connected to different ones of the chip select 10 terminals, and the contacts of the at least one chip in each unit desirably are connected to the traces of the circuit panel in that unit so that the chip select contacts are connected to the common sections of the multi-branch traces. The method according to this aspect of the invention desirably includes 15 the step of selectively interrupting the branches of the multibranch traces so that the common section of a multi-branch trace in each unit is connected to less than all of the chip select terminals of that unit. The method preferably includes the step of stacking the units and interconnecting terminals of 20 different units to one another to form vertical buses.

The selectively interrupting step desirably is performed so that the chip select terminals of chips in different units are connected to different ones of the vertical buses. Most preferably, prior to the step of selectively interrupting the multi-branch traces, the units are substantially identical to one another. The step of selectively interrupting the multi-branch traces may be performed at any time during or after formation of the units. In one arrangement, the step of providing the units includes connecting the chips to the traces 30 using a tool such as a thermosonic bonding tool, and the step of selectively interrupting the branches is performed by engaging the same tool with the branches as part of the same processing operation.

In another arrangement, the step of selectively 35 interrupting the branches is performed later as, for example,

#### PCT/US02/32251

just prior to the stacking step. Thus, the units may be provided as substantially identical elements which may be handled and stocked as mutually interchangeable parts. Here again, the dielectric layers of the various units may include interruption openings extending through the dielectric layers, and the branches of the multi-branch traces may extend across these interruption openings prior to the severing step. The step of selectively interrupting the branches may include breaking the branches at these interruption openings.

10 Alternatively, the interruption openings may be formed at the same time as the branches are broken as, for example, by removing small regions of each multi-branch trace and portions of the dielectric layers underlying these regions, such as by punching the circuit panels to form the interruption openings while also breaking the branches of the traces.

Because the units are substantially identical to one another and can be treated as parts interchangeable with one another up to and including the step of severing the branches, handling and stocking of the units in commerce is substantially 20 simplified. For example, the units can be fabricated at a chip packing plant arranged to handle bare semiconductor chips and to mount the bare semiconductor chips to the circuit panels of the individual units. The stacking operation can be performed in a circuit board stuffing plant having tools and equipment 25 adapted for surface-mounting packaged chips to circuit boards. Indeed, the stacking operation can be performed concomitantly with mounting the assembly to a circuit board. For example, the units can be stacked and the solder balls joining the various units can be reflowed at the same time as the solder 30 balls joining the bottom unit in the stack to the circuit board are reflowed.

A further aspect of the invention provides an in-process collection of interchangeable semi-finished units usable in a stacking process and assembly as discussed above.

PCT/US02/32251

A further aspect of the invention provides additional semiconductor chip assemblies. A chip assembly according to this aspect of the invention also includes a plurality of units, each including a semiconductor chip having contacts on a 5 front surface, and including a circuit panel having a central region and a peripheral region. The panel desirably includes a dielectric layer having first and second surfaces and at least one bond window extending between the first and second surfaces in the central region. The panel also includes a plurality of 10 terminals in the peripheral region, the terminals being exposed at both the first and second surfaces. Preferably, the dielectric layer has a plurality of terminal apertures extending between the first and second surfaces in the peripheral region and the terminals are pads aligned with the 15 terminal apertures. The chip is disposed with the front surface of the chip facing toward a surface of the panel in the central region and the contacts of the chip are connected to the traces on the panel in the at least one bond window. The units are superposed on one another in a stack so that the rear 20 surface of a chip in one unit faces toward a surface of the dielectric layer in a next adjacent unit. The units most preferably bear on one another in at least those portions of the central regions occupied by the traces. A plurality of conductive masses are disposed between the terminals of the 25 units and connect the terminals of the adjacent units to one another.

In one arrangement, the traces of each unit extend along the first surface of the dielectric layer in that unit, and the front surface of the chip in each unit faces toward the second surface of the dielectric layer in that unit. In a chip assembly of this type, at least some of the units desirably include heat transfer layers overlying the traces of such units, and these units bear on one another through the heat transfer layers. Thus, the heat transfer layer of each such unit desirably abuts the rear surface of the chip in the next

WO 03/032370 PCT/US02/32251

adjacent unit. The heat transfer layers of these units desirably extend across the bond windows in the dielectric layers of these units and are substantially flat, at least in the region extending across the bond windows. Such units of desirably further include an encapsulant at least partially filling the bond windows. During manufacture, the heat transfer layers may serve as masking layers which confine the encapsulant so that the encapsulant does not protrude beyond the dielectric layer. As further discussed below, the flat heat transfer layers allow close engagement of the units with one another and good thermal contact between adjoining units. These features contribute to the low height of the assembly and promote effective heat dissipation from chips within the assembly.

In an assembly according to a further aspect of the invention, the heat transfer layer may be present or may be omitted, but the encapsulant defines a surface substantially flush with the first surface of the dielectric layer or recessed relative to such surface. Where the heat transfer layer is omitted, the dielectric layer of each unit may bear directly on the rear surface of the chip in the next adjoining

These and other objects, features and advantages of the present invention will be more readily apparent from the 25 detailed description of the preferred embodiments set forth below, taken in conjunction with the accompanying drawings.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a top plan view of a circuit panel used in one embodiment of the invention.

9 FIG. 2 is a diagrammatic elevational view of a stacked package using the circuit panel of FIG. 1.

FIG. 3 is a diagrammatic sectional view of a stacked package in accordance with a further embodiment of the invention in conjunction with a circuit board.

#### PCT/US02/32251

FIG. 4 is a view similar to FIG. 1, but depicting a circuit panel in accordance with a further embodiment of the invention.

FIG. 5 is a view similar to FIG. 2, but depicting a 5 stacked package using the circuit panel of FIG. 4.

FIG. 6 is a diagrammatic plan view of a circuit panel used in yet another embodiment of the invention.

FIG. 7 is a diagrammatic sectional view of a stacked package made using the circuit panel of FIG. 6.

10 FIG. 8 is a diagrammatic plan view of a translation panel used in a further embodiment of the invention.

FIG. 9 is a diagrammatic sectional view of a package using the translation panel of FIG. 8.

FIG. 10 is a diagrammatic sectional view of a stacked 15 package according to a further embodiment of the invention.

FIG. 11 is a fragmentary view of a portion of a package element in accordance with another embodiment of the invention.

FIG. 12 is a fragmentary, diagrammatic plan view of a package unit in accordance with a further embodiment of the 20 invention.

FIG. 13 is a fragmentary plan view on an enlarged scale of the unit shown in FIG. 12.

FIG. 14 is a fragmentary, sectional elevational view taken along line 14-14 in FIG. 13.

FIG. 15 is a fragmentary, diagrammatic plan view of a circuit panel in accordance with yet another embodiment of the invention.

FIG. 16 is a fragmentary, diagrammatic perspective view of an in-process assemblage including a plurality of units formed 30 using the circuit panels of FIG. 15.

FIG. 17 is a diagrammatic elevational view of a cutting tool usable with the circuit panel and units of FIGS. 15 and 16.

PCT/US02/32251

FIG. 18 is a fragmentary, diagrammatic plan view of a circuit panel in accordance with yet another embodiment of the invention.

FIG. 19 is a fragmentary, diagrammatic elevational view of an assembly formed from the circuit panel of FIG. 18.

FIG. 20 is a fragmentary, diagrammatic sectional view of a unit in accordance with yet another embodiment of the invention.

MODES FOR CARRYING OUT THE INVENTION

A package in accordance with one embodiment of the 10 invention uses a plurality of package elements 20, each such element being in the form of a circuit panel. Each such circuit panel may include a dielectric layer in the form of a thin, flexible dielectric tape as, for example, a layer of 15 reinforced or unreinforced polyimide, BT resin or the like on the order of 25-100 µm thick, most preferably 25-75 µm thick. Alternatively, each panel may include a dielectric such as a fiberglass-reinforced epoxy as, for example, an FR-4 or FR-5 board. The panel has numerous terminals 22 disposed in rows 20 within a peripheral region of the panel, adjacent the edges 24 of the panel. In the embodiment illustrated, rows of terminals are provided along all four edges. However, the terminals can be provided adjacent less than all of the edges as, for example, in two rows adjacent to two opposite edges of the 25 panel. Each terminal 22 may be in the form of a flat, relatively thin disc of copper or other suitable metallic material on a first surface 26 of the panel (the surface visible in FIG. 1). As best seen in FIG. 2, the panel also has holes 28 extending through it in alignment with terminals 22. 30 Each such hole extends between the first surface 26 of the panel and the opposite, second surface 30.

Each panel 20 further has an elongated bond window 32 extending adjacent the center of the panel. The panel further has a large number of leads 36. Each lead includes a trace 38 extending along the first surface 32 of the panel and a

connection section 40 formed integrally with the trace projecting from the trace across the bond window. In the unassembled state depicted in FIG. 1, each connection section is connected by a frangible element 42 to an anchor section 44 projecting from the side of the bond window opposite trace 38. The traces and anchor portions are arranged in a row extending along the length of the bond window. Different traces extend to opposite sides of the bond window, so that some of the connection sections 40 project into the bond window from one side, whereas others project into the bond window from the opposite side. The arrangement of the traces and their connection sections may be substantially as shown in U.S. Patent 5,489,749, the disclosure of which is hereby incorporated by reference herein.

The terminals 22 include a first set of select terminals 22A-22D; a second set of select terminals 22E-22H; as well as other terminals, referred to herein as non-select terminals, as, for example, terminals 22J and 22K. Each trace 38 includes a common section 46 adjacent to and connected to a connection section 40. Some of the traces are connected to the non-select terminals. These traces have common sections 46 which extend all the way to the associated terminals, such as to terminals 22J and 22K, so that the common section 46 of each such trace is connected directly with a non-select terminal.

25 Those traces 38 associated with the select terminals are multi-branched traces 50. Each such multi-branched trace has a plurality of branches connected to its common section 46 and connected to one of the associated select terminals. For example, trace 38A includes branch 50A connected to select terminal 22B; branch 50C connected to select terminal 22C; and branch 50D connected to select terminal 22C; and branch 50D connected to select terminal 22D. Trace 38A also includes a distribution section 52A extending transverse to the common section 46A and interconnecting the various branches 50A-50D with the common section. Trace 38E associated with terminals

22E-22H is also a multi-branched trace and has a similar set of branches 50E-50H and distribution section 52E, so that all of the branches 50E-50H are connected to the common section 46E of the trace and to its connection section 40E. The dielectric of panel 20 has disconnection apertures 54 aligned with the branches 50 of each multi-branched trace 38, so that each such branch extends across a disconnection aperture. The disconnection apertures are disposed adjacent to the select terminals 22A, 22B, etc.

The terminals and the leads, including the traces and connection sections, are formed as a single layer of metallic features on the first surface of the panel. These metallic features desirably are less than about 30  $\mu m$  thick, typically about 5-25  $\mu m$  thick as, for example, about 20  $\mu m$  thick. A thin 15 adhesive layer (not shown) optionally may be provided between the dielectric layer 20 and the metal layer. This adhesive layer should also be as thin as practicable, desirably about 15 μm or less thick. The terminals and traces can be formed by conventional processes used in manufacture of tape automated 20 bonding tapes and the like as, for example, by etching a laminate including a layer of copper or other metal and the dielectric material which forms the panel so as to remove portions of the metallic layer. Alternatively, the terminals and traces can be formed by a deposition process such as 25 electroless plating and/or electroplating. The bond window, the holes associated with the terminals and the disconnection apertures may be formed by etching or ablating the dielectric

The stacked chip assembly includes a plurality of units 56 is [FIG. 2]. Except as otherwise stated, each unit 56 is identical to each other unit 56 in the stack. Each such unit includes a panel or chip carrier 20 as discussed above with reference to FIG. 1 and a chip 58 associated with that panel. Each such chip has a front or contact bearing surface 60 and a sear surface 62. The front surface 60 of each chip has

PCT/US02/32251

contacts 64 arranged in rows adjacent the center of the chip.

The chip also has edges 66 bounding the front and rear surfaces 62. The thickness t of the chip (the dimension between the front surface 60 and back surface 62) typically is substantially smaller than the other dimensions of the chip. For example, a typical chip may be about 100-500 microns thick and may have horizontal dimensions (in the plane of the front and rear surfaces) of about 0.5 cm or more. The front surface 60 of the chip faces towards the second surface 30 of the 10 associated panel 20.

A layer of adhesive 68 is disposed between the chip and the panel of each unit. The adhesive layer 68 defines an aperture in alignment with the bond window. Adhesive layer 68 may be provided by applying a liquid or gel material between 15 the chip and the panel at the time of assembly or by providing a porous layer such as an array of small resilient elements between the layers and injecting a flowable material into such layer as taught, for example, in certain embodiments of U.S. Patents 5,659,952 and 5,834,339, the disclosures of which are 20 hereby incorporated by reference herein. Preferably, however, the adhesive layer is provided as one or more solid or semisolid pads having substantially the same horizontal extent as the desired adhesive layer in the final product. These pads are placed between the chip and panel during assembly. For 25 example, the pad may be pre-assembled to the panel or to the chip before the chip is juxtaposed with the panel. Such a solid or semi-solid pad can be placed quite accurately in relation to the chip and the panel. This helps to assure that the pad does not cover terminals 22, even where there is only a 30 small clearance between the nominal position of the pad edge and the terminals. Such a pad may include an uncured or partially cured layer and other adhesion-promoting features as discussed, for example, in U.S. Patent 6,030,856, the disclosure of which is hereby incorporated by reference herein. 35 Alternatively or additionally, the pad may be provided with a

PCT/US02/32251

thin layer of a flowable adhesive on one or both surfaces, and this layer may be a non-uniform layer as described in U.S. Patent 5,548,091, the disclosure of which is hereby incorporated by reference herein, to help prevent gas 5 entrapment in the layer during assembly. Adhesive layer 68 desirably is as thin as practicable as, for example, about 10-125 µm thick, most preferably about 25-75 µm.

The chip 58 of each unit is aligned with the central region of the associated panel, so that the rows of contacts 64 are aligned with the bond window 32 in the panel. The connection section 40 of each lead is connected to a contact 64 of the chip. During this process, the connection section of each lead is detached from the anchor section 44 of the lead by breaking the frangible section 42 of the lead. This process 15 may be performed as described in the aforementioned U.S. Patent 5,489,749 by advancing a tool (not shown) such as a thermal, thermosonic or ultrasonic bonding tool into the bond window of the panel in alignment with each connection section so that the tool captures the connection section and forces it into 20 engagement with the appropriate contact. The common section 46 of the trace 38 in each lead (FIG. 1) is connected by a connection section 40 to a contact on the chip. arrangement of the contacts and connection sections is selected so that the common sections 46A and 46E of multi-branched 25 traces 38A and 38E are connected to select contacts on the chip, i.e., to contacts of the chip which are not to be connected in parallel with corresponding contacts on all of the other chips in the stack. The common sections of the other traces are connected to the non-select contacts, i.e., contacts 30 of the chip which are to be connected in parallel with corresponding contacts of the other chips in the stack.

Each unit 56 further includes a solder mask layer 70 (FIG.

2) overlying the traces and terminals in the peripheral region of the panel. The solder mask layer has apertures aligned with 35 the terminals 22. The solder mask layer can be applied as a

conformal coating or sheet by conventional processes. unit further includes a heat transfer layer 76 overlying the traces 38 and the first surface 26 of the panel in the central region of the panel aligned with the chip 58. As further 5 discussed below, the heat transfer layer will establish intimate contact with the rear surface of the chip in the next adjacent unit of the stack. The heat transfer layer may be formed from a material such as a gel or grease loaded with a thermally conductive filler, or from a material which can be 10 brought to a deformable condition during assembly as, for example, a thermoplastic material or an uncured or partially cured epoxy or other reactive resin. Desirably, the heat transfer layer is a dielectric material and hence does not electrically short the various traces to one another. The heat 15 transfer layer may be formed integrally with the solder mask layer so that a central portion of the solder mask layer, aligned with chip 58, forms the heat transfer layer.

The heat transfer layer, whether formed integrally with the solder mask layer or separately from the solder mask layer, 20 desirably is as thin as practicable as, for example, about 40 µm thick or less, and desirably about 30 µm thick or less. An integral solder mask layer and heat transfer layer may be provided as a conformal coating having a thickness of about 5-20 µm in those regions of the coating overlying the traces and 25 about 10-40 µm thick in those regions disposed between the traces. Such a coating adds only about 5-20 µm to the overall thickness of the unit. As seen in FIG. 2, the central portion of the heat transfer layer or solder mask layer bridges across the aperture 32 in the dielectric layer. Preferably, the 30 central portion of the heat transfer layer or solder mask layer is substantially planar, and does not bulge substantially away from dielectric layer 20.

An encapsulant 33 may be provided in aperture 32, surrounding the connection sections 40 of the leads. The 35 encapsulant may be separate from the adhesive layer 68 and may

PCT/US02/32251

be introduced using the techniques disclosed in U.S. Patents 6,232,152 and 5,834,339, the disclosures of which are incorporated by reference herein. As disclosed in certain preferred embodiments taught in the '152 and '339 patents, the layer attaching the chip to the dielectric layer (adhesive layer 68) may define a channel extending to one or both edges of the chip, and the encapsulant may be introduced into this channel at the edges of the chip. Alternatively, where the adhesive layer is formed in whole or in part by a flowable material introduced between the chip and the dielectric layer as discussed above, the encapsulant may be formed by the flowable material. In either process, the heat transfer layer 76 (or internal heat transfer and solder mask layer) covers the bond window in the dielectric layer so that the encapsulant 15 cannot project beyond the first surface 76 of the dielectric laver.