(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-514765

(P2005-514765A)

(43) 公表日 平成17年5月19日(2005.5.19)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 21/3065

H01L 29/423

H01L 29/49

F 1

H01L 29/78 301S

H01L 21/302 105B

H01L 29/58 G

テーマコード(参考)

4M104

5FO04

5F140

審査請求 未請求 予備審査請求 有 (全 15 頁)

(21) 出願番号 特願2003-555572 (P2003-555572)

(86) (22) 出願日 平成14年12月19日 (2002.12.19)

(85) 翻訳文提出日 平成16年8月17日 (2004.8.17)

(86) 國際出願番号 PCT/US2002/041105

(87) 國際公開番号 WO2003/054948

(87) 國際公開日 平成15年7月3日 (2003.7.3)

(31) 優先権主張番号 10/023,328

(32) 優先日 平成13年12月20日 (2001.12.20)

(33) 優先権主張国 米国(US)

(71) 出願人 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68(番地なし)

(74) 代理人 100099324

弁理士 鈴木 正剛

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】エッチング停止層としてポリシリコン再酸化層を使用することによって、シリコン層の凹部を減少する窒化オフセットスペーサ

## (57) 【要約】

基板(20)上にゲート電極(22)を提供し、この基板(20)およびゲート電極(22)上にポリシリコン再酸化層(26)を形成する、半導体デバイスを形成する方法である。窒化物層(28)は、ポリシリコン再酸化層(26)上にたい積され、異方性エッチングされる。このエッチングは、ゲート電極(22)上に窒化物オフセット・スペーサ(30)を形成して、ポリシリコン再酸化層(26)上で停止する。エッチング停止層としてポリシリコン再酸化層(26)を使用することは、オフセット・スペーサ(30)が形成されるようにする一方で、窒化物層(28)の真下にあるシリコン基板(20)の掘り下げを防ぐ。

**【特許請求の範囲】****【請求項 1】**

基板(20)上にゲート電極(22)を形成するステップと、

前記基板(20)および前記ゲート電極(22)上にポリシリコン再酸化層(26)を形成するステップと、

前記ポリシリコン再酸化層(26)上に窒化物層(28)をたい積するステップと、

前記窒化物層(28)を異方性エッチングし、前記ゲート電極(22)上に窒化物オフセット・スペーサ(30)を形成するように、前記ポリシリコン再酸化層(26)上で前記異方性エッチングを停止するステップと、

を含む、半導体デバイスを形成する方法。

10

**【請求項 2】**

前記窒化物層(28)がエッチングされた後、前記基板(20)中にソース／ドレイン拡張部(36)を形成するステップと、

前記オフセット・スペーサ(30)上にサイドウォール・スペーサ(38)を形成するステップと、

前記基板(20)中にソース／ドレイン(40)を形成するステップとをさらに含む、

請求項1記載の方法。

**【請求項 3】**

前記窒化物層(28)をたい積する前に、前記基板(20)中にハロー・インプラント(24)を形成するステップをさらに含む、

請求項2記載の方法。

20

**【請求項 4】**

前記ポリシリコン再酸化層を形成するステップは、約700から約900の間の温度で、酸化物を前記基板および前記ゲート電極上に熱処理によって成長させることを含む、

請求項3記載の方法。

**【請求項 5】**

前記窒化物層(28)をエッチングした後であって、前記基板(20)中に前記ソース／ドレイン拡張部(36)を形成する前に、前記露出したポリシリコン再酸化層を除去するステップをさらに含む、

請求項4記載の方法。

**【請求項 6】**

基板(20)上にゲート電極(22)を形成するステップと、

前記基板(20)上にエッチング停止層(26)を形成するステップと、

前記エッチング停止層(26)上に窒化物層(28)を形成するステップと、

前記ゲート電極(22)上にオフセット・スペーサ(30)を形成するように前記窒化物層(28)をエッチングし、前記エッチングを前記エッチング停止層(26)上で停止するステップと、

前記基板(20)中にハロー・インプラント(24)を形成するステップと、

を含む、ハロー・インプラントを備えた半導体デバイスを形成する方法。

30

**【請求項 7】**

前記エッチング停止層(26)は、ポリシリコン再酸化層(26)である、

請求項6記載の方法。

40

**【請求項 8】**

前記窒化物層(28)がエッチングされた後、前記ポリシリコン再酸化層(26)を貫通してインプラントすることによって、ソース／ドレイン拡張部(36)およびソース／ドレイン・インプラント(40)を形成するステップをさらに含む、

請求項7記載の方法。

。

**【請求項 9】**

前記基板(20)を露出するように、前記窒化物層(28)をエッチングすることによつて露出した前記ポリシリコン再酸化層(26)の一部を除去するステップをさらに含む、

請求項8記載の方法。

**【請求項 10】**

50

前記窒化物層(28)をエッティングするステップは、前記窒化物層(28)を、窒化物対酸化物の高い選択性を有するプラズマ・エッチャント・ガスで、反応性イオンエッティングするステップを含む、請求項9記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して、半導体デバイス製造の分野に関し、より詳しくは、半導体デバイスの形成の間のオフセット・スペーサの使用に関する。

【背景技術】

【0002】

半導体集積回路の最小加工寸法が縮小するにつれて、ソース／ドレイン領域間の距離はより減少する。

電界効果トランジスタ(FET)についてのソース／ドレイン領域間の間隔の減少によって、パンチスルー現象、ソース・ドレイン間の降伏電圧の減少、しきい値電圧(V<sub>t</sub>)の減少、Sファクタ(subthreshold swing)の増加のような短チャネル効果が生じる。

この短チャネル効果を抑制するために、半導体産業は、常にMOSFETデバイスについての製造プロセスを最適化している。

浅い接合は、ソース／ドレイン空乏領域のチャネルへの浸食を少なくするので、CMOSデバイスのVLSI製造における最近の動向は、ソース／ドレイン領域の接合深さを浅くする方向に向かっている。

【0003】

半導体処理技術の進歩は、チャネル長が0.25μmを充分下回るまでに減少させた。

これらのサイズでは、実効チャネル長が少しでも減少すると、トランジスタの降伏電圧を低下させる観点でコストがかかる可能性がある。

従って、ソース／ドレイン中の不純物の横方向の拡散の制限はますます重要である。

【0004】

「ポケット・インプラント」とも呼ばれるハロー・インプラント(halo implant)は、ソース／ドレイン中の不純物の横方向の拡散を制限することができる。

ハロー・インプラントの不純物は、ソースおよびドレインの導電型(conductivity type)と反対の導電型を有する。

通常、ハロー・インプラントは、ゲートを定義した後であってソース／ドレイン拡散の前に行われる。

マスク効果により、ハロー・インプラントは、典型的にソース／ドレイン領域近傍において最も高い不純物濃度を示す。

ソース／ドレイン中の不純物の垂直方向の拡散を防止するために、ハロー・インプラントのためのインプラント・エネルギーは、不純物濃度の最も高い位置から離れた位置のハローの深さがソース／ドレインのインプラントの深さよりも深くなるように、慎重に選択されるべきである。

【0005】

ゲート電極とドレイン電極間のオーバーラップ・キャパシタンスを減少し、これにより、このトランジスタのためのより良いAC性能を提供するために、ハローと拡張部を分離することが望ましい。従って、ゲート電極の横に形成されるオフセット・スペーサが使用されている。

ハローを形成し、その後ゲート電極のサイドウォール上のオフセット・スペーサを形成し、それからソース／ドレイン拡張部を形成することによって、ハローは、物理的に拡張部の正面に位置する。

オフセット・スペーサの使用は、与えられた物理的なチャネル長よりも実効チャネル長をより長くする。

【0006】

オフセット・スペーサの形成において、絶縁層は、典型的に基板およびゲート電極上に

10

20

30

40

50

たい積される。

異方性エッチングは、ゲート・サイドウォールの表面上に絶縁層の一部を残しながらその一方で、絶縁層のゲート電極表面の基板を取り除くために行なわれる。

このゲート・サイドウォール上に残っている絶縁層の部分は、オフセット・スペーサを形成する。

上述のオフセット・スペーサとして使用するための材料は、酸化シリコンと窒化シリコンを含む。

オフセット・スペーサが形成されると、ソース／ドレイン拡張部のインプラントが、オフセット・スペーサをマスクとして使用しながら実行される。

継続的な処理ステップは、深いソース／ドレインのインプラントがその後行われる、オフセット・スペーサ上にサイドウォール・スペーサを形成するステップを含む。 10

#### 【0007】

上述した方式におけるオフセット・スペーサの形成は、異方性エッチングが、絶縁層（これからオフセット・スペーサが形成される）をオーバーエッチングすることにより、シリコン基板を掘り下げるという問題を引き起こす。

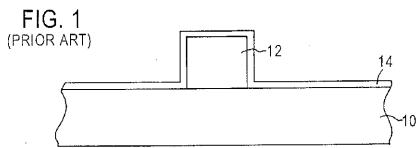

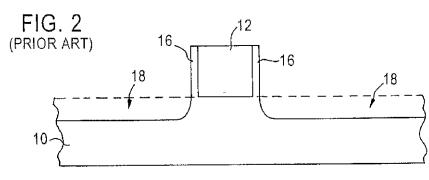

この状況を、図1および図2に概略的に記載する。

図1において、基板10は、その表面上にゲート電極12を有する。絶縁層14は、基板10とゲート電極12を被覆する。

オフセットスペーサ16を形成するため、基板から絶縁材14を取り除く異方性エッチングが実行される。 20

しかしながら、異方性エッチングプロセスをシリコン上で停止させるのは難しいので、凹部（recess）18はまた、オーバー・エッチングによって引き起こされる基板10の掘り下げによって形成される。

凹部18の形成は、特にソース／ドレイン拡張部の領域において問題となる。

これは、シリコンの掘り下げは、接合深さを増加させることと同じであるためであり、接合深さの増加は、浅い深さの接合が今日の技術において要求されるため、不適当である。 30

さらに、オフセット・スペーサ生成中に生成される掘り下げは、オーバーラップ・キャパシタンスに悪影響を及ぼす。

#### 【0008】

オフセット・スペーサを形成する絶縁層のエッチング中にシリコン基板の掘り下げを防ぐような方式の、オフセット・スペーサを備えた半導体デバイスを形成する方法が必要とされている。 30

#### 【発明の概要】

#### 【0009】

基板上にゲート電極を形成するステップと、この基板およびゲート電極を被覆するポリシリコン再酸化層（polysilicon reoxidation layer）を形成するステップとを含む半導体デバイスの形成方法を提供する本発明の実施形態は、これらの要望および他の要望を満たす。

窒化物層は、ポリシリコン再酸化層上にたい積される。 40

窒化物層は異方性エッチングされ、このエッチングは、ゲート電極上に窒化物オフセット・スペーサを形成するように、ポリシリコン再酸化層上で停止する。

窒化物オフセット・スペーサの形成中に、エッチング停止層としてポリシリコン再酸化層を使用することは、本発明の実施形態に従ってシリコン基板の掘り下げを防ぐ。

極薄ポリシリコン再酸化層は基板上に残るようにすることができ、ソース／ドレイン拡張部およびソース／ドレイン領域を形成するように、残っているポリシリコン再酸化層を通じて、制御可能に、確実に、インプラントが行われてもよい。

代替的に、ポリシリコン再酸化層は、通常、絶縁層のドライ・エッチングに関連する掘り下げを生成しないウェット・エッチングによって取り除くこともできる。

#### 【0010】

10

20

30

40

50

基板上にゲート電極を形成するステップと、この基板上にエッチング停止層を形成するステップとを含む、ハロー・インプラントを備えた半導体デバイスを形成する方法を提供する本発明の実施形態もまた、既に記述の要望を満たす。

窒化物層は基板およびゲート電極上に形成される。

窒化物層は、ゲート電極上にオフセット・スペーサを形成するようにエッチングされ、このエッチングは、エッチング停止層上で停止する。

#### 【0011】

本発明の、前述した構造およびその他の構造、様式および利点は、本発明の以下の詳細な説明および図面からより明白になる。

#### 【本発明の詳細な説明】

10

#### 【0012】

本発明は、半導体デバイスの生成におけるオフセット・スペーサの形成と関係する問題を扱い、解決する。

特に、本発明は、ゲート電極のサイドウォール上にオフセット・スペーサを形成するための絶縁層のエッチング中に発生する掘り下げの問題の一部を解決する。

本発明は、半導体デバイスの基板上に、ポリシリコン再酸化層のようなエッチング停止層を提供することによって、これらの問題の一部を解決する。

窒化物層は、ポリシリコン再酸化層上にたい積される。

窒化物層の異方性エッチングは、ポリシリコン再酸化層上でエッチングが停止するように選択され、ポリシリコン再酸化層を貫通してシリコン基板を掘り下げないようになっている。

ポリシリコン再酸化層は極薄であるので、インプラント・プロセスが、ソース／ドレイン拡張部およびソース／ドレイン領域を形成するように、ポリシリコン再酸化層を通じて、制御可能に、正確に行うことができる。

代替的に、ポリシリコン再酸化層は、シリコン基板を掘り下げる恐れのないウェットエッチング・プロセスによって安全に除去されてもよい。

掘り下げの防止は、ハローと拡張部を分離し、トランジスタのよりよいAC性能を提供すべく、オーバーラップ・キャパシタンスを縮小する。

さらに本発明は、シリコンの掘り下げを防止することによって、浅い深さ形成の効果を維持する。

30

#### 【0013】

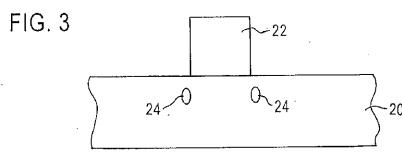

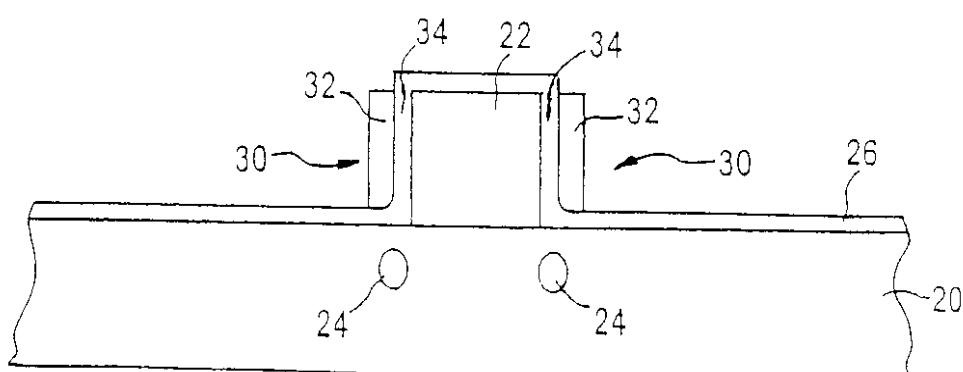

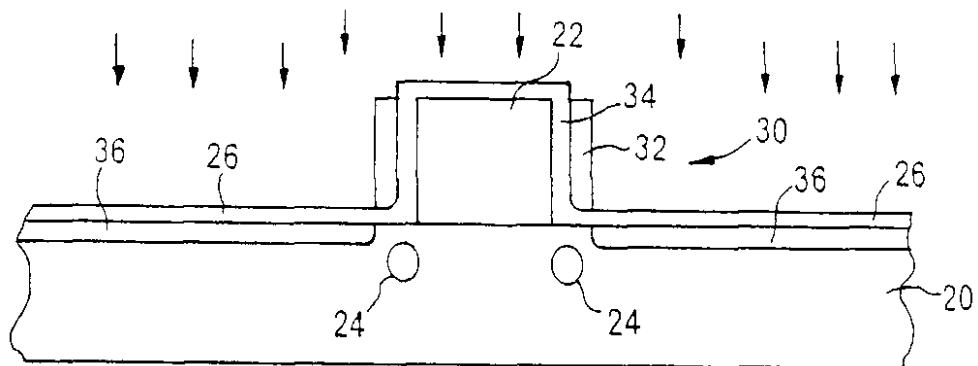

図3は、本発明の実施形態に従ってデバイスを形成する間の、半導体デバイスの断面図を示す。

このデバイスは、例えばシリコンからなる基板20を含む。この基板20の上表面上には、例えばポリシリコンからなるゲート電極が提供される。

ポリシリコン・ゲート電極22は従来の方法で形成されてもよいし、その後ポリシリコンまたは他のゲート電極材料がたい積され、ゲート電極22を形成すべくエッチングされる、ゲート酸化膜の形成を含んでいてもよい。

#### 【0014】

図3は、ハロー・インプラント24を示す。ハロー・インプラント24は、従来のハロー・インプラント・プロセスによって提供される。

ハロー・インプラント24は、本発明の方法の全体にわたって記載されるが、ハロー・インプラント24は任意のものであり、本発明の実施形態はこのようなハロー・インプラントを有することなく、半導体デバイスを形成することが理解される。

これらの実施形態は、図3ないし図8において記載されていないが、当業者は、本発明の方法がハロー・インプラント24と共に実行されても、ハロー／インプラント24を有することなく実行されてもよいことを認識するだろう。

しかしながら、説明と例示のため、ハロー・インプラント24は、図3ないし図8において示される。

#### 【0015】

50

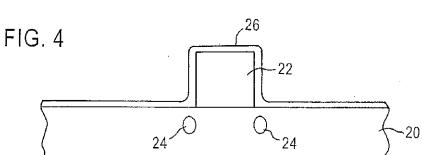

図4は、本発明の方法の実施形態に従ってポリシリコン再酸化ステップを実行した後の図3の構造を記載する。

ポリシリコン再酸化ステップは、基板20およびゲート電極22の表面上にポリシリコン再酸化層26を形成する。

ポリシリコン再酸化層26は、従来のポリシリコン再酸化形成プロセスによって形成される。このプロセスは、約750から900の間の温度で熱処理により成長した酸化層を提供する。

ポリシリコン再酸化層26は、15から約50の厚みに形成され、好ましくは25の厚みに形成される。

ポリシリコン再酸化層26は、後述するその後のエッチングステップにおいて、エッチング停止層として優れた選択性を提供する、非常に高密度で高品質な絶縁層である。10

#### 【0016】

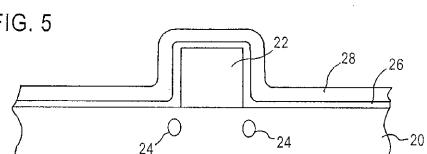

図5において、窒化物層28は、ポリシリコン再酸化層26上に共形にたい積されている。

窒化シリコン製とすることができます窒化物層28は、例えば、典型的な技術として、プラズマ強化化学気相たい積法(PECVD)(plasma enhanced chemical vapor deposition)または減圧化学気相たい積法(LPCVD)(low pressure chemical vapor deposition)による従来の方式でたい積することができる。

窒化物は、100から500の厚みでたい積されてもよい。本発明の実施例の一つにおいては、約250の厚みにたい積された窒化物を使用する。20

#### 【0017】

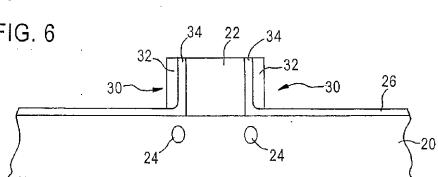

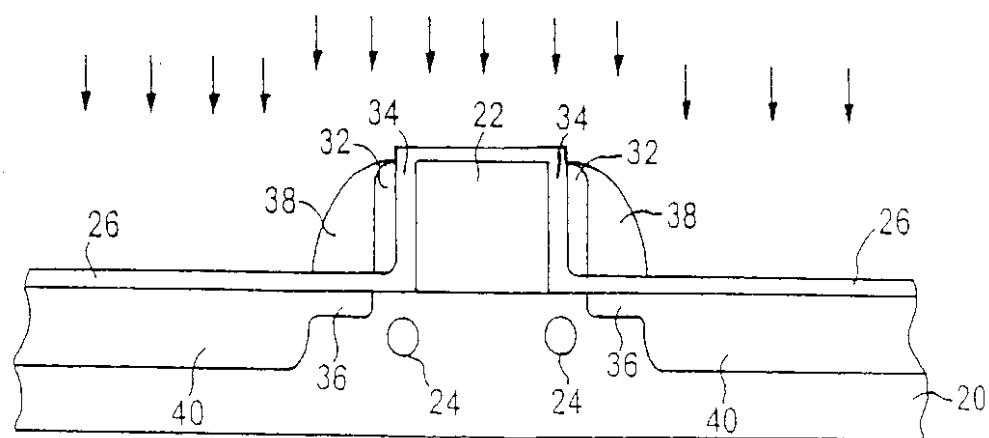

図6は、窒化物層28のたい積の後に、異方性エッチング・ステップが実行された状態を示す。

異方性エッチングは、例えばCHF<sub>3</sub>を使用する、反応性イオン・エッチングであってよい。

このエッチングは、ゲート電極22および基板20の頂部のような水平表面から、窒化物層28を除去する。

ポリシリコン再酸化層26は、エッチング停止層としての役割を果たすので、エッチングは、ポリシリコン再酸化層26上で停止する。このことは、窒化物層28のエッチングの間、シリコン基板20の掘り下げを防ぐことになる。30

先行技術の方法では、前述したように、エッチングは、基板中へと進んで掘り下げおよび凹部を形成することになり、好ましくない結果となる。

ポリシリコン再酸化層26は、エッチャントについての窒化物/酸化物の選択性が、典型的に酸化物/シリコンの選択性または窒化物/シリコンの選択性よりも高いという優れた選択性を提供する。

従って、窒化物層28のエッチングは、ポリシリコン再酸化層26上で正確に停止することができる。

#### 【0018】

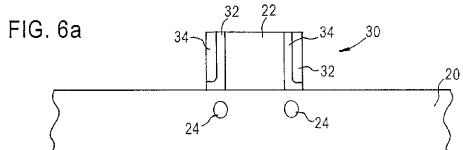

オフセット・スペーサ30は、窒化物部分32およびポリシリコン再酸化部分34によってゲート電極22のサイドウォール上に形成される。40

図6Aに示すように、異方性エッチング中にエッチング停止層としての役割を果たしたポリシリコン層26の部分は、ある実施形態において、基板20の上表面を露出すべく、ウェットエッチング・プロセスによって除去されてもよい。

シリコン基板20に破壊的な化学作用を及ぼすことなくポリシリコン再酸化層26を除去する、典型的なウェットエッチング・プロセスは、100:1のHF溶液である。

基板20上のポリシリコン再酸化層26を除去することによって、ソース/ドレイン拡張部およびソース/ドレイン領域のインプラントが妨げられないようになる。

しかしながら、本発明の他の実施形態においては、基板20上のポリシリコン再酸化層26が、基板20上に残るようにしてよい。

これは、基板上のポリシリコン再酸化層26の厚みが相対的に極薄であるため、ポリシ50

リコン再酸化層 26 を通じての基板 20 中へのインプラントが、正確に、制御可能に行うことができるためである。

以下の詳細な説明および図面は、ポリシリコン再酸化層 26 が基板 20 に残っているものと仮定するものである。

しかしながら、本発明の他の実施形態は、ポリシリコン再酸化層 26 を取り除くべく提供されることが明白に理解されるべきである。

#### 【0019】

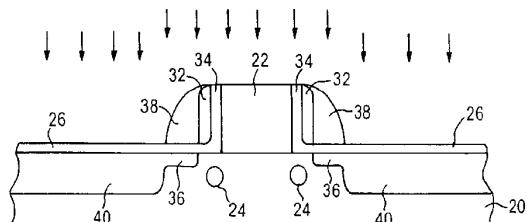

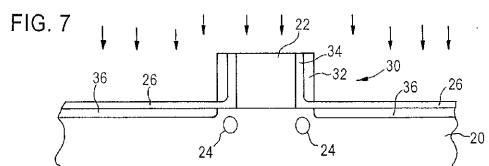

図 7 に示すように、オフセット・スペーサ 30 の形成に続いて、ソース／ドレイン拡張部 36 を生成すべく、ソース／ドレイン拡張部のインプラントが実行される。

このインプラント中、オフセット・スペーサ 30 は、通常理解されているようにマスクの役割を果たす。

#### 【0020】

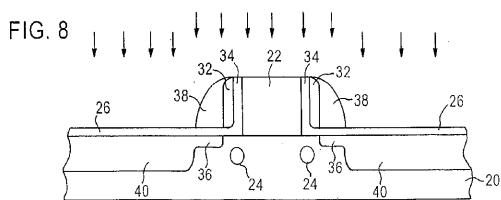

図 8 においては、ソース／ドレイン拡張部 36 の上に、マスクの役割を果たすサイドウォール・スペーサ 38 が形成されている。

その後、基板 20 中にソース／ドレイン領域 40 を形成すべく、ソース／ドレインのインプラントが、実行される。

活性化アニーリング・ステップは従来の方法に従ってインプラントの後に実行される。

#### 【0021】

本発明は、このようにオフセット・スペーサの利点を有するが、オフセット・スペーサを使用した先行技術の半導体デバイスが呈する掘り下げを有しない。

これは、絶縁層（この絶縁層から、異方性エッチング・ステップで、オフセット・スペーサがエッチングされる）の下にあるエッチング停止層の使用によって遂行される。

#### 【0022】

本発明の別の態様は、ボロン突き抜け（boron penetration）を防ぐと共に、ポリシリコン・ゲート電極全体の好ましくないシリサイド化（silicidation）を防ぐ。このボロン突き抜けおよびシリサイド化は、ゲート酸化膜の信頼性に関する問題を引き起こすことがある。さらに、この態様は、ポリシリコンの消耗をより少なくする。

#### 【0023】

デバイスの大きさが小さくなるにつれて、薄いポリシリコンが必要となる。

しかしながら、薄いポリシリコンについては、ボロン突き抜けの問題がより悪化する。

さらに、上述したようにポリシリコンは極薄であるので、全てのポリシリコンがシリサイド化される可能性がある。

このことは、ポリシリコン／ゲート酸化膜の界面を粗くし、ゲート酸化膜の信頼性についての問題を引き起こす。

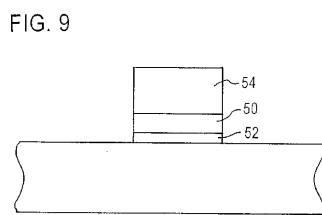

本発明はボロン突き抜けを防ぐため、図 9 に記載されるように、ゲート酸化膜 52 上であって、ポリシリコン 54 のたい積の前に、金属窒化物バリア層 50 を形成する。

さらに、後のシリサイド化は、この伝導性の金属窒化物バリア層 50 上で停止する。このプロセスの他の利点には、ポリシリコン消耗がほとんどまたは全くないことが含まれる。

#### 【0024】

本発明は、詳細に記載されると共に図示されたが、これらは単なる実例および例であり、制限的なものではなく、本発明の範囲は、添付された請求項の用語よってのみ制限されるものとして、明白に理解される。

#### 【図面の簡単な説明】

#### 【0025】

【図 1】先行技術によるデバイスの形成中における、半導体デバイスの断面図の概要を示す図。

【図 2】先行技術の方法によって、基板の掘り下げを伴う、絶縁層のドライ・エッチングを行った後の図 1 の構造を示す図。

【図 3】本発明の実施形態によって半導体デバイスの形成する間の基板とゲート電極を示す図。

10

20

30

40

50

す図。

【図4】本発明の実施形態によって基板およびゲート電極上のポリシリコン再酸化層を形成した後の図3の構造を示す図。

【図5】本発明の実施形態によって、ポリシリコン再酸化層上に窒化物層をたい積した後の、図4の構造を示す図。

【図6】本発明の実施形態によって、窒化物層の水平部分を除去するように、異方性エッチングが行なわれた後の、図5の構造を示す図。

【図6A】本発明のある実施形態によって、ポリシリコン再酸化層の一部がウェットエッチング・プロセスによって除去された、本発明の実施形態を示す図。

【図7】本発明の実施形態によって、ソース／ドレイン拡張部が、基板ヘインプラントされた後の、図6の構造を示す図。 10

【図8】本発明の実施形態によって、ソース／ドレインのインプラント・ステップが行なわれた後の、図7の構造を示す図。

【図9】本発明の態様に従って形成されたゲート電極を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 6 a】

【図 9】

【図 7】

【図 8】

## 【手続補正書】

【提出日】平成16年1月19日(2004.1.19)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

## 【請求項1】

基板(20)上にゲート電極(22)を形成するステップと、前記基板(20)上にエッチング停止層(26)を形成するステップと、前記エッチング停止層(26)上に窒化物層(28)を形成するステップと、前記ゲート電極(22)上にオフセット・スペーサ(30)を形成するように前記窒化物層(28)をエッチングし、前記エッチングを前記エッチング停止層(26)上で停止するステップと、を含む、半導体デバイスを形成する方法。

## 【請求項2】

前記窒化物層(28)がエッチングされた後、前記基板(20)中にソース／ドレイン拡張部(36)を形成するステップと、

前記オフセット・スペーサ(30)上にサイドウォール・スペーサ(38)を形成するステップと、

前記基板(20)中にソース／ドレイン(40)を形成するステップとをさらに含む、請求項1記載の方法。

## 【請求項3】

前記窒化物層(28)をたい積する前に、前記基板(20)中にハロー・インプラント

(24)を形成するステップをさらに含む、請求項1または2記載の方法。

【請求項4】

前記エッティング停止層(26)を形成するステップは、約700から約900間の温度で、酸化物を前記基板(20)および前記ゲート電極(22)上に熱処理によって成長させることを含む、請求項1ないし3のいずれかの項記載の方法。

【請求項5】

前記窒化物層(28)をエッティングした後であって、前記基板(20)中に前記ソース／ドレイン拡張部(36)を形成する前に、前記露出した熱処理によって成長した酸化物層を除去するステップをさらに含む、請求項4記載の方法。

【請求項6】

前記エッティング停止層(26)は、酸化シリコンを含むポリシリコン再酸化層(26)である、請求項1記載の方法。

【請求項7】

前記窒化物層(28)がエッティングされた後、前記ポリシリコン再酸化層(26)を貫通してインプラントすることによって、ソース／ドレイン拡張部(36)およびソース／ドレイン・インプラント(40)を形成するステップをさらに含む、請求項6記載の方法。

【請求項8】

前記基板(20)を露出するように、前記窒化物層(28)をエッティングすることによって露出した前記ポリシリコン再酸化層(26)の一部を除去するステップをさらに含む、請求項7記載の方法。

【請求項9】

前記窒化物層(28)をエッティングするステップは、前記窒化物層(28)を、窒化物対酸化物の高い選択性を有するプラズマ・エッチャント・ガスで、反応性イオンエッティングするステップを含む、請求項8記載の方法。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0002

【補正方法】変更

【補正の内容】

【0002】

米国公開特許公報5912188号および米国公開特許公報6165831号は、上位層のエッティング中の基板の化学的な破壊(attack)を避けるため、基板上にエッティング停止層を使用する、従来の半導体デバイスの製造方法の一例である。

半導体集積回路の最小加工寸法が縮小するにつれて、ソース／ドレイン領域間の距離はより減少する。

電界効果トランジスタ(FET)についてのソース／ドレイン領域間の間隔の減少によって、パンチスルーエフェクト(panchell-through effect)現象、ソース・ドレイン間の降伏電圧の減少、しきい値電圧(V<sub>t</sub>)の減少、Sファクタ(subthreshold swing)の増加のような短チャネル効果が生じる。

この短チャネル効果を抑制するために、半導体産業は、常にMOSFETデバイスについての製造プロセスを最適化している。

浅い接合は、ソース／ドレイン空乏領域のチャネルへの浸食を少なくするので、CMOSデバイスのVLSI製造における最近の動向は、ソース／ドレイン領域の接合深さを浅くする方向に向かっている。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0018

【補正方法】変更

【補正の内容】

【0018】

オフセット・スペーサ 30 は、窒化物部分 32 およびポリシリコン再酸化部分 34 によってゲート電極 22 のサイドウォール上に形成される。

図 6 A に示すように、異方性エッチング中にエッチング停止層としての役割を果たしたポリシリコン再酸化層 26 の部分は、ある実施形態において、基板 20 の上表面を露出すべく、ウェットエッチング・プロセスによって除去されてもよい。

シリコン基板 20 に破壊的な化学作用を及ぼすことなくポリシリコン再酸化層 26 を除去する、典型的なウェットエッチング・プロセスは、100:1 の HF 溶液である。

基板 20 上のポリシリコン再酸化層 26 を除去することによって、ソース／ドレイン拡張部およびソース／ドレイン領域のインプラントが妨げられないようになる。

しかしながら、本発明の他の実施形態においては、基板 20 上のポリシリコン再酸化層 26 が、基板 20 上に残るようにしてよい。

これは、基板上のポリシリコン再酸化層 26 の厚みが相対的に極薄であるため、ポリシリコン再酸化層 26 を通じての基板 20 中へのインプラントが、正確に、制御可能に行うことができるためである。

以下の詳細な説明および図面は、ポリシリコン再酸化層 26 が基板 20 に残っているものと仮定するものである。

しかしながら、本発明の他の実施形態は、ポリシリコン再酸化層 26 を取り除くべく提供されることが明白に理解されるべきである。

**【手続補正 4】**

**【補正対象書類名】** 図面

**【補正対象項目名】** 図 6

**【補正方法】** 変更

**【補正の内容】**

**【図 6】**

**【手続補正 5】**

**【補正対象書類名】** 図面

**【補正対象項目名】** 図 7

**【補正方法】** 変更

**【補正の内容】**

【図7】

【手続補正6】

【補正対象書類名】図面

【補正対象項目名】図8

【補正方法】変更

【補正の内容】

【図8】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                            | International Application No<br>PCT/US 02/41105                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 H01L21/31 H01L21/318 H01L21/335                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                            |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                            |                                                                                |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                            |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                            |                                                                                |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Citation of document, with indication, where appropriate, of the relevant passages         | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EP 0 345 875 A (PHILIPS NV)<br>13 December 1989 (1989-12-13)<br>abstract<br>---            | 1-10                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 5 670 404 A (DAI CHANG-MING)<br>23 September 1997 (1997-09-23)<br>abstract<br>---       | 1-10                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 6 165 831 A (HSU CHEN-CHUNG)<br>26 December 2000 (2000-12-26)<br>abstract<br>---        | 1-10                                                                           |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 5 912 188 A (HAUSE FREDERICK N ET AL)<br>15 June 1999 (1999-06-15)<br>abstract<br>----- | 1-10                                                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                            | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                            |                                                                                |

| Date of the actual completion of the international search<br><br>9 May 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                            | Date of mailing of the international search report<br><br>02 JUN 2003          |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5918 Patentlaan 2<br>NL-2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                            | Authorized officer<br><br>ERIK MILIANDER/JA A                                  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

| Int'l  | Application No |

|--------|----------------|

| PCT/US | 02/41105       |

| Patent document cited in search report |   | Publication date | Patent family member(s)                                                                                                                              |  | Publication date                                                                                                           |

|----------------------------------------|---|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------|

| EP 0345875                             | A | 13-12-1989       | GB 2219434 A<br>CN 1042274 A ,B<br>DE 68917995 D1<br>DE 68917995 T2<br>EP 0345875 A2<br>JP 1945065 C<br>JP 2025026 A<br>JP 6080651 B<br>US 4956312 A |  | 06-12-1989<br>16-05-1990<br>13-10-1994<br>04-05-1995<br>13-12-1989<br>23-06-1995<br>26-01-1990<br>12-10-1994<br>11-09-1990 |

| US 5670404                             | A | 23-09-1997       | NONE                                                                                                                                                 |  |                                                                                                                            |

| US 6165831                             | A | 26-12-2000       | NONE                                                                                                                                                 |  |                                                                                                                            |

| US 5912188                             | A | 15-06-1999       | NONE                                                                                                                                                 |  |                                                                                                                            |

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 ウェン - ジー キ

アメリカ合衆国、テキサス州 78750、オースティン、ノッティー パイン コウブ 980

2

(72)発明者 ジョン ジー . ベレリン

アメリカ合衆国、テキサス州 78739、オースティン、ニーダム レイン 6546

(72)発明者 ウィリアム ジー . エン

アメリカ合衆国、カリフォルニア州 95035、ミルピータス、アレクサンダー ウェイ 49

5

(72)発明者 マーク ダブリュ . マイケル

アメリカ合衆国、テキサス州 78613、オースティン、デイフラワー トレイス 1805

(72)発明者 ダリン エイ . チャン

アメリカ合衆国、カリフォルニア州 95008、キャンベル、アンソニー ドライブ 2054

F ターム(参考) 4M104 AA01 BB01 CC05 DD04 EE09 GG09 GG10 GG14

5F004 BA04 DA16 DB03 DB07 EA04 EA23 EA27 EA33 EA38 EB08

5F140 AA00 AA12 AA13 AA28 BF01 BF04 BF10 BF11 BF14 BG10

BG12 BG14 BG20 BG49 BG50 BG52 BG53 BG58 BH14 BH36

BK02 BK10 BK13 BK21