(19) 日本国特許庁 (JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2005-143114

(P2005-143114A)

(43) 公開日 平成17年6月2日(2005.6.2)

(51) Int. Cl.<sup>7</sup>

F

### テーマコード（参考）

НОЗК 3/02

HO 3 K 3/02

P

5 J 039

G06F 1/04

GO 6 F 1/04

A

5 J 043

НОЗК 5/00

HO 3 K 5/00

M

審査請求 未請求 請求項の数 17 O L (全 11 頁)

(21) 出願番号 特願2004-320690 (P2004-320690)

(22) 出願日 平成16年11月4日 (2004. 11. 4)

(31) 優先権主張番号 10351218.7

(32) 優先日 平成15年11月3日 (2003. 11. 3)

(33) 優先権主張国 ドイツ (DE)

(71) 出願人 390009232

ハイデルベルガー ドルツクマシーネン

アクチエンゲゼルシヤフト

Heidelberger Druckmaschinen AG

ドイツ連邦共和国 ハイデルベルク クア

フュルステン-アンラーゲ 52-60

Kurfuersten-Anlage

52-60, Heidelberg, Federal Republic of Germany

(74) 代理人 100123788

弁理士 宮崎 昭夫

(74) 代理人 100106138

弁理士 石橋 政幸

最終頁に続く

(54) 【発明の名称】 クロック補間をするためのスイッチング回路

(57) 【要約】

【課題】 第1の周波数を有する入力信号を処理して、周波数が前記入力信号の第1の周波数の倍数である少なくとも1つの出力信号を出力するためのスイッチング回路において、振動信号から補間された高い分解能の出力信号を生成する。

【解決手段】 入力信号がPLL周波数測定回路6で周波数と位相に関して測定され、測定された入力信号1nが少なくとも1つの周波数倍増器3およびこれに後続する発振器1によって倍増される。

### 【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

第1の周波数を有する入力信号(  $I_n$  )を処理して、周波数が前記入力信号(  $I_n$  )の第1の周波数の倍数である少なくとも1つの出力信号(  $O_{ut}$  )を出力するスイッチング回路( 7 )において、

前記入力信号(  $I_n$  )がPLL周波数測定回路( 6 )で周波数と位相に関して測定可能であり、測定された入力信号(  $I_n$  )が少なくとも1つの周波数倍器( 3 )およびこれに後続する発振器( 1 )によって倍可能であることを特徴とするスイッチング回路。

**【請求項 2】**

前記スイッチング回路( 7 )がデジタル式に構成されている、請求項1に記載のスイッチング回路。 10

**【請求項 3】**

倍された入力信号(  $I_n$  )と同じ位相の出力信号(  $O_{ut}$  )として出力可能である、請求項2に記載のスイッチング回路。

**【請求項 4】**

前記スイッチング回路( 7 )が回転検出器からの回転角入力信号(  $I_n$  )を入力信号(  $I_n$  )として処理し、前記回転角入力信号(  $I_n$  )の倍数の解像度を有する出力信号(  $O_{ut}$  )を出力する、請求項1から3までのいずれか1項に記載のスイッチング回路。 20

**【請求項 5】**

前記PLL周波数測定回路( 6 )が周波数倍器( 3 )を介してデジタル発振器( 1 )の入力部に接続されており、その出力クロック信号(  $CLK_{OUT}$  )がデジタルスイッチング回路( 7 )の出力信号(  $O_{ut}$  )である、請求項2から4までのいずれか1項に記載のスイッチング回路。 20

**【請求項 6】**

前記PLL周波数測定回路( 6 )にあるデジタル発振器( 1 )と、周波数倍器( 3 )を介して前記PLL周波数測定回路( 6 )に接続されたデジタル発振器( 1 )とが、同じシステムクロック信号( 2 )で制御可能である、請求項2から5までのいずれか1項に記載のスイッチング回路。 20

**【請求項 7】**

前記PLL周波数測定回路( 6 )が、2つまたは3つ以上の周波数倍器( 3 )を介して、2つまたは3つ以上の付属のデジタル発振器( 1 )の入力部に接続されており、その出力クロック信号(  $CLK_{OUT}$  )が前記スイッチング回路( 7 )の出力信号(  $O_{ut}$  )である、請求項2から6までのいずれか1項に記載のスイッチング回路。 30

**【請求項 8】**

前記スイッチング回路( 7 )の回転角入力信号(  $I_n$  )として、2チャンネル回転検出器のデジタル出力信号( A, B )が用いられる、請求項2から7までのいずれか1項に記載のスイッチング回路。 30

**【請求項 9】**

前記スイッチング回路( 7 )がプログラマブル・ロジックデバイスによって実現されている、請求項2から8までのいずれか1項に記載のスイッチング回路。 40

**【請求項 10】**

前記スイッチング回路( 7 )が信号プロセッサによって実現されている、請求項2から8までのいずれか1項に記載のスイッチング回路。 40

**【請求項 11】**

前記スイッチング回路( 7 )がASICによって実現されている、請求項2から8までのいずれか1項に記載のスイッチング回路。 40

**【請求項 12】**

前記スイッチング回路( 7 )の一部がプログラマブル・ロジックデバイス、ASIC、または信号プロセッサの内部で実現されており、前記デジタルスイッチング回路( 7 )の他の部分は前記グループのうち残りの2つのデジタルモジュールの内部で実現されている 50

、請求項 2 から 11 までのいずれか 1 項に記載のスイッチング回路。

【請求項 13】

前記周波数倍器(3)が有理補間係数(i)を有している、請求項 2 から 12 までのいずれか 1 項に記載のスイッチング回路。

【請求項 14】

請求項 2 から 13 までのいずれか 1 項に記載のスイッチング回路(7)を備える被印刷体処理機械。

【請求項 15】

第 1 の周波数を有する入力信号(In)を処理して、周波数が前記入力信号(In)の第 1 の周波数の倍数である少なくとも 1 つの出力信号(Out)を出力する方法において

10

、前記入力信号(In)を PLL 周波数測定回路(6)で周波数と位相に関して測定し、測定された入力信号(In)を少なくとも 1 つの周波数倍器(3)およびこれに後続する発振器(1)によって倍する方法。

【請求項 16】

倍された入力信号(Out)がデジタル信号処理によって同じ位相で出力信号(Out)として出力される、請求項 15 に記載の方法。

【請求項 17】

回転検出器からの回転角入力信号(Out)が前記入力信号(Out)として処理される、請求項 16 に記載の方法。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、第 1 の周波数を有する入力信号を処理して、周波数が入力信号の第 1 の周波数の倍数である少なくとも 1 つの出力信号を出力するスイッチング回路および方法に関するものである。

【背景技術】

【0002】

印刷機の制御は、今日、精度の要求が高まっているために、印刷機の回転部品に回転検出器を使用することなしには考えることができない。特に、個別駆動式の個々の印刷ユニットの間に一貫した機械的な駆動接続を備えていない印刷機では、互いに機械的に連結されていない印刷ユニットを正しい見当で作動させることができるようにするために、駆動される個々の印刷胴すべてに回転角検出器を設けることが必要である。このとき回転角検出器は、時間に対してプロットされた印刷胴等の回転部品の回転角を検出して、この回転角を、印刷機の機械制御部に送ることができる電気信号に変換する。しかし最近では、回転検出器は印刷胴を同期化するために必要なばかりでなく、版露光器やいわゆる DI 印刷機において、すなわち、版胴が機械内部でたとえばレーザにより書き込まれ、それによって画像付けされるオフセット印刷機において、画像付けプロセスを制御するのにも必要となっている。このような画像付けを十分に正確に行えるようになるためには、回転する版胴で用いられる回転角検出器の信号が、高い解像度を備えていなくてはならない。

30

【0003】

回転角検出器では、基本的に、物理的な解像度と補間された解像度とを区別することができる。回転検出器が 1 回転についてたとえば 360 ステップの下位区分を有しているとすると、このことは、回転検出器の物理的な解像度に相当している。この信号を電子回路で補間によってもっと解像度の高いフォーマットに変換することができ、この場合には誤差が発生するのが通常である。角度補間をするために、従来技術からいくつかの方法が公知となっている。高い解像度の回転角情報を生成するために駆動工学から公知となっている 1 つの解決法は、サイン/コサイン出力信号を出す回転検出器を利用し、この出力信号

40

50

を基にして、アークタンジェント法を用いて瞬間の角度を算出することにある。所望の高い解像度をサイン／コサイン回転検出器で実現するためには、この回転検出器が非常に高い物理的なピッチ数で作動しなければならない。このような方法では、100を超える補間係数は実現するのが非常に難しいからである。そのためには設計的に非常に高いコストがかかり、したがって相応に高価になる。そのため、このような回転検出器で解像度を高めるためにしばしば利用される補間法は、適用される補間係数の変更がまったく不可能であるか、または非常に大まかな変更しか可能でなく、多くの場合、補間係数は整数に限られている。ところが印刷機で版胴を画像付けするときには明確な角度位置でクロックを生成しなければならず、このことは、上記に加えてさらに可変な有理補間係数を必要とする。

10

#### 【0004】

角度同期された高い解像度のクロック信号を生成するために従来技術から公知となっている別の方法は、たとえば二進法のクロック信号を周波数倍するためには用いられるいわゆる位相制御回路（PLL）と接続された、TTL回転検出器（TTLは”Transistor Transistor Logic”（トランジスタ・トランジスタ・ロジック）の略）とも呼ばれる、二進法の出力信号を出すデジタルエンコーダを利用することにある。PLLという概念は”Phase Locked Loop”（フェイズロックループ）を意味しており、出力信号が入力信号と同じ位相になるように適応制御される制御回路である。この場合、周波数が、回転検出器の二進法の出力信号の周波数の任意の倍数であるクロック出力信号を生成することができ、その際に位相情報が失われることがない。回転検出器の二進法の出力信号の周波数の有理倍数が要求される場合には、”Fractional-N”（フラクショナルN）の名称で知られる技術が適用される。この場合、位相制御回路のフィードバック分路に、分周比の時間的な変更を可能にするプログラミング可能な分周器が設けられる。分周比の時間的な変更によって、位相制御回路の入力周波数を、時間的な平均値を中心として有理係数で倍することができるが、この位相制御回路は原則として整数によってしか分割することができない。たとえば出力信号を係数10.5だけ高めたいときは、時間を通して平均したときに10.5の係数が得られるように、分周器の分周比を10と11へ交互に変更しなければならない。「フラクショナルN」技術の場合、特に、システム誤差が原理的に発生することが欠点となる。位相制御回路の位相検出器の出力部でプログラミング可能な分周器の分周比を変更すると、外乱が発生するからである。

20

#### 【0005】

回転検出器の出力クロックが周期時間にわたって測定され、次いで、出力クロックの倍された周波数が算出される周波数倍方法も、類似の取り組みを追求するものである。出力クロックを正しい位相で入力クロックと組み合わせるために、位相制御回路がこの場合にも用いられ、この位相制御回路は、出力信号における位相誤差の修正を絶えず行うために、入力信号の周波数を直接制御するように構成されている。この方法は特許文献1に詳細に記載されている。

30

#### 【0006】

印刷機製造の分野では、特許文献2より、入力信号の倍数をもつ出力クロック信号の生成が通常のPLL周波数倍回路によって行われる、TTL回転検出器の二進法のクロック信号を周波数倍する方法が公知となっている。周波数倍回路の出力信号は、いわゆるDDS周波数発生器の供給クロック信号となる。DDSは”Direct Digital Synthesis”（ダイレクトデジタル合成）の略である。しかしこの設計形態は、このような通常の位相制御回路ではDDS周波数発生器への供給クロックの生成が非常に限られた周波数領域でしか機能しないという欠点がある。

40

【特許文献1】オーストリア実用新案明細書004985U1

【特許文献2】ドイツ特許出願公開明細書19743943A1

【発明の開示】

【発明が解決しようとする課題】

50

## 【0007】

そこで本発明の目的は、振動信号から補間された高い解像度の出力信号を生成し、その際に、従来技術の上述した欠点を回避することである。

## 【課題を解決するための手段】

## 【0008】

この目的は、請求項1および15によって本発明により解決される。本発明のその他の実施態様は、従属請求項および図面から読み取ることができる。

## 【0009】

本発明のスイッチング回路および本発明の方法により、一定の周波数を有する振動信号を遙倍することが容易に可能である。スイッチング回路は、アナログ技術で構成されてもデジタル技術で構成されていてもよい。

10

## 【0010】

本発明の第1の実施態様では、スイッチング回路がデジタル式に構成されている。このデジタル構造は、入力信号の周波数を測定できるという位相制御回路(PLL)の特性を利用したものである。位相制御回路がラッチング状態(eingera steten)で作動している限り、位相情報が失われることはないので、位相制御回路の出力信号は同じ位相で入力信号の周波数に比例する。さらに、位相制御回路の出力信号は周波数遙倍器によって遙倍されて発振器の入力部に転送され、この発振器の出力信号が、所望の出力クロックの周波数を有している。このようなシステムでは、出力クロックの位相はもはや閉ループ制御(geregel t)されるのではなく、開ループ制御(gesteuert)されるにすぎず、したがって、本方法は完全にデジタル式のシステムで実現されなくてはならない。本発明の大きな利点は、「フラクショナルN」技術の場合のようにシステム誤差を修正するために追加の実現コストを払わなくてもすみ、その一方で、回転検出器の所望の高い分解能を実現できるという点にある。さらに、印刷胴の画像付けするときに、明確な角度位置に対応するクロック信号を出力することができる。しかもデジタルスイッチング回路は、広い周波数領域をカバーすることができるという利点や、該当するデジタルモジュールを単にプログラミングするだけで、スイッチング回路を非常にフレキシブルに設計することができるという利点をもたらす。

20

## 【0011】

本発明の別の実施態様では、PLL周波数測定回路が周波数遙倍器を介してデジタル発振器の入力部に接続されており、その出力信号がデジタルスイッチング回路の出力信号である。すでに述べたように、位相制御回路の発振器は、周波数遙倍に引き続いて、開ループ制御されるにすぎない別の発振器と同期化されなくてはならないので、本発明のスイッチング回路は完全にデジタル式の技術でしか実現することができない。この理由から、周波数遙倍器の出力部にある発振器もデジタル発振器であることが必要である。

30

## 【0012】

この場合にはさらに、PLL周波数測定回路にあるデジタル発振器と、周波数遙倍器を介してPLL周波数測定回路に接続されたデジタル発振器とが、同じシステムクロック信号で制御可能であるのが有利である。両方のデジタル発振器は、同じシステムクロックが供給される場合にのみ同期して作動することができる。完全にデジタル式のシステム構造によってのみ、このような同じシステムクロックを両方の発振器で使用することができる。

40

## 【0013】

本発明の別の有利な実施態様では、デジタルスイッチング回路の入力信号が、2チャンネル回転検出器のデジタル出力信号である。2チャンネル回転検出器では、両方の出力チャネルが互いに90度だけ位相がずれた状態で通っている。(1回転を一義的に分解することはデジタルエンコーダにはできない。それができるのは絶対値発生器だけである。)そして2チャンネル回転検出器のデジタル出力信号を、デジタルスイッチング回路で処理するために使用することができる。この場合、分解能が特別に高くはない、市販されている通常のデジタルインクリメンタルエンコーダを利用することができ、このことはコス

50

トを大幅に引き下げる。

【0014】

さらに、PLL周波数測定回路が、2つまたは3つ以上の周波数倍器を介して、2つまたは3つ以上の付属のデジタル発振器の入力部に接続されており、その出力クロック信号がスイッチング回路の出力信号であることが好ましい。それにより、位相結合された状態で共通の入力信号になる、異なる周波数の出力信号を並行して供給することが可能である。この場合、接続されているすべてのデジタル発振器がシステムクロックに拘束される。

【0015】

さらに、デジタルスイッチング回路が、プログラマブル・ロジックデバイスによって実現されることが意図される。このようなシステムは、プログラマブル・ロジックデバイス、たとえばCPLD (Complex Programmable Logic Device、コンプレックス・プログラマブル・ロジック・デバイス) やFPGA (Field Programmable Gate Array、フィールド・プログラマブル・ゲートアレイ) である。

【0016】

さらに、これに代えて、デジタルスイッチング回路が信号プロセッサによって実現されることが意図される。信号プロセッサはロジックデバイスとは異なり、デジタル信号処理の分野における特別な役割に合わせて設計されている。DSPもしくはロジックデバイスに代えて、またはこれに加えて、ASICを使用することができる。ASIC (Application Specific Integrated Circuit、特定用途向け集積回路) は特定の利用目的のために製作されており、すなわち非常に特殊化したモジュールである。あるいは、デジタルスイッチング回路の一部がプログラマブル・ロジックデバイスで具体化されており、デジタルスイッチング回路の別の部分は信号プロセッサまたはASICで具体化することも可能である。このようにして、個々のデジタルモジュールの利点を互いに組み合わせることができる。

【0017】

周波数倍器は、有理補間係数で倍率をすることが好ましい。有理補間係数を用いることで、回転検出器の角度信号の解像度をほぼ無段階に規定することができる。というのも、二進法の量子化だけが解像度を制限するからである。解像度の無段階に可変な構造によって初めて、物理的な解像度の整数倍に相当しない明確な角度位置でクロック信号を生成することが可能となる。このことは、たとえば印刷機での版胴の画像付けのときに必要なので、本発明は、印刷機またはその他の被印刷体処理機械の回転検出器からの角度信号を処理するのに特に適している。

【発明を実施するための最良の形態】

【0018】

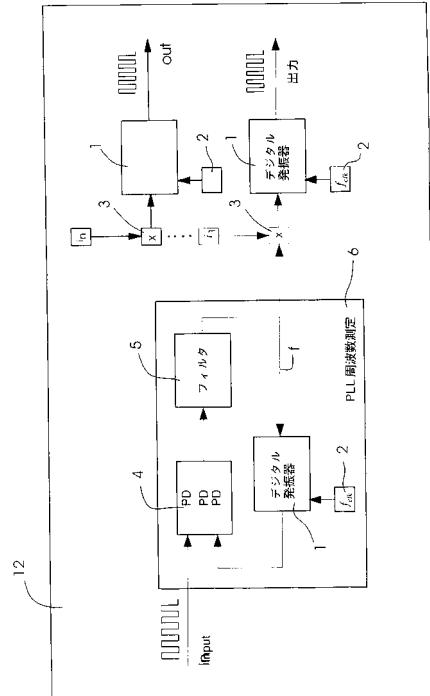

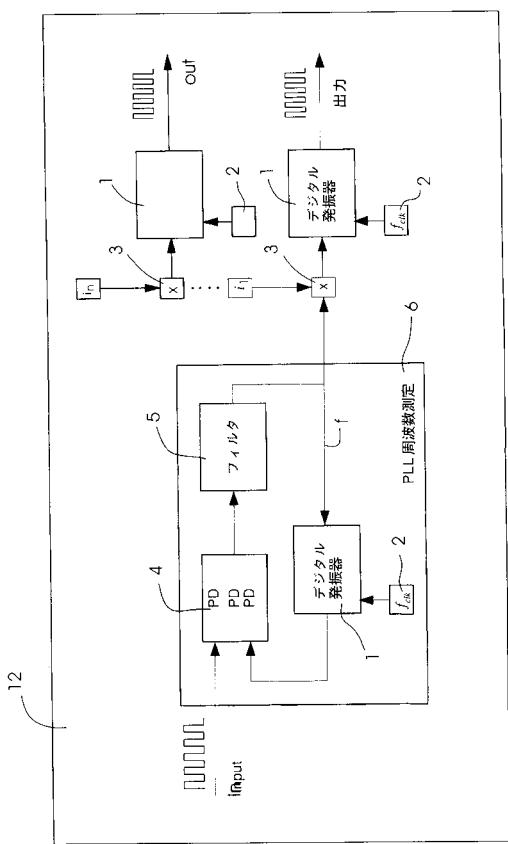

図1は、印刷機12で使用する場合の本発明によるデジタルスイッチング回路の原理的な構造を示している。このデジタルスイッチング回路は、一方では、回転検出器の出力信号を入力信号Inとして入力し、入力信号Inと位相結合された信号fを出力するPLL周波数測定回路6で構成されている。PLL周波数測定回路6は、入力信号Inと信号fとの間の位相差を判定する位相検出器と、これと接続されたコントローラ5で構成されている。閉ループ制御される信号fは、デジタル発振器1を有するフィードバック分路へ供給される。PLL周波数測定回路6によって周波数倍なしに測定され、引き続いて周波数倍器3で任意の補間係数i1で倍率された信号fの値は、第2のデジタル発振器1の入力部に印加され、このデジタル発振器が出力信号Outを生成する。この変形例では、出力クロックOutの位相はもはや閉ループ制御されず、開ループ制御されるだけなので、完全にデジタル式のシステムとしてしか具体化することができない。開ループ制御されるデジタル発振器1の両方のクロックの位相は、同じシステムクロック2の供給を受けることによって互いに同期化されており、このことは、図1のブロック図では小さなブロック2が記号で図示されている。PLL周波数測定回路6には複数の周波数倍器3とデジ

10

20

30

40

50

タル発振器 1 が接続されていてよく、それにより、補間係数  $i_1$  から  $i_n$  が異なっていれば、異なる周波数をもつ出力信号  $out$  を出力することができる。これらの出力信号  $out$  は並行して利用することができ、すべて入力信号  $In$  と位相結合されている。

## 【0019】

入力信号  $In$  の周波数の測定を、どうしてマイクロコントローラ等を用いて直接行わないのかという疑問が浮かぶが、その理由は、PLL周波数測定回路6によって周波数が位相制御されながら測定されることにある。周波数と位相の間には不可分の関係があるため、簡単な周波数測定では、たとえばデジタル乗算の量子化雑音や、入力信号の時間的な量子化といった誤差が制御不能に合算されてしまい、すなわち、印刷機12の回転部品の回転角に関する情報が失われてしまう。これとは異なり、PLL周波数測定回路6は位相情報を失うことなく入力信号  $In$  の周波数を測定する。というのも、PLL周波数測定回路6がラッチング状態で作動している限り、位相が繰り返して検知されるからである。この事実は数学的に表現することができる。測定される周波数は、本当の成分  $f_{in}(t)$  と誤差成分  $f_e(t)$  とで成り立っているので、出力信号の周波数  $f_{out}(t)$  については、次式が成立する。

## 【0020】

## 【数1】

$$\begin{aligned} f_{out}(t) &= i \cdot f_{in}(t) \\ &= i \cdot (f_{in}(t) + f_e(t)) \end{aligned}$$

10

20

## 【0021】

もしくは積分の後、その位相について次式が成立する。

## 【0022】

## 【数2】

$$\begin{aligned} \varphi_{out}(t) &= i \cdot \int_0^t 2\pi f_{in}(\tau) d\tau + i \cdot \int_0^t 2\pi f_e(\tau) d\tau \\ &= i \cdot \varphi_{in}(t) + i \cdot \varphi_e(t) \end{aligned}$$

30

## 【0023】

PLL周波数測定回路6は、 $f_e(t)$  が定常成分を含まず、 $f_e(t)$  が見積可能な限度内に収まるように作用する。簡単な周波数測定の場合には位相制御が行われず、誤差を限定できなくなる。したがって、PLL周波数測定回路6の周波数測定特性は、周波数が第1のクロック信号  $In$  の周波数の有理倍数  $i$  であり、かつ、位相が第1のクロック信号  $In$  の位相に結合されたクロック信号  $out$  を生成するために直接利用することができる。

## 【0024】

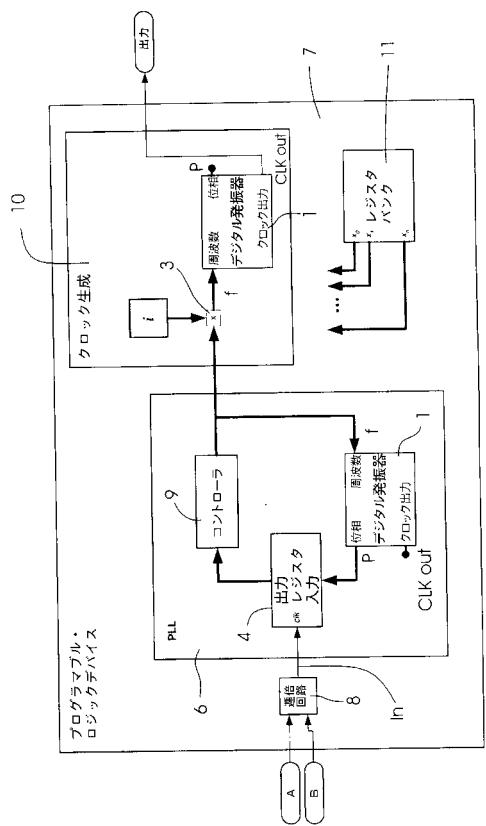

図3では、図1に示す完全にデジタル式のシステムが、プログラマブル・ロジックデバイス7の内部で実現されている。このシステムを信号プロセッサの内部で具体化したり、あるいはこの両方の実施形態を組み合わせて、さまざまなコンポーネントをプログラマブル・ロジックデバイス7と信号プロセッサに振り分けることも可能である。図3では、ここには図示しない回転検出器の両方のチャンネルA, Bが左側から入ってきている。両方の信号は90°だけ電気的に位相がずれている。遅倍回路8が、両方のチャンネルAおよびBの立下りエッジと立上りエッジを評価する。こうして生成された信号が、入力信号  $In$  の周波数を測定するPLL周波数測定回路6への入力信号  $In$  を形成する。PLL周波数測定回路6の後に本来のクロック生成スイッチング回路10が続いており、ここで、PLL周波数測定回路6によって供給された測定値  $f$  が周波数遅倍器3により相応の補間係数  $i$  で増減されたうえで、出力信号  $out$  を実効クロックCLK\_outとして生成するデジタル発振器1の入力部に送られる。ロジックデバイス7のレジスタバンク11には、全回路の読み出し可能・書き込み可能なパラメータがあるので、全回路を汎用的に利用可能で

40

50

ある。

【0025】

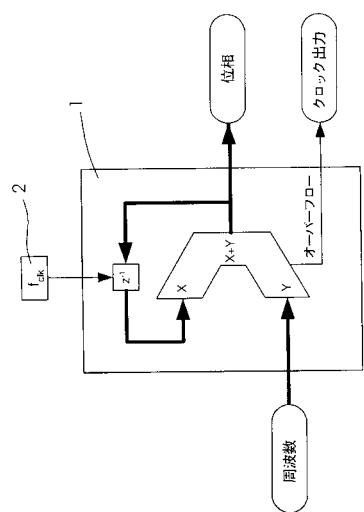

図2にはデジタル発振器1のブロック図を見ることができ、PLL周波数測定回路6の追従する発振器1と、クロック生成スイッチング回路10の発振器1とはいずれも簡単な位相累算器として構成されている。このような累算器では、たとえば発振器1の周波数fを表す二進ワード $f_w$ が、ここでは $f_{clk}$ であるシステムクロック2と累算される。クロック出力CLK\_outとして、回路は累算器のオーバーフロービットを利用する。出力信号CLK\_outの周波数 $f_{osc}$ は次式の値となる。

【0026】

【数3】

10

$$f_{osc} = \frac{f_w}{2^n} \cdot f_{clk}.$$

【0027】

これに加えて、位相累算器の最新の値が印加される出力部Pがある。このことは、以下に説明するような位相検知機能の簡単な回路工学上の具体化を可能にする。PLL周波数測定回路6の入力信号Inと、開ループ制御される追従する発振器1の出力クロックCLK\_outとの間の位相ずれを測定する位相検知器4をなすのは、PLL周波数測定回路6の入力信号による、追従する発振器1の位相信号Pの走査である。すなわち、入力パルスがロジックデバイス7のレジスタに位相累積器の内容を書き込む。このレジスタ内容は、追従する発振器1の入力信号Inと出力信号CLK\_outの間の位相ずれを、2の補数で表している。

20

【0028】

コントローラ9はデジタル計算回路、たとえばデジタルPIコントローラ9として具体化される。PLL周波数測定回路6の追従する発振器1の周波数ワードを補間係数iで増減する周波数遅倍器3が本来の角度補間であり、ここでは入力信号Inの周波数fが遅倍される。増減演算の実行は、n×nビット乗算として行われる。

【図面の簡単な説明】

【0029】

30

【図1】周波数遅倍器と、開ループ制御されるデジタル発振器とが後置された、本発明の位相制御回路の概略的な構造を示す図である。

【図2】デジタル発振器のブロック図である。

【図3】本発明によるデジタルスイッチング回路をプログラマブル・ロジックデバイスで具体化した様子を示す図である。

【符号の説明】

【0030】

40

- 1 デジタル発振器

- 2 システムクロック信号

- 3 周波数遅倍器

- 4 位相検知器

- 5 コントローラ

- 6 PLL周波数測定回路

- 7 プログラマブル・ロジックデバイス

- 8 遅倍回路

- 9 デジタルPIコントローラ

- 10 クロック生成スイッチング回路

- 11 レジスタバンク

- 12 印刷機

- In 入力信号

- Out 出力信号

50

P 位相信号

f 周波数信号

C L K o u t 出力クロック信号

i 補間係数

A 回転検出器のチャンネル 1

B 回転検出器のチャンネル 2

【図 1】

【図 2】

【図3】

---

フロントページの続き

(74)代理人 100120628

弁理士 岩田 慎一

(74)代理人 100127454

弁理士 緒方 雅昭

(72)発明者 ポリス ヤスニエヴィツツエ

ドイツ連邦共和国 6 9 1 1 5 ハイデルベルク カイザーシュトラーセ 9 8

(72)発明者 ハルトムト ケイル

ドイツ連邦共和国 6 9 2 0 7 ザンドハウゼン フリードリッヒシュトラーセ 1

F ターム(参考) 5J039 AC01 KK00 KK01 MM00

5J043 AA00 BB04 CC03 DD00 DD06