(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년12월11일

(11) 등록번호 10-1471950

(24) 등록일자 2014년12월05일

(51) 국제특허분류(Int. Cl.)

H01L 21/66 (2006.01) G03F 7/20 (2006.01)

(21) 출원번호 10-2010-7003699

(22) 출원일자(국제) 2008년07월21일

심사청구일자 2013년03월13일

(85) 번역문제출일자 2010년02월19일

(65) 공개번호 10-2010-0039411

(43) 공개일자 2010년04월15일

(86) 국제출원번호 PCT/US2008/070647

(87) 국제공개번호 WO 2009/015084

국제공개일자 2009년01월29일

(30) 우선권주장

12/176,095 2008년07월18일 미국(US)

60/950,974 2007년07월20일 미국(US)

(56) 선행기술조사문헌

US20050117796 A1\*

W02006063268 A2\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

케이엘에이-텐코어 코오포레이션

미국 캘리포니아 밀피타스 원 테크놀로지 드라이

브 (우: 95035)

(72) 발명자

바스카, 크리스

미국 95120 캘리포니아 샌어제이 퀸브릿지 코트

1061

맥코드, 마크

미국 94040 캘리포니아 마운틴 뷰 보니타 애브뉴

1273

(뒷면에 계속)

(74) 대리인

이시용, 정현주

전체 청구항 수 : 총 44 항

심사관 : 박성호

(54) 발명의 명칭 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 방법들 및 웨이퍼를 검사하기 위한 방법들

**(57) 요 약**

다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 방법들 및 웨이퍼를 검사하기 위한 방법들이 제공된다. 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 하나의 컴퓨터-구현 방법은 웨이퍼 상에 중앙에 위치한 다이 및 상기 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 상기 방법은 또한 상기 출력의 내부 다이 위치들에 기초하여 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계를 포함한다. 추가로, 상기 방법은 상기 결합 단계의 결과들에 기초하여 상기 표준 기준 다이를 생성하는 단계를 포함한다.

**대 표 도** - 도3

(72) 발명자

바타차리야, 산토시

미국 95123 캘리포니아 샌어제이 쿠니 플레이스

5440

리양, 아디스

미국 94539 캘리포니아 프레몬트 임페리오 플레이

스 40367

월링포드, 리차드

미국 95118 캘리포니아 샌어제이 젠킨스 애브뉴

3749

---

알렌도르퍼, 후베르트

미국 94035 캘리포니아 레드우드 쇼어스 메리디안

드라이브 324

마야, 카이스

미국 95014 캘리포니아 쿠퍼티노 포그 웨이 20667

아파트먼트 334

## 특허청구의 범위

### 청구항 1

다이 대 표준 기준 다이 검사(die to standard reference die inspection)에서의 이용을 위한 표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법으로서,

웨이퍼 상에 중앙에 위치한 다이 및 상기 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 검사 시스템의 출력을 획득하는 단계;

상기 출력의 내부 다이 위치(within die position)들에 기초하여 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계 – 상기 출력은 그레이 페넬들을 포함하고, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐서 상기 그레이 페넬들의 평균값 및 중간값을 결정하는 단계를 포함함 –; 및

상기 결합의 결과들에 기초하여 상기 표준 기준 다이를 생성하는 단계

를 포함하고,

상기 표준 기준 다이는 상기 내부 다이 위치들에 걸친 상기 평균값을 포함하고,

상기 방법은, 상기 내부 다이 위치들에 걸친 상기 중간값의 추가적인 표준 기준 다이를 생성하는 단계를 더 포함하는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

### 청구항 2

제 1 항에 있어서,

상기 표준 기준 다이는 이미지를 포함하는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

### 청구항 3

제 1 항에 있어서,

상기 다이 대 표준 기준 다이 검사는 리피터 결함(repeater defect)들에 대한 검사를 포함하는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

### 청구항 4

제 1 항에 있어서,

상기 표준 기준 다이는 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에서의 랜덤 결함들로부터의 어떠한 잡음도 포함하지 않는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

### 청구항 5

제 1 항에 있어서,

상기 표준 기준 다이를 디자인 데이터 공간(design data space)에 정렬시키는 단계를 더 포함하고,

상기 결합의 결과들에 기초하여 상기 표준 기준 다이를 생성하는 단계는, 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함하는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

### 청구항 6

제 1 항에 있어서,

상기 결합하는 단계는, 상기 내부 다이 위치들에 걸친 상기 출력의 특성 및 상기 내부 다이 위치들에 걸친 상기 특성에서의 잡음을 결정하는 단계를 포함하는,

표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법.

#### 청구항 7

웨이퍼를 검사하기 위한 방법으로서,

상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계;

상기 출력의 내부 다이 위치들에 기초하여 상기 웨이퍼 상에 중앙에 위치한 다이 및 상기 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계 – 상기 출력은 그레이 레벨들을 포함하고, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐서 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 단계를 포함함 –;

상기 결합의 결과들에 기초하여 표준 기준 다이를 생성하는 단계 – 상기 표준 기준 다이는 상기 내부 다이 위치들에 걸친 평균값을 포함함 –; 및

하나 이상의 테스트 다이들에서의 결함들을 검출하기 위해서 상기 표준 기준 다이를 상기 웨이퍼 상의 상기 하나 이상의 테스트 다이들에 대한 출력과 비교하는 단계

를 포함하고,

상기 방법은, 상기 내부 다이 위치들에 걸친 상기 중간값의 추가적인 표준 기준 다이를 생성하는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 8

제 7 항에 있어서 ,

상기 하나 이상의 테스트 다이들에 대한 출력 및 상기 표준 기준 다이는 이미지를 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 9

제 7 항에 있어서,

상기 방법의 모든 단계들은 상기 웨이퍼의 검사의 런타임(run time) 동안에 수행되는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 10

제 7 항에 있어서,

상기 결함들은 리피터 결함들을 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 11

제 7 항에 있어서,

상기 결함들은, 상기 웨이퍼를 가공하는데에 이용되는 레티클(reticle)의 제조에 의해 야기되는 조직적인 결함(systematic defect)들을 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 12

제 7 항에 있어서,

상기 결함들은 조직적인 결함들을 포함하고, 상기 하나 이상의 테스트 다이들은 프로세스 윈도우 검정 방법론(process window qualification methodology)을 이용하여 상기 웨이퍼 상에서 형성되는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 13

제 7 항에 있어서,

상기 표준 기준 다이는 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에서의 랜덤 결함들로부터의 어떠한 잡음도 포함하지 않는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 14

제 7 항에 있어서,

두 개 이상의 테스트 다이들에 대한 결합된 출력이 상기 하나 이상의 테스트 다이들 각각에 대한 출력보다 랜덤 결함들로부터의 더 적은 잡음을 포함하도록, 상기 하나 이상의 테스트 다이들 중 두 개 이상에 대한 출력을 결합하는 단계를 더 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 15

제 7 항에 있어서,

상기 하나 이상의 테스트 다이들 중 두 개 이상에 대한 상기 출력을 결합하는 단계를 더 포함하고, 상기 비교하는 단계는 상기 두 개 이상의 테스트 다이들에서의 결함들을 검출하기 위해서 상기 표준 다이를 상기 두 개 이상의 테스트 다이들에 대한 상기 결합된 출력과 비교하는 단계를 포함하며, 상기 결함들은 리피터 결함들을 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 16

제 7 항에 있어서,

상기 비교하는 단계는 적응적 스레스홀딩(adaptive thresholding)을 이용하여 수행되는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 17

제 7 항에 있어서,

상기 비교하는 단계는, 상기 하나 이상의 테스트 다이들 및 상기 표준 기준 다이에 대한 히스토그램들의 등화를 이용하여 상기 하나 이상의 테스트 다이들에 대한 상기 출력과 상기 표준 기준 다이를 정렬시키는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 18

제 7 항에 있어서,

상기 비교하는 단계는, 상기 표준 기준 다이에서의 픽셀들의 이웃 및 상기 하나 이상의 테스트 다이들에 대한 상기 출력에서의 픽셀들의 이웃의 템플릿 매칭(template matching)을 포함하는,

웨이퍼를 검사하기 위한 방법.

## 청구항 19

제 7 항에 있어서,

상기 획득하는 단계는 상기 웨이퍼 상의 상기 테스트 다이들 중 일부에 대해서만 상기 출력을 획득하는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

## 청구항 20

제 7 항에 있어서,

상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 더 포함하고,

상기 결합의 결과들에 기초하여 표준 기준 다이를 생성하는 단계는, 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

## 청구항 21

웨이퍼를 검사하기 위한 방법으로서,

표준 기준 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계;

상기 출력의 내부 다이 위치들에 기초하여 상기 표준 기준 웨이퍼 상에 중앙에 위치한 다이 및 상기 표준 기준 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계 – 상기 출력은 그레이 레벨들을 포함하고, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐서 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 단계를 포함함 –;

상기 결합의 결과들에 기초하여 표준 기준 다이를 생성하는 단계 – 상기 표준 기준 다이는 상기 내부 다이 위치들에 걸친 평균값을 포함함 –;

상기 웨이퍼에 대한 상기 검사 시스템의 출력을 획득하는 단계; 및

하나 이상의 테스트 다이들에서의 결합들을 검출하기 위해서, 상기 표준 기준 다이를 상기 웨이퍼 상의 상기 하나 이상의 테스트 다이들에 대한 출력과 비교하는 단계

를 포함하고,

상기 방법은, 상기 내부 다이 위치들에 걸친 상기 중간값의 추가적인 표준 기준 다이를 생성하는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

## 청구항 22

제 21 항에 있어서,

상기 비교하는 단계 이전에 디자인 데이터 공간에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력의 위치 및 상기 표준 기준 다이의 위치를 결정하는 단계, 및

상기 비교하는 단계 이전에 상기 디자인 데이터 공간에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력 및 상기 표준 기준 다이의 위치들에 기초하여 상기 하나 이상의 테스트 다이들에 대한 상기 출력 및 상기 표준 기준 다이를 정렬시키는 단계

를 더 포함하는,

웨이퍼를 검사하기 위한 방법.

## 청구항 23

제 21 항에 있어서,

프레임 대 프레임 정렬 기술(frame by frame alignment technique)을 이용하여 상기 비교하는 단계 이전에 상기 표준 기준 다이를 상기 하나 이상의 테스트 다이들에 대한 상기 출력에 정렬시키는 단계를 더 포함하는, 웨이퍼를 검사하기 위한 방법.

#### 청구항 24

제 21 항에 있어서,

전체적인 정렬(global alignment)에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력의 제1 스와스(swath)를 정렬시키는 단계, 및

상기 하나 이상의 테스트 다이들에 대한 상기 출력의 제2 스와스를 상기 제1 스와스에 정렬시켜 그에 따라 상기 제2 스와스를 상기 전체적인 정렬에 정렬시키는 단계

를 더 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 25

제 21 항에 있어서,

상기 웨이퍼에 대한 상기 검사 시스템의 상기 출력은 상기 웨이퍼 상의 조명 스팟(illumination spot) 당 적어도 두 개의 샘플들을 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 26

제 21 항에 있어서,

상기 웨이퍼에 대한 상기 검사 시스템의 출력을 획득하는 단계는, 상기 웨이퍼 상의 상기 테스트 다이들 중 일부에 대해서만 상기 출력을 획득하는 단계를 포함하는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 27

제 21 항에 있어서,

상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 상기 출력을 획득하는 단계는 광대역 딥 자외선 모드 검사(broadband deep ultraviolet mode inspection)를 이용하여 수행되는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 28

제 21 항에 있어서,

상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 상기 출력을 획득하는 단계는 광대역 에지 콘트라스트 모드 검사(broadband edge contrast mode inspection)를 이용하여 수행되는,

웨이퍼를 검사하기 위한 방법.

#### 청구항 29

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법으로서,

상기 웨이퍼 상에 형성된 구조의 복합 이미지를 생성하기 위해서 상기 구조의 다수의 이미지들을 결합하는 단계 – 상기 다수의 이미지들은 상기 구조가 형성되는 상기 웨이퍼 상의 다수의 위치들에서 획득되고, 상기 다수의 이미지들은 그레이 레벨들을 포함하며, 상기 결합하는 단계는 내부 다이 위치들에 걸쳐서 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 단계를 포함하고, 상기 복합 이미지는 상기 내부 다이 위치들에 걸친 상기 평균값

을 포함함 - ;

상기 내부 다이 위치들에 걸친 상기 중간값의 추가적인 복합 이미지를 생성하는 단계; 및

상기 웨이퍼 상의 결합들을 검출하기 위해서 상기 복합 이미지를 기준과 비교하는 단계

를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 30

제 29 항에 있어서,

상기 결합들은 조직적인 결합들을 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 31

제 29 항에 있어서,

상기 결합들은 상기 구조의 라인 에지 거칠기(line edge roughness)와 동일한 크기를 갖는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 32

제 29 항에 있어서,

상기 결합하는 단계는 상기 다수의 이미지들을 평균하는 단계를 더 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 33

제 29 항에 있어서,

상기 다수의 위치들은 동일한 디자인들을 갖는 셀들에서의 상기 구조의 위치들을 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 34

제 29 항에 있어서,

상기 다수의 위치들은 이웃하는 다이들에서의 상기 구조의 위치들을 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 35

제 29 항에 있어서,

상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 작은 라인 에지 거칠기를 갖도록

수행되는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 36

제 29 항에 있어서 ,

상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 작은 랜덤 변화를 갖도록 수행되

는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 37

제 29 항에 있어서,

상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 낮은 그레이 레벨 잡음을 갖도록 수행되는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 38

제 29 항에 있어서,

상기 기준은 상기 구조의 기지의 양호한 이미지를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 39

제 29 항에 있어서,

상기 기준은 표준 기준 다이에서 획득된 상기 구조의 이미지를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 40

제 29 항에 있어서,

상기 기준은 기준 이미지, 복합 테스트 이미지, 또는 프로세스 윈도우 검정 다이에서 획득되는 상기 구조의 기준 이미지 및 복합 테스트 이미지를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 41

제 29 항에 있어서,

상기 기준은 렌더링된(rendered) 데이터베이스 이미지를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 42

제 29 항에 있어서,

상기 기준은, 상기 웨이퍼 상의 또는 상이한 웨이퍼 상의 다수의 위치들에서 획득되는 다수의 이미지들로부터 생성되는 상기 구조의 복합 이미지를 포함하는,

웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법.

### 청구항 43

웨이퍼 상의 결합들을 검출하도록 구성되는 시스템으로서,

상기 웨이퍼 상에 형성된 구조의 다수의 이미지들을 획득하도록 구성되는 검사 시스템; 및

상기 구조의 복합 이미지를 생성하기 위해서 상기 다수의 이미지들을 결합하고 – 상기 다수의 이미지들은 상기 구조가 형성되는 상기 웨이퍼 상의 다수의 위치들에서 획득되고, 상기 다수의 이미지들은 그레이 레벨들을 포함하며, 상기 결합하는 것은 내부 다이 위치들에 걸쳐 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 것을 포함하고, 상기 복합 이미지는 상기 내부 다이 위치들에 걸친 상기 평균값을 포함함 –, 상기 내부 다이 위치들에 걸쳐 상기 중간값의 추가적인 복합 이미지를 생성하며, 그리고 상기 웨이퍼 상의 결합들을 검출하기 위해서 상기 복합 이미지를 기준과 비교하도록 구성되는 컴퓨터 시스템

을 포함하는,

웨이퍼 상의 결함들을 검출하도록 구성되는 시스템.

#### 청구항 44

컴퓨터 판독가능 매체로서,

웨이퍼 상의 결함들을 검출하기 위한 컴퓨터-구현 방법을 수행하기 위한 컴퓨터 시스템 상에서 실행가능한 프로그램 명령들을 포함하고,

상기 컴퓨터-구현 방법은,

상기 웨이퍼 상에 형성된 구조의 복합 이미지를 생성하기 위해서 상기 구조의 다수의 이미지들을 결합하는 단계 – 상기 다수의 이미지들은 상기 구조가 형성되는 상기 웨이퍼 상의 다수의 위치들에서 획득되고, 상기 다수의 이미지들은 그레이 레벨들을 포함하며, 상기 결합하는 단계는 내부 다이 위치들에 걸쳐 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 단계를 포함하고, 상기 복합 이미지는 상기 내부 다이 위치들에 걸친 상기 평균값을 포함함 –,

상기 내부 다이 위치들에 걸쳐 상기 중간값의 추가적인 복합 이미지를 생성하는 단계, 및

상기 웨이퍼 상의 결함들을 검출하기 위해서 상기 복합 이미지를 기준과 비교하는 단계

를 포함하는,

컴퓨터 판독가능 매체.

#### 청구항 45

삭제

### 명세서

#### 기술 분야

[0001]

본 발명은 다이 대 표준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 방법들 및 웨이퍼를 검사하기 위한 방법들에 관한 것이다. 특정한 실시예들은 웨이퍼 상의 중앙에 위치한 다이에 대한 검사 시스템의 출력 및 상기 출력의 내부 다이 위치들에 기초하여 상기 웨이퍼 상에 위치한 하나 이상의 다이들을 결합시키는 것을 포함하는, 표준 기준 다이 검사로의 다이에서의 이용을 위한 표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법에 관한 것이다.

#### 배경 기술

[0002]

이하의 설명 및 예들은 이 섹션에서의 그들의 포함에 의해서 종래 기술로 인정되는 것이 아니다.

[0003]

논리 및 메모리 장치들과 같은 반도체 장치들을 제조하는 것은 상기 반도체 장치들의 다수의 레벨들 및 다양한 특징들을 형성하기 위해서 많은 수의 반도체 제조 프로세스들을 이용하여 반도체 웨이퍼와 같은 기판을 프로세싱하는 것을 일반적으로 포함한다. 예컨대, 리소그래피(lithography)는 레티클(reticle)로부터 반도체 웨이퍼 상에 배열된 레지스트(resist)로 패턴을 전달하는 것을 수반하는 반도체 제조 프로세스이다. 반도체 제조 프로세서들의 추가적인 예들은 화학-기계적 연마(CMP), 에칭, 증착, 및 이온 주입을 포함하지만 이들에 제한되는 것은 아니다. 다수의 반도체 장치들은 단일의 반도체 웨이퍼 상에서 배열되어 제조될 수 있고 그 후에 개별 반도체 장치들로 분리될 수 있다.

[0004]

제조 프로세스에서 높은 수율을 그리고 이에 따라서 더 높은 이익들을 촉진하도록 웨이퍼들 상에서의 결함들을 검출하기 위해서, 반도체 제조 프로세스 동안에 다양한 단계들에서 검사 프로세스들이 이용된다. 검사는 항상 IC들과 같은 반도체 장치들을 제조하는 것의 중요한 부분이 되어 왔다. 하지만, 반도체 장치들의 치수들이 감소함에 따라, 허용가능한 반도체 장치들의 성공적인 제조에는 검사가 더욱 중요해졌는데, 그 이유는 더 작은 결함들이 장치들의 고장을 야기할 수 있기 때문이다. 예컨대, 반도체 장치들의 치수들이 감소함에 따라 감소하는 크기의 결함들의 검출이 필수적이게 되었고, 그 이유는 상대적으로 작은 결함들일지라도 상기 반도체 장치들에서 원하지 않는 변형들을 야기할 수 있기 때문이다.

[0005]

디자인 룰(design rule)이 축소됨에 따라, 반도체 제조 프로세스들은 또한 상기 프로세스들의 성능 능력 상의

제한들에 보다 가깝게 동작하고 있을 수 있다. 추가로, 더 작은 디자인 룰들에서, 일부의 경우들에서 고장을 일으키는 프로세스가 조직적이게 되는 경향이 있다. 즉, 장애를 일으키는 프로세스는 상기 디자인 내에서 종종 여러 번 반복되는 미리 결정된 디자인 패턴들에서 장애가 발생하는 경향이 있다. 공간적으로 조직적인, 전기적으로 관련된 결함들의 검출 및 제거가 중요한데, 그 이유는 그러한 결함들을 제거하는 것이 수율에 있어 상당히 포괄적인 영향을 미치기 때문이다.

[0006] 하지만, 다이-대-다이 검사 및 다이 대 표준 기준 다이 검사와 같은 검사 기술들을 이용하여 조직적이고 다른 리피터(repeater) 결함들을 검출하는 것은 많은 이유들로 바람직하지 않다. 예컨대, 다이-대-다이 검사 기술들이 임의의 결함들의 검출을 위해 웨이퍼 검사에서 광범위한 성공을 성취하였음에도 불구하고, 그들의 특성에 의해 그러한 검사 기술들은 조직적 리피터 결함들을 검출할 수 없다. 특히, 두 개의 테스트 다이를 서로 비교함으로써, 두 테스트 다이에서 발생하는 조직적 리피터 결함들은 검출될 수 없다. 추가로, 다이 대 표준 기준 다이 검사 기술들은 어플리케이션 관련 반도체 제조에서 다이-대-다이 검사 기술들보다 훨씬 더 적게 채택되고 있는데, 그 이유는 적합한 표준 기준 다이를 획득하기가 종종 어렵기 때문이다. 예컨대, 비교되는 다이들에 대한 출력이 일반적으로 웨이퍼의 동일한 검사 스캔에서 획득되는 다이-대-다이 검사 기술들과는 달리, 다이 대 표준 기준 다이 기술들은 종종 복잡한데, 그 이유는 컬러 변화들과 같은 테스트 다이 및 표준 기준 다이 사이의(또는 테스트 웨이퍼 및 표준 기준 웨이퍼 사이) 차이들 때문이고, 그리고 테스트 다이와 표준 기준 다이 사이에 상대적으로 정확한 정렬을 획득하는 것이 어렵기 때문이다.

[0007] 따라서, 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 방법, 및 다이 레티를 검사 및 프로세스 윈도우 검정(PWQ; process window qualification) 어플리케이션들과 같은 어플리케이션들에 대해 상대적으로 높은 정확도로 리피터(조직적) 결함들을 검출하는데에 이용될 수 있는 다이 대 표준 다이 기준 검사를 이용하는 웨이퍼를 검사하기 위한 방법을 개발하는 것이 바람직하다.

### 발명의 내용

[0008] 다양한 방법 실시예들의 이하의 기술은 첨부된 청구항들의 주제 내용들을 제한하는 것으로서 어떠한 방식으로도 해석되지는 않는다.

[0009] 일 실시예는 다이 대 표준 기준 다이 검사(die to standard reference die inspection)에서의 이용을 위한 표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법에 관한 것이다. 상기 방법은 웨이퍼 상에 중앙에 위치한 다이 및 상기 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 상기 방법은 또한 상기 출력의 내부 다이 위치(within die position)들에 기초하여 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계를 포함한다. 추가로, 상기 방법은 상기 결합의 결과들에 기초하여 상기 표준 기준 다이를 생성하는 단계를 포함한다.

[0010] 일 실시예에서, 상기 표준 기준 다이는 이미지를 포함한다. 다른 실시예에서, 상기 다이 대 표준 기준 다이 검사는 리피터 결함들에 대한 검사를 포함한다. 추가의 실시예에서, 상기 표준 기준 다이는 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에서의 랜덤 결함들로부터 실질적으로 어떠한 잡음도 포함하지 않는다. 추가의 실시예에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간(design data space)에 정렬시키는 단계를 포함한다. 그러한 일 실시예에서, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함한다.

[0011] 일 실시예에서, 상기 출력은 그레이 레벨들을 포함한다. 그러한 일 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐 상기 그레이 레벨들의 평균값을 결정하는 단계를 포함한다. 그러한 다른 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐서 상기 그레이 레벨들의 중간값을 결정하는 단계를 포함한다. 그러한 추가의 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐서 상기 그레이 레벨들의 평균값 및 중간값을 결정하는 단계를 포함한다. 그러한 실시예에서, 상기 표준 기준 다이는 상기 내부 다이 위치들에 걸친 상기 평균값을 포함하고, 상기 방법은 상기 내부 다이 위치들에 걸친 상기 중간값의 추가적인 표준 기준 다이를 생성하는 단계를 포함한다. 일부의 실시예들에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸친 상기 출력의 특성(characteristic) 및 상기 내부 다이 위치들에 걸친 상기 특성에서의 잡음을 결정하는 단계를 포함한다.

[0012] 상기한 방법의 단계들 각각은 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다. 상기한 방법의 실시예들 각각은 본 명세서에 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다. 추가로, 상기한 방법의

실시예들 각각은 본 명세서에 기술된 시스템들 중 임의의 시스템에 의해서 수행될 수 있다.

[0013] 다른 실시예는 웨이퍼를 검사하기 위한 방법에 관한 것이다. 상기 방법은 상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 상기 방법은 또한 상기 출력의 내부 다이 위치들에 기초하여 상기 웨이퍼 상에 중앙에 위치한 다이 및 상기 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계를 포함한다. 추가로, 상기 방법은 상기 결합의 결과들에 기초하여 표준 기준 다이를 생성하는 단계를 포함한다. 상기 방법은 하나 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 상기 표준 기준 다이를 상기 웨이퍼 상의 상기 하나 이상의 테스트 다이들에 대한 상기 출력과 비교하는 단계를 더 포함한다.

[0014] 일 실시예에서, 상기 표준 기준 다이 및 상기 하나 이상의 테스트 다이들에 대한 상기 출력은 이미지들을 포함한다. 다른 실시예에서, 상기 방법의 모든 단계들이 상기 웨이퍼의 검사의 런타임(run time) 동안에 수행된다.

[0015] 일부의 실시예들에서, 상기 결합들은 리피터 결함(repeater defect)들을 포함한다. 다른 실시예에서, 상기 결합들은 상기 웨이퍼를 가공하는데 이용되는 레티클(reticle)의 제조에 의해 야기되는 조직적인 결함(systematic defect)들을 포함한다. 추가의 실시예에서, 상기 결합들은 조직적인 결합들을 포함하고, 상기 하나 이상의 테스트 다이들은 프로세스 원도우 검정(PWQ) 방법을 이용하여 상기 웨이퍼 상에서 형성된다.

[0016] 일 실시예에서, 상기 표준 기준 다이는 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에서의 랜덤 결합들로부터 실질적으로 어떠한 잡음도 포함하지 않는다. 다른 실시예에서, 상기 방법은 두 개 이상의 테스트 다이들에 대한 결합된 출력이 상기 하나 이상의 테스트 다이들 각각에 대한 출력보다 랜덤 결합들로부터 더 적은 잡음을 포함하도록, 상기 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하는 단계를 포함한다. 추가의 실시예에서, 상기 방법은 상기 하나 이상의 테스트 다이들의 두 개 이상에 대한 상기 출력을 결합하는 단계를 더 포함하고, 상기 비교하는 단계는 상기 두 개 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 상기 표준 기준 다이를 상기 두 개 이상의 테스트 다이들에 대한 상기 결합된 출력과 비교하는 단계를 포함한다. 그러한 일 실시예에서, 상기 결합들을 리피터 결합들을 포함한다.

[0017] 일 실시예에서, 상기 비교하는 단계는 적응적 스레스홀딩(adaptive thresholding)을 이용하여 수행된다. 다른 실시예에서, 상기 비교하는 단계는, 상기 표준 기준 다이 및 상기 하나 이상의 테스트 다이들에 대한 히스토그램들의 등화를 이용하여 상기 하나 이상의 테스트 다이들에 대한 상기 출력과 상기 표준 기준 다이를 정렬시키는 단계를 포함한다. 추가의 실시예에서, 상기 비교하는 단계는, 상기 표준 기준 다이에서의 픽셀들의 이웃 및 상기 하나 이상의 테스트 다이들에 대한 상기 출력에서의 픽셀들의 이웃의 템플릿 매칭(template matching)을 포함한다.

[0018] 일 실시예에서, 상기 획득하는 단계는 상기 웨이퍼 상의 상기 테스트 다이들의 일부에 대해서만 상기 출력을 획득하는 단계를 포함한다. 다른 실시예에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 더 포함한다. 그러한 일 실시예에서, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함한다.

[0019] 상기한 방법의 단계들 각각은 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다. 상기한 방법의 실시예들 각각은 본 명세서에 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다. 추가로, 상기한 방법의 실시예들 각각은 본 명세서에 기술된 시스템들 중 임의의 시스템에 의해서 수행될 수 있다.

[0020] 추가의 실시예들은 웨이퍼를 검사하기 위한 다른 방법에 관한 것이다. 이 방법은 표준 기준 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 상기 방법은 또한 상기 출력의 내부 다이 위치들에 기초하여 상기 표준 웨이퍼 상에 중앙에 위치한 다이 및 상기 표준 기준 웨이퍼 상에 위치한 하나 이상의 다이들에 대한 상기 출력을 결합하는 단계를 포함한다. 추가로, 상기 방법은 상기 결합의 결과들에 기초하여 표준 기준 다이를 생성하는 단계를 포함한다. 상기 방법은 상기 웨이퍼에 대한 상기 검사 시스템의 출력을 획득하는 단계를 더 포함한다. 게다가, 상기 방법은 하나 이상의 테스트 다이들에서의 결합들을 검출하기 위해서, 상기 표준 기준 다이를 상기 웨이퍼 상의 상기 하나 이상의 테스트 다이들에 대한 출력과 비교하는 단계를 포함한다.

[0021] 일 실시예에서, 상기 결합들은 리피터 결합들을 포함한다. 다른 실시예에서, 상기 결합들은 상기 웨이퍼를 가공하는데 이용되는 레티클을 제조에 의해 야기되는 조직적인 결합들을 포함한다. 추가의 실시예에서, 상기 결합들은 조직적인 결합들을 포함하고, 상기 하나 이상의 테스트 다이들은 PWQ 방법론을 이용하여 상기 웨이퍼 상에서 형성된다.

- [0022] 일부의 실시예들에서, 상기 표준 기준 다이는 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에서의 랜덤 결합들로부터 실질적으로 어떠한 잡음도 포함하지 않는다. 다른 실시예에서, 두 개 이상의 테스트 다이들에 대한 결합된 출력이 상기 하나 이상의 테스트 다이들 각각에 대한 출력보다 랜덤 결합들로부터 더 적은 잡음을 포함하도록, 상기 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하는 단계를 더 포함한다. 추가의 실시예에서, 상기 하나 이상의 테스트 다이들의 두 개 이상에 대한 상기 출력을 결합하는 단계를 더 포함하고, 상기 비교하는 단계는 상기 두 개 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 상기 표준 기준 다이를 상기 두 개 이상의 테스트 다이들에 대한 상기 결합된 출력과 비교하는 단계를 포함한다. 그러한 일 실시예에서, 상기 결합들을 리피터 결합들을 포함한다.

- [0023] 일 실시예에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 포함한다. 그러한 일 실시예에서, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함한다. 다른 실시예에서, 상기 방법은 상기 비교하는 단계 이전에 디자인 데이터 공간에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력의 위치 및 상기 표준 기준 다이의 위치를 결정하는 단계, 및 상기 비교하는 단계 이전에 상기 디자인 데이터 공간에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력 및 상기 표준 기준 다이의 위치들에 기초하여 상기 하나 이상의 테스트 다이들에 대한 상기 출력 및 상기 표준 기준 다이를 정렬시키는 단계를 포함한다.

- [0024] 일 실시예에서, 상기 방법은 프레임 바이 프레임 정렬 기술(frame by frame alignment technique)을 이용하여 상기 비교하는 단계 이전에 상기 표준 기준 다이를 상기 하나 이상의 테스트 다이들에 대한 상기 출력에 정렬시키는 단계를 포함한다. 다른 실시예에서, 상기 방법은 전체적인 정렬에 대해서 상기 하나 이상의 테스트 다이들에 대한 상기 출력의 제1 스와스(swath)를 정렬시키는 단계, 및 상기 하나 이상의 테스트 다이들에 대한 상기 출력의 제2 스와스를 상기 제1 스와스에 정렬시켜 그에 따라 상기 제2 스와스를 상기 전체적인 정렬에 정렬시키는 단계를 포함한다.

- [0025] 일 실시예에서, 상기 비교하는 단계는 적응적 스팬서홀딩을 이용하여 수행된다. 다른 실시예에서, 상기 비교하는 단계는 상기 표준 기준 다이 및 상기 하나 이상의 테스트 다이들에 대한 히스토그램들의 등화를 이용하여 상기 하나 이상의 테스트 다이들에 대한 상기 출력과 상기 표준 기준 다이를 정렬시키는 단계를 포함한다. 추가의 실시예에서, 상기 웨이퍼에 대한 상기 검사 시스템의 상기 출력은 상기 웨이퍼 상의 조명 스팟(illumination spot) 당 적어도 두 개의 샘플들을 포함한다.

- [0026] 일 실시예에서, 상기 웨이퍼에 대한 상기 검사 시스템의 상기 출력을 획득하는 단계는 상기 웨이퍼 상의 상기 테스트 다이들의 일부에 대해서만 상기 출력을 획득하는 단계를 포함한다. 다른 실시예에서, 상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 상기 출력을 획득하는 단계는 광대역 딥 자외선 모드 검사(broadband deep ultraviolet mode inspection)를 이용하여 수행된다. 추가의 실시예에서, 상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 상기 출력을 획득하는 단계는 광대역 에지 콘트라스트 모드 검사(broadband edge contrast mode inspection)를 이용하여 수행된다. 일부의 실시예들에서, 상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 상기 출력을 획득하는 단계는 전자 빔 검사를 이용하여 수행된다.

- [0027] 상기한 방법의 단계들 각각은 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다. 상기한 방법의 실시예들 각각은 본 명세서에 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다. 추가로, 상기한 방법의 실시예들 각각은 본 명세서에 기술된 시스템들 중 임의의 시스템에 의해서 수행될 수 있다.

- [0028] 추가의 실시예는 웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법에 관한 것이다. 상기 방법은 상기 웨이퍼 상에 형성된 구조의 복합 이미지를 생성하기 위해서 상기 구조의 다수의 이미지들을 결합하는 단계를 포함한다. 상기 다수의 이미지들은 상기 구조가 형성되는 상기 웨이퍼 상의 다수의 위치들에서 획득된다. 상기 방법은 또한 상기 웨이퍼 상에서 결합들을 검출하기 위해서 상기 복합 이미지를 기준과 비교하는 단계를 포함한다.

- [0029] 일 실시예에서, 상기 결합들은 조직적인 결합들을 포함한다. 다른 실시예에서, 상기 결합들은 상기 구조의 라인 에지 거칠기(line edge roughness)와 거의 동일한 크기를 갖는다.

- [0030] 일 실시예에서, 상기 결합하는 단계는 상기 다수의 이미지들을 평균하는 단계를 포함한다. 일부의 실시예들에서, 상기 다수의 위치들은 동일한 디자인들을 갖는 셀들에서의 상기 구조의 위치들을 포함한다. 다른 실시예들에서, 상기 다수의 위치들은 이웃하는 다이들에서의 상기 구조의 위치들을 포함한다.

- [0031] 일 실시예에서, 상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 작은 라인 에지

거칠기를 갖도록 수행된다. 다른 실시예에서, 상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 작은 랜덤 변화를 갖도록 수행된다. 추가의 실시예에서, 상기 결합하는 단계는 상기 복합 이미지가 상기 다수의 이미지를 각각보다 더 낮은 그레이 톤을 갖도록 수행된다.

[0032] 일 실시예에서, 상기 기준은 상기 구조의 기지의 양호한 이미지를 포함한다. 다른 실시예에서, 상기 기준은 표준 기준 다이에서 획득된 상기 구조의 이미지를 포함한다. 추가의 실시예에서, 상기 기준은 기준 이미지, 복합 테스트 이미지, 또는 프로세스 윈도우 검정 다이에서 획득되는 상기 구조의 기준 이미지 및 복합 테스트 이미지를 포함한다. 추가의 실시예에서, 상기 기준은 렌더링된(rendered) 데이터베이스 이미지를 포함한다. 일부의 실시예들에서, 상기 기준은, 상기 웨이퍼 상의 또는 상이한 웨이퍼 상의 다수의 위치들에서 획득되는 다수의 이미지들로부터 생성되는 상기 구조의 복합 이미지를 포함한다.

[0033] 상기한 방법의 각 단계들은 본 명세서에 추가로 기술되는 바와 같이 구현될 수 있다. 상기한 방법의 각 실시예들은 본 명세서에 기술된 다른 단계(들) 및 임의의 방법(들)을 포함할 수 있다. 추가로, 상기한 방법의 각 실시예들은 본 명세서에 기술된 임의의 시스템들에 의해서 실시될 수 있다.

### 도면의 간단한 설명

[0034] 본 발명의 추가적인 장점들이 바람직한 실시예들의 이후의 상세한 설명의 이익 및 첨부된 도면들을 참조하여 본 기술분야에서 통상의 지식을 가진 자에게는 명확하게 될 수 있다:

도 1은 협대역 명시야 이미징(narrow band bright field imagin)에서의 구형파 함수 상에서의 단일층의 물질의 위상 콘트라스트 효과들을 기술하는 일련의 플롯들을 도시한다.

도 2는 협대역 에지 콘트라스트 모드 이미징에서 구형파 함수 상에서의 단일층의 물질의 위상 콘트라스트 효과들을 기술하는 일련의 플롯들을 도시한다.

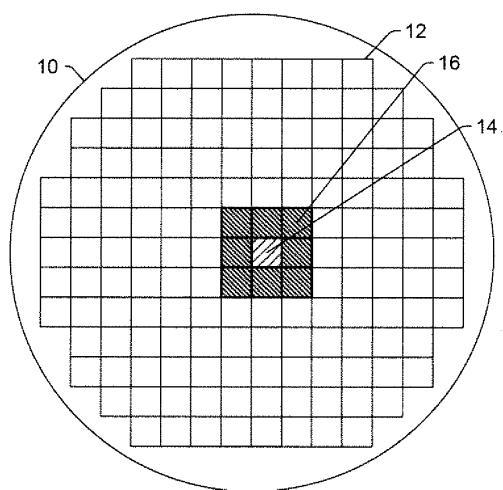

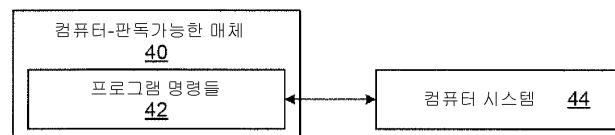

도 3은 웨이퍼 상에 위치한 하나 이상의 다이들 및 웨이어 상에 중앙 위치한 다이의 일 실시예의 평면도를 도시하는 개략적인 다이어그램이다.

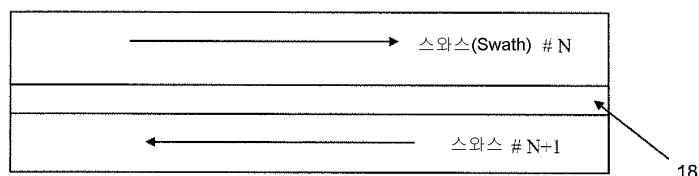

도 4는 웨이터에 대해 획득된 출력의 연속적 스와스(swath)들의 일 실시예의 평면도를 도시하는 개략적인 다이어그램이다.

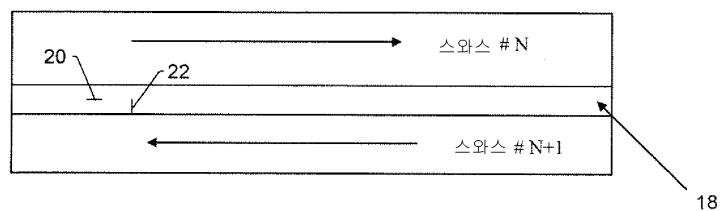

도 5는 웨이퍼에 대해 획득된 출력의 연속적 스와스들의 일 실시예의 평면도, 및 스와스 중첩 영역에서의 출력을 이용하여 다른 스와스에 대해 하나의 스와스의 위치를 결정하기 위한 전역 정렬을 기술하는 개략적인 다이어그램이다.

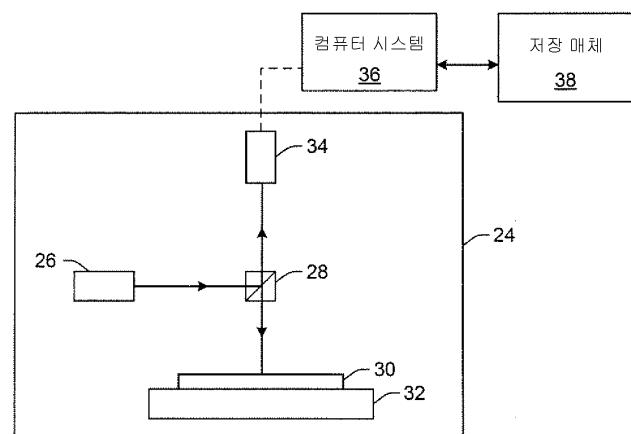

도 6은 본 명세서에 기술된 하나 이상의 실시예들을 수행하도록 구현되는 시스템의 일 실시예의 측면도를 도시하는 개략적인 다이어그램이다.

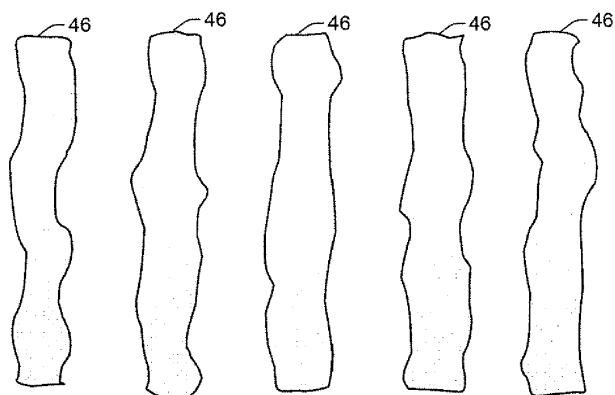

도 7은 본 명세서에 기술된 하나 이상의 실시예들을 수행하기 위한 컴퓨터 프로그램 상에서 실행가능한 컴퓨터 명령들을 포함하는 컴퓨터-판독가능한 매체의 일 실시예를 기술하는 블록도이다.

도 8은 웨이퍼 상에서 형성되는 다수의 이미지를 구조의 다양한 예들을 기술하는 개략적인 다이어그램이다.

도 9는 도 8에 도시된 다수의 이미지를 구조를 결합함으로써 생성되는 도 8의 이미지에 도시된 구조의 복합 이미지의 일 예를 기술하는 개략적인 다이어그램이다.

본 발명이 다양한 수정들 및 대안적 형태들을 가질 수 있는 한편, 그것의 특정한 실시예들은 도면들에서의 예에 의해 도시되고 본 명세서에서 상세하게 기술될 수 있다. 상기 도면들은 스케일링되지 않을 수 있다. 하지만, 상기 도면들 및 상세한 설명들이 본 발명의 개시된 특정한 형태로 본 발명을 제한하려는 의도가 아니고, 본 발명은 첨부된 청구항들에 의해서 정의되는 바와 같이 본 발명의 범위 및 사상 내에 있는 모든 수정들, 균등물들 및 대안들을 모두 커버하고자 하는 의도이다.

### 발명을 실시하기 위한 구체적인 내용

[0035] 본 명세서에서 이용되는 바로서, 용어 "웨이퍼(wafer)"는 일반적으로 반도체 또는 비반도체 물질로 형성되는 기판을 지칭한다. 그러한 반도체 또는 비반도체 물질의 예들은 단결정 실리콘, 갈륨 비소, 및 인듐 인화물을 포함하지만 이에 한정되지는 않는다. 그러한 기판들은 반도체 제조 설비들에서 공통으로 발견되거나 그리고/또는 프로세싱될 수 있다.

- [0036] 웨이퍼는 기판 상에 형성된 하나 이상의 층들을 포함할 수 있다. 예컨대, 그러한 층들은 레지스트(resist), 유전체 물질, 및 전도성 물질을 포함할 수 있지만, 이에 한정되지는 않는다. 그러한 층들의 많은 다른 타입들이 당업계에 알려져 있고, 본 명세서에서 이용되는 바와 같은 용어 웨이퍼는 그러한 층들의 모든 타입을 포함하는 웨이퍼를 포괄하려는 의도이다.

- [0037] 웨이퍼 상에 형성된 하나 이상의 층들은 패터닝되거나 또는 패터닝되지 않을 수 있다. 예컨대, 웨이퍼는 다수의 다이(die)들을 포함할 수 있고, 각각의 다이는 반복가능한 패터닝된 특징들을 갖는다. 물질들의 그러한 층들의 형성 및 프로세싱은 최종적으로 완성된 장치들에 이르게 할 수 있다. 집적 회로(IC)들과 같은 많은 상이한 타입의 장치들이 웨이퍼 상에서 형성될 수 있고, 본 명세서에서 사용되는 바와 같은 용어 웨이퍼는 당업계에 알려진 임의의 타입의 장치가 제작되는 웨이퍼를 포괄하려는 의도이다.

- [0038] 이제 도면들로 돌아와서, 도면들이 일정한 비율로 도시되지 않았음이 주목된다. 특히, 도면들에서의 일부 엘리먼트들의 스케일은 상기 엘리먼트들의 특징들을 강조하기 위해서 매우 과장된다. 도면들이 동일한 스케일로 도시되지 않았음이 또한 주목된다. 유사하게 구성될 수 있는 하나 이상의 도면에 도시된 엘리먼트들은 동일한 참조 번호들을 이용하여 표시된다.

- [0039] 본 명세서에 기술된 실시예들은 일반적으로 조직적인 (리피터) 결함들에 대한 알고리즘적 접근법들에 대한 사고의 새로운 방식들에 기초한다. 최근에는, 검사 시스템 소비자들이 검사 시스템이 조직적인 또는 리피터 결함들을 검출하는데에 이용될 수 있는 "표준 기준 다이 특성"을 포함하도록 요청하기 시작했다. 그러한 요청들은, 결정 성장 결함들이 프린트 가능할 때 웨이퍼들 상의 리피터 결함들을 야기하는 레티클들 상에서의 상기 결정 성장 결함들에 대한 우려들로부터 생겨났다. 상기 레티클이 단일 다이 레티클이면, 종래의 다이-대-다이 검사 접근법은 그러한 결함들을 검출할 수 없는데, 그 이유는 기준 비교 다이가 존재하지 않기 때문이다. 그러한 결정 성장 결함들을 검출하기 위한 가장 민감한 접근법은 본질적으로 반사된 그리고 전송된 광을 이용하여 검사하도록 구성되는 레티클 검사 시스템들을 이용하여 상기 레티클을 검사하는 것이고, 그러한 레티클 검사 시스템들은 KLA-Tencor, San Jose, California로부터 이용가능하다. 추가로, 그러한 시스템들을 이용하는 레티클 검사의 주파수가 형성 이후에 상대적으로 바로 상기 결정 성장 결함들을 검출하기 위해 증가될 수 있고, 따라서 웨이퍼 제조 상에서의 그러한 결함들의 부작용들을 감소시킬 수 있다.

- [0040] 하지만, 표준 기준 다이 검사 접근법(양호한 것으로 알려진 표준 기준 다이가 저장되고 그 후에 샘플과 비교되는)에 대한 요구가 여전히 남아있다. 추가로, 현재에는 그러한 검사 접근법에 대한 광범위한 요구가 존재하지 않음에도 불구하고(예컨대, 어쩌면 레티클 검사 시스템들 기반의 반사된 그리고 전송된 신호의 상대적으로 많은 채택 및/또는 상대적으로 고가의 단일 다이 레티클들의 제한된 이용 때문에), 효율적인 해결책의 전개를 보장하기 위해 표준 기준 다이 검사에 대한 충분한 요구가 존재한다. 게다가, 표준 기준 다이 기반의 검사로의 새로운 접근법이 바람직한데, 그 이유는 기준 웨이퍼 및 테스트 웨이퍼 간의 프로세스 잡음 차이들로 인해 이전에 이용된 표준 기준 다이 기반의 검사들이 일반적으로 종래의 다이-대-다이 비교들의 민감도를 결여하기 때문이다.

- [0041] 표준 기준 다이 기반의 검사 방법들은 리피터 (조직적인) 결함들을 검출하는데에 특히 유용하다. 추가로, 본래 위치에 리피터 결함들을 검출하기 위해 ADI(after develop inspection)에 대한 명시야(BF; bright field) 검사 시스템을 이용하는 것이 요망되고, 그에 따라 다수의 웨이퍼들이 최고급(high end) 단일 다이 레티클들을 이용해 프린트되는 웨이퍼들 상에서 제로 수율(zero yield)의 제조를 경험하지 않게 해준다. 웨이퍼들의 표준 기준 다이 기반의 검사를 수행하기 위한 다른 추진력은, 상기 웨이퍼들 상에서 프린트되는 리피터 결함들만이 검출될 웨이퍼들 상에서 리피터 결함들을 검사하는 것이다. 대조적으로, 잠재적 리피터 결함들에 대한 레티클을 검사함으로써, 웨이퍼들 상에서 프린트할 그리고 프린트하지 않을 리피터 결함들이 검출될 것이다. 게다가, ADI에서 검사하는 것은 필요에 따라 상기 웨이퍼들의 재작업을 가능하게 한다.

- [0042] 제품 웨이퍼들에 대해 획득되는 출력을 이용하여 생성되는 표준 기준 다이가 프로세스 윈도우 마진들의 감소로 인해 발생하는 조직적인 결함들을 검출하는데에 이용될 수 있다는 점에서, 표준 기준 다이 기반의 검사가 또한 PWQ(process window qualification) 방법들에 대해 또한 바람직할 수 있다. 하지만, 최악의(catastrophic) 프로세스 윈도우 마진 상태들이 발생하면, 다이에서의 가장 약한 디자인이 붕괴될 것이다. 불행히도, 그러한 결함들에 대해서 상기 신호가 약할뿐만 아니라 그러한 결함들이 반복되면, 그들은 사실상 단일 다이 리피터 문제이다.

- [0043] 다양한 타입들의 리피터 결함들이 있다. 예컨대, 리피터 결함들은 하드 리피터 결함들, 소프트 리피터 결함들, 및 마지널(marginal) 리피터 결함들을 포함할 수 있다. 하드 리피터 결함들은 검사된 다이들의 대다수(예컨대,

50% 이상)에서 대략 동일한 다이 위치에서 발생하는 결함들로서 본 명세서에서 정의된다. 소프트 리피터 결함들은 검사된 다이들의 소수(예컨대, 약 15% 내지 약 50%)에서 동일한 다이 위치에서 발생하는 결함들로서 본 명세서에서 정의된다. 리피터 결함들의 다른 모든 타입들은 랜덤 결함들(상기 마지막 리피터 결함들)로서 본 명세서에서 정의될 수 있다. 랜덤 결함들은 다소 임의적으로 정의될 수 있고, 상기 결함, 상기 결함의 위치, 상기 결함이 검출되는 다이들의 수, 및 웨이퍼 상에서 수행되는 프로세스에 종속하여 변화할 수 있다. 예컨대, 웨이퍼 상의 100개의 다이들의 검사는 중요한 것으로서 10개의 다이들에서 반복되는 결함을 식별할 수 있다.

[0044] 결정 성장 결함들의 정황에서, 결정 성장이 사실상 발생하지만(일반적으로 상기 레티클의 오픈 영역들에서) 상대적으로 낮은 불투명도를 갖고 그 결과로 웨이퍼 상에서 프린트하지 않는 상황이 종종 발생할 수 있다. 몇몇 다른 지점에서는, 결정 성장 결함들이 프린트하기 시작하고 웨이퍼들 상에서의 상대적으로 낮은 빈도 결함들일 수 있으며(하지만 매 다이 상에서 나타날 수 있음), 예컨대 임계치 이슈(결함들을 검출하는데에 이용되는 임계치에서) 때문에 그들은 산발적으로 발생할 수 있다(소프트 리피터들). 그러한 상황들에서, 일 접근법은 팹(fab)에서의 레티클 검사 시스템들(예컨대, 반사되고 전송되는 광 기반의 레티클 검사 시스템들)을 결함 검토 및/또는 검사 시스템(예컨대, 전자빔 기반 결함 검토 및/또는 검사 시스템들)과 링크시키는 것일 수 있다. 이러한 방식으로, 상기 레티클 상에서의 리피터 결함들이 상기 웨이퍼 상에서 프린트되고 있고 그리고 상기 웨이퍼 검사 시스템이 상기 결함들을 검출하고 있지 않은지를 결정하기 위해서, 레티클 검사 시스템 및 결함 검토 시스템의 출력이 이용될 수 있다. 예컨대, 쇼트 루프 검토 검사 사이클 최적화(RICO; review inspection cycle optimization) 타입 실험이 상기 웨이퍼 검사 시스템 및 상기 결함 검토 및/또는 검사 시스템(예컨대, 스캐닝 전자 현미경(SEM; scanning electron microscope)) 사이에서 수행될 수 있다.

[0045] 종래의 결함 검출 접근법들은 다수의 팩터들의 주변에 일반적으로 집중되었다. 그러한 하나의 팩터는 상기 신호(예컨대, 광학 광자들)를 최대화하는 것이다. 다른 팩터는 시스템 잡음(예컨대, 산탄 잡음, 다이-대-다이 정렬 잡음, 왜곡 잡음 등)을 최소화하는 것이다. 추가로, 다른 팩터는 웨이퍼 프로세스 잡음(예컨대, 컬러 잡음, 그레인 잡음, 이전 층 잡음 등)을 최소화하는 것이다. 종래의 결함 검출 접근법들은 또한 일반적으로 테스트 샘플이 적어도 두 개의 기준들과 비교되는 이중 검출 방식들에 기초한다. 몇몇 결함 검출 접근법들은 또한 상기 기준 상에서의 잡음(변화)을 감소시키고자 시도한다(예컨대, MDAT(multiple die auto thresholding)와 같은 알고리즘을 이용함으로써 노이즈(n)의 제곱근( $\sqrt{n}$ ) 만큼 상기 기준에서의 잡음을 감소시킨다). 추가로, 예컨대 거짓 알람들을 감소시키고 결함 검토(예컨대, SEM) 샘플링을 보조하는 것이 가능할 때에, 몇몇 결함 검출 접근법들은 상기 결함들을 제거하려 시도한다. 게다가, 결함 검출 접근법들은 웨이퍼당 스루풋을 최대화하고자 시도하는 경향이 있다(예컨대, 랜덤 결함 검출을 위해, 일부 접근법들은 한 시간 미만에 한 개 내지 두 개의 웨이퍼들 사이에서 검사하려 시도하고, 그에 따라 로트(lot)가 두 시간 이상 동안 지지되지 않도록 SEM 검토가 다른 시간에 수행될 수 있다). 추가로, 상기한 팩터들은 검사가 이용되는 어플리케이션들에 종속하여 변화할 수 있다(예컨대, 상이한 팩터들이 전기 분석(EA; electrical analysis) 및 라인 모니터링(LM; line monitoring)에 대한 검사 접근법들을 생성하기 위해 이용될 수 있다).

[0046] 몇몇 웨이퍼 검사 시스템들은, 검사 시스템의 광학의 분해능 한계의 상당히 미만인 중요 결함 타입을 검출하도록 바람직하게 설계된다. 그러한 검출을 성취하기 위해서, 상기 광학의 출력의 신호대잡음비(S/N)가 일반적으로 최대화된다. 상기 S/N을 최대화하기 위한 몇몇 접근법들은 상기 S/N을 최대화하기 위해 프론트 엔트 알고리즘들을 설계하는 것을 포함할 수 있다. 다른 접근법들은 광학, 어페처(aperture)들 등을 최대화하기 위해, 잠재적 결함 신호를 최대화하기 위해, 그리고 컬러 및 그레인 잡음을 최소화하도록 다양한 알고리즘들을 이용하기 위해서, 테스트 및 기준 웨이퍼들 사이의 동일한 패턴 에일리어싱을 실질적으로 생성(예컨대, KLT-Tencor에 의해 개발된 런타임 정렬(RTA; run time alignment) 특성을 이용하여)하려도 시도하는 것을 포함한다.

[0047] 하지만, 이러한 팩터들은 리피터 결함들을 검출하기 위해 검사 시스템들의 능력에 본질적으로 영향을 주거나 또는 그것을 결정하지 않을 수 있다. 예컨대, 리피터 결함 검출로부터 손상될 수 있는 하나의 팩터는, 랜덤 결함들을 검출하고 제거하기 위한 통계가 본질적으로 단독의 이벤트들을 검출하는 것에 기초하는 것이다. 잡음이 상기 기준 신호에서 감소될 수 있는 한편(그에 의해 "상기 기준 신호를 깨끗하게 한다"), 단독 이벤트 검출에 대한 어떠한 그러한 장치, 알고리즘 또는 방법도 존재하지 않는다. 예컨대, 상기 광학의 분해능 이하의 결함들을 검출하기 위한 몇몇 접근법들은, 결함 신호가 전체 신호로부터 나와 검출될 수 있도록 노이즈 플로어(이는 통산 웨이퍼 프로세스 유발 잡음에 의해 제한됨)로 민감도를 높이는 것, 및 검사를 위해 이용되는 알고리즘들 및 광학들을 조정하는 것을 수반하는 경향이 있다. 하지만, 랜덤 결함 검출과는 대조적으로, 리피터 결함의 위치가 알려지면 결함 검출을 가능하게 하기 위해 보다 많은 옵션들이 이용가능하게 된다.

[0048] 리피터 결함들의 다수의 특징들이 상기 검출 민감도를 증가시키기 위해 채택될 수 있다. 본 명세서에서 고려되

는 두 개의 카테고리들은 레티클 유발 리피터 결함들(팹에서) 및 PWQ 타입 조직적 최악 리피터 결함들을 포함한다. 레티클 리피터 결함들은 패턴으로서 노출되는 레티클 상에서의 입자들 또는 상기 언급된 결정 성장 때문에 발생한다. 결정 성장 결함들은 일반적으로 상기 레티클들의 에지들로부터 시작하여 (노출되는) 마스트의 투명한 영역에서 먼저 발생하고, 상기 레이어 상에서 아지랑이(haze)처럼 보이는 외관을 갖는다. 하지만, 일단 결정 성장 결함들이 웨이퍼들 상에서 프린트되기 시작하면, 상기 결정 성장 결함들은 잘 노출될 수 있고, 그에 따라 상대적으로 투명한 라인 단부(EOL; end of line) 장애를 야기하고, 약한 오픈들(큰 저항이지만 완전하지 않은 오픈)을 야기함으로써 신뢰성 실패로서 때때로 발생한다. 추가로, 결정 성장이 레티클들 상에서 광범위한 현상이기 때문에(진입 지점들이 에지일 수 있음에도 불구하고), 다수의 빈도로 일반적으로 발생할 것이다. 물론, 과제는 검사되는 웨이퍼에 대한 출력을 표준 기준과 비교하는 것이다. 채용될 수 있는 리피터 결함들의 다른 특징은, 상기 결함 리피터들의 기하구조에도 불구하고 그것이 매우 인공적이지 않을 것 같다는 것이다(예컨대, 선형, Manhattan 타입 기하구조들을 가짐). 후자의 특징은 형태 기반 비닝(shape based binning) 및 분류 알고리즘들에 의해 채용될 수 있다. 이러한 경우에 비닝 및 분류를 위한 트레이닝은 선형적으로 문제가 발생하는 웨이퍼들에 기초하여 수행될 수 있고, 이는 실제 랜덤 결함들을 이용하여 일반적으로 수행될 수 있는 무언인가가 아니다.

[0049]

PWQ 타입 리피터 결함들은 그들이 일반적으로 가장 정교한 구조들(예컨대, 가장 약한 패턴)에 영향을 미친다는 점에서 상기한 레티클 리피터 결함들과는 상이하다. 전체적인 붕괴가 발생하면, 명백한 오픈 또는 쇼트가 발생할 수 있다. 하지만, 종종 패턴 이동이 이슈일 수 있다. 그러므로, 표준 기준 타입 이미지를 이용하여 PWQ 타입 결함들을 검출하는 것은 위치 충실도(positional fidelity)(예컨대, 데이터를 설계하기 위한 서브-픽셀 정렬)를 필요로 한다. 그러한 결함들과 상이한 다른 팩터는, 기하구조 크기가 최소인("가장 타이트하고(tightest)") 궁극적으로 다수의 PWQ 결함들이 발생하고 그러므로 신호 콘트라스트가 잠재적으로 실질적으로 낮은 것이다. 또한, PWQ 타입 결함들의 결함 기하구조는, 레티클 리피터 결함들의 기하구조와는 달리, 자주 패턴화된 특성을처럼 보인다. 이러한 방식으로 나타내는 결함들은 시스템 정렬 에러들과 구별하는 것이 꽤 어려울 수 있다. 최종적으로, 레티클 리피터 결함들과 매우 유사하게, 그러한 이벤트들이 발생하는 선형적인 스팟(spot)들에 대한 전망이 매우 유망하다. 그러한 스팟들은 예컨대, KLA-Tencor로부터 상업적으로 이용가능한 DesignScan 분석 소프트웨어, 공동 소유된 미국 특허 출원 번호 제2006/0062445호로서 2006년 3월 23일자로 공개된, 2005년 9월 14일자로 출원된 Verma 등에 의한 미국 특허 출원 번호 제11/226,698호에 기재된 방법들과 같은 레티클 레이아웃 데이터를 평가하기 위한 방법들 – 이 출원들은 본 명세서에 마치 전체로 기술된 바와 같이 참조에 의해서 편입됨 –, 공동 소유되는 Zafar 등에 의한 2006년 11월 20일자 미국 특허 출원 번호 제11/561,659호 및 미국 특허 번호 제2007/0288219호로서 2007년 12월 13일자로 공개된 출원들에 기재된 것과 같이 수행될 수 있는 DBB(desing based binning) – 이 출원들은 본 명세서에 마치 전체로 기술된 바와 같이 참조에 의해서 편입됨 –, 및 핫 스팟 소스들을 제조(DFM)하기 위한 다른 디자인들을 이용하여 결정될 수 있다. 본 명세서에 기술된 실시예들은 이러한 출원들에서 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다.

[0050]

실질적으로 상기 팩터들 모두가 리피터 결함 검출에 영향을 미친다. 하지만, 추가적인 제약이 관심 결함들이 리피터 결함들만을 포함하고 랜덤 결함들을 포함하지 않는 것이라면, 다른 세트의 강조들이 일어날 수 있다. 예컨대, 랜덤 결함들(종종 1차 결함 타입으로서)이 리피터 결함에 더하여 검출되어야 할 때에, 리피터 결함 검출은 본질적으로 몇몇 캐비어트(caveat)들을 이용한 동일한 과제일 수 있다. 특히, 리피터 결함들에 대해 웨이퍼들에 프린트된 단일 다이 레티클의 검사가 수행될 수 없다. 추가로, 랜덤 결함 검출에 대해 수행되는 것 이상으로 이용가능한 고유 신호 또는 이미지 프로세싱 개선이 존재하지 않는다는 점에서, 리피터 결함 검출은 본질적으로 소프트웨어 적층 과제일 수 있다.

[0051]

ADI 검사는 이전 층 잡음을 갖는 이슈들 때문에 전통적으로 다소 하향-채택(under-adopted) 되어 왔다. 예컨대, 이전 층 잡음은 트랜치 에치, ADI 층들, 및 화학-기계적 연마(CMP) 이후의 좁은 트렌치 절연(STI; shallow trench isolation) 층 검사와 같은 층들에 대한 검사에서 상대적으로 중요할 수 있다. 그럼에도 불구하고, 리소그래피 단계들에서 보다 많은 이슈들이 일어남에 따라, 그러한 이슈들을 모니터링하고 제어하는데에 ADI 검사가 보다 많이 이용되고 있다. ADI 레지스트 층 검사의 이용은 또한 다른 장치들의 제조에 대해서 상이하다. 예컨대, ADI 레지스트 층 BF 검사는 메모리 제조와 비교하여 로직 제조에 대해 수행되는 더 큰 비율의 검사들을 규명할 수 있다.

[0052]

ADI 층 검사에 대한 다수의 현재 이용가능한 광학 접근법들이 존재한다. 예컨대, 풀 루프(상기 웨이퍼들 상에서 장치들의 완전한 구성) 및 짧은 루프(상기 웨이퍼들 상에서의 장치들의 부분적인 구성) 모두에 대해 레지스

트 충들의 ADI 검사에 대해 이용될 수 있는 다수의 다양한 스펙트럼 모드들이 존재한다. 그러한 스펙트럼 모드들의 예들은 딥밴드(deepband), 블루밴드(blueband), GHI 라인, G 라인, 및 브로드밴드(BB) 딥 자외선(DUV)을 포함한다. 일반적으로, 레지스트 층 ADI 검사들의 대부분(약 90%)은 상기 DUV 스펙트럼 영역에서 수행된다. 추가로, 에지 콘트라스트(EC, edge contrast) 모드(조명 및 이미징 경로들에서 상보적 어퍼처들이 이용됨) 및 BF 모드와 같은 상이한 이미징 모드들이 상기 풀 루프 및 짧은 루프에 대한 레지스트 층 ADI 검사들에 대해서 이용된다. 일반적으로, 많은 상이한 레지스트 층 ADI 검사들에 대해 EC 모드 및 BF 모드가 이용됨에도 불구하고, EC 모드가 BF 모드보다 더 자주 이용될 수 있다.

[0053] 상기한 BB DUV EC 모드(그리고, 가능할 때에, KLA-Tencor로부터 상업적으로 이용가능한 도구들의 Puma 시리즈들과 같은 UV 암시야(DF; dark field) 검사 시스템들)에 대한 더 큰 의존성은 적어도 부분적으로 이전 층 잡음 이유들 때문이다. 하지만, 이전 층 잡음(이전 층 결합 때문에)은 쉽게 제거될 수 있고(예컨대, 알고리즘들을 이용하여), EC mode 검사를 대신하여 BF BB DUV 검사가 이용될 수 있다. 이전 층 잡음을 제거하기 위해 이용될 수 있는 방법들의 예들은, 공동 소유되는 2006년 9월 19일자 Ramani 등에 의한 미국출원번호 제11/533,079호에 기술되고, 상기 출원은 본 명세서에 마치 전체로 기술된 바와 같이 참조에 의해서 편입된다. 본 명세서에 기술된 실시예들은 이러한 특허 출원에 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다. BF BB DUV 모드 검사를 이용하는 것은 컬러 잡음 고려들이 또한 안정되어야 하는 것에도 불구하고 분해능에 관해서 검사에 협력할 수 있다. 추가로, 본 명세서에 추가로 기술된 바와 같이, 본 명세서에 기술된 실시예들은 종래의 랜덤 결합 검사보다 더 느린 크기의 정도로 시간들을 스캐닝하게 할 수 있다(예컨대, 단지 일부 다이 상에서 포커싱되는 특정화된 리피터 결합 검출을 이용하여). 절반의 속도 또는  $\frac{1}{4}$ 의 속도로 스캐닝하는 것은 아주 적절할 수 있지만, 조사량(dosage)의 관점에서 보통의 주의가 또한 고려되어야 한다(예컨대, 상기 조사량이 상기 웨이퍼 또는 웨이퍼 상에 형성되는 물질들에 손상을 야기할 수 있는 레벨들에 접근하지 않도록).

[0054] 랜덤 결합 검출을 위해 이용되는 광학 신호는 리피터 결합 검출을 강화하기 위해서 또한 변경될 수 있다. 예컨대, 서브-파장 특징들의 검사를 위해 광학 선택이 좀더 정교해지고 있다. 하지만, 랜덤 결합 검출에 대한 종래의 접근법들에 대해 이용되는 광학들과 상이한 광학은 결점들이 형성된 웨이퍼들을 이용하여 결정될 수 있음에도 불구하고 필수적이지 않을 수 있다. 하지만, 세기(에너지), 분해능(예컨대, 개구수(NA; numerical aperture)), 콘트라스트(예컨대, 변조 전달 함수(MTF; modulation transfer function)), 모드들(어퍼처들, EC, 등) 및 스펙트럼과 같은 기본 팩터들의 일부가 그들이 리피터 결합들의 검출에 영향을 미치는지를 결정하기 위해 조사될 수 있다.

[0055] 에너지 팩터를 고려할 때에, 리피터 결합 검출에 이익이 될 수 있는 하나의 팩터는 표준 기준 다이 검사에 있고, 사용자는 전체 웨이퍼를 검사하는 것을 실제로 원하지 않는다. 사실상, 5개의 다이들을 검사하는 것이 충분하고 검사에 대해 허용된 시간은 약 1시간이며, 5개의 다이들이 5분 이하로 검사될 수 있다고 가정한다(본 명세서에 추가로 기술되는 바와 같이 좋은 이유들에 대해서). 그러므로, 검사에 대해 허용된 나머지의 시간은 많은 시각적인 기회들을 제시한다(어쩌면 또한 계산적으로). 예컨대, 보다 많은 광이 수집되고 검출되는 것을 가능하게 하기 위해서 스캐닝이 더 느리게 수행될 수 있다. 하지만, 더 느린 속도의 스캐닝은 광의 증가된 양에 웨이퍼를 노출시키는 것을 야기하고, 상기 웨이퍼 상의 물질들은 얼마나 많은 광에 상기 웨이퍼가 상기 물질들에서의 부작용 없이 노출될 수 있는지에 영향을 미칠 수 있다. 추가로, 상대적으로 높은 NA EC 모드에서 스캐닝은 좀 더 느리게 수행될 수 있고, 이는 일반적으로 "광 결핍(light starved)"이다. 게다가, 멀티-패스(multi-pass) 검사(조합된 BF 및 EC와 같은)는 나머지의 허용된 시간에서 수행될 수 있다. 그러므로, 이러한 팩터들은 그 상황에 영향을 주는 시스템 기반 해결책을 결정하기 위해 조사될 수 있다.

[0056] 일부의 실시예들에서, 상기 검사 시스템의 출력은 전자 빔 검사 시스템을 이용하여 획득된 출력을 포함할 수 있다. 상기 전자 빔 검사 시스템은 당업계에서의 기지의 임의의 적절한 전자 빔 검사 시스템을 포함할 수 있다. 전자 빔 검사에서, 더 낮은 빔 전류들이 이용될 수 있고, 이는 더 낮은 스루풋에도 불구하고 향상된 분해능을 가능하게 한다. 대안적으로, 픽셀 평균, 라인 평균, 또는 프레임 평균과 같은 다양한 평균 기술들이 더 낮은 유효 스캔 속도들에서 잡음을 줄이는데에 이용될 수 있다.

[0057] 최상의 콘트라스트를 제공하는 모드에서 또는 최상의 해상도에서 리피터 결합들에 대한 검사가 수행될 수 있음에 반해, 많은 웨이퍼 검사 시스템들은 결합들을 해결함이 없이 결합들을 검출하도록 설계된다. 하지만, 당해 결합(들)이 콘트라스트를 생성하는데에 충분한 명목적 배경을 교란할 수 있도록, 분해능은 일반적으로 충분해야 한다. 그러므로, 오정렬(misalignment)에 기인한 증가된 에일리어싱 에러들 또는 감소된 콘트라스트를 필수적으로 회생하지 않고 가능한 한 높은 분해능이 바람직할 수 있다. 예컨대, 광학의 NA를 증가시키는 것은 상기 검사 시스템의 분해능을 증가시킬 수 있지만, 또한 오정렬 에러들이 디지털화 이전에 보정되지 않는 한 상기 오

정렬 에러들을 또한 증가시킨다. 추가로, 랜덤 결합 검출과는 달리, 표준 기준 다이 검사와 같은 어플리케이션에 대해 오정렬 영향들이 고려되어야 한다. 일반적으로, 정렬 포지셔닝은 잠재적으로 오프된 몇몇 픽셀들일 것이고, 개략적(coarse) 에러들에 대한 보정 이후에 최악의 경우 오정렬 에러들은 여전히 픽셀의 약 절반일 수 있으며, 최대의 에일리어싱 에러를 생성할 수 있다. 이러한 효과를 광학적으로 완화하는 하나의 방법은 점 확산 함수(PSF; point spread function) 당 보다 많은 스팟들(예컨대, 대략 적어도 3.5 픽셀들) 또는 보다 많은 빈 확대(empty magnification)을 이용하는 것이다. 이러한 상황에서, 에지들 상에서의 보다 점진적인 상승 시간이 이용될 수 있다(예컨대, 광학 저역 통과 필터 또는 더 낮은 유효 공간 주파수 대역폭에 의해서)

[0058]

이러한 방식에서, 본 명세서에 기술된 표준 기준 다이 기반 검사는 오버샘플링을 이용해 수행될 수 있다. 그러한 검사를 위해, 오버샘플링은 스팟 당 2 샘플들의 나이퀴스트 기준(Nyquist criteria)보다 더 큰 임의의 샘플링일 수 있다. 오버샘플링은 일반적으로 회피되는데, 그 이유는 그것이 검사 프로세스의 스루풋을 감소시키기 때문이다. 하지만, 본 명세서에서 추가로 기술되는 바로서, 표준 기준 다이 기반 검사에 대해서 웨이퍼의 일부부만이 검사될 수 있고, 그에 따라 오버샘플링에 의해 야기되는 스루풋 우려들을 감소시킬 수 있다. 하지만, 샘플링이 에일리어싱 효과들을 생성하지 않도록 과도한 오버샘플링이 바람직하게 회피된다.

[0059]

콘트라스트를 향상시키는 다른 방법은, 웨이퍼들 상의 물질들에 의해 야기될 수 있는 박막 영향들 또는 위상 콘트라스트를 활용하는 것이다. 위상 콘트라스트 향상은 보통 증가된 방해 결합 검출과 같은 상당한 부작용들과 함께 오는데, 그 이유는 막 두께에서의 임의의 변화가 세기에서의 변화들을 야기할 수 있기 때문이다. 리피터 결합 검출 어플리케이션들을 위해 위상 콘트라스트 향상을 이용하는 것에 대한 큰 이슈들은, 기준 및 테스트 웨이퍼 사이에서 가질 위상 차이들의 타입이다. 하지만, 상이한 웨이퍼들 상에서의 동일한 다이에 대한 컬러(프로세스) 잡음 레벨은 대략 동일할 수 있다. 추가로, 일반적으로, 상기 웨이퍼의 중앙 쪽으로 위치된 다이들은 프로세스 잡음의 관점에서 상대적으로 잘 제어되는 경향이 있다. 그러므로, 표준 기준 다이 검사에 대한 기본 방법이 상대적으로 간단할 수 있다. 특히, 테스트 다이뿐만 아니라 상기 표준 기준 다이를 모두 생성하는데에 중앙 다이 행(예컨대, 중앙 다이 행의 5개 내지 8개의 다이들)이 이용될 수 있다. 항상 잔여 컬러 변화들이 존재할 것이고, 이러한 컬러 변화들은 알고리즘적으로 취급될 것이다. 이러한 방식으로, 컬러 변화의 다양한 영향들이 가능한 단순화될 수 있다.

[0060]

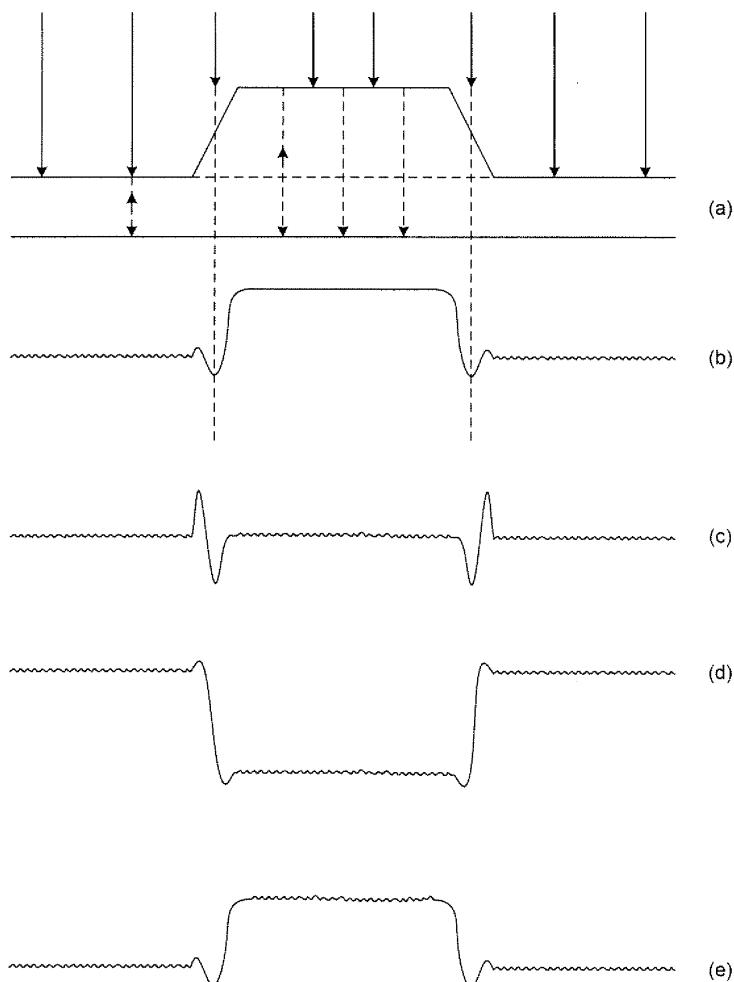

협대역(NB; narrow band) 이미징 모드 및 물질의 단일층 스택을 고려하면, 물질의 단일층은  $\frac{1}{4}$ 파 플레이트로서 유효하게 역할할 것이다. 그러므로, 도 1(a)에 도시된 바와 같이 종래의 근처  $\frac{1}{4}$ 파 에지 상의 물질의 단일층의 위상 콘트라스트 효과들은 BF 이미징에 대해 도 1에 도시된 응답들을 생성할 수 있다. 특히, 도 1(b)는 180도 위상 지연을 갖는 도 1(d)에 도시된 바와 같은 전체 콘트라스트 반전에 대해 90도 위상 지연을 갖는 도 1(c)에 도시된 바와 같은 임펄스형 함수 및 45도 위상 지연을 갖는 도 1(e)에 도시된 바와 같이 콘트라스트가 감소되는 무엇인가가 될 수 있는 단순한 계단형 함수(0도 위상 지연을 가짐)를 도시한다.

[0061]

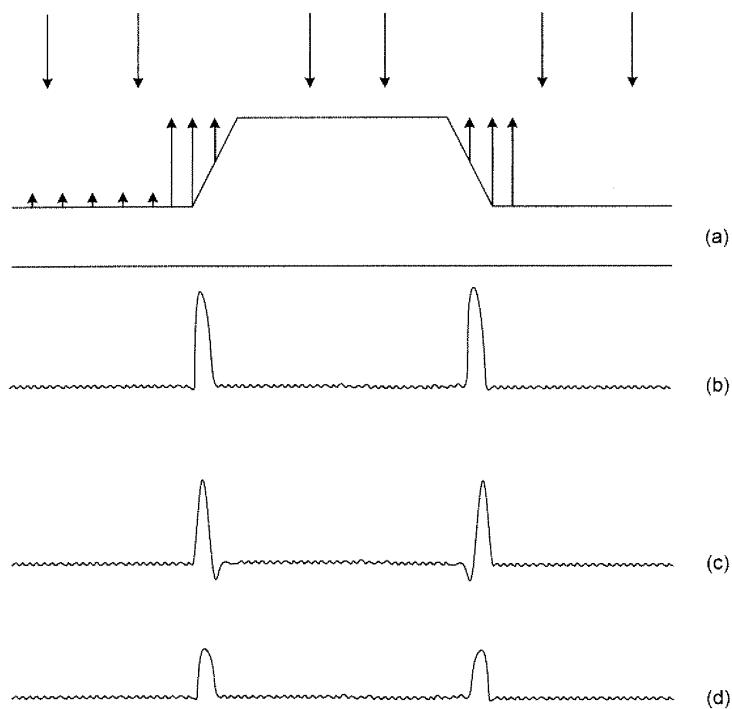

동일한 근처 구형파 에지가 도 2(a)에 도시되고, 도 2(b), 2(c), 및 2(d)는 NB EC 모드 이미징에서의 근처 구형파 에지 상에서의 물질의 단일층의 위상 콘트라스트 효과들을 도시한다. 특히, 도 2(b)는 개략적으로 180도의 위상 지연을 갖는 도 2(d)에 도시된 바와 같은 함수에 대해 개략적으로 90도의 위상 지연을 갖는 도 2(c)에 도시되는 바와 같은 함수가 될 수 있는 단순한 계단형 함수(0도의 위상 지연을 가짐)를 도시한다. EC 모드는 근처 구형파의 에지로부터만 분산을 유효하게 생성하고, 이는 BF 이미지의 광학 제1 유도처럼 유효하게 동작한다. 도 2에 도시된 바와 같이, 그러므로, EC 모드는 막 두께 변화에 응답하여 상기 에지들에 대응하는 출력의 진폭을 변화시킬 수 있다. NB EC 모드는 컬러 및 이전 층 신호들에 완전하게 영향을 받지 않는 것이 아닐 수 있는데, 왜냐하면 EC 이미징 어퍼처를 통과하도록 허용되는 이전 층들로부터 몇몇 배경 분산이 존재할 수 있기 때문이다. 추가로, 막 두께 변화들은 아마도 상기 에지들로부터 상이하게 분산할 것이고, 그러므로 에지 진폭들은 변화할 수 있다. 위상 콘트라스트 이슈들은 전방 말단층들과 반대로서 후방 말단층들에서 보다 많이 보인다(예컨대, 더 큰 막 스택 불안정도 때문에).

[0062]

이러한 효과들을 완화하는 기본적 접근법들은 스펙트럼을 확장하고 EC 모드를 이용하는 것일 수 있다. 두 경우들에서, 분해능(MTF)이 감소될 수 있다. 하지만, 본 명세서에 추가로 기술되는 바로서, 웨이퍼-대-웨이퍼 정렬 이슈들이 또한 이루어져야 한다. 액티브 RTA 시스템을 이용하지 않고 상기 웨이퍼-대-웨이퍼 정렬 이슈들을 완화하기 위해서, 스팟 당 보다 많은 샘플들(또는 주어진 픽셀 크기에 대해 상대적으로 낮은 NA)이 이용될 수 있다. 이러한 방식으로, 정렬 이슈들을 극복하기 위해서 오버샘플링이 이용될 수 있다.

[0063]

BF에 대해서 현재 이용되는 리피터 결합 검출 접근법들은 기본적으로 A-B, B-C 비교 기술들을 이용한다. 일반적인 경우에, A 및 C가 기준 다이들로서 이용되고, B는 결합들이 검출되는 테스트 또는 후보 다이로서

이용된다. 이러한 타입의 검사 접근법은, 비교의 양 쌍들에 대해 특정 임계치 이상의 명백한 이벤트들로서 보여지는 단일의 고립된 신호들을 포착하는 능력을 최대화하도록 시도한다. 이러한 비교의 보다 정교한 버전이 MDAT 알고리즘을 이용하여 수행될 수 있고, 이는 비교에 대한 정확한 기준을 생성하도록 시도한다. 이러한 접근법에서, 상기 기준 다이들 A 및 C는 실제로 다이 A 또는 C 각각 주변에 중앙에 위치한 약 5개의 다이들 내지 약 8개의 다이들의 세트의 평균 또는 중간값들이다(실제 구현은 변화할 수 있음에도 불구하고). BF 시스템들은 서브-픽셀 정확도를 전달하는 RTA 서브시스템을 갖는 경향이 있기 때문에, 0.1 픽셀 미만의 다이-대-다이 에일리어싱 에러들이 최소화되고, 상대적으로 큰 샘플 스팟들을 이용하여 픽셀들에 대해서 우수한 성능이 성취될 수 있다. 보다 정교한 보간(interpolation) 방식을 이용하여 이러한 에러들을 최소화하려(예컨대, 약 0.01 픽셀 미만으로) 추가로 시도하는 정교한 이미지 정렬 단계가 또한 존재한다. 상기 임계치 자체의 선택은 다양한 방법들로 수행될 수 있지만, 대부분은 주변의 상황에 기초하는 적응적 스레스홀딩(adaptive thresholding)의 형태를 이용한다. 그러한 접근법들은 전체적인 컬러 변화를 감소시키는데 있어서 꽤 성공적이다. 하지만, 제1의 장소에서 영역들이 얼마나 정확하게 라벨링되었느냐의 문제가 남아있다(예컨대, 구획 에러, 집단 크기 등 때문에). 이러한 관점에서, 상기 MDAT 알고리즘은 꽤 정교하다. 그러한 것으로서, 상기 MDAT 알고리즘은 우선 선택되는 알고리즘일 수 있다.

[0064] 리피터 결함들을 검출하는 것의 기본적인 제한은, 단일 다이 레티클(SDR; single die reticle)에서 리피터 결함이 패턴들과 구별될 수 없다는 것이다. SDR에서의 약한 리피터의 경우에, 실질적으로 약한 리피터만이 검출될 수 있다. 사실상, 상기 약한 리피터들은 너무 약해서(그것이 오직 랜덤하게 발생할 수 있다는 점에서) 그것은 랜덤 결함으로서 유효하게 검출될 수 있다. 그러한 결함들은 전체 웨이퍼에 걸쳐서 다수의 다이들에 대해 출력을 적층시킴으로써 잠재적인 리피터인 것으로 결정될 수 있다. 이러한 상황은, 레티클이 자연 기준(예컨대, 다수의 다이들 중 하나)을 포함하는 다수의 다이 레티클(MDR; multiple die reticle) 유발 결함들의 경우에 확실히 더 우수하다. 하지만, 다시 MDR에 대한 리피터 결함들의 검출이 실제로 최적이지 않다. 예컨대, 우선 상기 신호가 상대적으로 낮으면, 상기 신호를 증폭하기 위한 용이한 방법이 존재하지 않는다. 분명히, 이전 층 결합 잡음은 이러한 접근법을 복잡하게 한다.

[0065] 상기한 고려들에 기초하여, 리피터 결함 검출을 위한 표준 기준 다이 비교에 대한 알고리즘이 생성될 수 있다. 특히, 본 명세서에서 기술되는 실시예들은 리피터 (조직적인) 결함 검출을 가능하게 할 뿐만 아니라 리피터 결함 검출을 최적화할 수 있는 포괄적인 검사 방법을 제공한다. 본 명세서에서 기술되는 실시예들은, 어레이 모드들 및 랜덤 모드들과 같은 웨이퍼 검사에서의 모드 또는 다른 "패스(pass)"로서 이용될 수 있다. 예컨대, 본 명세서에 기술된 실시예들은 어쩌면 본 명세서에서 추가로 기술하는 바와 같은 구성에서의 적절한 변화들과 함께 현존하는 웨이퍼 검사 시스템 또는 다른 현존하는 시스템들을 이용하여 구현될 수 있다. 이러한 방식으로, 본 명세서에서 기술되는 실시예들은 표준 기준 다이 기반 검사를 채택하여 가능하게 하고, 이는 조직적인 결함들을 검출하는데에 가장 효율적인 방법이다.

[0066] 일 실시예는 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법에 관한 것이다. 일 실시예에서, 상기 다이 대 표준 기준 다이 검사는 리피터 결함들에 대한 검사를 포함하고, 이는 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다. 상기 리피터 결함들은 본 명세서에 기술된 임의의 리피터 결함들을 포함할 수 있다.

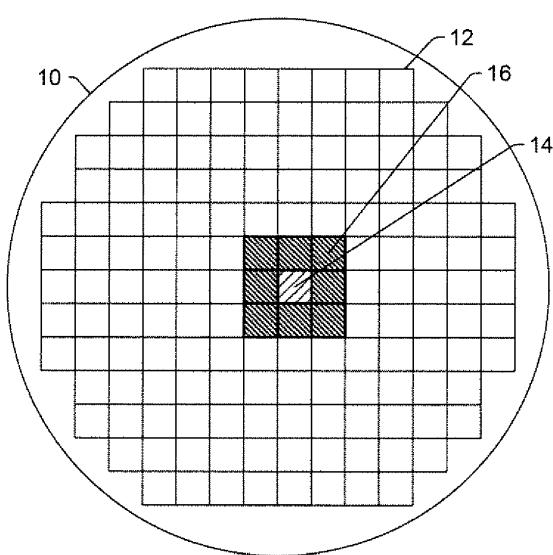

[0067] 본 방법은 웨이퍼 상에 위치한 하나 이상의 다이들 및 상기 웨이퍼 상에 중앙에 위치한 다이에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 일부의 실시예들에서, 하나 이상의 다이들이 상기 중앙에 위치한 다이에 인접하여 위치한다. 그러한 다이들의 일 실시예가 도 3에 도시된다. 예컨대, 도 3에 도시된 바와 같이, 웨이퍼(10)는 중앙에 위치한 다이(14) 및 상기 중앙에 위치한 다이에 인접하여 위치하는 다이들(16)을 포함하는, 웨이퍼 상에서 형성되는 다이들의 어레이(12)를 포함한다. 도 3에 도시된 바와 같이, 중앙에 위치한 다이는 정확하게 상기 웨이퍼의 중앙에 위치하지 않는다. 즉, 중앙에 위치한 다이의 중앙과 상기 웨이퍼의 중앙이 일치하지 않는다. 대신에, 이러한 실시예에서, 상기 중앙에 위치한 다이는 상기 웨이퍼의 중앙의 부근에 위치한다(예컨대, 상기 중앙에 위치한 다이의 일 예지가 상기 웨이퍼의 중앙에 대략 위치한다). 상기 중앙에 위치한 다이는, 특히 웨이퍼의 중앙이 어레이에서의 다이들 사이의 공간과 일치하는 도 3에 도시된 것과 같은 예들에서의 웨이퍼의 중앙 부근에 위치한 다이들 중 임의의 것으로 선택될 수 있다. 하지만, 상기 중앙에 위치한 다이는 상기 웨이퍼의 중앙에 포지셔닝될 수도 있다.

[0068] 상기 출력을 획득하는 단계는 예컨대 광을 이용해 상기 웨이퍼를 스캐닝하고 상기 웨이퍼로부터 반사되거나 분산된 광을 검출함으로써, 상기 웨이퍼 상의 하나 이상의 다이들 및 상기 웨이퍼 상에 중앙에 위치한 다이에 대한 출력을 획득하기 위해서 검사 시스템을 이용하는 단계를 포함할 수 있다. 이러한 방식으로, 상기 웨이퍼 상

에 위치한 하나 이상의 다이들 및 중앙에 위치한 다이에 대한 출력을 획득하는 단계는 그러한 다이들을 포함하는 상기 웨이퍼의 일부의 검사를 수행하는 단계와 유사할 수 있다. 상기 검사 시스템은 본 명세서에 기술된 바와 같이 구성될 수 있다. 대안적으로, 상기 출력을 획득하는 단계는 상기 출력을 생성하는데에 이용되는 검사 시스템으로부터 출력을 획득하는 단계를 포함할 수 있다. 예컨대, 상기 방법은 상기 검사 시스템이 상기 출력을 저장하였던 저장 매체로부터 상기 출력을 획득하는 단계를 포함할 수 있다. 상기 저장 매체는 상기 검사 시스템의 저장 매체, 펌 데이터베이스와 같은 저장 매체, 본 명세서에 기술되는 바와 같이 구성되는 저장 매체, 상기 검사 시스템에 결합되는 임의의 다른 저장 매체, 또는 당업계에서의 기지의 임의의 다른 적절한 저장 매체를 포함할 수 있다. 이러한 방식으로, 상기 웨이퍼 상의 하나 이상의 다이들 및 상기 중앙에 위치한 다이에 대한 출력을 획득하는 단계는 상기 웨이퍼를 검사하는 단계를 포함하지 않을 수 있다. 추가로, 상기 웨이퍼 상에 위치한 하나 이상의 다이들 및 상기 중앙에 위치한 다이에 대한 출력이 상기 표준 기준 다이를 생성하는데에만 이용될 수 있는 한, 상기 검사 시스템의 출력이 상기 전체 웨이퍼에 대해서 획득될 수 있다.

[0069] 상기한 획득하는 단계의 가장 간단한 구현은 웨이퍼의 중앙 다이 행을 검사하여 상기 중앙 다이(또는 둘) 주변에 중심에 위치한 표준 기준 다이 이미지를 생성하는 것이다. 일부의 실시예들에서, 적어도 5개의 다이들에 대해 획득되는 출력은 상기 표준 기준 다이를 생성하는데에 이용될 수 있다. MDAT를 이용하는 것은 8개의 다이들이 양호한 개수의 다이들일 수 있음을 제안한다. 하지만, 너무 많은 다이들에 대해 획득되는 출력이 상기 표준 기준 다이를 생성하는데에 이용되면, 웨이퍼에서의 컬러 변화들이 상기 표준 기준 다이에서 명백하게 될 수 있는데 왜냐하면 상기 컬러 변화들이 웨이퍼의 외부 에지의 부근에서 명백하게 되는 경향이 있기 때문이다. 일 실시예에서, 웨이퍼의 중앙에 또는 그 부근의 9개의 다이들(3개 다이 대 3개 다이 배열)에 대해 획득되는 출력이 상기 표준 기준 다이를 생성하는데에 이용될 수 있다.

[0070] 상기 웨이퍼 상의 하나 이상의 다이들 및 중앙에 위치한 다이에 대해 획득되는 상기 출력은 당업계에서의 기지의 임의의 적절한 포맷의 출력을 포함할 수 있다. 일 실시예에서, 상기 표준 기준 다이는 이미지를 포함한다. 이러한 방식으로, 본 명세서에 기술되는 상기 방법은 표준 기준 다이 이미지를 생성하는 단계를 포함할 수 있다. 그러한 일 실시예에서, 웨이퍼 상의 하나 이상의 다이들 및 중앙에 위치한 다이에 대한 출력을 생성했던 검사 시스템은 이미지 기반의 검사 시스템으로서 구성될 수 있다.

[0071] 상기 방법은 또한 상기 출력의 다이 위치들 내부에 기초하여 상기 하나 이상의 다이들 및 상기 중앙에 위치한 다이에 대한 출력을 결합하는 단계를 포함한다. 즉, 상기 하나 이상의 다이들 및 상기 중앙에 위치하는 다이에 대해 내부 다이 위치에서 동시에 획득되는 출력이 결합될 수 있다. 다수의 다이들에 대해 내부 다이 위치에서 동시에 획득되는 출력은 상기 다수의 다이들에 대해 획득되는 출력을 서로 정렬시킴으로써 식별될 수 있다. 추가로, 다수의 다이들에 대해 내부 다이 위치에서 동시에 획득되는 출력은 상기 출력의 내부 다이 위치를 결정함으로써 식별될 수 있다(예컨대, 몇몇 공통 기준 또는 좌표 시스템을 이용하여). 그러한 정렬 또는 내부 다이 위치를 결정하는 것은 본 명세서에서 추가로 기술되는 바와 같이 수행될 수 있다. 이러한 방식으로, 함께 스캐닝되지 않는 다이들이 평균되거나 또는 그렇지않으면 결합되면, 몇몇 상당한 구현 곤란함들이 존재할 수 있다. 고려할 하나의 흥미로운 아티팩트는 본 명세서에 기술된 실시예들에 대해 RTA를 이용할지 여부이다. 정렬은 본 명세서에서 추가로 기술될 것이다. 지금은 RTA가 이용되는 것으로 가정될 수 있다.

[0072] 일 실시예에서, 상기 출력은 그레이 레벨들을 포함한다. 그러한 일 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐 그레이 레벨들의 평균값을 결정하는 단계를 포함한다. 상기 평균값들은 임의의 적절한 알고리즘 및/또는 방법을 이용하여 결정될 수 있다. 다른 그러한 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐 그레이 레벨들의 중간값을 결정하는 단계를 포함한다. 상기 중간값은 임의의 적절한 알고리즘 및/또는 방법을 이용하여 결정될 수 있다. 추가의 그러한 실시예에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐 그레이 레벨들의 중간값 및 평균값을 결정하는 단계를 포함한다. 상기 평균값들 및 중간값들은 두 개의 서로 다른 표준 기준 다이들을 생성하는데에 이용될 수 있다. 예컨대, 그러한 일 실시예에서, 상기 표준 기준 다이는 상기 내부 다이 위치들에 걸친 상기 평균값을 포함하고, 상기 방법은 상기 내부 다이 위치들에 걸쳐 상기 중간값의 추가적인 표준 기준 다이를 생성하는 단계를 포함한다.

[0073] 일부의 실시예들에서, 상기 결합하는 단계는 상기 내부 다이 위치들에 걸쳐 특성에서의 잡음 및 상기 내부 다이 위치들에 걸쳐 출력의 특성을 결정하는 단계를 포함한다. 이러한 실시예들에서, 상기 출력의 특성은 본 명세서에 기술된 특성들(예컨대, 평균, 중간, 등) 중 임의의 것을 포함할 수 있다. 추가로, 상기 특성에서의 잡음은 본 명세서에서 추가로 기술되는 바와 같이 결정될 수 있다.

[0074] 상기 방법은 상기 결합하는 단계의 결과들에 기초하여 상기 표준 기준 다이를 생성하는 단계를 더 포함한다.

예컨대, 상기 표준 기준 다이를 생성하는 단계는 상기 표준 기준 다이의 하나 이상의 속성을 저장하는 단계를 포함할 수 있다. 저장할 가장 논리적인(가장 선형적으로 동작함) 값은 그레이 레벨의 평균값이다. 다음 후보는 그레이 레벨의 중간이고, 이는 평균값보다 더 날카로움을 유지할 것이지만 몇몇 흥미있는 비선형 아티팩트들을 또한 생성할 수 있다. MDAT가 성공적으로 중간값을 이용한다는 사실은 상기 중간값이 본 명세서에 기술하는 실시예들에 대한 선두 후보이어야 한다는 것을 암시한다.

[0075] 주변들에서의 잡음에 대한 정보가 또한 저장될 수 있다. 평균값에 대한 잡음 속성의 논리적 페어링은 중간값 아마도 범위를 갖는 표준 편차일 것이다. 상기 표준 기준 다이에서의 잡음에 대한 추가적인 속성을 저장하는 것은 추가적인 8개의 비트들을 필요로 할 것이다. 특히 범위가 실질적으로 정렬 에러들로 잡음이 섞일 수 있기 때문에, 이웃을 평활화하는 것(smoothing)이 본 명세서에서 기술된 실시예들에서 이용될 수 있다. 다른 한편, 상기 표준 기준 다이를 생성하는데에 이용되는 출력이 특히 잡음이 있는 영역에 있는지 여부를 아는 것이 유용할 수 있다. 일부의 실시예들에서, 잡음에 대한 추가적인 속성은 결함 검출에 대해 이용되는 임계치들 상의 제어로서 이용될 수 있다. 추가로, 또는 대안적으로, 잡음에 대한 추가적인 속성은 결함 검출에 대한 비교 벡터로서 이용될 수 있다.

[0076] 일 실시예에서, 상기 표준 기준 다이는 상기 하나 이상의 다이들 및 상기 중앙에 위치한 다이에서의 랜덤 결함들로부터 실질적으로 어떠한 잡음도 포함하지 않는다. 예컨대, 일부의 실시예들에서, 상기 방법은 상기 표준 기준 다이에서의 랜덤 결함들을 감소시키는 단계 및/또는 상기 표준 기준 다이에서 민감한(susceptible) 픽셀들을 식별하는 단계를 포함할 수 있다. 예컨대, 상기 방법은 상기 웨이퍼가 얼마나 양호한지(예컨대, 상기 웨이퍼가 얼마나 결함이 없는지)를 결정하는 단계를 포함할 수 있다. 상기 웨이퍼가 기준으로서 얼마나 양호한지를 결정하는 단계는, 상기 중앙에 위치한 다이 및 상기 하나 이상의 다이들에 대해 획득되는 출력에 기초하여 이러한 다이들의 결함 검토를 수행하는 단계를 포함할 수 있다. 추가로, 상기 표준 기준 다이를 생성하기 위해 상기한 바와 같이 두 개 이상의 다이들의 출력을 결합함으로써, 상기 표준 기준 다이에서의 잡음이 유효하게 감소되는 한편(예컨대, 평균함으로써) 비-잡음(non-noise) 신호들은 유효하게 증폭된다(예컨대, 평균함으로써). 예컨대, N 개의 다이들로부터의 데이터를 평균하는 프로세스는 상기 신호를 v n만큼 증폭할 것이다. 중간값은 그것이 랜덤 결함 또는 이전 층의 임의의 자취를 가장 잘 제거할 것 같다는 점에서 더 나은 속성이다. 본 명세서에 기술된 실시예들은 또한 픽셀들에서의 잡음의 척도(measure)로서 상기 중간값 및 평균값 간의 차이를 저장하는 단계를 포함할 수 있다. 하지만, 상기한 바와 같이, 상기 방법은 또한 16 비트 값(유효하게 2개의 이미지들)을 저장하는 단계를 포함할 수 있고: 하나는 평균값을 갖고 다른 것은 중간값을 갖는다. 이러한 단계들은 실제 웨이퍼들을 이용하여 어느 정도의 시뮬레이션 및 실험으로 수행될 수 있다.

[0077] 일 실시예에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 포함한다. 그러한 일 실시예에서, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에만 대한 표준 기준 다이를 생성하는 단계를 포함한다. 상기 미리 결정된 영역들은 예컨대 상기 디자인의 중요 영역들에 대응하는 상기 디자인 데이터에서의 영역들, 상기 디자인의 관심 영역들(또는 사용자가 "관심을 갖는" 영역들), 상기 디자인에서의 핫 스팟들 등을 포함할 수 있다. 상기 미리 결정된 영역들은 본 명세서에서 추가로 기술되는 바와 같이 임의의 적절한 방식으로 결정될 수 있다. 추가로, 상기 미리 결정된 영역들은 본 명세서에서 기술된 실시예들에 의해서 또는 다른 시스템 또는 방법에 의해서 결정될 수 있다.

[0078] 이러한 방식으로, 일부의 실시예들에서, 시스템들 접근법의 시스템이 상기 표준 기준 다이를 생성하기 위해 이용될 수 있다. 그러한 일 실시예에서, 레티를 검사 시스템들을 이용하여 기지의 "양호한" 표준 기준 다이가 생성될 수 있다. 다른 예에서, 출력 획득 및/또는 상기 표준 기준 다이를 생성하는데에 이용되는 획득된 출력의 프로세싱은 핫 스팟 생성된 샘플 계획 상에서 이루어질 수 있다. 상기 핫 스팟 생성된 샘플 계획은 DesignScan, DBB 등에 포함된 다수의 방식들로 생성될 수 있다. 예컨대, 컨텍스트 기반 검사(CBI; context based inspection) 방법들은, 중요한 디자인 데이터가 프린트된 웨이퍼의 부분들 및 중요하지 않은 디자인 데이터가 프린트된 웨이퍼의 부분들이 아닌 부분을 검사하기 위해서, 일반적으로 디자인 데이터에 대한 정보를 이용한다. 즉, CBI는 타겟팅된 또는 "스마트한" 검사를 수행하기 위해서 상기 디자인 데이터의 컨텍스트를 이용할 수 있다. 그러한 일 실시예에서, 상기 디자인 데이터의 오직 상대적으로 민감한 영역들에서의 결함들을 검출하기 위해 디자인 데이터가 검사 동안에 이용될 수 있다. 예컨대, 이미지와 같은 웨이퍼의 검사의 출력이 저장될 수 있고, 상기 설계의 민감 영역들에 대응하는 상기 이미지의 일부들만이 상기 이미지의 일부들에서의 결함들을 검출하기 위해서 비교될 수 있다. 그러한 것으로서, 상기 표준 기준 다이는 검사될 다이의 일부분들만을 포함하도록 생성될 수 있다. 예컨대, 상기 디자인 데이터는 테스트 다이의 어떠한 부분들이 상기 웨이퍼의 CBI에서

검사될 것인지를 결정하는데에 이용될 수 있고, 상기 표준 기준 다이는 검사될 테스트 다이의 일부분들에 대응하는 상기 다이의 일부분들만을 포함하도록 생성될 수 있다. 그러므로, 본 명세서에서 기술되는 실시예들에서 생성되는 상기 표준 기준 다이는 상대적으로 산재된(sparse) 표준 기준 다이일 수 있고, 이는 상기 표준 기준 다이에 대한 저장 요구조건들을 바람직하게 감소시킬 수 있다. 이러한 방식으로, 하나의 구현에서, 표준 기준 다이 검사는 이미지 및 캔텍스트 기반 검사를 포함할 수 있다. 추가로, 표준 기반 다이 검사 및 이미지 및 캔텍스트 기반 검사는 동시에 또는 순차적으로 수행될 수 있다.

[0079] 다른 실시예는 웨이퍼를 검사하기 위한 방법에 관한 것이다. 상기 방법은 상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계를 포함한다. 상기 획득하는 단계는 본 명세서에 기술된 바와 같이 수행될 수 있다. 상기 방법은 또한 상기 출력의 내부 다이 위치들에 기초하여 상기 웨이퍼 상에 위치한 하나 이상의 다이들 및 상기 웨이퍼 상에 중앙에 위치한 다이에 대한 출력을 결합하는 단계를 포함한다. 상기 결합하는 단계는 본 명세서에 기술된 바와 같이 수행될 수 있다. 추가로, 상기 방법은 상기 결합하는 단계의 결과들에 기초하여 표준 기준 다이를 생성하는 단계를 포함하고, 이는 본 명세서에 기술된 바와 같이 수행될 수 있다. 상기 표준 기준 다이는 본 명세서에 기술된 바와 같이 구성될 수 있다. 예컨대, 일 실시예에서, 상기 표준 기준 다이는 상기 하나 이상의 다이들 및 상기 중앙에 위치한 다이에서의 랜덤 결함들로부터 실질적으로 어떠한 잡음도 포함하지 않는다. 다른 예에서, 일부의 실시예들에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 포함하고, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함한다. 이러한 단계들은 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다.

[0080] 상기 방법은 하나 이상의 테스트 다이들에서의 결함들을 검출하기 위해서 상기 표준 기준 다이를 상기 웨이퍼 상의 하나 이상의 테스트 다이들에 대한 출력과 비교하는 단계를 더 포함한다. 이러한 방식으로, 상기 방법은 웨이퍼에 대한 상기 표준 기준 다이를 생성하는 단계, 및 동일한 웨이퍼에 대해 획득되는 출력을 이용하여 상기 웨이퍼 상에서의 결함들을 검출하는 단계를 포함할 수 있다. 상기 표준 기준 다이 및 하나 이상의 테스트 다이들에 대한 출력은 이미지들을 포함할 수 있다. 이러한 방식으로, 상기 표준 기준 다이 검사는 이미지 기반 검사를 포함할 수 있다. 비교하는 단계에서 검출되는 결함들은 본 명세서에 기술된 임의의 결함들을 포함할 수 있다. 예컨대, 일 실시예에서, 상기 결함들은 리피터 결함들을 포함할 수 있다. 다른 실시예에서, 상기 결함들은 상기 웨이퍼를 가공하는데에 이용되는 레티클의 제조에 의해 야기되는 조직적인 결함들을 포함한다. 추가의 실시예에서, 상기 결함들은 조직적인 결함들을 포함하고, 상기 하나 이상의 테스트 다이들은 PWQ 방법론을 이용하여 상기 웨이퍼 상에 형성된다. 그러한 몇몇 실시예들에서, 본 명세서에 기술된 바와 같이 출력이 상기 중앙에 위치한 다이의 출력과 결합되는 하나 이상의 다이들은 상기 중앙에 위치한 다이에 인접하지는 않지만 상기 웨이퍼에 걸쳐 분산된 하나 이상의 다이들을 포함한다. 공동 소유되는 Peterson 등의 미국특허번호 제6,902,855호에 기술된 PWQ 방법론을 이용하여 상기 하나 이상의 테스트 다이들이 상기 웨이퍼 상에 형성될 수 있고, 이 출원은 본 명세서에 마치 전체로 기술된 바와 같이 참조에 의해서 편입된다. 본 명세서에 기술된 실시예들은 이 특허에 기술된 임의의 방법(들)에서의 임의의 단계(들)를 포함할 수 있다.

[0081] 이러한 방식으로, 본 명세서에 기술된 바와 같이 모니터링될 수 있는 조직적 결함들의 소스들은, 조직적인 결함들이 디자인 프로세스 윈도우 또는 디자인 프로세스 윈도우 마진을 결정하는데에 이용되는 PWQ 어플리케이션들에서 관심 있는 조직적 결함들뿐만 아니라 레티클 제조에 의해 야기되는 결함들을 포함한다. 특히, 본 명세서에 기술된 방법들은 제품 PWQ 어플리케이션들에 대해 바람직하게 이용될 수 있는데, 왜냐하면 그렇지 않으면 그러한 어플리케이션들에서 부족할 수 있는 적절한 표준 기준 다이들을 제공하기 위해 본 명세서에 기술된 실시예들이 이용될 수 있기 때문이다. 추가로, 본 명세서에 기술된 리피터 결함 검출 접근법들은 다수의-다이 레티클의 리피터 결함 검사와 같은 종래의 리피터 결함 검출 어플리케이션들을 향상시키는데에 이용될 수 있다. 예컨대, 그러한 어플리케이션들에서, 다수의 테스트 다이가 향상된 리피터 결함 신호들을 획득하고 랜덤 잡음을 제거하기 위해서 본 명세서에서 기술된 바와 같이 이용될 수 있다.

[0082] 일 실시예에서, 상기 방법의 모든 단계들이 상기 웨이퍼의 검사의 런타임 동안에 수행될 수 있다. 이러한 방식으로, 상기 방법은 리피터 결함들의 런타임 검출을 포함할 수 있다. 예컨대, 근본적인 픽셀 비교 레벨에서, 리피터 결함들의 런타임 검출은 상기한 단계들을 포함할 수 있다. 특히, 표준 기준 다이 이미지는 런타임 동안에 생성될 수 있다. 그러면 상기 리피터 결함들을 검출하기 위해서, 상기 비교가 두 개의 이미지들 사이, 즉 상기 표준 기준 다이 이미지 및 상기 테스트 다이 이미지 사이에서 수행될 수 있다. 물론, 런타임 동안에 보다 넓은 세트의 통계치를 획득하기 위해서 보다 많은 다이들이 동일한 방식으로 검사될 수 있다. 그러한 구현에서, 상기 표준 기준 다이는 컴퓨터 시스템(예컨대, 병렬 프로세서의 각각의 리프 노드(leaf node) 상에서)에 저장(캐

성)될 수 있다. 이러한 방식으로, 본 명세서에 기술된 실시예들은 테스트 다이에 대한 출력을 절대 기준에 대한 출력과 비교함으로써 조직적인 결합들을 검출하기 위해서 보완적 검사 방법들을 이용할 수 있다.

[0083] 일 실시예에서, 상기 방법은 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하여 그에 따라 두 개 이상의 테스트 다이들에 대한 결합된 출력이 하나 이상의 테스트 다이들 각각에 대한 출력보다 랜덤 결합들로부터 더 적은 잡음을 포함하게 하는 단계를 포함한다. 예컨대, 상기 테스트 다이의 "리피터" 특징은 리피터 S/N을 증폭시키고 그리고 랜덤 잡음(또는 랜덤 결합들)을 제거하기 위해 활용될 수 있다. 그러한 일 실시예에서, 상기 표준 기준 다이를 생성하기 위해 상기한 것과 유사한 방식으로 상기 테스트 다이가 테스트 웨이퍼 상에서의 다수의 다이들로부터의 출력을 이용하여 생성될 수 있다. 추가로, 일 실시예에서, 상기 방법은 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하는 단계를 포함하고, 이는 본 명세서에 기술된 바와 같이 수행될 수 있으며, 상기 비교하는 단계는 두 개 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 상기 표준 기준 다이와 상기 두 개 이상의 테스트 다이들에 대한 결합된 출력을 비교하는 단계를 포함한다. 그러한 일 실시예에서, 검출되는 결합들은 리피터 결합들을 포함한다. 이러한 방식으로, 상대적으로 잡음이 없는 표준 기준 다이 및 상대적으로 잡음이 없는 테스트 다이가 생성될 수 있고, 이러한 방식으로 잡음을 감소시키는 것은 랜덤 결합들의 검출을 바람직하게 감소시킬 것이다.

[0084] 표준 기준 다이 기반 검사의 하나의 한계는 상기 표준 기준 다이 웨이퍼 및 상기 테스트 다이 웨이퍼 사이의 컬러 또는 위상 차이들일 수 있다. 하지만, 이러한 이슈들은, 자동-스레스홀딩(auto-thresholding), MDAT, 히스토그램 등화 등을 포함하는 하나 이상의 많은 잘 테스트되는 전체적 컬러 보상 알고리즘들에 더하여 BB DUV 또는 BB EC 모드를 이용함으로써 성공적으로 극복될 수 있다. 특히, 일 실시예에서, 상기 비교하는 단계는 적응적 스레스홀딩을 이용하여 수행된다. 예컨대, 기본적인 비교 접근법은 MDAT와 같은 적응적 스레스홀딩 알고리즘을 이용할 수 있고, 이는 다수의 다이로부터 결정된 하나 이상의 통계치들을 이용하여 스레스홀딩에 의한 컬러에 상대적으로 영향을 받지 않게 비교할 수 있다.

[0085] 본 명세서에서 기술되는 방법들에서, 웨이퍼 내에서 그들 스스로 반복하는 경향이 있지만 두 개의 웨이퍼들에 걸쳐 별개인 실제의 로컬 컬러 변화들은 문제를 일으킬 수 있다. 하지만, 그러한 컬러 변화들은 보다 후방의 말단층들에서 발생하는 경향이 있고 그리고 시스템들 사이의 자동초점 응답들에서의 에러들에 기인한다.

[0086] 일부의 실시예들에서, 상기 비교하는 단계는 하나 이상의 테스트 다이들 및 상기 표준 기준 다이에 대한 히스토그램들의 등화를 이용하여 하나 이상의 테스트 다이들 및 표준 기준 다이를 정렬시키는 단계를 포함한다. 이러한 방식으로, 히스토그램 등화가 상기 비교 단계에서 이용될 수 있다. 히스토그램 등화는 일반적으로, 상기 히스토그램들이 상이한지 여부를 결정하기 위해 두 개 이상의 다이들에 대한 출력의 그레이 레벨과 같은 하나 이상의 속성들의 히스토그램들을 이용하는 단계를 포함할 수 있다. 상기 히스토그램들이 충분히 상이하면, 상기 방법은 상기 히스토그램을 이용하여 서로에 대해 이미지들을 유효하게 정규화하기 위해서 상기 이전에 상기 출력의 보상을 수행하고 그것에 의해 상기 히스토그램을 이용하여 상기 이미지들을 서로 유효하게 매핑하는 단계를 포함할 수 있다. 모든 기술들에서 마찬가지로, 보간 잡음 소스들이 지배하기 시작할 수 있음에 따라(물론 추가적인 계산 버짓들), 다수의 접근법들을 이용해 수학 체감(diminishing returns)의 포인트가 존재한다.

[0087] 다른 실시예에서, 상기 결합하는 단계는 상기 표준 기준 다이에서의 픽셀들의 이웃 및 상기 하나 이상의 테스트 다이들에 대한 출력에서의 픽셀들의 이웃의 템플릿 매칭을 포함한다. 이러한 방식으로, 상기 방법은 템플릿 매칭에 의한 결합 검출을 포함할 수 있다. 예컨대, 대안적인 접근법(계산적으로 보다 고가일 수 있음)은 5 픽셀 대 5 픽셀 이웃에서 템플릿 매칭을 수행하는 것이다. 제곱된 차이들의 합(SSD; sum of squared differences) 또는 정규화된 교차 상관(NCC; normalized cross correlation) 중 어느 하나가 템플릿 매칭에 대해 이용될 수 있다. 상기 두 개의 이미지들 사이의 임의의 차이들이 강한 미스매치로서 식별될 수 있다. 두 단계들이 보통 상이함에도 불구하고 템플릿 매칭은 또한 상기 정렬 단계와 결합될 수 있는데, 왜냐하면 정렬에 대해서 더 큰 서치 윈도우가 유일함 및 그에 따라 상대적으로 정확한 정렬을 보정하는데에 이용될 수 있기 때문이다.

[0088] 일 실시예에서, 상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계는 상기 웨이퍼 상의 테스트 다이들의 일부에 대해서만 출력을 획득하는 단계를 포함한다. 예컨대, 표준 기준 다이 기반 검사에 대한 통계적으로 중요한 결과들은 상기 웨이퍼의 일부분(예컨대, 일반적으로 약 5개의 다이를 내지 약 8개의 다이들)만을 검사함으로써 획득될 수 있고, 이는 한 시간 이내에 수행될 수 있다(로트 홀드 샘플링 시간(lot hold sampling time)). 예컨대, 전체 웨이퍼에 대해 생성되는 출력이 랜덤 결합 검출에 대해 이용되는 랜덤 결합들을 검출하는데에 이용되는 다이-대-다이 검사 기술들과는 달리, 본 명세서에 기술된 실시예들은 전체 웨이퍼 미만에 대해 획득되는

출력(예컨대, 상기 웨이퍼 상에서 중앙에 위치하는 다이들과 같은 오직 하나의 다이에 대한 출력)을 이용하여 표준 기준 다이 검사를 수행할 수 있다. 퍽셀 당 추가적인 시간(종래의 스캔 시간들 미만의 정도일 수 있음)은 패스 당 더 많은 광자들을 획득하기 위해 활용될 수 있다(예컨대, S/N을 더욱 증가시키기 위해서 다수의 광학 모드들(다수의-패스)에 대해서 또는 ADI 층들에 관한 BB DUV EC 모드에 대하여). 추가로, 퍽셀 당 추가적인 시간이 계산 비용들을 적당하게 유지하기 위해 활용될 수 있다(예컨대, 현재의 계산 비용들과 거의 동일하거나 또는 약간 더 높음).

[0089] 기술된 바와 같이, 상기 표준 기준 다이를 생성하는데에 이용되는 출력 및 상기 테스트 다이(들)에 대한 출력이 동일한 웨이퍼에 대해서 획득될 수 있다. 하지만, 본 명세서에서 추가로 기술되는 다른 실시예들에서, 상기 표준 기준 다이를 생성하는데에 이용되는 출력은 표준 기준 웨이퍼에 대해 획득될 수 있는 한편 상기 하나 이상의 테스트 다이들에 대한 출력은 상이한 웨이퍼에 대해 획득될 수 있다.

[0090] 특히, 추가적인 실시예들은 웨이퍼를 검사하기 위한 상이한 방법에 관한 것이다. 이 방법은 표준 기준 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계를 포함하고, 이는 본 명세서에서 기술되는 바와 같이 수행될 수 있다. 상기 표준 기준 웨이퍼는 당업계에서 기지의 임의의 적절한 방식으로 제조될 수 있다. 상기 방법은 또한 출력의 내부 다이 위치들에 기초하여 상기 표준 기준 웨이퍼 상에 위치한 하나 이상의 다이들 및 상기 표준 기준 웨이퍼 상에 중앙에 위치한 다이에 대한 출력을 결합하는 단계를 포함한다. 이러한 결합 단계는 본 명세서에서 추가로 기술되는 바와 같이 수행될 수 있다. 추가로, 상기 방법은 상기 결합 단계의 결과들에 기초하여 표준 기준 다이를 생성하는 단계를 포함하고, 이는 본 명세서에서 기술된 바와 같이 수행될 수 있다. 예컨대, 일 실시예에서, 상기 방법은 상기 표준 기준 다이를 디자인 데이터 공간에 정렬시키는 단계를 포함하고, 상기 생성하는 단계는 상기 디자인 데이터 공간에서의 미리 결정된 영역들에 대응하는 상기 디자인 데이터 공간에서의 위치들에 대해서만 상기 표준 기준 다이를 생성하는 단계를 포함한다. 이러한 단계들은 본 명세서에 기술된 바와 같이 수행될 수 있다. 상기 표준 기준 다이는 본 명세서에 기술된 바와 같이 구성될 수 있다. 예컨대, 일 실시예에서, 상기 표준 기준 다이는 하나 이상의 다이들 및 중앙에 위치한 다이에서의 랜덤 결합들로부터 실질적으로 어떠한 잡음도 포함하지 않는다.

[0091] 상기 방법은 상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계를 더 포함하고, 이는 본 명세서에 기술된 바와 같이 수행될 수 있다. 예컨대, 일 실시예에서, 상기 웨이퍼에 대한 검사 시스템의 출력을 획득하는 단계는 상기 웨이퍼 상의 테스트 다이들의 일부에 대해서만 출력을 획득하는 단계를 포함하고, 이는 본 명세서에서 추가로 기술되는 바와 같이 수행될 수 있다. 다른 실시예에서, 상기 표준 웨이퍼 및 상기 웨이퍼에 대한 출력을 획득하는 단계는 BB DUV 모드 검사를 이용하여 수행될 수 있다. 추가적인 실시예에서, 상기 표준 기준 웨이퍼 및 상기 웨이퍼에 대한 출력을 획득하는 단계는 BB EC 모드 검사를 이용하여 수행될 수 있다.

[0092] 게다가, 상기 방법은 하나 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 상기 표준 기준 다이와 상기 웨이퍼 상의 하나 이상의 테스트 다이들에 대한 출력을 비교하는 단계를 포함하고, 이는 본 명세서에 기술된 바와 같이 수행될 수 있다. 예컨대, 일 실시예에서, 상기 비교하는 단계는 적응적 스레스홀딩을 이용하여 수행되고, 이는 상기한 바와 같이 수행될 수 있다. 다른 예에서, 일부의 실시예들에서, 상기 비교하는 단계는 상기 표준 기준 다이 및 상기 하나 이상의 테스트 다이들에 대한 히스토그램들의 등화를 이용하여 상기 표준 기준 다이 및 상기 하나 이상의 테스트 다이들에 대한 출력을 정렬시키는 단계를 포함하고, 이는 본 명세서에 기술된 바와 같이 수행될 수 있다.

[0093] 결합들을 검출하기 위해서 상기 표준 기준 다이와 비교되는 상기 웨이퍼 상의 하나 이상의 테스트 다이들에 대한 출력은 본 명세서에 기술된 바와 같이 생성될 수 있다. 예컨대, 상기 방법은 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하여 그에 따라 두 개 이상의 테스트 다이들에 대한 결합된 출력이 하나 이상의 테스트 다이들 각각에 대한 출력보다 랜덤 결합들로부터 더 적은 잡음을 포함하게 하는 단계를 포함한다. 그러한 결합은 본 명세서에서 추가로 기술되는 바와 같이 수행될 수 있다. 다른 실시예에서, 상기 방법은 하나 이상의 테스트 다이들의 두 개 이상에 대한 출력을 결합하는 단계를 포함하고, 이는 본 명세서에서 기술된 바와 같이 수행될 수 있으며, 상기 비교하는 단계는 두 개 이상의 테스트 다이들에서의 결합들을 검출하기 위해서 두 개 이상의 테스트 다이들에 대한 결합된 출력과 상기 표준 기준 다이를 비교하는 단계를 포함한다. 그러한 일 실시예에서, 상기 결합들은 리피터 결합들을 포함한다.

[0094] 이러한 방법에서 검출되는 결합들은 본 명세서에서 기술된 임의의 결합들을 포함할 수 있다. 예컨대, 일 실시예에서, 상기 결합들은 리피터 결합들을 포함한다. 다른 실시예에서, 상기 결합들은 상기 웨이퍼를 가공하는데에 이용되는 레티클의 제조에 의해 야기되는 조직적 결합들을 포함한다. 추가의 실시예에서, 상기 결합들은 조

직적인 결함들을 포함하고, 하나 이상의 테스트 다이들은 PWQ 방법론을 이용하여 상기 웨이퍼 상에서 형성된다.

[0095] 본 명세서에서 기술된 실시예들은 상기한 바와 같이 웨이퍼-대-웨이퍼(wafer-to-wafer) 비교를 이용하여 결함들을 검출하도록 구성될 수 있는데, 왜냐하면 상기 실시예들이 시스템-대-시스템(system-to-system) 잡음을 처리하도록 구성될 수 있기 때문이다. 예컨대, 웨이퍼 검사 시스템들 상의 많은 에러들이 공통 모드인 경향이 있는데, 이는 그들이 일반적으로 동일한 시스템 상에서 제조되기 때문이고 – 일반적으로 공통 모드 아웃 초점 에러들로의 웨이퍼 공간에 충분하게 밀접함 –, 비교되는 데이터가 동일한 광학 시야 등 내부에서 취해진다. 픽셀 크기 미스매치, 시간 지연 집적(TDI; time delay integration) 카메라 회전 정렬 에러들, 다이-대-다이 정렬 등과 같은 많은 에러들이 그러므로 공통 모드 또는 RTA 시스템 때문에 유효하게 제거될 수 있다. 이러한 에러 소스들의 일부 셋업 동안의 누적적 스티칭 에러(cumulative stitching error), 2차원(2D) 상관 에러, 광학 왜곡 및 확대 에러, 초점 유도된 이미지 이동, TDI 회전 에러, TDI 회전 불안정도, TDI 오프셋 교정 에러, TDI 오프셋 교정 불안정도(셋업 또는 동작 동안에), 픽셀 라운딩 에러, RTA 런아웃, 및 RSS 에러를 포함한다.

[0096] 다이 대 표준 기준 다이 기반 검사 시스템에서, 이러한 에러들은 절대적인 에러들이 되고, 그러므로 바람직하게 조직적으로 접근된다. 이러한 방식으로, 표준 기준 다이 기반 검사에 대한 주요 한계들 중 하나가 웨이퍼-대-웨이퍼 서브-픽셀 정렬일 수 있다. 약 1 픽셀 에러 웨이퍼-대-웨이퍼 미만을 성취하기 위한 일 접근법은 필수적으로 각각의 웨이퍼에 대한 출력을 디자인 데이터 공간에 정렬시켜 그에 따라 유효하게 상기 웨이퍼들을 서로 정렬시키는 것일 수 있다. 예컨대, 일 실시예에서, 상기 방법은 비교 단계 이전에 디자인 데이터 공간에 대하여 하나 이상의 테스트 다이들에 대한 출력의 위치 및 상기 표준 기준 다이의 위치를 결정하는 단계, 및 상기 비교 단계 이전에 상기 디자인 데이터 공간에 대하여 상기 하나 이상의 다이들에 대한 출력 및 상기 표준 기준 다이의 위치들을 기초로 하여 상기 하나 이상의 테스트 다이들에 대한 출력 및 상기 표준 다이를 정렬시키는 단계를 포함한다. 웨이퍼들에 대한 출력을 디자인 데이터 공간에 정렬시키는 단계는, 공동 소유되는 Kulkarni 등에 의한 2006년 11월 20일자 출원된 미국출원번호 제11/561,735호이고 미국출원공개번호 제2007/0156379호로서 2007년 7월 5일자 공개된 특허에서 기술된 바와 같이 수행될 수 있고, 이 출원은 본 명세서에 마치 전체로 기술된 바와 같이 참조에 의해서 편입된다. 본 명세서에서 기술된 실시예들은 이 특허 출원에서 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다.

[0097] 취해질 수 있는 다른 접근법은 비교의 목적들을 위해 프레임 바이 프레임 정렬(frame by frame alignment)을 수행하는 것이다. 예컨대, 다른 실시예에서, 상기 방법은 프레임 정렬 기술에 의한 프레임을 이용하여 비교하는 단계 이전에 상기 표준 기준 다이를 상기 하나 이상의 테스트 다이들에 대한 출력에 정렬시키는 단계를 포함한다. 프레임 바이 프레임 정렬은 상기 테스트 다이에 대해 획득된 출력의 각 프레임을 표준 이미지에 정렬시키는 것을 포함할 수 있다. 프레임들을 서로 정렬시키는 것은 상기 출력의 하나 이상의 속성들에 기초하여 프레임들의 스케일링, 이동 등을 포함할 수 있다. 예컨대, 상기 프레임들의 정렬은 평균 대 평균 비교, 통계적 기준 대 통계적 기준 비교 등에 기초하여 수행될 수 있다. 프레임 바이 프레임 정렬은 프레임들의 각각의 쌍 사이의 오프셋 에러뿐만 아니라 스케일 팩터 에러를 결정하는 것을 포함할 수 있고, 이는 그러한 정렬이 전체 이미지의 조작을 포함하기 때문에 실행가능할 수 있다. 추가로, 이러한 정렬은 런아웃 에러들을 보상하기 위해서 더 많은 중첩 구역(예컨대, 현재 이용되는 중첩 구역들보다 약 2배 정도 큰 중첩 구역)을 이용하여 수행될 수 있다.

[0098] 웨이퍼에 대한 출력을 디자인 데이터 공간에 정렬시키는 것에 의해 이루어지는 측정들에 더하여, 개별적인 RTA 에러들이 또한 표준 기준 다이 기반 검사 및 검사 스캔에 대해 활용될 수 있다. 예컨대, RTA가 디자인 데이터 공간과 같은 절대 기준 시스템에 걸쳐 가질 수 있는 일 장점은 RTA가 상대적인 RTA 오프셋 곡선들을 만드는데에 이용될 수 있다는 것이다. 그러므로, 전체적인 할당이 각각의 스와스(swath)를 이용해 관리될 수 있고, 상기 스와스들은 그들 각각의 RTA를 이용하여 서로 정렬될 수 있다. 예컨대, 일 실시예에서, 상기 방법은 전체적인 정렬에 대해서 하나 이상의 테스트 다이들에 대한 출력의 제1 스와스를 정렬시키는 단계, 및 상기 하나 이상의 테스트 다이들에 대한 출력의 제2 스와스를 상기 제1 스와스에 정렬시켜서 그에 따라 상기 제2 스와스를 전체적인 정렬에 정렬시키는 단계를 포함한다.

[0099] 그러한 일 실시예에서, 도 4에 도시된 바와 같이, 상기 스와스를 내의 화살표들에 의해 도시되는 바와 같이 웨이퍼를 반대 방향들로 스캐닝함으로써, 출력의 두 개의 스와스들(N 및 N+1)이 웨이퍼(도 4에 미도시)에 대해 획득될 수 있다. 도 4에 도시된 바와 같이, 스와스들(N 및 N+1)은 웨이퍼 공간에서의 영역(18)에서 서로 부분적으로 중첩한다. 그러므로, 두 스와스들은 영역(18)에 대한 출력을 포함할 것이다. 그러한 것으로서, 전체적인 정렬 특징들을 포함할 수 있는 이러한 영역에 대한 출력은 하나의 스와스를 다른 스와스에 정렬시키는데에 이용

될 수 있다. 그러한 하나의 실시예에서, 도 5는 두 개의 연속적인 스캔들에 대한 출력이 중첩되는 웨이퍼 공간에서의 스와스-내 중첩 영역(18)에서 형성되는 특징들(20 및 22)을 도시한다. 특징들(20 및 22)은 스와스-대-스와스 등록(swath-to-swath registration)을 수행하기 위해 이용될 수 있다. 특징들(20 및 22)은 당업계에 알려진 임의의 적절한 전체적 정렬 특징들을 포함할 수 있다.

[0100] 하지만, 그러한 시스템이 약 0.1 픽셀들 미만의 정렬 에러들을 성취할 수 있는지 여부가 아직 제시되어야 한다. 그러므로, 디자인 데이터 공간으로의 정렬에 의해 성취될 수 있는 정확도보다 훨씬 나은 정도의 정확도가 본 명세서에 기술되는 실시예들에 대해서 바람직하기 때문에, 테스트 및 표준 기준 다이들 사이의 액티브한 정렬이 수행될 수 있다.

[0101] 예컨대, 본 명세서에서 기술된 상기 방법은, 샘플링이 에일리어싱되는 정도가 이미지가 적절하게 구성되는 것을 가능하게 하는 것을 보장하기 위해 에일리어싱이 또한 반복되는 액티브 RTA를 이용할 수 있다. 일 실시예에서, 상기 웨이퍼에 대한 검사 시스템의 출력은 상기 웨이퍼 상의 조명 스팟 당 적어도 두 개의 샘플들을 포함한다. 예컨대, 종래의 BF RTA 없이 가까운 시일 내에 동작하기 위한 이러한 기술들에 대해서, 충분한 샘플링(예컨대, PSF 당 약 3.5 샘플들을 초과함)을 갖는 광학 모드들을 이용하는 레티클 검사 스타일 웨이퍼-대-웨이퍼 정렬 기술(예컨대, 웨이퍼-대-웨이퍼 서브-픽셀 정렬 기술)이 이용될 수 있다. 예컨대, 시뮬레이션들은 광학에서의 샘플당 약 3.5 스팟들 이상에 대해서 최소의 재구성 에러가 발생될 것이라는 것을 암시한다. 추가로, 상기 방법들은 정렬을 수행하기 위해서 특정한 디-컨볼루션(de-convolution) 기술들을 이용할 수 있다. 예컨대, 상기 검사가 실질적으로 오버샘플링되는 실질적으로 작은 픽셀 크기를 이용하여 수행되면, 상기 검사의 민감도가 감소될 수 있다. 하지만, 광학들의 PSF에 기초하여, 상기 광학들의 한계들이 상기 검사에 대한 적절한 파라미터들을 결정하기 위해 결정될 수 있다.

[0102] 일관적이지 않은 조명에 대한 광학 변환 함수(OTF; optical transform function) 이론으로부터, 롤리(Raleigh) 거리가 약 0.61/NA과 동일함에 반해, 일관적인 조명에 대해서는 분해능 거리가 약 0.5/NA와 동일하다. 스팟 당 적어도 약 두 개의 샘플들의 나이퀴스트(Nyquist) 기준을 적용하는 것은, 일관적이지 않은 조명에 대해 약 0.3/NA 및 일관적인 조명에 대해 약 0.25/NA와 동일한  $R_c$ 에 있는 것을 결정되고, 그리고 0.9의 NA에 대해서는 일관적이지 않은 조명에 대해 약 2.92 샘플들 및 일관적인 조명에 대해 약 3.6 샘플들과 동일한  $R_c$ 에 있는 것으로 결정된다. 언더샘플링 에러들(나이퀴스트 픽셀들에 대한 실제 픽셀들의 비율로서 표현될 수 있음)을 위해, 에러들을 에일리어싱하는 것은 1.0 미만의 비율들에서 획득되는 픽셀들의 재구성을 가능하게 할 것이다. 추가로, 시스템이 빈 확대 공간으로 이동함에 따라, 정렬 보간 에러들이 감소될 것이다. EC 모드에서의 에일리어싱 에러들을 제어하기 위한 하나의 추가적인 방법은 NA를 독립적으로 줄이는(stop down) 것이다.

[0103] 본 명세서에 기술된 방법들은 또한 본 명세서에 기술된 임의의 단계들의 결과들을 저장 매체(본 명세서에 추가로 기술되는 바와 같은)에 저장하는 단계를 포함할 수 있다. 예컨대, 상기 방법은 생성된 표준 기준 다이를 상기 저장 매체에 저장하는 단계를 포함할 수 있다. 생성된 표준 기준 다이는 본 명세서에 기술되는 임의의 구성을 가질 수 있다. 추가로, 상기 저장하는 단계는 본 명세서에 기술되는 임의의 다른 방법 실시예들의 임의의 단계들의 임의의 다른 결과들뿐만 아니라 상기 생성하는 단계의 결과들을 저장하는 단계를 포함할 수 있다. 상기 결과들은 당업계에서의 기지의 임의의 방식으로 저장될 수 있다. 추가로, 상기 저장 매체는 본 명세서에 기술되는 임의의 저장 매체 또는 당업계에서의 기지의 임의의 다른 적절한 저장 매체를 포함할 수 있다. 상기 결과들이 저장된 이후에, 상기 결과들은 상기 저장 매체에서 액세스될 수 있고, 본 명세서에 기술되는 임의의 방법, 시스템, 또는 컴퓨터-판독가능한 매체 실시예들에 의해 이용될 수 있으며, 사용자에게의 디스플레이를 위해 포매팅될 수 있고, 다른 소프트웨어 모듈, 방법, 또는 시스템 등에 의해 이용될 수 있다. 게다가, 상기 결과들은 "영구적으로", "반영구적으로", 일시적으로 또는 일부의 시간 기간 동안 저장될 수 있다. 예컨대, 상기 저장 매체는 랜덤 액세스 메모리(RAM)일 수 있고, 상기 생성하는 단계의 결과들은 상기 저장 매체에서 필수적으로 무기한으로 지속되지 않을 수 있다.

[0104] 다른 실시예는 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하고 그리고/또는 웨이퍼를 검사하도록 구성되는 시스템에 관한 것이다. 상기 시스템은 본 명세서에 기술된 실시예들 중 임의의 실시예에 따라 상기 표준 기준 다이를 생성하도록 구성될 수 있다. 상기 시스템은 또한 또는 대안적으로 본 명세서에 기술된 실시예들 중 임의의 실시예에 따라 상기 웨이퍼를 검사하도록 구성될 수 있다.

[0105] 그러한 시스템의 일 실시예가 도 6에 도시된다. 도 6에 도시된 바와 같이, 일 실시예에서, 상기 시스템은 웨이퍼들에 대한 출력을 획득하도록 구성되는 검사 시스템(24)을 포함한다. 검사 시스템(24)은 림 스플리터(28)로 광을 지향하도록 구성되는 광원(26)을 포함한다. 상기 광원은 본 명세서에 기술된 임의의 스펙트럼 영역(들)

(예컨대, DUV)에서 광을 생성하도록 구성되는, 당업계에서의 기지의 임의의 적절한 광원을 포함할 수 있다. 추가로, 상기 광원은 출력이 BB 및/또는 NB 스펙트럼 영역에서 획득될 수 있게 BB 광 및/또는 NB 광을 생성하도록 구성될 수 있다. 빔 스플리터(28)는 당업계에서의 기지의 임의의 적절한 광학 컴포넌트를 포함할 수 있다. 빔 스플리터(28)는 광을 웨이퍼(30)로 지향하도록 구성된다.

[0106] 상기 검사 시스템은 또한 광원(26)으로부터 웨이퍼(30)로의 광의 경로에 포지셔닝되는 어퍼쳐들과 같은 임의의 다른 적절한 광학 컴포넌트(들)(미도시)를 포함할 수 있고, 이는 상기 검사 시스템에서 스테이지(32)에 의해서 지지될 수 있다. 스테이지(32)는 당업계에서의 기지의 임의의 적절한 로봇식의 그리고/또는 기계적인 어셈블리를 포함할 수 있다. 스테이지(32)는 상기 웨이퍼를 이동시키도록 구성될 수 있고(예컨대, 회전 및/또는 이동에 의해서), 그에 따라 상기 웨이퍼로 지향되는 광이 꾸불꾸불한 스캔 경로와 같은 스캔 경로에서 웨이퍼에 걸쳐서 스캐닝될 수 있다.

[0107] 도 6에 추가로 도시된 바와 같이, 광원(26)으로부터의 광은 실질적으로 보통 입사각으로 빔 스플리터(28)에 의해 웨이퍼(30)로 지향될 수 있다. 하지만, 상기 검사 시스템은 상기 광이 임의의 적절한 입사각(들)으로 상기 웨이퍼로 지향될 수 있게 구성될 수 있다. 상기 웨이퍼로부터 반사되는 광은 빔 스플리터(28)를 통과하여 검출기(34)로 향하고, 이는 당업계에서의 기지의 임의의 적절한 비-이미징 검출기 또는 이미징 검출기를 포함할 수 있다. 상기 검사 시스템은 상기 웨이퍼로부터 반사되는 광의 경로에 포지셔닝되는 어퍼쳐들과 같은 임의의 다른 적절한 광학 컴포넌트(들)(미도시)를 포함할 수 있다. 검출기(34)는 상기 웨이퍼로부터 반사되는 광에 응답하는 출력을 생성하도록 구성된다.

[0108] 검사 시스템(24)이 도 6에서는 BF 검사 시스템으로서 도시되었음에도 불구하고, 본 명세서에 기술된 시스템 실시예들에 포함된 검사 시스템은 DF 구성, EC 구성 등과 같은 임의의 적절한 구성을 포함할 수 있다. 추가로, 상기 검사 시스템은 전자 빔 기반의 검사 시스템으로서 구성될 수 있다. 게다가, 상기 검사 시스템은 상기 검사 시스템의 하나 이상의 파라미터들이 상기 검사 시스템이 상이한 모드들의 검사를 수행할 수 있게 조정가능하도록 구성될 수 있다. 게다가, 상기 검사 시스템은 상기 검사 시스템이 두 개 이상의 모드의 검사들을 동시에 또는 순차적으로 수행할 수 있게 구성될 수 있다.

[0109] 상기 조사 시스템의 컴퓨터 시스템(36)은 상기 컴퓨터 시스템이 상기 검출기에 의해 생성되는 출력을 수신할 수 있도록 임의의 절절한 방식으로 상기 검출기에 결합될 수 있다. 상기 컴퓨터 시스템은 검사 시스템(24)의 검출기(34)에 의해 생성되는 출력을 이용하여 본 명세서에 기술된 하나 이상의 실시예들의 하나 이상의 단계들을 수행하도록 구성될 수 있다. 예컨대, 상기 컴퓨터 시스템은 상기 출력의 내부 다이 위치들에 기초하여 상기 웨이퍼 상에 위치한 하나 이상의 다이들 및 상기 웨이퍼(30) 상의 중앙에 위치한 다이에 대해 상기 검사 시스템(24)에 의해 획득된 출력을 결합하도록 구성될 수 있다. 상기 컴퓨터 시스템은 또한 상기 결합된 출력에 기초하여 상기 표준 기준 다이를 생성하도록 구성될 수 있다. 일부의 실시예들에서, 컴퓨터 시스템(36)은 상기 컴퓨터 시스템이 상기 컴퓨터 시스템에 의해 수행되는 하나 이상의 단계들의 결과들을 저장 매체로 전송할 수 있도록 상기 저장 매체(38)와 결합될 수 있다.

[0110] 상기 컴퓨터 시스템은 당업계에서의 기지의 임의의 적절한 컴퓨터 시스템을 포함할 수 있다. 예컨대, 컴퓨터 시스템(36)은 개인용 컴퓨터 시스템, 메인프레임 컴퓨터 시스템, 워크스테이션, 이미지 컴퓨터, 병렬 컴퓨터, 또는 당업계에서의 기지의 임의의 다른 장치를 포함하는 다양한 형태들을 취할 수 있다. 일반적으로, 용어 "컴퓨터 시스템"은 메모리 매체로부터의 명령들을 실행하는 하나 이상의 프로세서들을 갖는 임의의 장치를 포괄하는 것으로 광범위하게 정의될 수 있다.

[0111] 저장 매체(38)는 판독 전용 메모리, 랜덤 액세스 메모리, 자기 또는 광학 디스크, 또는 자기 테이프와 같은 당업계에서의 기지의 임의의 적절한 저장 매체를 포함할 수 있다.

[0112] 상기한 시스템은 본 명세서에 기술된 바와 같이 추가로 구성될 수 있다(예컨대, 본 명세서에 기술된 임의의 방법(들)의 임의의 다른 단계(들)를 수행하도록).

[0113] 도 7은 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 컴퓨터-구현 방법, 웨이퍼를 검사하기 위한 방법, 웨이퍼 상의 결함들을 검출하기 위한 컴퓨터-구현 방법, 또는 이들의 몇몇 조합을 수행하기 위한 컴퓨터 시스템(44)에서 실행가능한 프로그램 명령들(42)을 포함하는 컴퓨터-판독가능한 매체(40)의 일 실시예를 도시한다. 프로그램 명령들(42)이 컴퓨터 시스템(44) 상에서 실행가능한 방법은 본 명세서에 기술된 임의의 방법(들)의 임의의 단계(들)를 포함할 수 있다. 일부의 실시예들에서, 컴퓨터 시스템(44)은 도 4에 도시된 컴퓨터 시스템(36)과 같은 검사 시스템의 컴퓨터 시스템일 수 있다. 하지만, 다른 실시예들에서는,

컴퓨터 시스템(44)이 검사 시스템에 결합되거나 또는 포함되지 않을 수 있다. 일부의 그러한 실시예들에서, 컴퓨터 시스템(44)은 독립형(stand alone) 컴퓨터 시스템으로서 구성될 수 있다. 컴퓨터-판독가능한 매체(40), 프로그램 명령들(42), 및 컴퓨터 시스템(44)은 본 명세서에 기술된 바와 같이 추가로 구성될 수 있다.

[0114] 본 명세서에 기술된 방법들과 같은 방법들을 구현하는 프로그램 명령들(42)은 컴퓨터-판독가능한 매체(40)를 통해 전송되거나 또는 여기에 저장될 수 있다. 상기 컴퓨터-판독가능한 매체는 유선, 케이블, 또는 무선 전송 링크와 같은 전송 매체일 수 있다. 상기 컴퓨터-판독가능한 매체는 또한 판독 전용 메모리, 랜덤 액세스 메모리, 자기 또는 광학 디스크, 또는 자기 테이프와 같은 저장 매체일 수 있다.

[0115] 상기 프로그램 명령들은 절차 기반 기술들, 컴퓨터 기반 기술들, 및/또는 객체 지향 기술들, 다른 것들을 포함하는 많은 방법들 중 임의의 방법으로 구현될 수 있다. 예컨대, 상기 프로그램 명령들은 원하는 바로 액티브X 컨트롤(ActiveX control)들, C++ 오브젝트(C++ object)들, 자바빈(JavaBean)들, 마이크로소프트 파운데이션 클래스("MFC"; Microsoft Foundation Class)들, 또는 다른 기술들 또는 방법론들을 이용하여 구현될 수 있다.

[0116] 추가의 실시예는 웨이퍼 상의 결함들을 검출하기 위한 컴퓨터-구현 방법에 관한 것이다. 상기 방법은 상기 웨이퍼 상에 형성된 다수의 이미지들의 구조를 결합시켜서 복합 이미지의 구조를 생성하는 단계를 포함한다. 다수의 이미지들의 구조는 본 명세서에 추가로 기술되는 바와 같이 획득될 수 있다. 상기 구조는 상기 웨이퍼 상에 형성된 임의의 구조를 포함할 수 있다. 상기 구조의 다수의 이미지들을 결합하는 단계는 본 명세서에 추가로 기술되는 바와 같이 수행될 수 있다. 일 실시예에서, 상기 결합하는 단계는 상기 다수의 이미지들을 평균하는 단계를 포함한다. 상기 다수의 이미지들을 평균하는 단계는 본 명세서에 기술된 바와 같이 또는 당업계에서의 기지의 임의의 적절한 방법 및/또는 알고리즘을 이용하여 임의의 다른 적절한 방식으로 수행될 수 있다.

[0117] 상기 다수의 이미지들은 상기 구조가 형성되는 상기 웨이퍼 상의 다수의 위치들에서 획득된다. 일 실시예에서, 상기 다수의 위치들은 동일한 디자인들을 갖는 셀들에서의 상기 구조의 위치들을 포함한다. 다른 실시예에서, 상기 다수의 위치들은 이웃하는 다이들에서의 상기 구조의 위치들을 포함한다. 예컨대, PWQ 타입 검사 동안에, 각각의 초점 및 노출 포인트로부터의 다수의 다이들이 MDAT 알고리즘에 의해 수행되는 것과 실질적으로 유사한 방식으로 함께 평균될 수 있다. 상기 다수의 위치들은 본 명세서에 기술된 바와 같이 또는 임의의 다른 적절한 방식으로 결정되거나 또는 식별될 수 있다.

[0118] 일 실시예에서, 상기 복합 이미지가 상기 다수의 이미지들보다 더 적은 라인 에지 거칠기(LER; line edge roughness)를 갖도록 상기 결합하는 단계가 수행된다. 다른 실시예에서, 상기 복합 이미지가 상기 다중 이미지들보다 더 작은 랜덤 변화를 갖도록 상기 결합하는 단계가 수행된다. 예컨대, 개별 구조들은 조직적인 에러들을 저지하는 LER과 같은 랜덤 변화들을 가질 수 있다. 하지만, 상기 구조의 다중 이미지들을 함께 평균함으로써, 동일한 셀들(예컨대, 인접한 동일한 셀들)로부터 또는 이웃하는 다이들로부터, 복잡 이미지가 임의의 개별 구조보다 훨씬 낮은 LER 또는 랜덤 변화를 갖도록 구성될 수 있다.

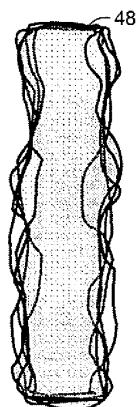

[0119] 그러한 일 실시예에서, 도 8에 도시된 바와 같이, 웨이퍼 상에 형성된 구조의 다수의 이미지들(46)은 개별 특성들의 개별 이미지들이 LER을 보인다는 것을 설명한다. 하지만, 도 9에 도시된 바와 같이, 도 8에 도시된 구조에 대한 다수의 이미지들을 평균함으로써 생성되는 상기 구조의 복합 이미지(48)는 상기 구조의 복합 이미지가 다수의 이미지들(46) 각각과 비교하여 더 낮은 LER을 갖는다는 것을 설명한다.

[0120] 추가의 실시예에서, 상기 복합 이미지가 상기 다수의 이미지들 각각에 비해 더 낮은 그레이 레벨 잡음을 갖도록 상기 결합하는 단계가 수행된다. 예컨대, 상기 복합 이미지는 산탄 잡음과 같은 소스들로부터의 더 적은 그레이 레벨 잡음을 포함할 것이다. 이러한 방식으로, 본 명세서에 기술된 실시예들은 산탄 잡음 및 다른 이미지 잡음 아티팩트들에서의 감소를 바람직하게 제공한다.

[0121] 상기 방법은 또한 상기 웨이퍼 상의 결함들을 검출하기 위해 상기 복합 이미지를 기준과 비교하는 단계를 포함한다. 일 실시예에서, 상기 기준은 상기 구조의 기지의 양호한 이미지를 포함한다. 다른 실시예에서, 상기 기준은 표준 기준 다이에서 획득된 상기 구조의 이미지를 포함한다. 추가의 실시예에서, 상기 기준은 기준 이미지, 복합 테스트 이미지, 또는 PWQ 다이에서 획득되는 상기 구조의 복합 테스트 이미지 및 기준 이미지를 포함한다. 일부의 실시예들에서, 상기 기준은 렌더링된(rendered) 데이터베이스 이미지를 포함한다. 이러한 방식으로, 상기 복합 이미지는 기지의 양호한 이미지(표준 기준 다이 또는 PWQ 다이로부터의) 또는 렌더링된 데이터베이스 이미지와 비교될 수 있다. 추가의 실시예에서, 상기 기준은 상기 웨이퍼 또는 상이한 웨이퍼 상의 다수의 위치들에서 획득되는 다수의 이미지들로부터 생성되는 상기 구조의 복합 이미지를 포함한다. 그러한 기준들은 본 명세서에 추가로 기술되는 바와 같이 생성될 수 있다. 추가로, 이러한 실시예들에서 이용되는 상기 기준

은 본 명세서에 기술되는 다른 기준들을 포함할 수 있다.

[0122] 일 실시예에서, 상기 결합들은 조직적인 결합들을 포함한다. 조직적인 결합들은 단일 다이의 어레이 구조 내에서 또는 다수의 다이 상의 동일한 구조 내에서 반복적으로 발생한다. 본 명세서에 기술된 실시예들에서 그러한 결합들을 검출하는 것은 바람직할 수 있는데, 왜냐하면 본 명세서에 기술된 실시예들은 향상된 조직적 결합 검출을 제공하기 때문이다. 특히, 본 명세서에 기술되는 실시예들은 향상된 조직적 결합 검출을 위한 랜덤 액세스 에러들을 감소시키기 위해서 다수의 특성 평균을 이용한다. 이러한 방식으로, 다수의 테스트 이미지들을 함께 평균하는 것은 조직적 결합들에 대한 검사 민감도를 향상시킨다. 그러한 것으로서, 본 명세서에 기술되는 실시예들은 웨이퍼 검사 상의 조직적 결합들의 향상된 민감도를 제공한다. 추가로, 본 명세서에 기술되는 실시예들은 바람직하게 랜덤 방해 결합들로의 감소된 민감도를 제공한다. 예컨대, 도 8에 도시된 바와 같이, 상기 구조의 다수의 이미지들은, 거짓 방해로서 검출될 수 있고 그러므로 결합 검출의 민감도를 제한할 수 있는 LER을 보여준다. 하지만, 도 9에 도시된 상기 구조의 복합 평균된 이미지는 조직적 라인 폭(LW; line width) 변화로의 더 나은 민감도를 가능하게 하기 위해서 상기 LER이 얼마나 감소되는지를 보여준다.

[0123] 다른 실시예에서, 상기 결합들은 상기 구조의 LER과 대략 동일한 크기를 갖는다. 예컨대, 본 명세서에 기술된 실시예들은 상기 결합 크기가 LER 및 다른 결합들 또는 변화들과 유사할 때에 웨이퍼 상의 조직적 결합들(부정확한 광학 근접 보정(OPC; optical proximity correction)으로부터 발생하는 결합들과 같은)의 검출을 가능하게 한다. 대조적으로, 몇몇 현재의 검사 방법들은 테스트 이미지 및 하나 이상의 기준 이미지들 사이의 픽셀 대 픽셀 빅 방법을 이용한다. 하지만, 조직적 결합 크기와 유사한 상기 테스트 또는 기준 이미지에서의 랜덤 변화가 존재하면, 검사는 검사 시스템을 궁극적으로 제한할 방해 결합들에 의해서 암도당할 것이다. 이러한 방식으로, 종래의 검사에서 가능한 것보다 훨씬 더 작은 조직적 결합들이 암도적인 방해 결합 검출 레이트 없이도 본 명세서에 기술된 실시예들에서 검출될 수 있다. 예컨대, 본 명세서에 기술된 실시예들은 종래의 검사 시스템 또는 다이-대-데이터베이스 검사 시스템의 결합 민감도를 10nm 범위 이하로 확장하는데에 이용될 수 있다.

[0124] 상기한 웨이퍼 상의 결합들을 검출하기 위한 컴퓨터-구현 방법의 실시예들 각각은 본 명세서에 기술된 임의의 다른 방법(들)의 임의의 단계(들)를 포함할 수 있다. 추가로, 상기한 컴퓨터-구현 방법의 실시예들 각각은 본 명세서에 기술된 임의의 시스템들에 의해서 수행될 수 있다.

[0125] 본 발명의 다양한 양상들의 수정들 및 대안적 실시예들은 이러한 설명의 관점에서 당업자에게 명백할 수 있다. 예컨대, 다이 대 표준 기준 다이 검사에서의 이용을 위한 표준 기준 다이를 생성하기 위한 방법들 및 웨이퍼를 검사하기 위한 방법들이 제공된다. 따라서, 이러한 설명은 단지 예시적인 것으로서 그리고 당업자에 기술하기 위한 목적으로 본 발명을 실시하기 위한 일반적인 방식으로서 해석되어야 한다. 도시되고 기술된 본 발명의 형태들이 현재에 바람직한 실시예들로서 취해져야한다는 것이 이해되어야 한다. 요소들 및 물질들이 본 명세서에 기술되고 설명된 것들로 대체될 수 있고, 일부들 및 프로세스들이 역전될 수 있으며, 본 발명의 특정한 특징들이 독립적으로 이용될 수 있고, 본 발명의 이러한 기술의 이득을 가진 이후에 이러한 모든 것은 당업자에게 명백할 것이다. 후술하는 청구항들에서 기술되는 바와 같이 본 발명의 범위 및 사상을 벗어남이 없이 본 명세서에 기술된 요소들에서의 변화들이 만들어질 수 있다.

도면

도면1

도면2

도면3

도면4

## 도면5

## 도면6

## 도면7

## 도면8

도면9