(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4339719号

(P4339719)

(45) 発行日 平成21年10月7日(2009.10.7)

(24) 登録日 平成21年7月10日(2009.7.10)

(51) Int.Cl.

H04N 5/335 (2006.01)

F 1

H04N 5/335

P

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2004-47246 (P2004-47246)

(22) 出願日 平成16年2月24日 (2004.2.24)

(65) 公開番号 特開2005-244266 (P2005-244266A)

(43) 公開日 平成17年9月8日 (2005.9.8)

審査請求日 平成19年1月29日 (2007.1.29)

(73) 特許権者 000000376

オリンパス株式会社

東京都渋谷区幡ヶ谷2丁目43番2号

(74) 代理人 100087273

弁理士 最上 健治

(72) 発明者 町屋 悟

東京都渋谷区幡ヶ谷2丁目43番2号 オ

リンパス株式会社内

審査官 松田 岳士

最終頁に続く

(54) 【発明の名称】 映像信号処理回路及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像素子からの入力信号を受けてフィードスルーレベルとデータレベルとの差を出力しリセットノイズを除去する映像信号処理回路において、フィードスルーレベルとデータレベルの一方を極性を逆にサンプリングする第1の容量回路とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第2の容量回路とからなり、前記第1及び第2の容量回路の出力の差分を電荷状態で演算するように構成された第1の減算ブロックと、フィードスルーレベルとデータレベルの一方を極性を逆にサンプリングする第3の容量回路とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第4の容量回路とからなり、前記第3及び第4の容量回路の出力の差分を電荷状態で演算するよう構成された第2の減算ブロックとを撮像素子からの入力端子と差動増幅器の負入力端子との間に並列に接続し、前記差動増幅器の負入力端子と出力端子との間に並列に接続されたりセットスイッチと帰還容量を接続し、前記差動増幅器の正入力端子には第1の参照電圧を接続し、前記第1の減算ブロックと第2の減算ブロックとを交互に動作させて減算した電荷信号を前記差動増幅器で増幅して出力するように構成したことを特徴とする映像信号処理回路。

## 【請求項 2】

前記第1の減算ブロックの第1の容量回路は、第1の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第1の蓄積容量の他端を前記差動増幅器の負入力端子又は第1の参照電圧に接続するように構成し、前記第2の減算ブロックの第

3の容量回路は、第3の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第3の蓄積容量の他端を前記差動増幅器の負入力端子又は第1の参照電圧に接続するように構成したことを特徴とする請求項1に係る映像信号処理回路。

#### 【請求項3】

前記請求項2に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第1の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第1の蓄積容量の他端に前記第1の参照電圧を接続し、前記第3の蓄積容量の一端に前記第1の参照電圧を接続し、前記第3の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第1の蓄積容量の一端に前記第1の参照電圧を接続し、前記第1の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第3の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第3の蓄積容量の他端に前記第1の参照電圧を接続するように制御することを特徴とする映像信号処理回路の制御方法。10

#### 【請求項4】

前記第1の減算ブロックの第2の容量回路は、第2の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第2の蓄積容量の他端を第1の参照電圧に接続するように構成し、前記第2の減算ブロックの第4の容量回路は、第4の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第4の蓄積容量の他端を前記第1の参照電圧に接続するように構成したことを特徴とする請求項1に係る映像信号処理回路。20

#### 【請求項5】

前記請求項4に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第2の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第2の蓄積容量の他端に前記第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第4の蓄積容量の他端に前記第1の参照電圧を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第2の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第2の蓄積容量の他端に第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第4の蓄積容量の他端に第1の参照電圧を接続するように制御することを特徴とする映像信号処理回路の制御方法。30

#### 【請求項6】

前記第1及び第2の減算ブロックは、フィードスルーレベルとデータレベルのサンプリングの際には第2の参照電圧を、差分演算の際には前記第1の参照電圧を、前記第1乃至第4の容量回路の基準電圧として使用するように構成し、且つ前記第2の参照電圧をフィードスルーレベルとデータレベルとの間の値になるように設定したことを特徴とする請求項1に係る映像信号処理回路。40

#### 【請求項7】

前記第1の減算ブロックの第1の容量回路は、第1の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第1の蓄積容量の他端を前記差動増幅器の負入力端子又は前記第2の参照電圧に接続するように構成し、前記第2の減算ブロックの第3の容量回路は、第3の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第3の蓄積容量の他端を前記差動増幅器の負入力端子又は第2の参照電圧に接続するように構成したことを特徴とする請求項6に係る映像信号処理回路。

#### 【請求項8】

前記請求項7に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差50

分演算をする際には、前記第1の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第1の蓄積容量の他端に前記第2の参照電圧を接続し、前記第3の蓄積容量の一端に前記第1の参照電圧を接続し、前記第3の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第1の蓄積容量の一端に前記第1の参照電圧を接続し、前記第1の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第3の蓄積容量の一端に前記第2の参照電圧を接続するように制御することを特徴とする映像信号処理回路の制御方法。

## 【請求項9】

10

前記第1の減算ブロックの前記第2の容量回路は、第2の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第2の蓄積容量の他端を前記第1の参照電圧又は前記第2の参照電圧に接続するように構成し、前記第2の減算ブロックの前記第4の容量回路は、第4の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第4の蓄積容量の他端を前記第1の参照電圧又は前記第2の参照電圧に接続するように構成したことを特徴とする請求項6に係る映像信号処理回路。

## 【請求項10】

前記請求項9に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第2の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第2の蓄積容量の他端に前記第2の参照電圧を接続し、前記第4の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第4の蓄積容量の他端に前記第1の参照電圧を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第2の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第2の蓄積容量の他端に第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第4の蓄積容量の他端に第2の参照電圧を接続するように制御することを特徴とする映像信号処理回路の制御方法。

## 【請求項11】

20

前記帰還容量を可変容量にしたことを特徴とする請求項1，2，4，6，7及び9のいずれか1項に係る映像信号処理回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、撮像素子からの出力信号を処理する映像信号処理回路及びその制御方法に関する。

## 【背景技術】

## 【0002】

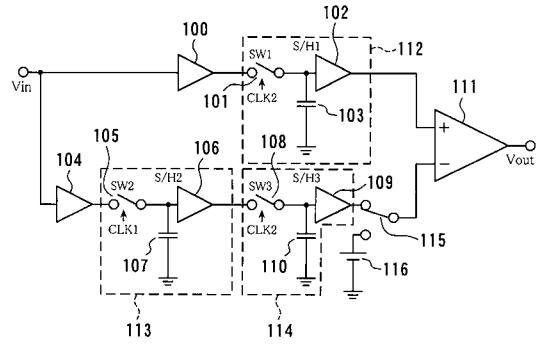

従来より、映像信号処理回路を使用して、固体撮像素子などの撮像素子からのアナログ画像出力信号中に含まれるリセットノイズなどの雑音を除去する方法が知られている。例えば、特開平2-154395号公報には、映像信号処理回路として図6に示すような構成のものが開示されている。この図6に示される映像信号処理回路は、第1のバッファ回路100と、第1のスイッチ101と第2のバッファ回路102と第1の蓄積容量103で構成される第1のサンプルホールド回路112と、第3のバッファ回路104と、第2のスイッチ105と第4のバッファ回路106と第2の蓄積容量107で構成される第2のサンプルホールド回路113と、第3のスイッチ108と第5のバッファ回路109と第3の蓄積容量110で構成される第3のサンプルホールド回路114と、選択スイッチ115と、参照電圧116と、差動増幅器111とで構成されている。

## 【0003】

40

50

そして、入力信号  $V_{in}$  は前記第 1 のバッファ回路 100 を経由して前記第 1 のサンプルホールド回路 112 に入力されると共に、前記第 3 のバッファ回路 104 を経由して前記第 2 のサンプルホールド回路 113 に入力されるように接続され、前記第 2 のサンプルホールド回路 113 の出力は、前記第 3 のサンプルホールド回路 114 に入力されるように接続されている。また、前記第 1 のサンプルホールド回路 112 の出力は、前記差動増幅器 111 の正入力に接続され、前記第 3 のサンプルホールド回路 114 の出力は、前記選択スイッチ 115 の一方の入力に接続されている。そして、前記選択スイッチ 115 の他方の入力には参照電圧 116 が接続され、前記選択スイッチ 115 の出力は前記差動増幅器 111 の負入力に接続され、前記選択スイッチ 115 は前記サンプルホールド回路 114 と参照電圧 116 を選択するように構成されている。

10

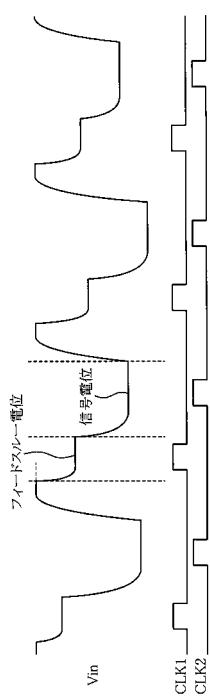

#### 【0004】

次に、このように構成されている映像信号処理回路の動作について、図 7 に示す信号波形図を使用して説明する。なお、参照電圧 116 については、映像信号処理回路としての動作には不要であるので、説明を割愛する。図 7 に示すように、フィードスルー期間では C L K 1 が H になり、第 2 のスイッチ 105 が ON して、第 2 の蓄積容量 107 にフィードスルー電位が蓄積される。次に、信号期間では C L K 2 が H になり、第 1 のスイッチ 101 と第 3 のスイッチ 108 が ON して、第 1 の蓄積容量 103 に信号電位が、第 3 の蓄積容量 110 には第 4 のバッファ回路 106 から出力されるフィードスルー電位が蓄積され、それぞれ差動増幅器 111 に入力されて、データ電位からフィードスルー電位を減算した信号が出力される。

20

#### 【特許文献 1】特開平 2 - 154395 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

ところで、図 6 に示した従来例においては、撮像素子からの入力信号  $V_{in}$  の値がそのままサンプルホールドされて差動増幅器 111 に入力されるので、入力信号  $V_{in}$  が差動増幅器 111 の入力 D レンジより大きい場合は、映像信号処理回路として機能しないという問題があった。

#### 【0006】

本発明は、従来提案されている映像信号処理回路における上記問題点を解消するためになされたもので、入力信号  $V_{in}$  が差動増幅器の入力 D レンジに制限されることがない映像信号処理回路及びその制御方法を提供することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0007】

上記問題点を解決するため、請求項 1 に係る発明は、撮像素子からの入力信号を受けてフィードスルーレベルとデータレベルとの差を出力しリセットノイズを除去する映像信号処理回路において、フィードスルーレベルとデータレベルの一方を極性を逆にサンプリングする第 1 の容量回路とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第 2 の容量回路とからなり、前記第 1 及び第 2 の容量回路の出力の差分を電荷状態で演算するように構成された第 1 の減算ブロックと、フィードスルーレベルとデータレベルの一方を極性を逆にサンプリングする第 3 の容量回路とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第 4 の容量回路とからなり、前記第 3 及び第 4 の容量回路の出力の差分を電荷状態で演算するように構成された第 2 の減算ブロックとを撮像素子からの入力端子と差動増幅器の負入力端子との間に並列に接続し、前記差動増幅器の負入力端子と出力端子との間に並列に接続されたりセットスイッチと帰還容量を接続し、前記差動増幅器の正入力端子には第 1 の参照電圧を接続し、前記第 1 の減算ブロックと第 2 の減算ブロックとを交互に動作させて減算した電荷信号を前記差動増幅器で増幅して増幅して出力するように構成したことを特徴とするものである。

40

#### 【0008】

請求項 2 に係る発明は、請求項 1 に係る映像信号処理回路において、前記第 1 の減算ブ

50

ロックの第1の容量回路は、第1の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第1の蓄積容量の他端を前記差動増幅器の負入力端子又は第1の参照電圧に接続するように構成し、前記第2の減算ブロックの第3の容量回路は、第3の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第3の蓄積容量の他端を前記差動増幅器の負入力端子又は第1の参照電圧に接続するように構成したことを特徴とするものである。

#### 【0009】

請求項3に係る発明は、請求項2に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第1の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第1の蓄積容量の他端に前記第1の参照電圧を接続し、前記第3の蓄積容量の一端に前記第1の参照電圧を接続し、前記第3の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第1の蓄積容量の一端に前記第1の参照電圧を接続し、前記第1の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第3の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第3の蓄積容量の他端に前記第1の参照電圧を接続するように制御することを特徴とするものである。

#### 【0010】

請求項4に係る発明は、請求項1に係る映像信号処理回路において、前記第1の減算ブロックの第2の容量回路は、第2の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第2の蓄積容量の他端を第1の参照電圧に接続するように構成し、前記第2の減算ブロックの第4の容量回路は、第4の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第4の蓄積容量の他端を前記第1の参照電圧に接続するように構成したことを特徴とするものである。

#### 【0011】

請求項5に係る発明は、請求項4に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第2の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第2の蓄積容量の他端に前記第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第4の蓄積容量の他端に前記第1の参照電圧を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第2の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第2の蓄積容量の他端に第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第4の蓄積容量の他端に第1の参照電圧を接続するように制御することを特徴とするものである。

#### 【0012】

請求項6に係る発明は、請求項1に係る映像信号処理回路において、前記第1及び第2の減算ブロックは、フィードスルーレベルとデータレベルのサンプリングの際には第2の参照電圧を、差分演算の際には前記第1の参照電圧を、前記第1乃至第4の容量回路の基準電圧として使用するように構成し、且つ前記第2の参照電圧をフィードスルーレベルとデータレベルとの間の値になるように設定したことを特徴とするものである。

#### 【0013】

請求項7に係る発明は、請求項6に係る映像信号処理回路において、前記第1の減算ブロックの第1の容量回路は、第1の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第1の蓄積容量の他端を前記差動増幅器の負入力端子又は前記第2の参照電圧に接続するように構成し、前記第2の減算ブロックの第3の容量回路は、第3の蓄積容量の一端を前記撮像素子からの入力端子又は前記第1の参照電圧に接続し、第3の蓄積容量の他端を前記差動増幅器の負入力端子又は第2の参照電圧に接続するよ

10

20

30

40

50

うに構成したことを特徴とするものである。

【0014】

請求項8に係る発明は、請求項7に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第1の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第1の蓄積容量の他端に前記第2の参照電圧を接続し、前記第3の蓄積容量の一端に前記第1の参照電圧を接続し、前記第3の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第1の蓄積容量の一端に前記第1の参照電圧を接続し、前記第1の蓄積容量の他端に前記差動増幅器の負入力端子を接続し、前記第3の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第3の蓄積容量の他端に前記第2の参照電圧を接続するように制御することを特徴とするものである。

10

【0015】

請求項9に係る発明は、請求項6に係る映像信号処理回路において、前記第1の減算ブロックの前記第2の容量回路は、第2の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第2の蓄積容量の他端を前記第1の参照電圧又は前記第2の参照電圧に接続するように構成し、前記第2の減算ブロックの前記第4の容量回路は、第4の蓄積容量の一端を前記撮像素子からの入力端子又は前記差動増幅器の負入力端子に接続し、第4の蓄積容量の他端を前記第1の参照電圧又は前記第2の参照電圧に接続するように構成したことを特徴とするものである。

20

【0016】

請求項10に係る発明は、請求項9に係る映像信号処理回路の制御方法において、前記第1の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングし、前記第2の減算ブロックが差分演算をする際には、前記第2の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第2の蓄積容量の他端に前記第2の参照電圧を接続し、前記第4の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第4の蓄積容量の他端に前記第1の参照電圧を接続し、前記第1の減算ブロックが差分演算を行い、前記第2の減算ブロックがフィードスルーレベル及びデータレベルをサンプリングをする際には、前記第2の蓄積容量の一端に前記差動増幅器の負入力端子を接続し、前記第2の蓄積容量の他端に第1の参照電圧を接続し、前記第4の蓄積容量の一端に前記撮像素子からの入力端子を接続し、前記第4の蓄積容量の他端に第2の参照電圧を接続するように制御することを特徴とするものである。

30

【0017】

請求項11に係る発明は1，2，4，6，7及び9のいずれか1項に係る映像信号処理回路において、前記帰還容量を可変容量にしたことを特徴とするものである。

【発明の効果】

【0018】

請求項1，2及び4に係る発明によれば、電荷状態で減算されたデータ成分のみが差動増幅器へ入力されるので、入力信号V<sub>in</sub>のDレンジを第1，第2，第3，第4の各容量回路が動作する範囲まで広げることが可能となる。また請求項3及び5に係る発明によれば、入力信号のDレンジを各容量回路が動作する範囲まで広げることが可能な映像信号処理回路の制御方法を実現することができる。また請求項6，7及び9に係る発明によれば、請求項1に係る発明の効果に加えて、フィードスルーレベルとデータレベルをサンプリングする際に、蓄積容量に加わる電位差を小さくすることができるので、サンプリング時間を短くすることができ、動作周波数の高速化を図ることができる。また請求項8及び10に係る発明によれば、入力信号のDレンジを各容量回路が動作する範囲まで広げることが可能で、サンプリング時間を短縮し動作周波数の高速化を図ることができるとされる映像信号処理回路の制御方法を実現することができる。また請求項11に係る発明によれば、請求項1及び6に係る発明の効果に加えて、ゲインを自由に設定することができるので、PGA回路の

40

50

役割をかねることができ、回路規模の縮小化を図ることができる。

**【発明を実施するための最良の形態】**

**【0019】**

次に、発明を実施するための最良の形態について説明する。

**【実施例】**

**【0020】**

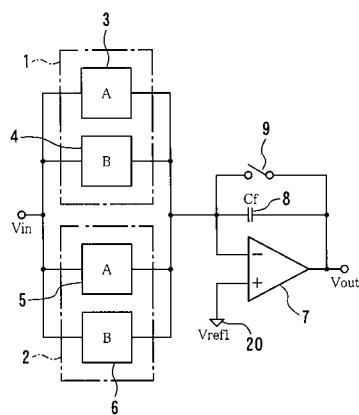

図1は、本発明に係る映像信号処理回路の実施例1の構成を示す概略ブロック図であり、この実施例は請求項1に係る映像信号処理回路に対応している。図1に示す映像信号処理回路は、フィードスルーレベルとデータレベルの一方の極性を逆にサンプリングする第1の容量回路3とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第2の容量回路4とからなり、第1及び第2の容量回路3, 4の出力の差分を電荷状態で演算するように構成された第1の減算ブロック1と、フィードスルーレベルとデータレベルの一方の極性を逆にサンプリングする第3の容量回路5とフィードスルーレベルとデータレベルの他方をそのままサンプリングする第4の容量回路6とからなり、第3及び第4の容量回路5, 6の出力の差分を電荷状態で演算するように構成された第2の減算ブロック2とを、撮像素子(図示せず)からの入力端子と差動増幅器7の負入力端子との間に並列に接続している。そして、前記差動増幅器7の負入力端子と出力端子との間に並列に接続されたリセットスイッチ9と帰還容量(Cf)8を接続し、前記差動増幅器7の正入力端子には第1の参照電圧(Vref1)20を接続し、前記第1及び第2の減算ブロック1, 2を交互に動作させて、減算した電荷信号を前記差動増幅器7で増幅して出力するように構成されている。

10

**【0021】**

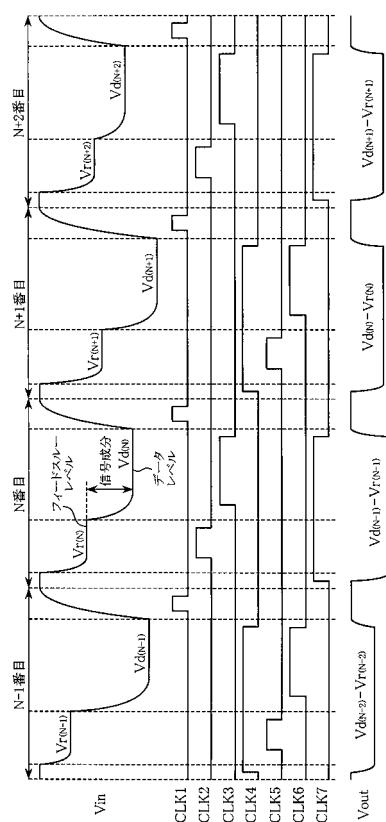

次に、図1に示した映像信号処理回路の動作を、図4の信号波形図の一部を用いて説明する。まず、上記のように構成された映像信号処理回路には、図4に示すような入力信号Vinが入力される。N番目の入力を例に説明し、フィードスルーレベルは第1及び第3の容量回路3, 5でサンプリングするものとする。N番目の入力のときは、第1の減算回路1が入力信号Vinをサンプリングすると、まず、N-1番目からN番目への切り替わりの際に、リセットスイッチ9がONして、帰還容量8を初期化(電荷Q=0)する。そして、フィードスルーレベルは第1の容量回路3にサンプリングされる。このとき、第1の容量回路3に電荷Q<sub>1(N)</sub>が保持される。次に、データレベルは第2の容量回路4にサンプリングされ、このとき、第2の容量回路4に電荷Q<sub>2(N)</sub>が保持される。また、フィードスルーレベル及びデータレベルに対応する電荷Q<sub>1(N)</sub>, Q<sub>2(N)</sub>をサンプリングしている間、N-1番目に第3の容量回路5で保持したフィードスルーレベルに対応する電荷Q<sub>1(N-1)</sub>と第4の容量回路6で保持したデータレベルに対応する電荷Q<sub>2(N-1)</sub>とで、差分演算が行われており、フィードスルーレベルに対応する電荷Q<sub>1(N-1)</sub>は極性が反転して出力されるので、Q<sub>2(N-1)</sub>-Q<sub>1(N-1)</sub>なる電荷が帰還容量(Cf)8に流れることになる。帰還容量(Cf)8の初期電荷は、リセットスイッチ9によりQ=0となっているので、

30

$$Q_{2(N-1)} - Q_{1(N-1)} = Cf (V_{out(N)} - V_{ref1}) \quad \dots \dots \dots \quad (1)$$

となり、出力V<sub>out(N)</sub>は、

$$V_{out(N)} = (Q_{2(N-1)} - Q_{1(N-1)}) / Cf + V_{ref1} \quad \dots \dots \dots \quad (2)$$

のようになり、電荷状態でフィードスルーレベルとデータレベルが差分演算された後、増幅されて出力されることとなる。

**【0022】**

N番目で信号のサンプリングとN-1番目の差分演算をした後は、再びリセットスイッチ9をONして帰還容量8をリセットする。そして、N+1番目では、今度は第3の容量回路5でフィードスルーレベルをサンプリングし、Q<sub>1(N+1)</sub>なる電荷を保持し、第4の容量回路6でデータレベルをサンプリングし、Q<sub>2(N+1)</sub>なる電荷を保持する。そして、第3, 第4の容量回路5, 6でサンプリングしている間、今度はN番目にサンプリングした電荷を差分演算することになり、このときの出力はN番目のときと同様に、

50

$V_{out(N+1)} = (Q_2(N) - Q_1(N)) / C_f + V_{ref1} \dots \dots \dots \quad (3)$

となる。

### 【0023】

図1に示した実施例1に係る映像信号処理回路は、上述したように動作することで、フィードスルーレベルとデータレベルの差分を取ることができる。そして、電荷状態で減算した結果が差動増幅器7に入力されるので、入力信号VinのDレンジを第1，第2，第3，第4の容量回路3，4，5，6が動作できる範囲まで広げることが可能となるという利点が得られる。なお、この実施例では、第1及び第3の容量回路3，5でフィードスルーレベルをサンプリングする場合を説明したが、第2及び第4の容量回路4，6でフィードスルーレベルをサンプリングする場合でも同様の効果を得ることができる。この場合は、10 第2及び第4の容量回路4，6にQ2としてフィードスルーレベル、第1及び第3の容量回路3，5にQ1としてデータレベルがサンプリングされることになり、第1及び第3の容量回路3，5でフィードスルーレベルをサンプリングする場合とは、極性が逆になることになる。

### 【0024】

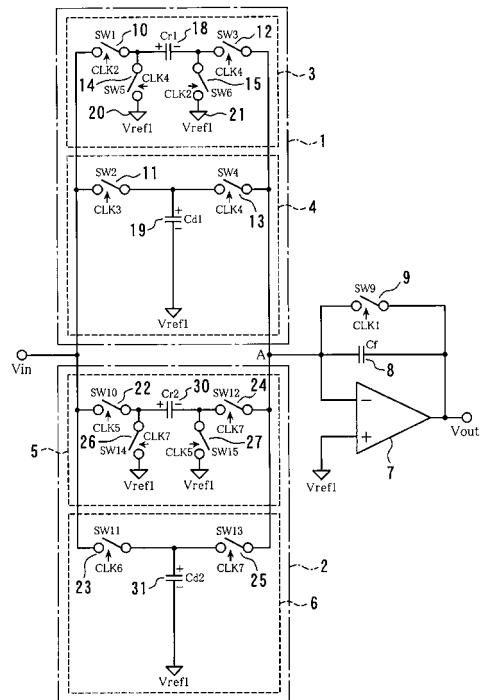

図2は、本発明の実施例2を示す回路構成図であり、この実施例2は請求項2乃至5に係る映像信号処理回路に対応している。本実施例は、図1に示した実施例1に係る映像信号処理回路における第1～第4の容量回路の具体的構成を示すものであり、図1に示した実施例1と同一あるいは対応する構成要素には同一符号を付して示している。この実施例においては、第1の減算ブロック1の第1の容量回路3は、第1の蓄積容量(Cr1)18の一端を第1のスイッチ(SW1)10を経由して撮像素子からの入力端子に接続すると共に、第5のスイッチ(SW5)14を経由して前記第1の参照電圧(Vref1)20に接続し、第1の蓄積容量18の他端を第3のスイッチ(SW3)12を経由して前記差動増幅器7の負入力端子(共通接続点A)に接続すると共に、第6のスイッチ(SW6)15を経由して第1の参照電圧20に接続されるように構成されている。前記第1の減算ブロック1の第2の容量回路4は、第2の蓄積容量(Cd1)19の一端を第2のスイッチ(SW2)11を経由して前記撮像素子からの入力端子に接続すると共に、第4のスイッチ(SW4)13を経由して前記差動増幅器7の負入力端子に接続し、第2の蓄積容量19の他端を第1の参照電圧20に接続するように構成している。20

### 【0025】

また、第2の減算ブロック2の第3の容量回路5は、第3の蓄積容量(Cr2)30の一端を第10のスイッチ(SW10)22を経由して前記撮像素子からの入力端子に接続すると共に、第14のスイッチ(SW14)26を経由して前記第1の参照電圧20に接続し、第3の蓄積容量30の他端を第12のスイッチ(SW12)24を経由して前記差動増幅器7の負入力端子に接続すると共に、第15のスイッチ(SW15)27を経由して第1の参照電圧20に接続されるように構成している。前記第2の減算ブロック2の第4の容量回路6は、第4の蓄積容量(Cd2)31の一端を第11のスイッチ(SW11)23を経由して前記撮像素子からの入力端子に接続すると共に、第13のスイッチ(SW13)25を経由して前記差動増幅器7の負入力端子に接続し、第4の蓄積容量31の他端を前記第1の参照電圧20に接続するように構成している。30

### 【0026】

次に、図2に示した実施例2の動作を、図4の信号波形図に基づいて説明する。図2に示した実施例2に係る映像信号処理回路には、図4に示すような入力信号Vinが入力される。そして、クロック信号CLK1は第9のスイッチ9を、クロック信号CLK2は第1及び第6のスイッチ10,15を、クロック信号CLK3は第2のスイッチ11を、クロック信号CLK4は第3,第4及び第5のスイッチ12,13,14を、クロック信号CLK5は第10及び第15のスイッチ22,27を、クロック信号CLK6は第11のスイッチ23を、クロック信号CLK7は第12,第13及び第14のスイッチ24,25,26をそれぞれ制御し、各クロック信号CLKがHのときに各スイッチはONするものとする。なお、各クロック信号CLKは図示しない制御部より送出されるようになっている。40

## 【0027】

実施例1と同じように、N番目の入力を例に説明し、フィードスルーレベルは第1及び第3の容量回路3, 5でサンプリングするものとする。N-1番目のデータレベルが終った直後にCLK1がHになり、第9のスイッチ9がONする。これにより、差動増幅器7はボルテージフォロアとして動作するので、帰還容量8の両端は同電位となり、電荷がリセットされる。そして、N番目のフィードスルーレベル $V_{r(N)}$ は、CLK2がHとなり、第1及び第6のスイッチ10, 15がONして、第1の蓄積容量(Cr1)18にサンプリングされる。このとき、保持している電荷 $Q_{1(N)}$ は、

$$Q_{1(N)} = (V_{r(N)} - V_{ref1}) Cr1 \quad \dots \dots \dots \dots \quad (4)$$

となる。

10

## 【0028】

次に、データレベル $Vd(N)$ は、CLK3がHとなり、第2のスイッチ11がONして、第2の蓄積容量(Cd1)19にサンプリングされる。このとき、保持している電荷 $Q_{2(N)}$ は、

$$Q_{2(N)} = (Vd(N) - V_{ref1}) Cd1 \quad \dots \dots \dots \dots \quad (5)$$

となる。また、フィードスルーレベル及びデータレベルに対応する電荷 $Q_{1(N)}$ ,  $Q_{2(N)}$ をサンプリングしている間、CLK7がHとなり、第12, 第13及び第14のスイッチ24, 25, 26がONする。A点(差動増幅器7の負入力端子)の電位は、差動増幅器7の仮想接地により $V_{ref1}$ であるので、第3及び第4の蓄積容量(Cr2, Cd2)30, 31の両端の電位が等しくなり、保持していた電荷は全てA点を経由して帰還容量8に流れ込むことになる。このとき、A点には第3の蓄積容量(Cr2)30の他端と第4の蓄積容量(Cd2)31の一端が接続されているので、第3の蓄積容量(Cr2)30が保持していた $Q_{1(N-1)}$ のみ極性が反転されて出力されることになる。よって、帰還容量(Cf)8には、 $Q_{2(N-1)} - Q_{1(N-1)}$ なる電荷が流れ込むことになる。 $Q_{1(N-1)}$ ,  $Q_{2(N-1)}$ は式(4), (5)と同様に、

$$Q_{1(N-1)} = (V_{r(N-1)} - V_{ref1}) Cr2 \quad \dots \dots \dots \dots \quad (6)$$

$$Q_{2(N-1)} = (Vd(N-1) - V_{ref1}) Cd2 \quad \dots \dots \dots \dots \quad (7)$$

となる。ここで、 $Cr2 = Cd2 = Cs$ として、式(6), (7)を式(2)に代入すると、

$$V_{out(N)} = (Q_{2(N-1)} - Q_{1(N-1)}) / Cf + V_{ref1}$$

$$= Cs / Cf \cdot (Vd(N-1) - V_{r(N-1)}) + V_{ref1} \quad \dots \dots \quad (8)$$

30

となり、データレベルとフィードスルーレベルの差分を増幅した値が出力される。

## 【0029】

その後、再びCLK1がHになり第9のスイッチ9をリセットした後、N+1番目では先のN番目とは逆に、N+1番目のフィードスルーレベル $V_{r(N+1)}$ は、CLK5がHとなり、第10及び第15のスイッチ22, 27がONして、第3の蓄積容量(Cr2)30にサンプリングされる。このとき、保持している電荷 $Q_{1(N+1)}$ は、

$$Q_{1(N+1)} = (V_{r(N+1)} - V_{ref1}) Cr2 \quad \dots \dots \dots \dots \quad (9)$$

となる。次に、データレベル $Vd(N+1)$ は、CLK6がHとなり、第11のスイッチ23がONして、第4の蓄積容量(Cd2)31にサンプリングされる。このとき、保持している電荷 $Q_{2(N+1)}$ は、

$$Q_{2(N+1)} = (Vd(N+1) - V_{ref1}) Cd2 \quad \dots \dots \dots \dots \quad (10)$$

40

となる。

## 【0030】

また、第3及び第4の蓄積容量30, 31でフィードスルーレベル及びデータレベルに対応する電荷 $Q_{1(N+1)}$ ,  $Q_{2(N+1)}$ をサンプリングしている間、CLK4がHとなり、第3, 第4及び第5のスイッチ12, 13, 14がONする。N番目のときと同様に、A点の電位は差動増幅器7の仮想接地により $V_{ref1}$ であるので、第1及び第2の蓄積容量(Cr1, Cd1)18, 19の両端の電位が等しくなり、保持していた電荷は全てA点を経由して帰還容量(Cf)8に流れ込むことになる。このとき、A点には第1の蓄積容量(Cr1)18の他端と第2の蓄積容量(Cd1)19の一端が接続されているので、第1の蓄積容量(Cr1)18が保

50

持していた  $Q_{1(N)}$  のみ極性が反転されて出力されることになる。よって、帰還容量 ( $C_f$ ) 8 には、 $Q_{2(N)} - Q_{1(N)}$  なる電荷が流れ込むことになる。ここで、 $C_{r2} = C_{d2} = C_s$  として、式(4), (5)を式(3)に代入すると

$$\begin{aligned} V_{out(N+1)} &= (Q_{2(N)} - Q_{1(N)}) / C_f + V_{ref1} \\ &= C_s / C_f \cdot (V_{d(N)} - V_{r(N)}) + V_{ref1} \dots \dots \dots (11) \end{aligned}$$

となり、データレベルとフィードスルーレベルの差分を増幅した値が出力される。

#### 【0031】

このように、本実施例に係る映像信号処理回路も、実施例1と同様に電荷状態で減算した結果を差動増幅器7に入力するようにしたことで、入力信号  $V_{in}$  のDレンジを第1, 第2, 第3及び第4の容量回路3, 4, 5, 6が動作できる範囲、つまり各スイッチが動作する範囲まで広げることが可能となる。なお、本実施例の説明では、第1及び第3の容量回路3, 5でフィードスルーレベルをサンプリングする場合を説明したが、第2及び第4の容量回路4, 6でフィードスルーレベルをサンプリングする場合では、式(8), (11)は、

$$V_{out(N)} = -C_s / C_f \cdot (V_{d(N-1)} - V_{r(N-1)}) + V_{ref1} \dots \dots (12)$$

$$V_{out(N+1)} = -C_s / C_f \cdot (V_{d(N)} - V_{r(N)}) + V_{ref1} \dots \dots (13)$$

となり、極性が変わるだけでその効果に変わりがないことがわかる。

#### 【0032】

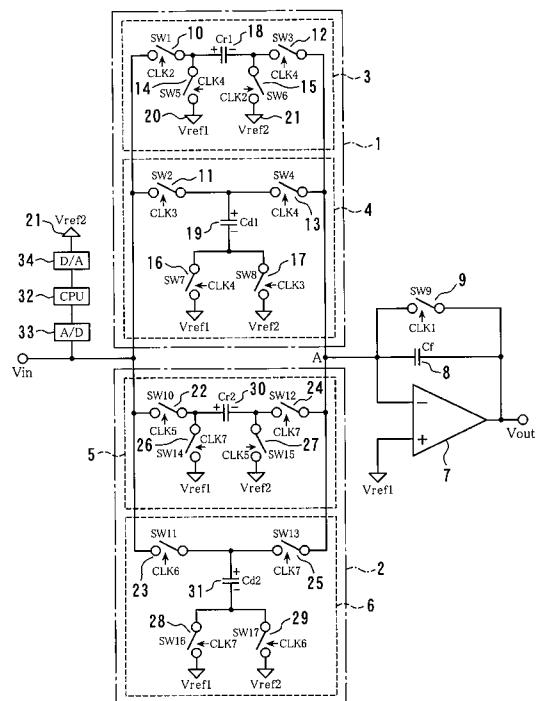

図3は、本発明の実施例3を示す回路構成図であり、図2に示した実施例2に係る映像信号処理回路と同一又は対応する構成要素には同一符号を付して示している。本実施例は、請求項6乃至10に係る映像信号処理回路に対応している。本実施例の特徴は、図2に示した実施例2の映像信号処理回路における前記第1の蓄積容量 ( $C_{r1}$ ) 18の他端を第3のスイッチ12を経由して前記差動増幅器7の負入力端子に接続すると共に、第6のスイッチ15を経由して第2の参照電圧 ( $V_{ref2}$ ) 21に接続されるように構成し、また前記第2の蓄積容量 ( $C_{d1}$ ) 19の他端を第7のスイッチ( $SW_7$ )16を経由して前記第1の参照電圧 ( $V_{ref1}$ ) 20に接続すると共に、第8のスイッチ( $SW_8$ )17を経由して前記第2の参照電圧 ( $V_{ref2}$ ) 21に接続するように構成している点である。更に、同様に前記第3の蓄積容量 ( $C_{r2}$ ) 30の他端を第12のスイッチ24を経由して前記差動増幅器7の負入力端子に接続すると共に、第15のスイッチ27を経由して第2の参照電圧 ( $V_{ref2}$ ) 21に接続されるよう構成し、また前記第4の蓄積容量 ( $C_{d2}$ ) 31の他端を第16のスイッチ( $SW_{16}$ )28を経由して前記第1の参照電圧 ( $V_{ref1}$ ) 20に接続すると共に、第17のスイッチ( $SW_{17}$ )29を経由して前記第2の参照電圧 ( $V_{ref2}$ ) 21に接続するように構成し、且つ前記第2の参照電圧 ( $V_{ref2}$ ) 21がフィードスルーレベルとデータレベルとの間の値になるように設定されている。

#### 【0033】

次に、図3に示した実施例3の動作を同じく図4の信号波形図を参照しながら説明する。なお、実施例2と同じ動作をする素子の動作説明は省略する。第7のスイッチ16はCLK4で、第8のスイッチ17はCLK3で、第16のスイッチ28はCLK7で、第17のスイッチ29はCLK6でそれぞれ制御され、CLKがHのときにONするものとする。実施例2と同じように、N番目の入力を例に説明し、フィードスルーレベルは第1及び第3の容量回路3, 5でサンプリングするものとする。

#### 【0034】

本実施例では、フィードスルーレベル  $V_{r(N)}$  をサンプリングする際は、第1のスイッチ10と第6のスイッチ15がONするので、第1の蓄積容量 ( $C_{r1}$ ) 18に保持される電荷  $Q_{1(N)}$  は、

$$Q_{1(N)} = (V_{r(N)} - V_{ref2}) C_{r1} \dots \dots \dots \dots \dots \dots \dots (14)$$

となり、データレベル  $V_{d(N)}$  をサンプリングする際は、第2のスイッチ11と第8のスイッチ17がONするので、第2の蓄積容量 ( $C_{d1}$ ) 19に保持される電荷  $Q_{2(N)}$  は、

$$Q_{2(N)} = (V_{d(N)} - V_{ref2}) C_{d1} \dots \dots \dots \dots \dots \dots \dots (15)$$

となる。フィードスルーレベル及びデータレベルに対応する電荷  $Q_{1(N)}$ ,  $Q_{2(N)}$  をサ

10

20

30

40

50

ンプリングしている間、C L K 7がHとなり、第12，第13，第14及び第16のスイッチ24，25，26，28がONする。A点の電位は差動増幅器7の仮想接地によりV ref1であるので、第3及び第4の蓄積容量(C r2，C d2)30，31の両端の電位が等しくなり、保持していた電荷は全てA点を経由して帰還容量(C f)8に流れ込むことになる。このとき、A点には第3の蓄積容量30の他端と第4の蓄積容量31の一端が接続されているので、第3の蓄積容量30に保持していた電荷Q<sub>1(N-1)</sub>のみ極性が反転されて出力されることになる。よって、帰還容量8には、Q<sub>2(N-1)</sub>-Q<sub>1(N-1)</sub>なる電荷が流れ込むことになる。Q<sub>1(N-1)</sub>，Q<sub>2(N-1)</sub>は式(14)，(15)と同様に、

$$Q_{1(N-1)} = (V_{r(N-1)} - V_{ref2}) C r2 \quad \dots \dots \dots \dots \dots \dots \quad (16)$$

$$Q_{2(N-1)} = (V_{d(N-1)} - V_{ref2}) C d2 \quad \dots \dots \dots \dots \dots \dots \quad (17)$$

となる。ここで、C r2=C d2=C sとして、式(16)，(17)を式(2)に代入すると、

$$V_{out(N)} = (Q_{2(N-1)} - Q_{1(N-1)}) / C f + V_{ref1}$$

$$= C s / C f \cdot (V_{d(N-1)} - V_{r(N-1)}) + V_{ref1} \quad \dots \dots \dots \quad (18)$$

となり、データレベルとフィードスルーレベルの差分を増幅した値が出力される。

### 【0035】

その後、再びC L K 1がHになり、第9のスイッチ9をリセットした後、N+1番目では先のN番目とは逆にN+1番目のフィードスルーレベルV<sub>r(N+1)</sub>は、C L K 5がHとなり、第10及び第15のスイッチ22，27がONして、第3の蓄積容量(C r2)30にサンプリングされる。このとき、保持している電荷Q<sub>1(N+1)</sub>は、

$$Q_{1(N+1)} = (V_{r(N+1)} - V_{ref2}) C r2 \quad \dots \dots \dots \dots \dots \dots \quad (19)$$

となる。

### 【0036】

次に、データレベルV<sub>d(N+1)</sub>は、C L K 6がHとなり、第11及び第17のスイッチ23，29がONして、第4の蓄積容量(C d2)31にサンプリングされる。このとき、保持している電荷Q<sub>2(N+1)</sub>は、

$$Q_{2(N+1)} = (V_{d(N+1)} - V_{ref2}) C d2 \quad \dots \dots \dots \dots \dots \dots \quad (20)$$

となる。また、フィードスルーレベル及びデータレベルに対応する電荷Q<sub>1(N+1)</sub>，Q<sub>2(N+1)</sub>をサンプリングしている間、C L K 4がHとなり、第3，第4，第5及び第7のスイッチ12，13，14，16がONする。N番目のときと同様に、A点の電位は差動増幅器7の仮想接地によりV ref1であるので、第1及び第2の蓄積容量18，19の両端の電位が等しくなり、保持していた電荷は全てA点を経由して帰還容量(C f)8に流れ込むことになる。このとき、A点には第1の蓄積容量18の他端と第2の蓄積容量19の一端が接続されているので、第1の蓄積容量18に保持されていた電荷Q<sub>1(N)</sub>のみ極性が反転されて出力されることになる。よって、帰還容量8には、Q<sub>2(N)</sub>-Q<sub>1(N)</sub>なる電荷が流れ込むことになる。ここで、C r1=C d1=C sとして、式(14)，(15)を式(3)に代入すると

$$V_{out(N+1)} = C s / C f \cdot (V_{d(N)} - V_{r(N)}) + V_{ref1} \quad \dots \dots \dots \quad (21)$$

となり、データレベルとフィードスルーレベルの差分を増幅した値が出力される。

### 【0037】

本実施例でも、式(18)，(21)に示したように、実施例2と同様の効果を得ることができる。また、本実施例では、それに加えて図3に示すように、撮像素子からの入力信号V<sub>in</sub>をA/Dコンバータ33によりデジタル値に変換した信号をC P U32で演算し、フィードスルーレベルの最小値とデータレベルの最大値をC P U32で算出し、参照電圧が、算出した2つの間になるようにC P U32で制御し、D/Aコンバータ34でアナログ値の参照電圧を生成し、これを第2の参照電圧(V<sub>ref2</sub>)21として用いるように構成している。これにより、サンプリングする際に蓄積容量の両端の電位差が小さくて済み、サンプリング時間を短くすることができるので、動作周波数を高速化できるという効果が得られる。この図3に示した実施例では、C P U32でフィードスルーレベルの最小値とデータレベルの最大値を算出し、第2の参照電圧を設定するようにしたものを見たが、フィードスルーレベルの平均値とデータレベルの平均値をそれぞれ算出して第2の参照電圧21を制御するなどの手法を用いてもよいし、他の手段として、C P Uではなくサンプルホールド回路など

10

20

30

40

50

を使用して設定するようにしても、同様の効果を得ることができる。

#### 【0038】

なお、図3に示した実施例3の説明では、第1及び第3の容量回路3, 5でフィードスルーレベルをサンプリングする場合を説明したが、第2及び第4の容量回路4, 6でフィードスルーレベルをサンプリングする場合では、式(18), (21)は、

$$V_{out(N)} = -Cs / Cf \cdot (Vd_{(N-1)} - Vr_{(N-1)}) + V_{ref1} \dots (22)$$

$$V_{out(N+1)} = -Cs / Cf \cdot (Vd_N - Vr_N) + V_{ref1} \dots (23)$$

となり、極性が変わるだけでその効果に変わりがないことがわかる。

#### 【0039】

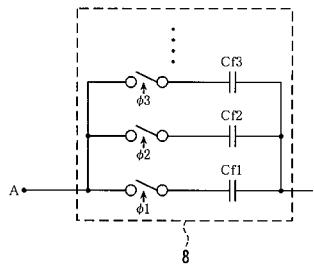

図5は、本発明の実施例4の特徴部を示す回路構成図であり、本実施例は請求項11に係る映像信号処理回路に対応している。本実施例の特徴は、先に示した実施例1～3に係る映像信号処理回路において、前記帰還容量8を可変できるように、複数の容量素子Cf1, Cf2, Cf3と、それに対応するスイッチ8a, 8b, 8cとで構成したものである。10

#### 【0040】

次に、図5に示したこの実施例の動作について説明する。前述のように、本実施例は、帰還容量8を構成する3つの容量素子Cf1, Cf2, Cf3を、信号1, 2, 3によるスイッチ8a, 8b, 8cのON, OFF制御により、帰還容量として使用するかどうか切り換えることができるようになっており、この実施例では信号1, 2, 3がHのときにスイッチがONするものとする。例えば、信号1のみがHのときは帰還容量として容量素子Cf1が使用され、信号2と3がHのときは、帰還容量として2つの容量素子Cf2とCf3とが帰還容量として使用されることとなる。これにより、式(2), (3), (8), (11), (12), (13), (18), (21), (22), (23)のCfの値を自由に変えることができるので、ゲインを自由に設定することができる。一般的に、撮像素子からの信号を処理する映像信号処理回路の次段には、ゲインを調整するPGA回路(プログラマブル・ゲイン・アンプ)が接続されるが、本実施例の映像信号処理回路ではゲインを自由に変えることができるので、PGA回路の役割を兼ねることができ、回路規模の縮小化を図ることができるという効果が得られる。20

#### 【0041】

なお、図5に示した実施例では、可変選択する容量素子が3つの例を示したが、容量素子の数には制限はなく、より多くの容量素子を並列に接続して使用するかどうかを制御し、ゲイン調整を行うこともできることは言うまでもない。30

#### 【図面の簡単な説明】

#### 【0042】

【図1】本発明に係る映像信号処理回路の実施例1の構成を示す概略ブロック図である。

【図2】本発明に係る映像信号処理回路の実施例2の構成を示す回路構成図である。

【図3】本発明に係る映像信号処理回路の実施例3の構成を示す回路構成図である。

【図4】図2及び図3に示した実施例2及び3の動作を説明するための信号波形図である。

【図5】本発明に係る映像信号処理回路の実施例4の特徴部の構成を示す回路構成図である。40

【図6】従来の映像信号処理回路の一例を示すブロック構成図である。

【図7】図6に示す従来の映像信号処理回路の動作を説明するための信号波形図である。

#### 【符号の説明】

#### 【0043】

- 1 第1の減算ブロック

- 2 第2の減算ブロック

- 3 入力の極性を反転させる第1の容量回路

- 4 入力の極性を反転させない第2の容量回路

- 5 入力の極性を反転させる第3の容量回路

- 6 入力の極性を反転させない第4の容量回路

50

|     |                 |    |

|-----|-----------------|----|

| 7   | 差動増幅器           |    |

| 8   | 帰還容量            |    |

| 9   | リセットスイッチ        |    |

| 10  | 第1のスイッチ         |    |

| 11  | 第2のスイッチ         |    |

| 12  | 第3のスイッチ         |    |

| 13  | 第4のスイッチ         |    |

| 14  | 第5のスイッチ         |    |

| 15  | 第6のスイッチ         |    |

| 16  | 第7のスイッチ         | 10 |

| 17  | 第8のスイッチ         |    |

| 18  | 第1の蓄積容量         |    |

| 19  | 第2の蓄積容量         |    |

| 20  | 第1の参照電圧         |    |

| 21  | 第2の参照電圧         |    |

| 22  | 第10のスイッチ        |    |

| 23  | 第11のスイッチ        |    |

| 24  | 第12のスイッチ        |    |

| 25  | 第13のスイッチ        |    |

| 26  | 第14のスイッチ        | 20 |

| 27  | 第15のスイッチ        |    |

| 28  | 第16のスイッチ        |    |

| 29  | 第17のスイッチ        |    |

| 30  | 第3の蓄積容量         |    |

| 31  | 第4の蓄積容量         |    |

| 32  | 第2の参照電圧を制御するCPU |    |

| 33  | A/Dコンバータ        |    |

| 34  | D/Aコンバータ        |    |

| 100 | 第1のバッファ回路       |    |

| 101 | 第1のスイッチ         | 30 |

| 102 | 第2のバッファ回路       |    |

| 103 | 第1の蓄積容量         |    |

| 104 | 第3のバッファ回路       |    |

| 105 | 第2のスイッチ         |    |

| 106 | 第4のバッファ回路       |    |

| 107 | 第2の蓄積容量         |    |

| 108 | 第3のスイッチ         |    |

| 109 | 第5のバッファ回路       |    |

| 110 | 第3の蓄積容量         |    |

| 111 | 差動増幅器           | 40 |

| 112 | 第1のサンプルホールド回路   |    |

| 113 | 第2のサンプルホールド回路   |    |

| 114 | 第3のサンプルホールド回路   |    |

| 115 | 選択スイッチ          |    |

| 116 | 参照電圧            |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

---

フロントページの続き

(56)参考文献 特開2003-289477(JP,A)

特開2003-163843(JP,A)

特開平09-298690(JP,A)

特開2002-043941(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/335