(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6306282号

(P6306282)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

|             |                |                  |             |                |             |

|-------------|----------------|------------------|-------------|----------------|-------------|

| <b>H03K</b> | <b>19/0185</b> | <b>(2006.01)</b> | <b>H03K</b> | <b>19/0185</b> | <b>230</b>  |

| <b>H01L</b> | <b>27/088</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/088</b>  | <b>331E</b> |

| <b>H01L</b> | <b>21/8238</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>27/092</b>  | <b>L</b>    |

| <b>H01L</b> | <b>27/092</b>  | <b>(2006.01)</b> | <b>H01L</b> | <b>27/088</b>  | <b>E</b>    |

| <b>H01L</b> | <b>21/8234</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>   | <b>618B</b> |

請求項の数 3 (全 40 頁) 最終頁に続く

(21) 出願番号

特願2012-275285 (P2012-275285)

(22) 出願日

平成24年12月18日(2012.12.18)

(65) 公開番号

特開2013-150313 (P2013-150313A)

(43) 公開日

平成25年8月1日(2013.8.1)

審査請求日

平成27年12月15日(2015.12.15)

(31) 優先権主張番号

特願2011-282510 (P2011-282510)

(32) 優先日

平成23年12月23日(2011.12.23)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 大嶋 和晃

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 白井 亮

前置審査

最終頁に続く

(54) 【発明の名称】 レベルシフト回路及び半導体集積回路

(57) 【特許請求の範囲】

【請求項 1】

トランジスタと、インバータ回路と、を有し、

前記トランジスタは、ドレイン及び第1のゲートに第1の電源電位が印加され、

前記トランジスタは、第2のゲートに第2の電源電位が印加されしきい値電圧が制御され、

前記インバータ回路は、第1の信号が入力され、第2の信号を出力し、

前記インバータ回路は、電源電圧として、前記第1の電源電位から前記制御されたしきい値電圧を減算した電位と、第3の電源電位とが印加され、

前記トランジスタのチャネル形成領域は、酸化物半導体を有し、

前記インバータ回路が有するトランジスタのチャネル形成領域は、シリコンを有することを特徴とするレベルシフト回路。

【請求項 2】

トランジスタと、第1及び第2のインバータ回路と、を有し、

前記トランジスタは、ドレイン及び第1のゲートに第1の電源電位が印加され、

前記トランジスタは、第2のゲートに第2の電源電位が印加されしきい値電圧が制御され、

前記第1のインバータ回路は、第1の信号が入力され、第2の信号を出力し、

前記第1のインバータ回路は、電源電圧として、前記第1の電源電位から前記制御されたしきい値電圧を減算した第1の電位と、第3の電源電位とが印加され、

10

20

前記第2のインバータ回路は、前記第2の信号が入力され、第3の信号を出力し、前記第2のインバータ回路は、電源電圧として、前記第1の電位と、前記第3の電源電位とが印加され、

前記トランジスタのチャネル形成領域は、酸化物半導体を有し、

前記インバータ回路が有するトランジスタのチャネル形成領域は、シリコンを有することを特徴とするレベルシフト回路。

### 【請求項3】

請求項1又は請求項2に記載のレベルシフト回路と、

第3のトランジスタ及び容量素子を有するメモリセルを複数備えたメモリセルアレイと、を有し、

10

前記第3のトランジスタのチャネル形成領域は、酸化物半導体を有し、

前記酸化物半導体を有するトランジスタは、絶縁膜を介して前記シリコンを有するトランジスタの上方に有することを特徴とする半導体集積回路。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

トランジスタを用いたレベルシフタに関する。また、その駆動方法に関する。

#### 【背景技術】

#### 【0002】

近年、電子機器のさらなる高性能化のために、CPU(Central Process 20

ing Unit)やメモリなど、複数の機能を有する回路が1つのチップに組み込まれたLSIなどの半導体集積回路の開発が進められている。このような集積回路の電源電圧については、低消費電力化のために低電圧化が要求されている。電源電圧の異なる複数の機能を有する回路間で信号の伝達を行う場合、信号のレベル変換を行う必要がある。

#### 【0003】

レベル変換のための一方法として、特許文献1には、N-chMOSトランジスタのゲートおよびドレインを電源電圧VDDに共通に接続し、ソースをCMOSインバータ回路の電源側回路端に接続されたレベルシフト回路が開示されている。特許文献1に記載のレベルシフト回路は、N-chMOSトランジスタのバックゲートに相当するP-Wellを、GNDに接続することにより、閾値電圧を制御し、レベルシフト回路の出力パルスの”H”レベルが電源電圧VDDよりもMOSトランジスタのしきい値電圧に近い値だけ低くなる波形を出力させると記載されている。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開2001-77684号公報

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、インバータに接続されたトランジスタのしきい値電圧を制御して、レベル変換する方式は、出力端子の電圧を高精度に制御することが容易ではない。個々のトランジスタのしきい値電圧のばらつきによって出力端子の電圧が変動するためである。

40

#### 【0006】

また、このようなレベルシフト回路を複数用いて、電源電圧の異なる複数の機能を有する回路間で信号の伝達を行う場合、複数のレベルシフト回路それぞれが異なる電圧を出力するためには、インバータに接続されたトランジスタのしきい値電圧をそれぞれ制御する必要がある。

#### 【0007】

この点において、特許文献1に記載されたレベルシフト回路では、トランジスタのしきい値電圧を変動させるために基板電圧を変動させる必要があると考えられる。基板電圧を変

50

動させてしまうと、他の回路のトランジスタのしきい値電圧も変動してしまうため、複数のトランジスタのしきい値電圧を個々に制御することが困難である。また、複数のトランジスタのしきい値電圧を個々に制御するために、別途回路が必要となるため、回路規模が増大する。

**【0008】**

また、複数のレベルシフト回路を、シリコンウエハを用いて作製する場合、インバータに接続されたトランジスタのしきい値電圧をそれぞれ変えるためには、トランジスタのL長や、チャネルドープ量を個々に変化させる必要があり、回路の設計が煩雑になる。

**【0009】**

上記問題に鑑み、本発明の一態様は、小型化されたレベルシフト回路を提供することを目的の一とする。また、複数の出力端子から、それぞれ異なる振幅を有する出力信号を出力させることができるレベルシフト回路を提供することを目的の一とする。また、該レベルシフト回路を用いて、より小型化され、低消費電力化された半導体集積回路を提供することを目的の一とする。10

**【課題を解決するための手段】**

**【0010】**

本発明の一態様は、第1の電源電位が印加される第1の入力端子と、第2の電源電位が印加される第2の入力端子と、第3の電源電位が印加される第3の入力端子と、第1の入力信号が印加される第4の入力端子と、信号が出力される第1の出力端子と、n型の第1のトランジスタと、p型の第2のトランジスタ及びn型の第3のトランジスタとを有するインバータ回路と、を有するレベルシフト回路である。20

**【0011】**

n型の第1のトランジスタは、酸化物半導体膜にチャネルが形成され、酸化物半導体膜を挟んで設けられた一対のゲート電極を有する。一対のゲート電極の一方は、酸化物半導体膜と第1のゲート絶縁膜を介して重畳し、一対のゲート電極の他方は、酸化物半導体膜と第2のゲート絶縁膜を介して重畳する構成とすることが好ましい。ここで、一対のゲート電極の一方を第1のトランジスタの第1のゲート電極とする。また、一対のゲート電極の他方を第1のトランジスタの第2のゲート電極とする(バックゲートとも呼ぶ)。そして、第1のトランジスタのしきい値電圧は、第2のゲート電極の電位の高さ、より具体的には、ソース電極と第2のゲート電極の電位差により制御される。第1のトランジスタのしきい値電圧の変化量  $V_{t_h}$  は、第2のゲート電極に印加される第2の電源電位によって制御することができる。30

**【0012】**

なお、本明細書等において、トランジスタのしきい値電圧の変化量とは、トランジスタの第2のゲート電極に、電位を印加する前と後におけるしきい値の変化量のことをいう。

**【0013】**

また、p型の第2のトランジスタ及びn型の第3のトランジスタは、シリコンなどの半導体膜にチャネルが形成される。該半導体膜は、シリコンや炭化シリコンなどの単結晶半導体膜、多結晶半導体膜、シリコンゲルマニウム、ガリウムヒ素、インジウムリンなどの化合物半導体膜を適用することができる。40

**【0014】**

第2のトランジスタのゲート電極及び第3のトランジスタのゲート電極は、第4の入力端子と接続され、第2のトランジスタのドレイン電極及び第3のトランジスタのソース電極は、第1の出力端子と接続される。また、第3のトランジスタのドレイン電極は、第3の入力端子と接続される。

**【0015】**

第1のトランジスタのソース電極と第1のゲート電極は、第1の入力端子と接続され、第2のゲート電極は、第2の入力端子と接続され、ドレイン電極は、第2のトランジスタのソース電極と接続される。

**【0016】**

50

20

30

40

したがって、本発明の一態様に係るレベルシフト回路は、入力信号がローレベルからハイレベルに変化すると、インバータ回路の第1の出力端子から、第3の電源電位が出力される。また、入力信号がハイレベルからローレベルに変化すると、インバータ回路の第1の出力端子から、第1の電源電位から第1のトランジスタのしきい値電圧の変化量を減算した電位が出力される。第1のトランジスタのしきい値電圧は、第2のゲート電極に印加される第2の電源電位によって制御することができる。

#### 【0017】

酸化物半導体膜が用いられた第1のトランジスタのしきい値電圧を、第2のゲート電極に印加される電位によって変動させることで、インバータ回路から出力される電位を容易に制御することができる。

10

#### 【0018】

また、上記構成のレベルシフト回路を複数用いた場合であっても、それぞれのレベルシフト回路が有する酸化物半導体膜を用いたトランジスタのしきい値電圧を、それぞれ変化させることができる。これにより、それぞれのレベルシフト回路から、異なる電位（または信号）を出力することができる。

#### 【0019】

本発明の一態様は、第1の電源電位が印加される第1の入力端子と、第2の電源電位が印加される第2の入力端子と、第3の電源電位が印加される第3の入力端子と、第1の入力信号が印加される第4の入力端子と、第1の出力信号が出力される第1の出力端子と、ソース電極及び第1のゲート電極に第1の電源電位が印加され、第2のゲート電極に第2の電源電位が印加される第1のトランジスタと、第1の入力信号が印加され、第1の電源電位から第1のトランジスタのしきい値電圧の変化量を減算した電位と、第3の電源電位とが電源電圧として供給され、第1の出力信号を出力するインバータ回路と、を有し、第1のトランジスタは、酸化物半導体膜にチャネルが形成されるレベルシフト回路である。

20

#### 【0020】

また、本発明の一態様は、第1の電源電位が印加される第1の入力端子と、第2の電源電位が印加される第2の入力端子と、第3の電源電位が印加される第3の入力端子と、第1の入力信号が印加される第4の入力端子と、第1の出力信号が出力される第1の出力端子と、第2の出力信号が出力される第2の出力端子と、ソース電極及び第1のゲート電極に第1の電源電位が印加され、第2のゲート電極に第2の電源電位が印加される第1のトランジスタと、第1の入力信号が印加され、第1の電源電位から第1のトランジスタのしきい値電圧の変化量を減算した電位と、第3の電源電位とが電源電圧として供給され、第1の出力信号を出力する第1のインバータ回路と、第1のインバータ回路から出力された第1の出力信号が入力され、第1の電源電位から第1のトランジスタのしきい値電圧の変化量を減算した電位と、第3の電源電位とが電源電圧として供給され、第2の出力信号を出力する第2のインバータ回路と、を有し、第1のトランジスタは、酸化物半導体膜にチャネルが形成されるレベルシフト回路である。

30

#### 【0021】

また、本発明の一態様は、第1の電源電位が印加される第1の入力端子と、第2の電源電位が印加される第2の入力端子と、第3の電源電位が印加される第3の入力端子と、第4の電源電位が印加される第4の入力端子と、第1の入力信号が印加される第5の入力端子と、第1の出力信号が出力される第1の出力端子と、第2の出力信号が出力される第2の出力端子と、ソース電極及び第1のゲート電極に第1の電源電位が印加され、第2のゲート電極に第2の電源電位が印加される第1のトランジスタと、ソース電極に第3の電源電位が供給され、第2のゲート電極に第4の電源電位が印加される第2のトランジスタと、第1の入力信号が印加され、第1の電源電位から第1のトランジスタのしきい値電圧の変化量を減算した電位と、第3の電源電位に第2のトランジスタのしきい値電圧の変化量が加算された電位とが電源電圧として供給され、第1の出力信号を出力する第1のインバータ回路と、第1のインバータ回路から出力された第1の出力信号が入力され、第1の電源電位から第1のトランジスタしきい値電圧の変化量を減算した電位と、第3の電源電位に

40

50

第2のトランジスタのしきい値電圧の変化量が加算された電位とが電源電圧として供給され、第2の出力信号を出力する第2のインバータ回路と、を有し、第1のトランジスタ及び第2のトランジスタは、酸化物半導体膜にチャネルが形成されるレベルシフト回路である。

#### 【0022】

上記各構成において、第2のインバータ回路は、p型の第3のトランジスタと、n型の第4のトランジスタと、を有し、第3のトランジスタ及び第4のトランジスタは、シリコン膜にチャネルが形成される。

#### 【0023】

また、上記各構成において、第1のインバータ回路は、p型の第5のトランジスタと、n型の第6のトランジスタと、を有し、第5のトランジスタ及び第6のトランジスタは、シリコン膜にチャネルが形成される。 10

#### 【0024】

また、上記各構成のいずれかを用いたレベルシフト回路と、第7のトランジスタ及び容量素子を有するメモリセルを複数備えたメモリセルアレイと、を用いることにより、半導体集積回路を構成することもできる。第7のトランジスタは、第1のトランジスタ及び第2のトランジスタと同様に、酸化物半導体膜にチャネルが形成されるトランジスタである。

#### 【発明の効果】

#### 【0025】

本発明の一態様は、小型化されたレベルシフト回路を提供することができる。また、複数の出力端子から、それぞれ異なる振幅を有する出力信号を出力させることができるレベルシフト回路を提供することができる。また、該レベルシフト回路を用いて、より小型化され、低消費電力化された半導体集積回路を提供することができる。 20

#### 【図面の簡単な説明】

#### 【0026】

【図1】本発明の一態様に係るレベルシフト回路。

【図2】本発明の一態様に係るレベルシフト回路。

【図3】本発明の一態様に係るレベルシフト回路。

【図4】本発明の一態様に係るレベルシフト回路。

【図5】本発明の一態様に係るレベルシフト回路。

【図6】半導体装置の作製工程の一例を示す図。

【図7】半導体装置の作製工程の一例を示す図。

【図8】半導体装置の作製工程の一例を示す図。

【図9】半導体装置の作製工程の一例を示す図。

【図10】半導体装置の一態様を説明する回路図及び斜視図。

【図11】半導体装置の一態様を説明する断面図及び平面図。

【図12】半導体装置の一態様を説明するブロック図。

【図13】半導体装置の一態様を説明するブロック図。

【図14】電子機器を説明する図。

#### 【発明を実施するための形態】

#### 【0027】

本発明の実施の形態の一例について、図面を用いて詳細に説明する。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。

#### 【0028】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

#### 【0029】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同 50

を避けるために付すものであり、数的に限定するものではない。

**【0030】**

なお、本明細書等において「電圧」と「電位」を同義で用いることがある。

**【0031】**

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

**【0032】**

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。10

**【0033】**

(実施の形態1)

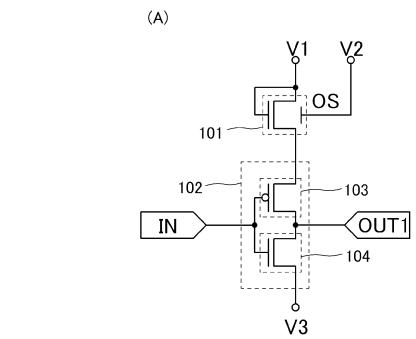

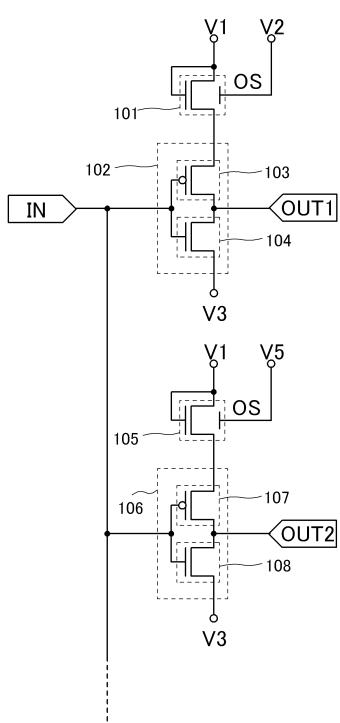

本実施の形態では、本発明の一態様に係るレベルシフト回路について、図1乃至図5を参照して説明する。なお、回路図において、酸化物半導体を用いたトランジスタであることを示すために、「OS」の符号を付す場合がある。

**【0034】**

レベルシフト回路構成1

図1(A)は、本発明の一態様に係るレベルシフト回路の構成例を示す図である。図1(A)に示すレベルシフト回路は、第1の電源電位V1が印加される第1の入力端子と、第2の電源電位V2が印加される第2の入力端子と、第3の電源電位V3が印加される第3の入力端子と、入力信号INが印加される第4の入力端子と、第1の出力信号OUT1が出力される第1の出力端子と、n型のトランジスタ101と、インバータ回路102と、を有する。また、インバータ回路102は、p型のトランジスタ103と、n型のトランジスタ104とを有する。20

**【0035】**

n型のトランジスタ101は、酸化物半導体膜にチャネルが形成され、酸化物半導体膜を挟んで設けられた一対のゲート電極を有する。一対のゲート電極の一方は、酸化物半導体膜と第1のゲート絶縁膜を介して重畠し、一対のゲート電極の他方は、酸化物半導体膜と第2のゲート絶縁膜を介して重畠する構成とすることが好ましい。ここで、一対のゲート電極の一方をトランジスタ101の第1のゲート電極とする。また、一対のゲート電極の他方をトランジスタ101の第2のゲート電極とする(バックゲートとも呼ぶ)。そして、トランジスタ101のしきい値電圧は、第2のゲート電極の電位の高さ、より具体的には、ソース電極と第2のゲート電極の電位差により制御される。トランジスタ101のしきい値電圧の変化量  $V_{th101}$  は、第2のゲート電極に印加される第2の電源電位V2によって制御することができる。30

**【0036】**

また、p型のトランジスタ103及びn型のトランジスタ104は、シリコンなどの半導体膜にチャネルが形成される。該半導体膜は、シリコンや炭化シリコンなどの単結晶半導体膜、多結晶半導体膜、シリコンゲルマニウム、ガリウムヒ素、インジウムリンなどの化合物半導体膜を適用することができる。40

**【0037】**

トランジスタ103のゲート電極及びトランジスタ104のゲート電極は、第4の入力端子と接続され、トランジスタ103のドレイン電極及びトランジスタ104のソース電極は、第1の出力端子と接続される。また、トランジスタ104のドレイン電極は、第3の入力端子と接続される。

**【0038】**

トランジスタ101のソース電極と第1のゲート電極は、第1の入力端子と接続され、第2のゲート電極は、第2の入力端子と接続され、ドレイン電極は、トランジスタ103の50

ソース電極と接続される。

**【0039】**

また、トランジスタ101は、酸化物半導体膜を用いて形成することができるため、トランジスタ103及びトランジスタ104の上に積層して形成することができる。これにより、レベルシフト回路を構成するトランジスタの一部を積層構造とすることができます、レベルシフト回路面積の縮小化を図ることができる。なお、本実施の形態に示す酸化物半導体膜を用いたトランジスタは、シリコンなどの半導体膜を用いたトランジスタの上に積層することが可能である。

**【0040】**

次に、図1(A)に示すレベルシフト回路の動作について説明する。なお、第1の電源電位V1はVDD、第2の電源電位V2はVSS、第3の電源電位V3はGND(接地電位)、入力信号INはローレベル信号をGND、ハイレベル信号をVDD、トランジスタ101のしきい値電圧の変化量を  $V_{th101}$  として説明する。

10

**【0041】**

図1(A)に示すレベルシフト回路は、入力信号INがローレベルからハイレベルに変化すると、インバータ回路102の第1の出力端子から、ローレベルの第1の出力信号OUT1(第3の電源電位V3)が出力される。

**【0042】**

また、入力信号INがハイレベルからローレベルに変化すると、インバータ回路102の第1の出力端子から、ハイレベルの第1の出力信号OUT1(第1の電源電位V1からトランジスタの101のしきい値電圧の変化量  $V_{th101}$  を減算した電位)が出力される。

20

**【0043】**

このように、トランジスタ101のしきい値電圧を、第2のゲート電極に印加される電位によって変動させることで、入力信号INがローレベル時の出力信号OUT1を容易に制御することができる。

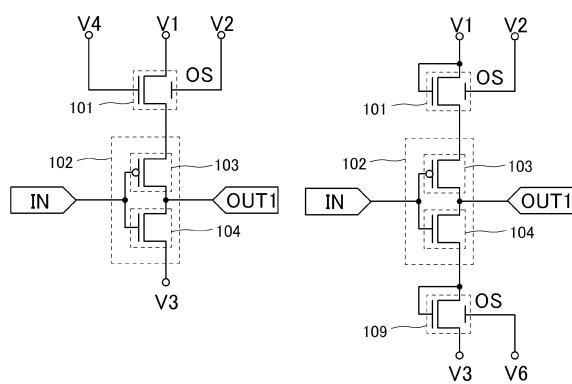

**【0044】**

図1(B)に示すレベルシフト回路は、図1(A)に示すレベルシフト回路において、トランジスタ101の第1のゲート電極を、第4の電源電位V4が印加される第5の入力端子に接続した構成である。なお、第4の電源電位V4は、例えば、VDDとすればよい。

30

**【0045】**

図1(A)に示すレベルシフト回路では、トランジスタ101の第1のゲート電極は、第1の入力端子に接続されているため、第1の電源電位V1によって制御される。これに対し、図1(B)に示すレベルシフト回路では、トランジスタ101の第1のゲート電極を、第4の電源電位によって制御することができる。トランジスタ101の第1のゲート電極と、第2のゲート電極とを個々に制御することによって、入力信号INがローレベル時の出力信号OUT1を容易に制御することができる。また、図1(B)に示すレベルシフト回路では、トランジスタ101の第1のゲート電極に、ハイレベル電位(例えば、VDD)またはローレベル電位(例えば、GND)を印加することにより、トランジスタ101のオンまたはオフを制御することができる。また、トランジスタ101を、酸化物半導体を用いたトランジスタで構成することにより、オフ電流を極めて小さくすることができる。よって、入力信号INがハイレベルの際は、トランジスタ101をオフ状態とすることにより、レベルシフト回路で消費される電力を低減することができる。

40

**【0046】**

図1(C)に示すレベルシフト回路は、図1(A)に示すレベルシフト回路の構成に加えて、第6の電源電位V6が印加される第7の入力端子と、n型のトランジスタ109と、を有する。

**【0047】**

n型のトランジスタ109は、n型のトランジスタ101と同様に、酸化物半導体膜にチャネルが形成され、酸化物半導体膜を挟んで設けられた一対のゲート電極を有する。ここ

50

で、一対のゲート電極の一方をトランジスタ109の第1のゲート電極とする。また、一対のゲート電極の他方をトランジスタ109の第2のゲート電極とする（バックゲートとも呼ぶ）。そして、トランジスタ109のしきい値電圧は、第2のゲート電極の電位の高さ、より具体的には、ソース電極と第2のゲート電極の電位差により制御される。

#### 【0048】

トランジスタ109のソース電極は、トランジスタ104のドレイン電極と接続され、第2のゲート電極は、第7の入力端子と接続され、ドレイン電極は、第3の入力端子と接続される。

#### 【0049】

次に、図1(C)に示すレベルシフト回路の動作について説明する。なお、第1の電源電位V1はVDD、第2の電源電位V2はVSS、第3の電源電位V3はGND(接地電位)、第6の電源電位V6はVDD、入力信号INはローレベル信号をGND、ハイレベル信号をVDD、トランジスタ101のしきい値電圧の変化量を $V_{th101}$ 、トランジスタ109のしきい値電圧の変化量を $V_{th109}$ として説明する。10

#### 【0050】

図1(C)に示すレベルシフト回路は、入力信号INがローレベルからハイレベルに変化すると、インバータ回路102の第1の出力端子から、ローレベルの第1の出力信号OUT1(第3の電源電位V3にトランジスタ109のしきい値電圧の変化量 $V_{th109}$ を加算した電位)が出力される。

#### 【0051】

また、入力信号INがハイレベルからローレベルに変化すると、インバータ回路102の第1の出力端子から、ハイレベルの第1の出力信号OUT1(第1の電源電位V1からトランジスタ101のしきい値電圧の変化量 $V_{th101}$ 減算した電位)が出力される。20

#### 【0052】

このように、図1(C)に示すレベルシフト回路は、トランジスタ101のしきい値電圧を、第2のゲート電極に印加される電位によって変動させ、トランジスタ109のしきい値電圧を、第2のゲート電極に印加される電位によって変化させることで、図1(A)、(B)に示すレベルシフト回路の出力信号OUT1よりも小さい振幅の出力信号(入力信号INがハイレベル時の電位が高い)を出力させることができる。

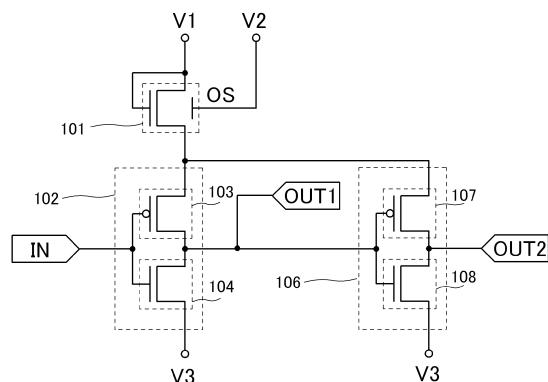

#### 【0053】

##### レベルシフト回路構成2

図2は、本発明の一態様に係るレベルシフト回路の他の構成例を示す図である。図2に示すレベルシフト回路は、図1(A)に示すレベルシフト回路の構成に加えて、第5の電源電位V5が印加される第6の入力端子と、第2の出力信号OUT2が出力される第2の出力端子と、n型のトランジスタ105と、インバータ回路106と、を有する。また、インバータ回路106は、p型のトランジスタ107と、n型のトランジスタ108とを有する。

#### 【0054】

n型のトランジスタ105は、n型のトランジスタ101と同様に、酸化物半導体膜にチャネルが形成され、酸化物半導体膜を挟んで設けられた一対のゲート電極を有する。ここで、一対のゲート電極の一方をトランジスタ105の第1のゲート電極とする。また、一対のゲート電極の他方をトランジスタ105の第2のゲート電極とする（バックゲートとも呼ぶ）。そして、トランジスタ105のしきい値電圧は、第2のゲート電極の電位の高さ、より具体的には、ソース電極と第2のゲート電極の電位差により制御される。トランジスタ105のしきい値電圧の変化量 $V_{th105}$ は、第2のゲート電極に印加される第5の電源電位V5によって制御することができる。40

#### 【0055】

また、p型のトランジスタ107及びn型のトランジスタ108は、シリコンなどの半導体膜にチャネルが形成される。トランジスタ107のゲート電極及びトランジスタ108のゲート電極は、第1の入力端子と接続され、トランジスタ107のドレイン電極及びト50

ランジスタ108のソース電極は、第2の出力端子と接続される。また、トランジスタ108のドレイン電極は、第3の入力端子と接続される。

#### 【0056】

トランジスタ105のソース電極は、トランジスタ101のドレイン電極とトランジスタ103のソース電極とが接続されたノードN1と接続され、第2のゲート電極は、第6の入力端子と接続され、ドレイン電極は、トランジスタ107のソース電極と接続される。

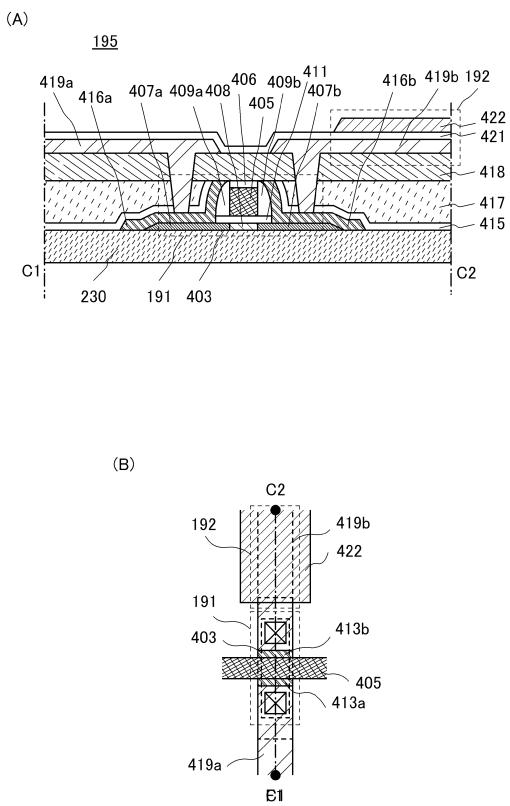

#### 【0057】

次に、図2に示すレベルシフト回路の動作について説明する。なお、第1の電源電位V1はVDD、第2の電源電位V2はVSS、第3の電源電位V3はGND(接地電位)、第5の電源電位V5はVDD、入力信号INはローレベル信号をGND、ハイレベル信号をVDD、トランジスタ101のしきい値電圧の変化量をV<sub>th101</sub>、トランジスタ105のしきい値電圧の変化量をV<sub>th105</sub>として説明する。

#### 【0058】

図2に示すレベルシフト回路は、入力信号INがローレベルからハイレベルに変化すると、インバータ回路102の第1の出力端子から、ローレベルの信号(第3の電源電位V3)が出力され、インバータ回路106の第2の出力端子から、ローレベルの信号(第3の電源電位V3)が出力される。

#### 【0059】

また、入力信号INがハイレベルからローレベルに変化すると、インバータ回路102の第1の出力端子から、ハイレベルの第1の出力信号OUT1(第1の電源電位V1からトランジスタ101のしきい値電圧の変化量V<sub>th101</sub>を減算した電位)が出力される。また、インバータ回路106の第2の出力端子から、ハイレベルの第2の出力信号OUT2(第1の電源電位V1からトランジスタ101のしきい値電圧の変化量V<sub>th101</sub>を減算した電位から、さらにトランジスタ105のしきい値電圧の変化量V<sub>th105</sub>を減算した電位)が出力される。

#### 【0060】

このように、トランジスタ101のしきい値電圧を、第2のゲート電極に印加される第2の電源電位V2によって変動させ、トランジスタ105のしきい値電圧を第5の電源電位V5によって変動させることで、第2の出力端子から第1の出力端子とは異なる振幅を有する信号を出力することができる。なお、第2の出力端子から出力される電位は、第1の出力端子よりも低い電位となる。

#### 【0061】

トランジスタ101の第1のゲート電極とトランジスタ101の第2のゲート電極の電位を制御することによって、入力信号INがローレベル時のインバータ回路102の第1の出力信号OUT1を容易に制御することが可能である。さらに、トランジスタ101の第1のゲート電極とトランジスタ101の第2のゲート電極を制御することによって生じたノードN1の電位を利用して、トランジスタ105の第1のゲート電極とトランジスタ105の第2のゲート電極の電位を制御することによって入力信号INがローレベル時のインバータ回路106の第2の出力信号OUT2を容易に制御することが可能である。回路構成2によって回路構成1では扱えない電位をインバータ回路106の第2の出力信号OUT2として出力することができる。

#### 【0062】

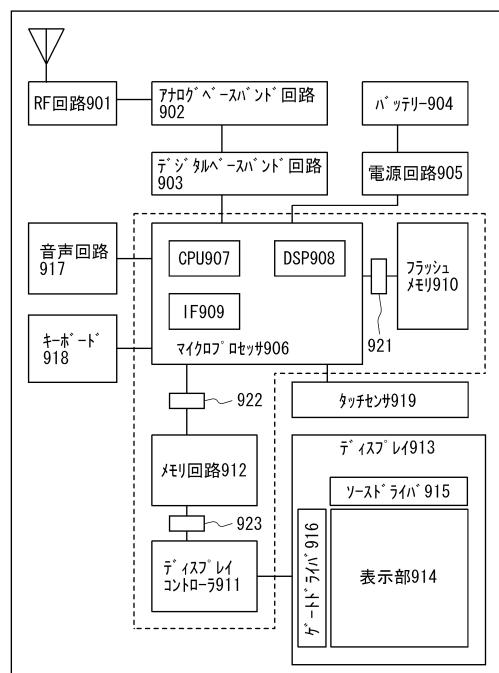

図2に示すレベルシフト回路において、2つの出力端子からそれぞれ異なる信号が出力される場合について説明したが、これに限定されず、3つ以上の出力端子からそれぞれ異なる信号を出力される構成としてもよい。例えば、3つの出力端子からそれぞれ異なる信号を出力させる場合には、図2に示すノードN2に、さらに酸化物半導体膜にチャネルが形成されるトランジスタのソース電極を接続し、ドレイン電極にインバータ回路を接続すればよい。該トランジスタの第2のゲート電極に印加される電源電位を制御することにより、該インバータから出力される第3の出力信号として、第2の出力信号よりも振幅が小さい(入力信号INがローレベル時の電位が低い)出力信号を出力することができる。

10

20

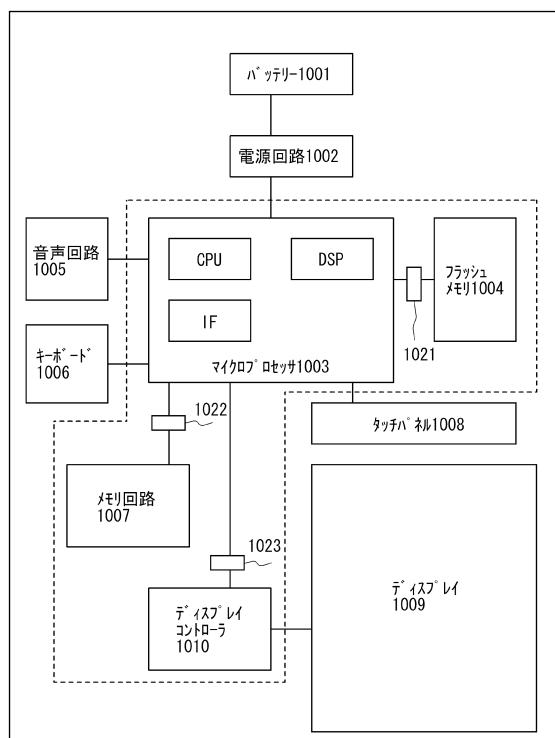

30

40

50

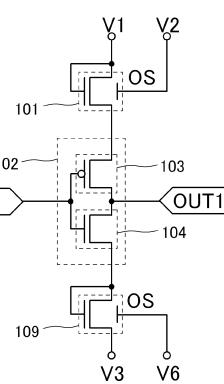

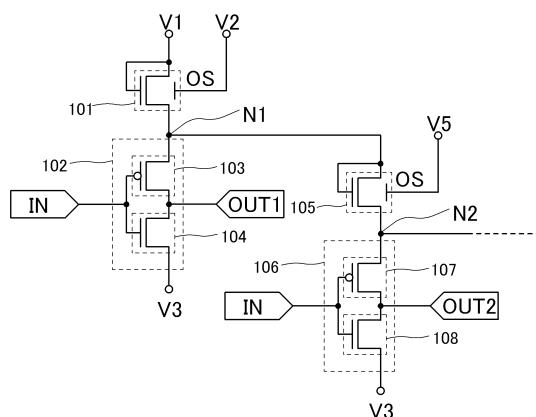

## 【0063】

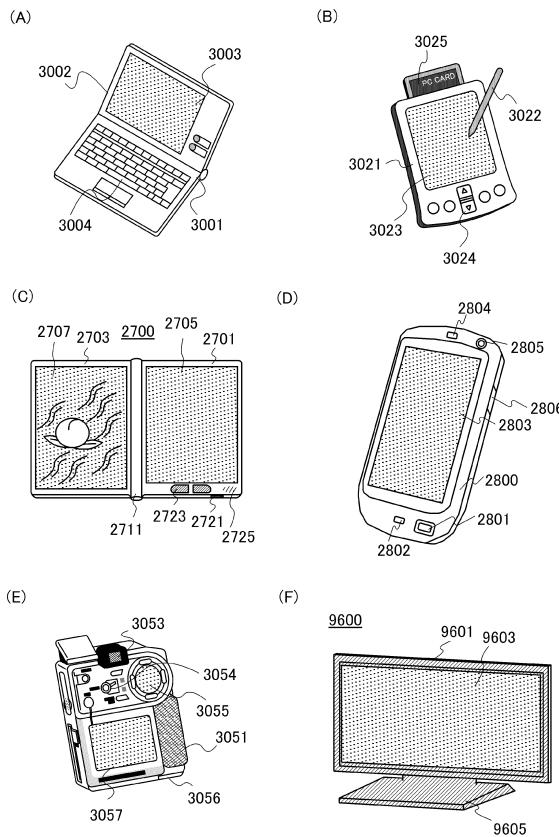

## レベルシフト回路構成3

図3は、本発明の一態様に係るレベルシフト回路の他の構成例を示す図である。図3に示すレベルシフト回路は、図2に示すレベルシフト回路とは、接続が異なる。

## 【0064】

図2に示すレベルシフト回路は、トランジスタ105のソース電極は、ノードN1と接続されるのに対し、図3に示すレベルシフト回路は、トランジスタ105のソース電極は、第1の入力端子と接続されている。

## 【0065】

次に、図3に示すレベルシフト回路の動作について説明する。なお、第1の電源電位V1はVDD、第2の電源電位V2はVSS、第3の電源電位V3はGND（接地電位）、第5の電源電位V5はVDD、入力信号INはローレベル信号をGND、ハイレベル信号をVDD、トランジスタ101のしきい値電圧の変化量を $V_{th101}$ 、トランジスタ105のしきい値電圧の変化量を $V_{th105}$ として説明する。10

## 【0066】

図3に示すレベルシフト回路は、入力信号INがローレベルからハイレベルに変化すると、インバータ回路102の第1の出力端子から、ローレベルの信号（第3の電源電位V3（例えば、GND））が出力され、インバータ回路106の第2の出力端子から、ローレベルの信号（第3の電源電位V3（例えば、GND））が出力される。20

## 【0067】

また、入力信号INがハイレベルからローレベルに変化すると、インバータ回路102の第1の出力端子から、ハイレベルの第1の出力信号OUT1（第1の電源電位（例えば、VDD）からトランジスタ101のしきい値電圧の変化量 $V_{th101}$ を減算した電位）が出力される。また、インバータ回路106の第2の出力端子から、ローレベルの第2の出力信号OUT2（第1の電源電位（例えば、VDD）からトランジスタ105のしきい値電圧の変化量 $V_{th105}$ を減算した電位）が出力される。20

## 【0068】

入力信号INが共通のインバータ回路102の第1の出力端子と、インバータ回路106の第2の出力端子を個別に制御することが可能であり、同じ論理動作でも異なる電位で出力が可能である。なお、トランジスタ101のしきい値電圧の変化量 $V_{th101}$ 及びトランジスタ105のしきい値電圧の変化量 $V_{th105}$ はそれぞれ、第2の電源電位V2及び第5の電源電位V5によって制御することができる。よって、第2の出力信号OUT2は第1の出力信号OUT1よりも振幅の大きい（入力信号INがローレベル時の電位が高い）出力信号であることも可能であるし、第1の出力信号OUT1よりも振幅の小さい（入力信号INがローレベル時の電位が低い）出力信号であることも可能である。30

## 【0069】

また、図3に示すレベルシフト回路において、2つの出力端子からそれぞれ異なる信号が出力される場合について説明したが、これに限定されず、3つ以上の出力端子からそれぞれ異なる信号を出力させる構成としてもよい。例えば、3つの出力端子からそれぞれ異なる信号を出力させる場合には、図3に示す第4の入力端子に、インバータ回路を接続し、インバータ回路が有するp型のトランジスタのソース電極に、酸化物半導体膜にチャネルが形成されるトランジスタのドレイン電極を接続すればよい。該トランジスタの第2のゲート電極に印加される電源電位を制御することにより、該インバータ回路の第3の出力端子から、第1の出力信号及び第2の出力信号とは異なる出力信号を出力させることができる。もちろん、それぞれの出力端子から、それぞれの振幅が同じ（入力信号INがローレベル時の電位が同じ）出力信号を出力させてもよい。40

## 【0070】

## レベルシフト回路構成4

図4は、本発明の一態様に係るレベルシフト回路の他の構成例を示す図である。図4に示すレベルシフト回路は、図1(A)に示すレベルシフト回路の構成に加えて、第2の出力50

信号 OUT 2 が出力される第 2 の出力端子と、インバータ回路 106 を有する。また、インバータ回路 106 は、p 型のトランジスタ 107 と、n 型のトランジスタ 108 とを有する。

#### 【 0071 】

p 型のトランジスタ 107 及び n 型のトランジスタ 108 は、シリコンなどの半導体膜にチャネルが形成される。トランジスタ 107 のゲート電極及びトランジスタ 108 のゲート電極は、第 1 の出力端子と接続され、トランジスタ 107 のドレイン電極及びトランジスタ 108 のソース電極は、第 2 の出力端子と接続される。

#### 【 0072 】

次に、図 4 に示すレベルシフト回路の動作について説明する。なお、第 1 の電源電位 V1 10 は VDD、第 2 の電源電位 V2 は VSS、第 3 の電源電位 V3 は GND ( 接地電位 ) 、入力信号 IN はローレベル信号を GND、ハイレベル信号を VDD、トランジスタ 101 のしきい値電圧の変化量を  $V_{th101}$  として説明する。

#### 【 0073 】

図 4 に示すレベルシフト回路は、入力信号 IN がローレベルからハイレベルに変化すると、インバータ回路 102 の第 1 の出力端子から、ローレベルの第 1 の出力信号 OUT 1 ( 第 3 の電源電位 V3 ) が output される。これにより、トランジスタ 107 のゲート電極及びトランジスタ 108 のゲート電極には、第 3 の電源電位 V3 が印加されるため、インバータ回路 106 の第 2 の出力端子から、ハイレベルの第 2 の出力信号 OUT 2 ( 第 1 の電源電位 V1 からトランジスタ 101 のしきい値電圧の変化量  $V_{th101}$  を減算した電位 ) が output される。 20

#### 【 0074 】

また、入力信号 IN がハイレベルからローレベルに変化すると、インバータ回路 102 の第 1 の出力端子から、ハイレベルの第 1 の出力信号 OUT 1 ( 第 1 の電源電位 V1 からトランジスタ 101 のしきい値電圧の変化量  $V_{th101}$  を減算した電位 ) が output される。これにより、トランジスタ 107 のゲート電極及びトランジスタ 108 のゲート電極には、第 1 の電源電位 V1 からトランジスタ 101 のしきい値電圧の変化量  $V_{th101}$  を減算した電位が印加されるため、インバータ回路 106 の第 2 の出力端子から、ローレベルの第 2 の出力信号 OUT 2 ( 第 3 の電源電位 V3 ) が output される。

#### 【 0075 】

第 1 の電源電位 V1 ( 例えば、VDD ) からトランジスタ 101 のしきい値電圧の変化量  $V_{th101}$  を減算した電位によって、インバータ回路 106 の第 2 の出力信号 OUT 2 がハイレベル時の電位を容易に制御することが可能である。 30

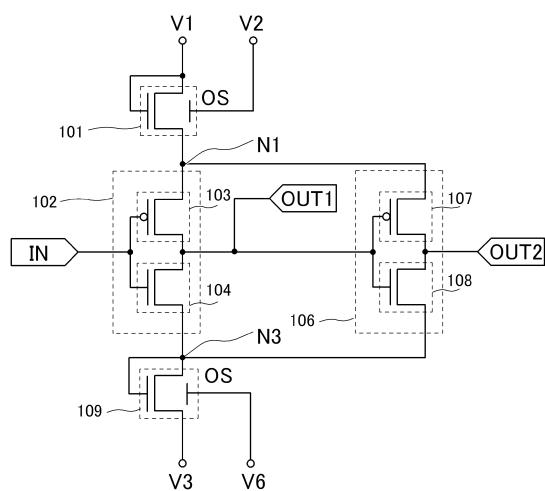

#### 【 0076 】

##### レベルシフト回路構成 5

図 5 は、本発明の一態様に係るレベルシフト回路の他の構成例を示す図である。図 5 に示すレベルシフト回路は、図 4 に示すレベルシフト回路の構成に加えて、第 6 の電源電位 V6 が印加される第 7 の入力端子と、n 型のトランジスタ 109 と、を有する。

#### 【 0077 】

n 型のトランジスタ 109 は、n 型のトランジスタ 101 と同様に、酸化物半導体膜にチャネルが形成され、酸化物半導体膜を挟んで設けられた一対のゲート電極を有する。ここで、一対のゲート電極の一方をトランジスタ 109 の第 1 のゲート電極とする。また、一対のゲート電極の他方をトランジスタ 109 の第 2 のゲート電極とする ( バックゲートとも呼ぶ )。そして、トランジスタ 109 のしきい値電圧は、第 2 のゲート電極の電位の高さ、より具体的には、ソース電極と第 2 のゲート電極の電位差により制御される。 40

#### 【 0078 】

トランジスタ 109 のソース電極は、トランジスタ 104 のドレイン電極と接続され、第 2 のゲート電極は、第 7 の入力端子と接続され、ドレイン電極は、第 3 の入力端子と接続される。

#### 【 0079 】

また、トランジスタ107のソース電極は、ノードN1と接続され、トランジスタ108のドレイン電極は、トランジスタ104のドレイン電極とトランジスタ109のソース電極とが接続されたノードN3と接続される。

#### 【0080】

次に、図5に示すレベルシフト回路の動作について説明する。なお、第1の電源電位V1はVDD、第2の電源電位V2はVSS、第3の電源電位V3はGND(接地電位)、第6の電源電位V6はVDD、入力信号INはローレベル信号をGND、ハイレベル信号をVDD、トランジスタ101のしきい値電圧の変化量を $V_{th101}$ 、トランジスタ109のしきい値電圧の変化量を $V_{th109}$ として説明する。

#### 【0081】

図5に示すレベルシフト回路は、入力信号INがローレベルからハイレベルに変化すると、インバータ回路102の第1の出力端子から、ローレベルの第1の出力信号OUT1(第3の電源電位V3にトランジスタ109のしきい値電圧の変化量 $V_{th109}$ を加算した電位)が出力される。これにより、トランジスタ107のゲート電極及びトランジスタ108のゲート電極に、第3の電源電位V3にトランジスタ109のしきい値電圧の変化量 $V_{th109}$ を加算した電位が印加されるため、インバータ回路106の第2の出力端子から、ハイレベルの第2の出力信号OUT2(第1の電源電位V1からトランジスタ101のしきい値電圧の変化量 $V_{th101}$ を減算した電位)が出力される。

#### 【0082】

また、入力信号INがハイレベルからローレベルに変化すると、インバータ回路102の第1の出力端子から、ハイレベルの第1の出力信号OUT1(第1の電源電位V1からトランジスタ101のしきい値電圧の変化量 $V_{th101}$ 減算した電位)が出力される。これにより、トランジスタ107のゲート電極及びトランジスタ108のゲート電極に、第1の電源電位V1からトランジスタ101のしきい値電圧の変化量 $V_{th101}$ を減算した電位が印加されるため、インバータ回路106の第2の出力端子から、ローレベルの第2の出力信号OUT2(第3の電源電位V3にトランジスタ109のしきい値電圧の変化量 $V_{th109}$ を加算した電位)が出力される。

#### 【0083】

トランジスタ107のソース電極がノードN1と接続され、トランジスタ108のドレイン電極がノードN3と接続されることにより、インバータ回路106の第2の出力端子から出力される電位を入力信号INがハイレベル時とローレベル時の両方で容易に制御可能である。

#### 【0084】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0085】

##### (実施の形態2)

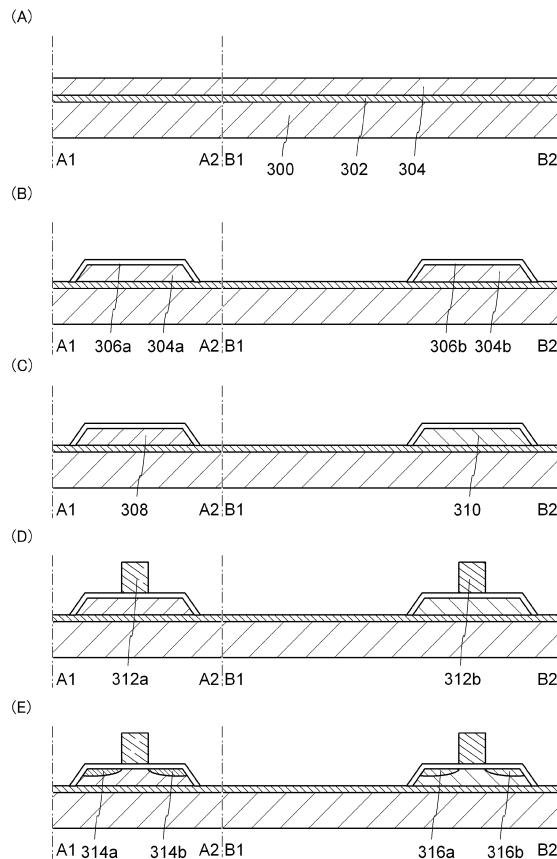

本実施の形態では、実施の形態1に示すレベルシフト回路の作製方法の一例について図6乃至図9を参照して説明する。はじめに、レベルシフト回路の下部に形成されるトランジスタの作製方法について説明し、その後、上部に形成されるトランジスタの作製方法について説明する。

#### 【0086】

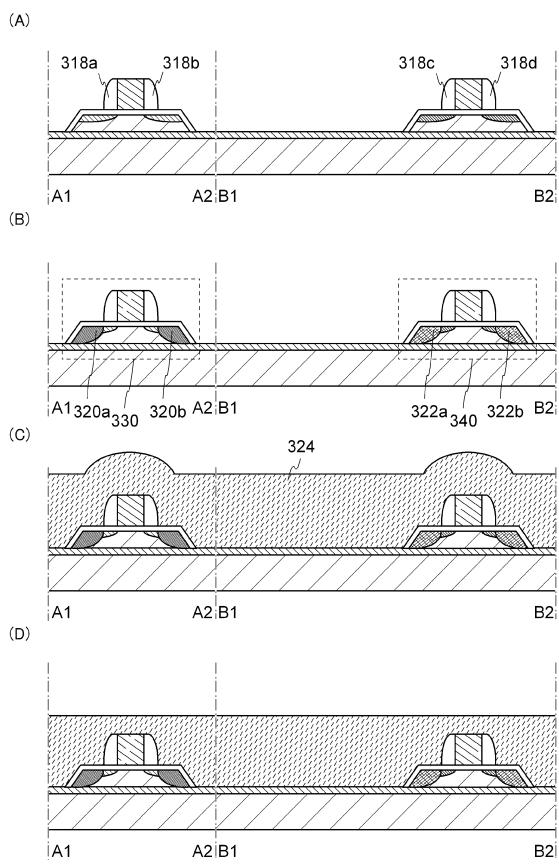

図6乃至図9における作製工程を示す断面図において、A1-A2はトランジスタ330を作製する工程を示し、B1-B2はトランジスタ340上にトランジスタ410を作製する工程を示す。なお、本実施の形態で示すトランジスタ410は、実施の形態1に示すトランジスタ101に相当し、本実施の形態で示すトランジスタ330は、実施の形態1に示すトランジスタ103に相当し、本実施の形態で示すトランジスタ340は、実施の形態1に示すトランジスタ104に相当する。

#### 【0087】

##### 下部のトランジスタの作製方法

10

20

30

40

50

まず、絶縁膜302を介して半導体膜304が設けられた基板300を用意する（図6（A）参照）。

#### 【0088】

基板300として、例えば、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム、ガリウムヒ素、インジウムリンなどの化合物半導体基板を適用することができる。また、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板なども挙げられる。

#### 【0089】

絶縁膜302は、酸化シリコン、酸化窒化シリコン、窒化シリコンなどを含む単層構造又は積層構造とする。なお、絶縁膜302の形成方法としては、熱酸化法、CVD法、スペッタリング法などが挙げられる。絶縁膜302の膜厚は、1nm以上100nm以下、好みしくは10nm以上50nm以下とする。

10

#### 【0090】

また、半導体膜304は、シリコンや炭化シリコンなどの単結晶半導体膜、多結晶半導体膜、シリコンゲルマニウム、ガリウムヒ素、インジウムリンなどの化合物半導体膜を適用することができる。なお、半導体膜304は、酸化物半導体材料を含まないため、酸化物半導体以外の半導体材料とも記す。

#### 【0091】

半導体膜304として、シリコンなどの単結晶半導体膜を用いる場合には、トランジスタ103及びトランジスタ104などの動作を高速化することができるため好ましい。

20

#### 【0092】

また、絶縁膜302を介して半導体膜304が設けられた基板300として、SOI基板も適用することができる。なお、一般に「SOI基板」は、絶縁表面上にシリコン層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体膜が設けられた構成の基板も含む。つまり、「SOI基板」が有する半導体膜は、シリコン層に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁膜を介して半導体膜が設けられた構成も含む。本実施の形態では、絶縁膜302を介して半導体膜304が設けられた基板300として、単結晶シリコン基板上に酸化シリコン膜を介してシリコン膜が設けられたSOI基板を用いる場合について説明する。

30

#### 【0093】

次に、半導体膜304を島状に加工して、半導体膜304a、304bを形成する（図6（B）参照）。当該加工方法として、ドライエッチングを用いることが好適であるが、ウェットエッチングを用いてもよい。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。

#### 【0094】

次に、半導体膜304a、304bを覆うように、ゲート絶縁膜306a、306bを形成する（図6（C）参照）。ゲート絶縁膜306a、306bは、例えば、半導体膜304a、304b表面の熱処理（熱酸化処理や熱窒化処理など）によって形成することができる。熱処理に代えて、高密度プラズマ処理を適用してもよい。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などのうちいずれかの混合ガスを用いて行うことができる。もちろん、CVD法やスペッタリング法等を用いてゲート絶縁膜を形成しても良い。

40

#### 【0095】

ゲート絶縁膜306a、306bは、酸化シリコン、酸化窒化シリコン、窒化シリコン、酸化アルミニウム、酸化タンタルなどの材料を用いることができる。また、ゲート絶縁膜として、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0, y > 0$ )）、窒素が添加されたハフニウムシリケート（ $HfSi_xO_yN_z$  ( $x > 0, y > 0, z > 0$ )）、窒素が添加されたハフニウムアルミネート（ $HfAl_xO_yN_z$  ( $x > 0, y > 0, z > 0$ )）等の高誘電率（high-k）材料を用いることもで

50

きる。ゲート絶縁膜は、上述の材料を用いて、単層構造又は積層構造で形成する。また、ゲート絶縁膜 306a、306b の膜厚は、例えば、1 nm 以上 100 nm 以下、好ましくは 10 nm 以上 50 nm 以下とすることができます。

#### 【0096】

上述のように、ゲート絶縁膜を薄くすると、トンネル効果などに起因するゲートリークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁膜に、上述した hig h-k 材料を用いると良い。hig h-k 材料をゲート絶縁膜に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。なお、hig h-k 材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

10

#### 【0097】

本実施の形態では、熱酸化処理を用いて、酸化シリコン膜を形成することによって、ゲート絶縁膜 306a、306b を形成する。

#### 【0098】

次に、トランジスタのしきい値電圧を制御するために、n 型の導電性を付与する不純物元素、及び p 型の導電性を付与する不純物元素をゲート絶縁膜 306a、306b を介して半導体膜 304a、304b に添加する（図 6 (C) 参照）。半導体膜 304a、304b がシリコンの場合、n 型の導電性を付与する不純物元素としては、例えば、リンや砒素などを用いることができる。また、p 型の導電性を付与する不純物元素としては、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。本実施の形態では、ゲート絶縁膜 306a を介して半導体膜 304a に硼素を添加することで不純物領域 308 を形成し、ゲート絶縁膜 306b を介して半導体膜 304b にリンを添加することで不純物領域 310 を形成する。

20

#### 【0099】

次に、ゲート絶縁膜 306a、306b 上にゲート電極（これと同じ層で形成される配線を含む）を形成するための導電膜を形成し、当該導電膜を加工して、ゲート電極 312a、312b を形成する（図 6 (D) 参照）。

#### 【0100】

ゲート電極 312a、312b に用いる導電膜としては、アルミニウム、銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。導電膜の形成方法も特に限定されず、蒸着法、CVD 法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。また、導電膜の加工は、レジストマスクを用いたエッチングによって行うことができる。本実施の形態では、スパッタリング法を用いて、窒化タンタル膜とタングステン膜とを積層し、加工することによってゲート電極 312a、312b を形成する。

30

#### 【0101】

次に、ゲート電極 312a、312b をマスクとして、n 型の導電型を付与する不純物元素及び p 型の導電性を付与する不純物元素をゲート絶縁膜 306a、306b を介して半導体膜 304a、304b に添加する（図 6 (E) 参照）。本実施の形態では、ゲート絶縁膜 306a を介して半導体膜 304a にリンを添加することで不純物領域 314a、314b を形成し、ゲート絶縁膜 306b を介して半導体膜 304b に硼素を添加することで不純物領域 316a、316b を形成する。

40

#### 【0102】

次に、ゲート電極 312a、312b の側面にサイドウォール構造の側壁絶縁膜 318a～318d を形成する（図 7 (A) 参照）。側壁絶縁膜 318a～318d は、ゲート電極 312a、312b を覆う絶縁膜を形成した後、これを RIE (Reactive ion etching : 反応性イオンエッチング) 法による異方性のエッチングによって絶縁膜を加工し、ゲート電極 312a、312b の側壁に自己整合的にサイドウォール構造の側壁絶縁膜 318a～318d を形成すればよい。ここで、絶縁膜について特に限定

50

はないが、例えば、TEOS (Tetraethyl-Ortho-Silicate) 若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性のよい酸化シリコンを用いることができる。また、低温酸化 (LTO: Low Temperature Oxidation) 法により形成する酸化シリコンを用いてもよい。絶縁膜は熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD、スパッタリング等の方法によって形成することができる。

#### 【0103】

次に、ゲート電極312a、312b、及び側壁絶縁膜318a～318dをマスクとして、n型の導電型を付与する不純物元素、及びp型の導電性を付与する不純物元素をゲート絶縁膜306a、306bを介して半導体膜304a、304bに添加する（図7（B）参照）。本実施の形態では、ゲート絶縁膜306aを介して半導体膜304aにリンを添加することで不純物領域320a、320bを形成し、ゲート絶縁膜306bを介して半導体膜304bに硼素を添加することで不純物領域322a、322bを形成する。

#### 【0104】

以上により、酸化物半導体以外の半導体材料を含む基板300を用いて、nチャネル型トランジスタ330及びpチャネル型トランジスタ340を作製することができる（図7（B）参照）。このようなトランジスタは、高速動作が可能であるという特徴を有する。このため、トランジスタをトランジスタ103及びトランジスタ104などに用いることにより、これらの動作を高速化することができるため好適である。

#### 【0105】

次に、トランジスタ330及びトランジスタ340を覆うように、絶縁膜324を形成する（図7（C）参照）。絶縁膜324は、酸化シリコン、酸化窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。絶縁膜324として、誘電率の低い（low-k）材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することができるため好ましい。なお、絶縁膜324として、上述の材料を用いた多孔性の絶縁膜を適用してもよい。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する容量をさらに低減することが可能である。また、絶縁膜324として、ポリイミド、アクリル等の有機絶縁材料を用いて形成することもできる。本実施の形態では、酸化窒化シリコンを用いて絶縁膜324を形成する場合について説明する。

#### 【0106】

次に、絶縁膜324を形成した後、半導体膜304a、304bに添加された不純物元素を活性化するための熱処理を行う。熱処理はファーネスアニール炉を用いて行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法（RTA法）を適用することができる。熱処理は窒素雰囲気中で400～600℃、代表的には450～500℃で1～4時間として行う。この熱処理により、不純物元素の活性化と同時に絶縁膜324の酸化窒化シリコン膜の水素が放出され、半導体膜304a、304bの水素化を行うことができる。

#### 【0107】

なお、上記の各工程の前後には、さらに電極や配線、半導体膜、絶縁膜などを形成する工程も含んでいてもよい。例えば、下部のトランジスタと、上部のトランジスタを接続するための電極や配線などを形成することが好ましい。また、配線の構造として、絶縁膜及び導電層の積層構造でなる多層配線構造を採用して、高度に集積化した半導体装置を実現することも可能である。

#### 【0108】

##### 上部のトランジスタの作製方法

まず、トランジスタ410の作製前の処理として、絶縁膜324の表面を平坦化させる（図7（D）参照）。絶縁膜324の平坦化処理としては、化学的機械研磨（CMP: Chemical Mechanical Polishing、以下CMP処理という）などの研磨処理の他にエッチング処理、プラズマ処理などを用いることができる。

10

20

30

40

50

**【 0 1 0 9 】**

ここで、C M P処理とは、被加工物の表面を化学的・機械的な複合作用により平坦化する手法である。より具体的には、研磨ステージの上に研磨布を貼り付け、被加工物と研磨布との間にスラリー（研磨剤）を供給しながら研磨ステージと被加工物とを各々回転または揺動させて、スラリーと被加工物との化学反応と、研磨布の被加工物との機械研磨の作用により、被加工物の表面を研磨する方法である。

**【 0 1 1 0 】**

また、プラズマ処理としては、例えば、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことができる。逆スパッタリングとは、アルゴン雰囲気下で基板側にR F電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。逆スパッタリングを行うと、絶縁膜324の表面に付着している粉状物質（パーティクル、ごみともいう）を除去することができる。10

**【 0 1 1 1 】**

平坦化処理として、研磨処理、ドライエッティング処理、プラズマ処理は複数回行ってもよく、それらを組み合わせて行ってもよい。また、組み合わせて行う場合、工程順も特に限定されず、絶縁膜324表面の凹凸状態に合わせて適宜設定すればよい。

**【 0 1 1 2 】**

絶縁膜324に平坦化処理を行うことにより、絶縁膜324の表面の平均面粗さ（Ra）を、1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下とすることができます。Raとは、J I S B 0 6 0 1 : 2 0 0 1 ( I S O 4 2 8 7 : 1 9 9 7 )で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、下記の式にて定義される。20

**【 0 1 1 3 】****【 数 1 】**

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

30

**【 0 1 1 4 】**

ここで、指定面とは、粗さ計測の対象となる面であり、座標((x<sub>1</sub>, y<sub>1</sub>, f(x<sub>1</sub>, y<sub>1</sub>)), (x<sub>1</sub>, y<sub>2</sub>, f(x<sub>1</sub>, y<sub>2</sub>)), (x<sub>2</sub>, y<sub>1</sub>, f(x<sub>2</sub>, y<sub>1</sub>)), (x<sub>2</sub>, y<sub>2</sub>, f(x<sub>2</sub>, y<sub>2</sub>)))の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS<sub>0</sub>、基準面の高さ（指定面の平均の高さ）をZ<sub>0</sub>とする。Raは原子間力顕微鏡（AFM：A t o m i c F o r c e M i c r o s c o p e）にて測定可能である。

**【 0 1 1 5 】**

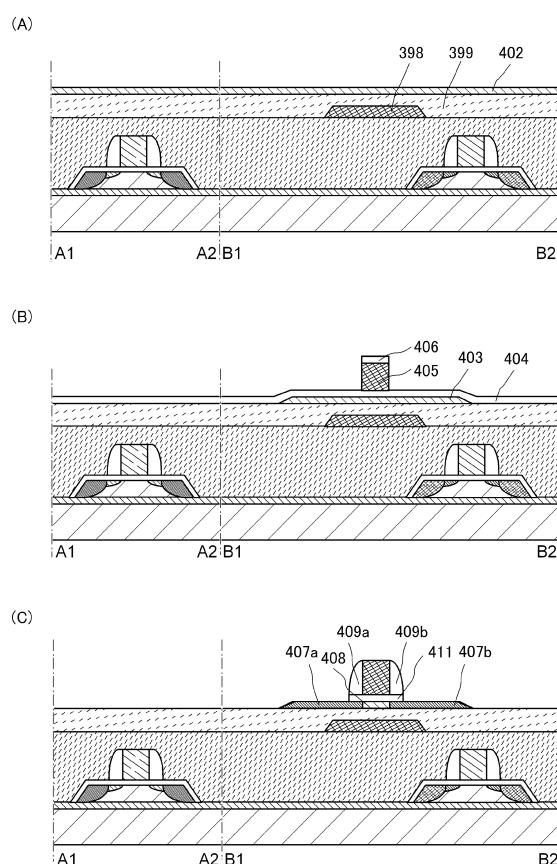

次に、平坦化された絶縁膜324上にゲート電極（これと同じ層で形成される配線を含む）を形成するための導電膜を形成し、当該導電膜を加工して、ゲート電極398を形成する。なお、ゲート電極398は、第2のゲート電極として機能する。40

**【 0 1 1 6 】**

ゲート電極398の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極398としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極398は、単層構造または積層構造で成膜される。

**【 0 1 1 7 】**

50

また、ゲート電極 398 の材料は、酸化インジウム酸化スズ、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

#### 【0118】

次に、絶縁膜 324 及びゲート電極 398 上に、絶縁膜 399 を形成する。絶縁膜 399 としては、プラズマ CVD 法またはスパッタリング法により、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウムなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いて単層構造または積層構造で形成することができる。

10

#### 【0119】

絶縁膜 399（積層構造の場合は、後に形成される酸化物半導体膜 402 と接する膜）の膜中（バルク中）には少なくとも化学量論的組成を超える量の酸素が存在することが好ましい。例えば、絶縁膜 399 として、酸化シリコン膜を用いる場合には、酸素の量を  $\text{SiO}_{2+\delta}$ （ただし、 $\delta > 0$ ）とすることが好ましい。絶縁膜 399 を形成した後、絶縁膜 399 に酸素を導入することで、酸素を多く含む絶縁膜 399 を形成することができる。

#### 【0120】

酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。

20

#### 【0121】

酸化物半導体膜は、成膜中や、その後の加熱処理、加工において、酸素欠損が形成される場合がある。酸化物半導体膜中に酸素欠損が形成されると、多数キャリアが形成され、トランジスタのしきい値電圧をマイナスシフトさせてしまうという問題が生じる。よって、酸化物半導体膜に酸素欠損を低減させる処理を行うことが好ましい。

#### 【0122】

例えば、酸素の供給源となる酸素を多く（過剰に）含む絶縁膜 399 を後に形成される酸化物半導体膜 402 と接して設けることによって、絶縁膜 399 から酸化物半導体膜 402 へ酸素を供給させる。また、酸化物半導体膜 402 と、絶縁膜 399 の少なくとも一部とが接した状態で加熱処理を行うことによって酸化物半導体膜 402 への酸素の供給を行ってもよい。酸素を多く含む絶縁膜 399 を用いることにより、酸化物半導体膜 402 に酸素を供給することができるため、酸化物半導体膜 402 の酸素欠損を低減することができる。これにより、多数キャリアの形成を抑制することができる。

30

#### 【0123】

本実施の形態では、絶縁膜 399 として、スパッタリング法により、膜厚 300 nm の酸化シリコン膜を形成する。

#### 【0124】

ここで、後に形成される酸化物半導体膜 402 表面の平坦性を高めるために、絶縁膜 399 において、酸化物半導体膜 402 が接して形成される領域に、平坦化処理を行うことが好ましい。平坦化処理としては、絶縁膜 324 で行った平坦化処理と同様に行うことができる。絶縁膜 399 の平坦化処理を行うことによって、絶縁膜 399 表面の平均面粗さ（Ra）を 1 nm 以下、好ましくは 0.3 nm 以下、より好ましくは 0.1 nm 以下とすることが好ましい。

40

#### 【0125】

次に、絶縁膜 399 上に酸化物半導体膜 402 を形成する（図 8（A）参照）。

#### 【0126】

酸化物半導体膜 402 に用いる酸化物半導体としては、少なくともインジウム（In）を含む。特にインジウム（In）と亜鉛（Zn）を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、

50

それらに加えてガリウム (Ga) を有することが好ましい。また、スタビライザーとしてスズ (Sn)、ハフニウム (Hf)、アルミニウム (Al)、ジルコニウム (Zr) のいずれか一種または複数種を有することが好ましい。

#### 【0127】

また、他のスタビライザーとして、ランタノイドである、ラントン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) のいずれか一種あるいは複数種を有してもよい。

#### 【0128】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物 (IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

10

#### 【0129】

例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0130】

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

30

#### 【0131】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Ga : Zn = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ )、あるいは $In : Ga : Zn = 3 : 1 : 2$  ( $= 1/2 : 1/6 : 1/3$ ) の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1/3 : 1/6 : 1/2$ ) あるいは $In : Sn : Zn = 2 : 1 : 5$  ( $= 1/4 : 1/8 : 5/8$ ) の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0132】

40

しかし、インジウムを含む酸化物半導体は、これらに限られず、必要とする半導体特性 (移動度、しきい値、ばらつき等) に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0133】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低くすることにより移動度を上げることができる。

#### 【0134】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c$  ( $a + b +$

50

$c = 1$  ) である酸化物の組成が、原子数比が  $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$  ) の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$  が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことをいい、 $r$  としては、例えば、0.05 とすればよい。他の酸化物でも同様である。

#### 【0135】

酸化物半導体膜 402 は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

#### 【0136】

好ましくは、酸化物半導体膜 402 は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

10

#### 【0137】

CAAC-OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS 膜は、非晶質相に結晶部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像では、CAAC-OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって CAAC-OS 膜には粒界(グレインバウンダーともいう。)は確認できない。そのため、CAAC-OS 膜は、粒界に起因する電子移動度の低下が抑制される。

#### 【0138】

20

CAAC-OS 膜に含まれる結晶部は、 $c$  軸が CAAC-OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ  $a$   $b$  面に垂直な方向から見て三角形状または六角形状の原子配列を有し、 $c$  軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ  $a$  軸および  $b$  軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上 95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上 5°以下の範囲も含まれることとする。

#### 【0139】

30

なお、CAAC-OS 膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【0140】

CAAC-OS 膜に含まれる結晶部の  $c$  軸は、CAAC-OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS 膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部の  $c$  軸の方向は、CAAC-OS 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

40

#### 【0141】

CAAC-OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性を高くすることができる。

#### 【0142】

なお、酸化物半導体膜を構成する酸素の一部は窒素で置換されてもよい。

#### 【0143】

また、CAAC-OS のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ( $R_a$ )が 1 nm 以下、好ましくは 0

50

. 3 nm 以下、より好ましくは 0 . 1 nm 以下の表面上に形成するとよい。

**【 0 1 4 4 】**

酸化物半導体膜 402 の膜厚は、1 nm 以上 30 nm 以下（好ましくは 5 nm 以上 10 nm 以下）とし、スパッタリング法、MBE (Molecular Beam Epitaxy) 法、プラズマ CVD 法、パルスレーザ堆積法、ALD (Atomic Layer Deposition) 法等を適宜用いることができる。また、酸化物半導体膜 402 は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

**【 0 1 4 5 】**

また、酸化物半導体膜 402 に含まれる水素又は水の濃度は、できる限り低いことが好ましい。水素濃度が高いと、酸化物半導体に含まれる元素と水素との結合により、水素の一部がドナーとなり、キャリアである電子が生じてしまうためである。10

**【 0 1 4 6 】**

したがって、酸化物半導体膜 402 の形成工程において、酸化物半導体膜 402 に水素、又は水がなるべく含まれないようにするために、酸化物半導体膜 402 の成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜 399 が形成された基板を予備加熱し、基板及び絶縁膜 399 に吸着した水素、水分などの不純物を脱離させ、排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。

**【 0 1 4 7 】**

なお、酸化物半導体膜 402 は、成膜時に酸素が多く含まれるような条件（例えば、酸素 100 % の雰囲気下でスパッタリング法により成膜を行うなど）で成膜して、酸素を多く含む（好ましくは酸化物半導体が結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている）膜とすることが好ましい。20

**【 0 1 4 8 】**

本実施の形態において、酸化物半導体膜 402 として、DC 電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚 10 nm の In - Ga - Zn 系酸化物膜 (IGZO 膜) を成膜する。本実施の形態において、In : Ga : Zn = 3 : 1 : 2 の原子比の In - Ga - Zn 系酸化物ターゲットを用いる。

**【 0 1 4 9 】**

酸化物半導体膜 402 を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。30

**【 0 1 5 0 】**

減圧状態に保持された成膜室内に基板を保持する。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて絶縁膜 399 上に酸化物半導体膜 402 を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜 402 に含まれる水素、水、水酸基又は水素化物などの不純物の濃度を低減できる。40

**【 0 1 5 1 】**

また、絶縁膜 399 を大気に解放せずに絶縁膜 399 と酸化物半導体膜 402 を連続的に形成することが好ましい。絶縁膜 399 を大気に曝露せずに絶縁膜 399 と酸化物半導体膜 402 を連続して形成すると、絶縁膜 399 表面に水素や水分などの不純物が吸着することを防止することができる。

**【 0 1 5 2 】**

次に、フォトリソグラフィ工程により酸化物半導体膜上にレジストマスクを形成し、選択的にエッチングを行って島状の酸化物半導体膜 403 を形成する。島状の酸化物半導体膜 403 を形成した後、レジストマスクを除去する。50

**【 0 1 5 3 】**

また、島状の酸化物半導体膜403を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

**【 0 1 5 4 】**

なお、酸化物半導体膜402のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。例えば、酸化物半導体膜402のウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO-07N(関東化学社製)を用いてもよい。また、ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッティング法によるドライエッティングによってエッティング加工してもよい。10

**【 0 1 5 5 】**

また、酸化物半導体膜403に、過剰な水素(水や水酸基を含む)を除去(脱水化または脱水素化)するための加熱処理を行ってもよい。加熱処理の温度は、300以上700以下、または基板の歪み点未満とする。加熱処理は減圧下又は窒素雰囲気下などで行うことができる。

**【 0 1 5 6 】**

また、酸化物半導体膜403として結晶性酸化物半導体膜を用いる場合、結晶化のための加熱処理を行ってもよい。

**【 0 1 5 7 】**

本実施の形態では、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜403に対して窒素雰囲気下450において1時間、さらに窒素及び酸素雰囲気下450において1時間の加熱処理を行う。20

**【 0 1 5 8 】**

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、LRTA(Lamp Rapid Thermal Anneal)装置、GRTA(Gas Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。30

**【 0 1 5 9 】**

例えば、加熱処理として、650～700の高温に加熱した不活性ガス中に基板を入れ、数分間加熱した後、基板を不活性ガス中から出すGRTAを行ってもよい。

**【 0 1 6 0 】**

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。40

**【 0 1 6 1 】**

また、加熱処理で酸化物半導体膜403を加熱した後、同じ炉に高純度の酸素ガス、高純度の一酸化二窒素ガス、又は超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気)を導入してもよい。酸素ガスまたは一酸化二窒素ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する酸素ガスまたは一酸化二窒素ガスの純度を、6N以上好まし50

くは 7 N 以上（即ち、酸素ガスまたは一酸化二窒素ガス中の不純物濃度を 1 p p m 以下、好ましくは 0 . 1 p p m 以下）とすることが好ましい。酸素ガス又は一酸化二窒素ガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体膜 403 の酸素欠損を低減することができる。

#### 【 0162 】

なお、脱水化又は脱水素化のための加熱処理を行うタイミングは、膜状の酸化物半導体膜 402 の形成後でも、島状の酸化物半導体膜 403 形成後でもよい。

#### 【 0163 】

また、脱水化又は脱水素化のための加熱処理は、複数回行ってもよく、他の加熱処理と兼ねてもよい。10

#### 【 0164 】

脱水化又は脱水素化のための加熱処理を、酸化物半導体膜 403 として島状に加工される前、膜状の酸化物半導体膜 402 が絶縁膜 399 を覆った状態で行うと、絶縁膜 399 に含まれる酸素が加熱処理によって外部に放出されてしまうことを防止できる。

#### 【 0165 】

また、脱水化又は脱水素化のための加熱処理を行った後に、酸化物半導体膜に、酸素を導入する工程を行ってもよい。酸化物半導体膜に酸素を導入することにより、加熱処理により酸化物半導体膜から放出された酸素を補填することができるため、酸化物半導体膜に含まれる酸素欠損を低減することができる。20

#### 【 0166 】

酸素の導入工程は、酸化物半導体膜 403 に直接導入してもよいし、後に形成されるゲート絶縁膜などの他の膜を透過させて酸化物半導体膜 403 へ導入してもよい。酸素を他の膜を透過させて導入する場合は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いればよい。また、露出された酸化物半導体膜へ直接導入する場合は、プラズマ処理なども用いることができる。

#### 【 0167 】

次に、絶縁膜 399 及び酸化物半導体膜 403 上に、後にゲート絶縁膜となる絶縁膜 404 を形成する。

#### 【 0168 】

なお、絶縁膜 404 の被覆性を向上させるために、酸化物半導体膜 403 表面に平坦化処理を行ってもよい。特に、絶縁膜 404 として膜厚の薄い絶縁膜を用いる場合、酸化物半導体膜 403 表面の平坦性が良好であることが好ましい。30

#### 【 0169 】

絶縁膜 404 の膜厚は、1 nm 以上 20 nm 以下とし、スパッタリング法、MBE 法、プラズマ CVD 法、パルスレーザ堆積法、ALD 法等を適宜用いることができる。また、絶縁膜 404 は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

#### 【 0170 】

絶縁膜 404 の材料としては、酸化シリコン、酸化ガリウム、酸化アルミニウム、窒化シリコン、酸化窒化シリコン、酸化窒化アルミニウム、または窒化酸化シリコンを用いて形成することができる。また、絶縁膜 404 の材料として酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSiO_xN_y$  ( $x > 0$ ,  $y > 0$ ))、ハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、酸化ランタンなどの h i g h - k 材料を用いることでゲートリーキ電流を低減できる。また、絶縁膜 404 は、上記の材料を用いて、単層構造または積層構造で形成することができる。40

#### 【 0171 】

本実施の形態では、プラズマ CVD 法により、酸化窒化シリコン膜を 20 nm 形成する。

#### 【 0172 】

次に、絶縁膜404上に、ゲート電極（これと同じ層で形成される配線を含む）となる導電膜を形成した後、絶縁膜を形成する。その後、フォトリソグラフィ工程により該絶縁膜上にレジストマスクを形成し、選択的にエッチングを行ってゲート電極405及び絶縁膜406を積層して形成する（図8（B）参照）。

#### 【0173】

ゲート電極405の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極405としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極405は、単層構造または積層構造で成膜される<sup>10</sup>。

#### 【0174】

また、ゲート電極405の材料は、酸化インジウム酸化スズ、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

#### 【0175】

また、絶縁膜404と接するゲート電極405として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Ga-O膜や、窒素を含むIn-Sn-O膜や、窒素を含むIn-Ga-O膜や、窒素を含むIn-Zn-O膜や、窒素を含むSn-O膜や、窒素を含むIn-O膜や、金属窒化膜（InN、SnNなど）を用いることができる。これらの膜は、5eV（電子ボルト）、好ましくは5.5eV（電子ボルト）以上の仕事関数を有するため、ゲート電極として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

#### 【0176】

また、絶縁膜406は、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化シリコン、窒化アルミニウム、窒化酸化シリコン、窒化酸化アルミニウムなどの無機絶縁材料を用いることができる。絶縁膜406は、プラズマCVD法又はスパッタリング法などを用いて形成することができる。<sup>30</sup>

#### 【0177】

次に、ゲート電極405及び絶縁膜406をマスクとして、絶縁膜404を介して、酸化物半導体膜403にドーパントを添加し、ドーパントを含む領域407a、407bを形成する。

#### 【0178】

ドーパントは、酸化物半導体膜403の導電率を変化させる元素を用いる。ドーパントとしては、15族元素（例えば、窒素（N）、リン（P）、砒素（As）、及びアンチモン（Sb））、ホウ素（B）、アルミニウム（Al）、アルゴン（Ar）、ヘリウム（He）、ネオン（Ne）、インジウム（In）、フッ素（F）、塩素（Cl）、チタン（Ti）、及び亜鉛（Zn）のいずれかから選択される一又は複数を用いる。<sup>40</sup>

#### 【0179】

ドーパントは、添加方法により、他の膜（本実施の形態では、絶縁膜404）を通過して、酸化物半導体膜403に添加することもできる。ドーパントの添加方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。その際には、ドーパントの単体のイオンあるいはフッ化物、塩化物のイオンを用いると好ましい。

#### 【0180】

ドーパントの導入工程は、加速電圧、ドーズ量などの注入条件、また通過させる膜の膜厚を適宜設定して制御すればよい。本実施の形態では、ドーパントとしてリンを用いて、イオン注入法でリンイオンの注入を行う。なお、ドーパントのドーズ量は $1 \times 10^{-3}$  i o<sup>50</sup>

$\text{n s} / \text{cm}^2$  以上  $5 \times 10^{16}$  ions /  $\text{cm}^2$  以下とすればよい。

【0181】

酸化物半導体膜403にドーパントを添加することにより、ドーパントを含む領域407a、407bのドーパントの濃度が、 $5 \times 10^{18} / \text{cm}^3$  以上  $1 \times 10^{22} / \text{cm}^3$  以下となることが好ましい。

【0182】

酸化物半導体膜403にドーパントを添加する際に、基板を加熱しながら行ってもよい。また、酸化物半導体膜403にドーパントを導入する処理は、複数回行ってもよく、ドーパントの種類も複数種用いててもよい。

【0183】

また、ドーパントの添加後、加熱処理を行ってもよい。加熱条件としては、温度300以上700以下、好ましくは300以上450以下で1時間、酸素雰囲気下で行うことが好ましい。また、窒素雰囲気下、減圧下、大気（超乾燥エア）下で加熱処理を行ってもよい。

【0184】

本実施の形態では、イオン注入法により酸化物半導体膜403に、リン（P）イオンを注入する。なお、リン（P）イオンの注入条件は加速電圧25kV、ドーズ量を $1.0 \times 10^{15}$  ions /  $\text{cm}^2$  とする。

【0185】

酸化物半導体膜403をCAC-OS膜とした場合、ドーパントの添加により、一部非晶質化する場合がある。この場合、ドーパントの導入後に加熱処理を行うことによって、酸化物半導体膜403の結晶性を回復することができる。

【0186】

ドーパントの添加工程により、チャネル形成領域408を挟んでドーパントを含む領域407a、407bが設けられた酸化物半導体膜403が形成される。

【0187】

次に、ゲート電極405及び絶縁膜406上に絶縁膜を形成し、該絶縁膜をエッチングしてサイドウォール絶縁膜409a、409bを形成する。さらに、ゲート電極405及びサイドウォール絶縁膜409a、409bをマスクとして、絶縁膜404をエッチングし、ゲート絶縁膜411を形成する（図8（C）参照）。

【0188】

サイドウォール絶縁膜409a、409bは、絶縁膜406と同様な材料及び方法を用いて形成することができる。本実施の形態では、サイドウォール絶縁膜409a、409bとして、CVD法により形成された酸化窒化シリコン膜を用いる。

【0189】

次に、酸化物半導体膜403、ゲート絶縁膜411、サイドウォール絶縁膜409a、409b、及び絶縁膜406を覆うように、後にソース電極及びドレイン電極（これと同じ層で形成される配線を含む）となる導電膜を形成する。

【0190】

ソース電極及びドレイン電極となる導電膜は、例えば、アルミニウム（Al）、クロム（Cr）、銅（Cu）、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タンクスチタン（W）から選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜）などを用いて形成することができる。また、アルミニウム、銅などの金属膜の下側及び上側の少なくとも一方に、チタン、モリブデン、タンクスチタンなどの高融点金属膜またはそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜）を積層させた構成としてもよい。

【0191】

また、ソース電極及びドレイン電極となる導電膜として、導電性の金属酸化物を用いて形成することもできる。導電性の金属酸化物として、酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化インジウム酸化スズ（In<sub>2</sub>O<sub>3</sub> - SnO<sub>2</sub>）

10

20

30

40

50

<sub>2</sub>、ITOと略記する)、酸化インジウム酸化亜鉛(Indium oxide - Zinc oxide)又はこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。また、上記導電性材料と、上記金属酸化物材料の積層構造とすることもできる。

【0192】

次に、導電膜上に、フォトリソグラフィ工程によりレジストマスクを形成し、導電膜に選択的にエッチングを行うことより、ソース電極及びドレイン電極のチャネル幅W方向の加工を行う。

【0193】

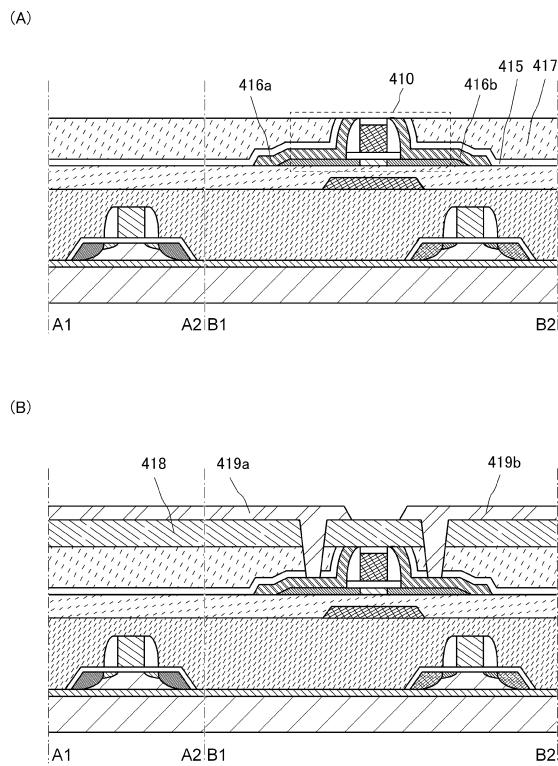

次に、導電膜上に、絶縁膜415及び絶縁膜417を形成する。

【0194】

絶縁膜415及び絶縁膜417は、スパッタリング法などにより、水素などの不純物を混入させない方法を適宜用いて形成する。

10

【0195】

絶縁膜415及び絶縁膜417は、代表的には酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、又は酸化ガリウム、窒化シリコン、窒化アルミニウム、窒化酸化シリコン、窒化酸化アルミニウムなどの無機絶縁膜を用いることができる。

【0196】

絶縁膜415として、ソース電極416a、ドレイン電極416bに接して緻密性の高い無機絶縁膜を設けるとよい。例えば、ソース電極416a、ドレイン電極416b上にスパッタリング法により酸化アルミニウム膜を形成する。酸化アルミニウム膜を高密度(膜密度3.2g/cm<sup>3</sup>以上、好ましくは3.6g/cm<sup>3</sup>以上)とすることによって、トランジスタ410に安定な電気特性を付与することができる。膜密度はラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)や、X線反射率測定法(XRR: X-Ray Reflection)によって測定することができる。

20

【0197】

トランジスタ410上に設けられる無機絶縁膜として用いることのできる酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ロック効果)が高い。

30

【0198】

従って、酸化アルミニウム膜は、トランジスタ作製工程中及び作製後において、トランジスタの電気特性の変動要因となる水素、水分などの不純物の酸化物半導体膜403への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜403からの放出を防止する保護膜として機能する。

【0199】

次に、絶縁膜415、絶縁膜417、及び導電膜に、絶縁膜406が露出するまで、研磨処理を行う。これにより、絶縁膜415、絶縁膜417、及び導電膜の一部を除去することで、ソース電極416a及びドレイン電極416bを形成する。

【0200】

40

研磨処理として、化学的機械研磨(Chemical Mechanical Polishing: CMP)法を用いることができるが、他の切削(研削、研磨)方法を用いてもよい。また、研磨処理を行った後、ドライエッチング法やプラズマ処理(逆プラズマ処理)などを行うことにより、研磨処理表面の平坦化を向上させることができる。

【0201】

本実施の形態では、ゲート電極405上に絶縁膜406が設けられているため、絶縁膜415、絶縁膜417、及び導電膜に研磨処理を行っても、ゲート電極405と、ソース電極416a、ドレイン電極416bとがショートしてしまうことを抑制できる。

【0202】

以上の工程で、本発明の一態様に係るトランジスタ410が作製される(図9(A)参照)

50

)。

### 【0203】

次に、トランジスタ410を覆うように絶縁膜418を形成する。絶縁膜418は、絶縁膜415、絶縁膜417の材料や方法を用いて形成することができるため、詳細な説明は省略する。

### 【0204】

次に、絶縁膜418上に配線419a、419bを形成する。配線419a、419bはトランジスタ410と他のトランジスタを接続するために設けられる。配線419aは、絶縁膜415、絶縁膜417、及び絶縁膜418に形成された開口を介してソース電極416aと電気的に接続される。また、配線419bは、絶縁膜418、絶縁膜415、及び絶縁膜417に形成された開口を介してドレイン電極416bと電気的に接続される。

10

### 【0205】

配線419a及び配線419bはゲート電極405と同様の材料及び方法を用いて形成することができるため、詳細な説明は省略する。

### 【0206】

例えば、配線419a及び配線419bとして、モリブデン膜の単層、窒化タンタル膜と銅膜との積層、又は窒化タンタル膜とタンゲステン膜との積層などを用いることができる。

。

### 【0207】

以上の工程で、本発明の一態様に係るレベルシフト回路を作製することができる。

20

### 【0208】

本実施の形態に示す作製方法によれば、シリコンなどの単結晶半導体膜を用いたトランジスタに積層して、酸化物半導体などの半導体膜を用いたトランジスタを形成することができる。これにより、レベルシフト回路を構成するトランジスタの一部を積層構造とすることができますため、レベルシフト回路面積の縮小化を図ることができる。

### 【0209】

また、本実施の形態に示す作製方法によれば、酸化物半導体膜に含まれる水素などの不純物が十分に除去され、または、十分な酸素が供給されて酸素が過飽和の状態とされることにより、高純度化されたものとすることができる。具体的には、酸化物半導体膜の水素濃度は $5 \times 10^{19}$  atoms / cm<sup>3</sup>以下、望ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より望ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。なお、上述の酸化物半導体膜中の水素濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)で測定されるものである。また、酸化物半導体膜に酸素が十分に供給され、酸素欠損が低減されることで、多数キャリアの増加が抑制される。これにより、多数キャリアの増加によるトランジスタのしきい値電圧の変動を抑制することができるため、トランジスタの信頼性を向上させることができる。

30

### 【0210】

以上のことから、酸化物半導体膜403の多数キャリア(電子)は、トランジスタのソースから流れるのみとなる。また、チャネル形成領域を完全空乏化することができるため、トランジスタのオフ電流を極めて小さくすることが可能である。酸化物半導体膜403を用いたトランジスタのオフ電流は、室温において、10 yA / μm以下、85 ~ 95においても、1 zA / μm以下となり、極めて小さい。

40

### 【0211】

したがって、酸化物半導体膜403を用いたトランジスタは、S値が小さくなり、理想的な値が得られる。また、当該トランジスタは、信頼性が高い。

### 【0212】

よって、本実施の形態に示すトランジスタ410は、第2のゲート電極に印加される電位によって、しきい値電圧を容易に制御することができる。このようなトランジスタ410を用いてレベルシフト回路を構成することで、レベルシフト回路から出力される信号の振幅を容易に制御することができる。

50

**【0213】**

なお、本実施の形態では、レベルシフト回路を構成するトランジスタの説明を行ったが、本実施の形態に示す作製方法を適用して、レベルシフト回路だけでなく、半導体集積回路に含まれる他の回路を作製することも可能である。例えば、上部の酸化物半導体膜403を用いたトランジスタ410は、上述のようにオフ電流が極めて低いため、これを利用して、不揮発性のメモリセルアレイを構成することができる。不揮発性のメモリセルアレイの詳細については、実施の形態3で説明する。このようなメモリセルアレイと、レベルシフト回路に含まれるトランジスタとを上部に形成し、メモリ回路を駆動するための周辺回路と、レベルシフト回路に含まれるインバータ回路とを下部に形成することで、半導体集積回路の小型化を図ることができる。

10

**【0214】**

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0215】****(実施の形態3)**

本実施の形態においては、実施の形態2に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い記憶装置について、図10及び図11を用いて説明を行う。

**【0216】**

本実施の形態に示す記憶装置は、実施の形態2に示すレベルシフト回路を構成するトランジスタと同時に作製することができる。

20

**【0217】**

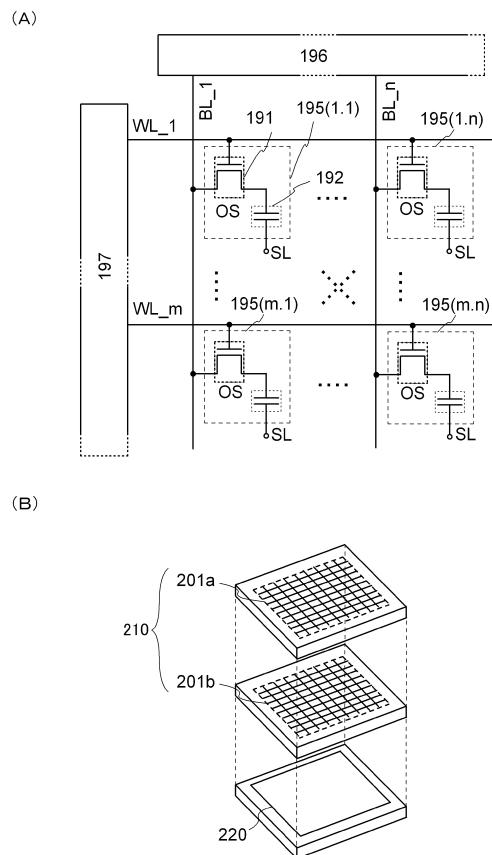

図10(A)は、記憶装置の回路構成の一例を示し、図10(B)は記憶装置の一例を示す概念図である。まず、図10(A)に示す装置について説明を行い、続けて図10(B)に示す半導体装置について、以下説明を行う。

**【0218】**

図10に示す記憶装置は、n本のビット線BLと、m本のワード線WLと、メモリセル195が縦m個(行)×横n個(列)のマトリクス状に配置されたメモリセルアレイと、n本のビット線BLに接続する第1の駆動回路196と、m本のワード線WLに接続する第2の駆動回路197と、を有する。

30

**【0219】**

メモリセル195は、トランジスタ191及び容量素子192を有する。ビット線BLは、トランジスタ191のソース電極又はドレイン電極と電気的に接続され、ワード線WLは、トランジスタ191のゲート電極と電気的に接続され、トランジスタ191のソース電極又はドレイン電極と容量素子192の第1の端子とは電気的に接続されている。

**【0220】**

次に、図10(A)に示す半導体装置(メモリセル195)に、情報の書き込みおよび保持を行う場合について説明する。

**【0221】**

まず、ワード線WLの電位を、トランジスタ191がオン状態となる電位として、トランジスタ191をオン状態とする。これにより、ビット線BLの電位が、容量素子192の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ191がオフ状態となる電位として、トランジスタ191をオフ状態とすることにより、容量素子192の第1の端子の電位が保持される(保持)。

40

**【0222】**

酸化物半導体を用いたトランジスタ191は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ191をオフ状態とすることで、容量素子192の第1の端子の電位(あるいは、容量素子192に蓄積された電荷)を極めて長時間にわたって保持することが可能である。

**【0223】**

50

次に、情報の読み出しについて説明する。トランジスタ191がオン状態となると、浮遊状態であるビット線BLと容量素子192とが導通し、ビット線BLと容量素子192の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子192の第1の端子の電位（あるいは容量素子192に蓄積された電荷）によって、異なる値をとる。

#### 【0224】

例えば、容量素子192の第1の端子の電位をV、容量素子192の容量をC、ビット線BLが有する容量成分（以下、ビット線容量とも呼ぶ）をCB、電荷が再分配される前のビット線BLの電位をVB0とすると、電荷が再分配された後のビット線BLの電位は、 $(CB \times VB_0 + C \times V) / (CB + C)$ となる。従って、メモリセル195の状態として、容量素子192の第1の端子の電位がV1とV0 ( $V_1 > V_0$ )の2状態をとるとすると、電位V1を保持している場合のビット線BLの電位 ( $= (CB \times VB_0 + C \times V_1) / (CB + C)$ )は、電位V0を保持している場合のビット線BLの電位 ( $= (CB \times VB_0 + C \times V_0) / (CB + C)$ )よりも高くなることがわかる。10

#### 【0225】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

#### 【0226】

このように、図10(A)に示す半導体装置は、トランジスタ191のオフ電流が極めて小さいという特徴から、容量素子192に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。20

#### 【0227】

次に、図10(B)に示す半導体装置について、説明を行う。

#### 【0228】

図10(B)に示す半導体装置は、上部に記憶回路として図10(A)に示したメモリセル195を複数有するメモリセルアレイ201a及び201bを有し、下部に、メモリセルアレイ210（メモリセルアレイ201a及び201b）を動作させるために必要な周辺回路220を有する。なお、周辺回路220は、メモリセルアレイ201a、メモリセルアレイ201bとそれぞれ電気的に接続されている。30

#### 【0229】

図10(B)に示した構成とすることにより、周辺回路220をメモリセルアレイ210（メモリセルアレイ201a及び201b）の真下に設けることができるため半導体装置の小型化を図ることができる。

#### 【0230】

周辺回路220に設けられるトランジスタは、トランジスタ191とは異なる半導体材料を用いることがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、該トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することができる。周辺回路220に設けられるトランジスタについては、実施の形態2におけるトランジスタ330及び340の記載を参照できる。40

#### 【0231】

なお、図10(B)に示した半導体装置では、2つのメモリセルアレイ210（メモリセルアレイ201aと、メモリセルアレイ201b）が積層された構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としても良い。50

**【0232】**

次に、図10(A)に示したメモリセル195の具体的な構成について図11を用いて説明を行う。

**【0233】**

図11は、メモリセル195の構成の一例である。図11(A)に、メモリセル195の断面図を、図11(B)にメモリセル195の平面図をそれぞれ示す。ここで、図11(A)は、図11(B)のC1-C2における断面に相当する。

**【0234】**

図11(A)及び図11(B)に示すトランジスタ191は、実施の形態2で示したトランジスタ410と同様の構成とすることができるため、詳細な説明は省略する。

10

**【0235】**

また、容量素子192は、絶縁膜421上に、電極422を形成することにより、形成される。電極422の材料や方法については、配線419a、419bの記載を参照することができる。

**【0236】**

図11に示すメモリセル195は、実施の形態2に示すトランジスタ410に配線419a、419bを形成した後、絶縁膜421を形成し、電極422を形成するのみで、容量素子192を形成することができる。よって、レベルシフト回路に用いるトランジスタ410と、メモリセルに用いるトランジスタとを作り分ける必要はない。

**【0237】**

なお、メモリセルアレイを積層構造とする場合には、絶縁膜421及び電極422上にさらに絶縁膜を形成し、該絶縁膜上にトランジスタ191と同様の酸化物半導体を用いたトランジスタを形成すればよい。

20

**【0238】**

また、図11(B)に示す平面レイアウトを採用することにより、半導体装置の占有面積の低減を図ることができるため、高集積化を図ることができる。

**【0239】**

以上のように、多層に形成された複数のメモリセルは、酸化物半導体を用いたトランジスタにより形成されている。酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。

30

**【0240】**

このように、酸化物半導体以外の材料を用いたトランジスタ（換言すると、十分な高速動作が可能なトランジスタ）を用いた周辺回路と、酸化物半導体を用いたトランジスタ（より広義には、十分にオフ電流が小さいトランジスタ）を用いた記憶装置とを一体に備えた半導体装置を実現することができる。

**【0241】**

また、メモリセルアレイと、レベルシフト回路に含まれるトランジスタとを上部に形成し、メモリセルアレイを駆動するための周辺回路と、レベルシフト回路に含まれるインバータ回路とを下部に形成することで、半導体集積回路の小型化を図ることができる。

40

**【0242】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

**【0243】****(実施の形態4)**

本実施の形態では、先の実施の形態で示したレベルシフト回路及びメモリ回路を用いて半導体集積回路を構成し、携帯電話、スマートフォン、電子書籍などの携帯機器に応用した場合の例を図12及び図13を用いて説明する。

**【0244】**

50

図12に携帯機器のブロック図を示す。図12に示す携帯機器はRF回路901、アナログベースバンド回路902、デジタルベースバンド回路903、バッテリー904、電源回路905、マイクロプロセッサ906、フラッシュメモリ910、ディスプレイコントローラ911、メモリ回路912、ディスプレイ913、タッチセンサ919、音声回路917、キーボード918などより構成されている。ディスプレイ913は表示部914、ソースドライバ915、ゲートドライバ916によって構成されている。マイクロプロセッサ906はCPU907、DSP908、インターフェイス909(IF909)を有している。なお、マイクロプロセッサ906、フラッシュメモリ910、メモリ回路912、及びディスプレイコントローラ911は、1つのチップに組み込むことができる(図12中、点線参照)。

10

#### 【0245】

マイクロプロセッサ906は、レベルシフト回路921を介してフラッシュメモリ910と接続される。また、マイクロプロセッサ906は、レベルシフト回路922を介してメモリ回路912と接続される。また、メモリ回路912は、レベルシフト回路923を介してディスプレイコントローラ911と接続される。レベルシフト回路921～923はそれぞれ図1～図5で示したレベルシフト回路のいずれかを適用することができる。例えば、図2又は図3のレベルシフト回路を適用すれば、レベルシフト回路921乃至レベルシフト回路923は、個々に設ける必要はなく、いずれかを設けない構成とすることもできる。レベルシフト回路は、積層構造で形成することが可能であるため、レベルシフト回路面積の縮小化を図ることができる。よって、半導体集積回路の小型化を図ることができる。また、フラッシュメモリ910、メモリ回路912、ディスプレイコントローラ911を駆動するための最小限の電圧に、適宜設定することができるため、半導体集積回路の低消費電力化を図ることができる。

20

#### 【0246】

また、メモリ回路912に先の実施の形態で説明した記憶装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を十分に低減することができる。また、レベルシフト回路と同様に、積層構造で形成することができるため、メモリ回路912の回路面積の縮小化を図ることができる。よって、半導体集積回路の小型化を図ることができる。

#### 【0247】

30

図13に電子書籍のブロック図を示す。図13はバッテリー1001、電源回路1002、マイクロプロセッサ1003、フラッシュメモリ1004、音声回路1005、キーボード1006、メモリ回路1007、タッチパネル1008、ディスプレイ1009、ディスプレイコントローラ1010によって構成される。なお、マイクロプロセッサ1003、フラッシュメモリ1004、メモリ回路1007、及びディスプレイコントローラ1010は、1つのチップに組み込むことができる(図13中、点線参照)。

#### 【0248】

マイクロプロセッサ1003は、レベルシフト回路1021を介してフラッシュメモリ1004と接続される。また、マイクロプロセッサ1003は、レベルシフト回路1022を介してメモリ回路1007と接続される。また、マイクロプロセッサ1003は、レベルシフト回路1023を介してディスプレイコントローラ1010と接続される。レベルシフト回路1021～1023はそれぞれ図1～図5で示したレベルシフト回路のいずれかを適用することができる。例えば、図2又は図3のレベルシフト回路を適用すれば、レベルシフト回路1021乃至レベルシフト回路1023は、個々に設ける必要はなく、いずれかを設けない構成とすることもできる。レベルシフト回路は、積層構造で形成することができるため、レベルシフト回路面積の縮小化を図ることができる。よって、半導体集積回路の小型化を図ることができる。また、フラッシュメモリ1004、メモリ回路1007、ディスプレイコントローラ1010を駆動するための最小限の電圧に、適宜設定することができるため、半導体集積回路の低消費電力化を図ることができる。

40

#### 【0249】

50

また、メモリ回路 1007 に先の実施の形態で説明した記憶装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を十分に低減することができる。また、レベルシフト回路と同様に、積層構造で形成することができるため、メモリ回路 1007 の回路面積の縮小化を図ることができる。よって、半導体集積回路の小型化を図ることができる。

#### 【0250】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0251】

##### (実施の形態 5 )

10

本発明の一態様に係る半導体装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した半導体装置を具備する電子機器の例について説明する。

#### 【0252】

図 14 (A) は、ノート型のパーソナルコンピュータであり、本体 3001、筐体 3002、表示部 3003、キーボード 3004 などによって構成されている。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することができる。先の実施の形態に係る半導体集積回路を適用することにより、小型化されたノート型のパーソナルコンピュータとすることができます。

20

#### 【0253】

図 14 (B) は、携帯情報端末 (PDA) であり、本体 3021 には表示部 3023 と、外部インターフェイス 3025 と、操作ボタン 3024 等が設けられている。また操作用の付属品としてスタイラス 3022 がある。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することにより、小型化された携帯情報端末 (PDA) とすることができます。

30

#### 【0254】

図 14 (C) は、電子書籍の一例を示している。例えば、電子書籍 2700 は、筐体 2701 および筐体 2703 の 2 つの筐体で構成されている。筐体 2701 および筐体 2703 は、軸部 2711 により一体とされており、該軸部 2711 を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

#### 【0255】

筐体 2701 には表示部 2705 が組み込まれ、筐体 2703 には表示部 2707 が組み込まれている。表示部 2705 および表示部 2707 は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図 14 (C) では表示部 2705）に文章を表示し、左側の表示部（図 14 (C) では表示部 2707）に画像を表示することができる。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することができる。先の実施の形態に係る半導体集積回路を適用することにより、小型化された電子書籍 2700 とすることができます。

40

#### 【0256】

また、図 14 (C) では、筐体 2701 に操作部などを備えた例を示している。例えば、筐体 2701 において、電源 2721、操作キー 2723、スピーカー 2725 などを備えている。操作キー 2723 により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB 端子など）、記録媒体挿入部など

50

を備える構成としてもよい。さらに、電子書籍 2700 は、電子辞書としての機能を持たせた構成としてもよい。

#### 【0257】

また、電子書籍 2700 は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

#### 【0258】

図 14 (D) は、スマートフォンであり、筐体 2800 と、ボタン 2801 と、マイクロフォン 2802 と、タッチパネルを備えた表示部 2803 と、スピーカー 2804 と、カメラ用レンズ 2805 と、を具備し、携帯型電話機としての機能を有する。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することができる。先の実施の形態に係る半導体集積回路を適用することにより、小型化されたスマートフォンとすることができる。10

#### 【0259】

表示部 2803 は、使用形態に応じて表示の方向が適宜変化する。また、表示部 2803 と同一面上にカメラ用レンズ 2805 を備えているため、テレビ電話が可能である。スピーカー 2804 及びマイクロフォン 2802 は音声通話に限らず、テレビ電話、録音、再生などが可能である。

#### 【0260】

また、外部接続端子 2806 は A C アダプタ及び U S B ケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部メモリスロット（図示せず）に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。20

#### 【0261】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

#### 【0262】

図 14 (E) は、デジタルビデオカメラであり、本体 3051、表示部 (A) 3057、接眼部 3053、操作スイッチ 3054、表示部 (B) 3055、バッテリー 3056 などによって構成されている。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することができる。先の実施の形態に係る半導体集積回路を適用することにより、小型化されたデジタルビデオカメラとすることができます。30

#### 【0263】

図 14 (F) は、テレビジョン装置の一例を示している。テレビジョン装置 9600 は、筐体 9601 に表示部 9603 が組み込まれている。表示部 9603 により、映像を表示することが可能である。また、ここでは、スタンド 9605 により筐体 9601 を支持した構成を示している。また、図示しないが、本体内部にある半導体集積回路として先の実施の形態に係る半導体集積回路を適用することができる。先の実施の形態に係る半導体集積回路を適用することにより、小型化されたテレビジョン装置 9600 とすることができます。40

#### 【0264】

テレビジョン装置 9600 の操作は、筐体 9601 が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

#### 【0265】

なお、テレビジョン装置 9600 は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。50

## 【0266】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【符号の説明】

## 【0267】

|         |          |    |

|---------|----------|----|

| 1 0 1   | トランジスタ   |    |

| 1 0 2   | インバータ回路  |    |

| 1 0 3   | トランジスタ   |    |

| 1 0 4   | トランジスタ   |    |

| 1 0 5   | トランジスタ   | 10 |

| 1 0 6   | インバータ回路  |    |

| 1 0 7   | トランジスタ   |    |

| 1 0 8   | トランジスタ   |    |

| 1 0 9   | トランジスタ   |    |

| 1 9 1   | トランジスタ   |    |

| 1 9 2   | 容量素子     |    |

| 1 9 5   | メモリセル    |    |

| 1 9 6   | 駆動回路     |    |

| 1 9 7   | 駆動回路     |    |

| 2 0 1 a | メモリセルアレイ | 20 |

| 2 0 1 b | メモリセルアレイ |    |

| 2 1 0   | メモリセルアレイ |    |

| 2 2 0   | 周辺回路     |    |

| 3 0 0   | 基板       |    |

| 3 0 2   | 絶縁膜      |    |

| 3 0 4   | 半導体膜     |    |

| 3 0 4 a | 半導体膜     |    |

| 3 0 4 b | 半導体膜     |    |

| 3 0 6 a | ゲート絶縁膜   |    |

| 3 0 6 b | ゲート絶縁膜   | 30 |

| 3 0 8   | 不純物領域    |    |

| 3 1 0   | 不純物領域    |    |

| 3 1 2 a | ゲート電極    |    |

| 3 1 2 b | ゲート電極    |    |

| 3 1 4 a | 不純物領域    |    |

| 3 1 4 b | 不純物領域    |    |

| 3 1 6 a | 不純物領域    |    |

| 3 1 6 b | 不純物領域    |    |

| 3 1 8 a | 側壁絶縁膜    |    |

| 3 1 8 d | 側壁絶縁膜    | 40 |

| 3 2 0 a | 不純物領域    |    |

| 3 2 0 b | 不純物領域    |    |

| 3 2 2 a | 不純物領域    |    |

| 3 2 2 b | 不純物領域    |    |

| 3 2 4   | 絶縁膜      |    |

| 3 3 0   | トランジスタ   |    |

| 3 4 0   | トランジスタ   |    |

| 3 9 8   | ゲート電極    |    |

| 3 9 9   | 絶縁膜      |    |

| 4 0 2   | 酸化物半導体膜  | 50 |

|         |              |    |

|---------|--------------|----|

| 4 0 3   | 酸化物半導体膜      |    |

| 4 0 4   | 絶縁膜          |    |

| 4 0 5   | ゲート電極        |    |

| 4 0 6   | 絶縁膜          |    |

| 4 0 7 a | 領域           |    |

| 4 0 7 b | 領域           |    |

| 4 0 8   | チャネル形成領域     |    |

| 4 0 9 a | サイドウォール絶縁膜   |    |

| 4 0 9 b | サイドウォール絶縁膜   |    |

| 4 1 0   | トランジスタ       | 10 |

| 4 1 1   | ゲート絶縁膜       |    |

| 4 1 5   | 絶縁膜          |    |

| 4 1 6 a | ソース電極        |    |

| 4 1 6 b | ドレイン電極       |    |

| 4 1 7   | 絶縁膜          |    |

| 4 1 8   | 絶縁膜          |    |

| 4 1 9 a | 配線           |    |

| 4 1 9 b | 配線           |    |

| 4 2 1   | 絶縁膜          |    |

| 4 2 2   | 電極           | 20 |

| 9 0 1   | R F 回路       |    |

| 9 0 2   | アナログベースバンド回路 |    |

| 9 0 3   | デジタルベースバンド回路 |    |

| 9 0 4   | バッテリー        |    |

| 9 0 5   | 電源回路         |    |

| 9 0 6   | マイクロプロセッサ    |    |

| 9 0 7   | C P U        |    |

| 9 0 8   | D S P        |    |

| 9 0 9   | I F          |    |

| 9 1 0   | フラッシュメモリ     | 30 |

| 9 1 1   | ディスプレイコントローラ |    |

| 9 1 2   | メモリ回路        |    |

| 9 1 3   | ディスプレイ       |    |

| 9 1 4   | 表示部          |    |

| 9 1 5   | ソースドライバ      |    |

| 9 1 6   | ゲートドライバ      |    |

| 9 1 7   | 音声回路         |    |

| 9 1 8   | キーボード        |    |

| 9 1 9   | タッチセンサ       |    |

| 1 0 0 1 | バッテリー        | 40 |

| 1 0 0 2 | 電源回路         |    |

| 1 0 0 3 | マイクロプロセッサ    |    |

| 1 0 0 4 | フラッシュメモリ     |    |

| 1 0 0 5 | 音声回路         |    |

| 1 0 0 6 | キーボード        |    |

| 1 0 0 7 | メモリ回路        |    |

| 1 0 0 8 | タッチパネル       |    |

| 1 0 0 9 | ディスプレイ       |    |

| 1 0 1 0 | ディスプレイコントローラ |    |

| 2 7 0 0 | 電子書籍         | 50 |

|         |            |    |

|---------|------------|----|

| 2 7 0 1 | 筐体         |    |

| 2 7 0 3 | 筐体         |    |

| 2 7 0 5 | 表示部        |    |

| 2 7 0 7 | 表示部        |    |

| 2 7 1 1 | 軸部         |    |

| 2 7 2 1 | 電源         |    |

| 2 7 2 3 | 操作キー       |    |

| 2 7 2 5 | スピーカー      |    |

| 2 8 0 0 | 筐体         |    |

| 2 8 0 1 | ボタン        | 10 |

| 2 8 0 2 | マイクロフォン    |    |

| 2 8 0 3 | 表示部        |    |

| 2 8 0 4 | スピーカー      |    |

| 2 8 0 5 | カメラ用レンズ    |    |

| 2 8 0 6 | 外部接続端子     |    |

| 3 0 0 1 | 本体         |    |

| 3 0 0 2 | 筐体         |    |

| 3 0 0 3 | 表示部        |    |

| 3 0 0 4 | キー ボード     |    |

| 3 0 2 1 | 本体         | 20 |

| 3 0 2 2 | スタイルス      |    |

| 3 0 2 3 | 表示部        |    |

| 3 0 2 4 | 操作ボタン      |    |

| 3 0 2 5 | 外部インターフェイス |    |

| 3 0 5 1 | 本体         |    |

| 3 0 5 3 | 接眼部        |    |

| 3 0 5 4 | 操作スイッチ     |    |

| 3 0 5 6 | バッテリー      |    |

| 9 6 0 0 | テレビジョン装置   |    |

| 9 6 0 1 | 筐体         | 30 |

| 9 6 0 3 | 表示部        |    |

| 9 6 0 5 | スタンド       |    |

【図1】

(B)

(C)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/786 (2006.01) H 01 L 29/78 6 1 3 B

(56)参考文献 特開平05-235739 (JP, A)

特開平03-206712 (JP, A)

特開昭63-314913 (JP, A)

特開2011-142314 (JP, A)

特開平06-343033 (JP, A)

特開2001-077684 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 03 K 19 / 0185

H 01 L 21 / 8234

H 01 L 21 / 8238

H 01 L 27 / 088

H 01 L 27 / 092

H 01 L 29 / 786