(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7673003号

(P7673003)

(45)発行日 令和7年5月8日(2025.5.8)

(24)登録日 令和7年4月25日(2025.4.25)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| H 1 0 D | 86/40 (2025.01) | H 1 0 D | 86/40 | 1 0 1 Z |

| H 1 0 D | 30/67 (2025.01) | H 1 0 D | 30/67 | 1 0 2 A |

| H 1 0 D | 62/10 (2025.01) | H 1 0 D | 30/67 | 2 0 6 Z |

| H 1 0 D | 84/83 (2025.01) | H 1 0 D | 62/10 | 1 0 1 F |

| B 8 1 B | 7/02 (2006.01)  | H 1 0 D | 84/83 | B       |

請求項の数 18 (全21頁) 最終頁に続く

(21)出願番号 特願2022-19486(P2022-19486)

(22)出願日 令和4年2月10日(2022.2.10)

(65)公開番号 特開2022-138120(P2022-138120)

A)

(43)公開日 令和4年9月22日(2022.9.22)

審査請求日 令和7年2月10日(2025.2.10)

(31)優先権主張番号 17/196,329

(32)優先日 令和3年3月9日(2021.3.9)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 504407000

パロ アルト リサーチ センター,エル

エルシー

アメリカ合衆国 カリフォルニア州 94

304 パロ アルト カイオーテ ヒル

ロード 3333

(74)代理人 100094569

弁理士 田中 伸一郎

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100067013

弁理士 大塚 文昭

(74)代理人 西島 孝喜

(74)代理人

最終頁に続く

(54)【発明の名称】 薄膜電子部品を使用するスケーラブルな高電圧制御回路

## (57)【特許請求の範囲】

## 【請求項1】

デバイスであって、

第1の段であって、

第1の光スイッチと、

前記第1の光スイッチに接続された第1のトランジスタと、

前記第1の光スイッチ及び前記第1のトランジスタに接続された第2のトランジスタと、を備え、前記第2のトランジスタが、ソース、ゲート、及びドレインを備え、前記第2のトランジスタの前記ゲートが、前記第1の光スイッチによって制御され、前記第2のトランジスタが、前記ゲートと前記ドレインとの間に非ゲートチャネル領域を有する薄膜トランジスタ(TFT)、及び前記ゲートと前記ドレインとの間の1つ以上のフィールドプレートを備える、第1の段と、

第2の段であって、

第2の光スイッチと、

前記第2のトランジスタ及び前記第2の光スイッチに接続された第3のトランジスタと、

前記第2のトランジスタ、前記第2の光スイッチ、及び前記第3のトランジスタに接続された第4のトランジスタと、を備える、第2の段と、を備える、デバイス。

## 【請求項2】

前記第1の光スイッチが、2つの端子接点を有する半導体を備え、前記半導体が、水素

化アモルファスシリコン ( a - S i : H ) を含み、前記端子接点が、前記半導体に対するショットキバリアを形成する、請求項 1 に記載のデバイス。

【請求項 3】

前記第 1 の光スイッチが、2 つの端子接点を有する半導体を備え、前記半導体が、有機材料、金属酸化物、又はそれらの組み合わせを含む、請求項 1 に記載のデバイス。

【請求項 4】

前記第 1 及び第 2 の光スイッチ並びに前記第 2 及び第 4 のトランジスタが、前記デバイスの動作電圧範囲を拡大するために直列にカスケード接続される、請求項 1 に記載のデバイス。

【請求項 5】

前記デバイスが、

ゲート誘電体層と、

前記ゲート誘電体層上に位置付けられたレベル間誘電体 ( I L D ) 層と、を更に備え、前記第 2 のトランジスタが、

ソースと、

ゲートと、

ドレインと、

第 1 のフィールドプレートであって、前記ゲート及び前記第 1 のフィールドプレートが、前記ゲート誘電体層内に少なくとも部分的に位置付けられ、前記ゲート及び前記第 1 のフィールドプレートが、それらの間の非ゲートチャネルによって分離される、第 1 のフィールドプレートと、

前記 I L D 層内に、かつ前記ソースと前記ドレインとの間に少なくとも部分的に位置付けられたチャネルであって、水素化アモルファスシリコン ( a - S i : H ) を含む、チャネルと、

前記 I L D 層内に、かつ前記ソースと前記ドレインとの間に少なくとも部分的に位置付けられた窒化物層であって、前記チャネル上に少なくとも部分的に位置付けられる、窒化物層と、を備える、請求項 1 に記載のデバイス。

【請求項 6】

前記第 1 の光スイッチが、

前記ゲート誘電体層内に位置付けられた第 2 のフィールドプレートと、

I L D 層内に少なくとも部分的に位置付けられた n + ドープされた a - S i : H 層であって、互いに分離されている第 1 の部分、第 2 の部分、及び第 3 の部分を備える、n + ドープされた a - S i : H 層と、

前記 I L D 層内に少なくとも部分的に位置付けられた金属層であって、前記金属層が、

前記 n + ドープされた a - S i : H 層の前記第 1 の部分に少なくとも部分的に位置付けられる第 1 の部分と、

前記 n + ドープされた a - S i : H 層の前記第 2 の部分に少なくとも部分的に位置付けられる第 2 の部分と、

前記 n + ドープされた a - S i : H 層の前記第 3 の部分に少なくとも部分的に位置付けられる第 3 の部分と、

前記第 2 のフィールドプレート上に少なくとも部分的に、前記 n + ドープされた a - S i : H 層の前記第 2 及び第 3 の部分の間に少なくとも部分的に、かつ前記金属層の前記第 2 及び第 3 の部分の間に少なくとも部分的に位置付けられる第 4 の部分と、を備える、金属層と、を備える、請求項 5 に記載のデバイス。

【請求項 7】

前記第 1 の光スイッチが、

前記 I L D 層内に少なくとも部分的に位置付けられた金属層であって、前記金属層が、第 1 の部分及び第 2 の部分を備え、前記金属層の前記第 1 及び第 2 の部分が、段付きプロファイルを有する、金属層と、

前記 I L D 層内に、かつ前記金属層の前記第 1 及び第 2 の部分の間に少なくとも部分的

10

20

30

40

50

に位置付けられた第2のチャネルであって、a - S i : Hを含む、第2のチャネルと、前記I L D層内に少なくとも部分的に、前記金属層の前記第1及び第2の部分の間に少なくとも部分的に、かつ前記第2のチャネル上に少なくとも部分的に位置付けられた第2の窒化物層と、を備える、請求項5に記載のデバイス。

【請求項8】

デバイスであって、

第1の段であって、

第1の光スイッチと、

前記第1の光スイッチに接続された第1のトランジスタと、

前記第1の光スイッチ及び前記第1のトランジスタに接続された第2のトランジスタと 10

を備え、前記第1のトランジスタが、前記第2のトランジスタよりも長く、かつ狭く、

前記第1のトランジスタが、約0.1～約0.01のW/L比を有し、前記第2のトランジスタが、前記第1のトランジスタよりも高い電圧で動作するように構成されている、第1の段と、

第2の段であって、

第2の光スイッチと、

前記第2のトランジスタ及び前記第2の光スイッチに接続された第3のトランジスタと、

前記第2のトランジスタ、前記第2の光スイッチ、及び前記第3のトランジスタに接続された第4のトランジスタと、を備える、第2の段と、を備える、デバイス。

【請求項9】

20

アクチュエータを駆動するためのスイッチングデバイスであって、

第1の段であって、

第1のフォトダイオードと、

ソースと、ゲートと、ドレインと、を備える、第1のトランジスタであって、前記第1のトランジスタの前記ソース及び前記ゲートが、互いに接続され、前記第1のトランジスタの前記ドレインが、前記第1のフォトダイオードに接続される、第1のトランジスタと、

ソースと、ゲートと、ドレインと、を備える、第2のトランジスタであって、前記第2のトランジスタの前記ソースが、前記第1のトランジスタの前記ソース及び前記ゲートに接続され、前記第2のトランジスタの前記ゲートが、前記第1のフォトダイオード及び前記第1のトランジスタの前記ドレインに接続され、前記第2のトランジスタの前記ドレインが、前記第1のフォトダイオードに接続される、第2のトランジスタと、を備える、第1の段と、 30

第2の段であって、

第2のフォトダイオードと、

ソースと、ゲートと、ドレインと、を備える、第3のトランジスタであって、前記第3のトランジスタの前記ソース及び前記ゲートが、互いにかつ前記第2のトランジスタの前記ドレインに接続され、前記第3のトランジスタの前記ドレインが、前記第2のフォトダイオードに接続される、第3のトランジスタと、

ソースと、ゲートと、ドレインと、を備える、第4のトランジスタであって、前記第4のトランジスタの前記ソースが、前記第2のトランジスタの前記ドレインに、かつ前記第3のトランジスタの前記ソース及び前記ゲートに接続され、前記第4のトランジスタの前記ゲートが、前記第2のフォトダイオード及び前記第3のトランジスタの前記ドレインに接続され、前記第4のトランジスタの前記ドレインが、前記第2のフォトダイオードに接続される、第4のトランジスタと、を備える、第2の段と、を備える、スイッチングデバイス。 40

【請求項10】

前記第1のトランジスタが、前記第2のトランジスタよりも長く、かつ狭く、前記第2のトランジスタが、前記第1のトランジスタよりも高い電圧で動作するように構成されている、請求項9に記載のスイッチングデバイス。 50

## 【請求項 1 1】

前記第 2 のトランジスタが、薄膜トランジスタ ( T F T ) を備え、前記第 2 のトランジスタの前記ゲートが、前記第 1 のフォトダイオードによって制御される、請求項 9 に記載のスイッチングデバイス。

## 【請求項 1 2】

前記第 2 のトランジスタが、前記第 2 のトランジスタの前記ゲートと前記ドレインとの間に位置付けられるフィールドプレート及び非ゲートチャネル領域を更に備え、前記非ゲートチャネル領域が、前記第 2 のトランジスタの前記ゲートと前記フィールドプレートとの間に位置付けられる、請求項 1 1 に記載のスイッチングデバイス。

## 【請求項 1 3】

光源が前記第 1 及び第 2 のフォトダイオードに光電流を誘導させて、前記第 2 及び第 4 のトランジスタのゲート電位をドレイン電圧に向かってバイアスすることに応答して、前記スイッチングデバイスがオン状態に作動するように構成されている、請求項 9 に記載のスイッチングデバイス。

## 【請求項 1 4】

微小電気機械システム ( M E M S ) アクチュエータを駆動するための高電圧スイッチングデバイスであって、

第 1 の段であって、

第 1 の端子接点及び第 2 の端子接点を有する半導体を備える第 1 のフォトダイオードであって、前記半導体が、水素化アモルファスシリコン ( a - S i : H ) を含み、前記第 1 及び第 2 の端子接点が、前記半導体に対するショットキバリアを形成する、第 1 のフォトダイオードと、

ソースと、ゲートと、ドレインと、を備える、第 1 のトランジスタであって、前記第 1 のトランジスタの前記ソース及び前記ゲートが、互いに接続され、前記第 1 のトランジスタの前記ドレインが、前記第 1 のフォトダイオードの前記第 1 の端子接点に接続され、前記第 1 のトランジスタが、約 0 . 1 ~ 約 0 . 0 1 の W / L 比を有する、第 1 のトランジスタと、

ソースと、ゲートと、ドレインと、を備える、第 2 のトランジスタであって、前記第 2 のトランジスタの前記ソースが、前記第 1 のトランジスタの前記ソース及び前記ゲートに接続され、前記第 2 のトランジスタの前記ゲートが、前記第 1 のフォトダイオード及び前記第 1 のトランジスタの前記ドレインの前記第 1 の端子接点に接続され、前記第 2 のトランジスタの前記ドレインが、前記第 1 のフォトダイオードの前記第 2 の端子接点に接続される、第 2 のトランジスタと、を備える、第 1 の段と、

第 2 の段であって、

第 2 のフォトダイオードと、

ソースと、ゲートと、ドレインと、を備える、第 3 のトランジスタであって、前記第 3 のトランジスタの前記ソース及び前記ゲートが、互いにかつ前記第 2 のトランジスタの前記ドレインに接続され、前記第 3 のトランジスタの前記ドレインが、前記第 2 のフォトダイオードに接続される、第 3 のトランジスタと、

ソースと、ゲートと、ドレインと、を備える、第 4 のトランジスタであって、前記第 4 のトランジスタの前記ソースが、前記第 2 のトランジスタの前記ドレインに、かつ前記第 3 のトランジスタの前記ソース及び前記ゲートに接続され、前記第 4 のトランジスタの前記ゲートが、前記第 2 のフォトダイオード及び前記第 3 のトランジスタの前記ドレインに接続され、前記第 4 のトランジスタの前記ドレインが、前記第 2 のフォトダイオードに接続される、第 4 のトランジスタと、を備える、第 2 の段と、を備える、高電圧スイッチングデバイス。

## 【請求項 1 5】

前記第 1 のトランジスタが、前記第 2 のトランジスタよりも長く、かつ狭く、前記第 2 のトランジスタが、前記第 1 のトランジスタよりも高い電圧で動作するように構成されている、請求項 1 4 に記載のスイッチングデバイス。

10

20

30

40

50

## 【請求項 16】

ゲート誘電体層と、

前記ゲート誘電体層上に位置付けられたレベル間誘電体(ILD)層と、を更に備え、前記第2のトランジスタが、

第1のフィールドプレートであって、前記第2のトランジスタの前記ゲート及び前記第1のフィールドプレートが、前記ゲート誘電体層内に少なくとも部分的に位置付けられ、前記第2のトランジスタの前記ゲート及び前記第1のフィールドプレートが、それらの間の非ゲートチャネルによって分離される、第1のフィールドプレートと、

前記ILD層内に、かつ前記第2のトランジスタの前記ソースと前記ドレインとの間に少なくとも部分的に位置付けられたチャネルであって、水素化アモルファスシリコン(a-Si:H)を含む、チャネルと、

前記ILD層内に、かつ前記第2のトランジスタの前記ソースと前記ドレインとの間に少なくとも部分的に位置付けられた窒化物層であって、前記チャネル上に少なくとも部分的に位置付けられる、窒化物層と、を備える、請求項14に記載のスイッチングデバイス。

## 【請求項 17】

前記第1のフォトダイオードが、

前記ゲート誘電体層内に位置付けられた第2のフィールドプレートと、

前記ILD層内に少なくとも部分的に位置付けられたn+ドープされたa-Si:H層であって、互いに分離されている第1の部分、第2の部分、及び第3の部分を備える、n+ドープされたa-Si:H層と、

前記ILD層内に少なくとも部分的に位置付けられた金属層であって、前記金属層が、

前記n+ドープされたa-Si:H層の前記第1の部分に少なくとも部分的に位置付けられる第1の部分と、

前記n+ドープされたa-Si:H層の前記第2の部分に少なくとも部分的に位置付けられる第2の部分と、

前記n+ドープされたa-Si:H層の前記第3の部分に少なくとも部分的に位置付けられる第3の部分と、

前記第2のフィールドプレート上に少なくとも部分的に、前記n+ドープされたa-Si:H層の前記第2及び第3の部分の間に少なくとも部分的に、かつ前記金属層の前記第2及び第3の部分の間に少なくとも部分的に位置付けられる第4の部分と、を備える、金属層と、を備える、請求項16に記載のスイッチングデバイス。

## 【請求項 18】

前記第1のフォトダイオードが、

前記ILD層内に少なくとも部分的に位置付けられた金属層であって、前記金属層が、第1の部分及び第2の部分を備え、前記金属層の前記第1及び第2の部分が、段付きプロファイルを有する、金属層と、

前記ILD層内に、かつ前記金属層の前記第1及び第2の部分の間に少なくとも部分的に位置付けられた第2のチャネルであって、a-Si:Hを含む、第2のチャネルと、

前記ILD層内に少なくとも部分的に、前記金属層の前記第1及び第2の部分の間に少なくとも部分的に、かつ前記第2のチャネル上に少なくとも部分的に位置付けられた第2の窒化物層と、を備える、請求項16に記載のスイッチングデバイス。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本教示は、概して、微小電気機械システム(microelectromechanical system、MEMS)に関するものであり、より具体的には、MEMSアクチュエータを駆動するための高電圧スイッチングデバイスに関する。

## 【背景技術】

## 【0002】

10

20

30

40

50

MEMSは、小さい（例えば、顕微鏡的な）システム、特に可動部分を有するものである。MEMSは、1~100マイクロメートル（ $\mu\text{m}$ ）のサイズの構成要素から作製され、MEMSは、一般に、20マイクロメートル~1ミリメートル（mm）のサイズの範囲である。MEMSは、通常、データを処理する中央ユニット（例えば、マイクロプロセッサ）と、環境（例えば、マイクロセンサ）と相互作用するいくつかの構成要素と、を含む。MEMSの大きい表面積対容積比のため、周囲の電磁気（例えば、静電荷及び磁気モーメント）及び流体力学（例えば、表面張力及び粘度）によって生成される力は、より大規模な機械デバイスによるものよりも重要な設計上の考慮事項である。

### 【0003】

MEMSは、典型的には、静電作動、圧電作動、又は熱作動を使用する。静電作動は、電磁作動及び熱作動よりも良好により小さいサイズにスケールダウンされる。しかしながら、静電作動は、典型的には、十分な出力を発生させるために、電磁作動及び熱作動よりも高い電圧（例えば、数kV）に依存する。同程度のサイズ及び重量のアクチュエータを有する微小電子部品においてそのような高電圧を発生させること及び制御することはどちらも困難である。

10

### 【発明の概要】

### 【0004】

以下は、本教示の1つ以上の実施形態のいくつかの態様の基本的な理解を提供するために、簡略化された概要を提示する。この概要は、広範な概略ではなく、本教示の主要又は重要な要素を特定することも、本開示の範囲を明示することも意図していない。むしろ、その主な目的は、単に、後に提示される詳細な説明の前置きとして、1つ以上の概念を簡略化された形式で提示するだけである。

20

### 【0005】

デバイスが開示される。本デバイスは、第1の光スイッチを有する第1の段と、第1の光スイッチに接続された第1のトランジスタと、第1の光スイッチ及び第1のトランジスタに接続された第2のトランジスタと、を含む。本デバイスはまた、第2の光スイッチを有する第2の段と、第2のトランジスタ及び第2の光スイッチに接続された第3のトランジスタと、第2のトランジスタ、第2の光スイッチ、及び第3のトランジスタに接続された第4のトランジスタと、を含む。

### 【0006】

30

アクチュエータを駆動するためのスイッチングデバイスが開示される。スイッチングデバイスは、第1の段を含む。第1の段は、第1のフォトダイオードを含む。第1の段はまた、ソースと、ゲートと、ドレインと、を有する、第1のトランジスタも含む。第1のトランジスタのソース及びゲートは、互いに接続され、第1のトランジスタのドレインは、第1のフォトダイオードに接続される。第1の段はまた、ソースと、ゲートと、ドレインと、を有する、第2のトランジスタも含む。第2のトランジスタのソースは、第1のトランジスタのソース及びゲートに接続される。第2のトランジスタのゲートは、第1のフォトダイオード及び第1のトランジスタのドレインに接続される。第2のトランジスタのドレインは、第1のフォトダイオードに接続される。スイッチングデバイスはまた、第2の段も含む。第2の段は、第2のフォトダイオードを含む。第2の段はまた、ソースと、ゲートと、ドレインと、を有する、第3のトランジスタも含む。第3のトランジスタのソース及びゲートは、互いに、かつ第2のトランジスタのドレインに接続され、第3のトランジスタのドレインは、第2のフォトダイオードに接続される。第2の段はまた、ソースと、ゲートと、ドレインと、を有する、第4のトランジスタも含む。第4のトランジスタのソースは、第2のトランジスタのドレインに、かつ第3のトランジスタのソース及びゲートに接続される。第4のトランジスタのゲートは、第2のフォトダイオード及び第3のトランジスタのドレインに接続される。第4のトランジスタのドレインは、第2のフォトダイオードに接続される。

40

### 【0007】

微小電気機械システム（MEMS）アクチュエータを駆動するための高電圧スイッチ

50

ングデバイスが開示される。スイッチングデバイスは、第1の段を含む。第1の段は、第1の端子接点及び第2の端子接点を備える半導体を有する第1のフォトダイオードを含む。半導体は、水素化アモルファスシリコン (hydrogenated amorphous silicon, a-Si : H) を含む。第1及び第2の端子接点は、半導体に対するショットキバリアを形成する。第1の段はまた、ソースと、ゲートと、ドレインと、を有する、第1のトランジスタも含む。第1のトランジスタのソース及びゲートは、互いに接続される。第1のトランジスタのドレインは、第1のフォトダイオードの第1の端子接觸に接続される。第1のトランジスタは、約0.01～約0.1のW/L比を有する。第1の段はまた、ソースと、ゲートと、ドレインと、を有する、第2のトランジスタも含む。第2のトランジスタのソースは、第1のトランジスタのソース及びゲートに接続される。第2のトランジスタのゲートは、第1のフォトダイオードの第1の端子接点及び第1のトランジスタのドレインに接続される。第2のトランジスタのドレインは、第1のフォトダイオードの第2の端子接点に接続される。スイッチングデバイスはまた、第2の段も含む。第2の段は、第2のフォトダイオードを含む。第2の段はまた、ソースと、ゲートと、ドレインと、を有する、第3のトランジスタも含む。第3のトランジスタのソース及びゲートは、互いに、かつ第2のトランジスタのドレインに接続される。第3のトランジスタのドレインは、第2のフォトダイオードに接続される。第2の段はまた、ソースと、ゲートと、ドレインと、を有する、第4のトランジスタも含む。第4のトランジスタのソースは、第2のトランジスタのドレインに、かつ第3のトランジスタのソース及びゲートに接続される。第4のトランジスタのゲートは、第2のフォトダイオード及び第3のトランジスタのドレインに接続される。第4のトランジスタのドレインは、第2のフォトダイオードに接続される。10 20

【図面の簡単な説明】

【0008】

本明細書の一部に組み込まれ、本明細書の一部を構成する添付図面は、本教示の実施形態を示し、本明細書と共に本開示の原理を説明する役割を果たす。

【0009】

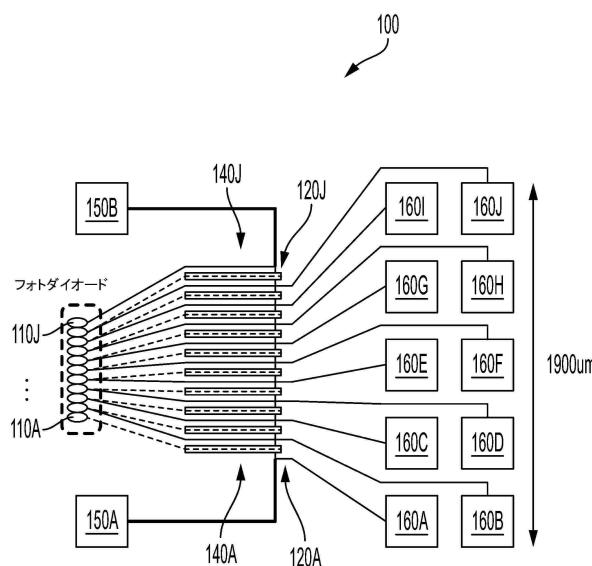

【図1】一実施形態による、MEMSアクチュエータを駆動するための高電圧スイッチングデバイスの概略図を表す。

【0010】

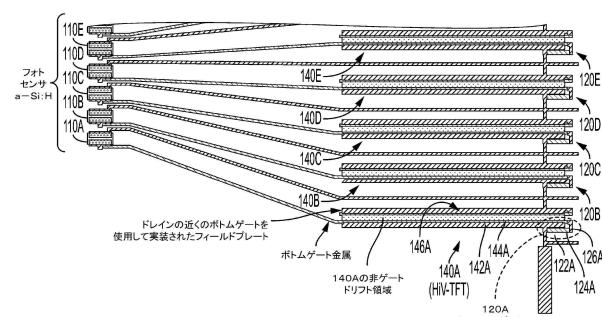

【図2】一実施形態による、図1の一部分の拡大図を表す。

【0011】

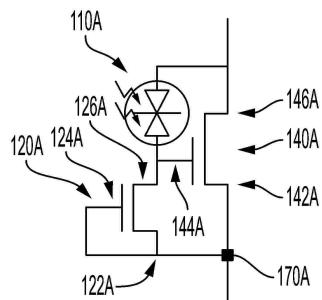

【図3】一実施形態による、デバイスの第1の段の回路図を表す。

【0012】

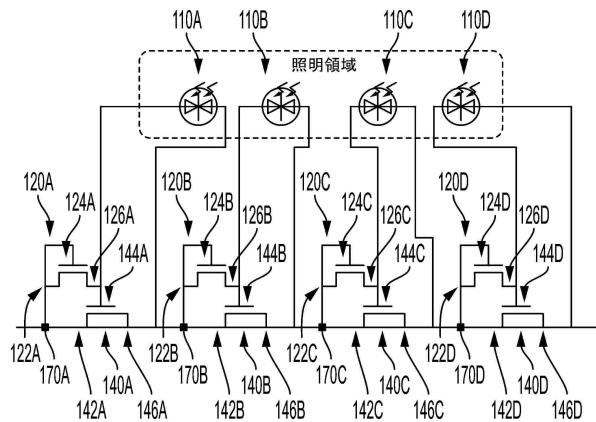

【図4】一実施形態による、一緒にスタックされたデバイスの複数（例えば、4つ）の段の回路図を表す。

【0013】

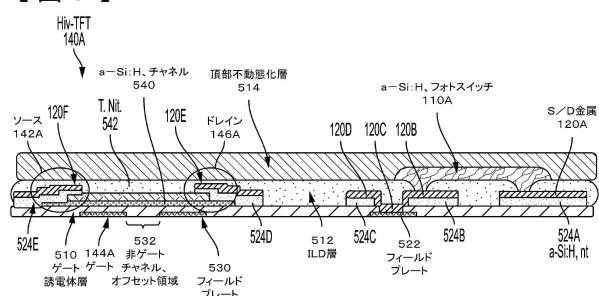

【図5】一実施形態による、デバイスの第1の段の一部分の概略側断面図を表す。

【0014】

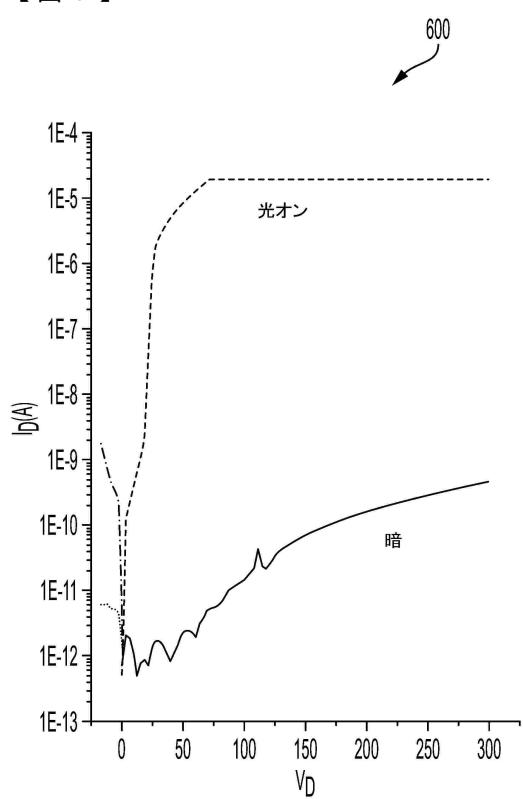

【図6】一実施形態による、デバイスの第1の段の電流電圧特性を示すグラフを表す。

【0015】

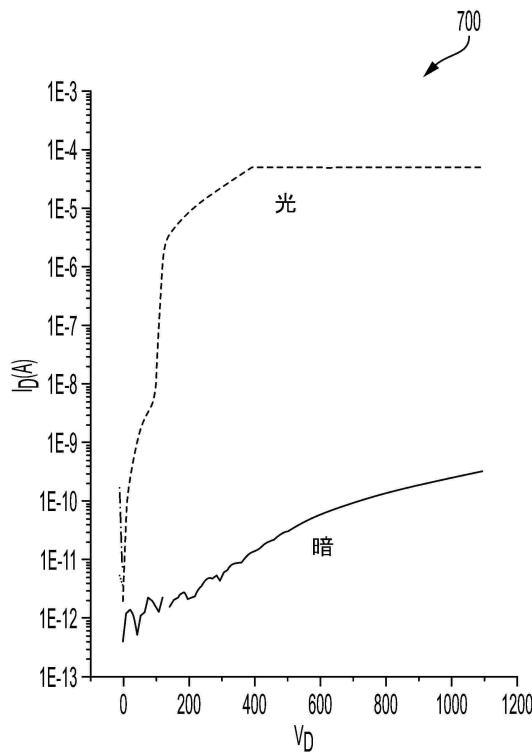

【図7】一実施形態による、複数のスタック及び/又はカスケードされたデバイスの段（例えば、4段）の電流電圧特性を示すグラフを表す。

【0016】

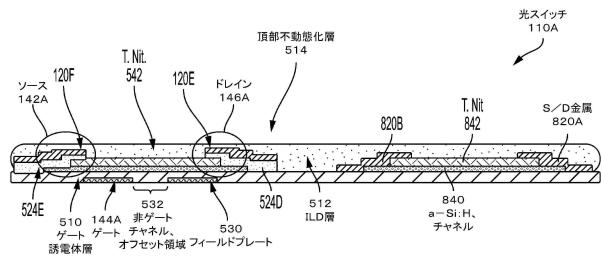

【図8】一実施形態による、デバイスの第1の段の一部分の概略側断面図を表す。

【0017】

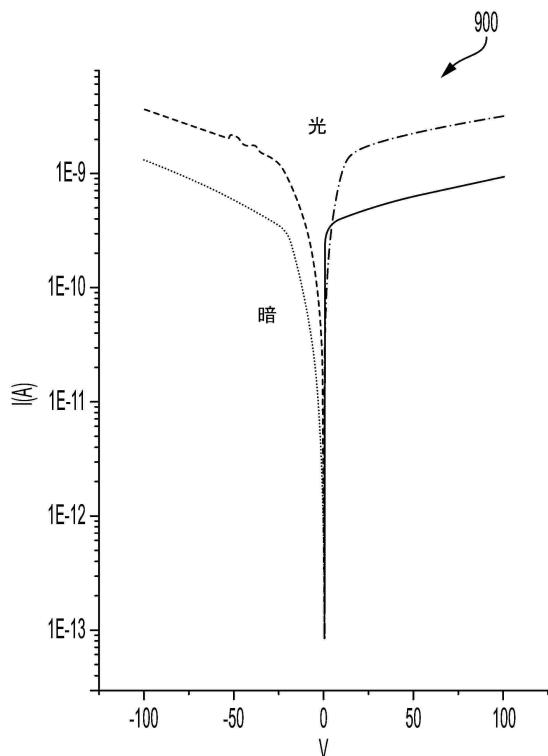

【図9】一実施形態による、n+ドープされたa-Si:H層が、S/D金属層とチャネルとの間に少なくとも部分的に位置付けられる場合の、デバイスの光スイッチの電流電圧特性を示すグラフを表す。

【0018】

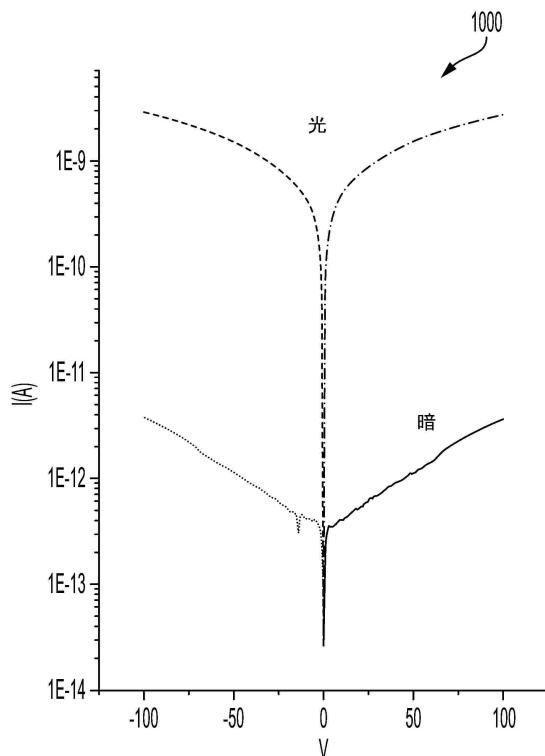

【図10】一実施形態による、S/D金属層が、チャネル（図8の右側に示す）上に少な

10

20

30

40

50

くとも部分的に位置付けられる（すなわち、と直接接触した）場合の、光スイッチの電流電圧特性を示すグラフを表す。

【0019】

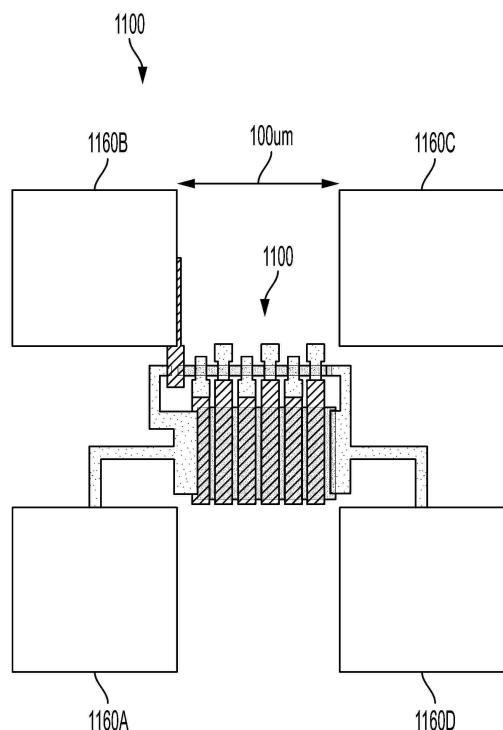

【図11】一実施形態による、MEMSアクチュエータを駆動するための別の高電圧スイッチングデバイスの概略図を表す。

【0020】

【図12】一実施形態による、図11の拡大部分を表す。

【0021】

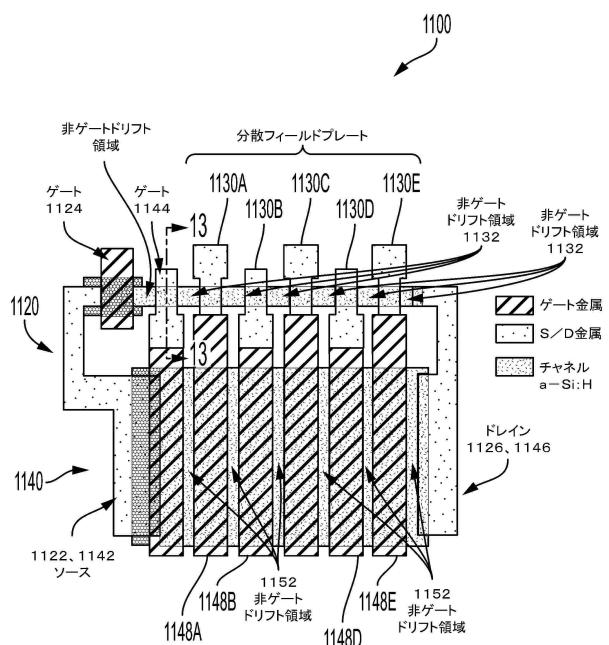

【図13】一実施形態による、図11に示されるデバイスの一部分の概略側断面図を表す。

【0022】

【図14】一実施形態による、図11のデバイスの変換特性を示すグラフを表す。

【発明を実施するための形態】

【0023】

ここで、本教示の例示の実施形態を詳細に参照し、この実施例を添付図面に示す。可能な限り、同じ参照番号が、同じ、類似、又は同様の部分を指すように図面全体にわたって使用される。

【0024】

本開示は、微小電気機械システム（MEMS）に関する。MEMSの第1の実施形態は、光カプラ（オプトカプラとも称される）であり得るか、又はそれを含み得る。光カプラ手法は、低電圧制御回路に対するインターフェース及び分離を簡略化する。光カプラ手法はまた、多数の段をカスケード（例えば、スタック）して、電圧定格を高め得る。光カプラ手法は、デバイスをオン及びオフするために光源が必要であるので、エネルギー効率が低下し得る。MEMSの第2の実施形態は、インバータ薄膜トランジスタ（thin-film transistor、TFT）及びバッファTFTがサブデバイスレベルで密に集積される、2段インバータ／バッファトランジスタ構造であり得るか、又はそれを含み得る。そのような密な集積は、高電圧定格を達成することができるよう、バッファTFTのドレイン領域全体に高電圧を均一に分配するのを補助する。

【0025】

水素化アモルファスシリコン（a-Si:H）ベースの高電圧（high-voltage、HiV）-TFT、特に「オフセットゲート」TFTアーキテクチャは、200V～500V又は300V～400Vの動作電圧を提供することができる。オフセットゲートTFTアーキテクチャは、非ゲートドリフトチャネル領域を有し得、これは、高電圧を非ゲート領域全体に分配して、高電界に起因する任意の流出プロセスを防止するための半導体のセクションを提供する。非ゲート領域は、任意の電圧（例えば、 $E = V / L$ ）を有する同じ電界を維持するように、長さをスケーリングすることができる。一実施例では、この設計に基づいて、800VのHiV-TFTが構築され得る。

【0026】

しかしながら、800Vを超える電圧をスケーリングするには、この手法は、次第に効果的でなくなる。高電圧が局所的に集中して暴走破壊プロセスを生じさせないように、非ゲート領域全体に高電圧を一様に分配するように保つことは困難である。加えて、より長い非ゲート領域を有することは、オン電流に対する悪影響を有し得る。非ゲートチャネルは、必然的に「抵抗性」である。長い非ゲートチャネルを有するTFTのオン電流は、同じチャネル幅には小さい場合がある。非ゲートチャネル長さの長さを拡大することは、オン／オフ比を急激に低下させ得る。800VのHiV-TFTは、約3～4桁のオン／オフ比を有し得る。広範囲にわたって所望の電圧を実装するための信頼性の高い方式を有するスケーラブルな高電圧ドライバの基本的な難点は、暴走破壊プロセスを生じさせる高電圧が、チャネル材料又はデバイスの小さい領域に集中することを防止することである。

【0027】

動作電圧範囲を拡大するために、複数の別個のトランジスタがカスケードされ得る。しかしながら、TFTの回路に実装することは困難であり、これまで行われなかった。別

10

20

30

40

50

個のデバイス及びTFTプロセスを使用することの間にはいくつかの違いが存在する。N型金属酸化膜半導体 (N-type metal-oxide-semiconductor、NMOS) 能動デバイスだけが、a-Si:H TFTプロセスにおいて利用可能である。利用可能なP型金属酸化膜半導体 (P-type metal-oxide-semiconductor、PMOS) 又はバイポーラデバイスは存在しない。抵抗器は、a-Si:H TFTプロセスの制限範囲を限定し、通常、レイアウト占有領域の非効率的な使用と考えられる。サブ回路は、典型的には、TFT回路の能力を超える複雑なDC-DCコンバータであるので、複数の電圧レールを提供して、カスケードされたトランジスタアレイのゲートを制御するためにサブ回路を担持することは、一般に、利用不可能である。

## 【0028】

10

図1は、一実施形態による、MEMSアクチュエータを駆動するための高電圧スイッチングデバイス100の概略図を表し、図2は、一実施形態による、図1の一部分の拡大図を表す。デバイス100は、1つ以上の光スイッチを含むことができる（10個が示される：110A～110J）。光スイッチ110A～110Jは、光を電流に変換するフォトダイオード（例えば、半導体ダイオード）であり得るか、又はそれを含み得る。一実施形態では、半導体は、a-Si:Hであり得るか、又はそれを含み得る。半導体は、各々が2つの端子接点を含み得る。端子接点は、半導体に対するショットキバリアを形成し得る。端子接点材料は、TiW、MoCr、Mo、Ito、若しくはそれらの組み合わせであり得るか、又はそれを含み得る。

## 【0029】

20

デバイス100はまた、1つ以上の第1のトランジスタも含み得る（10個が示される：120A～120J）。第1のトランジスタ120A～120Jは、TFTであり得るか、又はそれを含み得る。第1のトランジスタ120A、120Jは、（下で導入され、説明される）第2のトランジスタのゲートの放電経路を提供するために長く、かつ狭くあり得る。例えば、第1のトランジスタ120A～120Jは、約20um～約500umの長さ、及び約3um～約10umの幅を有し得る。

## 【0030】

第1のトランジスタ120A～120Jの各々は、ソース122Aと、ゲート124Aと、ドレイン124Aと、を含み得る。下で更に詳細に説明するように、第1のトランジスタ120A～120Jの各々は、光スイッチ110A～110Jのそれぞれ1つに接続され得る。例えば、第1のトランジスタ120Aが光スイッチ110Aに接続され得る、及び第1のトランジスタ120Bが光スイッチ110Bに接続され得る、などである。第1のトランジスタ120A～120Jは、1未満であるW/L比を有し得る。例えば、W/L比は、約0.1～約0.01であり得る。

30

## 【0031】

デバイス100はまた、1つ以上の第2のトランジスタも含み得る（10個が示される：140A～140J）。第2のトランジスタ140A～140Jは、HiV-TFTであり得るか、又はそれを含み得る。より具体的には、第2のトランジスタ140A～140Jは、第1のトランジスタ120A～120Jよりも高い電圧で動作するように構成され得る。例えば、第1のトランジスタ120A～120Jは、約10V～約100V（例えば、20V）の電圧に定格され得、第2のトランジスタ140A～140Jは、約200V～約1000V（例えば、400V）の電圧に定格され得る。第2のトランジスタ140A～140Jは、第1のトランジスタ120A～120Jよりも短く、かつより広く／より厚くなり得る。例えば、第2のトランジスタ140A～140Jは、約3um～約10umの長さ、及び約10um～約1000umの幅を有し得る。

40

## 【0032】

第2のトランジスタ140A～140Jの各々は、ソース142Aと、ゲート144Aと、ドレイン144Aと、を含み得る。第2のトランジスタ140A～140Jの各々は、光スイッチ110A～110Jのそれぞれ1つに、及び第1のトランジスタ120A～120Jのそれぞれ1つに接続され得る。例えば、第2のトランジスタ140Aが光ス

50

イッチ 110 A 及び第 1 のトランジスタ 120 A に接続され得る、並びに第 2 のトランジスタ 140 B が光スイッチ 110 B 及び第 1 のトランジスタ 120 B に接続され得る、などである。第 2 のトランジスタ 140 A ~ 140 B のゲート 144 A ~ 144 J は、光スイッチ 110 A ~ 110 J によって制御され得る。例えば、第 2 のトランジスタの各々（例えば、140 A）は、光スイッチのそれぞれ 1 つ（例えば、110 A）及び／又は第 1 のトランジスタのそれぞれ 1 つ（例えば、120 A）を使用して制御され得、第 2 のトランジスタ（例えば、140 A）のゲート（例えば、144 A）を、第 2 のトランジスタ（例えば、140 A）のソース（例えば、142 A）と同じ電位にさせる。これは、光スイッチ 110 A が照明されていないときに、第 2 のトランジスタ（例えば、140 A）をオフ状態にさせ得る。

10

### 【0033】

光スイッチ 110 A、第 1 のトランジスタ 120 A、及び第 2 のトランジスタ 120 A がデバイス 100、光スイッチ 110 B、第 1 のトランジスタ 120 B の第 1 の段を形成し得る、並びに第 2 のトランジスタ 120 B がデバイス 100 の第 2 の段を形成し得る、などである。したがって、デバイス 100 は、スタッツ及び／又はカスケードされる複数の（例えば、10 の）段を含み得、これは、デバイス 100 が、単一の TFT が取り扱うこと／耐えることができるよりも高い（例えば、10 倍の）動作可能な電圧範囲を達成するのを補助し得る。例えば、光スイッチ 110 A ~ 110 J 及び第 2 のトランジスタ 140 A ~ 140 J は、デバイス 100 の動作電圧範囲を拡大するために、直列に接続されたカスケードであり得る。

20

### 【0034】

デバイス 100 はまた、1 つ以上のパッドも含み得る（2 つが示される：150 A、150 B）。パッド 150 A、150 B は、プローブステーションを使用してプローブするため使用されるように構成されている、金属パッドであり得る。第 1 のパッド 150 A は、第 1 の段に（例えば、第 1 のトランジスタ 120 A 及び／又は第 2 のトランジスタ 140 A に）接続され得る。第 2 のパッド 150 B は、最後の（例えば、第 10 の）段に（例えば、第 1 のトランジスタ 120 J 及び／又は第 2 のトランジスタ 140 J に）接続され得る。

### 【0035】

デバイス 100 はまた、1 つ以上のパッドも含み得る（10 個が示される：160 A ~ 160 J）。第 1 のパッド 160 A が第 1 の段に（例えば、第 1 のトランジスタ 120 A 及び／又は第 2 のトランジスタ 140 A に）接続され得る、並びに第 2 のパッド 160 B が第 2 の段に（例えば、第 1 のトランジスタ 120 B 及び／又は第 2 のトランジスタ 140 B に）接続され得る、などである。

30

### 【0036】

デバイス 100 をオンにするには、光源（例えば、低電圧制御回路によって制御される LED）が光スイッチ 110 A ~ 110 J を照明し、これが光電流を誘導し、第 2 のトランジスタ 140 A ~ 140 J のゲート電位をドレイン電圧に向かってバイアスする。これは、第 2 のトランジスタ 140 A ~ 140 J をオンにさせる。第 1 のトランジスタ 120 A ~ 120 J は、光スイッチ 110 A ~ 110 J の負荷としての役割を果たし得る。第 2 のトランジスタ 140 A ~ 140 J をオン状態に作動させる十分なゲート電圧を光電流によって誘導するために、所定の抵抗が必要である。

40

### 【0037】

図 3 は、一実施形態による、デバイス 100 の第 1 の段の回路図を表す。上で述べられるように、第 1 のトランジスタ 120 A は、ソース 122 A と、ゲート 124 A と、ドレイン 126 A と、を含み得、第 2 のトランジスタ 140 A は、ソース 142 A と、ゲート 144 A と、ドレイン 146 A と、を含み得る。第 1 のトランジスタ 120 A のドレイン 126 A は、光スイッチ 110 A の第 1 の側及び第 2 のトランジスタ 140 A のゲート 144 A に接続され得る。第 1 のトランジスタ 120 A のソース 122 A は、（例えば、共通ノード 170 A において）第 1 のトランジスタ 120 A のゲート 124 A 及び第 2 の

50

トランジスタ 140A のソース 142A に接続され得る。第 2 のトランジスタ 140A のドレイン 146A は、光スイッチ 110A の第 2 の側に接続され得る。

【0038】

図 4 は、一実施形態による、一緒にスタックされたデバイス 100 の複数（例えば、4 つ）の段の回路図 400 を表す。示されるように、光スイッチ 110A 及び第 1 の段の第 2 のトランジスタ 140A のドレイン 146A は、第 2 の段の共通ノード 170B に接続され得、光スイッチ 110B 及び第 2 の段の第 2 のトランジスタ 140B の 146B は、第 3 の段階の共通ノード 170C に接続され得、光スイッチ 110C 及び第 3 の段の第 2 のトランジスタ 140C のドレイン 146C は、第 4 の段の共通ノード 170D に接続され得る。光スイッチ 110A ~ 110D は、光の利用及び照明の均一性を確実にするために、照明領域の中へ一緒に近づけて位置付けられ得る。光スイッチ 110A ~ 110D は、一緒にグループ化されて、低電圧電子部品によって作動される 1 つの（又はより多くの）光源によって制御され得る。

【0039】

図 5 は、一実施形態による、デバイス 100 の第 1 の段の一部分の概略側断面図を表す。第 1 の段は、後方チャネルエッチストップ a - Si : H TFT プロセスを使用して形成され得る。第 1 の段は、ゲート誘電体層（底部窒化物層とも称される）510 と、ゲート誘電体層 510 上に位置付けられたレベル間誘電体（interlevel dielectric、ILD）層 512 と、ILD 層 512 上に位置付けられた（頂部）不動態化層 514 と、を含み得る。

【0040】

第 1 の段はまた、光スイッチ 110A と、第 1 のトランジスタ 120A（図 5 に示さず）と、第 2 のトランジスタ 140A と、を含み得る。光スイッチ 110A は、ILD 層 512 及び / 又は不動態化層 514 内に少なくとも部分的に位置付けられ得る。光スイッチ 110A は、S / D 金属層に実装され得る（6 つの部分 120A ~ 120F を示す）。示されるように、光スイッチ 110A の第 1 の面は、S / D 金属層の第 1 の部分 520A に実装され得、光スイッチ 110A の第 2 の面は、S / D 金属層の第 2 の部分 520B に実装され得る。S / D 金属層の第 1 の部分 520A 及び第 2 の部分 520B は、ILD 層 512 内に位置付けられ得る。S / D 金属層の第 1 の部分 520A 及び第 2 の部分 520B は、互いに分離され得る（すなわち、ILD 層 512 の一部分は、それらの間に位置付けられ得る）。S / D 金属層の第 2 の部分 520B は、ゲート誘電体層 510 内に少なくとも部分的に位置付けられ得る S / D 金属層の第 3 の部分 520C に接続され得る。S / D 金属層の第 3 の部分 520C は、ゲート誘電体層 510 内に位置付けられるフィールドプレート 522 上に位置付けられ及び / 又は接続され得る。S / D 金属層の第 3 の部分 520C は、ILD 層 512 内に位置付けられる S / D 金属層 520D の第 4 の部分に接続され得る。

【0041】

n + ドープされた a - Si : H 層（5 つの部分が示される：524A ~ 524E）は、ILD 層 512 内に少なくとも部分的に位置付けられ得る。示されるように、S / D 金属層の第 1 の部分 520A は、n + ドープされた a - Si : H 層の第 1 の部分 524A に少なくとも部分的に位置付けられ得、S / D 金属層の第 2 の部分 520B は、n + ドープされた a - Si : H 層の第 2 の部分 524B に少なくとも部分的に位置付けられ得、S / D 金属層の第 4 の部分 520D は、n + ドープされた a - Si : H 層の第 3 の部分 524C に少なくとも部分的に位置付けられ得る。

【0042】

第 2 のトランジスタ 140A は、ソース 142A と、ゲート 144A と、ドレイン 146A と、を含み得る。第 2 のトランジスタ 140A はまた、ゲート誘電体層 510 内でゲート 144A からオフセットされるフィールドプレート 530 を含み得る。フィールドプレート 530 は、ゲート 144A とドレイン 146A との間に位置付けられ得る。非ゲートチャネル（例えば、オフセット領域）532 は、ゲート誘電体層 510 内に位置付け

られ得る。非ゲートチャネル 532 は、ゲート 144A とフィールドプレート 530 の間に位置付けられ得る。非ゲートチャネル 532 はまた、又はその代わりに、ゲート 144A とドレイン 146A との間に位置付けられ得る。フィールドプレート 530 及び / 又は非ゲートチャネル領域 532 は、約数 10 ボルトの S / D 動作範囲を数百ボルトの動作範囲に拡大するために、ドレイン 146A の近くに位置付けられ得る。これは、オフセットゲート HiV-TFT のアーキテクチャに特有である。

#### 【0043】

第 2 のトランジスタ 140A はまた、S / D 金属層の第 5 の部分 520E 及び第 6 の部分 520F を含み得る。S / D 金属層の第 5 の部分 520E 及び第 6 の部分 520F は、ILD 層 512 内に位置付けられ得る。S / D 金属層の第 5 の部分 520E 及び第 6 の部分 520F は、互いに分離され得る（すなわち、ILD 層 512 の一部分は、それらの間に位置付けられ得る）。S / D 金属層の第 5 の部分 520E 及び第 6 の部分 520F は、それらが互いに向かってより近くに移動するにつれて各々が不動態化層 514 のより近くに前進するように、段付きプロファイルを有し得る。

10

#### 【0044】

第 2 のトランジスタ 140A はまた、n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E を含み得る。n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E は、ILD 層 512 内に位置付けられ得る。n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E は、互いに分離され得る（すなわち、ILD 層 512 の一部分は、それらの間に位置付けられ得る）。n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E は、それらが互いに向かってより近くに移動するにつれて各々が不動態化層 514 のより近くに前進するように、段付きプロファイルを有し得る。

20

#### 【0045】

第 2 のトランジスタ 140A はまた、チャネル 540（例えば、a - Si : H を含む）と、頂部窒化物（T. Nit.）層 542 と、を含み得る。チャネル 540 は、ゲート誘電体層 510 上に及び / 又は ILD 層 512 内に位置付けられ得る。チャネル 540 は、n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E の間に少なくとも部分的に位置付けられ得る。頂部窒化物層 542 は、チャネル 540 上に位置付けられ得る。頂部窒化物層 542 は、n+ ドープされた a - Si : H 層の第 4 の部分 524D 及び第 5 の部分 524E の間に少なくとも部分的に位置付けられ得る。チャネル 540 は、頂部窒化物層 542 よりも広い幅を有し得る。

30

#### 【0046】

ソース 142A は、S / D 金属層の第 6 の部分 520F、n+ ドープされた a - Si : H 層の第 5 の部分 524E、チャネル 540、及び頂部窒化物層 542 の少なくとも一部分を含み得る。ドレイン 146A は、S / D 金属層の第 5 の部分 520E、n+ ドープされた a - Si : H 層の第 4 の部分 524D、チャネル 540、及び頂部窒化物層 542 の少なくとも一部分を含み得る。チャネル 540 及び頂部窒化物層 542 は、ソース 142A とドレイン 146 との間に少なくとも部分的に位置付けられ得る。

40

#### 【0047】

一実施形態では、光スイッチ 110A の分離された a - Si : H 層 520 は、同じ a - Si : H チャネル材料で実装され得る。しかしながら、プロセスの修正は、光スイッチ 110A が所定のオン / オフ比を有することを確実にするように行うことが必要である。この代替の注入は、後に考察される。

#### 【0048】

図 6 は、一実施形態による、デバイス 100 の第 1 の段の電流電圧特性を示すグラフ 600 を表し、図 7 は、一実施形態による、複数のスタック及び / 又はカスケードされたデバイス 100 の段（例えば、4 段）の電流電圧特性を示すグラフ 700 を表す。グラフ 600、700 はどちらも、デバイス 100 の第 1 の（例えば、オン）状態の 1 つの曲線、及びデバイス 100 の第 2 の（例えば、オフ）状態の別の曲線を示す。グラフから分か

50

るよう、デバイス 100 が 4 段を有する場合、デバイス 100 は、デバイス 100 が單一段を有する場合と比較したときに、4 倍の電圧を発生させ得る。例えば、單一段の実施形態は、最大約 300V で機能し、多段の実施形態は、最大約 1200V で機能する。單一段の実施形態の電流制限は、20  $\mu$ A に設定され、多段の実施形態の電流制限は、50  $\mu$ A に設定される。单一の実施形態及び多段の実施形態の両方について、6 枝を超えるオン／オフ比が示される。

#### 【0049】

図 8 は、一実施形態による、デバイス 100 の第 1 の段の一部分の概略的な側断面図を表す。図 8 の実施形態は、図 5 の実施形態の代替例である。この実施形態では、第 1 の段は、ゲート誘電体層 510 と、ゲート誘電体層 510 に位置付けられたレベル間誘電体 (ILD) 層 512 と、を含み得る。(頂部) 不動態化層 514 は、隨意に省略され得る。

10

#### 【0050】

光スイッチ 110A は、S / D 金属層の 2 つの部分 820A、820B を含み得る。S / D 金属層の部分 820A、820B は、それらが互いに向かってより近くに移動するにつれて各々がゲート誘電体層 510 からより遠くに前進するように、段付きプロファイルを有し得る。光スイッチ 110A はまた、チャネル 840 (例えば、a - Si : H を含む) と、頂部窒化物層 842 と、を含み得る。チャネル 840 は、ゲート誘電体層 510 上に及び / 又は ILD 層 512 内に位置付けられ得る。チャネル 840 は、S / D 金属層の部分 820A、820B の間に少なくとも部分的に位置付けられ得る。頂部窒化物層 842 は、チャネル 840 上に位置付けられ得る。頂部窒化物層 842 は、S / D 金属層の部分 820A、820B の間に少なくとも部分的に位置付けられ得る。

20

#### 【0051】

上で述べられるように、光スイッチ 110A 及び第 2 のトランジスタ 140A は、同じ a - Si : H 材料層を共有し得、これは、層構造及びプロセスを簡略化し得る。示されるように、第 2 のトランジスタ 140A (左側に例示する) 及び光スイッチ 110A (右側に例示する) は、光スイッチ 110A が 2 端子デバイスであるので光スイッチ 110A がゲートを含まないことを除いて、ほぼ同一の構造を共有する。加えて、S / D 金属層 820A、820B とチャネル 840 との間には、n + ドープされた a - Si : H 層が存在しない。この構造は、S / D 金属及び n +、a - Si : H が 1 つのステップでパターン化され、同じマスクパターンを共有すると仮定する従来の a - Si : H TFT プロセスと比較して、構築に追加のステップを必要とし得る。

30

#### 【0052】

しかしながら、図 9 及び図 10 は、光スイッチ 110A 及び第 2 のトランジスタ 140A について異なる接点構造を別個に使用することの重要性を示す。

#### 【0053】

図 9 は、一実施形態による、n + ドープされた a - Si : H 層が、S / D 金属層とチャネルとの間に少なくとも部分的に位置付けられる場合の、光スイッチ 110A の電流電圧特性を示すグラフ 900 を表す。より具体的には、図 9 は、n + ドープされた a - Si : H 層が、図 8 の左側に示される第 2 のトランジスタ 140A と同様に、S / D 金属層とチャネルとの間に位置付けられることを除いて、図 8 の右側に示される光スイッチ 110A と同様の構造を有する光スイッチの電流電圧特性を示す。このデバイスのオン／オフ比は 10 未満であり、不十分である。

40

#### 【0054】

図 10 は、一実施形態による、S / D 金属層 820A、820B が、チャネル 840 (図 8 の右側に示す) 上に少なくとも部分的に位置付けられる (すなわち、と直接接触した) 場合の、光スイッチ 110A の電流電圧特性を示すグラフ 1000 を表す。オン／オフ比は、2 枝を超える程度から 1000 を超えるように改善される。同様に、第 2 のトランジスタ 140A の n + ドープされた a - Si : H 層を伴うことなく、第 2 のトランジスタ 140A は、非常に小さいオン電流を有し得る。

#### 【0055】

50

図11は、一実施形態による、MEMSアクチュエータを駆動するための別の高電圧スイッチングデバイス1100の概略図を表し、図12は、一実施形態による、図11の拡大部分を表す。デバイス1100は、全電気注入であり得るか、又はそれを含み得る。図11に示されるデバイス1100と、図1～図10を参照して説明されるデバイス100との1つの違いは、図11のデバイス1100が、複数のKV範囲まで直接的にスケーラブルであることである。

#### 【0056】

デバイス1100は、複合デバイスであり得るか、又はそれを含み得る。デバイス1100は、1つ以上のトランジスタ（2つが示される：1120、1140）を含み得る。第1の（例えば、上部）トランジスタ1120は、TFTであり得るか、又はそれを含み得る。例えば、第1のトランジスタ1120は、ソース1122と、ゲート1124と、ドレイン1126と、を有する、HiV-TFTであり得るか、又はそれを含み得る。第1のトランジスタ1120は、長く、かつ狭くあり得る。例えば、第1のトランジスタ1120は、約20um～約1000umの長さ、及び約3um～約20umの幅／厚さを有し得る。第1のトランジスタ1120は、インバータ（例えば、第1の段インバータ）としての役割を果たし得る。示される実施形態では、従来のインバタ回路とは異なり、第1のトランジスタ1120の負荷抵抗器が存在しない。

10

#### 【0057】

デバイス1100は、第1の（例えば、オフの）状態と第2の（例えば、オンの）状態との間で作動可能であり得る。デバイス1100は、ゲート1124が第1のトランジスタ1120をオフにしたときに、オフ（例えば、低電流）の状態になり得る。デバイス1100は、ゲート1124が第1のトランジスタ1120をオンにしたときに、オン（例えば、より高い電流）の状態になり得る。

20

#### 【0058】

第2の（例えば、下部）トランジスタ1140もまた、TFTであり得るか、又はそれを含み得る。例えば、第2のトランジスタ1140は、ソース1242と、ゲート1144と、ドレイン1146と、を有する、HiV-TFTであり得るか、又はそれを含み得る。第2のトランジスタ1140は、第1のトランジスタ1120よりも広くなり得る。例えば、第2のトランジスタ1140は、約20um～約1000mmの幅を有し得る。第2のトランジスタ1140は、駆動及び／又は出力トランジスタとしての役割を果たし得る。

30

#### 【0059】

ソース1122、1142は、（例えば、金属によって）接続され得るが、ソース1122、1142は、共有され得ない（例えば、それらの半導体チャネルが分離され得る）。同様に、ドレイン1126、1146は、（例えば、金属によって）接続され得るが、ドレイン1126、1146は、共有され得ない（例えば、それらの半導体チャネルが分離され得る）。トランジスタ1120、1140のサブ構成要素は、デバイス1100が従来のインバータ+出力トランジスタでないように密に結合される。むしろ、デバイス1100は、ソースと、ゲートと、ドレインと、を有する、複合3端子デバイスである。

#### 【0060】

40

第1のトランジスタ1120は、1つ以上のタップ電極（5つが示される：1130A～1130E）を含み得る。電極1130A～1130Eは、第1のトランジスタ1120の非ゲートチャネル（非ゲートドリフト領域とも称される）1132の高電圧ドリフト領域全体に分配され得る。第1のトランジスタ1120の電極1130A～1130Eは、ゲート1124とドレイン1126との間に少なくとも部分的に位置付けられ得る。電極1130Aのうちの1つは、第2のトランジスタ1140のゲート1144に接続され得る。

#### 【0061】

第2のトランジスタ1140は、1つ以上のフィールドプレート（5つが示される：1148A～1148E）を含み得る。第2のトランジスタ1140のゲート1144及

50

びフィールドプレート 1148A ~ 1148E は、第 1 のトランジスタ 1120 の電極 1130A ~ 1130E に（例えば、直接）接続され得る。フィールドプレート 1148A ~ 1148E は、ゲート 1144 とドレイン 1126、1146 との間に少なくとも部分的に位置付けられ得る。フィールドプレート 1148A ~ 1148E は、第 2 のトランジスタ 1140 の非ゲートチャネル（非ゲートドリフト領域とも称される）1152 全体に高電圧を実質的に一様に分配し得、これは、早期の破壊を低減及び／又は防止し得る。示されるように、非ゲートチャネル 1132、1152 は、ゲート 1124、1144 とドレイン 1126、1146 との間に少なくとも部分的に位置付けられ得る。デバイス 1100 の動作電圧範囲は、第 1 のトランジスタ 1120 の電極 1130A ~ 1130E の数を増加させることによって、及び／又は第 2 のトランジスタ 1140 のフィールドプレート 1148A ~ 1148E の数を増加させることによって拡大され得る。

10

#### 【0062】

ソース 1122、1142、ゲート 1144、ドレイン、1126、1146、電極 1130A ~ 1130E、又はそれらの組み合わせは、第 1 の材料（例えば、S / D 金属）で作製され得る。ゲート 1124、フィールドプレート 1148A ~ 1148E、又はそれらの組み合わせは、第 1 の材料とは異なる第 2 の材料（例えば、ゲート金属）で作製され得る。チャネル 1132、1152 は、第 1 及び第 2 の材料とは異なる第 3 の材料（例えば、a : Si : H）で作製され得る。

#### 【0063】

図 11 に示されるように、デバイス 1100 は、1 つ以上のパッド（4 つが示される：1160A ~ 1160D）に接続され得る。パッド 1160A ~ 1160D は、プローブステーションを使用してプローブするために使用されるように構成されている、金属パッドであり得る。示されるように、パッド 1160A は、ソース 1122、1142 に接続され得、パッド 1160B は、ゲート 1144 に接続され得、パッド 1160D は、ドレイン 1126、1146 に接続され得る。

20

#### 【0064】

第 1 のトランジスタ 1120 は、修正された（例えば、非従来型の）構造を有し得る。より具体的には、ソース 1122、ゲート 1124、及びドレイン 1126 に加えて、第 1 のトランジスタ 1120 はまた、ゲート 1124 とドレイン 1126 との間の非ゲートドリフト領域 1132 に沿って分配された 1 つ以上のタップ付きドレインを含み得る。タップ付きドレインは、ゲート 1144 及び／又は電極 1130A ~ 1130E であり得るか、又はそれを含み得る。タップ付きドレインは、第 2 のトランジスタ 1140 のステップ電圧をサンプリングするように構成され得る。タップ付きドレインはまた、又はその代わりに、第 2 のトランジスタ 1140 のフィールドプレート電圧を提供するように構成され得る。一実施形態では、タップ付きドレインは、第 1 のトランジスタ 1120 のフィールドプレートであり得る。別の実施形態では、タップ付きドレインは、第 1 のトランジスタ 1120 のフィールドプレートでない場合がある。

30

#### 【0065】

一実施形態では、電極 1130 は、第 1 のトランジスタ 1120 のフィールドプレート及び／又はドレインとしての役割を果たし得る。一実施形態では、ゲート 1144 は、第 1 のトランジスタ 1120 のフィールドプレート及び／又はドレインとしての役割を果たし得る。一実施形態では、電極 1130 は、第 2 のトランジスタ 1140 のフィールドプレートとしての役割を果たし得る。

40

#### 【0066】

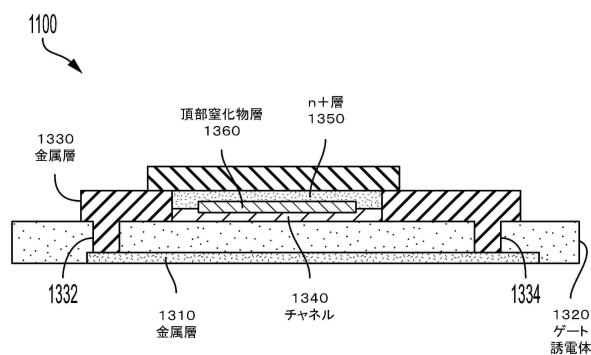

図 13 は、一実施形態による、図 11 の線 13 - 13 で切断した、デバイス 1100 の一部分の概略側断面図を表す。断面は、図 11 ではゲート 1144 を通っているように示されているが、断面はまた、又はその代わりに、電極 1130A ~ 1130E のうちの任意の 1 つを通って切断され得る。

#### 【0067】

デバイス 1100 は、第 1 の（例えば、下部）金属層 1310 を含み得る。第 1 の金

50

属層 1310 は、ゲート 1124 と同じ種類の金属で作製され得る。ゲート誘電体層 1120 は、第 1 の金属層 1310 に少なくとも部分的に位置付けられ得る。第 2 の（例えば、上部）金属層 1330 は、ゲート誘電体層 1120 に少なくとも部分的に位置付けられ得る。第 2 の金属層 1330 は、ドレイン 1126 と同じ種類の金属で作製され得る。少なくとも 1 つの実施形態では、金属層 1310、1330 は、同じ種類の金属で作製され得る。別の実施形態では、金属層 1310、1330 は、異なる種類の金属で作製され得る。第 2 の金属層 1330 は、第 1 の金属層 1310 に向かってゲート誘電体層 1120 を通して少なくとも部分的に拡大する、1 つ以上の脚部（2 つが示される：1332、1334）を含み得る。少なくとも 1 つの実施形態では、脚部 1332、1334 は、第 1 の金属層 1310 に位置付けられ、及び／又は接触する。

10

## 【0068】

チャネル 1340 は、第 2 の金属層 1330 内に少なくとも部分的に位置付けられ得る。チャネル 1340 は、a : Si : H で作製され得る。n+層 1350 は、第 2 の金属層 1330 内に少なくとも部分的に位置付けられ得る。n+層 1350 は、少なくとも部分的にチャネル 1340 上に及び／又はその上側に位置付けられ得る。n+層 1350 は、n+ドープされた a - Si : H 層であり得るか、又はそれを含み得る。頂部窒化物層 1360 は、第 2 の金属層 1330 内に少なくとも部分的に位置付けられ得る。頂部窒化物層 1360 は、チャネル 1340 と n+層 1350 との間に少なくとも部分的に位置付けられ得る。例えば、頂部窒化物層 1360 は、チャネル 1340 の上側に、かつ頂部窒化物層 1360 の下側に位置付けられ得る。

20

## 【0069】

第 3 の金属層 1370 は、第 2 の金属層 1330 及び／又は n+層 1350 上に及び／又はその上側に少なくとも部分的に位置付けられ得る。第 3 の金属層 1370 は、第 2 の金属層 1330 と同じ種類の金属で作製され得る。少なくとも 1 つの実施形態では、層 1330、1370 は、同じ層であり得る。

## 【0070】

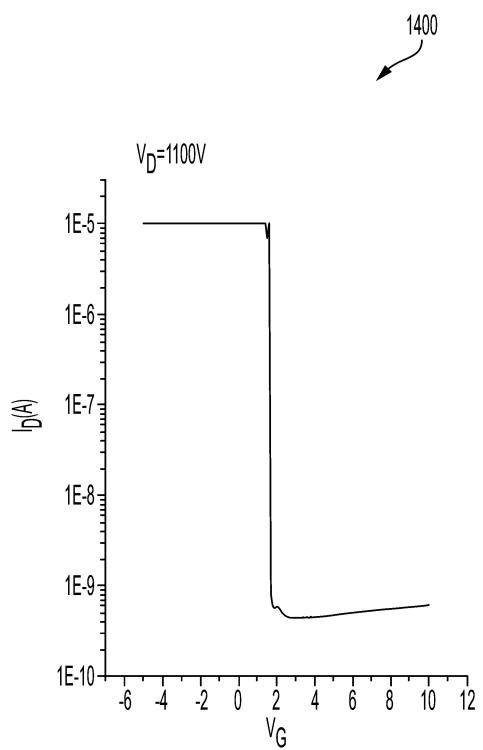

図 14 は、一実施形態による、このデバイス 1100 の変換特性を示すグラフ 1400 を表す。低入力ゲート電圧 ( $V_g < 2 \text{ V}$ ) において、デバイス 1100 は、10  $\mu\text{A}$ （例えば、器具コンプライアンス設定）を超えるオン電流を有する「オン」状態であり、有する。高いゲート入力電圧 ( $V_g > 2.5 \text{ V}$ ) の場合、デバイス 1100 は、オフ状態であり、漏出電流は、1100  $\text{V}$  で数百  $\text{pA}$  であり得る。一実施形態では、1100  $\text{V}$  は、デバイス 1100 が提供することができる最高電圧であり得る。入力電圧は、-5  $\text{V}$  ~ +10  $\text{V}$  へとスイープされ得、S/D ドレインは、測定設定の最大電圧範囲（例えば、1100  $\text{V}$ ）に設定され得る。電流対応は、10  $\mu\text{A}$  に設定される。デバイス 1100 は、4 ~ 5 衍のオン／オフを達成し得る。

30

## 【0071】

本教示の広い範囲を記載する数値範囲及びパラメータは近似値であるにもかかわらず、特定の実施例に記載される数値は、可能な限り正確に報告される。しかしながら、いかなる数値も、それぞれの試験測定において見られる標準偏差から必然的に生じる特定の誤差を本質的に含む。更に、本明細書に開示される全ての範囲は、その中に含まれるありとあらゆるサブ範囲を包含すると理解されるべきである。例えば、「10 未満」の範囲は、0 の最小値と 10 の最大値との間の（0 の最小値と 10 の最大値とを含む）ありとあらゆるサブ範囲、すなわち、0 以上の最小値及び 10 以下の最大値を有するありとあらゆるサブ範囲、例えば、1 ~ 5 を含み得る。

40

## 【0072】

本教示は、1 つ以上の実装態様に対して示されているが、添付の特許請求の範囲の趣旨及び範囲から逸脱することなく、示された実施例に対して変更及び／又は修正が行われ得る。例えば、プロセスが一連の行為又は事象として説明されているが、本教示は、そのような行為又は事象の順序によって限定されないことが理解され得る。一部の行為は、異なる順序で、及び／又は本明細書に記載されているものとは別の他の行為若しくは事象と

50

同時に発生する可能性がある。また、全てのプロセス段階が、本教示の1つ以上の様又は実施形態に従う方法論を実装するために必要とされ得るわけではない。構造的物体及び／若しくは処理段階が追加され得るか、又は既存の構造的物体及び／若しくは処理段階が除去若しくは修正され得ることが理解され得る。更に、本明細書に示される行為のうちの1つ以上は、1つ以上の別個の行為及び／又は段階で実行され得る。更に、「含む (including)」、「含む (includes)」、「有する (having)」、「有する (has)」、「有する (with)」という用語、又はそれらの変形が発明を実施するための形態及び特許請求の範囲のいずれかで使用される限りにおいて、そのような用語は、「含む (comprising)」という用語と同様の様式で包括的であることが意図されている。「少なくとも1つ」の用語は、列挙された項目のうちの1つ以上が選択され得ることを意味するよう使用される。更に、本明細書における考察及び特許請求の範囲において、2つの材料に対して使用される「上」という用語、他方「上」の一方は、材料間の少なくとも一部の接触を意味し、一方、「の上」は、材料が、場合によっては、接触が可能であるが必要とされないように、1つ以上の追加の介在材料に近接していることを意味する。「上 (on)」又は「の上 (over)」のいずれも、本明細書で使用される場合にいかなる指向性も暗示しない。「共形」という用語は、下にある材料の角度が共形材料によって保持されるコーティング材料を記述する。「約」という用語は、変更が、示された実施形態に対してプロセス又は構造の不適合とならない限り、列挙される値が少し変更され得ることを示す。「結合する」、「結合される」、「接続する」、「接続」、「接続される」、「と接続して」、及び「接続している」という用語は、「と直接接続する」又は「1つ以上の中间要素又は部材を介して接続する」ことを指す。最後に、「例示の」又は「例示的な」という用語は、説明が理想的であることを意味するのではなく一例として使用されることを示す。本教示の他の実施形態は、本明細書及び本明細書での本開示の慣行を考慮して当業者に明らかであり得る。本明細書及び実施例は、例示としてのみみなされることが意図され、本教示の真の範囲及び趣旨は、以下の特許請求の範囲によって示される。

## 【図面】

## 【図1】

## 【図2】

10

20

30

40

50

【図3】

【図4】

10

【図5】

【図6】

20

30

40

50

【図 7】

【図 8】

10

20

30

40

【図 9】

【図 10】

50

【図 1 1】

【図 1 2】

10

20

【図 1 3】

【図 1 4】

30

40

50

## フロントページの続き

(51)国際特許分類

F I

H 1 0 D 84/83 1 0 1 E

B 8 1 B 7/02

上杉 浩

(74)代理人 100120525

弁理士 近藤 直樹

(74)代理人 100139712

弁理士 那須 威夫

(72)発明者 チョンピン・ルー

アメリカ合衆国 カリフォルニア州 94304 パロアルト, コヨーテ ヒル ロード 3333,

パロ アルト リサーチ センター インコーポレイテッド宛

審査官 市川 武宜

(56)参考文献

特開2009-260305 (JP, A)

特開平11-121731 (JP, A)

特開2012-160250 (JP, A)

特開平5-3320 (JP, A)

特開平4-154128 (JP, A)

特開2020-98883 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

B 8 1 B 7 / 0 2

H 1 0 D 3 0 / 6 7

H 1 0 D 6 2 / 1 0

H 1 0 D 8 4 / 8 3

H 1 0 D 8 6 / 4 0