## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) Int. Cl. (45) 공고일자 2006년09월19일

*G11C 11/4067* (2006.01) (11) 등록번호 10-0623603

*G11C 7/00* (2006.01) (24) 등록일자 2006년09월06일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2005-0000345 | (65) 공개번호 | 10-2005-0072673 |

| (22) 출원일자 | 2005년01월04일     | (43) 공개일자 | 2005년07월12일     |

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2004-00001057 | 2004년01월06일 | 일본(JP) |

|            | JP-P-2004-00262033 | 2004년09월09일 | 일본(JP) |

(73) 특허권자 미쓰비시덴키 가부시키가이샤

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 7반 3고

(72) 발명자 사카타히로시

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 2반 3고 미쓰비시덴키 가부

시키가이샤 나이

타나카토모후미

일본국 도쿄도 지요다쿠 마루노우치 2쵸메 2반 3고 미쓰비시덴키 가부

시키가이샤 나이

(74) 대리인 권태복

이화의

심사관 : 장호근

---

#### (54) 반도체장치 및 반도체장치 모듈

---

#### 요약

센트저항을 사용하지 않고 단락보호기능을 실현한 반도체장치 및 해당 반도체장치를 내장한 IPM을 제공한다. 절연 게이트형 트랜지스터인 트랜지스터(12)의 게이트 전극에는, 제어장치(LIC)의 제어신호 출력단자( $U_{ou_T}$ )로부터 제어출력신호가 제공되지만, 절연 게이트형 트랜지스터에서는, 해당 트랜지스터가 단락상태가 되면 제어출력신호에도 영향이 미치고, 정상동작상태와는 다른 신호파형이 된다. 이것을 이용하고, 절연 게이트형 트랜지스터의 제어출력신호를 모니터함으로써 단락상태를 검지하고, 단락상태가 된 경우에는, 강제적으로 해당 제어출력신호를 정지함으로써 절연 게이트형 트랜지스터의 단락 보호를 행한다.

#### 대표도

도 2

#### 색인어

반도체, 모듈, 절연 게이트, IGBT, 트랜지스터, 패키징, 단락보호

## 명세서

### 도면의 간단한 설명

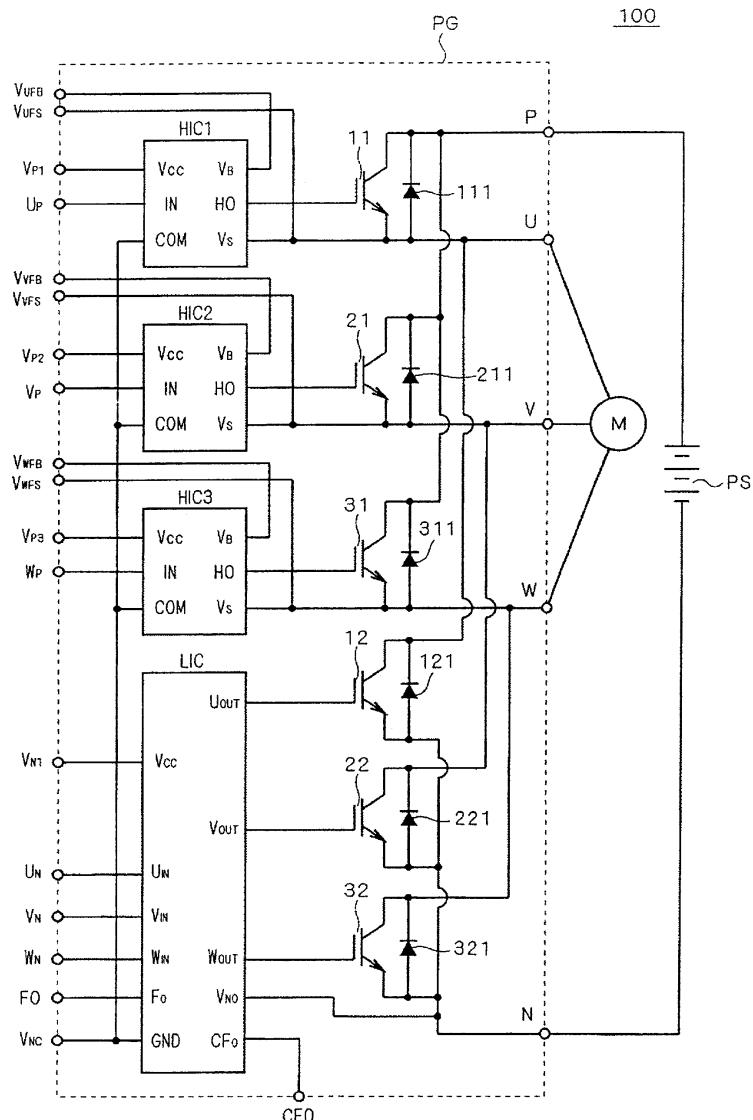

도 1은 본 발명에 관한 인버터 모듈의 구성을 나타내는 도면이다.

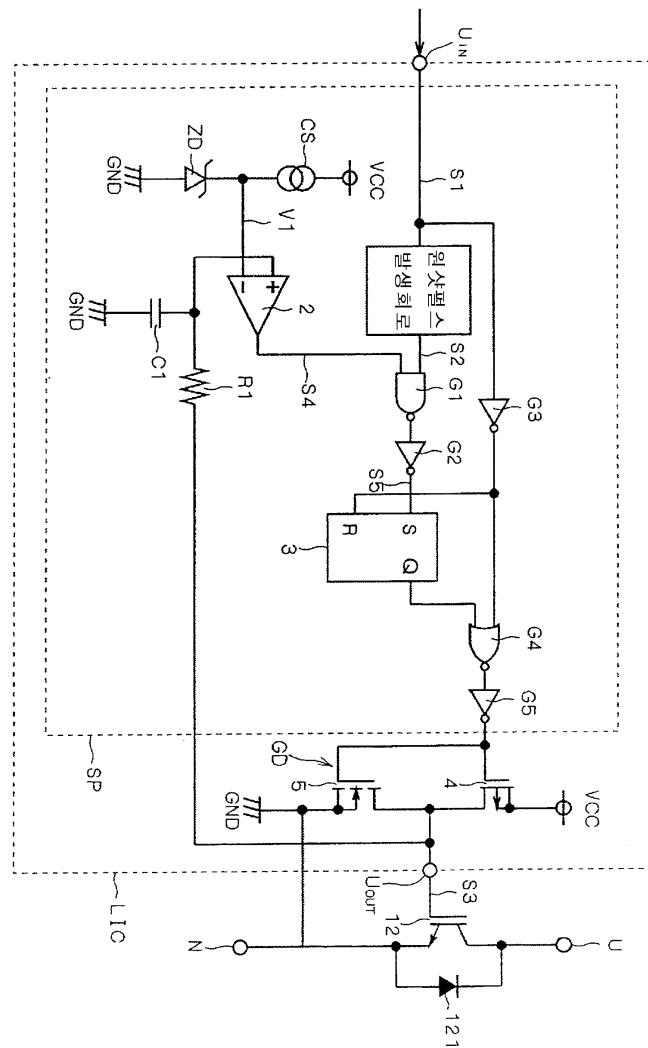

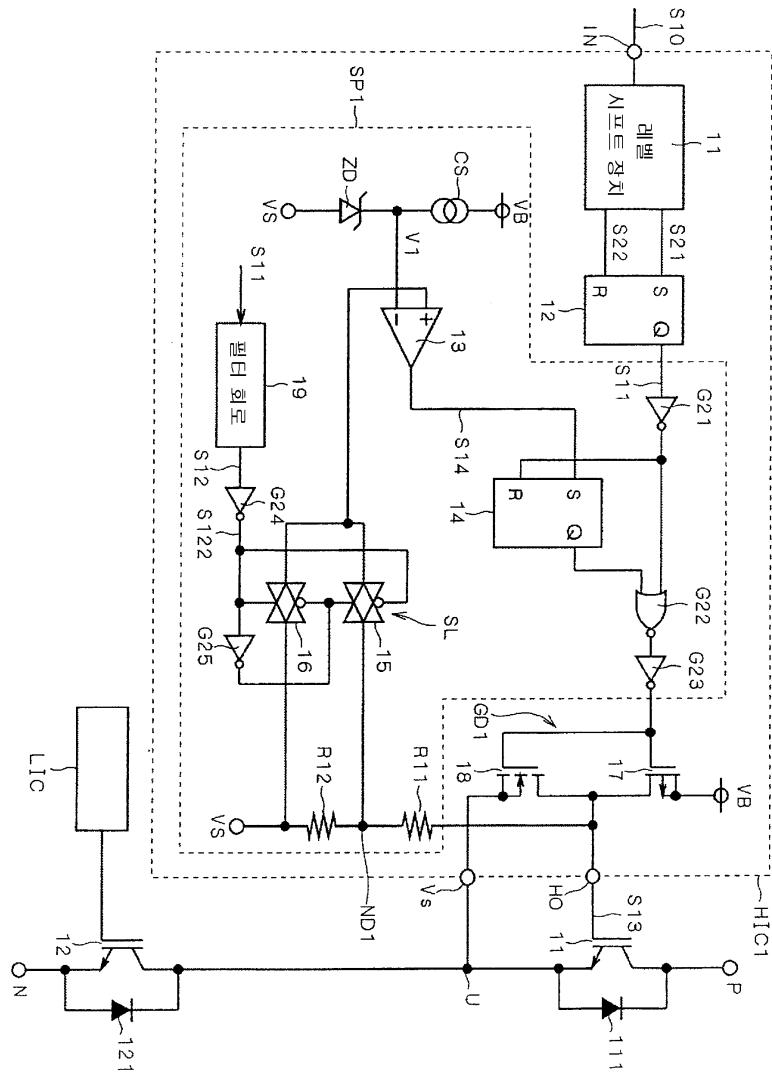

도 2는 본 발명에 관한 실시예 1의 제어장치의 구성을 나타내는 도면이다.

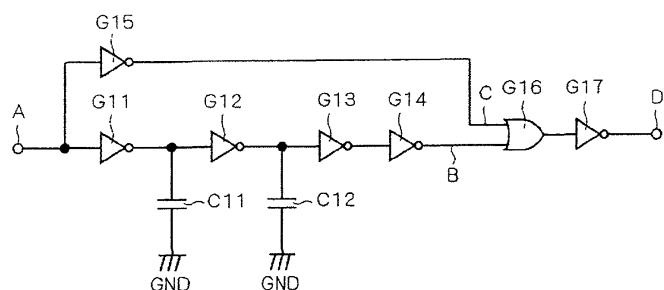

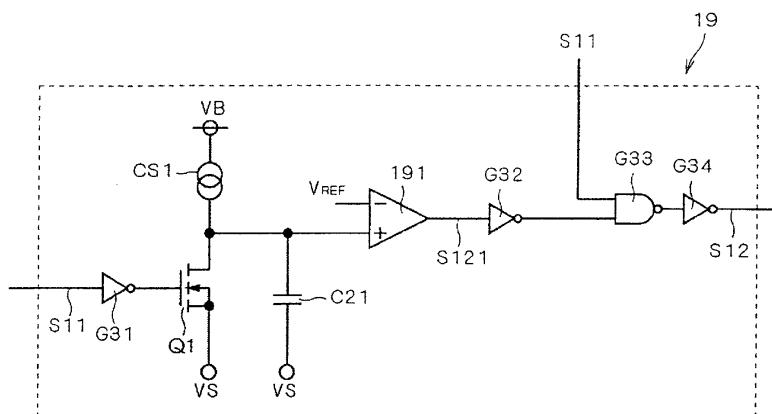

도 3은 원샷펄스 발생회로의 구성을 나타내는 도면이다.

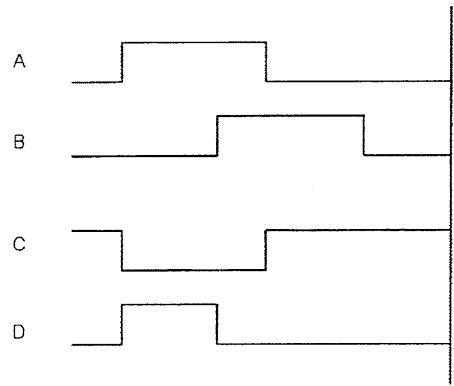

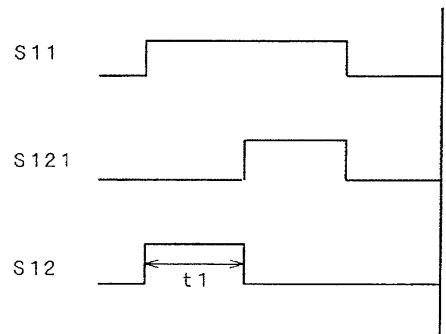

도 4는 원샷펄스 발생회로의 동작을 설명하는 타이밍 차트이다.

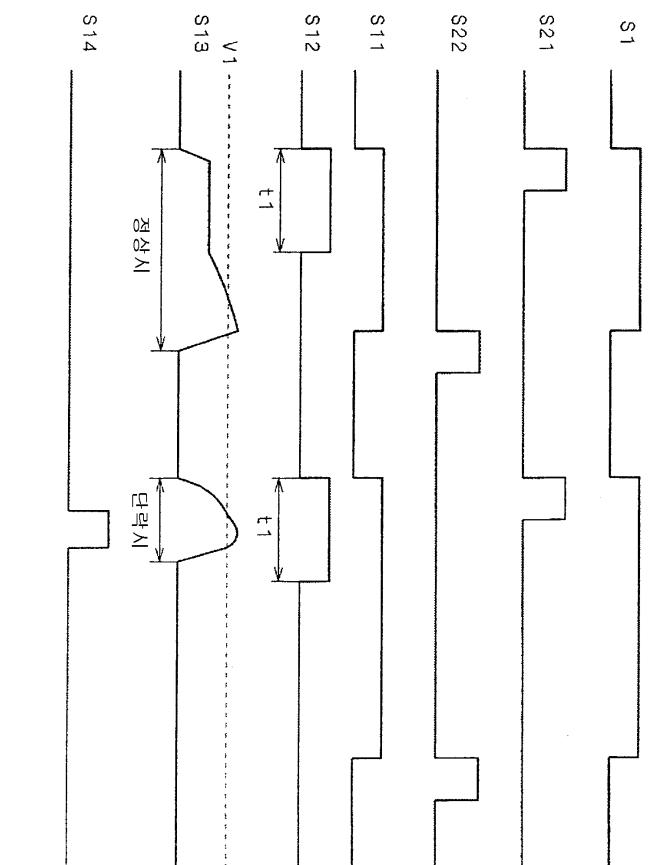

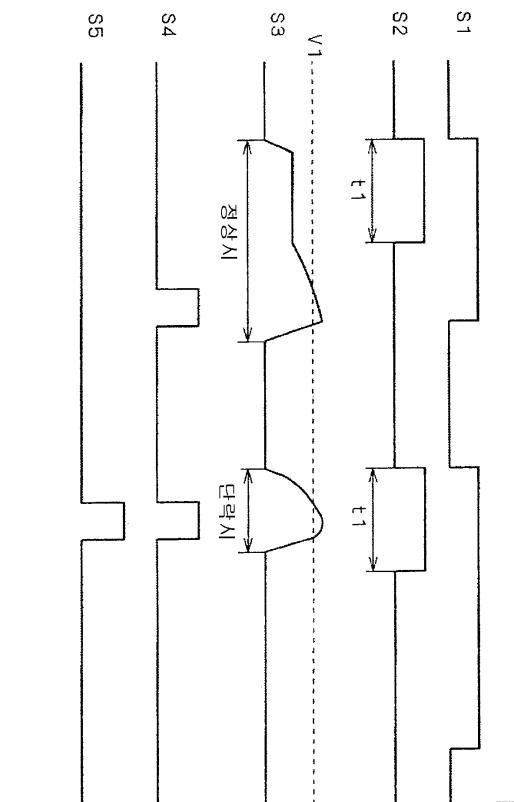

도 5는 본 발명에 관한 실시예 1의 제어장치의 동작을 설명하는 타이밍 차트이다.

도 6은 본 발명에 관한 실시예 2의 제어장치의 구성을 나타내는 도면이다.

도 7은 필터회로의 구성을 나타내는 도면이다.

도 8은 필터회로의 동작을 설명하는 타이밍 차트이다.

도 9는 본 발명에 관한 실시예 2의 제어장치의 동작을 설명하는 타이밍 차트이다.

### \*도면의 주요 부분에 대한 부호의 설명\*

LIC, HIC1~HIC3 : 제어장치 GD, GD1 : 게이트 드라이버

SP, SP1 : 단락보호회로 SL : 신호선택부

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체장치 및 반도체장치 모듈에 관한 것으로서, 특히 IGBT(절연 게이트형 바이폴라 트랜지스터) 등의 절연 게이트형의 스위칭 디바이스의 단락보호기능을 구비한 반도체장치 및 반도체장치 모듈에 관한 것이다.

IGBT 등의 절연 게이트형의 스위칭 디바이스와, 해당 스위칭 디바이스의 구동제어를 행하는 제어회로가 패키징된 반도체 장치는, IPM(Intelligent Power Module)이라 호칭되지만, 종래의 IPM에서는 패키지의 외부에, 스위칭 디바이스의 주전원 단자 사이에 흐르게 되는 주전류를 검출하는 센트저항을 접속하고, 주전류를 모니터함으로써 단락 보호를 행하고 있었다.

예를 들면, 특허문현 1에서는, 패키지의 외부에서, 주전원 단자 사이에 흐르게 되는 주전류를 검출하는 센트저항이 접속된 구성이 개시되어 있고, 패키지에는 센트저항에 걸리는 전압을 검출하기 위한 전류검출단자가 설치되어 있었다.

[특허문현 1] 일본국 특허공개 2002-247857호 공보(도 1)

#### 발명이 이루고자 하는 기술적 과제

전술한 바와 같이 종래의 IPM에서는, 패키지의 외부에 설치한 센트저항에 의해 스위칭 디바이스의 주전류를 검출함으로써 단락 보호를 행하고 있었으므로, 센트저항에 걸리는 전압을 검출하기 위한 전류검출단자가 필요했었다.

또한, 센트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위해, CR 필터 등의 필터회로를 패키지의 외부에 설치할 필요가 있고, 장치가 대형화할 가능성이 있었다.

또한, 션트저항을 설치함으로써, 스위칭 디바이스의 접지측 주전극으로부터 접지단자까지의 배선길이가 길어지면, 스위칭 디바이스의 스위칭에 따른 전압 서지가 커지고, 오동작을 일으킬 가능성도 있었다.

본 발명은 상기와 같은 문제점을 해소하기 위해 이루어진 것으로, 션트저항을 사용하지 않고 단락보호기능을 실현한 반도체장치 및 해당 반도체장치를 내장한 IPM을 제공하는 것을 목적으로 한다.

### 발명의 구성 및 작용

본 발명의 청구항 제1항 기재의 반도체장치는, 제어입력신호에 의거하여 제어출력신호를 생성해서 절연 게이트형 트랜지스터의 구동제어를 행하는 반도체장치에 있어서, 상기 제어출력신호를 출력하는 드라이버와, 상기 제어출력신호를 검출하고, 상기 제어출력신호가 상기 절연 게이트형 트랜지스터의 도통을 지시하고나서 소정기간 경과하기까지의 사이에, 상기 제어출력신호의 검출전압이 소정의 기준전압을 초과하는 경우에는, 상기 제어출력신호를 강제적으로 정지하도록 상기 드라이버를 제어하는 단락보호회로를 구비하고 있다.

본 발명의 청구항 제6항 기재의 반도체장치 모듈은, 고전위의 제1 주전원단자와 저전위의 제2 주전원단자와의 사이에 직렬로 개재되고, 상보적으로 동작하는 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터와, 고전위측의 상기 제1 절연 게이트형 트랜지스터의 구동제어를 행하는 제1 제어장치와, 저전위측의 상기 제2 절연 게이트형 트랜지스터의 구동제어를 행하는 제2 제어장치를 구비하고, 상기 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터, 상기 제1 및 제2 제어장치가 폐키지에 수지밀봉되고, 상기 제2 제어장치로서, 청구항 제2항 또는 제3항 기재의 상기 반도체장치를 사용한다.

본 발명의 청구항 제7항 기재의 반도체장치 모듈은, 고전위의 제1 주전원단자와 저전위의 제2 주전원단자와의 사이에 직렬로 개재되고, 상보적으로 동작하는 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터와, 고전위측의 상기 제1 절연 게이트형 트랜지스터의 구동제어를 행하는 제1 제어장치와, 저전위측의 상기 제2 절연 게이트형 트랜지스터의 구동제어를 행하는 제2 제어장치를 구비하고, 상기 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터, 상기 제1 및 제2 제어장치가 폐키지에 수지밀봉되며, 상기 제1 제어장치로서, 청구항 제4항 기재의 상기 반도체장치를 사용한다.

본 발명의 청구항 제1항 기재의 반도체 장치에 의하면, 절연 게이트형 트랜지스터의 제어출력신호를 검출하고, 제어출력신호가 절연 게이트형 트랜지스터의 도통을 지시하고나서 소정기간 경과하기까지 그 사이에, 제어출력신호의 검출전압이 소정의 기준전압을 초과하는 경우에는, 제어출력신호를 강제적으로 정지하도록 드라이버를 제어하는 단락보호회로를 구비하므로, 단락 보호를 위한 구성을 간단화할 수 있다.

본 발명의 청구항 제6항 기재의 반도체장치 모듈에 의하면, 저전위측의 절연 게이트형 트랜지스터의 제어출력신호를 모니터함으로써 단락상태를 검지하고, 절연 게이트형 트랜지스터가 단락상태가 된 경우에는, 강제적으로 제어출력신호를 정지하는 제2 제어장치를 내장하므로, 폐키지의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 폐키지에도 제2 제어장치에도 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되고, 장치를 전체적으로 소형화 할 수 있다. 또한 션트저항이 불필요하게 되므로, 절연 게이트형 트랜지스터의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭에 따른 전압 서지를 감소할 수 있다.

본 발명의 청구항 제7항 기재의 반도체장치 모듈에 의하면, 고전위측의 절연 게이트형 트랜지스터의 제어출력신호를 모니터함으로써 단락상태를 검지하고, 절연 게이트형 트랜지스터가 단락상태가 된 경우에는, 강제적으로 제어출력신호를 정지하는 제2 제어장치를 내장하므로, 폐키지의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 폐키지에 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되고, 장치를 전체적으로 소형화 할 수 있다. 또한 션트저항이 불필요하게 되므로, 절연 게이트형 트랜지스터의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭에 따른 전압 서지를 감소할 수 있다.

### [발명의 실시예]

<본 발명을 적용한 IPM의 구성 예>

도 1에 본 발명을 적용한 IPM(Intelligent Power Module)의 일례로서, 인버터 모듈(100)의 내부 구성을 설명한다. 이때, 인버터 모듈(100)은, 패키지(PG)의 2개의 길이방향 측면에, 각각 1열에 단자열이 설치된 DIP(Dual-In-line Package) 구조로 되어 있다.

도 1에 나타내는 바와 같이 전원 PS에 접속되고, 주전원단자가 되는 P-N 단자 사이(고전위의 주전원단자 P와 저전위의 주전원단자 N과의 사이)에, IGBT(절연 게이트형 바이폴라 트랜지스터) 등의 절연 게이트형 스위칭 디바이스인 트랜지스터 11 및 12, 21 및 22, 31 및 32(모두 N 채널형)의 쌍이 토템폴 접속되고, 각각의 접속 노드가 패키지(PG)의 U상, V상, W상의 출력단자 U, V, W에 접속되어 있다. 이때, 출력단자 U, V, W에는, 예를 들면 3상 모터 M의 각 상이 접속된다.

또한, 트랜지스터 11, 12, 21, 22, 31 및 32에는, 각각 프리휠링 다이오드 111, 121, 211, 221, 311 및 321이 역병렬접속되어 있다.

그리고, 고전위측 디바이스인 트랜지스터 11, 21 및 31을 각각 제어하기 위해, 제어장치 HIC1, HIC2 및 HIC3이 배치되어 있다. 이때, 제어장치 HIC1~HIC3은 소위 HVIC(고전압 집적회로 : High Voltage Integrated Circuit)이며, 기능적으로 동일한 것이므로, 단자부호는 동일한 것으로 한다.

트랜지스터 11, 21 및 31의 각각의 게이트 전극에는, 제어장치 HIC1, HIC2 및 HIC3의 각각의 제어신호 출력단자 HO로부터 제어출력신호가 제공되는 구성으로 되어 있다.

또한, 제어장치 HIC1~HIC3의 각 기준전위단자 Vs는, 각각 출력단자 U, V, W에 접속되는 동시에, 패키지(PG)의 기준전위단자 V<sub>UFS</sub>, V<sub>VFS</sub>, V<sub>WFS</sub>에 접속되어 있다. 또한, 제어장치 HIC1~HIC3의 각 구동전압단자 VB는 각각 패키지(PG)의 구동전압단자 V<sub>UFB</sub>, V<sub>VFB</sub>, V<sub>WFB</sub>에 접속되어 있다. 이때, 구동전압단자 VB는 고전위측의 구동전압 VB를 각 HVIC 내에 공급하는 단자이며, 기준전위단자 Vs는, 고전위측의 기준전위 VS를 각 HVIC 내에 공급하는 단자이다.

또한, 제어장치 HIC1~HIC3은 모두 구동전압단자 Vcc, 접지단자 COM, 제어신호 입력단자 IN을 가지고 있다.

그리고, 제어장치 HIC1~HIC3의 각 구동전압단자 Vcc는 각각 패키지(PG)의 구동전압단자 Vp1, Vp2 및 Vp3에 접속되고, 각 접지단자 COM은 패키지(PG)의 접지단자 VNC에 공통으로 접속되어 있다.

또한, 제어장치 HIC1~HIC3의 각 제어신호 입력단자 IN은, 각각 패키지(PG)의 제어신호 입력단자 Up, Vp 및 Wp에 접속되어 있다.

또한, 인버터 모듈(100) 내에는, 저전위측 디바이스인 트랜지스터 12, 22 및 32를 제어하기 위해, 제어장치(LIC)가 배치되어 있다. 이때, 제어장치(LIC)는 소위 LVIC(저전압 집적회로 : Low Voltage Integrated Circuit)이다.

트랜지스터 12, 22 및 32의 각 게이트 전극에는, 각각 제어장치(LIC)의 제어신호 출력단자 U<sub>OUT</sub>, V<sub>OUT</sub> 및 W<sub>OUT</sub>로부터 제어출력신호가 제공되는 구성으로 되어 있다.

또한, 제어장치(LIC)의 기준전위단자 V<sub>NO</sub>는, 패키지(PG)의 저전위측의 주전원단자 N에 접속되어 있다. 이때, 기준전위단자 V<sub>NO</sub>는 저전위측의 기준전위(접지전위)를 제어장치(LIC) 내에 공급하는 단자이다.

또한, 제어장치(LIC)는 트랜지스터 12, 22 및 32의 각각을 제어하기 위한 제어출력신호가 제공되는 제어신호 입력단자 U<sub>IN</sub>, V<sub>IN</sub> 및 W<sub>IN</sub>을 가짐과 동시에, 구동전압단자 V<sub>CC</sub>, 폴트단자 F<sub>O</sub>, 단락 등의 이상 사태가 발생하고나서, 보호 동작을 해제할 때까지의 시간을 설정하는 에러출력 시간설정단자 CF<sub>O</sub>, 접지단자 GND를 가지고 있다.

그리고, 제어장치(LIC)의 구동전압단자 Vcc, 폴트단자 F<sub>O</sub>, 에러출력 시간설정단자 CF<sub>O</sub> 및 접지단자 GND는, 각각 패키지(PG)의 구동전압단자 V<sub>N1</sub>, 폴트단자 FO, 에러출력 시간설정 단자 CFO 및 접지단자 V<sub>NC</sub>에 접속되어 있다.

또한, 제어장치(LIC)의 제어신호 입력단자 U<sub>IN</sub>, V<sub>IN</sub> 및 W<sub>IN</sub>은 각각 패키지(PG)의 제어신호 입력단자 U<sub>N</sub>, V<sub>N</sub> 및 W<sub>N</sub>에 접속되어 있다.

이상 설명한 인버터 모듈(100)은, 종래는 필요로 했던 션트저항 및 션트저항을 접속하는 전류검출단자를 갖지 않고, 단락 보호기능은, 모듈 내의 LVIC 혹은 HVIC가 구비하는 구성으로 되어 있다.

이하, 본 발명에 관한 실시예 1 및 2의 각각에 있어서, 단락보호기능을 LVIC 및 HVIC가 구비하는 경우에 대하여 설명한다.

#### <A. 실시예 1>

##### <A-1. 장치구성>

본 발명에 관한 실시예 1로서, 도 2에 단락보호기능을 구비하는 제어장치(LIC)의 구성을 나타낸다. 이때, 도 2에서는 제어장치(LIC) 중, 트랜지스터 12의 스위칭 제어를 행하는 회로를 예로 들어 설명한다.

도 2에 나타내는 바와 같이 트랜지스터 12의 게이트 전극에는, 제어장치(LIC)의 제어신호 출력단자  $U_{OUT}$ 로부터 제어출력 신호가 제공되지만, 절연 게이트형 트랜지스터에서는, 해당 트랜지스터가 단락상태가 되면 제어출력신호에도 영향이 미치고, 정상동작상태와는 다른 신호파형이 된다. 본 발명은 이 현상에 착안한 것으로, 절연 게이트형 트랜지스터의 제어출력 신호를 모니터함으로써 단락상태를 검지하고, 단락상태가 된 경우에는, 강제적으로 해당 제어출력신호를 정지함으로써 절연 게이트형 트랜지스터의 단락 보호를 행하는 것이다.

구체적으로는, 절연 게이트형 트랜지스터의 제어출력신호, 즉 구동전압 VCC와 접지전위 GND와의 사이에 직렬로 접속된 P 채널 MOS 트랜지스터(4) 및 N 채널 MOS 트랜지스터(5)로 구성되는 게이트 드라이버(GD)의 출력신호를, 제어출력신호(S3)로서 트랜지스터 12의 게이트 전극에 제공하는 동시에, 제어출력신호(S3)의 검출전압으로서 비교기(2)의 +측 입력단자에도 입력하고, 비교기(2)에서, -측 입력단자에 제공되는 기준전압 V1과의 비교를 행하여 비교결과를 비교결과신호(S4)로서 출력한다. 이때, 비교기(2)의 +측 입력 라인에 개재된 저항(R1) 및 해당 +측 입력 라인과 접지전위 GND와의 사이에 개재된 커패시터(C1)는 노이즈 필터를 구성한다.

여기서, 기준전압 V1 공급을 위한 구성으로서는, 예를 들면 도 2에 나타내는 바와 같이 정전류원 CS와 제너레이터 ZD를 사용한 간단한 구성을 들 수 있고, 제너레이터 ZD의 제너전압특성을 사용하여 구동전압 VCC를 원하는 전압으로 클램프함으로써 기준전압 V1을 얻을 수 있다.

한편, 트랜지스터(12)의 제어 때문에, 제어신호 입력단자  $U_{IN}$ 을 통해 외부로부터 제공되는 제어입력신호 S1은 인버터 회로 G3, NOR 회로 G4 및 인버터 회로 G5를 경유해서 게이트 드라이버(GD)에 제공되는 동시에, 원샷(one-shot)펄스 발생회로(1)에도 제공된다.

원샷펄스 발생회로(1)는 제어입력신호 S1의 상승의 타이밍에 맞추어 상승하고, 미리 정한 소정기간만큼 고전위 (「H」) 상태를 유지하는 펄스신호 S2를 단발적으로 출력하는 회로이다.

여기서, 원샷펄스 발생회로(1)의 구성 예 및 동작에 대하여, 도 3 및 도 4를 사용하여 설명한다.

도 3에 나타내는 바와 같이 원샷펄스 발생회로(1)는 직렬로 접속된 4개의 인버터 회로 G11, G12, G13 및 G14와, 인버터 회로(G11~G14)와는 별개로 배치된 인버터 회로 G15와, 인버터 회로 G14 및 G15의 출력을 수신하는 OR 회로 G16과, OR 회로 G16의 출력을 수신하는 인버터 회로 G17과, 인버터 회로 G11과 G12와의 접속점과 접지전위 GND와의 사이 및, 인버터 회로 G12와 G13과의 접속점과 접지전위 GND와의 사이에 각각 배치된 커패시터 C11 및 C12를 가지고 있다.

도 3에서는, 인버터 회로 G11 및 G15의 신호입력부를 A점, 인버터 회로 G14의 출력점을 B점, 인버터 회로 G15의 출력점을 C점, 인버터 회로 G17의 출력점을 D점으로 하고, 각 점에서의 신호상태를 도 4에 나타내고 있다.

이때, 도 4에 나타내는 A점에서의 펄스신호는, 원샷펄스 발생회로(1)에 제공되는 제어입력신호(S1)에 해당한다.

인버터 회로 G11에 입력된 펄스신호는, 인버터 회로 G12 및 G13을 경유하는 동안에, 커패시터 C11의 존재에 의해 지연이 발생하고, 도 4에 나타내는 바와 같이 B점에서는 대폭 지연한 신호가 된다.

한편, 인버터 회로 G15에 입력된 펄스는, C점에서 반전되어 출력되지만 지연은 발생하지 않고 있다. 따라서, B점 및 C점에서의 신호를 OR 회로 G16에 입력하고, OR 회로 G16의 출력을 인버터 회로 G17에 입력하면, D점에서는 신호지연 폭에 해당하는 펄스폭을 가지는 원샷펄스를 얻을 수 있게 된다.

이와 같이, 원샷펄스 발생회로(1)에, 펄스신호를 입력함으로써 입력된 펄스신호의 상승에 동기하고, 회로 내부의 구성으로 설정되는 소정기간만큼 「H」 상태를 유지하는 펄스를 얻을 수 있다.

여기서, 도 2의 설명으로 되돌아간다. 원샷펄스 발생회로(1)의 출력하는 펄스신호 S2는 비교기(2)가 출력하는 비교결과신호(S4)와 함께 NAND 회로 G1에 제공되고, NAND 회로 G1의 출력은 인버터 회로 G2를 경유해서 신호 S5로서 RS 플립플롭회로(3)의 셋트 입력(S)에 제공된다.

또한, RS 플립플롭회로(3)의 리셋트 입력(R)에는, 인버터 회로 G3을 경유해서 반전한 제어입력신호(S1)가 제공되고, RS 플립플롭회로(3)의 Q 출력은 NOR 회로 G4의 한쪽의 입력에 제공된다.

NOR 회로 G4의 다른쪽의 입력에는, 인버터 회로 G3을 경유해서 반전한 제어입력신호 S1이 제공되고, NOR 회로 G4의 출력은 인버터 회로 G5를 경유하여, 반전되어 P 채널 MOS 트랜지스터(4) 및 N 채널 MOS 트랜지스터(5)의 게이트 전극에 제공된다. 이때, 도 2에서 게이트 드라이버(GD) 이외의 요소는 단락보호회로 SP를 구성한다.

#### <A-2. 장치동작>

다음에 도 2를 참조하면서, 도 5에 나타내는 타이밍 차트를 사용하여, 제어장치(LIC)의 동작에 대하여 설명한다.

제어신호 입력단자  $U_{IN}$ 을 통해 외부로부터 제공되는 제어입력신호(S1)는 그 상승에 맞추어 트랜지스터 12를 온하고, 해당 제어입력신호(S1)가 고전위상태에 있는 기간은 트랜지스터 12는 온상태를 유지한다.

따라서, 도 5에 나타내는 바와 같이, 게이트 드라이버(GD)로부터 출력되는 제어출력신호(S3)는 제어입력신호(S1)의 상승에 맞추어 상승된다. 그리고, 제어출력신호(S3)의 전압이 트랜지스터 12의 임계치를 초과하면 트랜지스터 12가 온상태가 되고, 트랜지스터 12의 콜렉터 에미터 사이 전압이 저하하므로, 미러 효과에 의해 제어출력신호(S3)의 전압이, 소정기간, 일정한 전압에 클램프되지만, 그 후는 제어출력신호(S3)의 전압은 게이트 드라이버(GD)의 구동전압 VCC에 거의 동일한 값까지 상승한다. 그리고, 제어입력신호(S1)의 하강에 맞추어 하강하고, 트랜지스터 12를 오프한다.

이와 같이, IGBT 등의 절연 게이트형 스위칭 디바이스인 트랜지스터 12는 정상적으로 동작하고 있는 경우에는, 그 제어출력신호(S3)가 상승으로부터 소정기간은 일정한 전압으로 클램프된다는 특성을 가지고 있다.

여기서, 제어출력신호(S3)는 비교기(2)에도 제공되어 기준전압 V1과 비교되고, 제어출력신호(S3)의 전압이 기준전압 V1을 초과하면, 비교기(2)는 그 출력인 비교결과신호(S4)를 유의상태, 이 경우에는 고전위 「H」 상태로 한다. 그 상태는 제어출력신호(S3)의 전압이 기준전압 V1을 초과하고 있는 동안은 유지된다. 따라서, 도 2에 표시되는 트랜지스터 12가 정상적으로 동작하고 있는 경우(정상시)에 있어서는, 제어출력신호(S3)가, 클램프 기간이 지나쳐 전압이 증가를 시작하고, 기준전압 V1을 초과하면 비교기(2)가 비교결과신호(S4)를 출력한다. 그리고, 제어출력신호(S3)가 하강하기 시작하여 기준전압 V1을 하회하면 비교결과신호(S4)도 하강된다.

이와 같이, 트랜지스터 12가 정상적으로 동작하고 있는 경우에는, 제어출력신호(S3)의 전압이 클램프 기간을 지나친 후에 비교기(2)로부터 출력되는 비교결과신호(S4)가 유의상태가 된다. 이때, 기준전압 V1은 구동전압 VCC보다도 낮고, 클램프 전압보다도 높은 값으로 설정된다. 일례로서는, 클램프 전압의 50% 증가 정도의 값을 채용한다.

여기서, 원샷펄스 발생회로(1)는 제어입력신호(S1)의 상승에 맞추어 유의상태가 되는 펄스신호 S2를 출력하지만, 유의상태, 이 경우에는 「H」 상태에 있는 기간 t1은 제어출력신호(S3)가 일정한 전압으로 클램프되어 있는 기간에 거의 동일하게 되도록 설정되어 있다. 따라서, 트랜지스터 12의 정상시에는 펄스신호 S2와 비교기(2)가 출력하는 비교결과신호(S4)가 동시에 유의상태가 되지 않으므로, RS 플립플롭회로(3)의 셋트 입력에 제공되는 신호 S5는 저전위(「L」)상태를 유지하고, RS 플립플롭회로(3)의 Q 출력도 「L」 상태를 유지한다. 따라서, 제어출력신호 S3도 유지되어, 트랜지스터 12의 온상태가 유지된다.

이와 같이 기간 t1을 설정함으로써 트랜지스터 12의 정상시에 제어출력신호(S3)가 기준전압 V1을 초과하여도, 트랜지스터 12가 강제적으로 오프되는 것을 방지할 수 있다.

한편, 트랜지스터 12의 소스/드레인 사이가 단락한 상태에서 트랜지스터 12가 온한 경우나, 트랜지스터 12에 토템폴 접속되는 트랜지스터 11(도 1)이 온되어 있는 상태에서 트랜지스터 12가 온한 경우(암 단락)에는, 제어출력신호(S3)에는 전압의 클램프 기간이 존재하지 않고, 제어출력신호(S3)의 전압이 급속하게 구동전압 VCC에 거의 동일한 값까지 상승하게 된다. 이 상태를, 도 5에서 단락시의 제어출력신호(S3)의 과정으로서 나타낸다.

도 5에 나타내는 바와 같이 트랜지스터 12의 단락시에는, 제어출력신호(S3)의 전압이 급속하게 상승해서 비교기(2)의 기준전압 V1을 초과하고, 비교기(2)로부터 출력되는 비교결과신호(S4)가 유의상태가 된다.

이때, 원샷펄스 발생회로(1)로부터는, 제어입력신호(S1)의 상승에 맞추어 펄스신호(S2)가 출력되지만, 펄스신호(S2)가 유의상태에 있는 기간에 비교결과신호(S4)도 유의하게 되므로, 펄스신호(S2)와 비교결과신호(S4)가 동시에 유의상태가 되는 기간이 존재하고, 그 기간은 RS 플립플롭회로(3)의 셋트 입력에 제공되는 신호 S5는 「H」 상태가 된다. 그 결과, RS 플립플롭회로(3)의 Q 출력은 「H」 상태로 변하고, 게이트 드라이버(GD)의 P 채널 MOS 트랜지스터(4)가 오프하며, N 채널 MOS 트랜지스터(5)가 온상태가 되고, 제어출력신호(S3)가 「L」 상태가 되어 트랜지스터 12가 강제적으로 오프된다. 이때, 신호 S5는 게이트 드라이버(GD)의 제어출력신호(S3)의 유의출력을 정지하므로 정지신호라 호칭하는 경우도 있다.

#### <A-3. 효과>

이상 설명한 바와 같이, 단락보호기능을 구비하는 제어장치(LIC)에 있어서는, 주회로를 구성하는 트랜지스터 12의 제어출력신호(S3)를 모니터함으로써 단락상태를 검지하고, 트랜지스터 12가 단락상태가 된 경우에는, 강제적으로 제어출력신호(S3)를 정지하도록 했으므로, 인버터 모듈(100)에서는, 종래의 IPM과 같이, 패키지(PG)(도 1)의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 패키지(PG)에도 제어장치(LIC)에도 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화 할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되고, 장치를 전체적으로 소형화 할 수 있다.

또한 션트저항이 불필요하게 되므로, 스위칭 디바이스의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭 디바이스의 스위칭에 따른 전압 서지를 감소할 수 있다.

#### <B. 실시예 2>

##### <B-1. 장치구성>

본 발명에 관한 실시예 2로서, 도 6에 단락보호기능을 구비하는 제어장치 HIC1의 구성을 나타낸다. 이때, 도 6에 나타내는 제어장치 HIC1은, 트랜지스터 11의 스위칭 제어를 행하는 회로이고, 도 1에 나타낸 제어장치 HIC2 및 HIC3도 동일한 기능을 가지고 있다.

도 6에 나타내는 바와 같이 트랜지스터 11의 게이트 전극에는, 구동전압 VB와 기준전위 VS와의 사이에 직렬로 접속된 P 채널 MOS 트랜지스터(17) 및 N 채널 MOS 트랜지스터(18)로 구성되는 게이트 드라이버(GD1)의 출력신호가 제어출력신호(S13)로서 제어신호 출력단자(HO)로부터 제공되는 동시에, 제어출력신호(S13)는 저항 R11 및 저항 R12에서 저항분할되어 제어출력신호(S13)의 검출전압으로서 비교기(13)의 +측 입력단자에도 입력된다.

비교기 13에서는, 일측 입력단자에 제공되는 기준전압 V1과의 비교를 행해서 비교결과가 비교결과신호 S14로서 출력된다. 이때, 기준전압 V1 공급을 위한 구성으로서는, 도 2에 나타낸 구성을 채용하면 된다.

여기서, 제어출력신호 S13을 저항분할하기 위해, 제어신호 출력단자 HO와 기준전위 VS와의 사이에, 저항 R11 및 저항 R12가 직렬을 이루도록 설치되고, 저항 R11 및 저항 R12의 접속점은, 트랜스미션 게이트 15의 입력단에 접속되어 있다. 또한, 저항 R12의 기준전위측 단부는 트랜스미션 게이트 16의 입력단에 접속되고, 트랜스미션 게이트 15 및 16의 출력단은, 비교기(13)의 +측 입력단자에 접속되어 있다.

이와 같이, 제어출력신호 S13을 저항분할하는 구성을 구비함으로써 소위 고전위측의 디바이스인 트랜지스터 11의 제어출력신호 S13을 검출할 수 있다.

이 때, 트랜스미션 게이트 15 및 16은 필터회로(19)가 출력하는 펄스신호 S12에 근거하여 제어출력신호 S13을 저항분할한 전압 및 접지전위를 선택해서 출력하므로, 신호선택부(SL)라 호칭한다.

또한, 필터회로(19)가 출력하는 펄스신호 S12를 인버터 회로 G24에서 반전함으로써 트랜스미션 게이트 15 및 16의 제어신호 S122를 얻을 수 있고, 트랜스미션 게이트 15의 반전 게이트 및 트랜스미션 게이트 16의 게이트에는 제어신호 S122를 제공하고, 트랜스미션 게이트 15의 게이트 및 트랜스미션 게이트 16의 반전 게이트에는 제어신호 S122를 인버터 회로 G25에서 더 반전해서 제공하는 구성으로 되어 있다.

트랜지스터 11의 제어를 위해, 제어신호 입력단자 IN을 통해 외부로부터 제공되는 제어입력신호(S10)는, 레벨시프트를 위한 레벨시프트 장치(11)에 제공된다.

즉, 트랜지스터 11은 고전위측의 디바이스이고, 그 기준전위는 기준전위단자 Vs로부터 공급된다. 따라서, 접지전위를 기준으로서 생성된 제어입력신호(S10)는, 레벨시프트 장치(11)를 통해 고전위측에 레벨시프트할 필요가 있다.

레벨시프트 장치(11)는 제공된 제어입력신호(S10)에 근거하여 트랜지스터 11의 온 및 오프의 타이밍을 지시하는 원샷펄스신호를 생성한다. 이 때, 해당 원샷펄스신호는, 레벨시프트 장치(11) 내의 고내압 트랜지스터를 통해 고전위를 기준으로 하는 신호로 레벨시프트되고, 원샷펄스신호 S21 및 S22로서 출력된다.

그리고, 원샷펄스신호 S21 및 S22는, RS 플립플롭회로 12의 셋트 입력(S) 및 리셋트 입력(R)에 각각 제공되고, RS 플립플롭회로 12의 Q 출력으로부터는, 제어입력신호(S10)와 동등한 레벨시프트 완료신호 S11로서 출력된다.

레벨시프트 완료신호 S11은, 인버터 회로 G21, NOR 회로 G22 및 인버터 회로 G23을 경유해서 게이트 드라이버(GD1)에 제공되는 동시에, RS 플립플롭회로 14의 리셋트 입력에도 제공된다.

한편, RS 플립플롭회로 14의 셋트 입력에는, 비교결과신호 S14가 제공되고, RS 플립플롭회로 14의 Q 출력은 NOR 회로 G22의 한쪽의 입력에 제공된다.

NOR 회로 G22의 다른쪽의 입력에는, 인버터 회로 G21을 경유해서 반전한 레벨시프트 완료신호 S11이 제공되고, NOR 회로 G22의 출력은 인버터 회로 G23을 경유해서 반전되어, P 채널 MOS 트랜지스터 17 및 N 채널 MOS 트랜지스터 18의 게이트 전극에 제공된다.

여기서, 펄스발생회로로서 동작하는 필터회로(19)의 구성에 및 동작에 대해서, 도 7 및 도 8을 사용하여 설명한다.

도 7에 나타내는 바와 같이 필터회로(19)는 정전류원(CS1)과, 정전류원(CS1)에 드레인이 접속되고, 소스가 기준전위 VS에 접속된 N 채널 MOS 트랜지스터(Q1)와, RS 플립플롭회로(12)로부터 출력되는 레벨시프트 완료신호 S11을 받고, 해당 신호 S11을 반전해서 트랜지스터 Q1의 게이트 전극에 제공하는 인버터 회로 G31과, 트랜지스터 Q1의 드레인이 +측 입력단자에 접속되는 비교기(191)와, 트랜지스터 Q1의 드레인과 기준전위 VS와의 사이에 개재된 커패시터 C21과, 비교기 191의 출력신호 S121을 받는 인버터 회로 G32와, 인버터 회로 G32의 출력 및 RS 플립플롭회로 12가 출력하는 레벨시프트 완료신호 S11을 받는 NAND 회로 G33과, NAND 회로 G33의 출력을 반전해서 펄스신호 S12로서 출력하는 인버터 회로 G34를 구비하고 있다.

다음에 동작에 대하여 설명한다. 레벨시프트 완료신호 S11이 「H」 상태가 되어 트랜지스터 Q1이 오프하면, 커패시터 C21을 충전하도록 정전류원 CS로부터 전류가 흐른다. 그리고, 커패시터 C21의 전압이 비교기(191)에 제공되는 기준전압  $V_{REF}$ 의 값을 초과하면 비교기(191)의 출력신호 S121이 「H」 상태가 된다. 이 때, 신호 S121의 상승까지의 시간은, 커패시터 C21의 용량과, 기준전압  $V_{REF}$ 의 값에 의해 설정된다.

도 8에 나타내는 바와 같이, 레벨시프트 완료신호 S11이 「H」 상태이고, 신호 S121이 「L」 상태인 기간은, 펄스신호 S12는 「H」 상태(유의상태)가 되고, 이 기간  $t_1$ 이 단락보호기능을 작동시키는 기간이며, 제어출력신호 S13이 일정한 전압에 클램프되어 있는 기간에 거의 동일하게 되도록 설정되어 있다.

또한, 도 6에서, 게이트 드라이버(GD1), 레벨시프트 장치(11) 및 RS 플립플롭(12) 이외의 요소는 단락보호회로(SP1)를 구성한다.

## <B-2. 장치동작>

다음에, 도 6을 참조하면서, 도 9에 나타내는 타이밍 차트를 사용하여, 제어장치 HIC1의 동작에 대하여 설명한다.

제어신호 입력단자(IN)를 통해 외부로부터 제공되는 제어입력신호(S10)는, 레벨시프트 장치(11)에 의해, 그 상승에 맞추어 상승되는 원샷펄스신호 S21과, 그 하강에 맞추어 상승되는 원샷펄스신호 S22로 변환된다.

그리고, 원샷펄스신호 S21 및 S22는 RS 플립플롭회로(12)에 제공되어, 레벨시프트 완료신호 S11이 된다.

레벨시프트 완료신호 S11은 그 상승에 맞추어 트랜지스터 11을 온하고, 해당 신호 S11이 고전위상태에 있는 기간은 트랜지스터 11은 온상태를 유지한다.

도 9에 나타나 있는 바와 같이, 게이트 드라이버(GD1)로부터 출력되는 제어출력신호 S13은 레벨시프트 완료신호 S11의 상승에 맞추어 상승하고, 레벨시프트 완료신호 S11은 실질적으로 제어입력신호 10과 동일하므로, 레벨시프트 완료신호 S11을 제어입력신호라 호칭하는 경우도 있다.

이때, 트랜지스터 11의 정상동작시 및 단락시의 제어출력신호 S13의 파형에 대해서는, 실시예 1에서 설명한 제어출력신호(S3)와 동일하므로, 설명은 생략한다. 이때, 도 9에서는, 제어출력신호 S13과 기준전압 V1을 비교하도록 나타내고 있지만, 이것은 편의적인 기재이고, 실제로는 제어출력신호 S13의 분압전압과 기준전압 V1을 비교한다.

제어출력신호 S13은 저항 R11 및 R12에 의해 분압되어 비교기(13)에 제공되어 기준전압 V1과 비교되지만, 필터회로(19)가 출력하는 펄스신호 S12가 「L」의 기간은, 트랜스미션 게이트 16이 온하므로, 비교기(13)에는 기준전위 VS가 제공되고, 비교기(13)가 출력하는 비교결과신호 S14는 항상 「L」 상태가 된다.

한편, 펄스신호 S12가 「H」인 기간은, 트랜스미션 게이트 15가 온하므로, 비교기(13)에는 제어출력신호 S13의 분압전압이 제공되고, 비교기(13)가 출력하는 비교결과신호 S14는 해당 분압전압과 이 기준전압 V1과의 비교결과에 근거하여 「H」 또는 「L」 상태가 된다.

즉, 제어출력신호 S13의 분압전압이 기준전압 V1을 초과하면, 비교기(13)는 그 출력인 비교결과신호 S14를 유의상태, 이 경우에는 「H」 상태로 한다.

트랜지스터 11의 단락시에는, 제어출력신호 S13의 전압이 급속하게 상승하고, 그 분압전압이 비교기(13)의 기준전압 V1을 초과하지만, 이때는 펄스신호 S12가 「H」 상태이므로, 비교기(13)는 그 출력인 비교결과신호 S14를 「H」 상태(유의상태)로 한다. 이 상태는 제어출력신호 S13의 분압전압이 기준전압 V1을 초과하고 있는 동안은 유지된다. 그 결과, RS 플립플롭회로 14의 Q 출력은 「H」 상태로 변하고, 게이트 드라이버(GD1)의 P 채널 MOS 트랜지스터 17이 오프하고, N 채널 MOS 트랜지스터 18이 온상태가 되고, 제어출력신호 S13이 「L」 상태가 되어 트랜지스터 11이 강제적으로 오프된다. 이때, 신호 S13은 게이트 드라이버(GD1)의 제어출력신호 S13의 유의출력을 정지하므로 정지신호라 호칭하는 경우도 있다.

이때, 트랜지스터 11이 정상적으로 동작하고 있는 경우(정상시)에 있어서는, 제어출력신호 S13의 클램프 기간이 지나치면 전압이 증가를 시작하고, 기준전압 V1을 초과하지만, 이 시점에서는 펄스신호 S12가 「L」 상태이므로, 비교결과신호 S14는 「L」 상태이다. 그 결과, RS 플립플롭회로(14)의 Q 출력은 「L」 상태를 유지하고, 제어출력신호 S13이 「H」 상태를 유지하므로, 트랜지스터 11은 온상태를 유지한다.

## <B-3. 효과>

이상 설명한 바와 같이, 단락보호기능을 구비하는 제어장치 HIC1에서는, 주회로를 구성하는 트랜지스터 11의 제어출력신호 S13을 모니터함으로써 단락상태를 검지하고, 트랜지스터 11이 단락상태가 된 경우에는, 강제적으로 제어출력신호 S13을 정지하도록 했으므로, 인버터 모듈(100)에서는, 종래의 IPM과 같이, 패키지(PG)(도 1)의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 패키지(PG)에 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화 할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되며, 장치를 전체적으로 소형화 할 수 있다.

또한, 션트저항이 불필요하게 되므로, 스위칭 디바이스의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭 디바이스의 스위칭에 따른 전압 서지를 감소할 수 있다.

또한 필터회로(19)에 의해, 단락보호기능을 작동시키는 기간  $t_1$ 을 설정하고, 해당 기간  $t_1$ 만 제어출력신호 S13을 모니터 하므로, 모니터 시스템에 걸리는 부담을 경감할 수 있다.

#### <B-4. 변형 예>

이상 설명한 실시예 2는 HVIC에의 적용을 전제로 했지만, LVIC에 적용하는 것도 할 수 있다.

그 경우에는, 레벨시프트 장치(11) 및 RS 플립플롭(12)은 불필요하게 되고, 레벨시프트 완료신호 S11 대신에 제어입력신호 S1을 인버터 회로(G21) 및 필터회로(19)에 제공한다. 그리고, 기준전위 VS 대신에, 접지전위 GND를 사용한다.

또한, 이상 설명한 실시예 1 및 2에서는, 각종의 신호는 제어입력신호에 대하여 지연을 갖지 않는 것으로서 취급했지만, 예를 들면 펄스신호 S2는 제어입력신호(S1)에 대하여 다소의 지연이 생길 경우도 있지만, 그 경우에서도 본 발명의 동작에 지장은 생기지 않는다.

또한, 이상에서 설명한 실시예 1 및 2에서는, 절연 게이트형 트랜지스터 11 및 12, 21 및 22, 31 및 32는 모두 N 채널형으로서 설명했지만, 이것들을 P채널형으로 구성하는 것도 할 수 있다.

#### 발명의 효과

본 발명의 청구항 제1항 기재의 반도체장치에 의하면, 절연 게이트형 트랜지스터의 제어출력신호를 검출하고, 제어출력신호가 절연 게이트형 트랜지스터의 도통을 지시하고나서 소정기간 경과하기까지 그 사이에, 제어출력신호의 검출전압이 소정의 기준전압을 초과하는 경우에는, 제어출력신호를 강제적으로 정지하도록 드라이버를 제어하는 단락보호회로를 구비하므로, 단락 보호를 위한 구성을 간단화할 수 있다.

본 발명의 청구항 제6항 기재의 반도체장치 모듈에 의하면, 저전위측의 절연 게이트형 트랜지스터의 제어출력신호를 모니터함으로써 단락상태를 검지하고, 절연 게이트형 트랜지스터가 단락상태가 된 경우에는, 강제적으로 제어출력신호를 정지하는 제2 제어장치를 내장하므로, 패키지의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 패키지에도 제2 제어장치에도 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되고, 장치를 전체적으로 소형화 할 수 있다. 또한 션트저항이 불필요하게 되므로, 절연 게이트형 트랜지스터의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭에 따른 전압 서지를 감소할 수 있다.

본 발명의 청구항 제7항 기재의 반도체장치 모듈에 의하면, 고전위측의 절연 게이트형 트랜지스터의 제어출력신호를 모니터함으로써 단락상태를 검지하고, 절연 게이트형 트랜지스터가 단락상태가 된 경우에는, 강제적으로 제어출력신호를 정지하는 제2 제어장치를 내장하므로, 패키지의 외부에 션트저항을 설치하는 것이 불필요하게 된다. 이 때문에, 패키지에 션트저항의 전압을 측정하기 위한 전류검출단자가 불필요하게 되고, 모듈을 소형화할 수 있는 동시에, 션트저항 및 전류검출단자에 들어가는 노이즈를 제거하기 위한 필터회로도 불필요하게 되고, 장치를 전체적으로 소형화 할 수 있다. 또한 션트저항이 불필요하게 되므로, 절연 게이트형 트랜지스터의 접지측 주전극으로부터 접지단자까지의 배선길이를 짧게 할 수 있고, 스위칭에 따른 전압 서지를 감소할 수 있다.

#### (57) 청구의 범위

##### 청구항 1.

제어입력신호에 의거하여 제어출력신호를 생성해서 절연 게이트형 트랜지스터의 구동제어를 행하는 반도체장치로서,

상기 제어출력신호를 출력하는 드라이버와,

상기 제어출력신호를 검출하고, 상기 제어출력신호가 상기 절연 게이트형 트랜지스터의 도통을 지시하고나서 소정기간 경과하기까지의 사이에, 상기 제어출력신호의 검출전압이 소정의 기준전압을 초과하는 경우에는, 상기 제어출력신호를 강제적으로 정지하도록 상기 드라이버를 제어하는 단락보호회로를 구비한 것을 특징으로 하는 반도체장치.

## 청구항 2.

제 1 항에 있어서,

상기 단락보호회로는, 상기 제어입력신호를 받고, 상기 제어입력신호가 상기 절연 게이트형 트랜지스터의 도통을 지시하는 타이밍에 맞추어서 상기 소정기간만 유의로 되는 제 1 펄스신호를 출력하는 펄스 발생회로와,

상기 제어출력신호의 검출전압을 받고, 상기 기준전압과의 비교를 행하여, 상기 제어출력신호의 검출전압이 상기 기준전압을 초과하는 기간에 유의로 되는 제2 펄스신호를 출력하는 비교기와,

상기 제 1 및 제 2 펄스신호를 받고, 상기 제 1 펄스신호가 유의인 기간에 상기 제 2 펄스신호가 유의로 된 경우에는, 상기 제어출력신호의 출력을 강제적으로 정지하는 정지신호를 출력하는 논리회로를 구비한 것을 특징으로 하는 반도체 장치.

## 청구항 3.

제 1 항에 있어서,

상기 단락보호회로는, 상기 제어입력신호를 받고, 상기 제어입력신호가 상기 절연 게이트형 트랜지스터의 도통을 지시하는 타이밍에 맞추어서 상기 소정기간만 유의로 되는 제 1 펄스신호를 출력하는 펄스 발생회로와,

상기 제어출력신호의 검출전압 및 상기 기준전압보다도 낮은 소정전압을 받고, 상기 제 1 펄스신호에 의거하여 한쪽을 선택하여 출력하는 신호 선택부와,

상기 신호 선택부의 상기 출력을 받고, 상기 기준전압과의 비교를 행하여, 상기 출력이 상기 기준전압을 초과하는 기간에 유의로 되는 제 2 펄스신호를 출력하는 비교기를 구비하고,

상기 신호 선택부는, 상기 제 1 펄스신호를 받고, 상기 제 1 펄스신호가 유의인 기간에는, 상기 제어출력신호의 검출전압을 선택하고, 그 이외의 기간에는 상기 기준전압보다도 낮은 소정전압을 선택하여 출력하고,

상기 비교기는, 상기 제 1 펄스신호가 유의인 기간에만 상기 제어출력신호의 검출전압을 받고, 상기 제어출력신호의 검출전압이 상기 기준전압을 초과한 경우에 상기 제 2 펄스신호를 유의로 하고,

상기 제 2 펄스신호는, 그것이 유의로 된 경우에는, 상기 제어출력신호의 출력을 강제적으로 정지하는 정지신호로서 기능하는 것을 특징으로 하는 반도체 장치.

## 청구항 4.

제 3 항에 있어서,

상기 제어출력신호의 검출전압은, 상기 드라이버의 출력단과 기준전압과의 사이에 직렬로 접속된 분할저항에 의해 검출되는 것을 특징으로 하는 반도체 장치.

## 청구항 5.

제 2 항 또는 제 3 항에 있어서,

상기 제 1 펄스신호가 유의로 되는 상기 소정기간에는, 상기 절연 게이트형 트랜지스터의 정상 동작시에 상기 제어출력신호의 전압이 일정하게 클램프되어 있는 기간에 의거하여 설정되는 것을 특징으로 하는 반도체 장치.

### 청구항 6.

고전위의 제 1 주전원단자와 저전위의 제 2 주전원단자와의 사이에 직렬로 개재되고, 상보적으로 동작하는 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터와,

고전위측의 상기 제1 절연 게이트형 트랜지스터의 구동제어를 행하는 제1 제어장치와,

저전위측의 상기 제2 절연 게이트형 트랜지스터의 구동제어를 행하는 제2 제어장치를 구비하고,

상기 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터, 상기 제1 및 제2 제어장치가 패키지에 수지밀봉되며,

상기 제2 제어장치로서, 청구항 2 또는 청구항 3 기재의 상기 반도체장치를 사용하는 것을 특징으로 하는 반도체장치 모듈.

### 청구항 7.

고전위의 제1 주전원단자와 저전위의 제2 주전원단자와의 사이에 직렬로 개재되고, 상보적으로 동작하는 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터와,

고전위측의 상기 제1 절연 게이트형 트랜지스터의 구동제어를 행하는 제1 제어장치와,

저전위측의 상기 제2 절연 게이트형 트랜지스터의 구동제어를 행하는 제2 제어장치를 구비하고,

상기 적어도 1쌍의 제1 및 제2 절연 게이트형 트랜지스터, 상기 제1 및 제2 제어장치가 패키지에 수지밀봉되며,

상기 제1 제어장치로서, 청구항 4 기재의 상기 반도체장치를 사용하는 것을 특징으로 하는 반도체장치 모듈.

도면

## 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9