(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5547150号

(P5547150)

(45) 発行日 平成26年7月9日(2014.7.9)

(24) 登録日 平成26年5月23日(2014.5.23)

(51) Int.Cl.

F 1

|                    |                  |                   |            |

|--------------------|------------------|-------------------|------------|

| <b>H01L 27/146</b> | <b>(2006.01)</b> | <b>H01L 27/14</b> | <b>A</b>   |

| <b>H04N 5/374</b>  | <b>(2011.01)</b> | <b>H04N 5/335</b> | <b>740</b> |

| <b>H04N 5/357</b>  | <b>(2011.01)</b> | <b>H04N 5/335</b> | <b>570</b> |

| <b>H04N 5/369</b>  | <b>(2011.01)</b> | <b>H04N 5/335</b> | <b>690</b> |

請求項の数 6 (全 12 頁)

(21) 出願番号

特願2011-202814 (P2011-202814)

(22) 出願日

平成23年9月16日 (2011.9.16)

(65) 公開番号

特開2013-65652 (P2013-65652A)

(43) 公開日

平成25年4月11日 (2013.4.11)

審査請求日

平成25年9月2日 (2013.9.2)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 110000235

特許業務法人 天城国際特許事務所

(72) 発明者 関根 弘一

岩手県北上市北工業団地6番6号 岩手東芝エレクトロニクス株式会社内

審査官 多賀 和宏

最終頁に続く

(54) 【発明の名称】 固体撮像素子

## (57) 【特許請求の範囲】

## 【請求項 1】

それぞれ多角形の平面形状を有し、中心部に前記多角形の辺により空間が形成されるように配列された6個のフォトダイオードと、これらのフォトダイオードにより光電変換され、蓄積された信号電荷を検出するために、前記中心部の空間内に配置されたフローティングジャンクションと、前記フォトダイオードに蓄積された信号電荷を前記フローティングジャンクションに読み出すために、前記中心部の空間内に配置された転送ゲートトランジスタと、前記中心部の空間内に配置され、前記フローティングジャンクションの電位変化を検出するアンプトランジスタおよび前記フローティングジャンクションの電位をリセットするリセットトランジスタを含む2組の出力回路と、を基本単位セルとして含み、この基本単位セルを2次元に複数個配置してなる固体撮像装置。

## 【請求項 2】

前記2組の出力回路は、前記リセットトランジスタのドレイン電極を共用していることを特徴とする請求項1に記載の固体撮像装置。

## 【請求項 3】

前記フォトダイオードと、前記出力回路との間にはシャロートレンチを用いた素子分離領域が形成されていることを特徴とする請求項2に記載の固体撮像装置。

## 【請求項 4】

前記6個のフォトダイオードのうち、互いに隣接するフォトダイオード間にはイオン注入による素子分離領域が形成されていることを特徴とする請求項2または3に記載の固体

撮像装置。

【請求項 5】

前記複数個の基本単位セルは市松状に配置されていることを特徴とする請求項 1 に記載の固体撮像装置。

【請求項 6】

前記各基本単位セルに含まれる前記フォトダイオード、前記リセットトランジスタあるいは前記アンプトランジスタは、それぞれ行および列からなる格子状に配列され、前記格子状に配列されたフォトダイオードのうち、同じ行に配列されたフォトダイオードに蓄積された信号電荷を読み出すための転送ゲートトランジスタの転送ゲート電極に共通接続された転送ゲート配線と、前記格子状に配列されたリセットトランジスタのうち、同じ行に配列されたリセットトランジスタのリセットゲート電極に共通接続されたリセット配線と、前記前記格子状に配列されたアンプトランジスタのうち、同じ列に配列されたアンプトランジスタのソース電極に共通接続された出力配線と、を備えることを特徴とする請求項 5 に記載の固体撮像装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、画素の集積度を向上させた C M O S センサタイプの固体撮像素子に関する。 20

【背景技術】

【0002】

従来の C M O S センサタイプの固体撮像素子のセル構造としては、2 画素 1 セルの構成のタイプがよく知られている。これは、光電変換により発生した電荷を蓄積するフォトダイオード（以下略して P D と呼ぶ）を 2 つ配置し、これらの P D から読み出された信号電荷を電圧に変換する出力回路を、2 つの P D で共有化した、所謂シェアドピクセルタイプである。代表例として、特許文献 1 や、本出願人より提案した特許文献 2 に記載されている構造が有る。 30

【0003】

2 画素 1 セルタイプの固体撮像素子の構成要素は、P D と、P D から電荷転送するフローティングジャンクション（以下略して F J と呼ぶ）と、この転送を制御する転送ゲートトランジスタ（以下略して T G と呼ぶ）と、F J の電位変化を検知する出力アンプトランジスタ（以下略して A m p と呼ぶ）と、P D からの電荷を F J へ転送する前に F J の電位を一定電位にリセットするためのリセットトランジスタ（以下略して R S と呼ぶ）のゲート電極と、このリセットトランジスタのリセット電位及び A m p の電源を兼ねるリセットドレイン電極（以下略して R D と呼ぶ）とから成る。A m p のソース電極側には F J に連結されたゲート電極の電位変化を外部に出力するための出力ソース電極（以下略して O S と呼ぶ）がある。 30

【0004】

この様にそれぞれの P D には電荷転送用の T G が有り、2 つの P D は F J 、R S 、A m p 、R D を共有している。従って一つの P D の周囲にはこれらの構成要素が配置されるため、素子分離領域が多くなる。通常 2 画素 1 セルのトランジスタの数としては、2 つの T G 、1 つの R S 、1 つの A m p があり、1 つの P D 当たり 2 つのトランジスタが必要となる。また配線の数も、縦方向に 2 P D が配置された 2 画素 1 セル構造では、2 P D 当たり 2 T G 、1 R S 、1 R D 、1 出力配線（O S L と連結されている）となる。従って 1 P D 当たり、1 本の T G 配線（横方向）、0 . 5 本の R S 配線（横方向）および R D 配線（横方向）、1 本の出力配線（縦方向）が必要となる。 40

【0005】

素子分離領域としては、通常の微細セルでは P D とトランジスタ間の素子分離で有るために、シャロートレンチアイソレーション（以下略して S T I と呼ぶ）と言われる構造で素子分離される。これは半導体基板に浅い溝（トレンチ）を堀り、そこに酸化膜を埋め込ん 50

で分離する方法である。半導体基板に溝を掘るためダメージが入り、これによる画像劣化（白キズ）を防止するために、トレンチの周囲には不純物領域を設け、PDからの空乏層がこのダメージ領域まで届かない様な工夫を行っている。この不純物領域の形成は画質改善には貢献するも、PDの実効的な面積縮小になり、画素の微細化の際には、PDで蓄積できる電荷量（以下飽和電荷量と略す）の減少をもたらす。

#### 【0006】

一方、配線本数の増加はPDに取り込まれる入射光の収集効率低下をもたらし、画面周辺部でもシェーディング劣化を引き起こす。やはりこれらは微細セル化と共に画質劣化をもたらしていた。

#### 【先行技術文献】

10

#### 【特許文献】

#### 【0007】

【特許文献1】米国特許第6091449号明細書

【特許文献2】特開2006-302970号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明の実施形態は、微細セルに於いても、白キズ劣化無く、飽和電荷量の劣化を防ぎ、かつシェーディング劣化も抑える固体撮像素子を提供することを目的とする。

#### 【課題を解決するための手段】

20

#### 【0009】

本発明の実施形態に係る固体撮像装置は、それぞれ多角形の平面形状を有し、中心部に前記多角形の辺により空間が形成されるように配列された6個のフォトダイオードと、これらのフォトダイオードにより光電変換され、蓄積された信号電荷を検出するために、前記中心部の空間内に配置されたフローティングジャンクションと、前記フォトダイオードに蓄積された信号電荷を前記フローティングジャンクションに読み出すために、前記中心部の空間内に配置された転送ゲートトランジスタと、前記中心部の空間内に配置され、前記フローティングジャンクションの電位変化を検出するアンプトランジスタおよび前記フローティングジャンクションの電位をリセットするリセットトランジスタを含む2組の出力回路と、を基本単位セルとして含み、この基本単位セルを2次元に複数個配置してなるものである。

30

#### 【図面の簡単な説明】

#### 【0010】

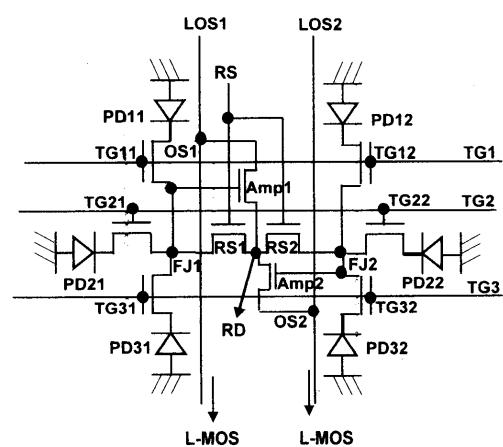

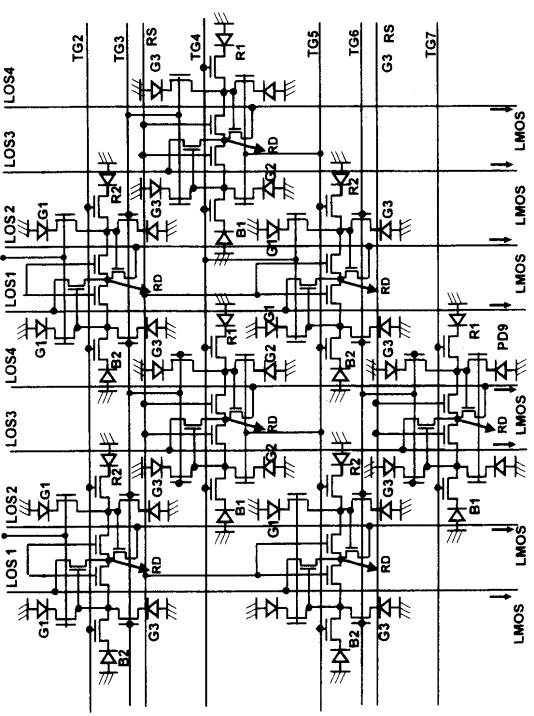

【図1】本発明の実施形態に係る固体撮像素子を構成する6画素1セル用単位セルの等価回路図である。

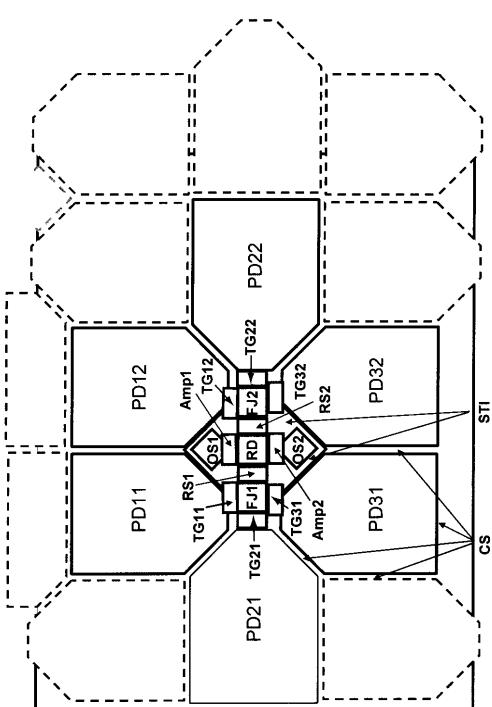

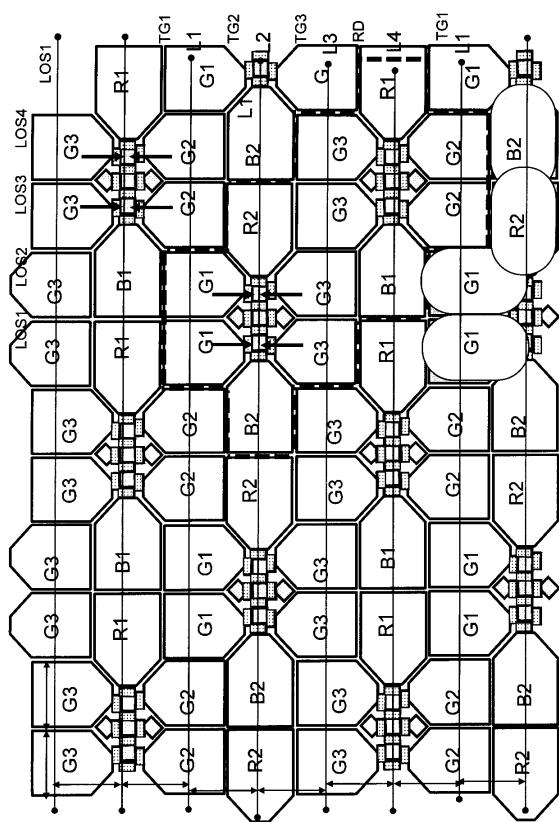

【図2】図1に示す6画素1セル用単位セルのパターンレイアウトを示す平面図である。

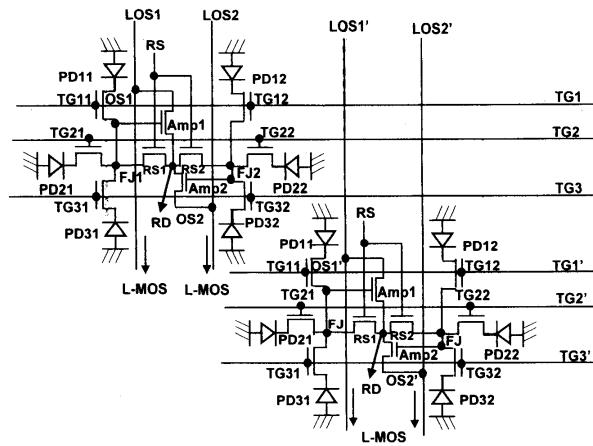

【図3】図1に示す単位セルを2ブロック組み合わせた12画素1セル用単位セルの等価回路図である。

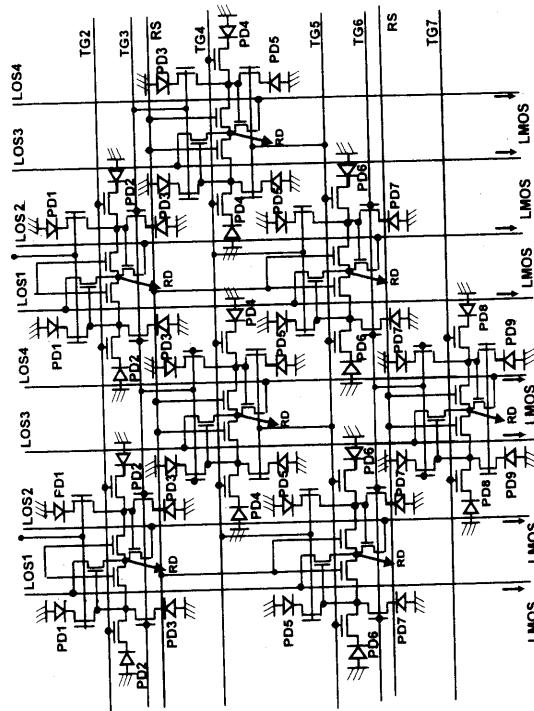

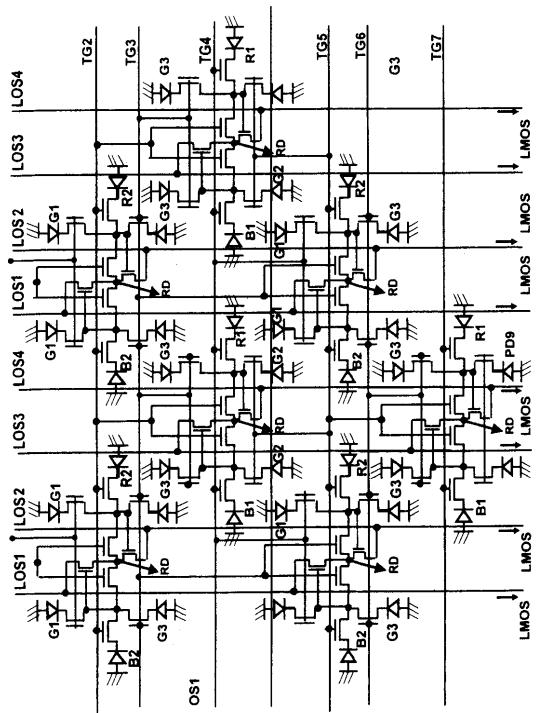

【図4】図3に示す12画素1セル用単位セルを繰り返し展開してなる固体撮像素子の等価回路図である。

40

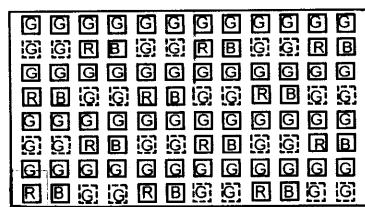

【図5】図4に示す固体撮像素子のパターンレイアウトを色フィルタ配置とともに示す平面図である。

【図6】図4に示す等価回路に色情報と読み出し情報とを付記した等価回路図である。

【図7】本発明の他の実施形態に係る固体撮像素子の等価回路図である。

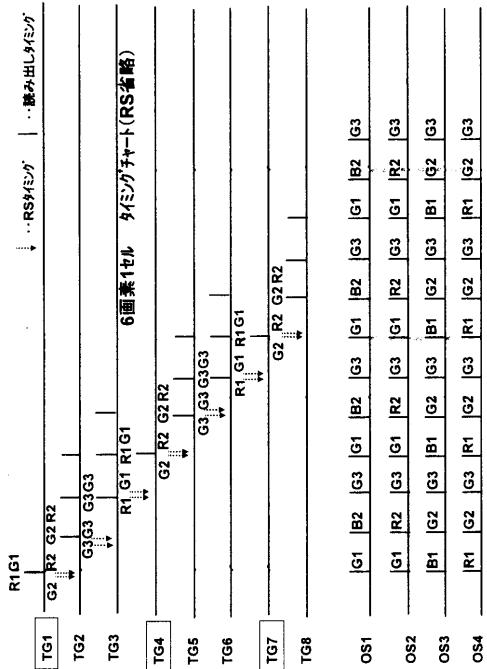

【図8】図7に示す固体撮像素子の画素読み出しタイミングチャート図である。

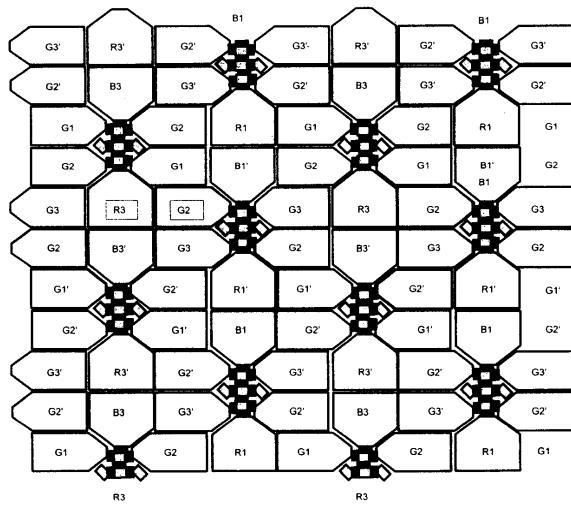

【図9】本発明の他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図である。

【図10】図9に示す固体撮像素子のパターンレイアウトに適用する色フィルタ配置を示す平面図である。

【図11】本発明の他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図

50

である。

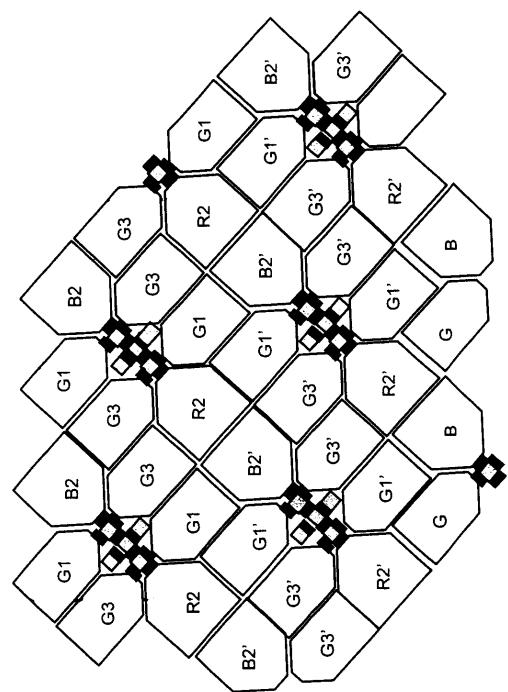

【図12】本発明の他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図である。

**【発明を実施するための形態】**

**【0011】**

本発明の実施形態に係る固体撮像素子は、6画素1セルを一つのブロックとし、これを市松状に配置した12画素1セルを繰り返し単位として配置したCMOSセンサである。出力回路を複数PDで共有化することにより、PDに隣接したSTI領域の長さを減らし、PD間の素子分離の大部分をイオン注入領域で行う事で、微細セルでも白キズ劣化を防止しつつ、飽和電荷量も確保し、かつ1PD当たりの配線本数を減らし、シェーディング劣化を防止することが可能である。

10

**【0012】**

以下に、本発明の実施形態に係る固体撮像素子について、図面を参照して詳細に説明する。

**【0013】**

(第1の実施形態)

図1は、第1の実施形態に係る固体撮像素子を構成する基本セルの等価回路図である。6つのフォトダイオードPD(PD11、PD12、PD21、PD22、PD31、PD32)は、左右2つに分かれしており、左側のPD11、PD21、PD31は転送ゲートトランジスタTG11、TG21、TG31を介しフローティングジャンクションFJ1に連結されている。右側のPD12、PD22、PD32はTG12、TG22、TG32を介しFJ2に連結されている。FJ1、FJ2はそれぞれリセットトランジスタRS1、RS2を介し共通のリセットドレイン端子RDに左右から連結されている。出力アンプトランジスタAmpのゲートAmp1、Amp2の上下から共通のドレインに連結しており、この共通のドレインはRDで兼ねる。FJ1、FJ2はそれぞれAmp1、Amp2のゲートに連結されており、FJ1、FJ2の電位変化を出力ソース電極OS1、OS2より外部に出力される。OS1、OS2はそれぞれ縦方向に伸びる出力信号線LOSS1、LOSS2に連結されている。LOSS1、LOSS2の先には、回路は図示されていないが負荷MOS(L-MOS)がある。また水平方向の同一ライン上のTG11、TG12は読み出しラインTG1、同様に水平方向の同一ライン上のTG21、TG22は読み出しラインTG2、水平方向の同一ライン上のTG31、TG32は読み出しラインTG3に連結されている。図1は6画素で1つのRDを共有化する構造であり、以下6画素1セル構造と称する。

20

30

**【0014】**

図1に示す基本セルの等価回路のレイアウトを図2に示す。特徴的な事はFJ1の4辺の内3辺にTG11、TG21、TG31を配置し、その先にPD11、PD21、PD31が配置されている。FJ1の残り1辺にはRS1が隣接配置され、RS1のFJ1と対向するドレイン側にはRDが配置されている。このRDをセンターに3画素1セルブロックを水平方向に180度回転させた3画素1セルをもう一つ配置させる。即ちRDのRS1と対向した位置にRS2を配置されている。RS2のRDと対向する辺にFJ2が配置され、FJ2の4辺の内3辺にTG12、TG22、TG32を配置し、その先にPD12、PD22、PD32が配置されている。一方RDの上下2辺にはAmpトランジスタのゲートAmp1、Amp2が隣接配置されている。Amp1、Amp2はそれぞれFJ1、FJ2と連結(連結配線は図示せず)されている。Amp1、Amp2のソース側にはソース電極OS1、OS2が配置され、これと連結され縦方向に出力信号線LOSS1、LOSS2(図示せず)が伸びる。

40

**【0015】**

それぞれPDと出力回路のOS間の素子分離はSTIで行われる。一方PD間の素子分離は、イオン注入方法で形成された不純物領域(以下チャネルストッパーと称しCSと略す)で素子分離を行う。

50

**【0016】**

図2に示す6画素1セルのレイアウトに於いては、隣接するセル配置を考慮すると、正方格子状に配置するよりは斜め方向にシフトさせ配置させると収まりが良くなる。この実用的な配置構造につき、図3を用い等価回路を説明する。図3は図1の6画素1セルを一つのブロックとして、斜め方向に2つのブロックを隣接させた等価回路である。所謂12画素1セルの等価回路になる。ここで、1ブロック目のPD31、PD32に隣接し、2ブロック目のPD11、PD12が同一水平ライン上に配置されている。2ブロック目の読み出しラインTG、出力ソース電極OSはそれぞれ1ブロック目と区別するため、TG1'、OS1'と示している。

**【0017】**

図3の12画素1セルを繰り返し配置した等価回路を図4に示す。図に於いて同一水平ライン上のPDは同じ記号にて示す。例えばPD11、PD12はPD1と呼ぶ。図3では1ブロック目のPD31、PD32に隣接し、2ブロック目のPD11、PD12があるが、図4では同一ライン上なのでPD3と示している。これに伴い、TG3とTG1'は同一読み出しタイミングとし、TG3で示し、2ブロック目のTG2'、TG3'はそれぞれTG4、TG5と示している。TG5は3ブロック目のTG1と同じ配線である。順次3ブロック目のTG2、TG3に相当する配線はTG6、TG7となり、TG7は4ブロック目のTG1'に対応する。図4に示す等価回路で特徴的な事は、斜め方向に隣接した2つのブロックが常にセットで出力回路がONになるようにTGが開く構成になっていることである。このためRSは2つのブロックのRS共通でリセットしていく配線になっている。また図3の出力信号線OS1'、OS2'は図4では、12画素1セルレイアウトのイメージでOS3、OS4と表記した。

10

**【0018】**

図4の12画素1セルの繰り返し等価回路図のレイアウトを図5に示す。図5では、色フィルタ配置の一例も合わせて表現している。色フィルタは輝度成分比率の高いGreen画素の数量を増やし、色信号を作り出すRed、Blueは人の眼の色解像度が低い事を利用し、数量をGreenの1/2に絞っている。

20

**【0019】**

斜め方向に隣接した2つのブロックの出力回路で同時に読み出されるPDに対しては、色フィルタの色情報を示すR、G、Bの文字の横に、読み出し情報1、2、3の数字を付記し表現している。即ち隣接する縦方向ラインの同じ数字の画素には、図4で示す同じTG配線により読み出し信号が印加され、同時に読み出される。この表記は以下の図面でも同じである。

30

**【0020】**

図5に示すレイアウトに対応した図4の等価回路図のPDに、上記に示した色情報と読み出し情報を付記した図を図6に示す。

**【0021】**

次に、図2～図6により説明した本実施形態に係る撮像素子の従来の撮像素子にはない特徴について説明する。本実施形態の撮像素子における基本ブロックである図2に示す6画素1セル構造においては、トランジスタの数として、6個のTG、2個のRS、2個のAMPを含んでおり、いわゆる、6画素10トランジスタ構造である。したがって、1つの画素(PD)当たり1.67個のトランジスタとなる。またRDを共有化しているため、6画素当たり1つのRDとなってRDの占有面積が減るため、1セル当たりのPDの専有面積割合が増える。

40

**【0022】**

また画素配置にも特徴があり、6画素で出力回路を囲むように画素が配置されている。隣接PDの一部を破線で示しているが、一つのPDの直交する3辺は他のPDと隣接しており、残り1辺もその一部がTGや他のPDに隣接し、残った部分で出力回路に隣接している。図ではこの残り1辺が更に鈍角で交差する3辺に別れ、それぞれPD、TG、出力回路のOSの素子分離領域(STI)と隣接している。このように一つのPDの直交する

50

3辺が隣接するPDと接している為、これらの隣接するPD間についてはイオン注入方法で形成された不純物領域で素子分離を行う事が出来る。

#### 【0023】

この点についてさらに詳細に説明すると、出力回路部では周辺の電位が信号レベルに影響するため、素子分離を強化させる必要があり、その素子分離にはSTIが使われる。しかしながらPD間の素子分離では、PDの電位井戸の壁を形成する目的で形成されるため、壁の高さが多少変動しても、通常の撮像状態では光電変換や信号電荷の蓄積には影響しない。飽和状態で隣接PDへ過剰電荷が漏れ込む懸念が有るが、閉じた状態でのTG電位を制御（少し開き気味に）することで、過剰な電荷をFJに流すように出来、これは信号電荷の読み出しの直前にRSを開いてRDで捨てる事が出来、画質劣化を抑える事が出来る。10

#### 【0024】

次に、PDの周囲の素子との分離にSTIを使わないメリットを示す。背景技術の項で説明したように、STIの問題点として白キズと飽和電荷量のトレードオフにより、微細化が進むにつれて素子の特性が大幅に劣化していた。特にそのしわ寄せは白キズに影響し、大規模なキズ補正を行うため、周辺回路に負荷が掛かり、また画像が不自然になる問題があった。本実施形態では素子分離がイオン注入だけで形成でき、半導体基板に対するダメージは熱処理（アニール）することで容易に回復でき、ダメージの少ない素子分離が可能となる為、白キズマージンが大幅に向上する。また素子分離幅も解像限界の抜きパターンで決める事が出来る。これはPDの実効的な面積縮小を抑制でき、PDの飽和電荷量の減少の抑制に繋がる。20

#### 【0025】

本実施形態に係る撮像素子の他の特徴としては、画素ピッチがほぼPDの大きさで決まり微細化に向いている。またFJ1からAmp1までの距離（FJ2からAmp2までの距離も同様）は近傍に隣接して配置されているため配線長を短くでき、FJに寄生する静電容量を減らし、アンプゲインを高める事も出来る。

#### 【0026】

##### （第2の実施形態）

図7は本発明の他の実施形態に係る固体撮像素子の等価回路図であり、図6に示す12画素1セルを繰り返し配置した等価回路図に於いて、RS配線をTG配線と共有化した回路図を示している。TG配線を介して読み出しパルス信号を印加しPDから信号電荷を読み出す際に、同じパルスを次の出力ブロックのRSと共に共有化する事により、次のブロックのPDからの信号電荷の読み出しに先立って行われるFJのリセット動作を兼用する事が出来る。30

#### 【0027】

図8は図7に示した等価回路での読み出しパルス信号TGとリセットパルス信号RSのタイミングチャートを示す。図に於いてTGでの読み出しタイミングを実線で、その読み出しパルス信号TGで次のラインのFJをリセット（RS）するタイミングを破線で示す。実線、破線の上に付記したR1、G1なる記号は破線のタイミングでR1、G1画素を読み出す回路ブロックのFJをRSするタイミングを示し、実線のタイミングでその読み出しパルス信号でPDからFJへの読み出しが行われる事を示している。レイアウトではR1、B1が同じライン上にあり同時に出てくるが、これはR1で代表して示している。RSを掛けるために、TGの読み出し後余分のパルスを印加している。図8の下に表記した4ラインはOS1、OS2、OS3、OS4に上記の読み出しパルス信号TGのタイミングで出力される画素の色情報と読み出し情報を示している。これは図7の画素に付記したものと同じである。40

#### 【0028】

図9は本発明の他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図で、図5に示した12画素1セルを繰り返し配置したレイアウトと水平走査線の構成を示す。画素配置に於いて、RとB画素と同じ走査線上の画素数はG画素の同じ走査線上の画素50

数の半分である。これは出力回路が R と B 画素ライン上にある為である。この出力回路部分の画素の抜けを補正する一例を図 9 により説明する。即ち出力回路の上下に隣接した画素は共に G 画素、 G 3、 G 3 および G 2、 G 2 であり、これらを平均化処理し仮想 G (以下 G<sub>r</sub> と呼ぶ) を作ることで、水平走査線上の画素数を揃える事が出来る。この仮想 G<sub>r</sub> で埋め込んだ際の各画素の色フィルタ配置を図 10 に示す。同図において破線で囲われた矩形 G が上記方法で作成した仮想 G<sub>r</sub> である。また図 9 右下の部分には、マイクロレンズの形状の一例も合わせて記載してある。

#### 【 0 0 2 9 】

次に、図 9 に示した実施形態を参照してその特徴を配線本数の観点から説明する。図 7 に示す読み出し配線 T G とリセット配線 R S の共通化配置を使うと、図 9 の右端に記したように、水平方向に走る配線は T G 1、 T G 2、 T G 3、 R D の 4 本配線の繰り返しである。なお、 T G 1、 T G 2、 T G 3、 R D の配線は図 9 には明示されていないが、 P D 間の隙部に沿って配線されている。また水平走査線は L 1、 L 2、 L 3、 L 4 の 4 本である。太い破線で囲まれた 1 2 画素 1 セルに於いて、下端の 2 画素 G 2、 G 2 を走る水平走査線は、上端の 2 画素 G 1、 G 1 を走る水平走査線 L 1 と同じ繰り返しとなり、やはり 4 本の繰り返しである。一方縦方向に走る出力信号線は L O S 1、 L O S 2、 L O S 3、 L O S 4 で示すように、やはり 4 本の繰り返しである。なお、 L O S 1、 L O S 2、 L O S 3、 L O S 4 の配線についても図 9 には明示されていないが、 P D 間の隙部に沿って配線されている。この水平走査線 4 本に対し、水平方向の配線も 4 本ということは、一画素当たり水平方向には 1 本の配線が走っている事を意味する。また縦方向も同様に 4 画素周期で 4 本の出力信号線が走っている。これは一画素 ( P D ) 当たり垂直方向にも 1 本の配線が走っている事を意味する。この様に本願では画素の周囲に水平垂直方向に 1 本ずつの配線が走っている。

#### 【 0 0 3 0 】

一方、従来の 2 画素 1 セル構造の配線の本数は、本願と同様にリセット配線 R S と読み出し配線 T G を共通化した前提で、水平方向は 2 画素当たり 2 T G、 1 R D であり、垂直方向は 1 画素当たり 1 本の出力配線となる。従って 1 画素当たり、水平方向には 1 . 5 本の配線、縦方向には 1 本の出力配線となる。この実施形態に於ける、配線本数の減少は P D に取り込まれる入射光の収集効率向上をもたらし、画面周辺部でのシェーディング劣化を抑制できる。これらは微細セル化による程効果が顕著になる。

#### 【 0 0 3 1 】

##### ( 第 3 の実施形態 )

図 11 は本発明の他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図である。この固体撮像素子のパターンレイアウトは、図 5 に示した 1 2 画素 1 セルの繰り返しブロックを 90 度回転させて配置したレイアウトであり、色フィルタの色情報を示す R、 G、 B の文字の横に、読み出し情報 1、 2、 3、 1'、 2'、 3' の数字を付記し表現している。画素からの読み出しは斜め方向に隣接する出力回路から 2 個ずつ、 4 画素単位 ( O S 1、 O S 2、 O S 3、 O S 4 ) で出力する方式を取っており、読み出し情報としては、従来の 1、 2、 3 に加え、 1'、 2'、 3' で付記した。

#### 【 0 0 3 2 】

図 12 は本発明のさらに他の実施形態に係る固体撮像素子のパターンレイアウトを示す平面図である。この固体撮像素子のパターンレイアウトは、図 5 に示した 1 2 画素 1 セルの繰り返しブロックを 45 度回転させて配置したレイアウトであり、色フィルタの色情報を示す R、 G、 B の文字の横に、読み出し情報 1、 2、 3、 1'、 2'、 3' の数字を付記し表現している。画素からの読み出しは水平方向に隣接する出力回路から 2 個ずつ、 4 画素単位 ( O S 1、 O S 2、 O S 3、 O S 4 ) で出力する方式を取っており、図 11 と同様に読み出し情報としては、従来の 1、 2、 3 に加え、 1'、 2'、 3' で付記した。

#### 【 0 0 3 3 】

以上本発明の実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。例えば、図 2 に示す 6 画素 1 セルを単純

10

20

30

40

50

に縦方向、横方向に正方格子状に配置しても良く、その隙間のスペースは P D を拡大することで充足した配置を取る事が出来る。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の趣旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。特に色フィルタの配置や、その読み出しの画素の組み合わせは色々な変形が可能である。

#### 【 0 0 3 4 】

これらの実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【 符号の説明 】

##### 【 0 0 3 5 】

P D …… フォトダイオード ( P D )

T G …… 転送ゲートトランジスタ

F J …… フローティングジャンクション

R S …… リセットトランジスタ

A m p …… 出力アンプトランジスタ

R D …… リセットドレイン

O S …… 出力ソース

L O S …… 出力信号線

L - M O S …… 負荷 M O S

S T I …… シャロートレンチアイソレーション ( 酸化膜埋め込み素子分離 )

C S …… チャネルストッパー ( イオン注入素子分離 )

10

20

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図 1 2】

---

フロントページの続き

(56)参考文献 特表2011-517506(JP,A)

特開2006-302970(JP,A)

特表2009-506575(JP,A)

特開2006-165567(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| H 01 L | 2 7 / 1 4 6 |

| H 04 N | 5 / 3 5 7   |

| H 04 N | 5 / 3 6 9   |

| H 04 N | 5 / 3 7 4   |