(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3979010号

(P3979010)

(45) 発行日 平成19年9月19日(2007.9.19)

(24) 登録日 平成19年7月6日(2007.7.6)

(51) Int.C1.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1335 (2006.01)

G02F 1/1335 500

G02F 1/1343 (2006.01)

G02F 1/1343

請求項の数 8 (全 23 頁)

(21) 出願番号 特願2001-7918 (P2001-7918)

(22) 出願日 平成13年1月16日 (2001.1.16)

(65) 公開番号 特開2001-330859 (P2001-330859A)

(43) 公開日 平成13年11月30日 (2001.11.30)

審査請求日 平成16年1月26日 (2004.1.26)

(31) 優先権主張番号 特願2000-77173 (P2000-77173)

(32) 優先日 平成12年3月17日 (2000.3.17)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 村出 正夫

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 右田 昌士

最終頁に続く

(54) 【発明の名称】電気光学装置及びプロジェクタ

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に、走査線と、前記走査線と交差するデータ線と、画素電極と、前記走査線と前記データ線の交差に対応して設けられ前記画素電極を制御するための薄膜トランジスタを有する電気光学装置であって、

前記薄膜トランジスタのゲート電極と前記画素電極との層間において、前記ゲート電極上に配置された第1導電層と、前記第1導電層上に配置された遮光性の第2導電層とを備え、

前記データ線は、前記第2導電層上に配置されており、

前記第1導電層と前記第2導電層は、前記薄膜トランジスタのチャネル領域を覆い、前記第2導電層の前記チャネル領域を覆う部分のチャネル幅方向の幅は前記第1導電層の前記チャネル領域を覆う部分のチャネル幅方向の幅よりも長いとともに、

前記データ線の幅は、前記第2導電層のチャネル領域を覆う部分のチャネル幅方向の幅よりも短いことを特徴とする電気光学装置。

## 【請求項2】

前記薄膜トランジスタの下方に下地遮光膜が配置されていることを特徴とする請求項1に記載の電気光学装置。

## 【請求項3】

前記第2導電層の前記チャネル領域を覆う部分のチャネル幅方向の幅は、前記下地遮光膜の前記チャネル領域の下方部分のチャネル幅方向の幅よりも長いことを特徴と

する請求項 2 に記載の電気光学装置。

【請求項 4】

前記第 1 導電層の前記チャンネル領域を覆う部分の前記チャンネル幅方向の幅は、前記下地遮光膜の前記チャンネル領域の下方部分のチャンネル幅方向の幅よりも長いことを特徴とする請求項 3 に記載の電気光学装置。

【請求項 5】

前記下地遮光膜の前記チャンネル領域の下方部分のチャンネル幅方向の幅は、前記薄膜トランジスタのチャネル領域の幅よりも長いことを特徴とする請求項 3 又は 4 に記載の電気光学装置。

【請求項 6】

前記第 2 導電層は、定電位源に接続されることを特徴とする請求項 1 乃至 5 のいずれか一項に記載の電気光学装置。

【請求項 7】

前記第 1 導電層は、前記薄膜トランジスタの半導体層のソース領域に電気的に接続されることを特徴とする請求項 1 乃至 6 のいずれか一項に記載の電気光学装置。

【請求項 8】

請求項 1 から 7 のいずれか一項に記載の電気光学装置をライトバルブとして用いることを特徴とするプロジェクタ。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は、アクティブマトリクス駆動方式の電気光学装置の技術分野に属し、特に画素スイッチング用の薄膜トランジスタ (Thin Film Transistor:以下適宜、TFTと称す) を構成する半導体層を基板上の積層構造中に備えており、プロジェクタ等に好適に用いられる TFT の上側に入射光に対する遮光膜を設けると共に TFT の下側に戻り光に対する遮光膜を設けた形式の電気光学装置の技術分野に属する。

【0002】

20

【背景技術】

従来、TFT 駆動によるアクティブマトリクス駆動方式の液晶装置等の電気光学装置においては、TFT のゲート電極に走査線を介して走査信号が供給されると、TFT はオン状態とされ、半導体層のソース領域にデータ線を介して供給される画像信号が当該 TFT のソース・ドレイン間を介して画素電極に供給される。このような TFT を構成する半導体層のチャネル領域或いはチャネル領域とソース・ドレインとの接合領域及びこれに隣接するソース・ドレインの少なくとも一部に光が入射すると、光励起が生じ、当該 TFT のトランジスタ特性は、例えば、オフ状態におけるリーク電流が増加するよう変化する。従って、このような光入射による TFT の特性変化を防止するために、例えば、プロジェクタ用途の透過型の電気光学装置のように特に強力な入射光が入射される型の電気光学装置の場合には、投射光の入射側については、TFT のチャネル領域を含む画素電極間の間隙領域を覆うように対向基板に遮光膜を設けたり、A1 膜等からなる不透明のデータ線を幅広に形成してチャネル領域を覆ったりしている。更に、出射側については、TFT の下側に遮光膜を設けることにより、裏面反射光や、複数の電気光学装置を組み合わせてプロジェクタを構成する場合の他の電気光学装置から合成光学系を突き抜けてくる投射光などの戻り光を遮光している。

【0003】

30

【発明が解決しようとする課題】

この種の電気光学装置においては、表示画像の高品位化という一般的な要請が強く、このためには、各画素において、表示光が透過しない非画素開口領域に対して、表示光が透過する画素開口領域を広げることで、画素ピッチを微細化しつつ、画素開口率化を高めると同時に、上述の如く TFT のチャネル領域や当該チャネル領域に隣接する領域（以下適宜、チャネル隣接領域と称す）、例えば LCD 構造の TFT の低濃度領域における入射光や

40

50

反射光に対する遮光を十分に行なうことが極めて重要となる。即ち、画素ピッチを微細化する程に、TFTにおける僅かな特性変化が画像品位の大きな劣化につながる。

#### 【0004】

しかしながら、画素開口率を高めれば高める程、全体として遮光膜或いは遮光機能を有する膜を配置できる平面領域は減ってしまうため、TFTを万全に遮光することがより困難になるという問題点がある。更に、画素ピッチの微細化が進む程に、基板面に対して僅かに傾斜した入射光や反射光であっても、斜めから入射した後に積層構造内で多重反射を起こして最終的にチャネル領域やチャネル隣接領域に入ってしまうという問題点がある。特に単位面積当たりの入射光や反射光の強度が極めて高いプロジェクタ用途の電気光学装置の場合には、画像品位を向上させる上では、このような問題は極めて深刻である。

10

#### 【0005】

本発明は上述の問題点に鑑みなされたものであり、画素開口率を高めつつ入射光や反射光による画素スイッチング用TFTの特性変化が低減されており、高品位の画像表示が可能な電気光学装置を提供することを課題とする。

#### 【0006】

##### 【課題を解決するための手段】

本発明の電気光学装置は上記課題を解決するために、基板上に、画素電極と前記画素電極を制御するための薄膜トランジスタを有する電気光学装置であって、前記薄膜トランジスタのゲート電極と前記画素電極との層間において、前記ゲート電極上に配置された第1導電層と、前記第1導電層上に配置された遮光性の第2導電層とを備え、前記第1導電層と前記第2導電層は、前記薄膜トランジスタのチャネル領域を覆い、前記第2導電層の幅は前記第1導電層の幅より長いことを特徴とする。

20

#### 【0007】

本発明の電気光学装置の一態様では、前記薄膜トランジスタの下方に下地遮光膜が配置されていることを特徴とする。

#### 【0008】

本発明の電気光学装置の一態様は、前記第2導電層の幅は、前記下地遮光膜の幅よりも長いことを特徴とする。

#### 【0009】

本発明のかかる構成によれば、チャネル領域のみならず、ソース・ドレイン領域とチャネル領域との接合領域及びその接合領域に隣接するソース・ドレイン領域の少なくとも一部が導電膜により覆われているので、例えばLDD構造の薄膜トランジスタにおける低濃度領域に対しても入射光に対する遮光を行うことが可能となり、薄膜トランジスタの特性変化をより低減可能である。

30

#### 【0010】

(3) 本発明の第1の電気光学装置の他の態様では、前記蓄積容量は、一方の容量電極をなす第1導電膜と、前記ドレイン領域となる半導体層と前記画素電極を電気的に接続するとともに、前記蓄積容量の他方の容量電極をなす第2導電膜からなることを特徴とする。

#### 【0011】

本発明のかかる構成によれば、前記蓄積容量の他方の電極となる第2導電膜はドレイン領域と画素電極とを中継するための導電膜としても機能するため、画素電極とドレイン領域とを接続するためのコンタクトホール開孔によるエッチングの突き抜け防止を防ぐことができる。即ち、ドレイン領域は、ドレイン領域上に形成されたコンタクトホールを介して第2導電膜に接続され、画素電極は、第2導電膜上に形成されたコンタクトホールを介して第2導電膜に接続されるため、2つのコンタクトホールが必要となり、コンタクトホールが短距離であるためエッチング深度の制御も容易となり、突き抜け防止を防ぐことができる。

40

#### 【0012】

本発明の電気光学装置の一態様は、前記第1導電層の幅は、前記下地遮光膜の幅よりも長いことを特徴とする。

50

**【0013】**

本発明の電気光学装置の一態様は、前記下地遮光膜の幅は、前記薄膜トランジスタのチャネル領域の幅よりも長いことを特徴とする。

**【0014】**

本発明の電気光学装置の一態様は、前記薄膜トランジスタの半導体層に電気的に接続されるデータ線を備え、前記データ線は前記第2導電層と重なると共に、前記データ線の幅は前記第2導電層よりも短いことを特徴とする。

**【0015】**

本発明の電気光学装置の一態様は、前記データ線は、前記第2導電層上に配置されることを特徴とする。

10

**【0016】**

本発明の電気光学装置の一態様は、前記第2導電層は、定電位源に接続されることを特徴とする。

**【0017】**

本発明の電気光学装置の一態様は、前記第1導電層は、前記薄膜トランジスタの半導体層のソース領域に電気的に接続されることを特徴とする。

**【0072】**

本発明のこのような作用及び他の利得は次に説明する実施の形態から明らかにする。

**【0073】****【発明の実施の形態】**

20

以下、本発明の実施形態を図面に基づいて説明する。

**【0074】****(第1実施形態)**

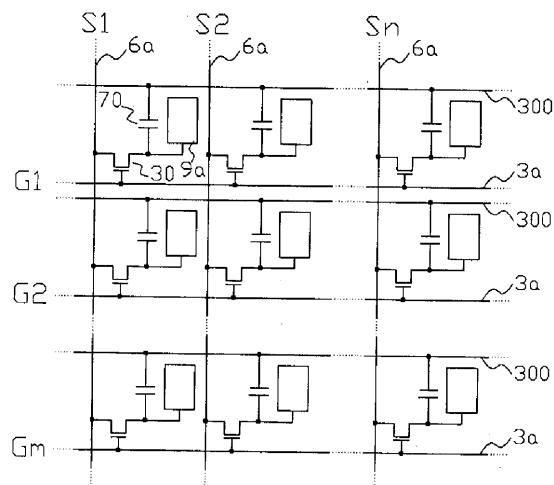

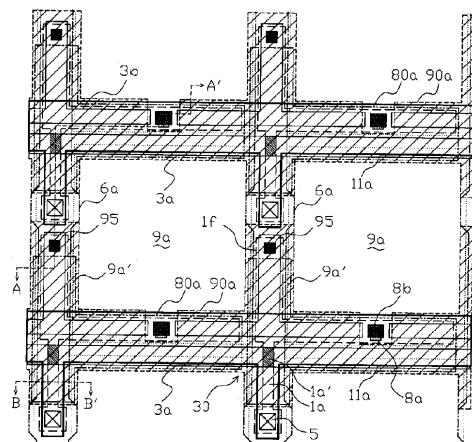

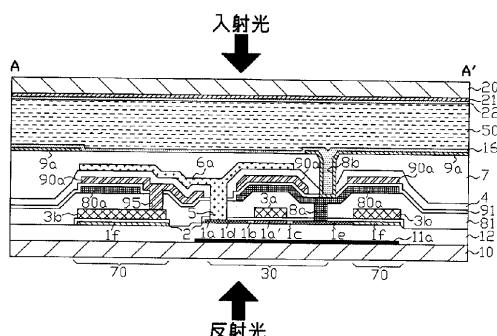

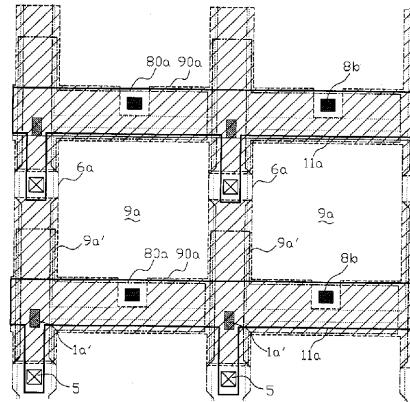

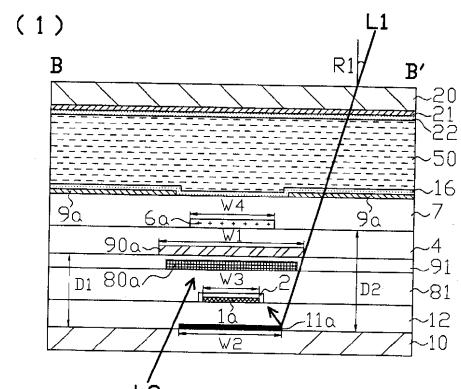

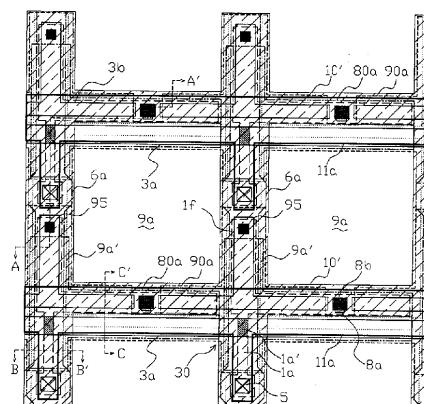

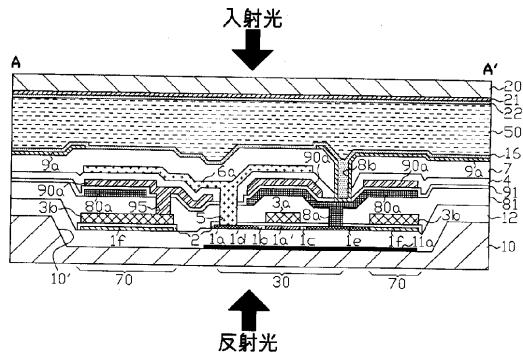

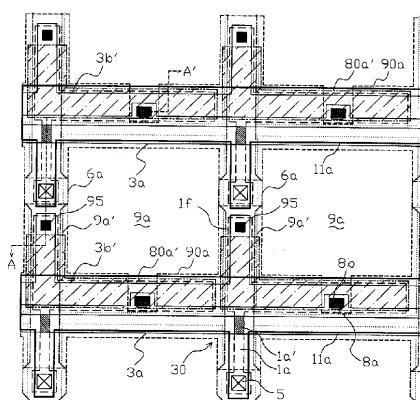

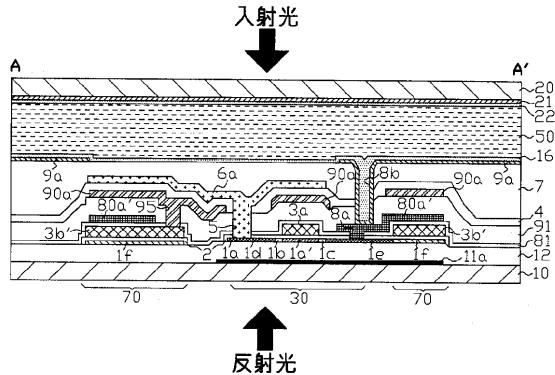

本発明の電気光学装置の一例である液晶装置の構成について、図1から図11を参照して説明する。図1は、液晶装置の画像表示領域を構成するマトリクス状に形成された複数の画素における各種素子、配線等の等価回路であり、図2は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図であり、図3は、図2のA-A'に沿った断面図である。尚、図3においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

**【0075】**

30

図1において、本実施形態における液晶装置の画像表示領域を構成するマトリクス状に形成された複数の画素は、画素電極9a及び画素電極9aを制御するためのTFT30が形成されており、画像信号が供給されるデータ線6aが当該TFT30のソースに電気的に接続されている。データ線6aに書き込む画像信号S1、S2、…、Snは、この順に線順次に供給しても構わないし、相隣接する複数のデータ線6a同士に対して、グループ毎に供給するようにしても良い。また、TFT30のゲートに走査線3aが電気的に接続されており、所定のタイミングで、走査線3aに走査信号G1、G2、…、Gmを、この順に線順次で印加するように構成されている。画素電極9aは、TFT30のドレインに電気的に接続されており、スイッチング素子であるTFT30を一定期間だけそのスイッチを閉じることにより、データ線6aから供給される画像信号S1、S2、…、Snを所定のタイミングで書き込む。画素電極9aを介して液晶に書き込まれた所定レベルの画像信号S1、S2、…、Snは、対向基板(後述する)に形成された対向電極(後述する)との間で一定期間保持される。液晶は、印加される電圧レベルにより分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能にする。ノーマリー・ホワイトモードであれば、印加された電圧に応じて入射光の透過光量減少し、ノーマリーブラックモードであれば、印加された電圧に応じて入射光の透過光量が増大し、全体として液晶装置からは画像信号に応じたコントラスト比を持つ光が出射する。ここで、保持された画像信号がリーケするのを防ぐために、画素電極9aと対向電極との間に形成される液晶容量と並列に蓄積容量70を付加する。蓄積容量70は、画素電極9aと電気的に接続された一方の容量電極と、定電位が供給された容量線300と電気的に接続された他方の容量電極との

40

50

間に誘電体膜を介して形成される。この蓄積容量70により、例えば画素電極9aの電圧は、ソース電圧が印加された時間よりも3桁も長い時間だけ保持される。これにより、保持特性は更に改善され、コントラスト比の高い液晶装置が実現できる。

#### 【0076】

図2において、液晶装置のTFTアレイ基板上には、マトリクス状に複数の透明な画素電極9a（点線部により画素電極端9a'が示されている）が設けられており、画素電極9aの縦横の境界に各々沿ってデータ線6a、走査線3aが設けられている。半導体層1aのうちチャネル領域1a'（図中右下りの斜線の領域）に対向するように走査線3aが配置されており、走査線3aはゲート電極として機能する。このように、走査線3aとデータ線6aとが交差する箇所には夫々、チャネル領域1a'に走査線3aの一部がゲート電極として対向配置されたTFT30が設けられている。画素電極9aは、中間導電膜である中継膜80aを中継して、コンタクトホール8a及び8bを介して半導体層1aのうち後述のドレインに電気的に接続されている。データ線6aは、コンタクトホール5を介してポリシリコン膜等からなる半導体層1aのうち後述のソース領域に電気的に接続されている。

#### 【0077】

また、半導体層1aから延設した容量電極1f（第4容量電極）と後述するゲート絶縁膜を介して少なくとも部分的に重なるように、走査線3aと同一膜からなる容量電極3b（第3容量電極）を設けても良い。これにより、図1における蓄積容量70の少なくとも一部を形成することができる。

#### 【0078】

更に、図2において太線で示した領域には夫々、走査線3aに沿ってTFT30の下側を通るように、下地遮光膜11aが設けられている。より具体的には、下地遮光膜11aは、少なくともTFTのチャネル領域1a'及び当該チャネル領域1a'のソース及びドレイン領域との接合領域をTFTアレイ基板側から見て夫々覆う位置に設けられている。また、走査線3aの方向に沿って画素電極9aがマトリクス状に形成された画像表示領域からその周囲に延設され、周辺領域にて定電位源と接続するようにすると良い。このように、下地遮光膜11aの電位を定電位に固定することにより、TFT30の誤動作を防ぐことができる。定電位源としては、後述する当該液晶装置を駆動するための周回路、例えば、走査線駆動回路、データ線駆動回路等に供給される負電源、正電源等の定電位源、接地電源、対向電極に供給される定電位源等が挙げられる。電位レベルとすれば、走査線3aに供給される走査信号のオフレベルにしておくことが望ましい。これにより、走査線3aとの間に寄生容量がほとんど発生しないので、走査線3aに供給される走査信号の遅延が生じることはほとんどない。

#### 【0079】

本実施形態では特に、図中右上がりの斜線で示した領域に、遮光性の導電膜（第1容量電極）90aが形成されている。遮光性の導電膜90aは、走査線3aとデータ線6aの間の層間に形成されており、コンタクトホール5及びコンタクトホール8bの形成領域を除く、データ線6aや走査線3a等の配線及びTFT30や蓄積容量の形成領域と平面的に見て重ねることができるため、TFTアレイ基板上の遮光を実現することができる。また、遮光性の導電膜90aは、走査線3aの方向に沿って画像表示領域からその周囲に延設し、周辺領域にて定電位源と接続することができる。これにより、遮光性の導電膜90aは図1における容量線300として機能することができる。また、コンタクトホール95を介して走査線3aと同一膜からなる容量電極3bに接続することにより、定電位を供給することで、容量電極1fとの間で蓄積容量70を容易に形成することができる。定電位源としては、後述する当該液晶装置を駆動するための周回路、例えば、走査線駆動回路、データ線駆動回路等に供給される負電源、正電源等の定電位源、接地電源、対向電極に供給される定電位源等が挙げられる。

#### 【0080】

次に図3の断面図に示すように、本実施形態における液晶装置は、基板の一例を構成する

10

20

30

40

50

透明な TFT アレイ基板 10 と、これに対向配置される透明な対向基板 20 を備えている。TFT アレイ基板 10 は、例えば石英基板やガラス基板あるいはシリコン基板からなり、対向基板 20 は、例えばガラス基板や石英基板からなる。TFT アレイ基板 10 には、ITO 膜などの透明導電性膜からなる画素電極 9a が設けられており、液晶層 50 に TN (Twisted Nematic) 液晶等を用いる場合、画素電極 9a の表面にラビング処理等の所定の配向処理が施された配向膜 16 を設けるようにする。

#### 【0081】

他方、対向基板 20 には、その全面に渡って ITO 膜などの透明導電性膜からなる対向電極 21 が設けられており、対向電極 21 の表面にラビング処理等の所定の配向処理が施された配向膜 22 を設けるようにする。

10

#### 【0082】

更に、TFT 30 に対向する位置において、TFT アレイ基板 10 と TFT 30 との間には、下地遮光膜 11a が設けられている。下地遮光膜 11a は、少なくとも画素スイッチング用の TFT 30 のチャネル領域 1a' 及び当該チャネル領域 1a' とソース及びドレイン領域との接合領域に対向する位置に形成されているので、TFT アレイ基板 10 側からの反射光等が、チャネル領域 1a' やその隣接領域に照射されることはない。これにより、光に起因したリーク電流の発生により TFT 30 の特性が変化することはない。下地遮光膜 11a としては、好ましくは Ti (チタン)、Cr (クロム)、W (タングステン)、Ta (タンタル)、Mo (モリブデン) 及び Pb (鉛) などの不透明な高融点金属を少なくとも一つ含む、金属単体、合金、金属シリサイド等から構成するのが好ましい。あるいは、直に入射光が回り込んでも光を吸収できるように、下地遮光膜 11a の表面にポリシリコン等の反射防止膜を形成しても良い。また、TFT アレイ基板 10 側からの反射光等が弱い場合には、下地遮光膜 11a にポリシリコン膜を用いても構わない。このような材料から下地遮光膜 11a を構成すれば、例えば、ゲート絶縁膜 2 の形成における高温処理により、下地遮光膜 11a が破壊されたり溶融しないようにできる。尚、本実施形態では下地遮光膜 11a を、各走査線 3a の下方を当該走査線 3a に沿って縞状に形成しているが、各データ線 6a の下方を当該データ線 6a に沿って縞状に形成しても良いし、あるいは各走査線 3a 及び各データ線 6a の下方に格子状に形成しても良いことは言うまでもない。このように下地遮光膜 11a を、縞状に形成すれば下地遮光膜 11a による応力の緩和を実現できるし、格子状に形成すれば遮光性が高まるだけでなく下地遮光膜 11a を更に低抵抗化を図ることができる。

20

#### 【0083】

また、下地遮光膜 11a と TFT 30 との間には、下地絶縁膜 12 が設けられている。下地絶縁膜 12 は、TFT 30 を構成する半導体層 1a を下地遮光膜 11a から電気的に絶縁するために設けられるものである。更に、下地絶縁膜 12 は、TFT アレイ基板 10 の全面に形成されることにより、TFT 30 のための下地膜としての機能をも有する。即ち、TFT アレイ基板 10 の表面の研磨時における荒れや、洗浄後に残る汚れ等で TFT 30 の特性変化を防止する機能を有する。下地絶縁膜 12 は、例えば、NSG (ノンドープシリケートガラス)、PSG (リンシリケートガラス)、BSG (ボロンシリケートガラス)、BPSG (ボロンリンシリケートガラス) などの高絶縁性ガラス又は、酸化シリコン膜、窒化シリコン膜等からなる。また、下地絶縁膜 12 により、下地遮光膜 11a が TFT 30 等を汚染する事態を未然に防ぐこともできる。

30

#### 【0084】

更に本実施形態では、下地絶縁膜 12 上に形成される TFT 30 は、LDD (Lightly Doped Drain) 構造を有しており、例えばポリシリコン膜からなる半導体層 1a は、走査線 3a からの電界によりチャネルが形成されるチャネル領域 1a' を挟んで低濃度ソース領域 1b 及び低濃度ドレイン領域 1c が形成され、低濃度ソース領域 1b には高濃度ソース領域 1d が接続され、低濃度ドレイン領域 1c には高濃度ドレイン領域 1e が接続されている。このように、TFT 30 を LDD 構造で形成することにより、TFT 30 のオフ時ににおけるリーク電流を大幅に低減することができ、保持性能を高めることができる。また、

40

50

TFT30は、低濃度ソース領域1b及び低濃度ドレイン領域1cに不純物の打ち込みを行わないオフセット構造を探っても良いし、走査線3aの一部であるゲート電極をマスクとして高濃度で不純物を打ち込み、自己整合的に高濃度ソース領域1d及び高濃度ドレイン領域1eを形成するセルファアライン型のTFTであっても良い。

#### 【0085】

半導体層1a上には100nm以下の薄膜でゲート絶縁膜2が形成される。ゲート絶縁膜2は、ポリシリコン膜を1000度以上の高温で酸化することにより緻密で絶縁性の高い膜を形成することができる。高温処理ができない場合は、CVD(Chemical Vapor Deposition)等により形成しても良い。ゲート絶縁膜2上には、例えばP(リン)が打ち込まれた低抵抗なポリシリコン膜で形成された走査線3aを配置し、半導体層1aと重なった部分の走査線3aがゲート電極として機能する。10

#### 【0086】

半導体層1a上に形成したゲート絶縁膜2及び走査線3a上に、CVD等により層間絶縁膜81を堆積し、高濃度ドレイン領域1eの所定箇所において、ゲート絶縁膜2及び層間絶縁膜81に対してコンタクトホール8aを開孔する。このコンタクトホール8aを介して高濃度ドレイン領域1eと導電性の中継膜80aを電気的に接続する。中継膜80a上には、層間絶縁膜91、層間絶縁膜4、層間絶縁膜7が順次積層され、これら層間絶縁膜に対して中継膜80a(第2容量電極)の所定位置にコンタクトホール8bを開孔する。このコンタクトホール8bを介して中継膜80aと画素電極9aを電気的に接続する。このように、中継膜80aは、半導体層1aと画素電極9aとを電気的に接続するための中間導電膜として機能する。この中継膜80aにより、画素電極9aから半導体層1aまでの長い距離に対して、一気にコンタクトホールを開孔しなくても良いため、例えば50nm程度と非常に薄い膜厚の半導体層1aの突き抜けを防止することができる。また、コンタクトホールを別々に開孔することで、コンタクトホール8a及び8bの径を夫々小さくできる利点がある。これにより、コンタクトホール8a及び8bを形成する領域が小さくて済むため、その分だけ画素開口率を高めたり、高精細化を実現することができる。中継膜80aの材質として下地遮光膜11aと同様に、Ti、Cr、W、Ta、Mo及びNbなどの不透明な高融点金属を少なくとも一つ含む、金属単体、合金、金属シリサイド等で形成すれば、遮光膜としても機能することができる。更に、エッチング時における選択比が高いため、中継膜80aを例えば50nm程度の膜厚で形成しても、コンタクトホール8bの開孔時に中継膜80aを突き抜けることはない。また、走査線3aと中継膜80aを絶縁するための層間絶縁膜81をTFT30のスイッチング動作に影響を与えない、例えば500nm以上の膜厚で形成すれば、中継膜80aはTFT30や走査線3a上に平面的に見て重なるように設けることができる。これにより、データ線6aの下方で且つTFT30を構成する半導体層1aの直近で遮光できるため、チャネル領域1a'やその接合領域である低濃度ソース領域1b及び低濃度ドレイン領域1cに入射光が直に照射されたり、データ線6a等により反射された迷光が照射されることはない。これにより、TFT30のオフ時におけるリーク電流を大幅に低減することができ、保持性能を格段に高めることができる。30

#### 【0087】

本実施形態では、更に図3に示すように、中継膜80a上に層間絶縁膜91を介して遮光性の導電膜90aを形成している。遮光性の導電膜90aは、前述したようにコンタクトホール5及び8bを除く非開口領域を遮光することができる。また、遮光性の導電膜90aは図1における容量線300として機能することができるため、導電膜90aと中継膜80aとの間で層間絶縁膜91を誘電体膜として蓄積容量70の少なくとも一部を形成することができる。即ち、中継膜80aと遮光性の導電膜90aが蓄積容量70を形成するための電極として機能するのである。また、TFT30を構成する半導体層1aの直近で中継膜80a及び遮光性の導電膜90aの2層で遮光できる。これにより、TFT30のオフ時におけるリーク電流を更に大幅に低減することができるため、投射型プロジェクタ等の強い光源の下で使用される液晶装置にはとても有利である。遮光性の導電膜90aの4050

材質は、下地遮光膜 11 a あるいは中継膜 80 a と同様に、Ti、Cr、W、Ta、Mo 及び Pb などの不透明な高融点金属を少なくとも一つ含む、金属単体、合金、金属シリサイド等で形成すれば、遮光性が高く低抵抗な配線を実現することができる。また、遮光性の導電膜 90 a を形成する前に、例えば活性化熱処理等の 400 度以上の高温処理が終わっていれば、更に低抵抗な Al (アルミニウム) を含む、金属単体、合金、金属シリサイド等から遮光性の導電膜 90 a を形成することができる。このように容量線 300 を兼ねる遮光性の導電膜 90 a をデータ線 6 a の材質と同じ Al で形成することにより、容量線 300 の抵抗を従来のポリシリコン膜に比べて 2 ~ 3 衍分の低減を図ることができる。これにより、容量線 300 の時定数が大きいことにより生じる走査線 3 a 方向のクロストークを大幅に低減できる。

10

#### 【0088】

また、遮光性の導電膜 90 a は各画素電極 9 a 毎にコンタクトホール 95 を介して、走査線 3 a と同一膜からなる容量電極 3 b と電気的に接続するようにしても良い。これにより、容量電極 3 b は遮光性の導電膜 90 a と同じ定電位に固定することができる。したがって、容量電極 3 b と半導体層 1 a の高濃度ドレイン領域 1 e と電気的に接続された中継膜 80 a との間で、層間絶縁膜 81 を誘電体膜として蓄積容量 70 の少なくとも一部をこの領域でも形成することができる。更に、容量電極 3 b と半導体層 1 a の高濃度ドレイン領域 1 e から延設された容量電極 1 f との間で、ゲート絶縁膜 2 を誘電体膜としてこの領域にも蓄積容量 70 の少なくとも一部を形成することもできる。また、コンタクトホール 95 は、データ線 6 a の下方にて開孔するようにし、データ線 6 a に沿って隣接する画素電極 9 a に接続された半導体層 1 a とデータ線 6 a とを電気的に接続するためのコンタクトホール 5 の直近にて、電気的に接続すると良い。このような構成を探れば、データ線 6 a の下方において、蓄積容量 70 を形成するための大きな領域を確保することが可能になる。

20

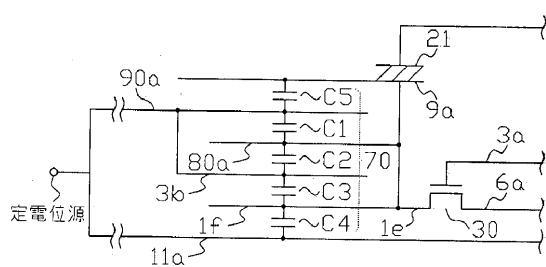

#### 【0089】

図 4 に、本実施形態の液晶装置を構成する 1 画素の等価回路図を示す。図 4 に示すとおり、半導体層 1 a の高濃度ドレイン領域 1 e と中継膜 80 a 及び画素電極 9 a を電気的に接続し、一方、遮光性の導電膜 90 a と容量電極 3 b を電気的に接続する。遮光性の導電膜 90 a は、画像表示領域からその周囲に延設し、周辺領域にて定電位源と接続されている。また、下地遮光膜 11 a と遮光性の導電膜 90 a を電気的に接続しても良い。これらの導電膜を組み合わせることにより、理想的なスタック構造による蓄積容量 70 を形成することができる。即ち本実施形態では、定電位に固定された遮光性の導電膜 90 a、容量電極 3 b 及び下地遮光膜 11 a の各導電膜の層間に誘電体膜を介して高濃度ドレイン領域 1 e から延設された容量電極 1 f、中継膜 80 a 及び画素電極 9 a を形成することができるようになる。

30

#### 【0090】

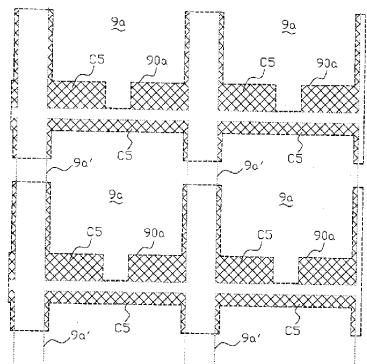

具体的に、図 2 の隣接する画素群の平面図において、どの領域に蓄積容量が形成されているかを図 5 から図 9 に示す。尚、図 2 及び図 5 から図 9 の縮尺は同じとする。

#### 【0091】

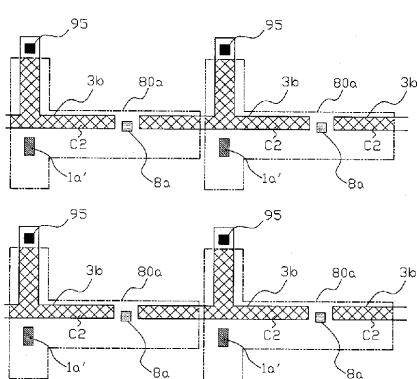

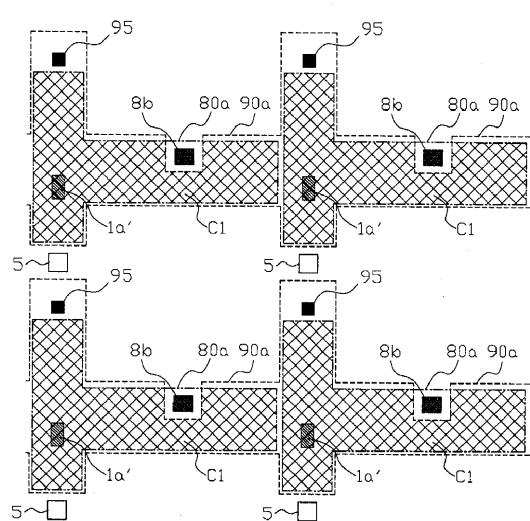

図 5 は、遮光性の導電膜 90 a と中継膜 80 a との間に形成される第 1 蓄積容量 C1 を示している。誘電体膜として、層間絶縁膜 91 を用いる。クロスハッチングの領域が実際に第 1 蓄積容量 C1 が形成される領域で、コンタクトホール 5 やコンタクトホール 95 並びにコンタクトホール 8 b を除く非開口領域のかなりの部分で蓄積容量 C1 を形成できる。ここで、容量電極 3 b を設けない場合は、当該容量電極 3 b と遮光性の導電膜 90 a を電気的に接続するためのコンタクトホール 95 を開孔する必要がなくなるので、この領域でも第 1 蓄積容量 C1 を形成することができる。また、本実施形態では、従来不可能であった TFT 30 のチャネル領域 1 a' 上にも第 1 蓄積容量 C1 を形成することができるため、透過型の液晶装置の画素開口率の向上や微細化にはとても有利である。層間絶縁膜 91 には、酸化膜や窒化膜等の絶縁性及び誘電率の高い膜を用いることができる。また、中継膜 80 a をポリシリコン膜で形成し、更に、遮光性の導電膜 90 a を、下層をポリシリコ

40

50

ン膜、上層を高融点金属を含有した遮光膜といった多層構造で構成することにより、層間絶縁膜 9 1 をポリシリコン膜との連続工程で形成することができるため、欠陥の少ない緻密な絶縁膜を形成することができる。これにより、装置欠陥が減るばかりか、層間絶縁膜 9 1 a を 100 nm 以下の膜厚に形成することが可能なため、第 1 蓄積容量 C 1 を更に増大することができる。

#### 【0092】

次に図 6 は、中継膜 8 0 a と容量電極 3 b との間に形成される第 2 蓄積容量 C 2 を示している。誘電体膜として、層間絶縁膜 8 1 を用いる。クロスハッチングの領域が実際に第 2 蓄積容量 C 2 が形成される領域である。容量電極 3 b は、半導体層 1 a と中継膜 8 0 a を電気的に接続するためのコンタクトホール 8 a の領域で、各画素毎に分断しており、コンタクトホール 9 5 にて上方の遮光性の導電膜 9 0 a と電気的に接続される。図 6 に示すように、容量電極 3 b を T 字型に形成すると、効率的に第 2 蓄積容量 C 2 を形成できる。層間絶縁膜 8 1 には、酸化膜や窒化膜等の絶縁性及び誘電率の高い膜を用いることができる。但し、容量電極 3 b は走査線 3 a と同一膜で形成しているため、第 2 蓄積容量 C 2 を形成できる領域は、図 5 における第 1 蓄積容量 C 1 を形成する領域よりも小さくなる。また、中継膜 8 0 a でチャネル領域 1 a' 及びその隣接領域を遮光する場合には、TFT 3 0 の誤動作を防ぐために層間絶縁膜 8 1 の膜厚は 500 nm 以上必要なことから、第 2 蓄積容量 C 2 は第 2 蓄積容量 C 1 ほど増大させることができない。

#### 【0093】

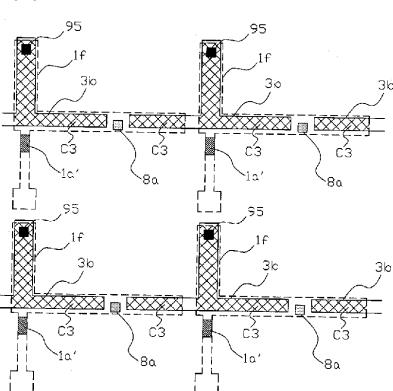

図 7 は、容量電極 3 b と容量電極 1 f との間に形成される第 3 蓄積容量 C 3 を示している。誘電体膜として、ゲート絶縁膜 2 を用いる。クロスハッチングの領域が実際に第 3 蓄積容量 C 3 が形成される領域である。ゲート絶縁膜 2 は前述のように、1000 度以上の高温で酸化して形成するため、緻密で絶縁性の高い膜が形成される。したがって、第 3 蓄積容量 C 3 を形成できる面積は図 6 の第 2 蓄積容量 C 2 を形成する領域とほとんど変わらないが、第 3 蓄積容量 C 3 は第 2 蓄積容量 C 2 より大きく形成することができる。また、容量電極 3 b と上方の遮光性の導電膜 9 0 a を電気的に接続するためのコンタクトホール 9 5 の形成領域の下方にも第 3 蓄積容量 C 3 を形成することができる。

#### 【0094】

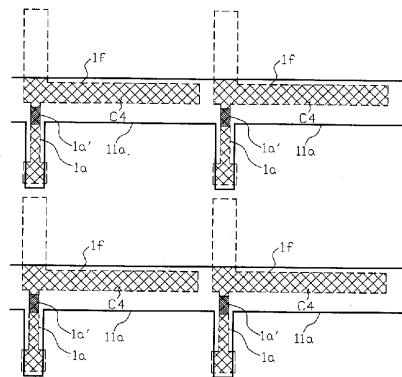

更に、図 8 に示すように、容量電極 1 f と下地遮光膜 1 1 a との間にも第 4 蓄積容量 C 4 を形成することができる。誘電体膜として、下地絶縁膜 1 2 を用いる。クロスハッチングの領域が実際に第 4 蓄積容量 C 4 が形成される領域である。下地絶縁膜 1 2 を 500 nm 以下の膜厚で形成すると、チャネル領域 1 a' と下地遮光膜 1 1 a の距離も近づくため、TFT 3 0 が下地遮光膜 1 1 a の電位によって誤動作してしまう。そこで、蓄積容量 1 f と下地遮光膜 1 1 a が平面的に見て重なる領域の下地絶縁膜 1 2 を選択的に薄膜化して第 4 蓄積容量 C 4 を増大させるようにしても良い。すなわち、チャネル領域 1 a に対向する下地絶縁膜 1 2 の領域以外の部分を薄膜にすることで、第 4 蓄積容量 C 4 を増大させることができる。

#### 【0095】

更に、図 9 に示すように、画素電極 9 a と遮光性の導電膜 9 0 a との間にも第 5 蓄積容量 C 5 を形成することができる。誘電体膜として、層間絶縁膜 4 及び層間絶縁膜 7 を用いる。クロスハッチングの領域が実際に第 5 蓄積容量 C 5 が形成される領域である。層間絶縁膜 4 及び層間絶縁膜 7 としては、例えば、NSG、PSG、BSG、BPSG などの高絶縁性ガラス又は、酸化シリコン膜、窒化シリコン膜等からなる。但し、データ線 6 a は層間絶縁膜 4 上に形成されるため、画素電極 9 a とデータ線 6 a との間に生じる寄生容量により表示画像が劣化するため、層間絶縁膜 7 を厚くする必要があり、実際には第 5 蓄積容量 C 5 を第 1 蓄積容量 C 1 ほどには増大することができない。

#### 【0096】

このように、本実施形態の液晶装置は、蓄積容量 7 0 を形成するための容量電極を誘電体膜を介して積層していくことにより、第 1 蓄積容量 C 1 から第 5 蓄積容量 C 5 まで 5 層からなるスタック型の蓄積容量 7 0 を形成することができる。これにより、蓄積容量形成用

10

20

30

40

50

の領域が小さくても、効率的に大きな蓄積容量 7 0 を形成することができる。ここで、本実施形態の液晶装置は、少なくとも第 1 蓄積容量 C 1 が形成できれば良い。今後、画素の高開口率化や微細化が更に進み、例えば蓄積容量電極 3 b を形成することができなくても、本実施形態の構造によれば第 1 蓄積容量 C 1 の誘電体膜である層間絶縁膜 9 1 を薄膜化することで十分な蓄積容量 7 0 を得ることができる。したがって、本実施形態によれば、電気光学装置の目的にあった仕様に対して、第 1 蓄積容量 C 1 から第 5 蓄積容量 C 5 までの蓄積容量の中から選択して用いることができ有利である。

#### 【 0 0 9 7 】

再び図 3 に示すように、データ線 6 a は、遮光性の導電膜 9 0 a より上方の層間絶縁膜 4 上に形成されている。また、データ線 6 a は、ゲート絶縁膜 2 , 層間絶縁膜 8 1 , 層間絶縁膜 9 1 及び層間絶縁膜 7 の所定箇所にコンタクトホール 5 を開孔し、このコンタクトホール 5 を介して半導体層 1 a の高濃度ドレイン領域 1 e と電気的に接続されている。更に、データ線 6 a は画像信号が供給されるため、A 1 等の低抵抗で遮光性の高い金属膜や金属シリサイド等から構成されている。

#### 【 0 0 9 8 】

ここで、本実施形態の液晶装置では、データ線 6 a に加えて、遮光性の導電膜 9 0 a 等により非開口領域である遮光領域を規定することができる。具体的には、図 10 に示すように、画素電極 9 a に重なるように遮光性の導電膜 9 0 a を形成し、チャネル領域 1 a' を含むほとんどの領域を遮光するようとする。また、遮光性の導電膜 9 0 a でデータ線 6 a に沿った領域のほとんどを遮光することができるため、従来のようにデータ線 6 a だけで遮光領域を規定する必要がなくなり、データ線 6 a と画素電極 9 a とを層間絶縁膜 7 を介して極力重ねないように構成することができる。これにより、データ線 6 a と画素電極 9 a との間の寄生容量を大幅に低減することができ、画素電極 9 a の電位変動による表示画質の低下を招くことがない。但し、遮光性の導電膜 9 0 a はデータ線 6 a より下方に形成されるので、データ線 6 a と半導体層 1 a を電気的に接続するためのコンタクトホール 5 を形成する領域は遮光できない。そこで、コンタクトホール 5 が形成される領域はデータ線 6 a を画素電極 9 a に一部重ねるように幅広に形成すれば良い。このコンタクトホール 5 を形成する領域がチャネル領域 1 a' の直近にあると、遮光性の導電膜 9 0 a でチャネル領域 1 a' 付近を十分に遮光できなくなるため、このような場合には、コンタクトホール 5 の形成領域をデータ線 6 a に沿ってチャネル領域 1 a' から遠ざける方向に移動しても何ら問題ない。本実施形態では、このようにコンタクトホール 5 の形成領域を移動しても中継膜 8 0 a と遮光性の導電膜 9 0 a との間に形成される第 1 蓄積容量 C 1 は変化しないという利点がある。また、遮光性の導電膜 9 0 a は、中継膜 8 0 a と画素電極 9 a とを電気的に接続するためのコンタクトホール 8 b の形成領域にも設けることができないため、この領域は中継膜 8 0 a で遮光すれば良い。もし、中継膜 8 0 a をポリシリコン膜等の光透過性の膜で形成する場合には、下地遮光膜 1 1 a にて遮光しても構わない。この際、コンタクトホール 8 b の形成領域は、チャネル領域 1 a' から遠ざけるようにした方が良い。図 10 に示すように、隣接するデータ線 6 a の中間にコンタクトホール 8 b を設けるようにすれば、入射光が下地遮光膜 1 1 a に照射されても、チャネル領域 1 a' に到達することができなく有利である。また、画素の構成をデータ線 6 a に対して線対称に形成できるため、例えば、T N 液晶の捻れ方向が異なる液晶装置を組み合わせるプロジェクタ等で、色むら等の表示画質の低下を招くことがない。

#### 【 0 0 9 9 】

このように、本実施形態では、TFT アレイ基板 1 0 上で遮光領域を規定することができるため、図 3 に示すように、対向基板 2 0 に遮光膜を設ける必要がなくなる。したがって、TFT アレイ基板 1 0 と対向基板 2 0 を機械的に貼り合わせる際に、アライメントがずれたとしても対向基板 2 0 上に遮光膜がないため、光が透過する領域（開口領域）が変化することはない。これにより、常に安定した画素開口率が得られるため、装置不良を大幅に低減することができる。

#### 【 0 1 0 0 】

10

20

30

40

50

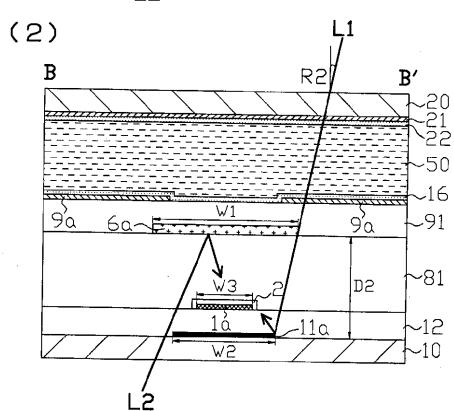

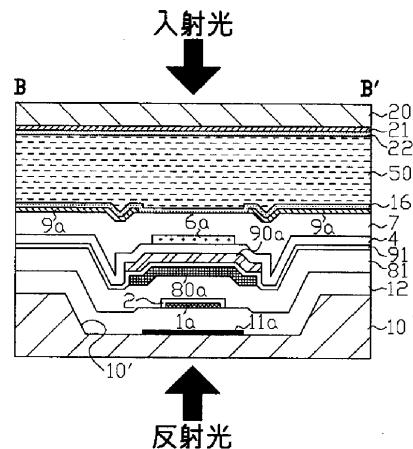

また、本実施形態による液晶装置は、入射光の入射角度に対しても従来より強い構造を採ることができる。そこで、図11を参照して説明する。図11(1)は、図2におけるB-B'に沿った断面図で、図11(2)は従来の構造を示している。尚、図11(1)及び(2)においては、同じ縮尺で表している。

#### 【0101】

一般に、半導体層1aのチャネル領域付近に光が照射されると、TFT30のオフ時において、光励起によるリーク電流が発生するため、画素電極9aに書き込まれた電荷を保持する能力が低下してしまう。そこで、本実施形態では、図11(1)に示すように、入射光L1に対しては遮光性の導電膜90aを設け、TFTアレイ基板10方向からの反射光L2に対しては下地遮光膜11aを設けることにより、半導体層1aへの光の照射を防ぐ構造を採る。また、入射光L1の光量に対して、反射光L2は100分の1以下の光量しか照射されないため、チャネル領域及びその近接領域において入射光L1を遮光するための遮光性の導電膜90aの幅W1の方が、下地遮光膜11aの幅W2より長くなるように構成する。即ち、チャネル領域及びその近接領域において下地遮光膜11aが遮光性の導電膜90aをはみ出さないように形成されている。更に、半導体層1aの幅W3はチャネル領域及びその近接領域において下地遮光膜11aの幅W2よりも短くなるように構成する。即ち、チャネル領域及びその近接領域がTFTアレイ基板側から見て下地遮光膜11aにより覆われている。このような構成を採ることにより、入射光L1がある角度をもって入射されたとしても、半導体層1aへ光が到達する可能性を低減することができる。また、本実施形態では、遮光性の導電膜90aをデータ線6aと半導体層1aの層間に形成することができるため、図11(2)に示す従来例のようにデータ線6aでチャネル領域を遮光する場合よりも、更にチャネル領域の直近で遮光することが可能になる。ここで、本実施形態及び従来例において、入射光L1の入射角度に対するマージンを考えてみる。通常、入射光L1は、半導体層1aに直接照射されることは半導体層1aの幅W3が、例えば $1\mu m$ と短いことから、あまり考えられない。そこで、半導体層1aの下方に設けられた下地遮光膜11aに照射された光が反射して半導体層1aに照射されると仮定してみる。ここで、図11における(1)本実施形態及び(2)従来例に示す下地遮光膜11aの幅は同じW2とする。また、入射光L1を遮るために本実施形態における遮光性の導電膜90aの幅と、従来例におけるデータ線6aの幅と同じW1とする。本実施形態では、下地遮光膜11aと遮光性の導電膜90aの層間距離をD1とし、一方従来例は、下地遮光膜11aとデータ線6aまでの層間距離をD2とする。ここで、本実施形態における下地遮光膜11aとデータ線6aまでの層間距離をD2とすると、 $D1 > D2$ の関係になる。したがって、入射光L1が同じ角度で入射されてきた場合、下地遮光膜11aまでの層間距離が短い分だけ、入射光L1の角度が本実施形態の方がマージンがあることになる。即ち、本実施形態における入射光L1のマージン角度をR1とし、従来例における入射光L1のマージン角度をR2とすると、 $R1 > R2$ の関係になる。この結果から、本実施形態の液晶装置の方が入射光の入射角度にマージンがあるため、今後、光学系が小型化されて更に入射角度が大きくなっても対応することができ、有利である。尚、本実施形態では、半導体層1aの側面部に絶縁膜を介して遮光膜を形成することも可能であり、入射角度への対応を更に向上させることができる。

#### 【0102】

また、本実施形態の液晶装置では、従来例のようにデータ線6aで遮光する必要がないため、チャネル領域及びその近接領域においてデータ線6aの幅W4を遮光性の導電膜90aの幅W1よりも短くすることができる。即ち、 $W1 > W4$ の関係になり、チャネル領域及びその近接領域において、データ線6aが遮光性の導電膜90aをはみ出さないように形成されている。これにより、データ線6aで反射された光が迷光となって半導体層1aに照射されるのを未然に防ぐことができる。特に、遮光性の導電膜90aは、データ線6aを形成するA1よりも反射率の低い高融点金属を含有した膜で形成することができるため、データ線6aによる迷光を遮光性の導電膜90aで吸収することも可能である。

#### 【0103】

10

20

30

40

50

更に、本実施形態の液晶装置では、遮光性の導電膜 90 a の下方に中継膜 80 a を形成することも可能なことから、この中継膜 80 a により半導体層 1 a を直近で遮光することができ、遮光性が向上する。この場合、中継膜 80 a の幅を遮光性の導電膜 90 a の幅 W1 とほぼ同じにすると、更に遮光性が高まる。また、万が一、TFTアレイ基板 10 側から反射光 L2 が入射された場合、従来例では反射率の高いデータ線 6 a を遮光膜として代用するため、データ線 6 a の下方で反射された迷光が半導体層 1 a に照射される恐れがあつたが、本実施形態では中継膜 80 a をポリシリコン膜や低反射な高融点金属を含有した膜で形成することにより光を吸収するようとする。これにより、内面反射の迷光を大幅に低減することができ、何ら TFT30 のリークによる画質表示の劣化を心配する必要がなくなる。また、中継膜 80 a を低反射な膜で形成することにより、遮光性の導電膜 90 a はデータ線 6 a と同じ高反射な A1 を少なくとも含有した膜で形成しても構わない。このように、液晶装置の遮光領域を例えば可視光領域において 80 % 以上の反射率を有する高反射率の A1 を少なくとも含有した膜で、データ線 6 a 及び遮光性の導電膜 90 a を形成することが可能になるため、入射光をデータ線 6 a 及び遮光性の導電膜 90 a で反射させ、液晶装置の温度上昇を防ぐことができる。したがって本実施形態における液晶装置では、例えばプロジェクトの冷却装置の開発にかかるコストを低減したり、液晶装置の耐光性を向上させることが可能である。

#### 【0104】

以上説明した本実施形態において、画素電極 9 a 下の層間絶縁膜 7 の表面を平坦化している。これは、配線や素子等の段差による液晶のディスクリネーションを防ぐためで、更に下方の層間絶縁膜 4 等に対して行っても良い。ここで、平坦化処理としては、有機や無機の SOG (Silicon On glass) 膜をスピンドルコーターにて塗布しても良いし、CMP 処理を施すことにより、平坦化を図ることも可能である。

#### 【0105】

##### (第2実施形態)

本発明の電気光学装置の第2実施形態の構成について、図12から図16を参照して説明する。

#### 【0106】

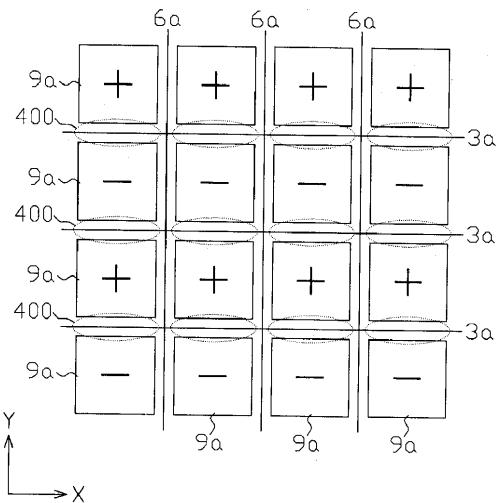

電気光学装置の一例である液晶装置は、一般に液晶の劣化を防ぐために交流反転駆動を行わなければならない。そこで、いくつかの駆動方法が提案されているが、本発明の第2実施形態の液晶装置では、図12に示すように走査線 3 a 每に液晶にかかる画像信号の極性を反転し、更に、これに加えて 1 フィールド毎に画像信号の極性を反転する構成を探る。これにより、液晶にかかる直流成分を極力抑えることができ、フリッカーの発生を大幅に低減することができる。このように走査線 3 a 每に画像信号の極性を反転させる場合、走査線 3 a に沿って X 方向に隣接する画素電極 9 a には同じ極性の画像信号が書き込まれるため、隣接する画素電極 9 a 間において、電界が発生しない。一方、データ線 6 a に沿って Y 方向に隣接する画素電極 9 a には、異なる極性の画像信号が書き込まれるため、隣接する画素電極 9 a 間において、電界が発生し液晶のディスクリネーション 400 が生じる。

#### 【0107】

そこで、図12におけるディスクリネーション 400 の発生領域を最小限に抑えるために、本発明の第2実施形態では、図13に示すように、TFTアレイ基板の相隣接する複数の画素群は、右上がりの斜線領域部において、TFTアレイ基板 10 に対して溝 10' を形成し、データ線 6 a 等の配線や TFT30 を部分的に埋め込んで平坦化する。また、TFTアレイ基板に対するラビング処理を矢印の方向で行う場合には、開口領域に接した走査線 3 a の領域に溝 10' を設けないようにすることで、ディスクリネーション 400 の発生領域を更に低減することができる。これにより、各画素の光漏れ領域が低減し、画素開口率を大幅に向上することができる。特に、明るさ及び小型を要求されるプロジェクト用の液晶装置には最適である。

#### 【0108】

10

20

30

40

50

図14は、図13のA-A'に沿った断面図を示す。図14に示すように、TFT30や蓄積容量70を形成する領域のTFTアレイ基板10に溝10'を形成することにより、画素電極9a及び配向膜16をほぼ平坦に形成することができる。溝10'は、パターン形成で通常に用いられるフォトリソグラフィ及びエッチングにより容易に形成できる。また、溝10'の側壁のテーパー角度はドライエッチング法やウェットエッチング法を駆使することにより様々に制御することができる。また、溝10'を形成しての平坦化は溝10'の深さの制御が重要になるが、ドライエッチングの時間管理等により容易に制御できる。このように、溝10'を形成して平坦化する場合には、光に対して感光しやすい有機膜等を一切使用せずに平坦化が実現できるので、強い光源を用いるプロジェクタに用いられる液晶装置には特に有利である。

10

#### 【0109】

図15は、図13のB-B'に沿った断面図で、図12においてX方向に相隣接する画素電極9a間の断面構造を示す。このように、TFTアレイ基板10に溝10'を形成することで、データ線6aの形成領域をほぼ完全に平坦化することができる。特に、図13に示すようにデータ線6aに沿ってラビング処理する場合に、データ線6a等が形成されている領域は埋め込まれて平坦化されているため、データ線6a等の配線や素子による段差でディスクリネーションが発生することはない。

#### 【0110】

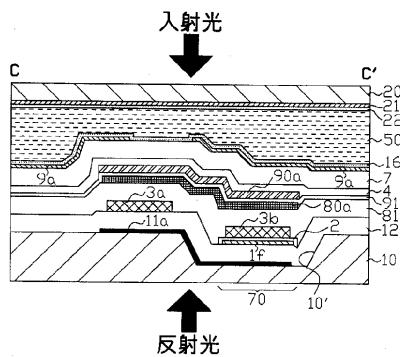

図16は、図13のC-C'に沿った断面図で、図12においてY方向に相隣接する画素電極9a間の断面構造を示す。この領域では、隣接する画素電極9a間の電界による液晶のディスクリネーションが発生するため、図16に示すように、隣接する画素電極9aの分断領域において、液晶層50のセルギャップが狭くなるように、走査線3aの形成領域にはTFTアレイ基板10に溝10'を形成しないようにする。これにより、相隣接する画素電極9a間で電界が生じても、対向基板20に設けられた対向電極21と画素電極9aとの電界が強められるため、液晶のディスクリネーションが発生する領域を極力小さくすることができるのである。また、液晶のセルギャップそのものを狭くしてディスクリネーションを低減する必要がないため、狭セルギャップ用の液晶開発やセルギャップ制御が困難になるといった諸問題が発生することもない。

20

#### 【0111】

このように、本発明の第2実施形態では、TFTアレイ基板10上に溝10'を形成し、その中に配線や素子をほぼ完全にあるいは部分的に埋め込むことができるので、CMP処理のように完全にしか平坦化できない場合と比較して、更に高開口率な画素を備えた電気光学装置を実現することができる。尚、溝10'はTFTアレイ基板10の他に、下地絶縁膜12や層間絶縁膜81等の層間絶縁膜に形成しても同様な効果が得られる。また、TFTアレイ基板10に設けられた溝10'と、下地絶縁膜12や層間絶縁膜81等の層間絶縁膜に設けた溝とを組み合わせて平坦化しても良いことは言うまでもない。

30

#### 【0112】

##### (第3実施形態)

本発明による電気光学装置の第3実施形態である液晶装置の構成について、図17及び図18を参照して説明する。図17は、データ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図であり、図18は、図17のA-A'に沿った断面図である。尚、図18においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

40

#### 【0113】

図17に示すように、第3実施形態では、走査線3aと同一膜で容量電極3bを兼ねた補助配線3b'を形成しているところが、第1実施形態と大きく違う。また、補助配線3b'は、走査線3aの方向に沿って画像表示領域からその周囲に延設し、周辺領域にて定電位源と接続することができる。定電位源としては、後述する当該液晶装置を駆動するための周辺回路（例えば、走査線駆動回路、データ線駆動回路等）に供給される負電源、正電源等の定電位源、接地電源、対向電極に供給される定電位源等が挙げられ、遮光性の導電

50

膜 9 0 a に供給される電位と同じであることが好ましい。これにより、補助配線 3 b' は図 1 における容量線 3 0 0 の一部として機能することができる。また、データ線 6 a の下方でコンタクトホール 9 5 を介して上方の遮光性の導電膜 9 0 a と電気的に接続することもできる。この際、コンタクトホール 9 5 を介しての補助配線 3 b' と遮光性の導電膜 9 0 aとの接続は、各画素電極 9 a 每に行っても構わないし、複数の画素電極 9 a 每に行っても良い。このように、補助配線 3 b' と遮光性の導電膜 9 0 a により冗長構造の容量線 3 0 0 を構築することができる。尚、第 1 実施形態や第 2 実施形態でも遮光領域にある場合は、容量電極 3 b を延設して補助配線 3 b' を構築しても良いことは言うまでもない。

## 【 0 1 1 4 】

10

また、第 3 実施形態では、図 1 7 に示すように、右上がりの斜線で示される中継膜 8 0 a' が走査線 3 a に平面的に重ならないように形成されているところが、第 1 実施形態と大きく違う。これは、図 1 8 に示すように、層間絶縁膜 8 1 を 1 0 0 nm 以下の膜厚で形成することにより、容量電極を含む補助配線 3 b' 上で大きな蓄積容量を形成することができる。即ち、図 4 に示す蓄積容量 C 2 を増大させることができる。この場合、走査線 3 a と中継膜 8 0 a' の間を絶縁するための層間絶縁膜 8 1 が薄膜化されるため、走査線 3 a 上に重なるように中継膜 8 0 a' を設けると寄生容量が増大し、走査信号が遅延してしまう。また、中継膜 8 0 a' にかかる電位の影響で TFT 3 0 が誤動作するため、チャネル領域 1 a' 付近にも中継膜 8 0 a' を設けることができない。しかしながら、半導体層 1 a と中継膜 8 0 a' との間の層間絶縁膜 8 1 を非常に薄く形成することができるため、半導体層 1 a の高濃度ドレイン領域 1 e と中継膜 8 0 a' とを電気的に接続するためのコンタクトホール 8 a 開孔時に半導体層 1 a を突き抜けることはない。また、コンタクトホール 8 a の開口径を非常に小さくすることができる利点がある。更に、遮光性の導電膜 9 0 a は、チャネル領域 1 a' 及びその隣接領域と走査線 3 a 上の遮光をするために、層間絶縁膜 9 1 を 5 0 0 nm 以上の膜厚で形成しなければならないが、補助配線 3 b' と遮光性の導電膜 9 0 aとの間で図 4 に示す蓄積容量 C 1 を形成することができる。

20

## 【 0 1 1 5 】

## ( 第 4 実施形態 )

30

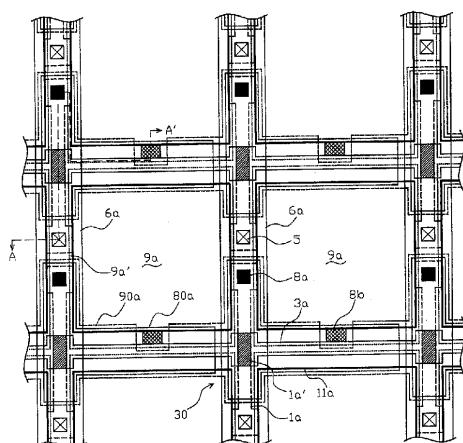

本発明による電気光学装置の第 4 実施形態である液晶装置の構成について、図 1 9 及び図 2 0 を参照して説明する。図 1 9 は、データ線、走査線、画素電極等が形成された TFT アレイ基板の相隣接する複数の画素群の平面図であり、図 2 0 は、図 1 9 の A - A' に沿った断面図である。尚、図 2 0においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。第 1 実施形態と同一の部材については同一の符号を付し詳細な説明は省略する。

## 【 0 1 1 6 】

40

第 4 実施形態は、図 1 9 に示すように、非開口領域のほぼ中心に走査線 3 a 及びデータ線 6 a を設けている。半導体層 1 a は、走査線 3 a と交差するようにデータ線 6 a の下方に配置する。図 2 0 に示すようにデータ線 6 a と半導体層 1 a の高濃度ソース領域 1 d は、データ線 6 a の下方においてコンタクトホール 5 を介して電気的に接続されている。また、半導体層 1 a の高濃度ドレイン領域 1 e と中継膜 8 0 a は、データ線 6 a の下方においてコンタクトホール 8 a を介して電気的に接続されている。このように半導体層 1 a を遮光性のデータ線 6 a の下方に配置することにより、対向基板 2 0 側から入射される光が直接半導体層 1 a に照射されることを防ぐ効果がある。更に、半導体層 1 a とコンタクトホール 5 及び 8 a を、走査線 3 a 方向の非開口領域及びデータ線 6 a 方向の非開口領域の中心線に対して線対称に形成することにより、段差形状をデータ線 6 a に対して左右対称にすることができ、液晶の回転方向による光抜けの差がなくなるので有利である。

## 【 0 1 1 7 】

半導体層 1 a の下方には、下地絶縁膜 1 2 を介して下地遮光膜 1 1 a が形成されている。下地遮光膜 1 1 a はデータ線 6 a 方向及び走査線 3 a 方向に沿って、マトリクス状に形成されている。半導体層 1 a は下地遮光膜 1 1 a の内側に配置されており、TFT アレイ基

50

板 10 側からの戻り光が、直接半導体層 1 a に照射されることを防ぐ効果がある。

#### 【 0 1 1 8 】

中継膜 8 0 a はポリシリコン膜や高融点金属等を含む導電膜から成り、半導体層 1 a と画素電極 9 a の層間に於いて、走査線 3 a 及びデータ線 6 a に沿って略 T 字型に延設され、半導体層 1 a と画素電極 9 a を電気的に接続するためのバッファとしての機能を果たす。具体的には、半導体層 1 a の高濃度ドレイン領域 1 e と導電性の中継膜 8 0 a をコンタクトホール 8 a において電気的に接続し、中継膜 8 0 a と画素電極 9 a をコンタクトホール 8 b において電気的に接続されている。このような構成を採る事により、層間絶縁膜に対して深いコンタクトホールを開孔する場合でも、エッチング選択比が大きい中継膜 8 0 a を設けることにより、コンタクトホール開孔時に半導体層 1 a を突き抜けてしまう危険を回避する事ができる。尚、データ線 6 a と半導体層 1 a の高濃度ソース領域 1 d とを電気的に接続するためのコンタクトホール 5 においても同様に、中継膜 8 0 a と同一膜で中継させても良い。10

#### 【 0 1 1 9 】

また、第 4 実施形態では、中継膜 8 0 a に層間絶縁膜 9 1 が積層され、その上に遮光性の導電膜 9 0 a を形成している。遮光性の導電膜 9 0 a は、コンタクトホール 8 b を除いて中継膜 8 0 a を覆うように走査線 3 a 方向に画像表示領域の外側まで延設され、走査線駆動回路やデータ線駆動回路等に供給される負電源、正電源等の定電位源、接地電源、あるいは対向電極に供給される定電位源等のいずれかと電気的に接続することにより電位が固定されている。したがって、中継膜 8 0 a を一方の容量電極とし、遮光性の導電膜 9 0 a を他方の容量電極として図 4 及び図 5 に示す蓄積容量 C 1 を形成することができる。この際、層間絶縁膜 9 1 が蓄積容量 C 1 の誘電体膜として機能することは言うまでもない。ここで、層間絶縁膜 9 1 は蓄積容量 C 1 を形成するためだけに積層するので、中継膜 8 0 a と遮光性の導電膜 9 0 aとの間でリークしない膜厚まで層間絶縁膜 9 1 を薄膜化することにより、蓄積容量 C 1 を増大できる。更に、第 4 実施形態では層間絶縁膜 8 1 を厚く形成することにより、中継膜 8 0 a を TFT 3 0 や走査線 3 a の上方まで延設することができるため、蓄積容量 C 1 を効率良く増大させることができる。更に、第 4 実施形態では半導体層 1 a を延設して容量電極を形成していない。これにより、走査線 3 a と同一膜で蓄積容量を形成するための容量電極及び容量線を形成する必要がないため、図 1 9 に示すように、走査線 3 a を遮光性の導電膜 9 0 a や下地遮光膜 1 1 a から規定される非開口領域のほぼ中心に配置することができる。また、ポリシリコン膜から成る半導体層 1 a は膜の低抵抗化をする必要がないので、容量電極形成部に不純物を打ち込まなくても良く、工程を削減する事ができる。20

#### 【 0 1 2 0 】

第 4 実施形態では、TFT 3 0 のチャネル領域 1 a' は、走査線 3 a とデータ線 6 a の交差部に形成することで、データ線 6 a 方向と走査線 3 a 方向の非開口領域のほぼ中心に設けることができる。これにより、対向基板 2 0 側からの入射光や TFT アレイ基板 1 0 側からの戻り光に対して、最も光が照射されにくい位置になるため、光による TFT 3 0 のリーク電流を大幅に低減することができる。30

#### 【 0 1 2 1 】

更に、第 4 実施形態では図 1 9 に示すように、チャネル領域 1 a' 付近において、遮光性の導電膜 9 0 a , 中継膜 8 0 a , 下地遮光膜 1 1 a の順にパターン幅を狭く形成する事により、入射光が直接下地遮光膜 1 1 a に照射されないように工夫してある。また、遮光性の導電膜 9 0 a と半導体層 1 a の間にポリシリコン膜からなる中継膜 8 0 a を介在させる事により、下地遮光膜 1 1 a 表面での反射光や TFT アレイ基板 1 0 側からの戻り光を吸収させる効果を持たせる事ができ、耐光性に有利である。40

#### 【 0 1 2 2 】

また、第 4 実施形態では、データ線 6 a , 遮光性の導電膜 9 0 a , 下地遮光膜 1 1 a 等により TFT アレイ基板 1 0 上で非開口領域を形成できるため、対向基板 2 0 に遮光膜を設けなくても良い。これにより、TFT アレイ基板 1 0 と対向基板 2 0 を機械的に貼り合わ50

せる際に、アライメントがずれたとしても対向基板 20 上に遮光膜がないため、光が透過する領域（開口領域）が変化することはない。これにより、常に安定した画素開口率が得られるため、装置不良を大幅に低減することができる。

### 【0123】

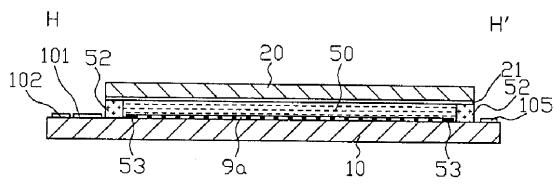

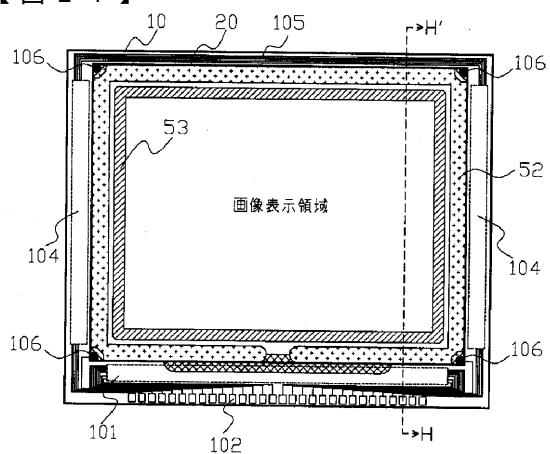

（電気光学装置の全体構成）

以上のように構成された各実施形態における液晶装置の全体構成を図21及び図22を参照して説明する。尚、図21は、TFTアレイ基板10をその上に形成された各構成要素と共に対向基板20の側から見た平面図であり、図22は、図21のH-H'断面図である。

### 【0124】

図21において、素子や配線が形成されたTFTアレイ基板10上には、シール材52が対向基板20の縁に沿って設けられており、その内側に並行して、画像表示領域の周辺を規定するための遮光性の額縁53が設けられている。この額縁53は、本実施形態のようにTFTアレイ基板10側に設けても良いし、対向基板20側に設けても良い。シール材52の外側の領域には、データ線6aに画像信号を所定タイミングで供給するためのデータ線駆動回路101及び外部回路接続端子102がTFTアレイ基板10の一辺に沿って設けられており、走査線3aに走査信号を所定タイミングで供給するための走査線駆動回路104が、この一辺に隣接する2辺に沿って設けられている。走査線3aに供給される走査信号の遅延が問題にならないのならば、走査線駆動回路104は片側だけでも良いことは言うまでもない。また、データ線駆動回路101を画像表示領域の辺に沿って両側に配列しても良い。更にTFTアレイ基板10の残る一辺には、画像表示領域の両側に設けられた走査線駆動回路104間に共通の信号を供給するための複数の配線105が設けられている。また、対向基板20のコーナー部の少なくとも1箇所において、TFTアレイ基板10と対向基板20との間で電気的な導通をとるための上下導通材106が設けられている。即ち、外部回路接続端子102から印加された対向電極電位が、TFTアレイ基板10に設けられた配線及び上下導通材106を介して、対向基板20に設けられた対向電極21に供給される。そして、図22に示すように、対向基板20がシール材52によりTFTアレイ基板10に固着されている。尚、TFTアレイ基板10上には、これらのデータ線駆動回路101、走査線駆動回路104等に加えて、複数のデータ線6aに画像信号を所定のタイミングで供給するサンプリング回路、複数のデータ線6aに所定電圧レベルのプリチャージ信号を画像信号に先行して各々供給するプリチャージ回路、製造途中や出荷時の当該液晶装置の品質、欠陥等を検査するための検査回路等を形成しても良い。このように、本実施形態における液晶装置では、画素電極9aを制御するためのTFT30を形成する工程で、データ線駆動回路101や走査線駆動回路102等の周辺回路を同一のTFTアレイ基板10上に形成することができるため、高精細で高密度な液晶装置を実現することができる。

### 【0125】

また、データ線駆動回路101及び走査線駆動回路104をTFTアレイ基板10上に設ける代わりに、例えばTAB(Tape Automated Bonding)基板上に実装された駆動用LSIに、TFTアレイ基板10の周辺部に設けられた異方性導電フィルムを介して電気的及び機械的に接続するようにしても良い。更に、対向基板20の投射光が入射する側及びTFTアレイ基板10の出射光が出射する側には各々、例えば、TNモード、VA(Vertically Aligned)モード、PDL C(Polymer Dispersed Liquid Crystal)モード等の動作モードや、ノーマリーホワイトモード／ノーマリープラックモードの別に応じて、偏光フィルム、位相差フィルム、偏光板などが所定の方向で配置しても良い。

### 【0126】

以上説明した各実施形態における液晶装置は、カラー表示のプロジェクタに適用されるため、3枚の液晶装置がR(赤)G(緑)B(青)用のライトバルブとして各々用いられ、各ライトバルブにはRGB色分解用のダイクロイックミラーを介して分解された各色の光が投射光として入射されることになる。従って、各実施形態では、対向基板20に、カラ

10

20

30

40

50

ーフィルタは設けられていない。しかしながら、画素電極 9 a に対向する所定領域に R G B のカラーフィルタをその保護膜と共に、対向基板 2 0 上に形成しても良い。あるいは、T F T アレイ基板 1 0 上において R G B に対向する画素電極 9 a 下にカラーレジスト等でカラーフィルタ層を形成することも可能である。このようにすれば、プロジェクタ以外にも直視型や反射型のカラー液晶テレビなどのカラー表示用の液晶装置に各実施形態における液晶装置を適用できる。更に、対向基板 2 0 上に 1 画素 1 個対応するようにマイクロレンズを形成しても良い。このようにマイクロレンズを形成することにより、入射光の集光効率を格段に向上でき、明るい液晶装置が実現できる。更にまた、対向基板 2 0 上に、何層もの屈折率の相違する干渉層を堆積することで、光の干渉を利用して、R G B 色を作り出すダイクロイックフィルタを形成しても良い。このダイクロイックフィルタ付き対向基板によれば、より明るいカラー表示用の液晶装置が実現できる。

#### 【0127】

尚、以上説明した各実施形態における液晶装置では、従来と同様に入射光を対向基板 2 0 の側から入射することとしたが、下地遮光膜 1 1 a 及び遮光性の導電膜 9 0 a を T F T アレイ基板 1 0 上に設けているので、T F T アレイ基板 1 0 の側から光を入射し、対向基板 2 0 の側から出射するようにしても良い。また、T F T アレイ基板 1 0 の裏面側での反射を防止するための反射防止用の A R (Anti Reflection) 被膜された偏光板を別途配置したり A R フィルムを貼り付ける必要もなく、その分だけ、材料コストを削減でき、また偏光板貼り付け時に、ごみ、傷等により、歩留まりを落とすことがなく大変有利である。また、耐光性が優れているため、明るい光源を使用したり、偏光ビームスプリッタにより偏光変換して、光利用効率を向上させても、光によるクロストーク等の画質劣化を生じない。また、本実施形態では、導電膜 9 0 a は遮光性で形成されているが、対向基板側からの光の入射に対して他に遮光性の膜が形成されている場合は、導電膜 9 0 a は遮光性で形成しない場合がある。導電膜 9 0 a が遮光性を有していない場合でも、本実施例の構成によれば、蓄積容量を増大することが可能である。

#### 【0128】

また、各画素に設けられるスイッチング素子としては、正スタガ型又はコプラナー型のポリシリコン T F T であるとして説明したが、逆スタガ型の T F T やアモルファスシリコン T F T 等の他の形式の T F T に対しても、各実施形態は有効である。

#### 【0129】

本発明の電気光学装置は、上述した各実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴なう電気光学装置もまた本発明の技術的範囲に含まれるものである。

#### 【図面の簡単な説明】

【図 1】本発明の第 1 実施形態の電気光学装置における画像表示領域を構成するマトリクス状の複数の画素に設けられた各種素子、配線等の等価回路図である。

【図 2】第 1 実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成された T F T アレイ基板の相隣接する複数の画素群の平面図である。

【図 3】図 2 の A - A' に沿った断面図である。

【図 4】本発明の実施形態の電気光学装置を構成する 1 画素の等価回路図である。

【図 5】図 2 のうち、遮光性の導電膜及び中継膜を抜粋して示す平面図である。

【図 6】図 2 のうち、中継膜及び第 2 容量電極を抜粋して示す平面図である。

【図 7】図 2 のうち、第 2 容量電極及び半導体層を抜粋して示す平面図である。

【図 8】図 2 のうち、半導体層及び下地遮光膜を抜粋して示す平面図である。

【図 9】図 2 のうち、遮光性の導電膜及び画素電極を抜粋して示す平面図である。

【図 10】図 2 のうち、下地遮光膜、遮光性の導電膜、中継膜及びデータ線を抜粋して示す平面図である。

【図 11】(1) は図 2 の B - B' に沿った断面図で、(2) は従来例の断面図である。

【図 12】本発明の第 2 実施形態の電気光学装置における画像表示領域を構成するマトリクス状の複数の画素電極に供給される画像信号の極性を示した模式図である。

10

20

30

40

50

【図13】第2実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図14】図13のA-A'に沿った断面図である。

【図15】図13のB-B'に沿った断面図である。

【図16】図13のC-C'に沿った断面図である。

【図17】第3実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。

【図18】図17のA-A'に沿った断面図である。

【図19】第4実施形態の電気光学装置におけるデータ線、走査線、画素電極等が形成されたTFTアレイ基板の相隣接する複数の画素群の平面図である。 10

【図20】図19のA-A'に沿った断面図である。

【図21】各実施形態の液晶装置におけるTFTアレイ基板をその上に形成された各構成要素と共に対向基板の側から見た平面図である。

【図22】図21のH-H'に沿った断面図である。

【符号の説明】

|                    |    |

|--------------------|----|

| 1 a ... 半導体層       |    |

| 1 a' ... チャネル領域    |    |

| 1 b ... 低濃度ソース領域   |    |

| 1 c ... 低濃度ドレイン領域  |    |

| 1 d ... 高濃度ソース領域   | 20 |

| 1 e ... 高濃度ドレイン領域  |    |

| 1 f ... 第1容量電極     |    |

| 2 ... ゲート絶縁膜       |    |

| 3 a ... 走査線        |    |

| 3 b ... 第2容量電極     |    |

| 4 ... 第3層間絶縁膜      |    |

| 5 ... コンタクトホール     |    |

| 6 a ... データ線       |    |

| 7 ... 第4層間絶縁膜      |    |

| 8 a ... コンタクトホール   | 30 |

| 8 b ... コンタクトホール   |    |

| 9 a ... 画素電極       |    |

| 10 ... TFTアレイ基板    |    |

| 11 a ... 下地遮光膜     |    |

| 12 ... 下地絶縁膜       |    |

| 16 ... 配向膜         |    |

| 20 ... 対向基板        |    |

| 21 ... 対向電極        |    |

| 22 ... 配向膜         |    |

| 30 ... TFT         | 40 |

| 50 ... 液晶層         |    |

| 70 ... 蓄積容量        |    |

| 80 a、80 a' ... 中継膜 |    |

| 81 ... 第1層間絶縁膜     |    |

| 90 a ... 遮光性の導電膜   |    |

| 91 ... 第2層間絶縁膜     |    |

| 95 ... コンタクトホール    |    |

| 101 ... データ線駆動回路   |    |

| 104 ... 走査線駆動回路    |    |

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【 図 1 3 】

【図14】

【 図 1 5 】

【 図 1 6 】

【 四 1 7 】

【 図 1 8 】

〔 四 19 〕

【図20】

【図22】

【図21】

---

フロントページの続き

(56)参考文献 特開平11-326945(JP,A)

特開平09-043639(JP,A)

特開平10-206889(JP,A)

特開2001-066587(JP,A)

特開2001-209067(JP,A)

特開平07-064111(JP,A)

特開平09-015650(JP,A)

特開平09-127497(JP,A)

特開平05-257164(JP,A)

特開平02-165125(JP,A)

特開平04-348324(JP,A)

特開平11-084422(JP,A)

特開昭58-159520(JP,A)

特開2000-012121(JP,A)

特開2000-010120(JP,A)

国際公開第98/016868(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1362 - 1/1368

G02F 1/1343

G02F 1/1335

G02F 1/1333

G02F 1/13 505

G09F 9/30