(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5164362号

(P5164362)

(45) 発行日 平成25年3月21日(2013.3.21)

(24) 登録日 平成24年12月28日(2012.12.28)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 23/12

Z

H05K 3/32 (2006.01)

H01L 23/12

F

H05K 1/18 (2006.01)

H05K 3/32

Z

H05K 1/18

R

請求項の数 5 (全 12 頁)

|              |                               |           |                                            |

|--------------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2006-291272 (P2006-291272)  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成18年10月26日 (2006.10.26)      | (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (65) 公開番号    | 特開2007-150275 (P2007-150275A) | (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (43) 公開日     | 平成19年6月14日 (2007.6.14)        | (72) 発明者  | 近藤 浩史<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| 審査請求日        | 平成21年10月26日 (2009.10.26)      |           |                                            |

| (31) 優先権主張番号 | 特願2005-318962 (P2005-318962)  |           |                                            |

| (32) 優先日     | 平成17年11月2日 (2005.11.2)        |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

審査官 宮本 靖史

最終頁に続く

(54) 【発明の名称】半導体内臓基板およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁樹脂からなるプリント配線板に半導体素子が埋め込まれた半導体内臓基板の製造方法において、前記半導体素子の表面に設けられた電極部に接続用のバンプを形成する工程と、該半導体素子を前記プリント配線板に形成された開口部に配置する工程と、該半導体素子と該プリント配線板の上に導電膜を形成するとともに、該半導体素子と該プリント配線板とを一体化する工程と、前記導電膜をパターニングすることで配線パターンを形成し、それとともに前記接続用のバンプの表面を露出させる工程と、前記露出した接続用のバンプと前記配線パターンとを接続用配線パターンにより接続する工程と、を有することを特徴とする半導体内臓基板の製造方法。

10

## 【請求項 2】

前記接続用配線パターンは、前記半導体素子と前記プリント配線板の上に接続用配線層を形成し、該接続用配線層の上にレジスト材からなる膜を形成し、該レジスト材を、ビームもしくはレーザーにより露光することで接続用配線パターンをパターニングし、接続用配線層をエッチングすることにより形成されることを特徴とする請求項1に記載の半導体内臓基板の製造方法。

## 【請求項 3】

前記接続用配線パターンは、前記半導体素子と前記プリント配線板の上に接続用配線層を形成し、該接続用配線層の上にレジスト材からなる膜を形成し、該レジスト材を、ビームもしくはレーザーにより露光することで接続用配線パターンをパターニングし、接続用

20

配線層をめっきにより形成されることを特徴とする請求項1に記載の半導体内臓基板の製造方法。

【請求項4】

前記接続用配線パターンは、前記絶縁樹脂層および半導体素子上に接続用配線層を形成し、接続用配線層の上にレジスト材を直接描画し、さらにエッチングすることにより形成されることを特徴とする請求項1に記載の半導体内臓基板の製造方法。

【請求項5】

前記接続用配線パターンは、前記絶縁樹脂層および半導体素子上に直接描画により形成されることを特徴とする請求項1に記載の半導体内臓基板の製造方法

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、絶縁樹脂からなるプリント配線板に半導体素子が埋設されている半導体内臓基板およびその製造方法に関するものである。

【背景技術】

【0002】

近年、半導体素子を搭載した半導体パッケージは、小型化・軽量化の一途をたどっている。そのために、半導体パッケージの電極部をエリアアレイ型にした、BGA（ボール・グリッド・アレイ）やCSP（チップ・スケール・パッケージ）といった構造が採用されるようになってきている。

20

【0003】

さらに、BGAやCSPのような2次元的な小型化だけでなく、特開平11-3970（特許文献1）に示されたように、1つのパッケージ内に複数の半導体素子を積層したマルチチップパッケージも提案されている。

【0004】

一方、このような半導体パッケージの小型化だけでなく、特開平9-321408（特許文献2）に示されたように、プリント配線板の内部に半導体素子を内蔵した半導体内臓基板が提案されている。特開平9-321408における半導体内臓基板は、あらかじめ凹部の形成されたプリント配線板に、スタッドバンプの形成された半導体素子を搭載し、その後にこの半導体素子を覆うように絶縁層を形成している。

30

【0005】

しかしながら、特開平9-321408に記載の半導体内臓基板では、プリント配線板の凹部を加工するためにルーター加工が必要となり、加工時間が大幅に増加する。また、半導体素子を埋め込むためには、凹部の底に半導体素子を保持できるようにするための保持面を形成しなければならず、この保持面には絶縁層が必要になる。その結果、半導体素子を挟んだ半導体内臓基板の厚みがきわめて厚くなり小型化が困難となる。

【0006】

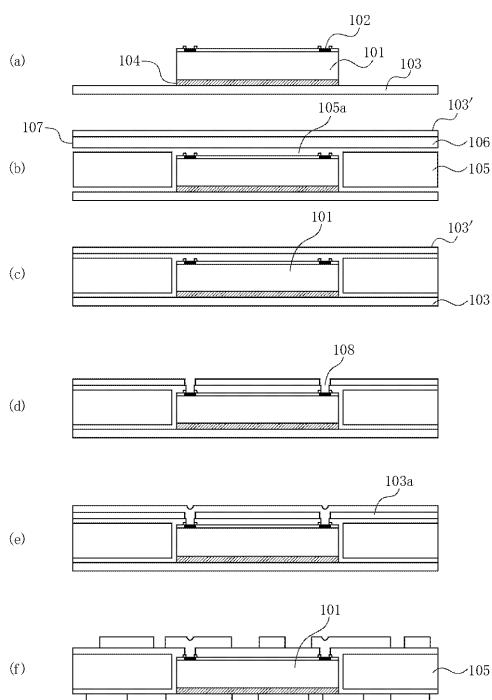

そこで、特開2004-335641（特許文献3）には、あらかじめプリント配線板に凹部を形成するのではなく、プリント配線板の製造時に半導体素子を埋め込むことで半導体内臓基板を製造する方式が記載されている。その時の製造方法を図12を参照して説明する。

40

【0007】

まず、図12(a)に示すように、Cu箔103の上に絶縁性エポキシ樹脂104を介して半導体素子101を搭載する。次に、図12(b)に示すように、プリプレグ材105を、その開口部105aが半導体素子101を収容する位置に配置する。プリプレグ材105は半導体素子101の厚みとほぼ同じ厚みを持ち、半導体素子101に対応する形状の開口部105aが打ち抜きプレスによって形成されている。また、プリプレグ材105の上には、Cu箔103'上に絶縁性樹脂であるエポキシ樹脂106がコーティングされたRCC（レジンコーテッドカッパー）材を載置する。このように積み重ねて配置し、Cu箔103、プリプレグ材105、エポキシ樹脂106、RCC材を、図12(c)に

50

示すように真空雰囲気にて熱圧着をおこなう。

#### 【0008】

次に、図12(d)に示すように、半導体素子101上の電極部に対応する位置のCu箔103'を、通常のエッティングで除去し穴部を形成す。その後、この穴部により露出するエポキシ樹脂106を、CO2あるいは、YAG、エキシマといったレーザーにより除去し開口部108を形成し、半導体素子101の電極部2を露出させる。次に、図12(e)に示すようにメッキ工程にて全面にCu層103aを形成するとともに、開口部108をCu層103aで埋め込む。

#### 【0009】

次に、Cu層103a上にレジスト材を塗り、マスクを介した露光工程及び現像工程により、配線パターンを形成し、図12(f)のような半導体素子101が内蔵された半導体内臓基板を得る。

10

【特許文献1】特開平11-3970号公報

【特許文献2】特開平9-321408号公報

【特許文献3】特開2004-335641号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

前述の特開2004-335641に記載されている半導体内臓基板では、レーザーにより開口部を正確に形成することにより、半導体素子の電極を外部に露出させている。また、プリント配線板上に形成されたCu層を、マスクを使ってエッティングすることにより、電極と接続された配線パターンを形成している。従って、半導体素子の電極とプリント配線板上の配線パターンが必ず接続される程度のパターニングおよびエッティング精度が必要であった。

20

#### 【0011】

一方、半導体素子は一枚の半導体ウエハから多数個取りで製造されるため、各半導体素子間には個体差があり、電極の位置に関しても各半導体素子間で位置誤差を有している。また、半導体素子のプリント配線板への取り付け位置は、必ず所定の範囲内の取り付け誤差が生ずる。そのため、配線パターンのパターニング位置と、半導体素子の電極の位置には、設計位置に対して位置ずれが発生する。

30

#### 【0012】

さらに、有機樹脂材料を用いたプリント配線板においては、有機樹脂材料のプロセス中の伸縮が大きく、かつその伸縮は場所により異なることから、この伸縮の補正が必要となる。通常この位置ずれを考慮して、マスクによるパターニング形状は、所定の大きさのマージンを持った形状となっている。

#### 【0013】

しかしながら半導体素子の電極が狭ピッチになると、隣接する配線パターンとの干渉を避けるため、前述のマージンを十分に取ることができなくなる。すなわち、前述の半導体素子のプリント配線板への取り付け誤差や、各半導体素子間の電極の位置誤差を、パターニング形状のマージンにより許容することが困難となる。それにより、半導体素子の電極とプリント配線板上の配線とが接続されなくなる。このような状況は、半導体素子の電極がピッチが狭くなれば狭くなるほど顕著となり、今後さらに問題となってくると思われる。

40

#### 【0014】

そこで本発明は、上記課題に鑑みてなされたものであり、半導体素子の電極部の狭ピッチ化に対応して、配線パターンとの電気接続の安定性を向上させることのできる半導体内臓基板およびその製造方法を提供することを目的とするものである。

#### 【課題を解決するための手段】

#### 【0016】

また本発明は、絶縁樹脂からなるプリント配線板に半導体素子が内蔵された半導体内臓

50

基板の製造方法において、前記半導体素子の表面に設けられた電極部に接続用バンプを形成する工程と、該半導体素子を前記プリント配線板に形成された開口部に配置する工程と、該半導体素子と該プリント配線板の上に導電膜を形成した状態で該半導体素子と該プリント配線板とを一体化する工程と、前記導電膜をパターニングすることにより配線パターンを形成するとともに、該半導体素子上の導電膜を除去し前記接続用バンプの表面を露出させる工程と、前記露出した接続用バンプと前記配線パターンとを接続する接続用配線パターンを形成する工程と、を有することを特徴とする半導体内臓基板の製造方法を提供する。

#### 【発明の効果】

#### 【0017】

10

本発明によれば、半導体内臓基板において、半導体素子の電極とプリント配線板上の配線パターンとを、接続用配線パターンにより接続している。またこの接続用配線パターンは、半導体素子をプリント配線板に埋め込んだ後の別工程で形成している。これにより、半導体素子の電極及びプリント配線板上のパターン配線の位置に対応して接続用配線パターンを形成することが可能となる。また、半導体素子の電極部が狭ピッチ化しても、配線パターンとの電気接続を確実に行なう事が可能となる。

#### 【発明を実施するための最良の形態】

#### 【0018】

本発明の実施の形態を説明する。

#### 【実施例1】

20

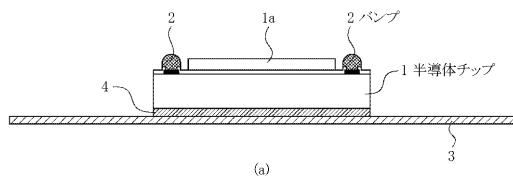

#### 【0019】

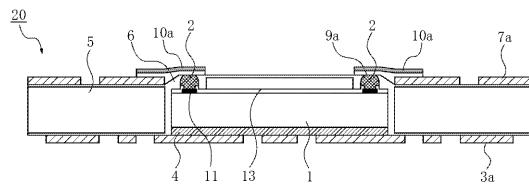

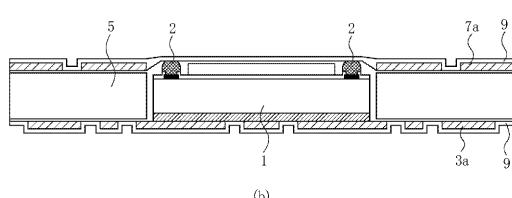

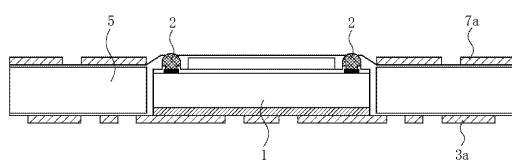

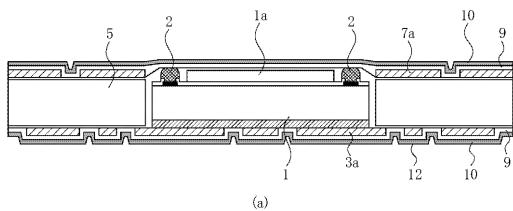

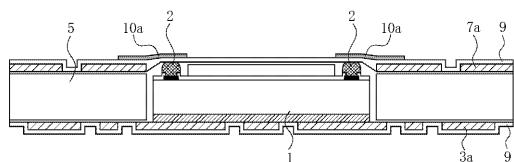

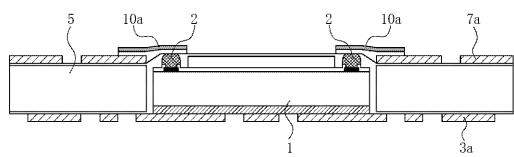

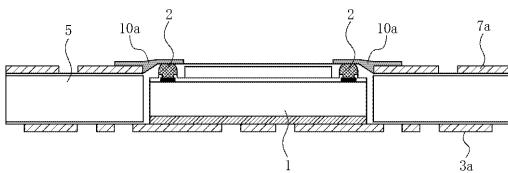

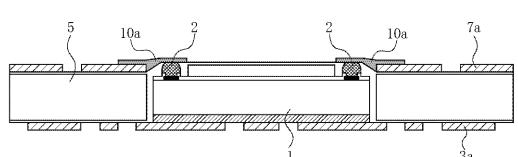

図1は本発明の実施例1における半導体内臓基板20の断面図である。図中1は半導体素子であり、2は半導体素子1上の電極部11に形成されたバンプである。半導体素子1上の電極部11以外の部分は絶縁層13により覆われている。1aは絶縁層13の上に設けられ、バンプ2とほぼ同じ高さの樹脂フィルムである。半導体素子1の下面には絶縁層4が設けられている。5はプリント配線板の本体をなす絶縁樹脂層である。3aは絶縁樹脂層5の裏面に形成された裏面配線パターンであり、7aは絶縁樹脂層5の表面に形成された表面配線パターンである。6は半導体素子1を封止する接着樹脂層である。10aは半導体素子1上のバンプ2と、絶縁樹脂層5上の表面配線パターン7aを接続する接続用配線パターンである。接続用配線パターン10aは導電性の保護層9aを介してバンプ2と表面配線パターン7aを接続している。

30

#### 【0020】

##### (製造方法1)

次に図1に示した半導体内臓基板20の製造方法1を、図2乃至4を参照して説明する。まず図2(a)に示すように、半導体素子1の上面に電極部11にバンプ2を形成する。バンプ2は金やCu等の金属やはんだが使用される。形状は直径20~30μmのボールや円柱が使用される。半導体素子1の表面は絶縁層13により覆われており、電極部11のみが上面に露出している。絶縁層13としてはエポキシ系樹脂等が使用可能である。さらに半導体素子1の上面に形成された絶縁層13の上面のアクティブエリアには、バンプ2とほぼ同じ高さの樹脂フィルム12を形成する。樹脂フィルム1aとしてはポリイミドフィルム等を使用することができる。

40

#### 【0021】

次に表面にバンプ2及び樹脂フィルム1aが形成された半導体素子1と裏面配線層3とを、絶縁層4を介して接着する。絶縁層4は厚み10~50μmのエポキシ樹脂等を使用する。厚みは裏面配線層3としては厚み10~35μmのCuやアルミニウム等の薄膜が使用可能である。半導体素子1は熱硬化により絶縁層4を介して裏面配線層3に接着される。

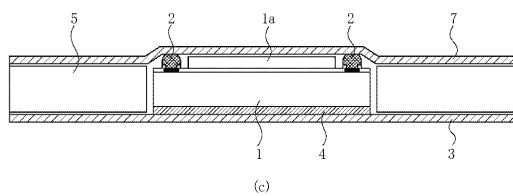

#### 【0022】

次に、図2の(b)に示すように、半導体素子1の厚み(50~150μm)とほぼ同じ厚みをもち、半導体素子1に対応する形状の開口部5aを有する絶縁樹脂層5を、その

50

開口部 5 a が半導体素子 1 を収容する位置に配置する。絶縁樹脂層 5 としてはガラスクロス入りのプリプレグ材を使用することができる。半導体素子 1 を絶縁樹脂層 5 の開口部 5 a に配置する。

#### 【 0 0 2 3 】

また絶縁樹脂層 5 および半導体素子 1 の上に、表面配線層 7 にエポキシ等の接着樹脂層 6 をライニングした RCC 材 8 を配置する。表面配線層 7 としては裏面配線層 3 と同様に、厚み 10 ~ 35 μm の Cu やアルミニウム等の薄膜が使用可能である。接着樹脂層 6 としては厚さ 20 ~ 60 μm のエポキシ樹脂等が使用可能である。

#### 【 0 0 2 4 】

次に、図 2 の (c) に示すように、裏面配線層 3 、絶縁樹脂層 5 、 RCC 材 8 を、真空 10 雰囲気にて 150 ~ 200 °C の温度で同時に熱プレスする。これにより裏面配線層 3 、絶縁樹脂層 5 、 RCC 材 8 は一体化し一つの基板となる。接着樹脂層 6 は加熱することで流動性が高くなるため、開口部 5 a の半導体素子 1 と絶縁樹脂層 5 との間に入り込み、半導体素子 1 を確実の固定する。また、バンプ 2 の上部の絶縁樹脂層 5 はバンプにより押し流されるため、バンプ 2 と表面配線層 7 は接触した状態になる。

#### 【 0 0 2 5 】

このとき、ガラスクロス入りのプリプレグ材 5 を使用するのは、熱プレス時の圧力により半導体素子 1 が存在する場所と存在しない場所での圧力差によりプレス後の表面の平坦性が損なわれるのを防ぐためである。そのことからも、ガラスクロスの厚みは半導体素子 1 の厚みとバンプ 2 の高さの合計と等しいか若干厚い方が好ましい。 20

#### 【 0 0 2 6 】

尚、前述の樹脂フィルム 12 は、半導体素子 1 上に設けられたバンプ 2 により、半導体素子 1 上の表面配線層 7 に凹凸がつくことを防止している。また、バンプ 2 が樹脂フィルム 12 の厚みまで変形すると、樹脂フィルム 12 も加圧力を受け持つため、バンプ 2 に集中してプレス圧力がかかることによる半導体素子 1 へのダメージを防ぐことができる。

#### 【 0 0 2 7 】

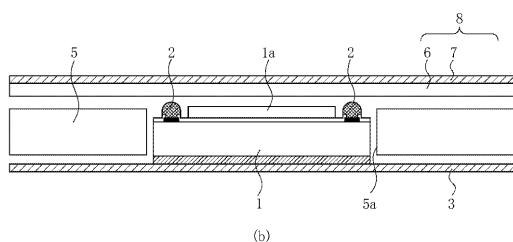

次に、図 3 (a) に示すように、一体化した基板の表面配線層 3 と裏面配線層 7 を、パターンングし、裏表面パターン配線 3 a 、表面パターン 7 a 形成する。これによりバンプ 2 の上部は、露出することとなる。

#### 【 0 0 2 8 】

次に図 3 (b) に示すように、基板の表裏面に無電解メッキにより厚さ 1 ~ 3 μm の保護層 9 を形成する。保護層 9 としては Ni 等の金属が使用可能である。保護層 9 は、先にパターン形成した配線パターン 7 a を保護するためと、次の工程で形成する導電膜を電気メッキで形成するための共通電極としての働きと、半導体素子 1 のバンプ 2 と後述する接続用配線パターン 10 a との間の拡散を防止する役割を果たしている。 30

#### 【 0 0 2 9 】

次に、図 4 (a) に示すように、保護層 9 上に電気メッキにより厚さ 1 ~ 3 μm の接続用配線層 10 を形成する。接続用配線層 10 としては Cu 等の金属が使用可能である。

#### 【 0 0 3 0 】

次にバンプ 2 と表面配線パターン 7 a の位置を確認し、それらの位置に合わせて、図 4 (b) に示すように、レジスト R 1 を形成する。具体的には、半導体素子 1 のバンプ 2 が露出していた面側にネガ型のレジスト層を設け、1 つ 1 つの半導体素子について、それぞれのバンプ 2 の位置検出を行う。その後に、バンプ 2 の露出する領域から接続すべき配線パターン 7 a の電極部までの間をビーム光で直接露光する。ビーム光としてはレジスト材が感光する波長帯を有しているものであれば、いずれの方式でもかまわないが、通常は UV 光が使われる。また直接露光する方法としては、ビームヘッド側に X - Y 駆動部を設けてもよいし、基板を保持するステージ側に X - Y 駆動部を設け、あらかじめプログラミングされたように駆動させればよい。 40

#### 【 0 0 3 1 】

尚、レジストパターン R 1 は、前述の一貫全面にレジスト膜を形成した後、レーザによ 50

り直描して形成する以外に、レジスト自体を直接描画することも可能である。レジスト自体を直接描画すれば製造工程を減らすことが可能となる。

#### 【0032】

次に、それぞれの半導体素子1について露光した後、現像を行うと半導体素子1のバンプ2から配線パターン7aの電極部までの部分のみにレジストパターンR1が形成される。この状態で接続用配線パターン層10を過硫酸系の溶液にてエッチングし、レジストパターンR1で覆われた部分以外の保護層(Ni層)9上の接続用配線パターン層(Cu層)10を除去する。これにより接続用配線パターン層10はパターニングされ、接続用配線パターン10aとなる。この時、エッチング液は、保護層(Ni層)9をエッチングしないように、エッチング条件を調整する。

10

#### 【0033】

次に、レジストパターンR1を残した状態で、保護層(Ni層)9をエッチングする。このとき、エッチング液としては、塩化第2鉄系の溶液を使用する。塩化第2鉄系の溶液は、接続用配線パターン10aもエッチングするが、保護層9にくらべ接続用配線パターン10aははるかに厚いので断線することはない。特に極細の接続用配線パターン10aに関しては、Ni上にCuおよびレジストが存在していることから、安定したパターン形成を行うことができる。

#### 【0034】

その後、レジストパターンR1を剥離することで、図4(c)に示すように、半導体内蔵基板20を得ることができる。

20

#### 【0035】

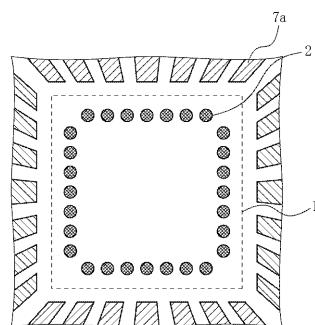

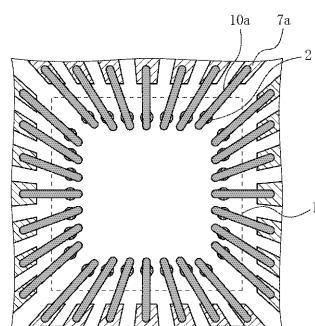

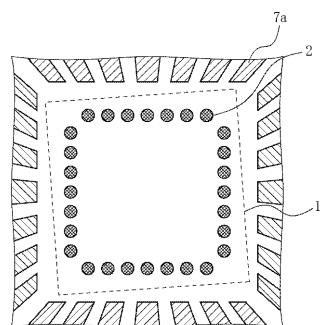

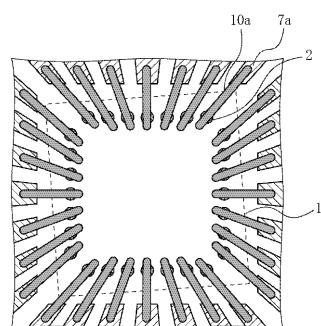

図5、図6は、バンプ2と配線パターン7aを接続する接続用配線パターン10aを示した、半導体内蔵基板20の平面図である。図5(a)、図6(a)は接続用配線パターン10aが形成される前の図であり、図5(b)、図6(b)は接続用配線パターン10aを形成した後の図である。図5に対して図6は半導体素子1が斜めに配置されている。本実施例では、前述の図4(b)に示すレジストR1の形成工程で、半導体素子1のバンプ2と配線パターン7aの接続部までの位置を、自動的に補正してレジストにビームを描画する。従って、半導体素子1のバンプ3と、表面配線パターン7aの位置が、多少ずれていたとしても、常に安定した接続を行うことができる。

30

#### 【0036】

本発明によれば、配線パターン7aを形成するプロセスと、接続用配線パターン10aを形成するプロセスと分離している。これにより、接続用配線パターン10aを形成する際のレジストを、1つ1つの半導体素子の電極の位置にあわせて行うことが可能となる。そのため、半導体素子の位置がずれていたとしても、描画プログラムの補正により対応することができるため、配線幅/スペース = 10 μm / 10 μm ~ 20 μm / 20 μmといった極めて微細な接続用配線パターン10aを容易に形成することができる。

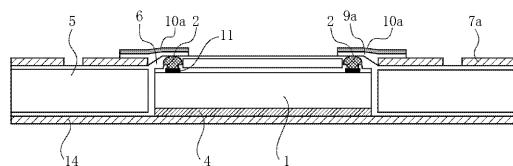

#### 【0037】

また、本実施例においては、プリント配線板の両面を配線層として使用する2層プリント配線板に関して説明した。しかしながら本発明はこれに限られるものではなく、図7に示すように、配線層が1層の片面プリント配線板にも使用可能である。この時、絶縁樹脂層に形成された開口部は、上下方向で貫通したものではなく、凹部形状のものとし、その凹部に半導体素子を配置することができる。

40

#### 【0038】

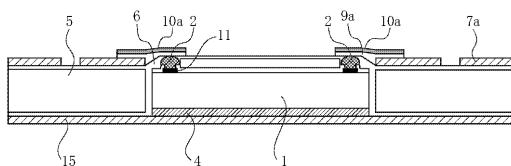

さらに、放熱性が要求される場合においては、図8に示すような半導体素子をCu合金等の放熱性の高い金属プレート15に配置して一体化した後、半導体素子の裏面側は配線パターンを設けず放熱板として使用してもかまわない。

#### 【0039】

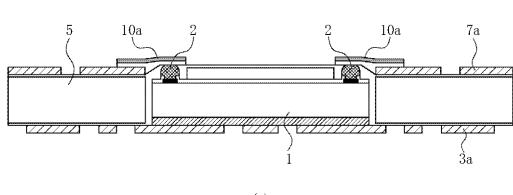

##### (製造方法2)

次に図1に示した半導体内蔵基板20の製造方法2を、図9を参照して説明する。製造方法2においては、製造方法1で使用したネガ型のレジストR1に代えて、ポジ型レジス

50

ト R 2 を使用している。製造方法 2 において製造方法 1 における図 2、図 3 で示した工程は同じであり、図 4 で示した工程に代えて図 9 で示す工程をおこなう。

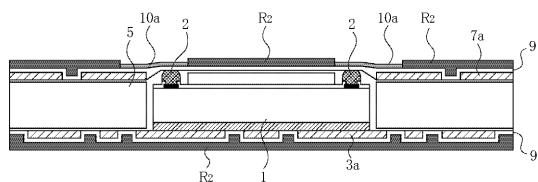

#### 【 0 0 4 0 】

図 9 ( a ) に示すように、接続用配線パターン 1 0 a を形成する部分の保護層 ( N i 層 ) 9 のみが露出するように、ポジ型レジスト R 2 を形成する。その後、保護層 9 を共通電極層として電気メッキを行い、接続用配線パターン ( C u 層 ) 1 0 a を形成する。接続用配線パターン ( C u 層 ) 1 0 a の厚さは、5 ~ 1 5  $\mu\text{m}$  が好ましい。

#### 【 0 0 4 1 】

次に図 9 ( b ) に示すようにレジストパターン R 2 を剥離し、図 9 ( c ) に示すように保護層 9 のエッチングを行う。その際、接続用配線パターン 1 0 a もエッチングされるが、保護層 9 よりも膜厚であるため、エッチングが終了した時の膜厚は、3 ~ 1 0  $\mu\text{m}$  程度となる。尚、レジストパターン R 2 は、前述のレジストパターン R 1 と同様に、レジスト自体を直接描画することも可能である。レジスト自体を直描すれば製造工程を減らすことが可能となる。

#### 【 実施例 2 】

#### 【 0 0 4 2 】

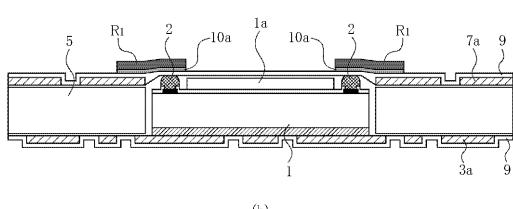

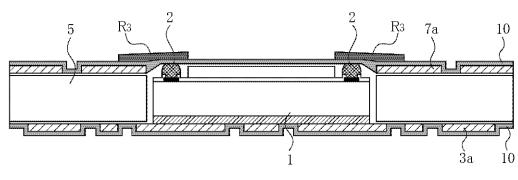

図 1 0 は本発明の実施例 2 における半導体内臓基板 3 0 の断面図である。本実施例では、図 1 に示した実施例 1 の半導体内臓基板 2 0 と比べて、保護層 9 のない構成となっている。本実施例においては、半導体素子 1 のバンプ 2 の組成が N i である。この場合は、拡散バリア層として機能する保護層 9 を、バンプ 2 と配線パターン 7 a との間に設ける必要がない。尚、図 1 0 において図 1 と同じ部材には同じ符号を付している。

#### 【 0 0 4 3 】

次に図 1 0 に示した半導体内臓基板 3 0 の製造方法を、図 1 1 を参照して説明する。本実施例における製造方法は、実施例 1 の製造方法 1 における図 2、図 3 で示した工程は同じであり、図 4 で示した工程に代えて図 1 1 で示す工程をおこなう。

#### 【 0 0 4 4 】

図 1 1 ( a ) に示すように、配線パターン 3 a、7 a を形成した後、全面に無電解メッキにより接続用配線パターン層 ( C u 層 ) 1 0 を 3 ~ 1 0  $\mu\text{m}$  の厚みで形成する。そして、ネガ型のレジストパターン R 3 を用いて接続用配線パターン層 1 0 をエッチングし、図 1 1 ( b ) に示すように極細パターンである接続用配線パターン 1 0 a を形成する。

#### 【 0 0 4 5 】

なお、本実施例においては、バンプ 2 が N i であり接続用配線パターン 1 0 a が C u であったが、バンプ 2 が C u であり接続用配線パターン 1 0 a が N i であってもかまわない。また、バンプ 2 が N i で接続用配線パターン 1 0 a が N i 、あるいはバンプ 2 が C u で接続用配線パターン 1 0 a が C u であってもかまわない。

#### 【 0 0 4 6 】

尚、レジストパターン R 3 は、前述のレジストパターン R 1 と同様に、レジスト自体を直描することも可能である。レジスト自体を直接描画すれば製造工程を減らすことが可能となる。

#### 【 0 0 4 7 】

またレジストに代えて、接続用配線パターン 1 0 a を直接描画すること効能である。これによりレジスト描画後の露光・現像のプロセスを省略することができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 4 8 】

【 図 1 】実施例 1 による半導体内臓基板の断面図。

【 図 2 】実施例 1 による半導体基板の製造方法 1 を示す工程図。

【 図 3 】実施例 1 による半導体基板の製造方法 1 を示す工程図。

【 図 4 】実施例 1 による半導体基板の製造方法 1 を示す工程図。

【 図 5 】実施例 1 による半導体素子のバンプと接続用配線パターンの配置を説明する平面図。

10

20

30

40

50

【図6】実施例1による半導体素子のバンプと接続用配線パターンの配置を説明する平面図。

【図7】実施例1による半導体内臓基板の断面図。

【図8】実施例1による半導体内臓基板の断面図。

【図9】実施例1による半導体基板の製造方法2を示す工程図。

【図10】実施例2による半導体内臓基板の断面図。

【図11】実施例2による半導体基板の製造方法を示す工程図。

【図12】従来例による半導体基板の製造工程を示す工程図。

【符号の説明】

【0049】

1 半導体素子

2 バンプ

3 裏面配線層

3 a 裏面配線パターン

4 絶縁樹脂層

5 絶縁樹脂層

5 a 開口部

6 接着樹脂層

7 表面配線層

7 a 表面配線パターン

8 R C C 材

9 保護層

10 接続用配線パターン層

10 a 接続用配線パターン

11 電極

12 樹脂フィルム

13 絶縁層

14 絶縁樹脂フィルム

15 金属プレート

20、30 半導体内臓基板

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

(a)

(b)

【図6】

(a)

(b)

【図7】

【図8】

【図9】

(a)

(b)

(c)

【図10】

【図11】

(a)

(b)

【図12】

---

フロントページの続き

(56)参考文献 特開2001-291797(JP,A)

特開平04-350951(JP,A)

特開2004-152982(JP,A)

特開平07-153867(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |           |   |           |

|--------|-----------|---|-----------|

| H 01 L | 2 3 / 1 2 | - | 2 3 / 1 5 |

| H 05 K | 1 / 1 8   |   |           |

| H 05 K | 3 / 3 2   | - | 3 / 3 4   |

| H 05 K | 3 / 4 6   |   |           |

| H 01 L | 2 1 / 6 0 |   |           |