(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5724086号

(P5724086)

(45) 発行日 平成27年5月27日(2015.5.27)

(24) 登録日 平成27年4月10日(2015.4.10)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 3 4

請求項の数 7 (全 96 頁)

(21) 出願番号 特願2012-104381 (P2012-104381)

(22) 出願日 平成24年5月1日 (2012.5.1)

(62) 分割の表示 特願2011-162587 (P2011-162587)

分割

原出願日 平成23年7月25日 (2011.7.25)

(65) 公開番号 特開2013-22448 (P2013-22448A)

(43) 公開日 平成25年2月4日 (2013.2.4)

審査請求日 平成24年5月10日 (2012.5.10)

(73) 特許権者 597044139

株式会社大都技研

東京都台東区東上野一丁目1番14号

(74) 代理人 100107102

弁理士 吉延 彰広

(74) 代理人 100164242

弁理士 倉澤 直人

(72) 発明者 岡田 康弘

東京都台東区東上野一丁目1番14号 株

式会社大都技研内

審査官 森田 真彦

最終頁に続く

(54) 【発明の名称】遊技台

## (57) 【特許請求の範囲】

## 【請求項 1】

マイクロプロセッサを少なくとも備えた遊技台であって、

前記遊技台は、ぱちんこ機またはスロットマシンであり、

前記マイクロプロセッサは、CPUが少なくとも搭載されたプロセッサであり、

前記マイクロプロセッサは、ROMが少なくとも搭載されたプロセッサであり、

前記マイクロプロセッサは、乱数回路が少なくとも搭載されたプロセッサであり、

前記ROMは、ユーザプログラムが少なくとも記憶されたものであり、

前記ユーザプログラムは、第一の処理のプログラムを含むプログラムであり、

前記ユーザプログラムは、第二の処理のプログラムを含むプログラムであり、

前記乱数回路は、設定された値の範囲で、乱数値を発生可能な回路であり、

前記第一の処理は、前記CPUがリセットされた場合に、先頭から開始される処理であり、

前記第二の処理は、割込みの発生に応じて、先頭から開始される処理であり、

前記第一の処理のプログラムは、前記値の範囲を設定するプログラムを含むプログラムであり、

前記第二の処理のプログラムは、前記乱数値を前記乱数回路のレジスタからロードする命令を含むプログラムであり、

前記CPUがリセットされた場合に、前記割込みの発生が禁止された状態にされるよう構成されており、

10

20

前記値の範囲は、前記割込みの発生が禁止された状態において設定されるものであり、

前記第一の処理のプログラムは、前記値の範囲を設定した後で、前記割込みの発生を許可する命令が実行されるように構成されたプログラムである、

ことを特徴とする遊技台。

【請求項 2】

請求項 1 に記載の遊技台であって、

前記遊技台は、前記乱数値を用いた抽選の結果に基づく利益を付与可能なものであり、

前記乱数値は、前記抽選の実行にあたって、前記第二の処理において前記 C P U のレジスタにロードされるように構成された値である、

ことを特徴とする遊技台。

10

【請求項 3】

請求項 1 または 2 に記載の遊技台であって、

前記値の範囲の下限値は、0 であり、

前記値の範囲の設定は、該値の範囲の下限値を変更するものではなく、該値の範囲の上限値を変更するものである、

ことを特徴とする遊技台。

【請求項 4】

請求項 1 乃至 請求項 3 のいずれか一項に記載の遊技台であって、

前記マイクロプロセッサは、割込み制御手段が少なくとも搭載されたプロセッサであり

、

前記割込み制御手段は、第一の割込み要求の通知があった場合に、前記割込み（以下、「第一の割込み」という。）を発生可能な制御手段であり、

前記第一の割込み要求は、設定された周期ごとに前記割込み制御手段に通知されるものである、

ことを特徴とする遊技台。

20

【請求項 5】

請求項 4 に記載の遊技台であって、

前記割込み制御手段は、第二の割込み要求の通知があった場合に、第二の割込みを発生可能な制御手段であり、

前記第二の割込みは、前記第一の割込みとは異なる割込みであり、

前記第二の割込み要求は、外部入力に応じて前記割込み制御手段に通知されるものであり、

前記ユーザプログラムは、第三の処理のプログラムを含むプログラムであり、

前記第三の処理は、前記第二の割込みの発生に応じて、先頭から開始される処理であり

、

前記第三の処理のプログラムは、外部入力に応じた命令を含むプログラムである、

ことを特徴とする遊技台。

30

【請求項 6】

請求項 1 乃至 請求項 5 のいずれか一項に記載の遊技台であって、

前記マイクロプロセッサは、セキュリティチェックを実行可能なプロセッサであり、

前記セキュリティチェックは、前記ユーザプログラムに異常がないかをチェックする機能を少なくとも有するものであり、

前記マイクロプロセッサは、前記セキュリティチェックのランダム延長を行うことが可能なプロセッサであり、

前記マイクロプロセッサは、前記セキュリティチェックのランダム延長によって、前記セキュリティチェックの時間をランダムに変化させることができ可能なプロセッサであり、

前記マイクロプロセッサは、前記セキュリティチェックにおいて異常なしであった場合に、前記第一の処理を先頭から開始可能なプロセッサである、

ことを特徴とする遊技台。

40

【請求項 7】

50

請求項 6 に記載の遊技台であって、

前記マイクロプロセッサは、システムリセットを発生させる機能を有するプロセッサで

あり、

前記マイクロプロセッサは、ユーザリセットを発生させる機能を有するプロセッサで

あり、

前記マイクロプロセッサは、システムリセット後に、前記セキュリティチェックを実行

可能なプロセッサである、

ことを特徴とする遊技台。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、弾球遊技機（パチンコ機）や回胴遊技機（スロットマシン）に代表される遊技台に関する。

**【背景技術】**

**【0002】**

従来の遊技台（例えば、スロットマシン、パチンコ機）は、図柄表示部の有効入賞ラインに沿って所定の図柄の組合せを停止表示させることで、遊技者が所定の利益を獲得できるように構成されていたり、遊技領域に設けられた所定の入賞口に遊技球を進入させることで、遊技者が所定の利益を獲得できるように構成されている。

20

**【0003】**

このような遊技台では、遊技者による不正な行為、静電気ノイズなどの外乱など様々な要因で、遊技制御が不安定になる場合があるが、このような問題点を解決するために、リセット受信からソフト起動までの時間をランダム化させる遊技台が提案されている（例えば、特許文献1参照）。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開2009-34162号公報**

30

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

しかしながら、特許文献1記載の遊技台では、電源投入時の不正行為を有効に阻止することができるものの、他のタイミングや要因については更なる改良がなされた遊技台が望まれている。

**【0006】**

本発明は、このような従来の問題点を解決するためになされたものであって、安定した遊技制御をおこなうことができる遊技台を提供することを目的とする。

**【課題を解決するための手段】**

**【0007】**

40

上記目的を解決する本発明の遊技台は、

マイクロプロセッサを少なくとも備えた遊技台であって、

前記遊技台は、ぱちんこ機またはスロットマシンであり、

前記マイクロプロセッサは、C P Uが少なくとも搭載されたプロセッサであり、

前記マイクロプロセッサは、R O Mが少なくとも搭載されたプロセッサであり、

前記マイクロプロセッサは、乱数回路が少なくとも搭載されたプロセッサであり、

前記R O Mは、ユーザプログラムが少なくとも記憶されたものであり、

前記ユーザプログラムは、第一の処理のプログラムを含むプログラムであり、

前記ユーザプログラムは、第二の処理のプログラムを含むプログラムであり、

前記乱数回路は、設定された値の範囲で、乱数値を発生可能な回路であり、

50

前記第一の処理は、前記CPUがリセットされた場合に、先頭から開始される処理であり、

前記第二の処理は、割込みの発生に応じて、先頭から開始される処理であり、

前記第一の処理のプログラムは、前記値の範囲を設定するプログラムを含むプログラムであり、

前記第二の処理のプログラムは、前記乱数値を前記乱数回路のレジスタからロードする命令を含むプログラムであり、

前記CPUがリセットされた場合に、前記割込みの発生が禁止された状態にされるよう構成されており、

前記値の範囲は、前記割込みの発生が禁止された状態において設定されるものあり、10

前記第一の処理のプログラムは、前記値の範囲を設定した後で、前記割込みの発生を許可する命令が実行されるように構成されたプログラムである、

ことを特徴とする。

#### 【発明の効果】

#### 【0009】

本発明によれば、安定した遊技制御をおこなうことができる遊技台を提供することができる。

#### 【図面の簡単な説明】

#### 【0010】

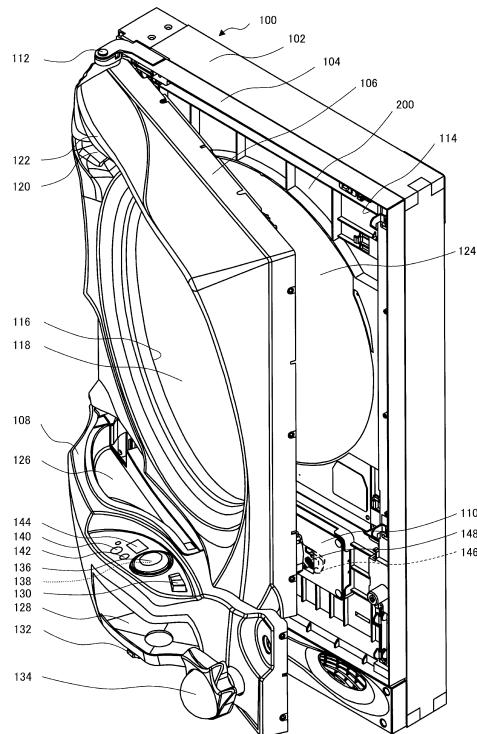

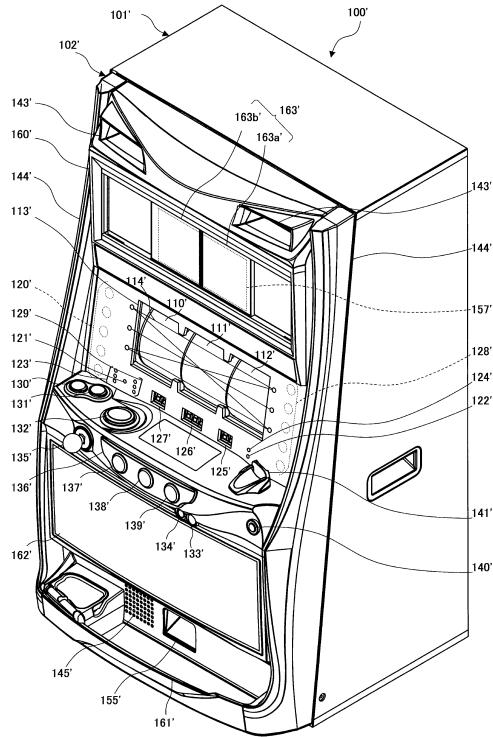

【図1】パチンコ機100を正面側(遊技者側)から見た外観斜視図である。

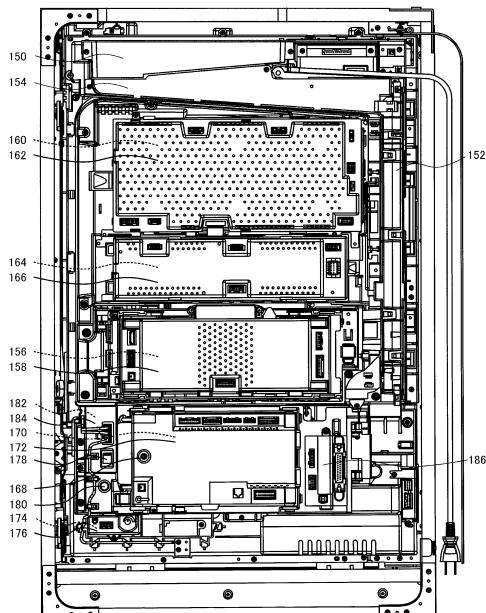

【図2】パチンコ機100を裏側から見た外観斜視図である。

【図3】遊技盤200を正面側(遊技者側)から見た略示正面図である。

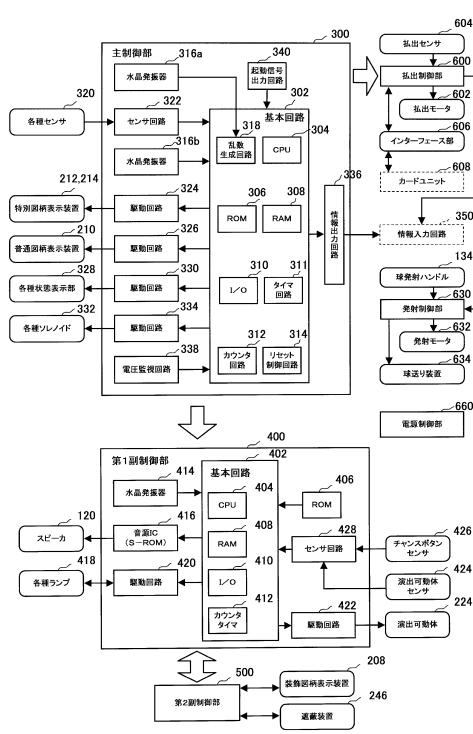

【図4】制御部の回路ブロック図を示したものである。

【図5】(a)は特図の停止回路の一例を示したものであり、(b)は装飾回路の一例を示したものであり、(c)は普図の停止表示回路の一例を示したものである。

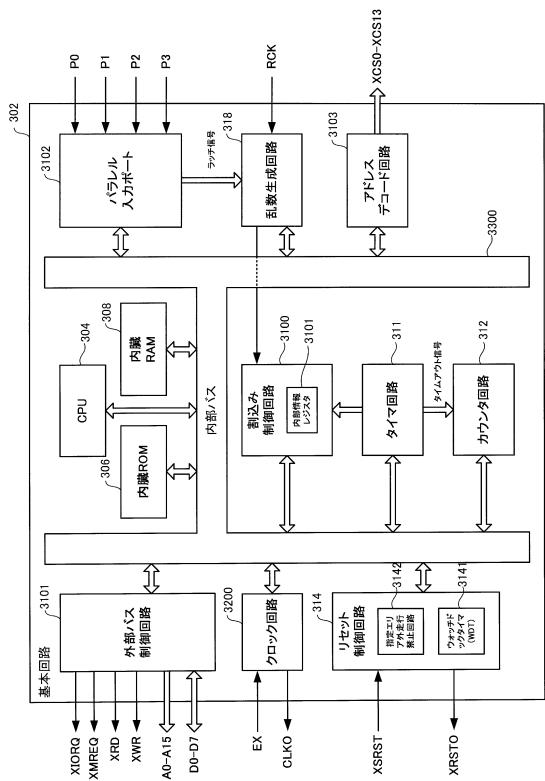

【図6】図4に示す基本回路302の構成例を示す図である。

【図7】基本回路302のメモリマップおよびI/Oマップの一例を示す図である。

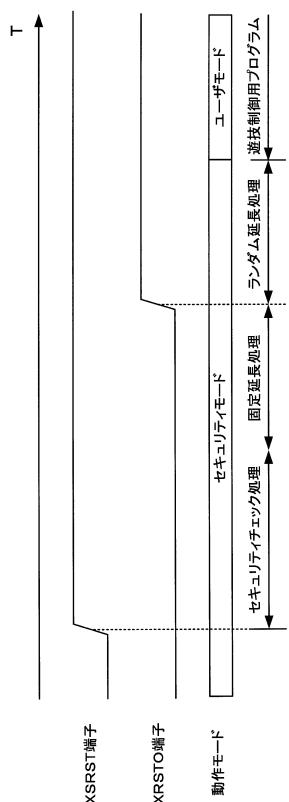

【図8】システムリセットの流れを示す図である。

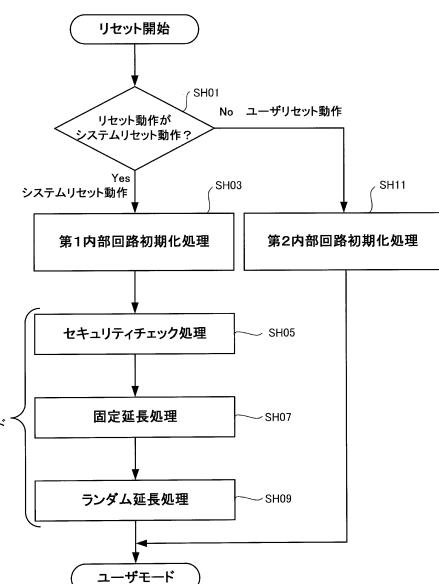

【図9】リセットの流れを示すフローチャートである。30

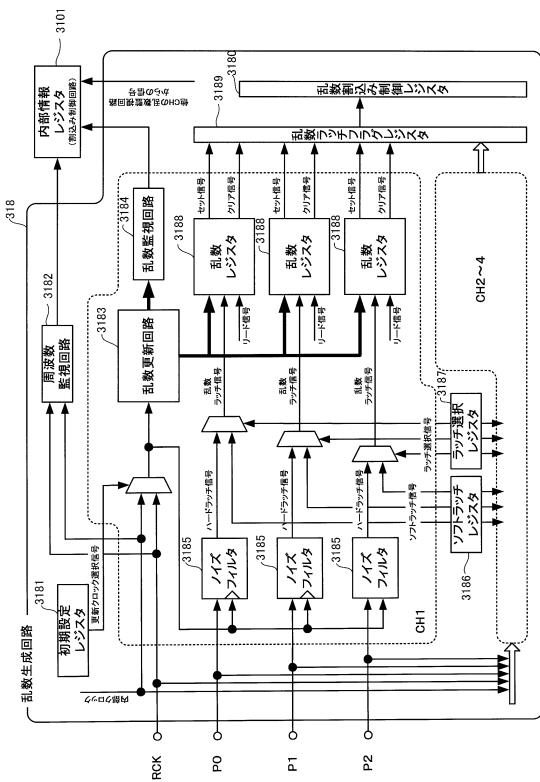

【図10】図6に示す乱数生成回路318の内部構成図である。

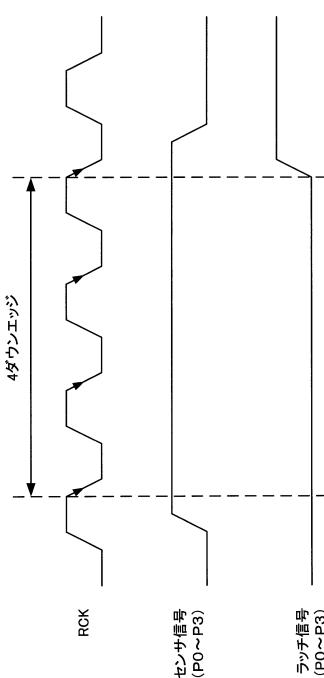

【図11】図10に示すノイズフィルタ3185による処理の一例を示す図である。

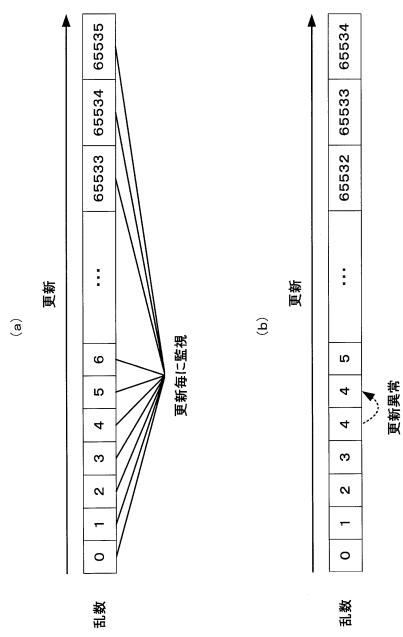

【図12】図10に示す乱数更新回路3183の詳細を示す図である。

【図13】乱数生成範囲の最大値が設定されていない場合において出力される乱数の範囲を示す図である。

【図14】図13とは異なる最大値が設定された場合に出力される乱数の範囲を示す図である。

【図15】最大値と最小値を設定した乱数生成範囲において、乱数を取得することができる範囲を示す図である。

【図16】本実施形態の遊技台で使用される乱数の導出源を表す図である。40

【図17】図6に示す割込み制御回路3100に設けられた内部情報レジスタ3101の一部を示す図である。

【図18】周波数監視回路3182における異常の検出例を示す図である。

【図19】乱数監視回路3184における異常の検出例を示す図である。

【図20】乱数が一巡する周期とタイマ割込みの周期を比較した図である。

【図21】主制御部メイン処理の流れを示すフローチャートである。

【図22】主制御部メイン処理における初期設定2の流れを示すフローチャートである。

【図23】ステップS1053における乱数生成回路初期設定処理の流れを示すフローチャートである。

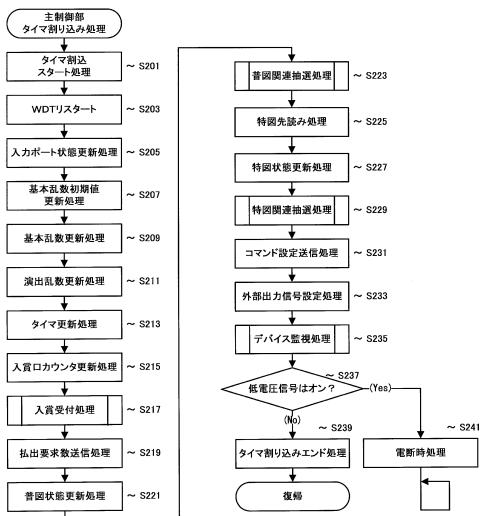

【図24】主制御部タイマ割込処理の流れを示すフローチャートである。50

【図25】(a)は、普図関連抽選処理の流れを示すフローチャートであり、(b)は、普図抽選テーブルを示す図である。

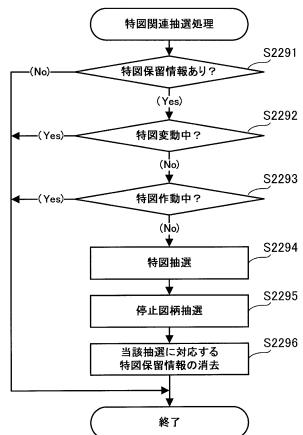

【図26】特図関連抽選処理の流れを示すフローチャートである。

【図27】(a)は、特図抽選テーブルを示す図であり、(b)は、停止図柄抽選テーブルを示す図である。

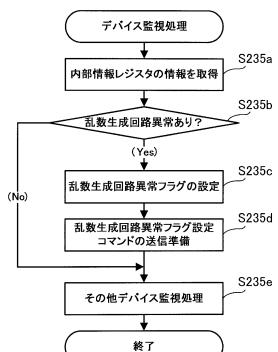

【図28】デバイス監視処理の流れを示すフローチャートである。

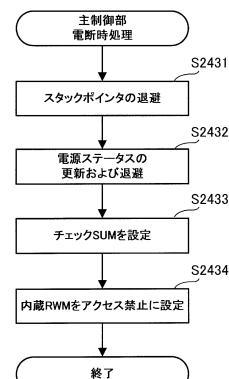

【図29】主制御部における電断時処理の流れを示すフローチャートである。

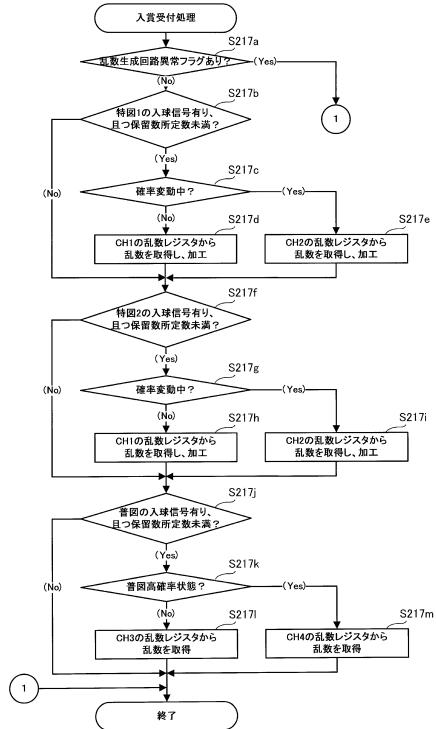

【図30】ステップS217における入賞受付処理のうち、特図当選乱数および普図当選乱数を取得する処理の流れを示した図である。

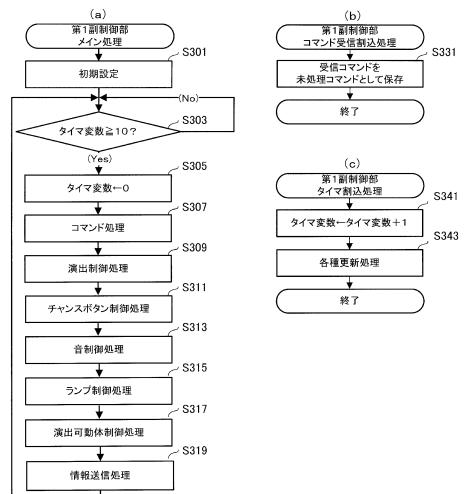

【図31】(a)は第1副制御部400のCPU404が実行するメイン処理のフローチャートであり、(b)は第1副制御部400のコマンド受信割込処理のフローチャートであり、(c)は第1副制御部400のタイマ割込処理のフローチャートである。

10

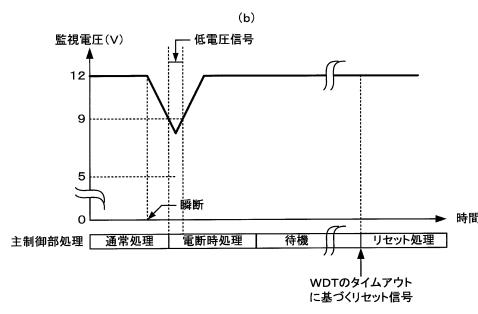

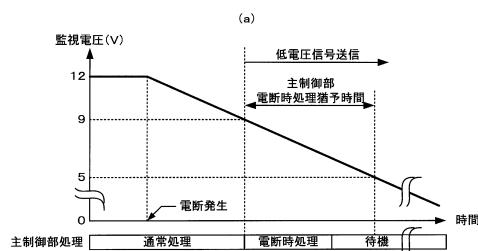

【図32】(a)は、電源オフの場合の動作を示す図であり、(b)は、瞬断の場合の動作を示す図である。

【図33】乱数生成範囲の問題点を示す図である。

【図34】図12で説明した乱数更新回路3183の変形例を示す図である。

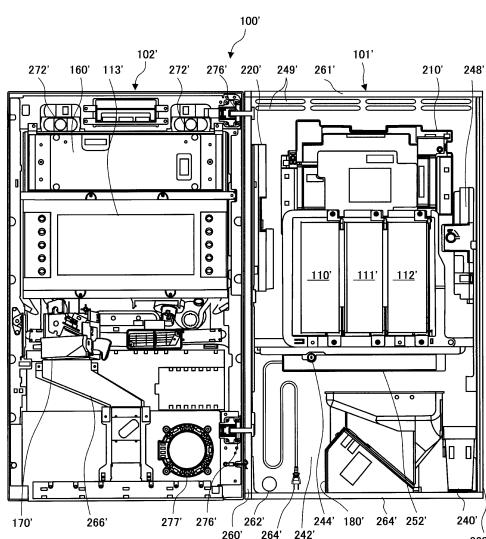

【図35】スロットマシン100'の外観を示す外観斜視図である。

【図36】前面扉を開けた状態のスロットマシンを示す正面図である。

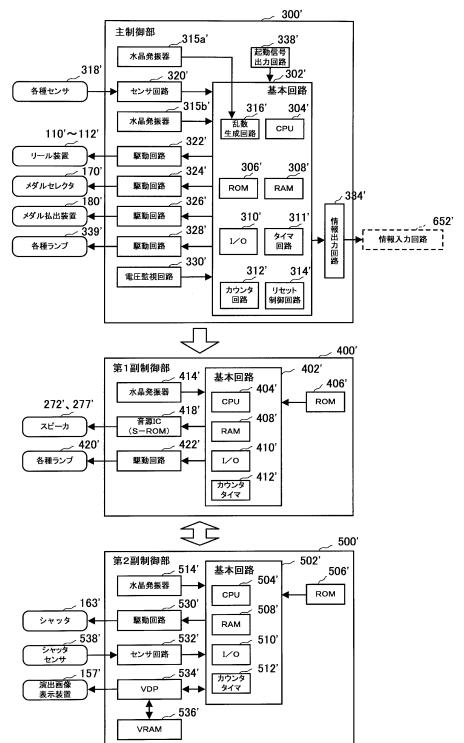

【図37】制御部の回路ブロック図である。

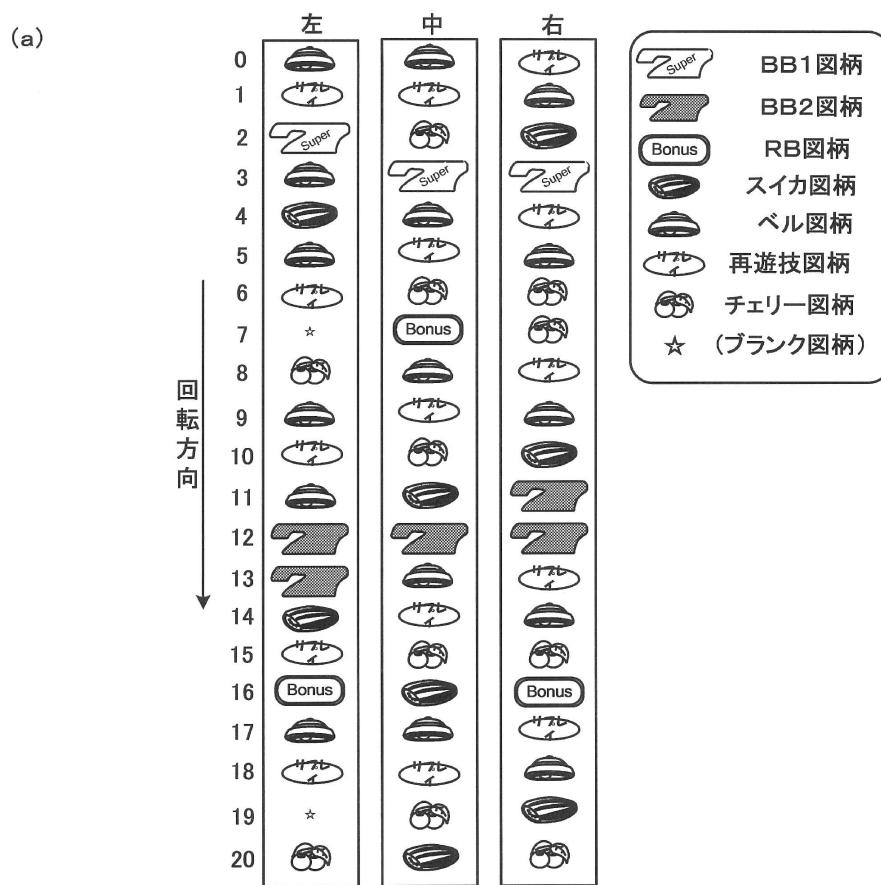

【図38】(a)は、リールに施される図柄の配列を平面的に展開して示した図であり、

(b)は、入賞役(作動役を含む)の種類、各入賞役に対応する図柄組合せ、各入賞役の

作動または払出を示す図である。

20

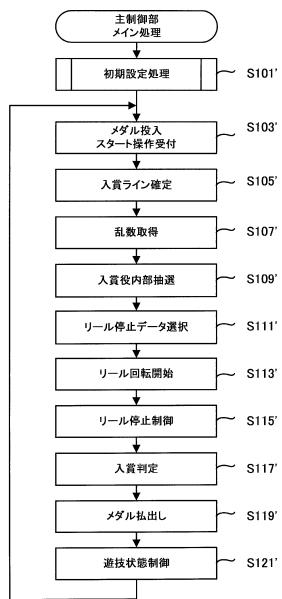

【図39】主制御部メイン処理の流れを示すフローチャートである。

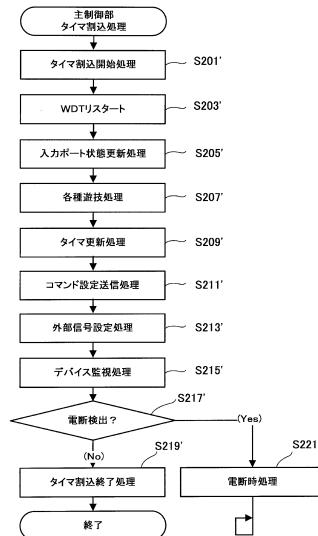

【図40】主制御部タイマ割込処理の流れを示すフローチャートである。

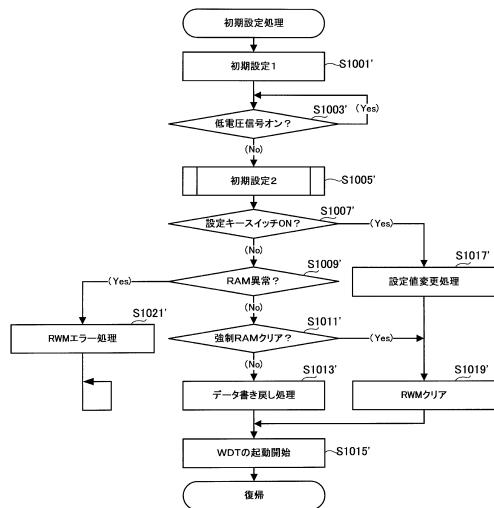

【図41】図39のステップS101における初期設定処理のフローチャートである。

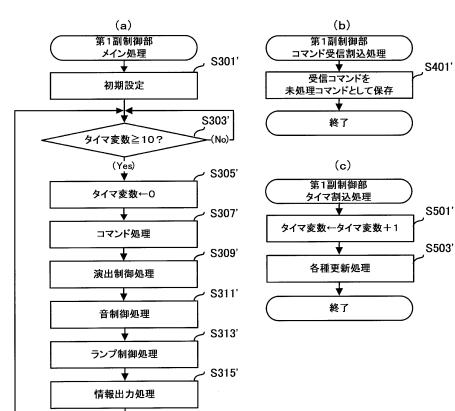

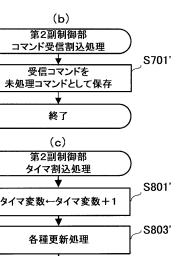

【図42】(a)は、第1副制御部のメイン処理のフローチャートであり、(b)は、第1副制御部のコマンド受信割込処理のフローチャートであり、(c)は、第1副制御部のタイマ割込処理のフローチャートである。

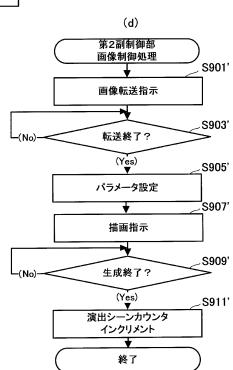

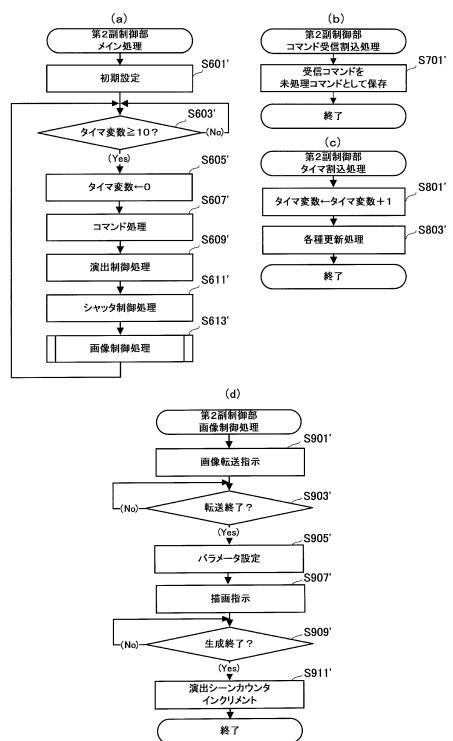

【図43】(a)は、第2副制御部のメイン処理のフローチャートであり、(b)は、第2副制御部のコマンド受信割込処理のフローチャートであり、(c)は、第2副制御部のタイマ割込処理のフローチャートである。

30

【発明を実施するための形態】

【0011】

以下、図面を用いて、本発明に係る遊技台(例えば、パチンコ機100等の弾球遊技機やスロット機等の回胴遊技機)について詳細に説明する。

【0012】

[実施形態1]

<全体構成>

まず、図1を用いて、本発明の第1実施形態に係るパチンコ機100の全体構成について説明する。なお、同図はパチンコ機100を正面側(遊技者側)から見た外観斜視図である。

40

【0013】

パチンコ機100は、外枠102と、本体104と、前面枠扉106と、球貯留皿付扉108と、発射装置110と、遊技盤200と、をその前面(遊技者側)に備える。

【0014】

外枠102は、遊技機設置営業店に設けられた設置場所(島設備等)へと固定させるための縦長方形状から成る木製の枠部材である。

【0015】

本体104は、外枠102の内部に備えられ、施錠機能付きで且つ、ヒンジ部112を介して外枠102に回動自在に装着された縦長方形状の遊技機基軸体となる扉部材である

50

。また、本体 104 は、枠状に形成され、内側に空間部 114 を有している。このパチンコ機 100 を設置した店舗（遊技店）の店員は、この本体 104 を開閉操作することが可能であり、本体 104 が開いたことを検出する本体開放センサ 1041 が設けられている。

#### 【0016】

前面枠扉 106 は、施錠機能付きで且つ開閉自在となるようにパチンコ機 100 の前面側となる本体 104 の前面に対しヒンジ部 112 を介して装着され、枠状に構成されることでその内側を開口部 116 とした扉部材である。遊技店の店員は、この前面枠扉 106 も開閉操作することが可能であり、前面枠扉 106 が開いたことを検出する前面枠扉センサ 1061 も設けられている。なお、この前面枠扉 106 には、開口部 116 にガラス製又は樹脂製の透明板部材 118 が設けられ、前面側には、スピーカ 120 や枠ランプ 122 が取り付けられている。前面枠扉 106 の後面と遊技盤 200 の前面とで遊技領域 124 が設けられる空間を区画形成する。なお、本実施形態では、光源を LED とするものもランプと称する。

#### 【0017】

球貯留皿付扉 108 は、パチンコ機 100 の前面において本体 104 の下側に対して、施錠機能付きで且つ開閉自在となるように装着された扉部材である。この球貯留皿付扉 108 は、前面枠扉 106 を開放した状態で操作可能となる開放レバー 1081 を押すことによって開く。また、球貯留皿付扉 108 が開いたことを検出する球貯留皿付扉センサ 1082 も設けられている。球貯留皿付扉 108 は、複数の遊技球（以下、単に「球」と称する場合がある）が貯留可能で且つ発射装置 110 へと遊技球を案内させる通路が設けられている上皿 126 と、上皿 126 に貯留しきれない遊技球を貯留する下皿 128 と、遊技者の操作によって上皿 126 に貯留された遊技球を下皿 128 へと排出させる球抜ボタン 130 と、遊技者の操作によって下皿 128 に貯留された遊技球を遊技球収集容器（俗称、ドル箱）へと排出させる球排出レバー 132 と、遊技者の操作によって発射装置 110 へと案内された遊技球を遊技盤の遊技領域 124 へと打ち出す球発射ハンドル 134 と、遊技者の操作によって各種演出装置 206（図 2 参照）の演出態様に変化を与えるチャンスボタン 136 と、チャンスボタン 136 に内蔵され、そのチャンスボタン 136 を発光させるチャンスボタンランプ 138 と、遊技店に設置されたカードユニット（CR ユニット）に対して球貸し指示を行う球貸操作ボタン 140 と、カードユニットに対して遊技者の残高の返却指示を行う返却操作ボタン 142 と、遊技者の残高やカードユニットの状態を表示する球貸表示部 144 と、を備える。また、図 1 に示すパチンコ機 100 には、下皿 128 が遊技球によって満タンになったことを検知する下皿満タン検知センサ（不図示）が設けられている。

#### 【0018】

発射装置 110 は、本体 104 の下方に取り付けられ、球発射ハンドル 134 が遊技者に操作されることによって回動する発射杆 146 と、遊技球を発射杆 146 の先端で打突する発射槌 148 と、を備える。この発射装置 110 は、遊技者に球発射ハンドル 134 が継続的に発射操作されている間は、所定の発射期間（例えば 0.6 秒）の経過ごとに遊技球を遊技盤の遊技領域 124 へ向けて発射する。

#### 【0019】

遊技盤 200 は、前面に遊技領域 124 を有し、本体 104 の空間部 114 に臨むように、所定の固定部材を用いて本体 104 に着脱自在に装着されている。遊技領域 124 は、遊技盤 200 を本体 104 に装着した後、開口部 116 から観察することができる。なお、図 1 では遊技領域 124 の具体的構成は図示省略しており、その具体的構成は図 3 に示す。

#### 【0020】

図 2 は、図 1 のパチンコ機 100 を背面側から見た外観図である。

#### 【0021】

パチンコ機 100 の背面上部には、上方に開口した開口部を有し、遊技球を一時的に貯

10

20

30

40

50

留するための球タンク 150 と、この球タンク 150 の下方に位置し、球タンク 150 の底部に形成した連通孔を通過して落下する球を背面右側に位置する払出装置 152 に導くためのタンクレール 154 とを配設している。

**【 0 0 2 2 】**

払出装置 152 は、筒状の部材からなり、その内部には、不図示の払出モータとスプロケットと払出センサとを備えている。この払出装置 152 は、着脱自在なものであり、所定位置に装着されると、タンクレール 154 の下流端に接続する。

**【 0 0 2 3 】**

スプロケットは、払出モータによって回転可能に構成されており、タンクレール 154 を通過して払出装置 152 内に流下した遊技球を一時的に滞留させると共に、払出モータを駆動して所定角度だけ回転することにより、一時的に滞留した遊技球を払出装置 152 の下方へ 1 個ずつ送り出すように構成している。すなわち、払出装置 152 は、遊技球に駆動力を与えてその遊技球を搬送する球送り装置の一種である。10

**【 0 0 2 4 】**

払出センサは、スプロケットが送り出した遊技球の通過を検知するためのセンサであり、遊技球が通過しているときにハイまたはローの何れか一方の信号を、遊技球が通過していないときはハイまたはローの何れか他方の信号を払出制御部 600 へ出力する。この払出センサを通過した遊技球は、不図示の球レールを通過してパチンコ機 100 の前面側に配設した上皿 126 に到達するように構成しており、パチンコ機 100 は、所定の付与条件が成立したことに基づいて遊技者にその付与条件に応じた量の遊技価値（遊技球）をこの構成により付与する（払い出す）。20

**【 0 0 2 5 】**

払出装置 152 の図中左側には、遊技全般の制御処理を行う主制御部 300（図 4 参照）を構成する主基板 156 を収納する主基板ケース 158、主制御部 300 が生成した処理情報に基づいて演出に関する制御処理を行う第 1 副制御部 400（図 4 参照）を構成する第 1 副基板 160 を収納する第 1 副基板ケース 162、第 1 副制御部 400 が生成した処理情報に基づいて演出に関する制御処理を行う第 2 副制御部 500（図 4 参照）を構成する第 2 副基板 164 を収納する第 2 副基板ケース 166、遊技球の払出に関する制御処理を行う払出制御部 600（図 4 参照）を構成するとともに遊技店員の操作によってエラーを解除するエラー解除スイッチ 168 を備える払出基板 170 を収納する払出基板ケース 172、遊技球の発射に関する制御処理を行う発射制御部 630（図 4 参照）を構成する発射基板 174 を収納する発射基板ケース 176、各種電気的遊技機器に電源を供給する電源管理部 660（図 4 参照）を構成するとともに遊技店員の操作によって電源をオンオフする電源スイッチ 178 と電源投入時に操作されることによって RAMクリア信号を主制御部 300 に出力する RAMクリアスイッチ 180 とを備える電源基板 182 を収納する電源基板ケース 184、および払出制御部 600 とカードユニットとの信号の送受信を行う CRインターフェース部 186 を配設している。30

**【 0 0 2 6 】**

図 3 は、遊技盤 200 を正面から見た略示正面図である。

**【 0 0 2 7 】**

遊技盤 200 には、外レール 202 と内レール 204 とを配設し、遊技球が転動可能な遊技領域 124 を区画形成している。40

**【 0 0 2 8 】**

遊技領域 124 の略中央には、演出装置 206 を配設している。この演出装置 206 には、略中央に装飾図柄表示装置 208 を配設し、その周囲に、普通図柄表示装置 210 と、第 1 特別図柄表示装置 212 と、第 2 特別図柄表示装置 214 と、普通図柄保留ランプ 216 と、第 1 特別図柄保留ランプ 218 と、第 2 特別図柄保留ランプ 220 と、高確中ランプ 222 を配設している。なお、以下、普通図柄を「普図」と称する場合があり、特別図柄、第 1 特別図柄、第 2 特別図柄のうちの一つまたは複数を「特図」と称する場合がある。50

## 【0029】

演出装置 206 は、演出可動体 224 を動作して演出を行うものであり、詳細については後述する。

## 【0030】

装飾図柄表示装置 208 は、装飾図柄ならびに演出に用いる様々な表示を行うための表示装置であり、本実施形態では液晶表示装置 (Liquid Crystal Dispaly) によって構成する。この装飾図柄表示装置 208 は、左図柄表示領域 208a、中図柄表示領域 208b、右図柄表示領域 208c および演出表示領域 208d の 4 つの表示領域に分割し、左図柄表示領域 208a、中図柄表示領域 208b および右図柄表示領域 208c はそれぞれ異なった装飾図柄を表示し、演出表示領域 208d は演出に用いる画像を表示する。さらに、各表示領域 208a、208b、208c、208d の位置や大きさは、装飾図柄表示装置 208 の表示画面内で自由に変更することを可能としている。なお、装飾図柄表示装置 208 として液晶表示装置を採用しているが、液晶表示装置でなくとも、種々の演出や種々の遊技情報を表示可能に構成されればよく、例えば、ドットマトリクス表示装置、7セグメント表示装置、有機EL (Electroluminescence) 表示装置、リール(ドラム)式表示装置、リーフ式表示装置、プラズマディスプレイ、プロジェクタを含む他の表示デバイスを採用してもよい。10

## 【0031】

普図表示装置 210 は、普図の表示を行うための表示装置であり、本実施形態では 7 セグメント LED によって構成する。第 1 特図表示装置 212 および第 2 特図表示装置 214 は、特図の表示を行うための表示装置であり、本実施形態では 7 セグメント LED によって構成する。これらの第 1 特図表示装置 212 および第 2 特図表示装置 214 は、所定の図柄表示手段である。なお、装飾図柄表示装置 208 に表示される装飾図柄は、第 1 特図表示装置 212 や第 2 特図表示装置 214 に表示される図柄を、演出を高めた形で表す図柄であり、装飾図柄表示装置 208 も、所定の図柄表示手段としてもよい。20

## 【0032】

普図保留ランプ 216 は、保留している所定の第 1 の変動遊技（詳細は後述する普図変動遊技）の数を示すためのランプであり、本実施形態では、普図変動遊技を所定数（例えば、4 つ）まで保留することを可能としている。

## 【0033】

第 1 特図保留ランプ 218 および第 2 特図保留ランプ 220 は、保留している所定の第 2 の変動遊技（詳細は後述する特図変動遊技）の数を示すためのランプであり、本実施形態では、特図変動遊技を所定数（例えば、4 つ、第 1 特図用と第 2 特図用を合わせると 8 つ）まで保留することを可能としている。ここにいう保留とは、後述する始動情報に基づく各種判定処理（抽選処理等）の開始を保留することを意味する。30

## 【0034】

高確中ランプ 222 は、現在の図柄制御状態を示す報知を行なうためのランプ（報知手段）である。この高確中ランプ 222 は、電源が投入されてから大当たり遊技の開始まで、現在の図柄制御状態を示す報知を行ない、それ以降は、現在の図柄制御状態を示す報知をしないように構成している。また図柄制御状態では、電源が再投入された場合には、電源が遮断される直前の図柄制御状態に復帰する。この図柄制御状態については後述するが、ここでの図柄制御状態として、通常状態、時短状態（電サボ状態）、および確変状態のうちのいずれの状態としてもよいし、特図確変ありの状態および特図確変なしの状態のうちの一方の状態としてもよい。40

## 【0035】

なお、本明細書では制御状態という遊技台（パチンコ機 100）の内部における状態をさす文言を用いて説明するが、この制御状態という文言にはいわゆる遊技状態の概念が含まれる。

## 【0036】

また、この演出装置 206 の周囲には、一般入賞口 226 と、普図始動口 228 と、第50

1特図始動口230と、第2特図始動口232と、可変入賞口234を配設している。

【0037】

一般入賞口226は、本実施形態では遊技盤200に複数配設しており、この一般入賞口226への入球を所定の球検出センサ(図示省略)が検出した場合(一般入賞口226に入賞した場合)、図2に示す払出装置152を駆動し、所定の個数(例えば、10個)の球を賞球として図1に示す上皿126に排出する。上皿126に排出した球は遊技者が自由に取り出すことが可能であり、これらの構成により、入賞に基づいて賞球を遊技者に払い出すようにしている。なお、一般入賞口226に入球した球は、パチンコ機100の裏側に誘導した後、遊技島側に排出する。本実施形態では、入賞の対価として遊技者に払い出す球を「賞球」、遊技者に貸し出す球を「貸球」と区別して呼ぶ場合があり、「賞球」と「貸球」を総称して「球(遊技球)」と呼ぶ。10

【0038】

普図始動口228は、ゲートやスルーチャッカーと呼ばれる、遊技領域124の所定の領域を球が通過したか否かを判定するための装置で構成しており、本実施形態では遊技盤200の左側に1つ配設している。普図始動口228を通過した球は一般入賞口226に入球した球と違って、遊技島側に排出することはない。球が普図始動口228を通過したことと所定の球検出センサが検出した場合、パチンコ機100は、普図表示装置210による普図変動遊技を開始する。

【0039】

第1特図始動口230は、本実施形態では遊技盤200の中央に1つだけ配設している。この第1特図始動口230は、遊技球が進入する入り口の大きさが変化しない第一の始動領域である。第1特図始動口230への入球を所定の球検出センサが検出した場合、図2に示す払出装置152を駆動し、所定の個数(例えば、3個)の球を賞球として上皿126に排出するとともに、第1特図表示装置212による特図変動遊技を開始する。なお、第1特図始動口230に入球した球は、パチンコ機100の裏側に誘導した後、遊技島側に排出する。この第1特図始動口230は、始動領域の一つであり、自身の大きさが変化しない固定始動領域の一例に相当する。20

【0040】

第2特図始動口232は、本実施形態では普図始動口228の下側に1つだけ配設している。すなわち、第2特図始動口232は、遊技盤200の右側に設けられている。この第2特図始動口232の近傍には、ソレノイドによって左右に開閉自在な一对の羽根部材2321が設けられており、一对の羽根部材2321と第2特図始動口232を併せたものが、可変始動手段に相当し、一般には、電動チューリップ(電チュー)と呼ばれる。一对の羽根部材2321は、第2特図始動口232への入賞の難易度を変更する部材である。すなわち、一对の羽根部材2321が閉じたままである第2特図始動口232への入球は不可能であり、一对の羽根部材2321が閉じた態様は入賞困難な開閉態様である。一方、普図変動遊技に当選し、普図表示装置210が当り図柄を停止表示した場合に一对の羽根部材2321が所定の時間間隔、所定の回数で開閉し、第2特図始動口232への球の入球が可能(入賞容易状態)になり、一对の羽根部材2321が開いた開状態は入賞容易な状態である。すなわち、第2特図始動口232は、入り口(遊技球の進入口)の大きさが小サイズ(第1の大きさに相当)と大サイズ(第2の大きさに相当)のうちのいずれか一方のサイズからいざれか他方のサイズに変化する、遊技球の進入のしやすさが可変の可変始動領域であって、第二の始動領域の一例に相当する。この大サイズの大きさは、第1特図始動口230の入り口の大きさよりも大きい。一对の羽根部材2321が開いた状態では、遊技領域124に進入した遊技球のうち、固定始動領域である第1特図始動口230に進入する遊技球よりも、可変始動領域である第2特図始動口232に进入する遊技球の方が多い。一方、小サイズの大きさは、第1特図始動口230の入り口の大きさよりも小さいか、あるいは第1特図始動口230の入り口の大きさ以下である。第2特図始動口232への入球を所定の球検出センサが検出した場合、払出装置152を駆動し、所定の個数(例えば、4個)の球を賞球として上皿126に排出するとともに、第2特図表示裝4050

置 214 による特図変動遊技を開始する。なお、第 2 特図始動口 232 に入球した球は、パチンコ機 100 の裏側に誘導した後、遊技島側に排出する。

#### 【0041】

可変入賞口 234 は、本実施形態では遊技盤 200 の中央部下方に 1 つだけ配設している。この可変入賞口 234 は、可変入賞開口と、ソレノイドによってその可変入賞開口を開閉自在な扉部材 2341 とを備えている。可変入賞開口は大入賞口と呼ばれることがあり、可変入賞口 234 はアタッカと呼ばれることがある。扉部材 2341 は、所定の閉状態およびその閉状態よりも遊技球の、可変入賞開口への進入が容易な開状態のうちのいずれか一方の状態からいずれか他方の状態に状態変更する。閉状態および開状態はともに静止状態であり、閉状態は所定の第 1 の静止状態であり、本実施形態の可変入賞口 234 における閉状態は、扉部材 2341 が遊技盤 200 の遊技者側の面と一致した静止状態である。一方、開状態は所定の第 2 の静止状態であり、本実施形態の可変入賞口 234 における開状態は、扉部材 2341 が遊技盤 200 に対して略垂直になるまで遊技者側に回動した静止状態である。可変入賞口 234 は、後述する大当たり遊技が開始されるまでは閉状態を維持し、大当たり遊技が開始されると、開状態と閉状態との間で状態変更を繰り返す。なお、閉状態には、完全に閉塞してしまる状態の他、遊技球の進入が実質的に不可能な程度に少し開いている状態であってもよい。また、可変入賞口は、遊技球が通過したり入り込んだりすること等によって遊技球の入賞となるものであればよく、図 3 に示すものに限定されない。特図変動遊技に当選して第 1 特図表示装置 212 あるいは第 2 特図表示装置 214 が大当たり図柄を停止表示した場合に扉部材 2341 が所定の時間間隔、所定の回数で開閉する。可変入賞口 234 への入球を所定の球検出センサが検出した場合、払出装置 152 を駆動し、所定の個数（例えば、15 個）の球を賞球として上皿 126 に排出する。なお、可変入賞口 234 に入球した球は、パチンコ機 100 の裏側に誘導した後、遊技島側に排出する。10

#### 【0042】

さらに、これらの入賞口や始動口の近傍には、風車と呼ばれる円盤状の打球方向変換部材 236 や、遊技釘 238 を複数個、配設していると共に、内レール 204 の最下部には、いずれの入賞口や始動口にも入賞しなかった球をパチンコ機 100 の裏側に誘導した後、遊技島側に排出するためのアウトロ 240 を設けている。20

#### 【0043】

上皿 126 に収容されている球は発射レールの発射位置に供給される。このパチンコ機 100 では、遊技者の球発射ハンドル 134 の操作量に応じた強度で発射モータを駆動し、発射杆 146 および発射槌 148 によって外レール 202、内レール 204 を通過させて遊技領域 124 に打ち出す。そして、遊技領域 124 の上部に到達した球は、打球方向変換部材 236 や遊技釘 238 等によって進行方向を変えながら下方に落下し、入賞口（一般入賞口 226、可変入賞口 234）や始動口（第 1 特図始動口 230、第 2 特図始動口 232）に入賞するか、いずれの入賞口や始動口にも入賞することなく、または普図始動口 228 を通過するのみでアウトロ 240 に到達する。30

#### 【0044】

##### <演出装置 206 >

次に、パチンコ機 100 の演出装置 206 について説明する。40

#### 【0045】

この演出装置 206 の前面側には、遊技球の転動可能な領域にワープ装置 242 およびステージ 244 を配設し、遊技球の転動不可能な領域に演出可動体 224 を配設している。また、演出装置 206 の背面側には、装飾図柄表示装置 208 および遮蔽装置 246（以下、扉と称する場合がある）を配設している。すなわち、演出装置 206 において、装飾図柄表示装置 208 および遮蔽装置 246 は、ワープ装置 242、ステージ 244、および演出可動体 224 の後方に位置することとなる。

#### 【0046】

ワープ装置 242 は、演出装置 206 の左上方に設けたワープ入口 242a に入った遊50

技球を演出装置 206 の前面下方のステージ 244 にワープ出口 242b から排出する。

**【0047】**

ステージ 244 は、ワープ出口 242b から排出された球や遊技釘 238 などによって乗り上げた球などが転動可能であり、ステージ 244 の中央部には、通過した球が第 1 特図始動口 230 へ入球し易くなるスペシャルルート 244a を設けている。

**【0048】**

演出可動体 224 は、本実施形態では人間の右腕の上腕と前腕を模した上腕部 224a と前腕部 224b とからなり、肩の位置に上腕部 224a を回動させる不図示の上腕モータと肘の位置に前腕部 224b を回動させる不図示の前腕モータを備える。演出可動体 224 は、上腕モータと前腕モータによって装飾図柄表示装置 208 の前方を移動する。

10

**【0049】**

遮蔽装置 246 は、格子状の左扉 246a および右扉 246b からなり、装飾図柄表示装置 208 および前面ステージ 244 の間に配設する。左扉 246a および右扉 246b の上部には、不図示の 2 つのブーリに巻き回したベルトをそれぞれ固定している。すなわち、左扉 246a および右扉 246b は、モータによりブーリを介して駆動するベルトの動作に伴って左右にそれぞれ移動する。遮蔽装置 246 は、左扉 246a および右扉 246b を閉じた状態ではそれぞれの内側端部が重なり、遊技者が装飾図柄表示装置 208 を視認し難いように遮蔽する。左扉 246a および右扉 246b を開いた状態ではそれぞれの内側端部が装飾図柄表示装置 208 の表示画面の外側端部と若干重なるが、遊技者は装飾図柄表示装置 208 の表示の全てを視認可能である。また、左扉 246a および右扉 246b は、それぞれ任意の位置で停止可能であり、例えば、表示した装飾図柄がどの装飾図柄であるかを遊技者が識別可能な程度に、装飾図柄の一部だけを遮蔽することができる。なお、左扉 246a および右扉 246b は、格子の孔から後方の装飾図柄表示装置 208 の一部を視認可能にしてもよいし、格子の孔の障子部分を半透明のレンズ体で塞ぎ、後方の装飾図柄表示装置 208 による表示を漠然と遊技者に視認させるようにしてもよいし、格子の孔の障子部分を完全に塞ぎ（遮蔽し）、後方の装飾図柄表示装置 208 を全く視認不可にしてもよい。

20

**【0050】**

図 1 に示すスピーカ 120 や枠ランプ 122 等の装飾ランプ、図 3 に示す装飾図柄表示装置 208 、演出可動体 224 、および遮蔽装置 246 は、演出手段に相当し、これらの中でも装飾図柄表示装置 208 は演出表示手段の一例に相当する。

30

**【0051】**

<制御部>

次に、図 4 を用いて、このパチンコ機 100 の制御部の回路構成について詳細に説明する。なお、同図は制御部の回路ブロック図を示したものである。

**【0052】**

パチンコ機 100 の制御部は、大別すると、遊技の中枢部分を制御する主制御部 300 と、主制御部 300 が送信するコマンド信号（以下、単に「コマンド」と呼ぶ）に応じて主に演出の制御を行う第 1 副制御部 400 と、第 1 副制御部 400 より送信されたコマンドに基づいて各種機器を制御する第 2 副制御部 500 と、主制御部 300 が送信するコマンドに応じて主に遊技球の払い出しに関する制御を行う払出制御部 600 と、遊技球の発射制御を行う発射制御部 630 と、パチンコ機 100 に供給される電源を制御する電源管理部 660 と、によって構成している。本実施形態では、主制御部 300 、第 1 副制御部 400 および第 2 副制御部 500 はそれぞれ別の回路基板からなるものであるが、これら 3 つの制御部（300, 400, 500）は、共通の一つの回路基板からなるものであってもよいし、第 1 副制御部 400 と第 2 副制御部 500 が、主制御部 300 の回路基板とは別の共通の一つの回路基板からなるものであってもよい。したがって、主制御部 300 、第 1 副制御部 400 および第 2 副制御部 500 それぞれを所定の制御手段ととらえることもできるし、これら 3 つの制御部（300, 400, 500）を併せた一つのものを所定の制御手段ととらえることもできるし、第 1 副制御部 400 および第 2 副制御部 500

40

50

を併せた一つのものを所定の制御手段ととらえることもできる。

**【0053】**

<主制御部>

まず、パチンコ機100の主制御部300について説明する。

**【0054】**

主制御部300は、主制御部300の全体を制御する基本回路302を備えており、この基本回路302には、CPU304（本発明の遊技制御手段、異常対応処理手段の一例に相当）と、制御プログラムや各種データを記憶するためのROM306と、一時的にデータを記憶するためのRAM308（本発明の記憶手段の一例に相当）と、各種デバイスの入出力を制御するためのI/O310と、リアルタイム割り込みや時間計測等を行うためのタイマ回路311と、時間や回数等を計測するためのカウンタ回路312と、後述するシステムリセットとユーザリセットを制御するリセット制御回路314（本発明の異常検出手段の一例に相当）と、水晶発振器316aを搭載している。なお、ROM306やRAM308については他の記憶装置を用いてもよい。また、ROM306には所定情報等を表す各種のデータがアドレスごとに格納されており、以降の説明でテーブルというときには、ROM306内のいずれのアドレスを指定するかを決定するための条件を表形式にまとめたものをさす場合がある。これらの点は後述する第1副制御部400や第2副制御部500についても同様である。この基本回路302のCPU304は、水晶発振器316bが出力する所定周期のクロック信号をシステムクロックとして入力して動作する。10

**【0055】**

また、基本回路302には、本体開放センサ1041、前面枠扉センサ1061、球貯留皿付扉センサ1082、および図1に示す下皿128が遊技球によって満タンになったことを検知する下皿満タン検知センサや、各始動口、入賞口の入り口および可変入賞口の内部に設けた球検出センサを含む各種センサ320が出力する信号を受信し、増幅結果や基準電圧との比較結果を乱数生成回路318および基本回路302に出力するためのセンサ回路322と、第1特図表示装置212や第2特図表示装置214の表示制御を行うための駆動回路324と、普図表示装置210の表示制御を行うための駆動回路326と、各種状態表示部328（例えば、普図保留ランプ216、第1特図保留ランプ218、第2特図保留ランプ220、高確中ランプ222等）の表示制御を行うための駆動回路330と、第2特図始動口232や可変入賞口234等を開閉駆動する各種ソレノイド332を制御するための駆動回路334を接続している。20

**【0056】**

乱数生成回路318は、基本回路302で使用する乱数を生成する。この乱数生成回路318における乱数の生成には、大別するとカウンタモードと乱数モードとの2種類の方法がある。カウンタモードでは、所定の時間間隔でカウントアップ（ダウン）する数値を取得して、その数値を乱数として導出する。乱数モードには、さらに2つの方法がある。乱数モードにおける一つ目の方法は、乱数の種を用いて所定関数（例えばモジュラス関数）による演算を行い、この演算結果を乱数として導出する。二つ目の方法は、0～65535の範囲の数値がランダムに配列された乱数テーブルから数値を読み出し、その読み出した数値を乱数として導出する。乱数生成回路318では、各種センサ320からセンサ回路322に入力される信号に重畠しているホワイトノイズを利用して不規則な値を取得する。乱数生成回路318は、こうして取得した値を、カウンタモードでカウントアップ（ダウン）させるカウンタの初期値として用いたり、乱数の種として用いたり、あるいは乱数テーブルの読み出し開始位置を決定する際に用いる。さらに、本実施形態では、生成する乱数の最大値を変更することにより、生成する乱数の範囲を変更できるように構成されている。この内容については後述する。40

**【0057】**

なお、第1特図始動口230に球が入賞したことを、各種センサ320のうちの球検出センサが検出した場合には、センサ回路322は球を検出したことを示す信号を乱数生成回路318に出力する。この信号を受信した乱数生成回路318は、第1特図始動口2350

0に対応する乱数生成回路のそのタイミングにおける値をラッチし、ラッチした値を、乱数生成回路318に内蔵された、第1特図始動口230に対応する乱数記憶用レジスタに記憶する。また、乱数生成回路318は、第2特図始動口232に球が入賞したことを示す信号を受信した場合も同様に、第2特図始動口232に対応する乱数生成回路のそのタイミングにおける値をラッチし、ラッチした値を、乱数生成回路318に内蔵された、第2特図始動口232に対応する乱数記憶用レジスタに記憶する。さらに、乱数生成回路318は、普図始動口228に球が入賞したことを示す信号を受信した場合も同様に、普図始動口228に対応する乱数生成回路のそのタイミングにおける値をラッチし、ラッチした値を、乱数生成回路318に内蔵された、普図始動口228に対応する乱数記憶用レジスタに記憶する。

10

#### 【0058】

また、この明細書にいう球検出センサとしては、具体的には、一般入賞口226、第1特図始動口230、第2特図始動口232、可変入賞口234など所定の入賞口に入賞した球を検出するセンサや、普図始動口228を通過する球を検出するセンサがあげられる。

#### 【0059】

さらに、基本回路302には、情報出力回路336を接続しており、主制御部300は、この情報出力回路336を介して、外部のホールコンピュータ（図示省略）等が備える情報入力回路350にパチンコ機100の遊技情報（例えば、制御状態を表す情報等）を出力する。

20

#### 【0060】

また、主制御部300には、電源管理部660から主制御部300に供給している電源の電圧値を監視する電圧監視回路338を設けており、この電圧監視回路338は、電源の電圧値が所定の値（本実施形態では9V）未満である場合に電圧が低下したことを示す低電圧信号を基本回路302に出力する。低電圧信号は、主制御部300のCPU304を動作させるための電気系統に異常があることを表す電気系統異常信号であり、電圧監視回路338は電気系統異常信号出力手段の一例に相当する。

#### 【0061】

また、主制御部300には、電源が投入されると起動信号（リセット信号）を出力する起動信号出力回路（リセット信号出力回路）340を設けており、CPU304は、この起動信号出力回路340から起動信号を入力した場合に、遊技制御を開始する（後述する主制御部メイン処理を開始する）。主制御部300のCPU304は、遊技制御手段の一例に相当する。

30

#### 【0062】

また、主制御部300は、第1副制御部400にコマンドを送信するための出力インターフェースと、払出制御部600にコマンドを送信するための出力インターフェースをそれぞれ備えており、この構成により、第1副制御部400および払出制御部600との通信を可能としている。なお、主制御部300と第1副制御部400および払出制御部600との情報通信は一方向の通信であり、主制御部300は第1副制御部400および払出制御部600にコマンド等の信号を送信できるように構成しているが、第1副制御部400および払出制御部600からは主制御部300にコマンド等の信号を送信できないように構成している。

40

#### 【0063】

##### <副制御部>

次に、パチンコ機100の第1副制御部400について説明する。第1副制御部400は、主に主制御部300が送信したコマンド等に基づいて第1副制御部400の全体を制御する基本回路402を備えており、この基本回路402には、CPU404と、一時的にデータを記憶するためのRAM408と、各種デバイスの入出力を制御するためのI/O410と、時間や回数等を計測するためのカウンタタイマ412を搭載している。この基本回路402のCPU404は、水晶発振器414が出力する所定期間のクロック信号

50

をシステムクロックとして入力して動作する。また、基本回路402には、制御プログラムや各種演出データを記憶するためのROM406が接続されている。なお、ROM406は、制御プログラムと各種演出データとを別々のROMに記憶させてもよい。

#### 【0064】

また、基本回路402には、スピーカ120（およびアンプ）の制御を行うための音源IC416と、各種ランプ418の制御を行うための駆動回路420と、演出可動体224の駆動制御を行うための駆動回路422と、演出可動体224の現在位置を検出する演出可動体センサ424と、図1に示すチャンスボタン136の押下を検出するチャンスボタン検出センサ426と、演出可動体センサ424やチャンスボタン検出センサ426からの検出信号を基本回路402に出力するセンサ回路428と、を接続している。10

#### 【0065】

さらに、第1副制御部400には、装飾図柄表示装置（液晶表示装置）208および遮蔽装置246の制御を行うための第2副制御部500が接続されている。

#### 【0066】

第1副制御部400と第2副制御部500を併せた副制御手段は、遊技制御手段である主制御部300からの指令信号を受信し、受信した指令信号に基づいて、装飾図柄表示装置208等の演出手段を制御する。

#### 【0067】

<払出手部、発射手部、電源管理部>

次に、パチンコ機100の払出手部600、発射手部630、電源管理部660について説明する。20

#### 【0068】

払出手部600は、主に主制御部300が送信したコマンド等の信号に基づいて図2に示す払出手部152の払出手モータ602を制御すると共に、払出手センサ604が出力する制御信号に基づいて賞球または貸球の払い出しが完了したか否かを検出すると共に、インターフェース部606を介して、パチンコ機100とは別体で設けられたカードユニット608との通信を行う。

#### 【0069】

発射手部630は、払出手部600が出力する、発射許可または停止を指示する制御信号や、球発射ハンドル134内に設けた発射強度出力回路が出力する、遊技者による球発射ハンドル134の操作量に応じた発射強度を指示する制御信号に基づいて、図1に示す発射杆146および発射桿148を駆動する発射モータ632の制御や、上皿126から発射装置110に球を供給する球送り装置634の制御を行う。30

#### 【0070】

電源管理部660は、パチンコ機100に外部から供給される交流電源を直流化し、所定の電圧に変換して払出手部600と第2副制御部500に所定電圧を供給する。主制御部300、第1副制御部400、および発射手部630は、払出手部600から所定電圧の供給を受ける。また、電源管理部660は、外部からの電源が断たれた後も所定の部品（例えば主制御部300のRAM308等）に所定の期間（例えば10日間）電源を供給するための蓄電回路（例えば、コンデンサ）を備えている。なお、本実施形態では、電源管理部660から払出手部600と第2副制御部500に所定電圧を供給し、払出手部600から主制御部300と第1副制御部400と発射手部630に所定電圧を供給しているが、各制御部や各装置に他の電源経路で所定電圧を供給してもよい。40

#### 【0071】

<図柄の種類>

次に、図5(a)～(c)を用いて、パチンコ機100の第1特図表示装置212、第2特図表示装置214、装飾図柄表示装置208、普通図柄表示装置210が停止表示する特図および普図の種類について説明する。

#### 【0072】

図5(a)は特図の停止図柄態様（第1の図柄態様）の一例を示したものである。第150

特図始動口 230 に球が入球したことを球検出センサである第 1 始動口センサが検出したことを条件として特図 1 変動遊技が開始され、第 2 特図始動口 232 に球が入球したことを球検出センサである第 2 始動口センサが検出したことを条件として特図 2 変動遊技が開始される。特図 1 変動遊技が開始されると、第 1 特別図柄表示装置 212 は、7 個のセグメントの全点灯と、中央の 1 個のセグメントの点灯を繰り返す「特図 1 の変動表示」(特図変動遊技)を行う。また、特図 2 変動遊技が開始されると、第 2 特別図柄表示装置 214 は、7 個のセグメントの全点灯と、中央の 1 個のセグメントの点灯を繰り返す「特図 2 の変動表示」(特図変動遊技)を行う。そして、特図 1 の変動開始前に決定した変動時間が経過すると、第 1 特別図柄表示装置 212 は特図 1 の停止図柄態様を停止表示し、特図 2 の変動開始前に決定した変動時間が経過すると、第 2 特別図柄表示装置 214 は特図 2 の停止図柄態様を停止表示する。以下、この「特図 1 又は 2 の変動表示」を開始してから特図 1 又は 2 の停止図柄態様を停止表示するまでの一連の表示を特図の変動表示と称することがある。この特図の変動表示は複数回、連続して行われることがある。

10

#### 【0073】

図 5 (a) には、図柄変動表示における停止図柄態様として「特図 A」から「特図 J」の 10 種類の特図が示されている。図 5 (a) においては、図中の白抜きの部分が消灯するセグメントの場所を示し、黒塗りの部分が点灯するセグメントの場所を示している。

#### 【0074】

本実施形態では、特図の停止図柄態様として、6 種類の大当たり図柄(「特図 A」から「特図 F」)が用意されている。「特図 A」は 15 ラウンド (R) 特別大当たり図柄であり、「特図 C」は 2 R 特別大当たり図柄であって、突然確変と称される。これらの図柄(特図 A, C)が停止表示されるとその後、制御状態は特図高確率普図高確率状態になる。「特図 B」は 15 R 大当たり図柄であり、「特図 D」は 2 R 大当たり図柄であって、突然時短と称される。特図 B または特図 D が停止表示されるとその後、制御状態は特図低確率普図高確率状態になる。「特図 E」は、隠れ確変と称される 2 R 大当たり図柄であり、「特図 F」は突然通常と称される 2 R 大当たり図柄である。特図 E が停止表示されるとその後、制御状態は特図高確率普図低確率状態になる。特図 F が停止表示されるとその後、制御状態は特図低確率普図低確率状態になる。

20

#### 【0075】

ここにいうラウンドとは、所定量の遊技価値(所定球数)を獲得することができるチャンスの回数をいう。本実施形態では、図 3 に示す可変入賞口 234 の作動回数を表すものであり、15 ラウンドとは、可変入賞口 234 の 1 または複数回の開閉動作を 1 回(1 回の作動)として、この作動が 15 回続くことを意味する。すなわち、1 回の作動が、開閉状態が第 1 の開閉状態(ここでは閉状態)から第 2 の開閉状態(ここでは開状態)に変化する特定変化の一例に相当し、可変入賞口 234 は、大当たり遊技中に、この特定変化を複数の定数回(15 ラウンドの場合であれば 15 回)行うものである。各ラウンドは所定のラウンド終了条件(例えば所定球数(一例として 10 球)の遊技球の進入、所定量の遊技価値(所定球数)の獲得、ラウンド開始から所定時間の経過などのうちのうちの 1 または複数)が成立することにより終了する。本実施形態のパチンコ機 100 では、後述するように、特図変動遊技における大当たりか否かの決定はハードウェア乱数の抽選によって行い、特別大当たりか否かの決定はソフトウェア乱数の抽選によって行う。大当たりと、特別大当たりあるいは時短大当たりとの違いは、次回の特図変動遊技で、大当たりに当選する確率が高い(特別大当たりあるいは時短大当たり)か低い(大当たり)かの違いである。以下、この大当たりに当選する確率が高い状態のことを特図高確率状態と称し、その確率が低い状態のことを特図低確率状態と称する。本実施形態では、大当たり遊技中には特図低確率状態へ移行し、特図 A、特図 C、および特図 E に当選した場合には、大当たり遊技終了後、次に大当たりするまで特図高確率状態が維持される。一方、特図 B、特図 D、および特図 F に当選した場合には、大当たり遊技終了後も特図低確率状態のままである。特図低確率状態は第 1 の確率制御状態の一例に相当する。また、大当たり遊技終了後に特図高確率状態になることを特図確変と称することもあり、大当たり遊技終了後に大当たりに当選する確率が高くなっている状態

30

40

50

(特図高確率状態)は、遊技者の有利度が高くなる制御状態であって第2の確率制御状態の一例に相当する。この特図高確率状態を確変状態と称することがある。なお、本明細書では制御状態という遊技台(パチンコ機100)の内部における状態をさす文言を用いて説明するが、この制御状態という文言にはいわゆる遊技状態の概念が含まれる。この確率制御状態の移行は主制御部300が行い、主制御部300は、確率制御状態移行手段の一例に相当する。

#### 【0076】

また、特図A～Dに当選すると、いずれも大当たり遊技終了後、電チューサポート(電サポ)有りの状態(以下、電サポ状態と称する)に移行する。電サポ状態とは、特図変動遊技における大当たりを終了してから、次の大当たりを開始するまでの時間を短くする等して、遊技者の有利度が非電サポ状態より高い所定状態のことという。この電サポ状態は、このパチンコ機100に用意された制御状態の一つであり、時短状態と称されることもある。すなわち、電サポ状態(時短状態)は、大当たり遊技の終了を条件に開始される。なお、厳密にいえば、「電サポ状態」はあくまでも普図がらみの状態であり、「時短状態」は特図がらみの状態または普図および特図がらみの状態である。主制御部300のRAM308には時短フラグも用意されており、時短フラグがオンに設定されていると、電サポ状態であり、普図高確率状態である。普図高確率状態では普図低確率状態に比べて、普図変動遊技に当選しやすくなる(普図確変)。例えば、普図変動遊技の当選確率が、普図低確率状態(非電サポ状態)では1/101であるのに対し、普図高確率状態(電サポ状態)では99/101に上昇する。また、電サポ状態の方が、非電サポ状態に比べて普図変動遊技の変動時間は短くなる(普図变短)。例えば、非電サポ状態では10秒の普図変動遊技の変動時間が電サポ状態では1.2秒に短縮される。また、電サポ状態では、非電サポ状態に比べて、第2特図始動口232の一対の羽根部材2321の1回の開放における開放時間が長くなりやすい(電チュー開放期間延長)。例えば、非電サポ状態では0.3秒の電チュー開放期間が電サポ状態では1.7秒に延長される。さらに、電サポ状態では非電サポ状態に比べて、一対の羽根部材2321は多く開きやすい(電チュー開放回数増加)。例えば、普図始動口228への1回の入賞につき非電サポ状態では1回しか開かない一対の羽根部材2321が、電サポ状態では3回開く(例えば、1.7秒開放することを3回繰り返し、開放と開放の間の閉鎖時間は1.6秒)。電チュー開放期間延長や電チュー開放回数増加により、第2特図始動口232に入球する確率が高まる。なお、時短フラグは、大当たり遊技中にはオフに設定される。したがって、大当たり遊技中には、非電サポ状態が維持される。これは、大当たり遊技中に電サポ状態であると、大当たり遊技中に可変入賞口234に所定の個数、遊技球が入球するまでの間に第2特図始動口232に多くの遊技球が入球し、大当たり中に獲得することができる遊技球の数が多くなってしまい射幸性が高まってしまうという問題があり、これを解決するためのものである。なお、本実施形態では、電サポ状態(時短状態)では、普図確変、普図变短、電チュー開放期間延長、および電チュー開放回数増加の総てが行われるが、これらのうちの少なくともいずれか一つが行われれば、遊技者の有利度が高い状態になり、電サポ状態(時短状態)としてもよい。あるいは、第2特図始動口232に入球する確率が高まる、電チュー開放期間延長または電チュー開放回数増加のうちのいずれか一方が行われれば、電サポ状態(時短状態)としてもよい。非電サポ状態では、電サポ状態よりも遊技球が第2特図始動口232に進入し難い。上述のごとく、第2特図始動口232は、遊技球が進入する入り口の大きさが小サイズと大サイズのうちのいずれか一方のサイズからいずれか他方のサイズに変化するものである。この第2特図始動口232は、入り口が、電サポ状態では非電サポ状態よりも長期間にわたって大サイズである。本実施形態では、特図Aおよび特図Cが停止表示されると、その後に行われる大当たり遊技終了後、次に大当たり遊技が開始されるまで電サポ状態(普図高確率状態)が維持され、特図Bおよび特図Dが停止表示されると、その後に行われる大当たり遊技終了後、特図変動遊技が100回行われる間、電サポ状態が維持され、101回目には非電サポ状態(普図低確率状態)に移行する。一方、電サポ無しの大当たり(特図E、特図F)に当選した場合には、大当たり遊技終了後に電サポ状態に移行しない。非電サポ状態では、電サポ状態よりも遊技球が第2特図始動口232に進入し難い。

10

20

30

40

50

態では、第2特図始動口232は、入り口が小サイズに維持される。一方、上述のごとく、電サポ状態では、第2特図始動口232は、入り口が大サイズになり、遊技球の進入率が高められる。すなわち、非電サポ状態では、遊技球が可変始動領域である第2特図始動口232に第1の進入率で進入するのに対し、電サポ状態では、遊技球が第2特図始動口232に上記第1の進入率よりも進入率が高い第2の進入率で進入する。したがって、非電サポ状態が第一の進入率制御状態の一例に相当し、電サポ状態が第二の進入率制御状態の一例に相当する。

#### 【0077】

さらに、本実施形態では、大当たり図柄の他に小当たり図柄として2種類の停止図柄が用意されている。図5(a)に示す、特図Gは第1小当たり図柄であり、特図Hは第2小当たり図柄である。小当たり遊技では、可変入賞口234の扉部材2341が所定回(例えば15回)作動し、その扉部材2341は、1回の作動につき開閉状態を最大で1.5秒間しか維持しない。小当たりにおける扉部材2341の開放では、例えば、1回目の開放で、遊技球が所定球数(例えば10球)進入してしまうと、あるいは所定量の遊技価値(所定球数)を獲得してしまうと、2回目以降の開放は行われない。小当たり遊技中には、特図低確率普図低確率状態へ移行する。小当たりは、小当たり遊技前後で制御状態が変化しない役であり、小当たり遊技終了後には小当たり遊技開始前の制御状態に復帰する。

#### 【0078】

大当たり遊技および小当たり遊技では、可変入賞口234の扉部材2341が1または複数回の開閉動作を行い、遊技者の有利度が相対的に高い状態になる。

#### 【0079】

また、本実施形態では、ハズレ図柄も2種類用意されている。図5(a)に示す、特図Iは第1ハズレ図柄であり、特図Jは第2ハズレ図柄である。ハズレ図柄が停止表示されると、可変入賞口234の扉部材2341は開閉動作を行わず、遊技者の有利度が相対的に低い状態になる。なお、「特図I」と「特図J」以外のハズレ図柄(例えば、第3のハズレ図柄等)をさらに用意しておいてもよく、本実施形態ではハズレ図柄は複数種類の図柄を含むものである。

#### 【0080】

以上説明したように、本実施形態のパチンコ機100では、遊技者の有利度が高い第2の有利度の当り制御状態(大当たり制御状態および小当たり制御状態)と、第2の有利度よりは有利度が低い第1の有利度のハズレ制御状態とが用意され、パチンコ機100は当り制御状態(第二の制御状態)とハズレ制御状態(第一の制御状態)のうちのいずれか一方の制御状態をとる。これらの制御状態の移行も主制御部300のCPU304が行い、主制御部300のCPU304は、制御状態移行手段の一例にも相当する。なお、小当たり制御状態は、可変入賞口234の扉部材2341が開閉動作を行うものの、可変入賞口234への入球はほとんど期待することができないため、小当たり制御状態を上記第1の有利度の制御状態(第一の制御状態)ととらえることもできる。

#### 【0081】

なお、本実施形態のパチンコ機100には、大当たり図柄1として「特図A」以外の図柄も用意されており、大当たり図柄2等の他の図柄についても同様である。

#### 【0082】

第1特図表示装置212および第2特図表示装置214は、当否判定結果(抽選結果)を報知する報知手段であって、図柄変動を開始してから当否判定の結果に対応した図柄様(特図A~と特図J)を停止表示するまでの図柄変動表示を行う図柄表示手段の一例に相当する。

#### 【0083】

図5(b)は装飾図柄の一例を示したものである。本実施形態の装飾図柄には、「装飾1」~「装飾10」の10種類がある。第1特図始動口230または第2特図始動口232に球が入賞したこと、すなわち、第1特図始動口230に球が入球したことを第1始動口センサが検出したこと、あるいは第2特図始動口232に球が入球したことを第2始動

10

20

30

40

50

口センサが検出したことを条件にして、装飾図柄表示装置 208 の左図柄表示領域 208 a、中図柄表示領域 208 b、右図柄表示領域 208 c の各図柄表示領域に、「装飾 1」

「装飾 2」 「装飾 3」 ··· ··· 「装飾 9」 「装飾 10」 「装飾 1」 ··· の順番で表示を切り替える「装飾図柄の変動表示」を行う。すなわち、装飾図柄表示装置 208 は、第 1 特別図柄表示装置 212 および第 2 特別図柄表示装置 214 とは別に、装飾図柄を変動表示するものである。そして、装飾図柄の組合せである停止図柄態様（第 2 の図柄態様）を停止表示する。15R 特別大当たりである「特図 A」や 2R 特別大当たりである「特図 C」を報知する場合には、図柄表示領域 208 a ~ 208 c に、同じ奇数の装飾図柄が 3 つ並んだ“装飾図柄の組合せ 2”（例えば「装飾 3 - 装飾 3 - 装飾 3」や「装飾 5 - 装飾 5 - 装飾 5」等）を停止表示する。10

15R 大当たりである「特図 B」を報知する場合には、図柄表示領域 208 a ~ 208 c に、同じ偶数の装飾図柄が 3 つ並んだ“装飾図柄の組合せ 1”（例えば「装飾 2 - 装飾 2 - 装飾 2」や「装飾 4 - 装飾 4 - 装飾 4」等）を停止表示する。また、隠れ確変である「特図 E」や、突然通常である「特図 F」や、小当たりである「特図 G」、「特図 H」を報知する場合には、図柄表示領域 208 a ~ 208 c に、「装飾 1 - 装飾 2 - 装飾 3」といった“装飾図柄の組合せ 3”を停止表示し、突然確変である「特図 C」や、突然時短である「特図 D」を報知する場合には、図柄表示領域 208 a ~ 208 c に、「装飾 1 - 装飾 3 - 装飾 5」といった“装飾図柄の組合せ 4”を停止表示する。また、ハズレである「特図 I」、「特図 J」を報知する場合には、図柄表示領域 208 a ~ 208 c に、“装飾図柄の組合せ 1” ~ “装飾図柄の組合せ 4”以外の装飾図柄の組合せ（例えば、ばらけ目）を停止表示する。20

以下、装飾図柄表示装置 208 において、この「装飾図柄の変動表示」を開始してから装飾図柄の停止図柄態様（例えば、“装飾図柄の組合せ 2”）を停止表示するまでの一連の表示を装飾図柄の変動表示と称することがある。

#### 【0084】

なお、特図 1 や特図 2 の停止図柄態様（図 5 (a) 参照）と、装飾図柄表示装置 208 の左中右の各図柄表示領域 208 a ~ c に表示される一つの装飾図柄の停止図柄態様（同図 (b) 参照）は、装飾図柄（同図 (b) 参照）の方が大きい。

#### 【0085】

図 5 (c) は普図の停止図柄態様（第 2 の図柄態様）の一例を示したものである。本実施形態の普図の停止表示態様には、当り図柄である「普図 A」と、ハズレ図柄である「普図 B」の 2 種類がある。普図始動口 228 を球が通過したことを球検出センサであるゲートセンサが検出したことに基づいて、普図表示装置 210 は、7 個のセグメントの全点灯と、中央の 1 個のセグメントの点灯を繰り返す「普図の変動表示」（普図変動遊技）を行う。そして、変動時間が経過した後に、当り図柄である「普図 A」とハズレ図柄である「普図 B」の内のいずれか一方の図柄を停止表示する。この図 5 (c) においても、図中の白抜きの部分が消灯するセグメントの場所を示し、黒塗りの部分が点灯するセグメントの場所を示している。30

#### 【0086】

以下、この「普図の変動表示」を開始してから普図の停止図柄態様を停止表示するまでの一連の表示を普図の変動表示と称することがある。普図表示装置 210 は補助図柄報知手段の一例に相当する。40

#### 【0087】

<主制御部の基本回路の構成例>

次に、図 6 を用いて、主制御部 300 の基本回路 302 の構成例について説明する。同図は、図 4 に示す基本回路 302 の構成例を示す図である。

#### 【0088】

図 6 に示す基本回路 302 には、CPU 304、ROM（内蔵 ROM）306、RAM（内蔵 RAM）308、外部バス制御回路 3101、パラレル入力ポート 3102、アドレスデコード回路 3103、タイマ回路 3111、カウンタ回路 3112、リセット制御回路 3114 に加え、割込み制御回路 3100、クロック回路 3200、乱数生成回路 318 が50

備えられており、これら全てが内部バス 3300 を介して互いに接続されている。

#### 【0089】

なお、外部バス制御回路 3101、パラレル入力ポート 3102、アドレスデコード回路 3103 の 3つが、図4の I/O 310 に相当するものである。

#### 【0090】

以下、上記説明した各部の詳細について説明する。

#### 【0091】

まず、CPU304、ROM306、RAM308 については、図4にて説明した通りである。

#### 【0092】

外部バス制御回路 3101 は、I/Oリクエスト端子(XIORQ端子)、メモリリクエスト端子(XMREQ端子)、リード信号端子(XRD端子)、ライト信号端子(XWR端子)、16ビット幅のアドレス出力端子(A0端子～A15端子)、および8ビット幅の入出力端子であるデータ入出力端子(D0端子～D7端子)を有する。本実施形態では、このうちデータ入出力端子(D0端子～D7端子)は、図4に示す各駆動回路 324, 326, 330, 334 へのデータ出力と、各周辺制御回路からのデータ入力に用いられている。このデータ入出力端子(D0端子～D7端子)によるデータの入出力先は、アドレス出力端子(A0端子～A15端子)から出力されるアドレス信号、およびアドレスデコード回路 3103 から出力されるチップセレクト信号を用いて切り替えられる。

#### 【0093】

パラレル入力ポート 3102 は、4つの入力端子(P0端子～P3端子)を有する。これらの入力端子(P0端子～P3端子)は、図4に示すセンサ回路 322 に接続されており、センサ回路 322 からの信号の入力に用いられている。本実施形態では、第1特図始動口 230 への入球を検出する球検出センサからの信号が P0 端子に入力され、第2特図始動口 232 への入球を検出する球検出センサからの信号が P1 端子に入力され、普図始動口 228 への入球を検出する球検出センサからの信号が P2 端子に入力される。また、センサ回路 322 からの信号は、乱数生成回路 318 が生成する乱数を CPU304 に取得させるためのラッチ信号として、乱数生成回路 318 に出力する。この動作については後述する。

#### 【0094】

アドレスデコード回路 3103 は、14の出力端子(XCS0端子～XCS13端子)を有する。この出力端子(XCS0端子～XCS13端子)は、基本回路 302 の外部にある周辺制御回路に接続されており、外部バス制御回路 3101 のデータ入出力端子(D0端子～D7端子)から出力されるデータの送信先を切り替えるためのチップセレクト信号等の出力に用いられている。

#### 【0095】

タイマ回路 311 は、時間の計測に用いられる。なお、タイマ回路 311 は設定された計測時間を過ぎると、タイムアウト信号をカウンタ回路 312 に出力する。一方、カウンタ回路 312 は、各種信号の立ち上がり(あるいは立ち下がり)の回数の計測に用いられる。このカウンタ回路で計測される信号には、基本回路 302 のシステムクロックの他、上記タイマ回路からのタイムアウト信号、メモリの読み書き信号、メモリリクエスト信号、外部入出力の信号、割込みに対する応答信号等も計測することができる。

#### 【0096】

リセット制御回路 314 は、システムリセット入力端子(XSRS端子)と、リセット出力端子(XRSTO端子)の2つの端子を有する。このシステムリセット入力端子(XSRS端子)は電圧監視回路 338 に接続されている。このシステムリセット入力端子(XSRS端子)からシステムリセット信号(例えば一定時間 L レベルの信号)が入力されると、リセット制御回路 314 は、基本回路 302 の内部の回路に対してこのシステムリセット信号を出力するとともに、基本回路 302 の外部にある周辺制御回路に対しリセット出力端子(XRSTO端子)からリセット信号(例えば、L レベルから H レベ

10

20

30

40

50

ルへの立ち上がり信号)が出力される。この場合、基本回路302では、システムリセットと称する処理が実行され、各回路が初期化される。このシステムリセットが実行される一例として、電源投入時が挙げられる。なお、このシステムリセットについては後述する。

#### 【0097】

また、リセット制御回路314は、ウォッチドッグタイマ(WDT)3141(本発明の復帰指示手段の一例に相当)、および指定エリア外走行禁止回路3142を備えている。WDT3141がタイムアウトになった場合や、CPU304が所定の範囲以外のアドレスを参照(指定エリア外走行)した場合には、リセット制御回路314は、基本回路302の内部の回路に対してシステムリセット信号およびユーザリセット信号のいずれかを出力する。なお、システムリセット信号およびユーザリセット信号のどちらを出力するかは、ROM306内のプログラム管理エリア(詳細は後述)の設定に従う。また、基本回路302の外部にある周辺制御回路に対しては、リセット出力端子(XRSTO端子)からリセット信号が出力される。

#### 【0098】

基本回路302では、設定によって上記のシステムリセットか、あるいはユーザリセットと称する処理のいずれかを実行させることができる。なお、ユーザリセットでは、各回路が必要に応じて初期化される。このユーザリセットについては後述する。

#### 【0099】

上記指定エリア外走行は、プログラムが想定外の動作をしていることを意味する。この場合、CPU304が本来プログラムとして扱われるはずのないコードにより動作することになる。このような状況は、プログラムミスによる所謂暴走した状態の他に、何らかの不正によって生じている可能性がある。この場合、上記のシステムリセットおよびユーザリセットのいずれかの処理により、正常な動作に復帰させることができるようになっている。また、WDT3141がタイムアウトになった場合としては、プログラムミスによる暴走した状態や、電圧降下によりCPU304が本来設計した動作を行うことができなくなった場合等がある。この場合にも、上記のシステムおよびユーザリセットのいずれかの処理により、正常な動作に復帰させることができるようになっている。

#### 【0100】

割込み制御回路3100は、外部入力や内部状態の変化に応じて適宜処理を実行させるために割込みを発生させる。この割込み処理には、例えば外部からの入力(センサによる信号)を受け付けた場合に実行する処理がある。なお、この割込み処理は、本発明の第三の処理に相当する。また、この割込み処理の契機となる、外部入力や内部状態の変化に応じた割込みは、本発明の第二の割込み要求に相当する。本実施形態では、乱数生成回路318が、乱数を取得するためのラッチ信号を受信した際にも、割込み処理を実行(割込みを発生)させることができるようになっている。なお、割込み制御回路3100は、内部情報レジスタ3101を備えており、この内部情報レジスタ3101には、乱数生成回路318で乱数更新周期を決める外部クロック(カウントクロック)の周期の異常、および乱数の更新に関する異常、さらに、直前に発生したユーザリセットのリセット要因の情報等が格納される。なお、この内部情報レジスタ3101は、異常検出情報保持手段の一例に相当する。

#### 【0101】

クロック回路3200は、図4に示すの水晶発振器316b(以下、システム用水晶発振器316bと称する場合がある)から外部クロック入力端子(EX端子)を介して入力される外部クロック(この例では、24MHzのクロック)を所定の分周比(この例では、1/2)で分周し、分周後のシステムクロック(この例では、12MHzのクロック)をこの基本回路302内部の各回路に供給する。また、このシステムクロックをシステムクロック出力端子(CLKO端子)を介して基本回路302外部の周辺制御回路に出力する。

#### 【0102】

10

20

30

40

50

乱数生成回路 318 は、乱数を更新するためのクロック信号（カウントクロック）を用いて、乱数のラッチ信号を受信したときにこの更新された乱数を乱数レジスタ内に保持するものである。本実施形態では、水晶発振器 316a から外部クロック入力端子（RCK 端子）を介して入力される外部クロック信号を所定の分周比（この例では、1/2）で分周してこのカウントクロックに用いているが、基本回路 302 内部のクロック信号を用いることもでき、この場合は水晶発振器 316a は不要となる。乱数レジスタに保持された値は、乱数として読み出して使用することができる。なお、乱数レジスタから乱数を読み出すと、乱数レジスタが次の乱数をラッチすることを許容する許容状態とすることができます。この乱数生成回路 318 の詳細は後述する。

## 【0103】

10

&lt;メモリマップおよびI/Oマップ&gt;

次に、図 7 を用いて、図 6 に示す基本回路 302 のメモリマップおよび I/O マップの一例について説明する。同図は、基本回路 302 のメモリマップおよび I/O マップの一例を示す図である。

## 【0104】

20

図 7 (a) には、図 6 に示す基本回路 302 におけるメモリマップの一例が示されている。このメモリマップには、0000H から FFFFH までのアドレス空間が示されている。このうち、0000H から 2FFFH までの空間には ROM306 が割り当てられ、F000H から F3FFFH までの空間には RAM308 が割り当てられ、FE00H から FEBFH までの空間には基本回路 302 内の各回路に内蔵されている内蔵レジスタが割り当てられている。CPU304 に、これらの番地に対してアクセスする命令を実行させることにより、対応するハードウェアに対するアクセスを実行させることができる。なお、0000H から 2FBFH までの空間（12224 バイト）は、プログラムコードとこのプログラムが使用するプログラムデータの格納に使用される空間であり、2FC0H から 2FFFH までの空間（64 バイト）は、プログラム管理エリアとして使用される空間である。プログラム管理エリアには、この基本回路 302 を動作させる際に用いられる各種設定（乱数生成回路の動作設定、WDT3141 の動作設定等）や、各種識別情報（製品コード、メーカーコード、ID ナンバー等）が格納される。

## 【0105】

30

図 7 (b) には、図 6 に示す基本回路 302 における I/O マップの一例が示されている。この I/O マップには、00H から FFH までの入出力空間が示されている。この図 7 (b) には、00H から BFH までの空間に内蔵レジスタが割り当てられている例が示されている。この場合、CPU304 に、これらの番地に対する入出力命令を実行させることにより、内蔵レジスタに対して入出力を行う事が出来る。図 6 に示す基本回路 302 では、内蔵レジスタを、図 7 (a) に示すようにメモリマップ上に割り当てるか、図 7 (b) に示すように I/O マップ上に割り当てるかを選択することができるようになっている。すなわち設計方針によって、何れかの方式を選択することができる。なお、本実施形態では、図 7 (a) の方式を採用している。

## 【0106】

40

&lt;リセット処理&gt;

次に、図 8 を用いて、システムリセットの流れについて説明する。同図は、システムリセットの流れを示す図である。

## 【0107】

上述したように、システムリセット信号がリセット制御回路 314 の XSRST 端子から入力されると、システムリセットと称する処理が実行される。

## 【0108】

50

まず、システムリセット信号は、所定時間（例えば、システムクロック 4 周期分）の L レベル信号である。この信号が XSRST 端子に入力されると、システムリセットが開始される。図 8 には、XSRST 端子の入力信号が所定時間の L レベルを経た直後に H レベルに立ち上がっていることが示されている。ここでは、この H レベルになる直前までがシ

システムリセット信号であるものとして説明を続ける。

#### 【0109】

システムリセット信号がリセット制御回路314に入力されると、リセット制御回路314からシステムリセット信号が基本回路302内の回路に送信される。このことにより、C P U 3 0 4を含む全ての内部回路が初期化され、セキュリティモードに移行し、その後ユーザモードに移行する。図8に示す動作モードには、システムリセット信号の後にセキュリティモードに移行し、その後ユーザモードに移行することが示されている。なお、この際、リセット制御回路314のX R S T O端子からはLレベルの信号が出力される。

#### 【0110】

ここで、ユーザモードとは、R O M 3 0 6に記憶されたプログラムに従ってC P U 3 0 4が処理を実行するモードである。より具体的には、メモリマップの0 0 0 0 H番地から命令が読み出され処理が開始される。一方、セキュリティモードとは、ユーザモードに移行する前のモードであり、ユーザモードにおいてR O M 3 0 6に記憶されたプログラムに従ってC P U 3 0 4を正常に動作させるためのセキュリティチェック処理が行われるモードである。

#### 【0111】

セキュリティチェック処理では、R O M 3 0 6のチェックや、内蔵レジスタのチェック等が実行される。なお、ここで異常がある場合、C P U 3 0 4の動作は停止される。

#### 【0112】

このセキュリティチェック処理に続いて、固定延長処理とランダム延長処理が実行される。固定延長処理とは、セキュリティモードを、設定した固定時間分延長する処理である。また、ランダム延長処理とは、セキュリティモードを、設定した時間範囲内でランダムな時間分延長する処理である。これらの固定時間、およびランダム時間は、上述したプログラム管理エリアにおいて設定することができる。

#### 【0113】

上記固定延長処理が終了すると、X R T S O端子からHレベルの信号が出力される。図8には、X R S T O端子の信号が、固定延長処理の終了時のタイミングでLレベルからHレベルへの立ち上がりっていることが示されている。この信号により、マイクロプロセッサ3 0 0 0の周辺回路の状態は初期化される。

#### 【0114】

固定延長処理に続き、ランダム延長処理が終了すると、セキュリティモードからユーザモードに移行し、遊技制御用のプログラム（具体的には、後述する主制御部メイン処理）が実行される。

#### 【0115】

ここで、上記構成の効果について説明する。

#### 【0116】

遊技台の制御は乱数生成回路318において生成される乱数を用いて行われる。しかし、この乱数は、乱数テーブルや所定の演算によって生成されるものであるため、一見ランダムであっても規則性を有するものである。こうした規則性を排除するために例えば入賞回数のような規則性のない要素を利用することが考えられるが、電源投入直後のような遊技が進行していない場合こうした要素は利用できない。また、ノイズのような規則性のない要素を利用する場合、このノイズが検知できないレベルであると利用することができない。このような理由から、電源投入後や、システムリセット直後の状態は規則性がより顕著になる期間であり、不正のターゲットになりやすい。

#### 【0117】

基本回路302でシステムリセットが実行される場合、内部の回路でどのような信号の送受信が行われているかは不明である。しかし、基本回路302の外部に接続された回路に対する信号の送受信は測定することが可能である。さらに、システムリセット時には基本回路302の外部の回路にリセット信号を送信する。仮に、外部の回路に対するリセット信号の出力と同時に、遊技制御用プログラムを開始させた場合、システムリセット直後

10

20

30

40

50

にどのような信号のやり取りがされているかが分析され、その規則性に基づいて不正が行われる虞がある。また、リセット信号の出力と同時にとも、遊技制御用プログラムが開始されるまでの間が一定期間であれば、同様の不正が行われる虞がある。

#### 【0118】

上記のシステムリセットでは、X R S T O 端子から外部の回路にリセット信号が出力されるが、その後ランダム延長処理により、ユーザモードの開始までの期間をランダムに変化させている。この構成により、上記のような不正を防止することができる。

#### 【0119】

なお、設定によりW D T 3 1 4 1 がタイムアウトになった場合や、指定エリア外走行した場合にも、上記システムリセットを実行させることができる。本実施形態では、システムリセットではなくユーザリセットを実行させるように設定している。10

#### 【0120】

続いて、図9を用いて、リセットが実行された場合の処理の流れについて説明する。同図は、リセットの流れを示すフローチャートである。このフローチャートは、リセット制御回路314にシステムリセット信号が入力された場合、W D T 3 1 4 1 がタイムアウトになった場合、あるいは指定エリア外走行を検知した場合に、基本回路302の各回路で実行される処理である。

#### 【0121】

最初のステップS H 0 1では、実行されるリセット動作が、システムリセット動作か否か判定される。基本回路302で実行されるリセット動作には、システムリセット動作(図8参照)とユーザリセット動作の2つがある。ここで、システムリセット動作を実行する場合には、ステップS H 0 3に進む。また、システムリセット動作でないリセット動作、すなわちユーザリセット動作を実行する場合には、ステップS H 1 1に進む。20

#### 【0122】

ステップS H 0 3では、第1内部回路初期化処理が実行される。この第1内部回路初期化処理は、C P U 3 0 4のコアや内蔵レジスタ(タイマ回路311、カウンタ回路312、パラレル入力ポート3102、R A M 3 0 8アクセスプロテクトレジスタ、割込み制御回路3100、乱数生成回路318を制御するレジスタ)の値を初期化する。この第1内部回路初期化処理が終了すると、ステップS H 0 5に進む。

#### 【0123】

ステップS H 0 5では、セキュリティチェック処理が実行される。このセキュリティチェック処理では、ユーザプログラムを基に計算された認証コード(R O M 3 0 6のプログラム管理エリアに記憶)が正しいか否か再計算を行う。認証コードが正しい場合にはステップS H 0 7に進み、そうでない場合にはC P U 3 0 4の動作を停止させる。30

#### 【0124】

ステップS H 0 7では、固定延長処理が実行される。この固定延長処理では、予め設定した固定時間(例えば、R O M 3 0 6のプログラム管理エリア内のセキュリティ時間設定の0~2ビットを用いて設定)だけセキュリティモードを延長する。例えば、nをプログラム管理エリアに設定された時間とし、システムクロックをS C L Kとした場合に、 $3n \times 2^{24} / S C L K$ 秒だけ延長する。なお、この延長時間の経過時にX R S T O端子からリセット信号を出力させる。その後ステップS H 0 9に進む。40

#### 【0125】

ステップS H 0 9では、ランダム延長処理が実行される。このランダム延長処理では、予めランダムに選択されたランダム時間(例えば、管理エリア内のセキュリティ時間設定の3~4ビットを用いて設定)だけセキュリティモードを延長する。例えばショートモードが設定されている場合には $0 \sim S \mu$ 秒、ミドルモードが設定されている場合には $0 \sim M \mu$ 秒、ロングモードが設定されている場合には、 $0 \sim L \mu$ 秒それぞれ延長する( $S < M < L$ )。この処理が終了するとユーザモードに移行し、C P U 3 0 4は、メモリマップの0000H番地から処理を開始する。本実施形態では、主制御部300のメイン処理が開始されることになる。50

**【 0 1 2 6 】**

一方、ステップ S H 0 1 で、ユーザリセット動作を実行する場合に進むステップ S H 1 1 では、第 2 内部回路初期化処理が実行される。この第 2 内部回路初期化処理は、C P U 3 0 4 のコアや内蔵レジスタ（タイマ回路 3 1 1、カウンタ回路 3 1 2、パラレル入力ポート 3 1 0 2、R A M 3 0 8 アクセスプロテクトレジスタ、割込み制御回路 3 1 0 0）の値を初期化する。ただし、乱数生成回路 3 1 8 を制御するレジスタの値はリセット前の状態が維持される。この第 2 内部回路初期化処理が終了すると、ユーザモードに移行し、C P U 3 0 4 は、メモリマップの 0 0 0 0 H 番地から処理を開始する。本実施形態では、主制御部 3 0 0 のメイン処理が開始されることになる。

**【 0 1 2 7 】**

10

&lt; 亂数生成回路 &gt;

次に、図 1 0 を用いて、図 6 に示す基本回路 3 0 2 の乱数生成回路 3 1 8 の詳細について説明する。同図は、図 6 に示す乱数生成回路 3 1 8 の内部構成図である。

**【 0 1 2 8 】**

乱数生成回路 3 1 8 は、それぞれ異なる乱数を生成する 4 つの乱数生成チャンネル C H 1 ~ C H 4 を備えている。なお、各チャンネル回路の内部構成は同一であるため、図 1 0 では、1 つの乱数生成チャンネル C H 1 を示し、残りの乱数生成チャンネル C H 2 ~ C H 4 については、図示を簡略化している。以下の説明では、この乱数生成チャンネル C H 1 を中心に乱数生成回路 3 1 8 について説明する。

**【 0 1 2 9 】**

20

乱数生成回路 3 1 8 は、初期設定レジスタ 3 1 8 1 と、周波数監視回路 3 1 8 2 と、乱数更新回路 3 1 8 3 と、乱数監視回路 3 1 8 4 と、ノイズフィルタ 3 1 8 5 と、ソフトラッチレジスタ 3 1 8 6 と、ラッチ選択レジスタ 3 1 8 7 と、乱数レジスタ 3 1 8 8 と、乱数ラッチフラグレジスタ 3 1 8 9 と、乱数割込み制御レジスタ 3 1 8 0 を備えている。なお、周波数監視回路 3 1 8 2 および乱数監視回路 3 1 8 4 は、本発明の更新異常検出手段の一例に相当する。

**【 0 1 3 0 】**

初期設定レジスタ 3 1 8 1 には、R C K 端子からの外部クロック信号とシステムクロック（内部クロック信号）のうち、いずれのクロック信号を乱数更新回路 3 1 8 3 で使用するかを決めるクロック選択情報が、プログラム管理エリア内の情報に基づいて設定される。R C K 端子からの外部クロック信号とシステムクロック（内部クロック信号）は乱数更新回路 3 1 8 3 の手前に設けられたマルチプレクサに入力される。初期設定レジスタ 3 1 8 1 が上記クロック選択情報に従って更新クロック選択信号をこのマルチプレクサに入力することにより、この更新クロック選択信号によって選択されたクロック信号が乱数更新回路 3 1 8 3 に入力されるようになっている。なお、外部クロック信号が選択されている場合、所定の分周比（この例では、1 / 2）で分周されたクロック信号が乱数更新回路 3 1 8 3 に入力される。なお、分周されたクロック信号が、内部クロックよりも低い周波数でない場合には使用することができない。なお、本実施形態では、外部クロック信号が選択されているものとして説明を続ける。

30

**【 0 1 3 1 】**

40

周波数監視回路 3 1 8 2 は、内部クロック信号および外部クロック信号の周期を監視し、この周期が一定でなくなった場合に、クロック信号に異常があることを示す情報を、内部情報レジスタ 3 1 0 1 に出力する。

**【 0 1 3 2 】**

乱数更新回路 3 1 8 3 は、初期設定レジスタ 3 1 8 1 によって選択されたクロック信号が入力され、このクロック信号の周期に従って乱数を更新する。更新した乱数の値は、乱数監視回路 3 1 8 4 および乱数レジスタ 3 1 8 8 にそれぞれ出力される。この乱数更新回路 3 1 8 3 の詳細については、図 1 2 ~ 図 1 5 を用いて後述する。

**【 0 1 3 3 】**

乱数監視回路 3 1 8 4 は、乱数更新回路 3 1 8 3 からの入力に基づいて、乱数が正常に

50

更新されているか否かを監視する。乱数の更新に異常がある場合、この乱数の更新に異常があることを示す情報を、内部情報レジスタ3101に出力する。

#### 【0134】

なお、上記の説明では、乱数生成回路318の内部に周波数監視回路3182および乱数監視回路3184が設けられている構成であったが、乱数生成回路318の外部に設けてもよい。また、上記の説明では、乱数更新回路3183とは別に周波数監視回路3182および乱数監視回路3184が設けられている構成であったが、乱数更新回路3183の内部にこれらの回路を設けてもよい。

#### 【0135】

ノイズフィルタ3185には、P0端子～P3端子からの入力が、パラレル入力ポート3102を介してラッチ信号として入力される。なお、図10では、P3端子、およびそのP3端子に接続された回路等は図示省略している。上述のごとく、P0端子には、第1特図始動口230への入球を検出する球検出センサからの信号が入力され、P1端子には、第2特図始動口232への入球を検出する球検出センサからの信号が入力され、P2端子には、普図始動口228への入球を検出する球検出センサからの信号が入力される。さらに、ノイズフィルタ3185には、初期設定レジスタ3181によって選択されたクロック信号が入力される。このクロック信号を利用して、P0端子～P3端子からの入力に生じるノイズを除去した上で、ラッチ信号を検出する。このラッチ信号が検出されると、ハードラッチ信号が乱数レジスタ3188の手前に設けられたマルチプレクサに出力される。なお、このノイズ除去の詳細については、図11を用いて後述する。

10

20

#### 【0136】

ソフトラッチレジスタ3186には、乱数レジスタ3188から乱数をラッチすることを示す情報がCPU304からの指示によって適宜設定される。この情報が、ソフトラッチ信号として乱数レジスタ3188の手前に設けられたマルチプレクサに出力される。

#### 【0137】

ラッチ選択レジスタ3187には、乱数レジスタ3188の手前に設けられたマルチプレクサからハードラッチ信号とソフトラッチ信号の何れを出力させるか、すなわち、乱数レジスタ3188にどちらのラッチ信号を入力するのかを示す情報が、CPU304からの指示によって適宜設定される。この情報を設定することにより、ハードラッチ信号とソフトラッチ信号を適宜使用して、乱数を取得することができる。

30

#### 【0138】

乱数レジスタ3188には、3つの信号が入力される。1つ目の信号は、乱数更新回路3183から出力された乱数を表す信号である。2つ目の信号は、手前に設けられたマルチプレクサから出力された乱数ラッチ信号（ハードラッチ信号とソフトラッチ信号のうち、ラッチ選択レジスタ3187で設定された信号）である。3つ目の信号は、乱数の読み取りを示すリード信号である。

#### 【0139】

乱数レジスタ3188には、乱数更新回路3183によって更新された乱数を示す信号が常に入力されている。ここで、乱数ラッチ信号が入力されると、この入力タイミングにおける乱数が乱数レジスタ3188内にラッチ（保持）される。このとき、乱数レジスタ3188からは、乱数がラッチされていることを示すセット信号が、乱数ラッチフラグレジスタ3189に出力される。このときCPU304は、ラッチされている乱数を取得することができる。なお、CPU304により乱数が取得されると、乱数レジスタ3188にリード信号が入力される。この信号により新たな乱数ラッチ信号が入力された場合に乱数をラッチすることを許容する許容状態となる。換言すれば、一度乱数をラッチすると、リード信号が入力されるまで新たに乱数をラッチすることができない非許容状態となる。なお、リード信号が入力されてもラッチされている乱数は保持し続けるため、CPU304はラッチされている同一のタイミングでラッチされた乱数を何度でも取得することができる。このように構成することで乱数ラッチ信号を出力するセンサ回路におけるチャタリングの影響を押さえることができる。なお、リード信号が入力されたことを示すクリア信

40

50

号が乱数ラッチフラグレジスタ 3189 に出力される。また、図 10 に示すように、乱数レジスタ 3188 が複数あることにより、同じ乱数更新回路から生成された乱数を様々なタイミングで取得することができる。

#### 【0140】

乱数ラッチフラグレジスタ 3189 には、乱数レジスタ 3188 に乱数がラッチされているか否かを示す情報が記憶される。

#### 【0141】

乱数割込み制御レジスタ 3180 には、乱数レジスタ 3188 に乱数が保持された際に割込み制御回路に割込みを発生させるか否かを示す情報が設定される。この情報は乱数レジスタ 3188 毎に設定することができる。例えば、第 1 特図始動口 230 への入球により乱数発生チャンネル CH1 の乱数がラッチされた場合には、割込みを発生させ、第 2 特図始動口 232 への入球により乱数発生チャンネル CH2 の乱数がラッチされた場合には、割込みを発生させない、というような設定をすることができる。10

#### 【0142】

上記説明した乱数生成回路 318 を用いて、本実施形態では、普図始動口 282、第 1 特図始動口 230、第 2 特図始動口 232 のそれぞれに入球したタイミングで乱数を取得する。なお、任意のタイミングで CPU304 に乱数を取得させるように、プログラムを実行させることもできる。さらに異なる乱数生成チャンネルを使用してそれぞれ独立の乱数を取得し、それぞれのチャンネル毎に乱数生成範囲の最大値を設定することができる。

#### 【0143】

なお、本実施形態では、個別のチャンネルに対して乱数生成範囲を変更することができ、設定されていない場合には所定の最大値（例えば 65535）が適用される例について説明したが、これ以外に例えば、乱数生成範囲を変更する場合に全てのチャンネルに対して乱数生成範囲を設定することを必要とする構成であってもよい。20

#### 【0144】

なお、普図始動口 282 に入球したタイミングで取得された乱数は、後述する普図当選乱数として用いられる。また、第 1 特図始動口 230 に入球したタイミングで取得された乱数は、加工（例えば、乱数生成回路とは異なる回路（例えば、基本回路 302 やカウンタ回路 312）でカウントアップ（ダウン）される値を乱数に加算（減算）する処理など）されて、後述する特図 1 当選乱数として用いられる。さらに、第 2 特図始動口 232 に入球したタイミングで取得された乱数は、加工されて、後述する特図 2 当選乱数として用いられる。30

#### 【0145】

なお、乱数の加工は、第 1 特図始動口 230 および第 2 特図始動口 232 に入球したタイミングで取得される乱数に限らず、他の契機（例えば、普図始動口 282 へに入球したタイミングなど）によって取得される乱数に対して行ってもよい。さらに、上述した乱数生成範囲の最大値を設定する場合においては、設定した最大値に応じた加工（例えば、この最大値を超えない値を乱数に加算する処理など）すれば良い。

#### 【0146】

また、乱数の加工は必ずしも行う必要はないが、乱数の加工を行うことは乱数の狙いうちの防止に有効に働く。例えば加工した後の乱数が更新されたか否かを CPU304 によって監視した場合、乱数生成回路 318 内での乱数の更新が正常に行われているか否かを正確に判断することができない。このように、乱数を加工する場合には、上述の乱数監視回路 3184 による乱数の更新の監視がより有効に働くこととなる。40

#### 【0147】

続いて、図 11 を用いてノイズフィルタ 3185 の動作について説明する。同図は、図 10 に示すノイズフィルタ 3185 による処理の一例を示す図である。

#### 【0148】

上述したように、ノイズフィルタ 3185 には、P0 端子～P3 端子からの入力が、パラレル入力ポート 3102 を介してラッチ信号として入力され、初期設定レジスタ 31850

1 によって選択されたクロック信号が入力される。このノイズフィルタ 3185 は、例えば図 11 に示すように、クロック信号のダウンエッジ (H レベルから L レベルへの立ち下り信号) が 4 回連続で入力されるまで、P0 端子～P3 端子からの入力信号が H レベルであれば、ハードウェアラッチ信号を出力するように構成されている。単純に信号の立ち上がりおよび立ち下りだけを基にハードウェアラッチ信号を出力すると、ノイズが入った場合にもハードウェアラッチ信号が出力されてしまう。このため、上記のようにクロック信号を用いて、一定期間のセンサ信号を検出させることで、ノイズによりハードウェアラッチ信号が出力されてしまわないように構成されている。

#### 【0149】

上記説明では、P0 端子～P3 端子からの入力によりハードラッチ信号を出力させる例について説明したが、例えば、P0 端子～P3 端子からの入力を一度 C P U 304 で受け付けた上で乱数を取得する方法もある。この場合には、ハードラッチ信号ではなく、ソフトラッチレジスタ 3186 から出力されたソフトラッチ信号により、乱数をラッチされることになる。この場合、上記ノイズフィルタによる処理と同様の処理が C P U 304 により実行される。すなわち、P0 端子～P3 端子からの入力が所定期間継続したか否かを判定し、これを満たす場合に P0 端子～P3 端子からの入力が正しく行われたと判定する。その後、ソフトラッチ信号を出力するようにソフトラッチレジスタ 3186 を設定する。

#### 【0150】

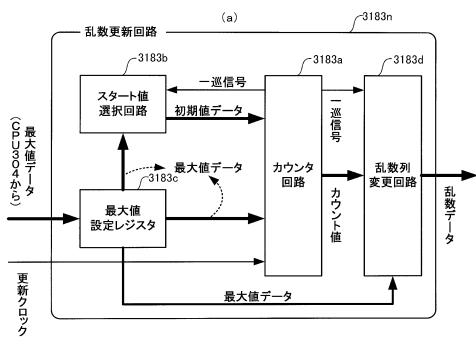

次に、図 12 を用いて、図 10 に示す乱数更新回路 3183 の詳細について説明する。同図は、図 10 に示す乱数更新回路 3183 の詳細を示す図である。

#### 【0151】

図 12 (a) に示す乱数更新回路 3183 は、カウンタ回路 3183a と、スタート値選択回路 3183b と、最大値設定レジスタ 3183c を備えている。なお、図 10 では、乱数更新回路 3183 に対して外部クロック信号および内部クロック信号のいずれかが乱数更新のための更新クロック信号として入力されることが示されているが、この図 12 に示す乱数更新回路 3183 には、さらに C P U 304 から最大値データが入力される。

#### 【0152】

カウンタ回路 3183a からは、乱数（乱数データ）が出力される。この乱数の初期値は、スタート値選択回路 3183b に設定されている。この初期値には、固定値（例えば 0）、プログラム管理エリア内に記憶されている基本回路 302 の ID ナンバーを基にした値、および、乱数生成範囲内で抽選された値のいずれかが設定される。

#### 【0153】

カウンタ回路 3183a には、更新クロック信号の 1 クロック毎に 1 が加算されるカウンタが設けられており、このカウンタの値に、スタート値選択回路 3183b から入力された乱数の初期値を加えた値を乱数として出力する。

#### 【0154】

カウンタ回路 3183a から出力される乱数の最大値は、最大値設定レジスタ 3183c に設定されている。なお、乱数の最大値は、C P U 304 からの命令に従って最大値設定レジスタ 3183c に設定される。図 12 (b) には、この最大値が設定されている 16 ビットのレジスタが示されている。C P U 304 から最大値を設定する命令がない場合の初期値は、FFFFFH (65535) である。なお、この最大値設定レジスタ 3183c の変わりに、例えば、ROM 306 のプログラム管理エリア内に最大値を設定する領域を設け、設定された最大値を参照する構成であってもよい。

#### 【0155】

カウンタ回路 3183a は、出力する乱数が最大値を超えた場合、この最大値に 1 を加えた値を減算した上で、この値を乱数として出力する。例えば最大値が 65535 の場合において、初期値とカウンタの値を足した値が、65534、65535、65536、65537 の順に更新されるとすると、出力される乱数は、65534、65535、0 (65536 - (65535 + 1))、1 (65537 - (65535 + 1)) のようになる。すなわち、最大値を超えると出力される乱数が 0 に戻ることになる。

10

20

30

40

50

**【 0 1 5 6 】**

また、カウンタ回路 3 1 8 3 a の内部に設けられたカウンタの値が、最大値レジスタ 3 1 8 3 c に設定された最大値になると、このカウンタの値が 0 にクリアされるとともに、カウンタ回路 3 1 8 3 a からスタート値選択回路 3 1 8 3 b に乱数の出力が一巡したことを示す信号（一巡信号）が出力される。この一巡信号を受けたスタート値選択回路 3 1 8 3 b では、乱数の初期値が更新される。この際更新される初期値が、最大値設定レジスタ 3 1 8 3 c に設定されている乱数の最大値を超えている場合、例えば、固定値を用いたり、一度現在の乱数の最大値を乗じてから設定可能な乱数生成範囲の最大値（6 5 5 3 5）で除算した値を用いることにより、乱数の最大値を超えない値（乱数生成範囲内の値）が初期値として再設定される。無論、最初からこの再設定方法などを用いて、乱数生成範囲内の値が初期値として設定されるようにしてもよい。

**【 0 1 5 7 】**

なお、本実施形態では、最大値設定レジスタ 3 1 8 3 c に設定された最大値は、カウンタ回路 3 1 8 3 a からの出力が一巡した時点で自動的に更新されるが、例えば C P U 3 0 4 からの更新命令が来た時点で更新されるようにしてもよい。

**【 0 1 5 8 】**

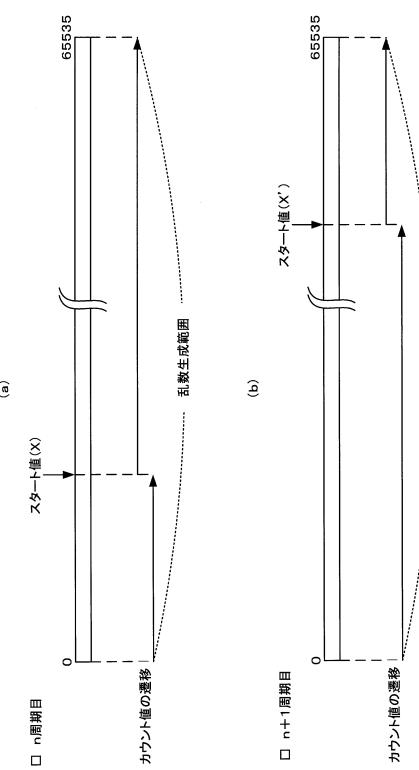

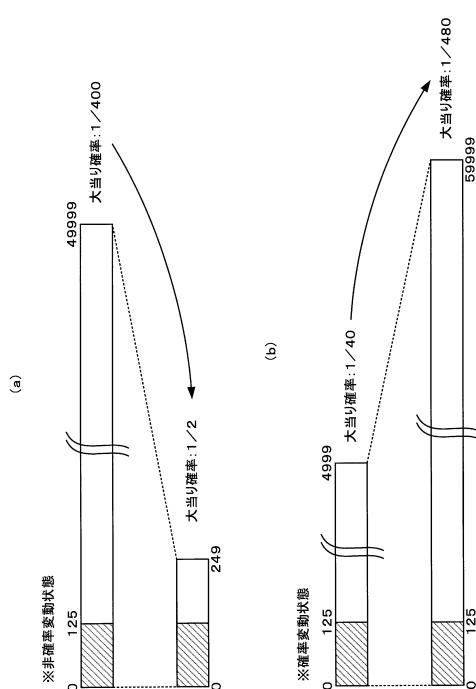

ここで、上記の乱数生成の範囲を図 1 3 および図 1 4 を用いて説明する。図 1 3 は、乱数生成範囲の最大値が設定されていない場合（デフォルトの状態）において出力される乱数の範囲を示す図である。また、図 1 4 は、図 1 3 とは異なる最大値が設定された場合に出力される乱数の範囲を示す図である。

**【 0 1 5 9 】**

まず、図 1 3 ( a ) では n 周期目（n - 1 回目の一巡信号が出力された直後）の状況について説明する。図 1 3 ( a ) には、0 ~ 6 5 5 3 5 の乱数生成範囲が示されている。また、出力される乱数の初期値がスタート値（X）として示されている。

**【 0 1 6 0 】**

乱数更新回路 3 1 8 3 からは、更新クロックの 1 クロック毎に乱数が更新されて出力される。より具体的には、最初にスタート値（X）が出力され、その後 1 クロック毎に、X + 1、X + 2 の順で更新された乱数が出力される。この乱数の値が乱数生成範囲の最大値である 6 5 5 3 5 になると、上記説明した処理によって、次に出力される乱数は 0 に戻る。その後、1、2、の順で更新された乱数が出力され、X - 1 が出力された時点でこの乱数生成範囲を一巡したことになる。なお、このとき、乱数更新回路 3 1 8 3 内のカウンタ回路 3 1 8 3 a のカウンタの値は最大値と同じ値になっている。スタート値選択回路 3 1 8 3 b に乱数の出力が一巡したことを示す信号（一巡信号）が出力される。

**【 0 1 6 1 】**

続いて 1 クロックが入力されると、乱数更新回路 3 1 8 3 の出力は n + 1 周期目（n 回目の一巡信号が出力された直後）に入る。この n + 1 周期目の状況について、図 1 3 ( b ) を用いて説明する。まず、乱数更新回路 3 1 8 3 内のカウンタ回路 3 1 8 3 a のカウンタの値は 0 にクリアされる。また、スタート値選択回路 3 1 8 3 b では、新たな初期値が設定される。図 1 3 ( b ) には、この新たな初期値がスタート値（X'）として示されている。この新たな初期値と、カウンタ回路 3 1 8 3 a のカウンタの値により、上記説明した流れと同様の流れで乱数が出力される。

**【 0 1 6 2 】**

次に、図 1 4 ( a ) では、図 1 3 に示す乱数生成範囲の最大値よりも小さい最大値が設定された場合の n 周期目（n - 1 回目の一巡信号が出力された直後）の状況について説明する。図 1 4 ( a ) には、0 ~ 6 5 5 3 5 のうち、設定された最大値によって図 1 3 ( a ) に示す乱数生成範囲よりも狭くなった乱数生成範囲が示されている。なお、出力されない乱数の範囲が左下がりのハッチングで示されている。また、出力される乱数の初期値がスタート値（Y）として示されている。

**【 0 1 6 3 】**

図 1 3 を用いて説明した状況と同様に、乱数更新回路 3 1 8 3 からは、最初にスタート

10

20

30

40

50

値（Y）が出力され、その後1クロック毎に、Y+1、Y+2の順で更新された乱数が出力される。この乱数の値が設定された最大値になると、上記説明した処理によって、次に出力される乱数は0に戻る。すなわち、左下がりのハッチングで示された範囲の乱数は出力されない。その後、1、2、の順で更新された乱数が出力され、Y-1が出力された時点での乱数生成範囲を一巡したことになる。なお、このとき、乱数更新回路3183内のカウンタ回路3183aのカウンタの値は設定された最大値と同じ値になっている。スタート値選択回路3183bに乱数の出力が一巡したことを示す信号（一巡信号）が出力される。

#### 【0164】

続いて1クロックが入力されると、乱数更新回路3183の出力はn+1周期目（n回目の一巡信号が出力された直後）に入る。このn+1周期目の状況について、図14（b）を用いて説明する。図13（b）を用いて説明した場合と同様、乱数更新回路3183内のカウンタ回路3183aのカウンタの値は0にクリアされる。また、スタート値選択回路3183bでは、新たな初期値が設定される。図14（b）には、この新たな初期値がスタート値（Y'）として示されている。この新たな初期値と、カウンタ回路3183aのカウンタの値により、上記説明した流れと同様の流れで乱数が出力される。

#### 【0165】

なお、上記のように乱数生成チャンネルの最大値を適切に設定する以外に、例えば、ある乱数生成チャンネルでは乱数の最大値が65535であるが、別の乱数生成チャンネルでは乱数の最大値が255である、というように、チャンネル毎に乱数生成範囲を予め異ならせておいてもよい。この場合には、必要とされる乱数生成範囲に応じてチャンネルを選択すればよい。この場合には、最大値設定レジスタの容量削減や、最大値設定の処理負担を軽減することができる。さらに、予め設定可能な最大値を複数設定した上で、これらの中から適切な最大値を選択して設定するようにしても、最大値設定レジスタの容量削減や、最大値設定の処理負担を軽減することができる。

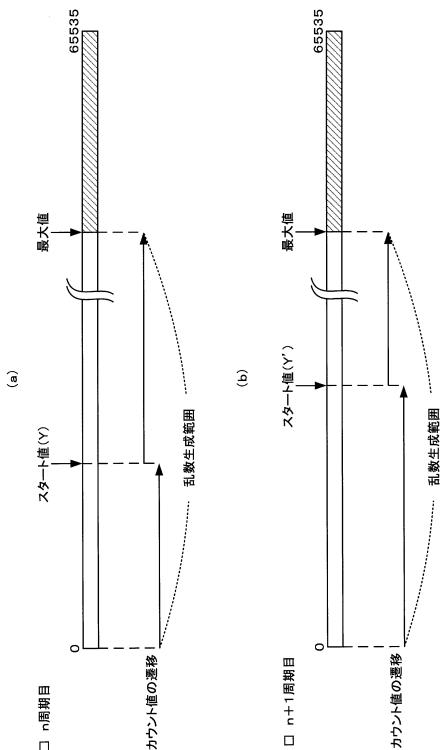

#### 【0166】

以上、乱数更新回路3183の乱数の出力について説明した。以下この乱数更新回路3183の変形例について図15を用いて説明する。同図は、最大値と最小値を設定した乱数生成範囲において、乱数を取得することができる範囲を示す図である。

#### 【0167】

図12から図14の例では、乱数生成範囲の最大値を変更する例について説明したが、例えば、最小値を設定できるものであってもよい。さらに、最大値だけでなく最小値を設定するレジスタを用意し、図15（a）に示すように、最小値、最大値を設定し、乱数生成範囲を設定できるものであってもよい。加えて、図15（b）に示すように、複数の乱数生成範囲を設定できるものであってもよい。すなわち、出力される乱数の範囲を設定出来る構成であればよい。また、上記説明では、説明を分かり易くするため出力される乱数が1ずつ増加する例について説明したが、これ以外の乱数の更新方法であってもよい。

#### 【0168】

以下、図16を用いて本実施形態の遊技台で使用される乱数と、その主な導出源について説明する。同図は、本実施形態の遊技台で使用される乱数の導出源を表で示す図である。なお、この図で示される各乱数は、後述のフローチャートで用いられる。

#### 【0169】

まず、特図1当選乱数、特図2当選乱数、および普図当選乱数は、上記乱数生成回路318の乱数生成チャンネルCH1～CH4によって生成される乱数が基になる。この値を必要に応じて適宜加工してこれらの乱数として使用する。

#### 【0170】

大当たり用特図乱数、小当たり用特図乱数、およびハズレ用特図乱数は、後述する主制御部タイマ割込み処理において生成される。すなわちこれらの乱数は、所謂ソフトウェア乱数である。なお、これらの乱数を生成する際に用いられる初期値生成用乱数は、主制御部メイン処理および主制御部タイマ割込み処理で生成される。

10

20

30

40

50

**【0171】**

特図変動時間決定用乱数、および普図変動時間決定用乱数は、カウンタ回路312の値を乱数として用いる。本実施形態のカウント回路312は、基本回路302のシステムクロックの他、上記タイマ回路からのタイムアウト信号、メモリの読み書き信号、メモリリクエスト信号、外部入出力の信号等もカウンタの対象として用いることができる。このため、これらを組み合わせることで規則性のない値を導出させ、上記の乱数に使用している。

**【0172】**

演出用乱数は、主制御部メイン処理および主制御部タイマ割込み処理で生成される。

**【0173】**

次に、図17を用いて、図6に示す割込み制御回路3100に設けられた内部情報レジスタ3101の詳細について説明する。同図は、図6に示す割込み制御回路3100に設けられた内部情報レジスタ3101の一部を示す図である。

**【0174】**

上述したように、内部情報レジスタ3101には、乱数生成回路318で乱数更新周期を決める外部クロック（カウントクロック）の周期の異常、および生成された乱数の異常、さらに、直前に発生したユーザリセットのリセット要因の情報が格納される。図17(a)には、内部情報レジスタ3101のうち、乱数生成回路318の異常を示す情報が記憶される範囲が示されている。この範囲は8ビットで構成されており、図17(b)には、これらの各ビットがどのような情報を示すものかが表で示されている。CPU304は、後述するタイマ割込みが実行される度にこの内部情報レジスタ3101の内容を確認する(図28のステップS235a)。この内容は、異常が発生した場合に遊技の進行を止める等の処理を行うか否かの判定に用いられる。例えば、本実施形態では、乱数生成回路318で異常が検出されると、入賞受付処理が実行されないように構成されている(図28のステップS235cおよび図30参照)。この他、球の打ち出しを行わないようにしたり、払出しを行わないようにしたり、あるいは、変動タイマの減算を行わないようにしてもよい。特に、乱数更新に異常があった場合、乱数更新回路3183に大電流が流れている状態(ラッチアップ状態)である可能性があるため、一度電源をオフにすることを報知するようにしてもよい。

**【0175】**

ビット番号0は、乱数生成回路318の外部クロック(更新クロック)の異常を示すビットであり、0は異常なし、1は異常ありを示す。

**【0176】**

ビット番号1～4は、乱数生成回路318で生成された乱数の異常を、各チャンネル毎に示すビットであり、0は異常なし、1は異常ありを示す。

**【0177】**

ビット番号5～7は、不使用(0に固定)である。

**【0178】**

内部情報レジスタ3101の値が1である場合、CPU304から読み出されると0に設定(クリア)される。なお、内部情報レジスタはCPU304に一度に読み出されるため、内部情報レジスタ3101が保持している値を0に設定(クリア)したい場合は、CPU304に内部情報レジスタ3101の値を読み出した後に読み出した値を破棄すれば良い。

**【0179】**

また、上述の通り、システムリセットおよびユーザリセットのいずれかの処理が実行された場合に、この内部情報レジスタは、CPU304から読み出された場合と同様に各ビットは0に設定(クリア)されることとなる。

**【0180】**

以上、乱数生成回路318の異常がどのように記憶されているかについて説明したが、この例と同様に上記リセット要因を示す情報についても、内部情報レジスタ3101に記

10

20

30

40

50

憶されている。なお、上記説明では、乱数生成チャンネルの異常をビット番号1～4によってそれぞれのチャンネル毎に表していたが、1つのビットによっていずれかのチャンネルで異常が起きたか否かを表すようにしてもよい（全てのチャンネルで共通にしてもよい）。なお、本実施形態では、内部情報レジスタ3101が割込み制御回路3100内に設けられているが、他の回路に設けられているものであってもよい。

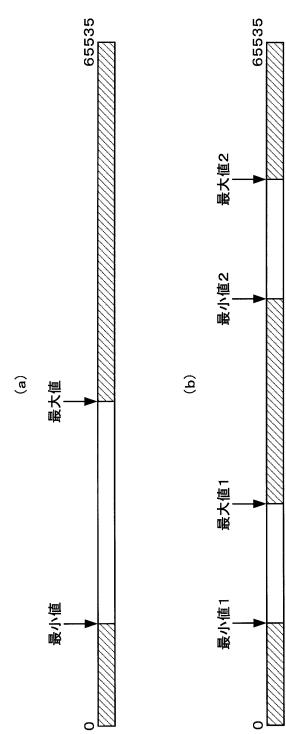

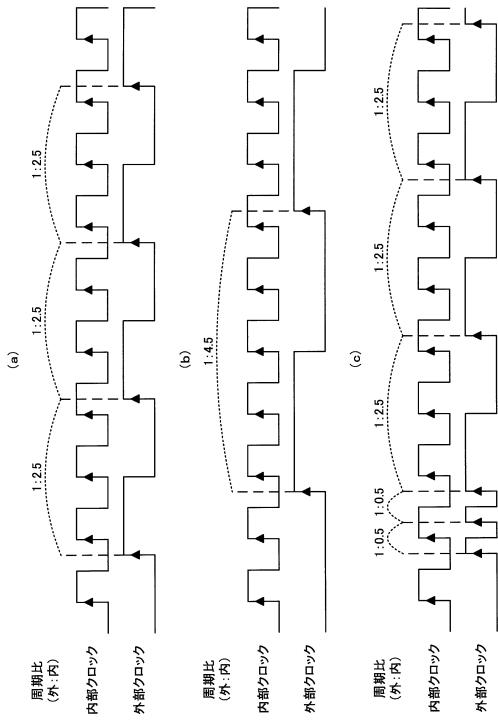

#### 【0181】

次に、図10に示す周波数監視回路3182における異常の検出例について、図18を用いて説明する。同図は、周波数監視回路3182における異常の検出例を示す図である。図18には、一番上からそれぞれ、正常時の動作、異常時の動作例1（異常時1）、異常時の動作例2（異常時2）が示されている。これらの例では、基本回路302の内部クロックと、乱数生成回路318に入力される外部クロック（RCK）に加え、外部クロックの1周期に対する内部クロックの周期の比率が示されている。

10

#### 【0182】

この検出動作では、外部クロックと内部クロックの周期の比率を監視し、この比率が変化した場合を異常として検出する。

#### 【0183】

図18（a）に示す正常時の例では、外部クロックの1周期の間に内部クロックが2.5周期ある状態が継続している。すなわち、外部クロックと内部クロックの周期の比率が変化しないため、異常を示す情報は出力されない。

#### 【0184】

次に、図18（b）に示す異常時の動作例1（異常時1）では、外部クロックの1周期の間に内部クロックが4.5周期ある状態が示されている。図18（a）に示す状態からこの図18（b）に示す状態になった場合には、この時点で異常を示す情報が出力される。

20

#### 【0185】

次に、図18（c）に示す異常時の動作例2（異常時2）の最初には、外部クロックの1周期の間に内部クロックが0.5周期ある状態が示されている。仮に、図18（a）に示す状態からこの図18（c）の最初の状態になった場合には、この時点で異常を示す情報が出力される。さらに、図18（c）には、外部クロックの1周期の間に内部クロックが0.5周期ある状態に続き、外部クロックの1周期の間に内部クロックが2.5周期ある状態が継続している。この周期の比率が変化した時点でも異常を示す情報が出力される。

30

#### 【0186】

上記の例では、外部クロックと内部クロックのいずれか一方の周期が異常になると、異常を示す情報が出力されることになる。すなわち、内部クロックを乱数の更新クロックとして使用した場合でも、異常を検出することができる。なお、外部クロックと内部クロックの比率が同じであれば、双方の周波数が変更されても異常を示す情報が出力されない。この場合、例えばプログラム管理エリア内に外部クロック又は内部クロックの周波数を示す情報を記憶させておき、この情報を用いて外部クロック又は内部クロックの異常を検出させることも可能である。なお、更新クロックの異常を検出する方法は上述した方法に限らず、更新クロックの周期の異常を検出可能な方法であれば他の方法を採用しても良い。

40

#### 【0187】

続いて、図10に示す乱数監視回路3184における異常の検出例について、図19を用いて説明する。同図は、乱数監視回路3184における異常の検出例を示す図である。この検出例では、1回の乱数の更新毎に更新前後の乱数を比較し、同じ乱数が生成されていないか否かをチェックする。仮に同じ乱数が生成されている場合には、異常を示す情報が出力される。図19（a）の例では、更新前後で同じ乱数が生成されていないため、異常を示す情報は出力されない。これに対して、図19（b）の例では、更新の途中で同じ乱数が生成されており（乱数4が2回生成されている）、この時点（2回目の4が出力された時点）で異常を示す情報が出力される。なお、上記の例では、乱数が更新される度に

50

チェックを行っているが、この乱数更新周期よりも長い所定の周期毎でチェックさせてもよい。

#### 【0188】

上記説明したように乱数生成回路318では、周波数監視回路3182と乱数監視回路3184から異常を示す情報が内部情報レジスタ3101に対して出力される。また、内部情報レジスタ3101の値は、タイマ割込み毎にCPU304によって読み出される。

#### 【0189】

このように周波数監視回路3182および乱数監視回路3184の双方を用いて乱数生成回路318の異常を監視することで、更新クロックの周波数に異常があるが、乱数の更新には異常がない異常状態（乱数監視回路3184のみでは検出できない異常状態）と、更新クロックの周波数に異常がないが、乱数の更新には異常がある異常状態の双方の異常状態を的確に把握することが可能になり、遊技制御の安定化を図ることができる。10

#### 【0190】

従来の遊技台では、遊技者に有利な抽選結果が導出されやすくなるように抽選に用いられる乱数に狙いを定めて不正が行われることがあり、遊技の公平性を担保することが困難になっている。しかし、本実施形態の遊技台によれば、上記の乱数生成318によって抽選に用いられる乱数の異常を把握したうえで対処することができるため、乱数の狙いうちを抑止して遊技の公平性を担保することができる。

#### 【0191】

なお、周波数監視回路3182および乱数監視回路3184は内部情報レジスタ3101に記憶されている情報に関わらず継続してそれぞれ監視を行っている。20

#### 【0192】

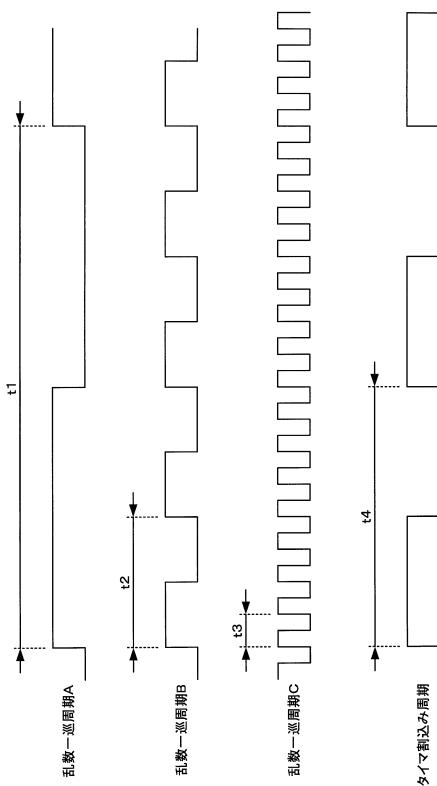

ここで、内部情報レジスタ3101の値が、乱数生成回路318により生成される乱数が一巡する周期（乱数生成範囲内の全ての値を各1回出力するのに必要な期間、以下、乱数一巡周期と称する）だけ保持され、その後クリアされる構成であった場合の問題点について図20を用いて説明する。同図は、乱数が一巡する周期とタイマ割込みの周期を比較した図である。図20の一番上には、一番下に示すタイマ割込み周期t4よりも長い乱数一巡周期t1が示されている。また、図20の上から二番目および三番目には、タイマ割込み周期t4よりも短い乱数一巡周期t2およびt3がそれぞれ示されている。

#### 【0193】

上述したように内部情報レジスタ3101の内容はタイマ割込み毎に確認される。例えば乱数一巡周期が、図20に示す乱数一巡周期t1のようにタイマ割込み周期t4よりも長い場合、内部レジスタ3101に保持された値がクリアされる前にこの値を読み取ることができる。しかし、本実施形態では、乱数生成範囲の最大値を設定するため、これに従って乱数一巡周期が短くなってしまう事態が生じ得る。例えば乱数一巡周期が、図20に示す乱数一巡周期t2およびt3のようにタイマ割込み周期t4よりも短い場合、内部レジスタ3101に保持された値を読み取る前にこの値がクリアされる場合がある。すなわち、CPU304が異常を示す情報を取得することが出来なくなる場合がある。30

#### 【0194】

本実施形態では、内部情報レジスタ3101の値が一旦セットされると、この値が読みとられるまでその値が保持される。すなわち、正常に戻ったか否かにかかわらずこの値が維持される。さらに、CPU304がこの値を読み取ると、読み取られた部分の値がクリアされるようになっている。このため、上記のように乱数一巡周期が変わってしまったとしても、内部情報レジスタ3101から異常を示す情報を取得することができる。なお、異常を示す値が読み取られた後に、異常が継続していれば再度異常を示す値がセットされる。

#### 【0195】

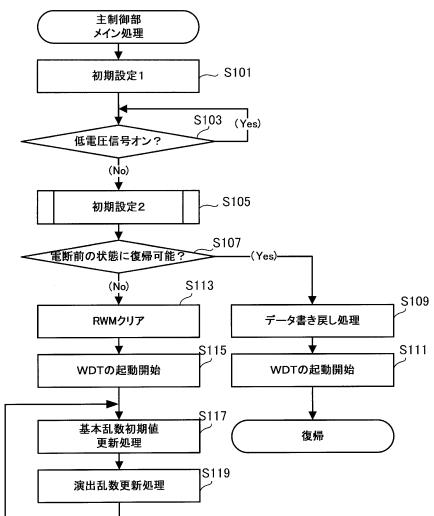

<主制御部メイン処理>

次に、図21を用いて、図4に示す主制御部300のCPU304が実行する主制御部40

50

メイン処理について説明する。なお、同図は主制御部メイン処理の流れを示すフローチャートである。

#### 【0196】

この主制御部メイン処理は上述のユーザモードにおける処理に相当し、システムリセットがかかった場合でも、ユーザーリセットがかかった場合でも実行される処理である。なお、この主制御部メイン処理は、本発明の第一の処理に相当する。図4に示す主制御部300のRAM308には、大当たり用特図1乱数カウンタ、小当たり用特図1乱数カウンタ、ハズレ用特図1乱数カウンタ、およびこれらのカウンタの特図2用のカウンタが設かれている。また、そのRAM308には、特図1の保留数、特図1当選乱数、大当たり用特図1乱数、小当たり用特図1乱数、ハズレ用特図1乱数、特図1当否判定結果、特図1決定結果、特図1変動時間、およびこれらの、保留数や乱数や結果の特図2用のものがそれぞれが記憶される。またRAM308には、当否判定(抽選)の開始を保留することができる最大数(この例では4つ)の領域に区分けされた保留記憶部が特図1と特図2で別々に用意されている。特図1の保留記憶部には、後述するように、特図1当選乱数、大当たり用特図1乱数、小当たり用特図1乱数、ハズレ用特図1乱数、および特図1変動時間決定用乱数の5つの乱数を1セットにしてこれら5つの乱数が入賞順(保留順)に1セットずつ1領域ごとに格納される。

#### 【0197】

上述したように、図4に示す主制御部300には、電源が投入されると起動信号(リセット信号)を出力する起動信号出力回路(リセット信号出力回路)340を設けている。この起動信号を入力した基本回路302のCPU304は、リセット割込によりリセットスタートしてROM306に予め記憶している制御プログラムに従って図6に示す主制御部メイン処理を実行する。

#### 【0198】

ステップS101では、初期設定1を行う。この初期設定1では、CPU304のスタックポインタ(SP)へのスタック初期値の設定(仮設定)、割込マスクの設定、I/O310の初期設定、RAM308に記憶する各種変数の初期設定等を行う。

#### 【0199】

ステップS103では、低電圧信号がオンであるか否か、すなわち、電圧監視回路338が、電源制御部660が第2副制御部500を介して主制御部300に供給している電源の電圧値が所定の値(本実施形態では9V)未満である場合に電圧が低下したことを示す低電圧信号を出力しているか否かを監視する。そして、低電圧信号がオンの場合(CPU304が電源の遮断を検知した場合)には繰り返しこのステップS103を実行し、低電圧信号がオフの場合(CPU304が電源の遮断を検知していない場合)にはステップS105に進む。なお、電源が投入された直後で未だ上記所定の値(9V)に達しない場合にも、供給電圧がその所定の値以上になるまでステップS103は繰り返し実行される。

#### 【0200】

ステップS105では、初期設定2を行う。

#### 【0201】

図22は、主制御部メイン処理における初期設定2の流れを示すフローチャートである。

#### 【0202】

まず、ステップS1051では、カウンタ回路312に最大値や更新ソースを決める数値を設定する処理等、カウンタ回路312に関する設定処理を行う。なお、後述する主制御部タイマ割込処理を定期毎に実行するための周期を決める数値をタイマ回路311に設定する処理等、タイマ回路311に関する設定処理も併せて行う。ステップS1052では、第1副制御部400への出力ポートからクリア信号を出力する処理を行い、ステップS1053に進む。ステップS1053では乱数生成回路初期設定処理を行い、次いで、ステップS1054でRAM308への書き込みを許可する設定を行って、この初期設定

2は終了になる。

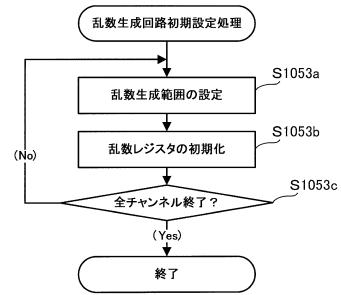

**【0203】**

図23は、ステップS1053における乱数生成回路初期設定処理の流れを示すフロー

チャートである。

**【0204】**

この乱数生成回路初期設定処理は、上述のユーザモードにおいて行われる、図10に示す乱数生成回路318の初期設定処理である。まず、乱数の取り得る範囲（乱数生成範囲）範囲の設定を行い（ステップS1053a）、ステップS1053bに進む。上述のごとく、図10に示す乱数生成回路318では、生成する乱数の最大幅は0～65535であり、この最大幅が乱数生成範囲のデフォルトになり、ここでは、図12～図15を用いて詳細に説明したように、その乱数生成範囲をデフォルトとは異なる範囲に設定することができる。図21に示す主制御部メイン処理は、リセット（システムリセットまたはユーザリセット）がかかる度に実行される処理であるため、乱数生成範囲の設定もリセットがかかる度に実行される。このようにすることで、図32、図33を用いて後述する乱数更新範囲の異常による問題を防止することができる。

10

**【0205】**

ステップS1053bでは、図10に示す乱数レジスタ3188の読み出しを行うとともに、読み出した乱数を破棄する処理を行い、ステップS1053cに進む。この処理によって、乱数生成範囲のリセットがかかるごとに乱数レジスタ3188が乱数をラッチすることを許容する許容状態になる。この許容状態においては、仮に異常の可能性がある乱数が乱数レジスタに残っている場合でもすぐに乱数を更新させることができるために、異常の可能性がある乱数の使用を防止することができる。

20

**【0206】**

本実施形態では、乱数生成回路318では、特図当選乱数の元になる乱数と普図当選乱数とを生成するが、制御状態に応じて出力チャンネルが異なる。すなわち、特図当選乱数の元になる乱数は、非確率変動中（特図低確率状態）にはチャンネルCH1から出力され、確率変動中（特図高確率状態）にはチャンネルCH2から出力される。また、普図当選乱数は、普図低確率状態（非電サポ中）にはチャンネルCH3から出力され、普図高確率状態（電サポ中）にはチャンネルCH4から出力される。なお、乱数生成回路318は、特図当選乱数そのものを生成するものであってもよいし、特図当選乱数の元になる乱数を生成するものであってもよい。また、普図当選乱数そのものを生成するものであってもよいし、普図当選乱数の元になる乱数を生成するものであってもよい。ステップS1053cでは、これら4チャンネル総てのチャンネルについてステップS1053aとステップS1053bが実行されたか否かを判定し、全チャンネルについて終了していなければ、ステップS1053aに戻り、1チャンネルごとに未了のチャンネルについて処理を行う。なお、乱数生成範囲の設定は、状態に応じて使用されているチャンネルのみを実行してもよいし、乱数生成範囲を設定されるチャンネルのみ実行するようにしてもよい。一方、全チャンネルについて終了していれば、この乱数生成回路初期設定処理は終了になる。

30

**【0207】**

本実施形態では、以上説明した乱数生成回路初期設定処理が行われると、乱数生成回路318は乱数の更新を開始する。ユーザリセットがかかった場合、乱数は更新されており、その状態で乱数生成範囲が更新されることに基づいて遅滞なく新しい乱数生成範囲で乱数が生成されるようになっている。なお、ユーザリセットがかかった場合には、一度乱数の更新を止める処理を行い、乱数生成範囲の設定を行った後に乱数の更新を再開させる処理を行うようにしてもよい。また、主制御部のタイマ割込みはこの時点では禁止されており、乱数生成回路初期設定処理はタイマ割込み許可前に行っていることになるため、新たに乱数がラッチされたとしても各種抽選に使用されることではなく、抽選処理の安定化を図ることができる。

40

**【0208】**

また、乱数生成回路318が、上記乱数生成回路初期設定処理を実行する指示をCPU

50

304から受けた場合に、乱数生成回路初期設定処理を行わないものであってもよい。すなわち、乱数生成回路318が乱数更新を行うか否かに関わらず、CPU304に乱数生成回路初期設定処理を実行する指示を行わせてもよい。この構成であれば、ユーザプログラムの解析結果と乱数生成回路318の動作が合わなくなるため、基本回路302の動作の解析が困難になり、不正を防止することができる。従って、不正により基本回路302の動作が不安定にされることなく、遊技制御の安定化を図ることができる。仮に、不正により基本回路302の動作が解析された場合、遊技者に有利な操作が行われてしまう虞があるが、上記の構成であればこのような不正が防止できるため、遊技制御の安定化を図ることができる。

#### 【0209】

10

さらに、乱数生成回路318が乱数更新を行うか否かに関わらず、CPU304に乱数生成回路初期設定処理を実行する指示を行わせた場合、ユーザリセットが実行された場合の処理を統一することができる。すなわち、ユーザリセット後に不安定な状態となった場合にも分岐処理を行わずにすむため、遊技制御の安定化を図ることができる。

#### 【0210】

なお、上述した内容はユーザリセットがかかった場合について述べたが、システムリセットがかかった場合についても同様の効果を得ることができる。

#### 【0211】

図21に示す主制御部メイン処理におけるステップS107では、電源の遮断前（電断前）の状態に復帰するか否かの判定を行い、電断前の状態に復帰しない場合（主制御部300の基本回路302を初期状態にする場合）にはRWMクリア処理（ステップS115）に進む。

20

#### 【0212】

具体的には、最初に、図2に示す電源基板182に設けたRAMクリアスイッチ180を遊技店の店員などが操作した場合に送信されるRAMクリア信号がオン（操作があったことを示す）であるか否か、すなわちRAMクリアが必要であるか否かを判定し、RAMクリア信号がオンの場合（RAMクリアが必要な場合）には、基本回路302を初期状態にすべくステップS113に進む。一方、RAMクリア信号がオフの場合（RAMクリアが必要でない場合）には、RAM308に設けた電源ステータス記憶領域に記憶した電源ステータスの情報を読み出し、この電源ステータスの情報がサスペンドを示す情報であるか否かを判定する。そして、電源ステータスの情報がサスペンドを示す情報でない場合には、基本回路302を初期状態にすべくステップS113に進み、電源ステータスの情報がサスペンドを示す情報である場合には、RAM308の所定の領域（例えば全ての領域）に記憶している1バイトデータを初期値が0である1バイト構成のレジスタに全て加算することによりチェックサムを算出し、算出したチェックサムの結果が、電断前にRAM308に設定した値と一致するか否か（チェックサムの結果が正常であるか否か）を判定する。そして、チェックサムの結果が特定の値の場合（チェックサムの結果が正常である場合）には電断前の状態に復帰すべくステップS109に進み、チェックサムの結果が特定の値以外である場合（チェックサムの結果が異常である場合）には、パチンコ機100を初期状態にすべくステップS113に進む。同様に電源ステータスの情報が「サスペンド」以外の情報を示している場合にもステップS113に進む。

30

#### 【0213】

40

ステップS109では、データ書き戻し処理を行う。このデータ書き戻し処理では、電断時にRAM308に設けられたスタックポインタ退避領域に記憶しておいたスタックポインタの値を読み出し、スタックポインタに再設定（本設定）する。また、電断時にRAM308に設けられたレジスタ退避領域に記憶しておいた各レジスタの値を読み出し、各レジスタに再設定した後、割込許可の設定を行う。以降、CPU304が、再設定後のスタックポインタやレジスタに基づいて制御プログラムを実行する結果、パチンコ機100は電源断時の状態に復帰する。すなわち、電断直前にタイマ割込処理（後述）に分岐する直前に行った命令の次の命令から処理を再開する。また、図4に示す主制御部300にお

50

ける基本回路 302 に搭載されている RAM308 には、送信情報記憶領域が設けられている。このステップ S109 では、その送信情報記憶領域に、復電コマンドをセットする。この復電コマンドは、電源断時の状態に復帰したことを表すコマンドであり、後述する、主制御部 300 のタイマ割込処理におけるステップ S231において、第 1 副制御部 400 へ送信される。

#### 【0214】

ステップ S111 では、WDT3141 を起動させる処理を行う。ここでは、WDT3141 の起動許可及び初期値の設定等を行う。なお、本実施形態では、WDT3141 に、初期値として 32.8 ms に相当する数値を設定する。

#### 【0215】

ステップ S113 では、RWMクリア処理を行う。このRWMクリア処理では、RAM308 の全ての記憶領域の初期化を行う。また、主制御部のタイマ割込み許可の設定、スタックポインタへのスタック初期値の設定（本設定）なども併せて行う。さらにここで、主制御部 300 の RAM308 に設けられた送信情報記憶領域に正常復帰コマンドをセットする。この正常復帰コマンドは、主制御部 300 の RWMクリア処理（ステップ S113）が行われたことを表すコマンドであり、復電コマンドと同じく、主制御部 300 のタイマ割込処理におけるステップ S231において、第 1 副制御部 400 へ送信される。

#### 【0216】

ステップ S115 では、ステップ S111 と同様、WDT3141 を起動させる処理を行う。

10

20

#### 【0217】

ステップ S117 では、基本乱数初期値更新処理を行う。ここにいう基本乱数とは、ソフトウェア乱数である、大当り用特図乱数、小当り用特図乱数、およびハズレ用特図乱数が相当する。なお、各乱数には特図 1 用の乱数と特図 2 用の乱数が存在するが、以降の説明では、特に断りを入れない限り両者を区別することなく単に特図として説明する。この基本乱数初期値更新処理では、大当り用特図乱数カウンタ、小当り用特図乱数カウンタ、およびハズレ用特図乱数カウンタそれぞれの初期値を生成するための初期値生成用乱数カウンタを更新する。各カウンタが RAM308 に設けられている。なお、初期値生成用乱数カウンタは、後述するステップ S204 でも更新する。

#### 【0218】

30

ステップ S119 では演出乱数更新処理を行う。ここにいう演出乱数もソフトウェア乱数であって、この演出乱数は、演出を決定する元になる乱数のことであり、本実施形態では、後述する先読み予告を実行するか否かを抽選する際に用いられる乱数等が相当する。この演出乱数更新処理では、RAM308 に設けられた演出乱数カウンタを更新する。なお、演出乱数カウンタは、後述するステップ S211 でも更新する。

#### 【0219】

主制御部 300 は、所定の周期ごとに開始するタイマ割込処理を行っている間を除いて、ステップ S117 およびステップ S119 の処理を繰り返し実行する。

#### 【0220】

< 主制御部タイマ割込処理 >

40

次に、図 24 を用いて、主制御部 300 の CPU304 が実行する主制御部タイマ割込処理について説明する。なお、同図は主制御部タイマ割込処理の流れを示すフローチャートである。

#### 【0221】

図 4 に示す主制御部 300 は、所定の周期（本実施形態では約 4 ms に 1 回）でタイマ割込信号を発生するタイマ回路 311 を備えており、このタイマ割込信号を契機として主制御部タイマ割込処理を所定の周期で開始する。なお、この主制御部タイマ割込処理は、本発明の第二の処理に相当する。また、主制御部タイマ割込処理の契機となるタイマ割込信号は、本発明の第一の割込み要求に相当する。

#### 【0222】

50

ステップS201では、タイマ割込スタート処理を行う。このタイマ割込スタート処理では、C P U 3 0 4 の各レジスタの値をスタック領域に一時的に退避する処理などを行う。

#### 【 0 2 2 3 】

ステップS203では、W D T 3 1 4 1 のカウント値が初期設定値（本実施形態では32.8m s）を超えてW D T 3 1 4 1 割込が発生しないように（処理の異常を検出しないように）、W D T 3 1 4 1 を定期的に（本実施形態では、主制御部タイマ割込の周期である約4m sに1回）リスタートを行う。

#### 【 0 2 2 4 】

ステップS205では、入力ポート状態更新処理を行う。この入力ポート状態更新処理では、I / O 3 1 0 の入力ポートを介して、各種の球検出センサを含む図4に示す各種センサ320の検出信号を入力して検出信号の有無を監視し、R A M 3 0 8 に各種センサ320ごとに区画して設けた信号状態記憶領域に記憶する。球検出センサの検出信号を例にして説明すれば、前々回のタイマ割込処理（約4m s前）で検出した各々の球検出センサの検出信号の有無の情報を、R A M 3 0 8 に各々の球検出センサごとに区画して設けた前々回検出信号記憶領域から読み出し、この情報をR A M 3 0 8 に各々の球検出センサごとに区画して設けた今回検出信号記憶領域から読み出し、この情報を上述の前回検出信号記憶領域に記憶する。また、今回検出した各々の球検出センサの検出信号を、上10述の今回検出信号記憶領域に記憶する。

#### 【 0 2 2 5 】

また、ステップS205では、上述の前々回検出信号記憶領域、前回検出信号記憶領域、および今回検出信号記憶領域の各記憶領域に記憶した各々の球検出センサの検出信号の有無の情報を比較し、各々の球検出センサにおける過去3回分の検出信号の有無の情報が入賞判定パターン情報と一致するか否かを判定する。一個の遊技球が一つの球検出センサを通過する間に、約2m sという非常に短い間隔で起動を繰り返すこの主制御部タイマ割込処理は何回か起動する。このため、主制御部タイマ割込処理が起動する度に、上述のステップS205では、同じ遊技球が同じ球検出センサを通過したことを表す検出信号を確認することになる。この結果、上述の前々回検出信号記憶領域、前回検出信号記憶領域、および今回検出信号記憶領域それぞれに、同じ遊技球が同じ球検出センサを通過したことを表す検出信号が記憶される。すなわち、遊技球が球検出センサを通過し始めたときには、前々回検出信号無し、前回検出信号有り、今回検出信号有りになる。本実施形態では、球検出センサの誤検出やノイズを考慮して、検出信号無しの後に検出信号が連続して2回記憶されている場合には、入賞があったと判定する。図4に示す主制御部300のR O M 3 0 6には、入賞判定パターン情報（本実施形態では、前々回検出信号無し、前回検出信号有り、今回検出信号有りであることを示す情報）が記憶されている。このステップS205では、各々の球検出センサにおいて過去3回分の検出信号の有無の情報が、予め定めた入賞判定パターン情報（本実施形態では、前々回検出信号無し、前回検出信号有り、今回検出信号有りであることを示す情報）と一致した場合に、一般入賞口226、可変入賞口234、第1特図始動口230、および第2特図始動口232への入球、または普図始動口228の通過があったと判定する。すなわち、これらの入賞口234、230やこれらの始動口230、232、228への入賞があったと判定する。例えば、一般入賞口226への入球を検出する一般入賞口センサにおいて過去3回分の検出信号の有無の情報が上述の入賞判定パターン情報と一致した場合には、一般入賞口226へ入賞があったと判定し、以降の一般入賞口226への入賞に伴う処理を行うが、過去3回分の検出信号の有無の情報が上述の入賞判定パターン情報と一致しなかった場合には、以降の一般入賞口226への入賞に伴う処理を行わずに後続の処理に分岐する。なお、主制御部300のR O M 3 0 6には、入賞判定クリアパターン情報（本実施形態では、前々回検出信号有り、前回検出信号無し、今回検出信号無しであることを示す情報）が記憶されている。入賞が一度ある40

10

20

30

40

50

ったと判定した後は、各々の球検出センサにおいて過去3回分の検出信号の有無の情報が、その入賞判定クリアパターン情報に一致するまで入賞があったとは判定せず、入賞判定クリアパターン情報に一致すれば、次からは上記入賞判定パターン情報に一致するか否かの判定を行う。

#### 【0226】

ステップS207およびステップS209では、基本乱数初期値更新処理および基本乱数更新処理を行う。これらの基本乱数初期値更新処理および基本乱数更新処理では、上記ステップS117で行った初期値生成用乱数カウンタの値の更新を行い、次に主制御部300で使用する、大当たり用特図乱数、小当たり用特図乱数、およびハズレ用特図乱数それぞれを生成するための乱数カウンタを更新する。例えば、大当たり用特図乱数として取り得る数値範囲が0～100とすると、RAM308に設けた大当たり用特図乱数を生成するための乱数カウンタ記憶領域から値を取得し、取得した値に1を加算してから元の乱数カウンタ記憶領域に記憶する。このとき、取得した値に1を加算した結果が101であれば0を元の乱数カウンタ記憶領域に記憶する。また、取得した値に1を加算した結果、乱数カウンタが一周していると判定した場合にはそれぞれの乱数カウンタに対応する初期値生成用乱数カウンタの値を取得し、乱数カウンタの記憶領域にセットする。例えば、0～100の数値範囲で変動する大当たり用特図乱数生成用の乱数カウンタから値を取得し、取得した値に1を加算した結果が、RAM308に設けた所定の初期値記憶領域に記憶している前回設定した初期値と等しい値（例えば7）である場合に、大当たり用特図乱数生成用の乱数カウンタに対応する初期値生成用乱数カウンタから値を初期値として取得し、大当たり用特図乱数生成用の乱数カウンタにセットすると共に、大当たり用特図乱数生成用の乱数カウンタが次に1周したことを判定するために、今回設定した初期値を上述の初期値記憶領域に記憶しておく。なお、本実施形態では特図1に関する乱数を取得するためのカウンタと特図2に関する乱数を取得するためのカウンタとを別々に設けているが、同一のカウンタを用いてもよい。

#### 【0227】

ステップS211では、演出乱数更新処理を行う。この演出乱数更新処理では、上記ステップS119と同様に、主制御部300で使用する演出用乱数を生成するための乱数カウンタを更新する。

#### 【0228】

ステップS213では、タイマ更新処理を行う。このタイマ更新処理では、普通図柄表示装置210に図柄を変動・停止表示する時間を計時するための普図表示図柄更新タイマ、第1特図表示装置212に図柄を変動・停止表示する時間を計時するための特図1表示図柄更新タイマ、第2特図表示装置214に図柄を変動・停止表示する時間を計時するための特図2表示図柄更新タイマ、所定の入賞演出時間、所定の開放時間、所定の閉鎖時間、所定の終了演出期間などを計時するためのタイマなどを含む各種タイマを更新する。

#### 【0229】

ステップS215では、入賞口カウンタ更新処理を行う。この入賞口カウンタ更新処理では、入賞口234、230や始動口230、232、228に入賞があった場合に、RAM308に各入賞口ごと、あるいは各始動口ごとに設けた賞球数記憶領域の値を読み出し、1を加算して、元の賞球数記憶領域に設定する。

#### 【0230】

また、ステップS217では、入賞受付処理を行う。この入賞受付処理では、第1特図始動口230に入賞があり、且つ、保留している特図1変動遊技の数が所定数（本実施形態では4）未満である場合には、所定の始動情報を取得する。すなわち、保留数が所定数未満であれば、図4に示す乱数生成回路318から、特図1当選乱数の元になるハードウェア乱数を得、加工を施すことによって特図1当選乱数を取得する。この点についてはさらに詳しく後述する。また、RAM308に設けた乱数カウンタ記憶領域から、大当たり用特図1乱数、小当たり用特図1乱数、およびハズレ用特図1乱数を取得する。大当たり用特図1乱数、小当たり用特図1乱数、およびハズレ用特図1乱数は、RAM308に設けられた

10

20

30

40

50

ソフトウェア乱数カウンタから導出されたソフトウェア乱数を加工した値（ソフトウェア乱数の値 + R レジスタの値 + 1）である。さらに、図 4 に示すカウンタ回路 312 から特図 1 変動時間決定用乱数を取得する。図 4 に示す乱数生成回路 318、カウンタ回路 312、RAM 308 に設けられたソフトウェア乱数カウンタ、および乱数加工を施す主制御部 300 を併せたものが、始動情報を生成して導出するものであり、始動情報導出手段（第 1 の始動情報導出手段、第 2 の始動情報導出手段）の一例に相当する。なお、ハードウェア乱数の生成に着目すれば、図 4 に示す乱数生成回路 318 あるいはカウンタ回路 312 が、始動情報を生成するものであり、始動情報生成手段（第 1 の始動情報生成手段、第 2 の始動情報生成手段）の一例に相当する。ここで取得された各種乱数（始動情報）は、RAM 308 に設けた特図 1 の保留記憶部の、入賞順（保留順）に応じた空いている領域に、1 セットの始動情報を記憶される。この特図 1 の保留記憶部は、第 1 特図始動口 230（第 1 の始動領域）に遊技球が進入した場合に取得した始動情報を所定の第 1 上限個数（ここでは 4 個）まで記憶可能な第 1 の始動情報記憶手段に相当する。このとき各種乱数（始動情報）を RAM 308 に設けた一時領域に一旦記憶し、その一時領域に記憶された値を特図 1 の保留記憶部に記憶してもよく、この場合、一時領域を第 1 の始動情報記憶手段としてもよいし、特図 1 の保留記憶部および一時領域を第 1 の始動情報記憶手段としてもよい。また、主制御部 300 の CPU 304 は、RAM 308 に記憶されている特図 1 の保留数の値に 1 を加算し、特図 1 の保留数が 1 増加する。したがって、主制御部 300 の CPU 304 が保留手段の一例に相当する。また、特図 2 についても、特図 1 と同様に始動情報である各乱数を取得し、取得した乱数を RAM 308 に設けた特図 2 の保留記憶部に、1 セットの始動情報を記憶され、さらに、RAM 308 に記憶されている特図 2 の保留数の値に 1 を加算する。特図 2 の保留記憶部は、第 2 特図始動口 232（第 2 の始動領域）に遊技球が進入した場合に取得した始動情報を所定の第 2 上限個数（ここでは 4 個）まで記憶可能な第 2 の始動情報記憶手段に相当する。このとき各種乱数（始動情報）を RAM 308 に設けた一時領域に一旦記憶し、その一時領域に記憶された値を特図 2 の保留記憶部に記憶してもよく、この場合一時領域を第 2 の始動情報記憶手段としてもよいし、特図 2 の保留記憶部および一時領域を第 2 の始動情報記憶手段としてもよい。

#### 【0231】

また、普図始動口 228 を球が通過したことを検出し、且つ、保留している普図変動遊技の数が所定数（本実施形態では 4）未満の場合には、そのタイミングで、図 4 に示す乱数生成回路 318 から普図当選乱数を所得し、RAM 308 に設けた特図用とは別の乱数記憶領域に記憶する。この乱数生成回路 318 から普図当選乱数を取得する点についても、さらに後述する。

#### 【0232】

また、この入賞受付処理では、所定の球検出センサにより、第 1 特図始動口 230、第 2 特図始動口 232、普図始動口 228、または可変入賞口 234 の入賞（入球）を検出した場合に、第 1 副制御部 400 に送信すべき送信情報に、第 1 特図始動口 230、第 2 特図始動口 232、普図始動口 228、および可変入賞口 234 の入賞（入球）の有無を示す入賞受付情報を設定する。

#### 【0233】

なお、特図の始動情報にても普図の始動情報にても、保留数がそれぞれの所定数以上であれば始動情報を取得せずに、ステップ S219 に進む。

#### 【0234】

ステップ S219 では、払出要求数送信処理を行う。図 4 に示す払出制御部 600 に出力する出力予定情報および払出要求情報は 1 バイトで構成しており、ビット 7 にストローブ情報（オンの場合、データをセットしていることを示す）、ビット 6 に電源投入情報（オンの場合、電源投入後一回目のコマンド送信であることを示す）、ビット 4～5 に暗号化のための今回加工種別（0～3）、およびビット 0～3 に暗号化加工後の払出要求数を示すようにしている。

## 【0235】

ステップS221では、普図状態更新処理を行う。この普図状態更新処理は、普図の状態に対応する複数の処理のうちの1つの処理を行う。例えば、普図変動表示の途中（上述する普図表示図柄更新タイマの値が1以上）における普図状態更新処理では、普通図柄表示装置210を構成する7セグメントLEDの点灯と消灯を繰り返す点灯・消灯駆動制御を行う。この制御を行うことで、普通図柄表示装置210は普図の変動表示（普図変動遊技）を行う。

## 【0236】

また、普図変動表示時間が経過したタイミング（普図表示図柄更新タイマの値が1から0になったタイミング）における普図状態更新処理では、当りフラグがオンの場合には、当り図柄の表示態様となるように普通図柄表示装置210を構成する7セグメントLEDの点灯・消灯駆動制御を行い、当りフラグがオフの場合には、ハズレ図柄の表示態様となるように普通図柄表示装置210を構成する7セグメントLEDの点灯・消灯駆動制御を行う。また、主制御部300のRAM308には、普図状態更新処理に限らず各種の処理において各種の設定を行う設定領域が用意されている。ここでは、上記点灯・消灯駆動制御を行うとともに、その設定領域に普図停止表示中であることを示す設定を行う。この制御を行うことで、普通図柄表示装置210は、当り図柄（図5(c)に示す普図A）およびハズレ図柄（図5(c)に示す普図B）いずれか一方の図柄の確定表示を行う。さらにその後、所定の停止表示期間（例えば500m秒間）、その表示を維持するためにRAM308に設けた普図停止時間管理用タイマの記憶領域に停止期間を示す情報を設定する。この設定により、確定表示された図柄が所定期間停止表示され、普図変動遊技の結果が遊技者に報知される。

10

20

30

## 【0237】

また、普図変動遊技の結果が当りであれば、後述するように、普図当りフラグがオンされる。この普図当りフラグがオンの場合には、所定の停止表示期間が終了したタイミング（普図停止時間管理用タイマの値が1から0になったタイミング）における普図状態更新処理では、RAM308の設定領域に普図作動中を設定するとともに、所定の開放期間（例えば2秒間）、第2特図始動口232の羽根部材2321の開閉駆動用のソレノイド（332）に、羽根部材2321を開放状態に保持する信号を出力するとともに、RAM308に設けた羽根開放時間管理用タイマの記憶領域に開放期間を示す情報を設定する。このようにして一对の羽根部材2321の開放制御を行う主制御部300のCPU304が、可変始動領域制御を行う可変始動領域制御手段の一例に相当する。一方、非電サポ状態であれば、RAM308の設定領域に普図非作動中を設定するとともに、第2特図始動口232の羽根部材2321の開閉駆動用のソレノイド（332）には、何ら信号を出力しない。こうすることで、羽根部材2321は閉じた状態のままになる。なお、羽根部材2321を閉じた状態に維持するための信号を必ず出力するようにしてもよい。

## 【0238】

また、電サポ状態であった場合には、所定の開放期間が終了したタイミング（羽根開放時間管理用タイマの値が1から0になったタイミング）で開始する処理では、所定の閉鎖期間（例えば0.1秒間）、羽根部材2321の開閉駆動用のソレノイド（332）に、羽根部材2321を閉鎖状態に保持する信号を出力するとともに、RAM308に設けた羽根閉鎖時間管理用タイマの記憶領域に閉鎖期間を示す情報を設定する。

40

## 【0239】

また、電サポ状態であった場合には、所定の閉鎖期間が終了したタイミング（羽根閉鎖時間管理用タイマの値が1から0になったタイミング）で開始する普図状態更新処理において、RAM308の設定領域に普図非作動中を設定する。さらに、普図変動遊技の結果がハズレであれば、後述するように、普図ハズレフラグがオンされる。この普図ハズレフラグがオンの場合には、上述した所定の停止表示期間が終了したタイミング（普図停止時間管理用タイマの値が1から0になったタイミング）における普図状態更新処理でも、RAM308の設定領域に普図非作動中を設定する。普図非作動中の場合における普図状態

50

更新処理では、何もせずに次のステップ S 2 2 3 に移行するようにしている。

**【 0 2 4 0 】**

続いて、ステップ S 2 2 3 では普図関連抽選処理を実行する。

**【 0 2 4 1 】**

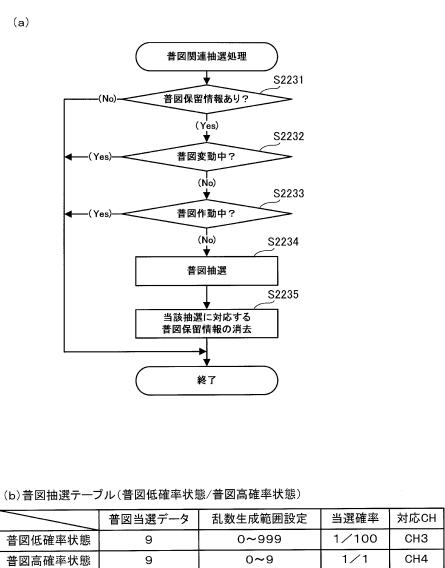

図 2 5 ( a ) は、普図関連抽選処理の流れを示すフローチャートである。

**【 0 2 4 2 】**

図 2 5 ( a ) に示す普図関連抽選処理では、まず、普図保留情報があるか否かを判定する（ステップ S 2 2 3 1）。ここにいう普図保留情報とは、普図の保留数を指す。すなわち、ここでは、保留している普図変動遊技の数が 1 以上であるか否かを判定する。なお、普図の保留数をデータとして持っていないとも、例えば、保留に対応した乱数（普図当選乱数）を普図保留情報として認識するようにしても良い。普図保留情報がなければ、この普図関連抽選処理は終了になり、普図保留情報があればステップ S 2 2 3 2 に進む。10 ステップ S 2 2 3 2 では、普図変動遊技が行われているか否かを判定し、行われていればこの普図関連抽選処理は終了になり、行われていなければステップ S 2 2 3 3 に進む。ステップ S 2 2 3 3 では、第 2 特図始動口 2 3 2 の開閉制御が行われているか否か（普図作動中か否か）を判定し、普図作動中であればこの普図関連抽選処理は終了になり、普図非作動中であればステップ S 2 2 3 4 に進む。

**【 0 2 4 3 】**

ステップ S 2 2 3 4 では、上述の乱数記憶領域に記憶している普図当選乱数に基づいた乱数抽選を行う。20

**【 0 2 4 4 】**

図 2 5 ( b ) は、普図抽選テーブルを示す図である。このテーブルは、主制御部 3 0 0 の R O M 3 0 6 に記憶されている。

**【 0 2 4 5 】**

主制御部 3 0 0 の C P U 3 0 4 は、R A M 3 0 8 の乱数記憶領域から普図当選乱数を取り出し、時短フラグを参照し、時短フラグがオンであれば普図高確率状態（電サポ中）であるため、取得した普図当選乱数から普図高確率状態の普図当選データを引き、キャリーが発生した場合（普図当選乱数よりも普図当選データの値が大きい場合）は普図当選とし、キャリーが発生しなかった場合は普図ハズレになる。すなわち、普図当選乱数範囲は 0 ~ 9 になる。普図高確率状態では、普図当選乱数は、図 1 0 に示す乱数生成回路 3 1 8 のチャンネル C H 4 から出力される。このチャンネル C H 4 には、図 2 3 に示す乱数生成回路初期設定処理における乱数生成範囲の設定（ステップ S 1 0 5 3 a ）において 0 ~ 9 の乱数生成範囲が設定されており、普図高確率状態の普図当選乱数の取り得る範囲は 0 ~ 9 になる。したがって、普図高確率状態における普図当選確率は 1 / 1 になる。一方、時短フラグがオフであれば普図低確率状態（非電サポ中）であるため、取得した普図当選乱数から、普図高確率状態のデータと同じ普図低確率状態の普図当選データを引き、キャリーが発生した場合（普図当選乱数よりも普図当選データの値が大きい場合）は普図当選とし、キャリーが発生しなかった場合は普図ハズレになる。すなわち、普図低確率状態の場合でも普図当選乱数範囲は 0 ~ 9 になる。普図低確率状態では、普図当選乱数は、図 1 0 に示す乱数生成回路 3 1 8 のチャンネル C H 3 から出力される。このチャンネル C H 3 には、乱数生成範囲の設定（ステップ S 1 0 5 3 a ）において 0 ~ 9 9 9 の乱数生成範囲が設定されており、普図低確率状態の普図当選乱数の取り得る範囲は 0 ~ 9 9 9 になる。したがって、普図低確率状態における普図当選確率は 1 / 1 0 0 になる。30

**【 0 2 4 6 】**

本実施形態では、普図当選乱数の取り得る範囲（乱数生成範囲）を、デフォルトの 0 ~ 6 5 5 3 5 から 0 ~ 9 9 9 に制限することで大当たり確率を、きりのよい 1 / 1 0 0 にすることができる。また、普図当選データを、普図高確率状態と普図低確率状態で同じ値にすることができる。乱数生成範囲を制限せずに確率を決定することは開発工数の増大を招くとともに誤った確率設計の原因となってしまう場合がある。特に、一の契機に基づいて複数回の抽選を行う場合に煩雑さはより顕著になってしまい。よって、乱数生成範囲を制限4050

することは開発工数を削減するとともに、抽選処理の安定化を図ることができるといえる。また、普図当選データを、普図高確率状態と普図低確率状態で共通化することも、開発工数を削減するとともに、抽選処理の安定化を図ることができるといえる。

#### 【0247】

普図抽選に当選した場合にはRAM308に設けた当りフラグをオンに設定する。ハズレ(不当選)の場合には、当りフラグをオフに設定する。また、普図抽選の結果に関わらず、図4に示すカウンタ回路312から普図変動時間決定用乱数を取得し、取得した普図変動時間決定用乱数に基づいて複数の変動時間のうちから普図表示装置210に普図を変動表示する時間を1つ選択し、この変動表示時間を、普図変動表示時間として、RAM308に設けた普図変動時間記憶領域に記憶する。なお、保留している普図変動遊技の数は、RAM308に設けた普図保留数記憶領域に記憶するようにしており、ステップS2234を実行するたびに、保留している普図変動遊技の数から1を減算した値を、この普図保留数記憶領域に記憶し直すようにしている。また、カウンタ回路312からの普図変動時間決定用乱数の取得は、普図始動口228への入賞時に行ってもよい。

10

#### 【0248】

ステップS2235では、上述の乱数記憶領域から、先の普図抽選に使用した普図当選乱数を消去し、この普図関連抽選処理は終了になる。

#### 【0249】

続いて、特図先読み処理(ステップS225)が実行される。この先読み処理では、まず、RAM308に設けられた特図1の保留記憶部内の特図1当選乱数を先読みするか、あるいは特図2の保留記憶部内の特図2当選乱数を先読みする。なお、ここでの先読みとは始動情報を当否判定(本抽選)の前に先に読むことを意味するが、以降の先読み処理では、先読みという言葉を、先(当否判定(本抽選)の結果)を読むという意味で使用することがある。このステップS225では、後述する特図関連処理(ステップS229)で用いる図27(a)に示す特図抽選テーブルの内容と同じ内容の事前判定用テーブルを用い、先読みした特図当選乱数に基づく当否判定の事前判定を行う。なお、特図関連処理では、特図抽選テーブルを用いて特図変動遊技の当否判定を改めて行い、ここでの判定結果は、あくまで事前判定の結果になる。当否判定の事前判定では、「大当たり」という結果か、あるいは「大当たり」以外という結果が導出され、「大当たり」という結果の場合には、RAM308に設けられた特図1の保留記憶部の大当たり用特図1乱数を先読みするか、あるいは特図2の保留記憶部の大当たり用特図2乱数を先読みする。続いて、ステップS229の特図関連処理で用いる図27(b)に示す停止図柄抽選テーブルの内容と同じ内容の事前判定用テーブルを用い、先読みした大当たり用特図乱数に基づく特図の停止図柄の事前判定を行う。なお、特図関連処理では、停止図柄抽選テーブルを用いて特図の停止図柄の抽選を改めて行い、ここでの判定結果は、あくまで事前判定の結果になる。こうして、特図の停止図柄を事前判定すると、先読み予告の実行可否抽選を行う。この先読み予告は、特図関連抽選処理(ステップS229)が実行される前、すなわち当否判定が行われる前に、当該特図関連抽選処理で行われる当否判定の結果が大当たり(ここではより限定して15Rの大当たり(15R特別大当たりか15R大当たり))になることを予告するための報知である。ここで先読み予告には、停止図柄の事前判定結果が15Rの大当たり図柄(特図Aまたは特図B)でなくても、15Rの大当たりになるかのように偽りで予告する偽の先読み予告も含まれる。すなわち、先読み予告は、当否判定の結果が15R大当たりになる可能性があることを表したり、遊技者に示唆する事前報知、あるいは当否判定の結果が15R大当たりになることを遊技者に期待させる事前報知であるといえる。先読み予告の実行可否抽選を行うタイミングで、RAM308に設けられた演出乱数カウンタから演出乱数(例えば、取り得る範囲は0~99)を取得し、取得した演出乱数に基づいて実行可否抽選を行う。なお、停止図柄の事前判定結果を第1副制御部400に送信し、この実行可否抽選は、第1副制御部400が行うようにしてもよい。

20

#### 【0250】

次に、特図1および特図2それぞれについての特図状態更新処理(ステップS227)

30

40

40

50

を行うが、最初に、特図2についての特図状態更新処理を行い、次いで、特図1についての特図状態更新処理を行う。特図2状態更新処理は、特図2の状態に応じて、次の8つの処理のうちの1つの処理を行う。例えば、特図2変動表示の途中（上述の特図2表示図柄更新タイマの値が1以上）における特図2状態更新処理では、第2特別図柄表示装置214を構成する7セグメントLEDの点灯と消灯を繰り返す点灯・消灯駆動制御を行う。この制御を行うことで、第2特別図柄表示装置214は特図2の変動表示（特図2変動遊技）を行う。

#### 【0251】

また、コマンド設定送信処理（ステップS231）で一般コマンド回転開始設定送信処理を実行させることを示す所定の送信情報を上述の送信情報記憶領域に追加記憶してから処理を終了する。10

#### 【0252】

また、主制御部300のRAM308には、15R大当たりフラグ、2R大当たりフラグ、第1小当たりフラグ、第2小当たりフラグ、第1ハズレフラグ、第2ハズレフラグ、確変フラグ、および時短フラグそれぞれのフラグが用意されている。特図2変動表示時間が経過したタイミング（特図2表示図柄更新タイマの値が1から0になったタイミング）で開始する特図2状態更新処理では、後述する特図関連抽選処理における特図決定結果（特図の停止図柄態様）に基づいて第2特別図柄表示装置214を構成する7セグメントLEDの点灯・消灯駆動制御を行い、RAM308の設定領域に特図2停止表示中であることを表す設定を行う。この制御を行うことで、第2特別図柄表示装置214は、15R特別大当たり図柄（特図A）、15R大当たり図柄（特図B）、2R特別大当たり図柄（特図C）、突然時短図柄（特図D）、隠れ確変図柄（特図E）、突然通常図柄（特図F）、第1小当たり図柄（特図G）、第2小当たり図柄（特図H）、第1ハズレ図柄（特図I）、および第2ハズレ図柄（特図J）のいずれか一つの図柄の確定表示を行う。さらにその後、所定の停止表示期間（例えば500m秒間）その表示を維持するためにRAM308に設けた特図2停止時間管理用タイマの記憶領域に停止時間を示す情報を設定する。この設定により、確定表示された特図2が所定期間停止表示され、特図2変動遊技の結果が遊技者に報知される。また、RAM308に設けられた電サポ回数記憶部に値がセットされている場合には、その値が1以上であれば、その時短回数から1を減算し、減算結果が1から0となった場合は、特図確率変動中でなければ、時短フラグをオフする。さらに、大当たり遊技中や小当たり遊技中にも、時短フラグをオフする。すなわち、主制御部300のCPU304は、大当たり遊技状態中および小当たり遊技状態中（第二の制御状態中）である場合に、非電サポ状態（第一の進入率制御状態）に移行させる。20

#### 【0253】

また、後述するコマンド設定送信処理（ステップS231）で一般コマンド回転停止設定送信処理を実行させることを示す所定の送信情報を上述の送信情報記憶領域に追加記憶するとともに、変動表示を停止する図柄が特図2であることを示す特図2識別情報を、後述するコマンドデータに含める情報としてRAM308に追加記憶してから処理を終了する。30

#### 【0254】

また、特図2変動遊技の結果が大当たりであれば、大当たりフラグがオンされる。この大当たりフラグがオンの場合には、所定の停止表示期間が終了したタイミング（特図2停止時間管理用タイマの値が1から0になったタイミング）における特図2状態更新処理では、RAM308の設定領域に特図2作動中を設定するとともに、所定の入賞演出期間（例えば3秒間）すなわち装飾図柄表示装置208による大当たりを開始することを遊技者に報知する画像を表示している期間待機するためにRAM308に設けた特図2待機時間管理用タイマの記憶領域に入賞演出期間を示す情報を設定する。また、コマンド設定送信処理（ステップS231）で一般コマンド入賞演出設定送信処理を実行させるために上述の送信情報記憶領域に5Hを送信情報（コマンド種別）として追加記憶する。40

#### 【0255】

10

20

30

40

50

また、所定の入賞演出期間が終了したタイミング（特図2待機時間管理用タイマの値が1から0になったタイミング）で開始する特図2状態更新処理では、所定の開放期間（例えば29秒間、または可変入賞口234に所定球数（例えば10球）の遊技球の入賞を検出するまで）可変入賞口234の扉部材2341の開閉駆動用のソレノイド（332）に、扉部材2341を開放状態に保持する信号を出力するとともに、RAM308に設けた扉開放時間管理用タイマの記憶領域に開放期間を示す情報を設定する。また、コマンド設定送信処理（ステップS231）で一般コマンド大入賞口開放設定送信処理を実行させるために上述の送信情報記憶領域に7Hを送信情報（コマンド種別）として追加記憶する。

#### 【0256】