# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-152437 (P2004-152437A)

最終頁に続く

(43) 公開日 平成16年5月27日(2004.5.27)

| (51) Int.C1. <sup>7</sup> | F 1                          |                   | テーマコード (参考)     |  |

|---------------------------|------------------------------|-------------------|-----------------|--|

| G11C 29/00                | G11C                         | 29/00 673Z        | 2G132           |  |

| GO1R 31/28                | GO6F                         | 12/14 3 2 O A     | 5 B O 1 7       |  |

| GO6F 12/14                | GO6F                         | 12/16 3 3 O A     | 5BO18           |  |

| GO6F 12/16                | GO1R                         | 31/28 B           | 5BO25           |  |

| G 1 1 C 16/02             | GO1R                         | 31/28 D           | 5 L 1 O 6       |  |

|                           | 審査請求                         | 未請求 請求項の数 5       | OL (全7頁) 最終頁に続く |  |

| (21) 出願番号                 | 特願2002-318390 (P2002-318390) | (71) 出願人 00000582 | 21              |  |

| (22) 出願日                  | 平成14年10月31日 (2002.10.31)     | 松下電器産業株式会社        |                 |  |

| , ,                       | ,                            | 大阪府門真市大字門真1006番地  |                 |  |

|                           |                              | (74) 代理人 10010564 | 17              |  |

|                           |                              | 弁理士               | 小栗 昌平           |  |

|                           |                              | (74)代理人 10010547  | 74              |  |

|                           |                              | 弁理士               | 本多 弘徳           |  |

|                           |                              | (74)代理人 10010858  | 39              |  |

|                           |                              | 弁理士               | 市川 利光           |  |

|                           |                              | (74)代理人 10011510  | )7              |  |

|                           |                              | 弁理士               | 高松 猛            |  |

|                           |                              | (74)代理人 10009034  | 人 100090343     |  |

|                           |                              | 弁理士               | 濱田 百合子          |  |

# (54) 【発明の名称】半導体集積回路装置

# (57)【要約】

【課題】チップ面積の増大を抑え、高い秘匿性、高い信頼性で秘密データ格納部の検査を行う。

【解決手段】秘密データを格納する秘密データ格納部302と、秘密データ格納部102から読み出されたデータを復元不可能なデータ形式に変換するCRC演算部303と、CRC演算部303から出力されたデータと外部から入力された比較用データ(CRC変換結果)との比較結果を外部に出力する比較部304とを備える。また、CRC演算部303は、入力端子308に入力されるCRC演算初期値切換制御信号によりCRC演算の初期値を切り換えることができる。

【選択図】 図1

### 【特許請求の範囲】

### 【請求項1】

データを格納するデータ格納手段と、

前記データ格納手段から読み出されたデータを復元不可能なデータ形式に変換する不可逆変換手段と、

前記不可逆変換手段から出力されたデータと外部から入力された比較用データとの比較結果を外部に出力する比較手段と、

を備える半導体集積回路装置。

### 【請求項2】

前記不可逆変換手段は、外部からの制御により変換方式の変更が可能であることを特徴とする請求項1に記載の半導体集積回路装置。

#### 【請求項3】

前記不可逆変換手段はパリティ演算を行うものであり、外部からの制御によりパリティの演算方向をビット方向とワード方向に切り換え可能であることを特徴とする請求項 2 に記載の半導体集積回路装置。

### 【請求項4】

前記不可逆変換手段は、巡回冗長演算を行うことを特徴とする請求項 1 または 2 に記載の 半導体集積回路装置。

# 【請求項5】

外 部 から の 制 御 に よ り 巡 回 冗 長 演 算 の 初 期 値 の 切 り 換 え が 可 能 で あ る こ と を 特 徴 と す る 請 求 項 4 に 記 載 の 半 導 体 集 積 回 路 装 置 。

【発明の詳細な説明】

### [0001]

【発明の属する技術分野】

本発明は、データ格納部を検査するテスト回路を内蔵した半導体集積回路装置に関する。

### [0002]

## 【従来の技術】

従来、半導体集積回路装置においては、その信頼性を確保するために、製造時の出荷検査は必須である。しかし、データの秘匿性が要求される秘密データを格納する秘密データ格納部を内蔵した半導体集積回路装置においては、秘密データの秘匿性を損なわないために、データが外部から読み取ることができないように秘密データ格納部を検査する必要がある。

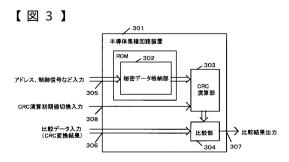

### [0003]

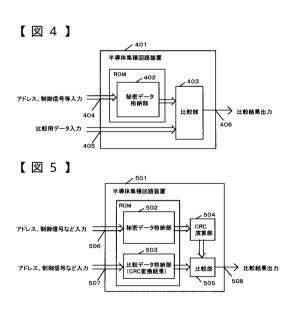

図4および図5は秘密データ格納部をテストするテスト回路を搭載した従来の半導体集積回路装置の構成を示す図である。図4に示す半導体集積回路装置401は、秘密データ格納部402の検査時には、外部のLSIテスタから入力端子405に入力した比較用のデータと、秘密データ格納部402より読み出されたデータとの比較を行い、比較結果のみを出力端子406より外部に出力する。以上の構成により、外部に直接秘密データを出力することなく、秘密データ格納部の検査を行うことができる。

# [ 0 0 0 4 ]

図5に示す半導体集積回路装置501は、秘密データ格納部502、比較データ格納部503、CRC演算部504および比較部505を内蔵し、秘密データ格納部502の検査時には、秘密データ格納部502から読み出されてRC演算部504で巡回冗長演算されたデータと、比較データ格納部503から読み出されたデータとの比較を行い、比較結果のみを出力端子508より外部に出力する。以上の構成により、外部に直接秘密データの出力や比較用のデータの入力を行うことなく秘密データ格納部の検査を行うことができ、また、図4に示した半導体集積回路装置では可能であった検査用プログラムの解析などにより秘密データの読み出しも不可能となるため、データの秘匿性をより高めることができる。

30

10

20

#### [00005]

比較データ格納部を内蔵する半導体集積回路装置は、例えば、特許文献 1 に開示されている。

[0006]

【特許文献1】

特開2001-344992号公報

[ 0 0 0 7 ]

【発明が解決しようとする課題】

しかし、図4に示した半導体集積回路装置では、検査の際に比較用のデータをLSIテスタ等から入力する必要があるため、例えば、検査用プログラムの解析により秘密データを特定することが可能であり、非常に高い秘匿性が必要とされる用途には使用できないという問題があった。一方、図5に示した半導体集積回路装置では、比較データ格納部を内蔵することによりチップ面積が増大し、製造コストが上がるという問題がある。また、比較データ格納部が故障していた場合、秘密データ格納部の信頼性が保証できないという問題があった。

[0008]

本発明は以上の課題を解決するもので、チップ面積の増大を抑え、高い秘匿性、高い信頼性で秘密データ格納部の検査が可能な半導体集積回路装置を提供することを目的とする。

[0009]

【課題を解決するための手段】

前記の問題を解決するために、請求項1の半導体集積回路装置は、データを格納するデータ格納手段と、前記データ格納手段から読み出されたデータを復元不可能なデータ形式に変換する不可逆変換手段と、前記不可逆変換手段から出力されたデータと外部から入力された比較用データとの比較結果を外部に出力する比較手段と、を備える。

[ 0 0 1 0 ]

上記構成によれば、データ格納部のデータを不可逆変換したデータを比較対象とすることで、比較用データを解析して可逆的にデータ格納部のデータを復元することが不可能になり秘匿性を高めることができる。さらに、比較用データ格納部を内蔵しないためチップ面積の増大が小さく製造コストの抑えることができる。さらに、比較用データ格納部を内蔵しないため故障時の信頼性低下を回避できる。

[0011]

請求項2の半導体集積回路装置は、請求項1記載の半導体集積回路装置において、前記不可逆変換手段は、外部からの制御により変換方式の変更が可能であることを特徴とする。

[ 0 0 1 2 ]

上記構成によれば、外部制御で変換方式を切り換える複数回の検査が可能となるため、より信頼性の高い検査が可能となる。

[0013]

請求項3に記載の半導体集積回路装置は、請求項2記載の半導体集積回路装置において、前記不可逆変換手段はパリティ演算を行うものであり、外部からの制御によりパリティの演算方向をビット方向とワード方向に切り換え可能であることを特徴とする。

[0014]

上記構成によれば、不可逆変換演算を単純加算のパリティ演算で行うことで、回路を簡易に構成することができ回路規模の縮小が可能となる。また、ビット方向とワード方向で演算方向を切り換えることで、より信頼性の高い検査が可能となる。

[0015]

請求項4に記載の半導体集積回路装置は、請求項1または2に記載の半導体集積回路装置において、前記不可逆変換手段は、巡回冗長演算を行うことを特徴とする。

[0016]

上記構成によれば、不可逆変換演算を巡回冗長演算で行うことにより、不可逆性を強めることができ、秘匿性を高めることができる。

20

10

30

40

#### [0017]

請求項5に記載の半導体集積回路は、請求項4に記載の半導体集積回路装置において、外部からの制御により巡回冗長演算の初期値の切り換えが可能であることを特徴とする。

### [0018]

上記構成によれば、外部制御で巡回冗長の初期値を切り換えて複数回の検査を行うことで、より信頼性の高い検査が可能となる。

#### [0019]

# 【発明の実施の形態】

以下、本発明の実施の形態について、図面を参照しながら説明する。

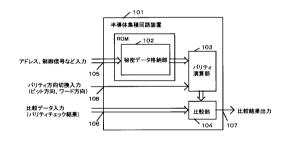

図1は、本発明の第1の実施の形態に係る半導体集積回路装置の構成を示すプロック図である。図1において、半導体集積回路装置101は、秘密データ格納部102と、秘密データ格納部102と、秘密データ格納部102と、秘密データ格納部102から読み出されたデータのパリティビットの計算を行うパリティ演算部104と、パリティ演算部104から出力されたパリティ演算結果データと入力端子106から入力された比較用データ(パリティチェック結果)との比較を行い、比較結果のみを出力端子107から外部へ出力する比較部105とを備えている。また、パリティ演算部104は、入力端子109から入力されたパリティ方向切換制御信号により、パリティ演算の方向をビット方向とワード方向に切り換えることができる。

### [0020]

上記構成の半導体集積回路装置101において、秘密データ格納部103の検査時には、外部のLSIテスタより、データの読み出しに必要なアドレスおよび制御信号を入力端子105から入力し、比較用データ(パリティチェック結果)を入力端子106から入力する。出力端子107には、秘密データのパリティ演算結果データと比較用データとの比較結果が出力され、この比較結果を外部のLSIテスタで期待値比較して良否判定を行う。

### [0021]

第1の実施の形態によれば、秘密データ格納部のデータを不可逆変換したデータを比較対象とすることで、比較用データを解析して可逆的に秘密データ格納部のデータを復元することが不可能になり秘匿性を高めることができる。さらに、比較用データ格納部を内蔵しないためチップ面積の増大が小さく製造コストの抑えることができる。さらに、比較用データ格納部を内蔵しないため故障時の信頼性低下を回避できる。また、パリティ方向をビット方向とワード方向に切り換えて2度検査を実施することで、より信頼性の高い検査を実施することができる。

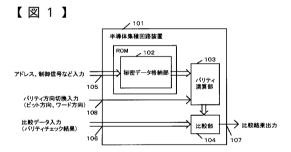

# [0022]

図2は、本発明の第2の実施の形態に係る半導体集積回路装置の構成を示すブロック図である。図2において、半導体集積回路装置201は、秘密データ格納部202と、秘密データ格納部202から読み出されたデータの巡回冗長演算を行うCRC演算部203と、CRC演算部203から出力されたCRC演算結果データと入力端子207から入力された比較用データ(CRC変換結果)との比較を行い、比較結果のみを出力する比較部204とを備えている。

# [0023]

上記構成の半導体集積回路装置201において、秘密データ格納部202の検査時には、外部のLSIテスタより、データの読み出しに必要なアドレスおよび制御信号を入力端子205から入力し、比較用データ(CRC変換結果)を入力端子206から入力する。出力端子207には、秘密データの巡回冗長演算結果データと比較用データとの比較結果が出力され、この比較結果を外部のLSIテスタで期待値比較して良否判定を行う。

### [0024]

第2の実施の形態によれば、主に通信用途に用いられるCRC演算部を内蔵した半導体集積回路装置において、秘密データ格納部の結果を実施する際にCRC演算部を利用することで、回路の有効利用が可能となり回路規模の縮小が可能となる。また、巡回冗長演算を行うことにより、不可逆性を強めることができ、秘匿性を高めることができる。

### [0025]

50

20

30

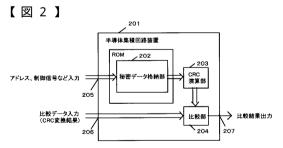

図3は、本発明の第3の実施の形態に係る半導体集積回路装置の構成を示すブロック図である。図3に示す半導体集積回路装置301は、図2に示す半導体集積回路装置201を発展させたもので、CRC演算部303の初期値を、入力端子308から入力されたCRC演算初期値切換制御信号により切り換え可能としたものである。CRC初期値を切り換えて複数回検査を実施することにより、非常に信頼性の高い検査を実施することができる

#### [0026]

# 【発明の効果】

以上説明した発明によれば、データ格納部のデータを不可逆変換したデータを比較対象とすることで、比較用データを解析して可逆的にデータ格納部のデータを復元することが不可能になり秘匿性を高めることができる。さらに、比較用データ格納部を内蔵しないためチップ面積の増大が小さく製造コストの抑えることができる。さらに、比較用データ格納部を内蔵しないため故障時の信頼性低下を回避できる。

# [0027]

また、外部制御で不可逆演算の変換方式を切り換える複数回の検査が可能となるため、より信頼性の高い検査が可能となる。

### 【図面の簡単な説明】

- 【図1】本発明の第1の実施の形態に係る半導体集積回路装置の構成を示すブロック図。

- 【図2】本発明の第2の実施の形態に係る半導体集積回路装置の構成を示すブロック図。

- 【図3】本発明の第3の実施の形態に係る半導体集積回路装置の構成を示すブロック図。

- 【図4】従来の半導体集積回路装置の構成を示すブロック図。

- 【図5】従来の半導体集積回路装置の構成を示すブロック図。

### 【符号の説明】

- 101 半導体集積回路装置

- 1 0 2 秘密データ格納部

- 103 パリティ演算部

- 1 0 4 比較部

- 105 入力端子

- 106 入力端子

- 107 出力端子

- 108 入力端子

- 2 0 1 半導体集積回路装置

- 2 0 2 秘密データ格納部

- 203 CRC演算部

- 2 0 4 比較部

- 2 0 5 入力端子

- 206 入力端子

- 207 出力端子

- 3 0 1 半導体集積回路装置

- 3 0 2 秘密データ格納部

- 303 CRC演算部

- 3 0 4 比較部

- 3 0 5 入力端子

- 3 0 6 入力端子

- 307 出力端子

- 3 0 8 入力端子

- 4 0 1 半導体集積回路装置

- 4 0 2 秘密データ格納部

- 4 0 3 比較部

- 404 入力端子

30

20

40

10

(6)

- 4 0 5 入力端子

- 406 出力端子

- 5 0 1 半導体集積回路装置

- 5 0 2 秘密データ格納部

- 5 0 3 比較データ格納部

- 5 0 4 C R C 演算部

- 5 0 5 比較部

- 506 入力端子

- 5 0 7 入力端子

- 5 0 8 出力端子

# フロントページの続き

(51) Int.CI.<sup>7</sup> F I テーマコード (参考)

G 0 1 R 31/28 V G 1 1 C 17/00 6 0 1 P

(72)発明者 片岡 武

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 2G132 AA09 AC03 AD06 AK09 AK12 AL00 AL11

5B017 AA03 BA09 CA12

5B018 GA03 JA26 NA04 QA13

5B025 AD05 AD13 AD16 AE09 AE10

5L106 AA07 DD00 EE03 FF05