(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6126602号

(P6126602)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4L 25/02 (2006.01) | HO4L 25/02 Z |

| HO4L 25/49 (2006.01) | HO4L 25/02 V |

|                      | HO4L 25/49 H |

請求項の数 22 (全 16 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-525317 (P2014-525317)  |

| (86) (22) 出願日 | 平成24年8月16日 (2012.8.16)        |

| (65) 公表番号     | 特表2014-524699 (P2014-524699A) |

| (43) 公表日      | 平成26年9月22日 (2014.9.22)        |

| (86) 国際出願番号   | PCT/DE2012/200053             |

| (87) 国際公開番号   | W02013/023655                 |

| (87) 国際公開日    | 平成25年2月21日 (2013.2.21)        |

| 審査請求日         | 平成27年8月17日 (2015.8.17)        |

| (31) 優先権主張番号  | 102011052762.1                |

| (32) 優先日      | 平成23年8月16日 (2011.8.16)        |

| (33) 優先権主張国   | ドイツ(DE)                       |

|           |                                                                                                                                                                                                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | シリコン・ライン・ゲー・エム・ペー・ハ<br>ー<br>ドイツ連邦共和国 80687 ミュンヘ<br>ン ランツベルガー・シュトラーゼ 31<br>4 / テア・ドリッテン エルゲーベー<br>LANDSBERGER STR. 31<br>4 / 111 RGB., 80687<br>MUENCHEEN, BUNDESRE<br>PUBLIK DEUTSCHLAND<br>(74) 代理人 110001818<br>特許業務法人 R&C |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】回路装置および信号を送信するための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)と、差動データ信号および差動クロック信号(LP)との両方を、少なくとも1つのデータソースに割り当て可能な少なくとも1つの送信装置(S)と、少なくとも1つのデータシンクに割り当て可能な少なくとも1つの受信装置(E)との間で、前記シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)と、前記差動データ信号およびクロック信号(LP)と、をシリアル化する少なくとも1つの共通信号ストリーム(SI)の形態で、および、少なくとも1つの信号ストリームの形態で、

前記シングルエンド論理レベルベースのデータ信号およびクロック信号(HS)と、前記差動データ信号およびクロック信号(LP)と、をシリアル化する少なくとも1つの共通信号ストリーム(SI)の形態で、および、

前記差動データ信号およびクロック信号(LP)と、バイナリ信号(PDO)と、の両方を備える、少なくとも1つの信号ストリームの形態で、伝送可能である回路装置。

## 【請求項 2】

前記差動データ信号はコモンモードベースである請求項1に記載の回路装置。

## 【請求項 3】

前記信号ストリームは双方向の形態である請求項1又は2に記載の回路装置。

## 【請求項 4】

前記共通信号ストリーム(SI)は、少なくとも1つの光媒体(OM)を介して送信され得ることを特徴とする請求項1～3のいずれか一項に記載の回路装置。

**【請求項 5】**

前記差動データ信号および差動クロック信号（L P）と、前記バイナリ信号（P D）との両方を備える前記信号ストリームを、少なくとも1つの電気的またはガルバニックなリンク（G A）を介して送信することができる特徴とする請求項1～4のいづれか一項に記載の回路装置。

**【請求項 6】**

前記電気的またはガルバニックなリンク（G A）は、

前記送信装置（S）において、少なくとも1つの送信／受信モジュール（T X R X S）に割り当てられ、および、

前記受信装置（E）において、少なくとも1つの送信／受信モジュール（T X R X E）10

に割り当てられ、それを用いて、前記差動データ信号および差動クロック信号（L P）と、前記バイナリ信号（P D）との両方を備える前記信号ストリームを送信／受信することができる特徴とする請求項5に記載の回路装置。

**【請求項 7】**

前記送信／受信モジュール（T X R X S, T X R X E）は、

前記差動データ信号および差動クロック信号（L P）と、前記バイナリ信号（P D）とをシリアル化するための少なくとも1つのマルチプレクサ（M U P）と、

前記マルチプレクサ（M U P）の下流の、シリアル化された信号ストリームを、バイナリN R Z（n o n r e t r u n - t o - z e r o）フォーマットからパルス幅変調フォーマットへ変えるための少なくとも1つのバイナリP W M（p u l s w i d t h m o d u l a t i o n）コンバータ（B P W M W）と。20

前記バイナリP W Mコンバータ（B P W M W）の下流の少なくとも1つのラインドライバ（L D）と、

前記ラインドライバ（L D）の下流の少なくとも1つの終端抵抗（R 0）と、

を備えることを特徴とする請求項6に記載の回路装置。

**【請求項 8】**

前記送信／受信モジュール（T X R X S, T X R X E）は、

前記終端抵抗（R 0）の下流の、前記終端抵抗（R 0）によって分けられた、重み付けされた少なくとも2つの信号（S A, S B）を減算するための少なくとも1つの差動増幅器（D V）と。30

前記差動増幅器（D V）の下流の、パルス幅変調フォーマットから前記バイナリN R Zフォーマットへ変えるための少なくとも1つのP W Mバイナリコンバータ（P W M B W）と、

前記P W Mバイナリコンバータ（P W M B W）の下流の、前記差動データ信号および差動クロック信号（L P）と前記バイナリ信号（P D）に非シリアル化するための少なくとも1つのデマルチプレクサ（D M P）と、

を備えることを特徴とする請求項7に記載の回路装置。

**【請求項 9】**

前記送信装置（S）は、

前記データ信号およびクロック信号のための少なくとも1つの入力部（E S）と、前記入力部（E S）の下流の、前記データ信号およびクロック信号を受け取るための少なくとも1つの送信インターフェースロジック（L S）と、40

前記送信インターフェースロジック（L S）の下流の、前記共通信号ストリーム（S I）を生成するための少なくとも1つのシリアライザ（S E）と、

前記シリアライザ（S E）の上流で、前記送信インターフェースロジック（L S）のクロックモジュール（C S）の下流に設けられた、少なくとも1つの基準クロックを生成するための少なくとも1つのクロック発振器（P S）と、

前記シリアライザ（S E）の下流の少なくとも1つの出力ドライバ（A T）と、

前記出力ドライバ（A T）の下流の、前記共通信号ストリーム（S I）を前記受信装置（E）へ送信するための少なくとも1つの出力部（A S）と、50

を備えることを特徴とする請求項 1 ~ 8 のいずれか一項に記載の回路装置。

**【請求項 1 0】**

前記クロック発振器 ( P S ) は、少なくとも 1 つの位相ロックループとして構成されることを特徴とする請求項 9 に記載の回路装置。

**【請求項 1 1】**

前記クロック発振器 ( P S ) は、少なくとも 1 つのクロックマルチプライヤユニットとして構成されることを特徴とする請求項 1 0 に記載の回路装置。

**【請求項 1 2】**

前記シリアルライザ ( S E ) は、

前記送信インターフェースロジック ( L S ) の下流の、前記共通信号ストリーム ( S I ) のための、前記受信装置 ( E ) で認識可能な少なくとも 1 つのフレームを生成するための少なくとも 1 つのフレーマ ( F R ) と、10

前記フレーマ ( F R ) の下流の、前記共通信号ストリーム ( S I ) を生成するための少なくとも 1 つのマルチブレクサ ( M U ) と、

を備えることを特徴とする請求項 9 ~ 1 1 のいずれか一項に記載の回路装置。

**【請求項 1 3】**

前記シングルエンド論理レベルベースのデータ信号 ( H S D 0 , H S D 1 , H S D 2 , H S D 3 ) と前記差動データ信号 ( D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - ) との両方を、前記フレーマ ( F R ) に印加することができること、および、前記フレーマは、少なくとも 1 つの符号器 ( K O ) を用いて、前記差動データ信号 ( D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - ) を、前記シングルエンド論理レベルベースのデータ信号 ( H S D 0 , H S D 1 , H S D 2 , H S D 3 ) のストリームに埋め込むことを特徴とする請求項 1 2 に記載の回路装置。20

**【請求項 1 4】**

前記少なくとも 1 つの符号器は、少なくとも 1 つの 5 b / 6 b 符号器ブロックである請求項 1 3 に記載の回路装置。

**【請求項 1 5】**

前記受信装置 ( E ) は、

前記送信装置 ( S ) によって送信された前記共通信号ストリーム ( S I ) のための少なくとも 1 つの入力部 ( E E ) と、30

前記共通信号ストリーム ( S I ) を受け取るための少なくとも 1 つの入力増幅器 ( E V ) と、

前記データ信号およびクロック信号を前記共通信号ストリーム ( S I ) から復元するための少なくとも 1 つのクロックおよびデータリカバリユニット ( C D ) と、

前記クロックおよびデータリカバリユニット ( C D ) の下流の、少なくとも 1 つの受信インターフェースロジック ( L E ) の少なくとも 1 つのクロックモジュール ( C E ) と、

前記クロックおよびデータリカバリユニット ( C D ) の下流の、前記データ信号を再並列化するための、および再並列化された前記データ信号を前記受信インターフェースロジック ( L E ) に割り当てるための少なくとも 1 つのデシリアルライザ ( D S ) と、40

前記受信インターフェースロジック ( L E ) の下流の、前記データ信号およびクロック信号のための少なくとも 1 つの出力部 ( A E ) と、

を備えることを特徴とする請求項 1 ~ 1 4 のいずれか一項に記載の回路装置。

**【請求項 1 6】**

前記デシリアルライザ ( D S ) は、

前記クロックおよびデータリカバリユニット ( C D ) の下流の、前記データ信号を再並列化するための少なくとも 1 つのデマルチブレクサ ( D M ) と、

前記デマルチブレクサ ( D M ) の下流の、再並列化された前記データ信号を、前記受信インターフェースロジック ( L E ) に割り当てるための少なくとも 1 つのデフレーマ ( D F ) と、50

を備えることを特徴とする請求項 15 に記載の回路装置。

**【請求項 17】**

前記デフレーマ (DF) は、前記差動データ信号 (DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-) を、少なくとも 1 つの復号器 (DK) を用いて、前記シングルエンド論理レベルベースのデータ信号 (HSD0, HSD1, HSD2, HSD3) と分けて、再並列化された前記データ信号を、それぞれのデータライン (CH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-) に割り当てる特徴とする請求項 16 に記載の回路装置。

**【請求項 18】**

前記少なくとも 1 つの復号器は、少なくとも 1 つの 5b / 6b 復号器ブロックである請求項 17 に記載の回路装置。 10

**【請求項 19】**

シングルエンド論理レベルベースのデータ信号およびクロック信号 (HS) と、差動データ信号および差動クロック信号 (LP) との両方を、少なくとも 1 つのデータソースに割り当て可能な少なくとも 1 つの送信装置 (S) と、少なくとも 1 つのデータシンクに割り当て可能な少なくとも 1 つの受信装置 (E) との間で、

前記シングルエンド論理レベルベースのデータ信号およびクロック信号 (HS) と、前記差動データ信号および差動クロック信号 (LP) とをシリアル化する少なくとも 1 つの共通信号ストリーム (SI) の形態で、および 20

前記差動データ信号および差動クロック信号 (LP) と、バイナリ信号 (PD) との両方を備える少なくとも 1 つの全二重に基づく信号ストリームの形態で、伝送する方法。

**【請求項 20】**

前記差動データ信号はコモンモードベースである請求項 19 に記載の方法。

**【請求項 21】**

前記信号ストリームは双方方向の形態である請求項 19 又は 20 に記載の方法。

**【請求項 22】**

前記差動データ信号および差動クロック信号 (LP) と、前記バイナリ信号 (PD) とが、異なる周波数でスキャンされることを特徴とする請求項 19 ~ 21 のいずれか一項に記載の方法。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、請求項 1 のプリアンブルに記載の回路装置、ならびに請求項 19 のプリアンブルに記載の対応する方法に関する。

**【背景技術】**

**【0002】**

ビット伝送層または物理層 (physical layer: PHY) は、OSI (Open Systems Interconnection) 参照モデルとも呼ばれる OSI 階層モデルの最下位層であり、コンピュータネットワークにおける通信プロトコルの設計基準としても役に立つ、国際標準化機構 (International Standardization Organization: ISO) の階層モデルを示す。 40

**【0003】**

物理層 (PHY) は、結合、順方向誤り訂正 (Forward Error Correction: FEC)、電力制御、拡散 (符号分割多元接続) (Code Division Multiple Access: CDMA) 等に関与し、およびデータもアプリケーションも識別せず、0 と 1 のみを識別する。PHY は、その上のセキュリティ層 (データリンク層) (Data Link Layer: DLL) が、特に、媒体アクセス制御 (Media Access Control: MAC) 層と呼ばれる部分層を利用 50

可能な論理チャネル(UMTS(Universal Mobile Telecommunications System)用のトランスポートチャネル)を形成する。

【0004】

原理的に、D-PHYは、モバイル装置内のコンポーネント間の通信リンクのためのフレキシブルで、低コストで、高速のシリアルインターフェースを実現できる。

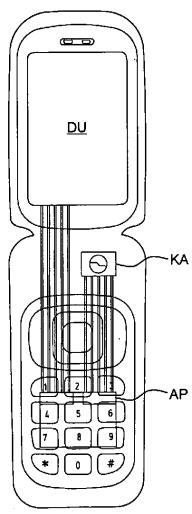

【0005】

図5Aに示すように、最新の携帯電話において、データソース、例えば、アプリケーションプロセッサは、関連するデータシンク上、例えば、関連するディスプレイ上の表示のために、イメージデータをD-PHY信号として、MIPI-DSI(Mobile Industry Processor Interface-Display Serial Interface)に供給する。また、アプリケーションプロセッサ等のデータシンクは、関連するデータソースから、例えば、関連するカメラから、MIPI-CSI(Camera Serial Interface)を介して、D-PHYフォーマットでイメージデータを受信することができる。

10

【0006】

D-PHYプロトコルに基づくDSIまたはDSI-2またはCSIまたはCSI-2またはCSI-3は、4つ以下の差動データラインと、差動クロックラインとを備え、これらは、銅ケーブルを用いて、該アプリケーションプロセッサを該ディスプレイおよび/または該カメラに接続する。差動データライン当たりのデータ転送速度は、最高で1.5Gbps(ギガビット/秒)である。

20

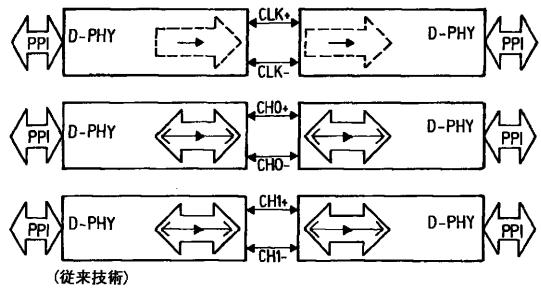

【0007】

1~4つの差動データ信号および差動クロックラインを介した、この従来のD-PHY-DSI信号またはD-PHY-CSI信号の送信および受信は、マスター側のモジュール(データソース、例えば、カメラおよび/またはアプリケーションプロセッサ)と、スレーブ側のモジュール(データシンク、例えば、アプリケーションプロセッサおよび/またはディスプレイユニット)との間の(データレーンCH0+, CH0-およびCH1+, CH1-と呼ばれる)2つの双方向データチャネルおよび(クロックレーンCLK+, CLK-と呼ばれる)クロックラインを手段として、図5BのD-PHYインターフェース構造に例として図示されている。その双方向マルチデータレーン構造において、図5Bの略語PPIは、「PHY Protocol Interface」を表す。

30

【0008】

この状況において、図5Aを見て分かるように、各関連するディスプレイのための、または、各関連するカメラのためのデータ伝送には、最高10の銅線(例えば、2つのデータラインの4倍と、2つのクロックラインの1倍)を要する。それに対応して、例えば、高解像度スクリーン、テレビ受像機またはカメラは、電気的MIPI(Mobile Industry Processor Interface)-D-PHYデータ伝送インターフェースを備える。

【0009】

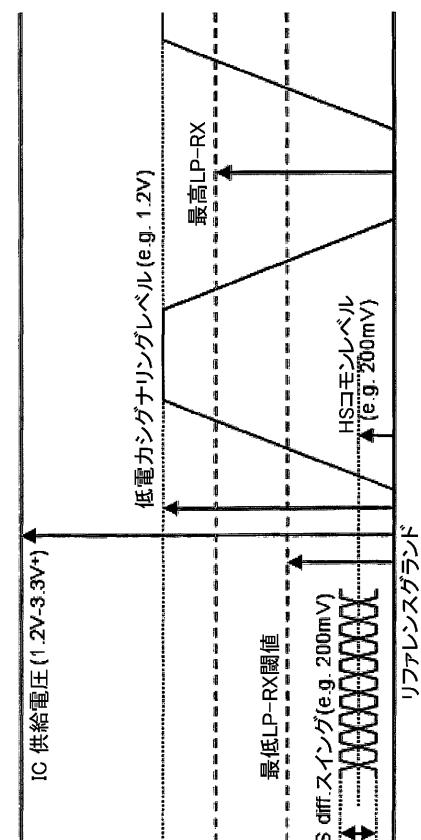

このインターフェースは、高速(High Speed: HS)データと低電力(Low Power: LP)データの両方を送信するのに用いられ、この場合、該LPデータのデータ転送速度は、典型的には、該HSデータのデータ転送速度よりもかなり遅い。これは図4に図示されており、該図において、それぞれの電圧レベルが、HSデータ伝送およびLPデータ伝送の場合について図示されている。

40

【0010】

これに関連して、MIPI-D-PHY規格に関するガイドラインが、HS/LPデータの伝送に対して義務付けられている。LPデータは、MIPI固有のプロトコルに従わなければならず、これは、小さな帯域幅、例えば、I2C(Inter-Integrated Circuit)、シリアル周辺機器インターフェース(Serial Peripheral Interface: SPI)またはその他のプロトコル等を用いた、シリアルデータの伝送のための既に確立されている業界標準の送信ができず、最後に述べた

50

プロトコルは、D - P H Y - H S データの伝送が必要であり、加えて、該プロトコルは、P H Y 準拠ではない追加的なバイナリデータの伝送も要する。

#### 【 0 0 1 1 】

具体的には、関連するM I P I 規格は、L P データであっても、双方向の、同時に双方向ではない、すなわち、全二重（全二重伝送）ではないが、半二重（交互伝送）での伝送を可能にする。

#### 【 0 0 1 2 】

そのため、M I P I - D - P H Y に準拠し、加えて、M I P I 規格に準拠しないL P データは別として、シリアルデータを便宜的に全二重（全二重伝送）で送信しなければならない場合、2つまたは3つの別々の電気ラインを、例えば、M I P I - D - P H Y に準拠しないL P データを伝達するための公知のD - P H Y システムに設けなければならない。10

#### 【 0 0 1 3 】

このことは、いくつかの用途、例えば、以下の用途、すなわち、

小さなリンクを備えた携帯電話、または、

その意図した目的を考慮して、本質的に、全体にわたって最小限の直径を有していなければならぬ内視鏡、

において、ケーブルが延びている場合、幾何学的な問題またはスペースの問題につながる可能性がある。

#### 【 0 0 1 4 】

このような別々のラインも、その通常のユニポーラデータラインが電磁エネルギーを放射するため、問題を引き起こす。20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 5 】

上述した欠点および不十分な点を発端として、ならびに概略が説明された従来技術を考慮して、本発明の目的は、全二重伝送が可能な方法で、上述したタイプの回路装置および上述したタイプの方法をさらに発展させることである。

#### 【課題を解決するための手段】

#### 【 0 0 1 6 】

この目的は、請求項1の特徴を有する回路装置と、請求項13の特徴を有する方法によって達成される。本発明の有利な実施形態および適切なさらなる発展は、それぞれの従属項において特徴付けられている。30

#### 【 0 0 1 7 】

したがって、それを用いて、

論理レベルに基づく信号に対応するシングルエンドH S データと、

特に、コモンモード信号に基づく信号に対応する差動L P データと、

が、共通信号ストリームを形成するようにシリアル化される回路装置および方法が提案される。

#### 【 0 0 1 8 】

この共通信号シリアル化信号ストリームに加えて、少なくとも1つの追加的な電気的またはガルバニックなリンクを介して、具体的には、少なくとも1つの追加的な銅ケーブルを介して、および／または例えば、少なくとも1つのプリント回路基板上に配置された追加的な電気ラインを介して一括化された、L P データのための、および同時に、さらなる多数の様々なバイナリデータのための全二重データ伝送が可能にされる。40

#### 【 0 0 1 9 】

本発明は、典型的には、シングルエンド論理レベルベースのデータ信号およびクロック信号と、特に、コモンモードベースの、差動データ信号およびクロック信号との両方の、具体的には、D - P H Y データ信号またはD - P H Y クロック信号、例えば、1～4ビット幅のM I P I - D - P H Y データ信号およびM I P I - D - P H Y クロック信号の、少なくとも1つのデータソース、具体的には、例えば、少なくとも高解像度カメラおよび／50

または画像ソースとして機能するカメラおよび／または少なくとも1つのアプリケーションプロセッサと、少なくとも1つのデータシンク、具体的には、少なくとも1つのアプリケーションプロセッサおよび／または少なくとも1つの高解像度ディスプレイユニットまたは例えば、画像シンクとして機能するディスプレイユニット、例えば、少なくとも1つのディスプレイまたは少なくとも1つのモニタとの間での、シリアルおよび／または一括の、具体的には、CSIプロトコルベースのおよび／またはCSI-2プロトコルベースのおよび／またはCSI-3プロトコルベースのおよび／またはDSIプロトコルベースのおよび／またはDSI-2プロトコルベースの伝送中に適用することができる。

#### 【0020】

前述したように、本発明に関する教示を有利な方法で具体化し、およびさらに発展させるための様々な可能性がある。このため、一方において、請求項1に従属する請求項について、および請求項13について説明し、他方においては、本発明の追加的な実施形態、特徴および効果が、以下により詳細に、とりわけ、図1A～図4によって図示されている例示的な実施形態によって説明されている。

10

#### 【図面の簡単な説明】

#### 【0021】

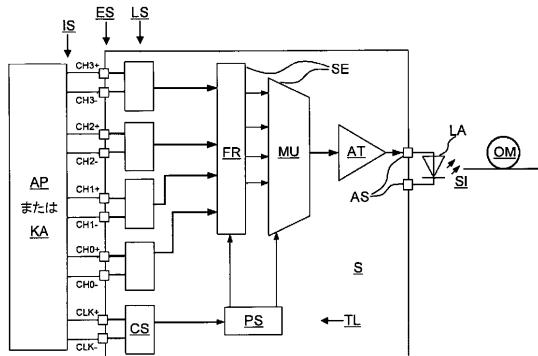

【図1A】本発明の方法に従って作動する、本発明による送信装置の実施形態の概念的略図である。

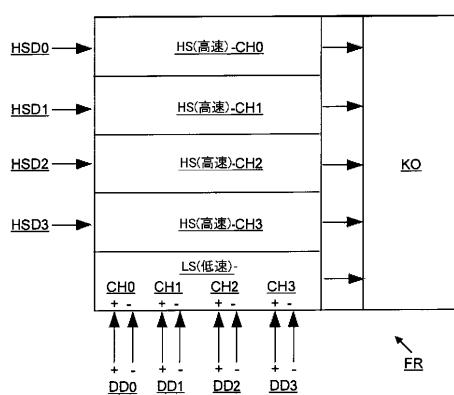

【図1B】図1Aにおける送信装置のフレーマの実施形態の詳細を示す、概念的略図である。

20

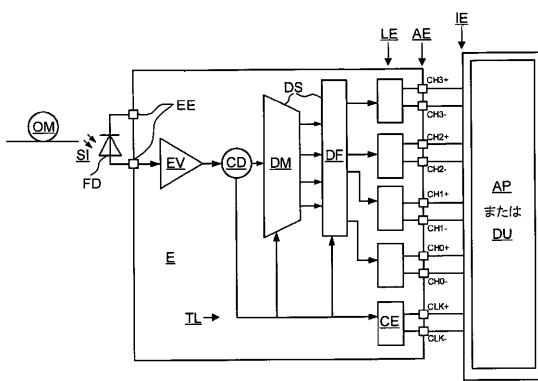

【図2A】本発明の方法に従って作動する、図1Aの送信装置に関連する受信装置の実施形態の概念的略図である。

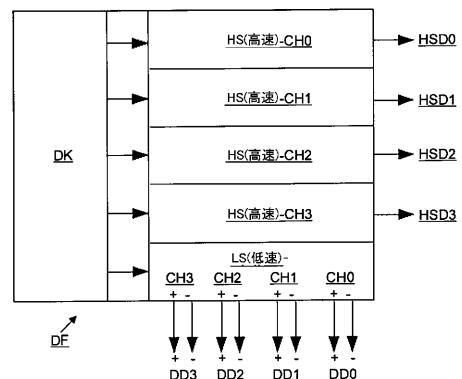

【図2B】図2Aの受信装置のデフレーマの実施形態の詳細を示す、概念的略図である。

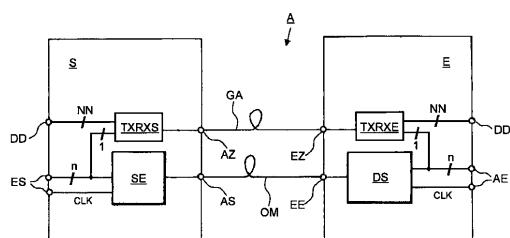

【図3A】本発明の方法に従って作動する、本発明による回路装置の実施形態の概念的略図である。

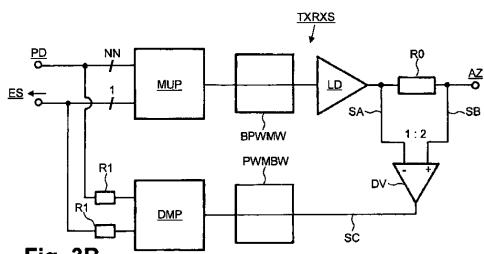

【図3B】図3Aによる回路装置における送信装置および受信装置の両方に含まれている送信／受信モジュールの実施形態の概念的略図である。

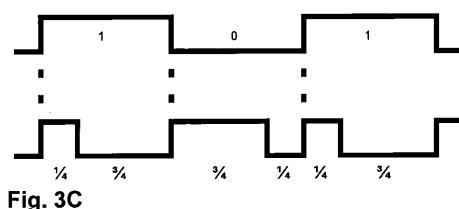

【図3C】図3Bの送信／受信モジュールに含まれているバイナリパルス幅変調（Pulse Width Modulation：PWM）コンバータを用いて実行することができるPWMの実施形態の概略図である。

30

【図4】HSデータ伝送およびLPデータ伝送の場合のそれぞれの電圧レベルの実施形態の概略図である。

【図5A】従来技術による典型的な装置の概念的略図である。

【図5B】図5Aに示す装置がそれをベースにしている、2つのデータチャネルとクロックラインとを備えるインターフェース構造の実施例の概念的略図である。

#### 【発明を実施するための形態】

#### 【0022】

図1A～図5Bにおいて、類似のまたは同様の実施形態、要素または機能には、同一の参照数字が付けられている。

#### 【0023】

40

(発明を具体化するための最良の方法)

原理的には、

本発明による送信装置Sに関する図1Aに示す実施形態によって、および

本発明による受信装置Eに関する図2Aに示す実施形態によって、

ケーブルベースのリンクを実現するおよび作動させるための、本発明による回路装置A(図3を参照)の実施形態が全体で得られ(本発明に関しては、互いに無関係に、送信装置Sと受信装置Eを実現すること、および作動させることが可能である)、

そのリンクは、光学的に、具体的には、少なくとも1つの光学媒体に基づいて、例えば、光導波路OM(図1A、図2Aの詳細図を参照)に基づいて、例えば、少なくとも1つのガラス纖維に基づいて、および／または少なくとも1つのプラスチック纖維に基づいて

50

多重化され、およびシリアル化され、および / または

そのリンクは、電気的にまたはガルバニックに、具体的には、少なくとも 1 つの電気的またはガルバニックなリンク G A ( 図 3 を参照 ) に基づいて、例えば、少なくとも 1 つの銅線に基づいて、および / または例えば、少なくともプリント回路基板上に配列された少なくとも 1 つの電気的ラインに基づいて多重化されていないことが可能である。

#### 【 0 0 2 4 】

図 1 A は、 D S I データ伝送インターフェース I S または C S I データ伝送インターフェース I S への接続のための送信装置 S の原理的構造の実施形態を示す。

#### 【 0 0 2 5 】

アプリケーションプロセッサ A P 内で、または、カメラ K A 内で生成された画像データは、 D - P H Y 補正クロック信号 C L K + , C L K - とともに、最高で 4 ビット幅のデータ伝送インターフェース I S において、 4 つ他のデータラインまたはデータチャネル C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - 上で D - P H Y 信号として利用可能になっている。

#### 【 0 0 2 6 】

送信装置 S は、これらの信号を集積インターフェースロジック L S において受け取り、そのブロックは、それらの信号が、 D - P H Y 信号の正しい解釈のための、および高周波データストリーム ( いわゆるシングルエンド論理レベルベースの信号に相当する H S データ ) と低周波データストリーム ( いわゆる特に、コモンモードベースの差動信号に相当する低速 ( L o w S p e e d : L S ) データ ) を区別するための少なくとも 1 つの状態機械を有することを証明できる。

#### 【 0 0 2 7 】

送信装置 S 内で後に続くフレーマ F R ( 図 1 B の詳細図も参照 ) は、入力信号の直流 ( D i r e c t C u r r e n t : D C ) 平衡を確保し、および受信側 ( 図 2 A を参照 ) で認識可能なフレームを生成し、そのことは、受信装置 E ( 図 2 A を参照 ) が、補正出力データラインまたは出力チャネル C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - に、受信したデータを再割当てすることを可能にする。

#### 【 0 0 2 8 】

詳細には、論理レベルベースのシングルエンドデータ信号 H S D 0 , H S D 1 , H S D 2 , H S D 3 と、差動データ信号 D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - の両方を、図 1 B によるフレーマ F R に印加することができる。 5 b / 6 b 符号化ロックとして構成されたその符号器 K O を用いて、図 1 B による該フレーマは、それらの差動データ信号 D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - を、シングルエンド論理レベルベースのデータ信号 H S D 0 , H S D 1 , H S D 2 , H S D 3 から成るストリームに埋め込む。

#### 【 0 0 2 9 】

フレーマ F R に隣接するマルチプレクサ M U 、具体的には、 H S M u x は、位相ロックループとして、具体的には、 C M U として構成されたクロック発振器 P S を用いて、高周波シリアルまたは一括送信信号を生成し、その信号は、出力ドライバ A T を用いて、送信装置 S の出力 A S において利用可能になっている。フレーマ F R とマルチプレクサ M U は、一緒にシリアルライザ S E を構成している。

#### 【 0 0 3 0 】

クロック発振器 P S を用いて、クロックポート C L K + , C L K - を介して、およびインターフェースロジック L S のクロックモジュール C S を介して供給された D - P H Y クロック信号は、シリアルライザ S E のための、具体的には、そのマルチプレクサ M U のための ( クロック ) 基準として用いられ、および該シリアルデータストリームに、すなわち、シリアル化された出力信号に埋め込まれる。これにより、受信装置 E ( 図 2 A を参照 ) に伝達される共通信号ストリーム S I が生成される。

#### 【 0 0 3 1 】

10

20

30

40

50

さらに図1Aを見て分かるように、出力ドライバATは、少なくとも1つの直接接続されたレーザLAを駆動するための、具体的には、少なくとも1つの面発光レーザ(Vertical Cavity Surface Emitting Laser diode:VCSEL)を駆動するための一体型レーザドライバとして実装されている。

【0032】

図2Aは、DSIデータ伝送インターフェースIEまたはCSIデータ伝送インターフェースIEへの接続のための受信装置Eの原理的構造の実施形態を示す。

【0033】

送信装置S(図1Aを参照)によって送出されたシリアルまたは一括データは、受信装置Eの入力増幅器EVを介して受け取られて、集積クロックまたはデータリカバリCDへ供給される。

10

【0034】

この集積クロックまたはデータリカバリCDは、共通信号ストリームSIから元のD-PHYクロックを再生し、その後、該クロックは、インターフェースロジックLEのクロックモジュールCEを介して、再び、DSIまたはCSIが直接、利用できるようにされる。残りのシリアルデータストリームは、デマルチプレクサDMによって細分化されて並列化され、原理的には、図1BによるフレーマFRの鏡像であるデフレーマDF(図2Bも参照)へ引き渡される。デマルチプレクサDMとデフレーマDFは、一緒にデシリアルライザDSを構成する。

【0035】

詳細には、図2BのデフレーマFRは、6b/5b復号器ブロックとして構成されたその復号器DKを用いて、差動データ信号は、DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-と、シングルエンド論理レベルベースのデータ信号HSD0, HSD1, HSD2, HSD3を分けて、再並列化されたデータ信号を、それぞれの適用可能なデータラインCH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-に再割り当てすることができる。

20

【0036】

受信装置E内に図示されているインターフェースロジックブロックLEは、それぞれ、D-PHY論理信号の正しい解釈のための、および高周波データストリームと低周波データストリームを区別するための少なくとも1つの状態機械を備えていてもよい。

30

【0037】

図2Aの説明図を見ても分かるように、入力増幅器EVは、集積トランスインピーダンス増幅器として実装され、該増幅器は、フォトダイオードFDを受信装置Eに直接接続することを可能にしている。

【0038】

このようにして、本発明によれば、回路装置A(図3を参照)に関しては、送信装置S(図1Aを参照)と受信装置E(図2Aを参照)との間で、ケーブルベースの多重化リンクを光学的に、すなわち、例えば、ガラス纖維の形態および/またはプラスチック纖維の形態で構成された光導波路OMを用いて実現し、および作動させることが可能である。

40

【0039】

図3は、送信装置S(図1Aを参照)および受信装置E(図2Aを参照)全体の実施形態を示す。これは、シリアルリンクを備えた、または、並列化されたデータストリームを伴うD-PHY伝送路である。

【0040】

この目的のために、D-PHY-HS/LPデータは、本質的に、シリアルライザSEと、特に、マルチプレクサMUとを備える送信装置S(図1Aを参照)によって一括化されて、シリアルデータストリームとして受信装置E(図2Aを参照)へ送信される。

【0041】

本質的に、シリアルライザDSと、ここでは特に、デマルチプレクサDMとを備えるこの受信装置E(図2Aを参照)は、該シリアルデータを細分化して、それを元の形態でD

50

- P H Y - H S / L P データとして再出力する。送信装置 S ( 図 1 A を参照 ) に印加される D - P H Y - クロック ( C l o c k : C L K ) は、シリアルライザ S E のためのクロック基準として用いられ、および該シリアルデータストリームに埋め込まれる。受信装置 E ( 図 2 A を参照 ) は、このクロックを再生して、それを D - P H Y - C L K として再出力する。

#### 【 0 0 4 2 】

銅ケーブルの形態の、または、例えば、プリント回路基板上に配置された例えは電気ラインの形態の独立したガルバニックなリンク G A は、少なくとも 1 つの D - P H Y レーンの D - P H Y - L P データを伝達するのに利用できる。本発明によれば、このガルバニックなリンク G A は、通常、このツイストペアで送信される D - P H Y - L P データと、さらなるデータ P D との両方を送信する目的で用いられる。10

#### 【 0 0 4 3 】

この目的のために、マルチプレクサ M U に隣接する送信装置 S ( 図 1 A を参照 ) と、一括化された D - P H Y - H S / L P データのためのデマルチプレクサ D M に隣接する受信装置 E ( 図 2 A を参照 ) の両方は、図 3 A を見て分かるように、送信 / 受信モジュール T X R X S / T X R X E ( 単に説明を明確にするために、図 1 A または図 2 A には図示せず ) も備えている。

#### 【 0 0 4 4 】

この送信 / 受信モジュール T X R X S / T X R X E は、L P モードの D - P H Y レーンのデータを、数 N N の他の並列 P D データとともに一括化する。後者の P D データは、この時点で、D - P H Y レーンの L P データとともに、送信装置 S ( 図 1 A を参照 ) と受信装置 E ( 図 2 A を参照 ) との間で、全二重送信することができ、「送信装置」および「受信装置」という名称は、マルチプレクサ M U からデマルチプレクサ D M までの一方向の送信機能を意味するものとする。20

#### 【 0 0 4 5 】

図 3 B に示すように、送信 / 受信モジュール T X R X S / T X R X E は、ここでもまた、マルチプレクサ M U を備え、該マルチプレクサは、L P データと、P D データを一括化して、マルチプレクサ M U P の下流のラインドライバ L D によって、反対側の送信 / 受信モジュール T X R X S / T X R X E へ送る。

#### 【 0 0 4 6 】

同時に、デマルチプレクサ D M P の上流の差動増幅器 D V は、1 : 2 の比で重み付けされた信号 S A および S B を減算し、結果、反対側によって印加された送信信号を、ローカル伝送信号と分離することができる。差動増幅器 D V の後で、このようにして得られた信号 S C は、デマルチプレクサ D M P へ供給され、該デマルチプレクサ D M P は、L P 信号および信号 P D の後で受信したシリアルデータストリームを分解する。30

#### 【 0 0 4 7 】

図 3 A に示す送信装置 S の追加的な出力部 A Z と、受信装置 E の追加的な入力部 E Z との間の信号を、独立したクロックラインを延ばすことなく伝送できるようにするために、ラインドライバ L D からのデータは、バイナリ / P W M コンバータ B P W M W によって、バイナリ非ゼロ復帰 ( N o n R e t u r n - t o - Z e r o : N R Z ) フォーマットから、図 3 C に示すパルス幅変調信号へ変えられる ( 図 3 C の上のライン : バイナリ信号 ; 図 3 C の上のライン : パルス幅変調信号 )。40

#### 【 0 0 4 8 】

同様に、受信した信号 S C は、P W M / バイナリコンバータ P W M B W によって、P W M からバイナリ N R Z フォーマットへの変換という逆のプロセスを受ける。

#### 【 0 0 4 9 】

データ L P および P D は、図 3 B に示すように、異なる周波数でスキャンすることができる。したがって、データ L P は、データ P D よりも 8 倍多い頻度でスキャンすることができ、他のデータと比較して、L P ( 低電力 ) の場合の有効なデータ転送速度を増すことができる。50

## 【0050】

図3AのポートAZ, EZ間の電気的またはガルバニックなリンクGAは、差動ラインとして実施することができる。これは、一方で、電磁放射を低減し、他方で、誘導結合または容量結合によって、および浮動的に、この電気的またはガルバニックなリンクGAを分解する可能性を呈している。

## 【0051】

反射を伴うことなく、長距離にわたってデータを伝送できるようにするために、ライントライバルDの下流の終端抵抗R0を、使用するラインの特性インピーダンスに従って選択することができる。

## 【0052】

一方で、最適と思われる上述した誘導結合または容量結合と、例えば、光データ伝送をサポートするために、他方で、受信側でのデータストリームの同期を確実にするために、生成されたシリアル信号の直流電圧からの自由度をもたらす以下に示す符号化/復号化システムを、図3BによるマルチプレクサMUPおよび図3BによるデマルチプレクサDMUPに用いることができる。すなわち、

## 【0053】

D<sub>P</sub>およびD<sub>N</sub>の場合のコード：

## 【0054】

## 【数1】

0△01

1△10

10

## 【0055】

GPTON<sub>x</sub>の場合のコード：

## 【0056】

## 【数2】

0△00

1△11

20

30

## 【0057】

## 【数3】

D<sub>P</sub>|D<sub>N</sub>|G<sub>1</sub>|11|D<sub>P</sub>|D<sub>N</sub>|G<sub>1</sub>|00|D<sub>P</sub>|D<sub>N</sub>|G<sub>2</sub>|00|D<sub>P</sub>|D<sub>N</sub>|G<sub>2</sub>|00|...

## 【0058】

フレームおよびビット位置

## 【0059】

## 【数4】

40

XOR, XOR, XNOR, AND, XOR, XOR, XNOR, NOR

## 【0060】

上述した本発明による解決法は、ラインGAを介して一括化された、D-PHY-LPデータ、および同時に、さらなる多数の様々なバイナリデータPDの全二重データ伝送を可能にする。

## 【符号の説明】

## 【0061】

50

|           |                                                                                    |    |

|-----------|------------------------------------------------------------------------------------|----|

| A         | 回路装置                                                                               |    |

| E         | 受信装置                                                                               |    |

| S         | 送信装置                                                                               |    |

| A E       | 受信装置 E の出力部                                                                        |    |

| A P       | アプリケーションプロセッサ                                                                      |    |

| A S       | 送信装置 S の出力部                                                                        |    |

| A T       | 出力ドライバ、具体的には、レーザドライバ                                                               |    |

| A Z       | 送信装置 S の他のまたはさらなるまたは追加的な出力部                                                        |    |

| B P W M W | バイナリ / PWM (パルス幅変調) コンバータ                                                          |    |

| C D       | クロックおよびデータリカバリユニット                                                                 | 10 |

| C E       | 受信インターフェースロジック L E のクロックモジュール                                                      |    |

| C H 0 ±   | 第 1 のデータラインまたは第 1 のチャネル                                                            |    |

| C H 1 ±   | 第 2 のデータラインまたは第 2 のチャネル                                                            |    |

| C H 2 ±   | 第 3 のデータラインまたは第 3 のチャネル                                                            |    |

| C H 3 ±   | 第 4 のデータラインまたは第 4 のチャネル                                                            |    |

| C L K ±   | クロックラインまたはクロックチャネル                                                                 |    |

| C S       | 送信インターフェースロジック L S のクロックモジュール                                                      |    |

| D D 0 ±   | 第 1 のデータラインまたは第 1 のチャネル C H 0 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                       |    |

| D D 1 ±   | 第 2 のデータラインまたは第 2 のチャネル C H 1 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                       | 20 |

| D D 2 ±   | 第 3 のデータラインまたは第 3 のチャネル C H 2 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                       |    |

| D D 3 ±   | 第 4 のデータラインまたは第 4 のチャネル C H 3 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                       |    |

| D F       | デフレーマ                                                                              |    |

| D K       | デフレーマ D F の復号器、具体的には、6 b / 5 b 復号器ブロック                                             |    |

| D M       | デマルチプレクサ                                                                           |    |

| D M P     | 受信装置 E の送信 / 受信モジュール T X R X E における、および送信装置 S の送信 / 受信モジュール T X R X S におけるデマルチプレクサ | 30 |

| D S       | デシリアルライゼーション要素またはデシリアルライザ                                                          |    |

| D U       | ディスプレイユニット                                                                         |    |

| D V       | 差動増幅器                                                                              |    |

| E E       | 受信装置 E の入力部                                                                        |    |

| E S       | 送信装置 S の入力部                                                                        |    |

| E V       | 入力増幅器、具体的には、トランスインピーダンス増幅器                                                         |    |

| E Z       | 受信装置 E の他のまたはさらなるまたは追加的な入力部                                                        |    |

| F D       | フォトダイオード                                                                           |    |

| F R       | フレーマ                                                                               |    |

| G A       | 電気的またはガルバニックなリンク、具体的には、例えば、プリント回路基板上に配置された銅線または電気的ライン                              | 40 |

| H S       | 高速                                                                                 |    |

| H S D 0   | 第 1 のデータラインまたは第 1 のチャネル C H 0 ± 上のシングルエンド論理レベルベースのデータ信号                            |    |

| H S D 1   | 第 2 のデータラインまたは第 2 のチャネル C H 1 ± 上のシングルエンド論理レベルベースのデータ信号                            |    |

| H S D 2   | 第 3 のデータラインまたは第 3 のチャネル C H 2 ± 上のシングルエンド論理レベルベースのデータ信号                            |    |

| H S D 3   | 第 4 のデータラインまたは第 4 のチャネル C H 3 ± 上のシングルエンド論理レベルベースのデータ信号                            | 50 |

I E データシンク関連の C S I および / または C S I - 2 および / または C S I - 3

および / または D S I および / または D S I - 2 インタフェース

I S データソース関連の C S I および / または C S I - 2 および / または C S I - 3

および / または D S I および / または D S I - 2 インタフェース

K A カメラ

K O フレーマの符号器、具体的には、5 b / 6 b 符号器ブロック

L A レーザ

L D ラインドライバ

L E 受信インターフェースロジック

L P 低電力

10

L S 送信インターフェースロジック

M U マルチプレクサ

M U P 受信装置 E の送信 / 受信モジュール T X R X E における、および送信装置 S の送

信 / 受信モジュール T X R X S におけるマルチプレクサ

O M 光学媒体、具体的には、光導波路、例えば、ガラス纖維および / またはプラスチ

ック纖維

P D バイナリおよび / または並列信号

P S クロック発振器、具体的には、位相ロックループ、例えば、クロックマルチプラ

イヤユニット

P W M B W P W M / バイナリコンバータ

20

R 0 終端抵抗器

R 1 抵抗器

S A 第 1 の重み付け信号

S B 第 2 の重み付け信号

S C 差動増幅器 D V の後の信号

S E シリアライゼーション要素またはシリアルライザ

S I 共通信号ストリーム

T L クロックライン

T X R X E 受信装置 E の送信 / 受信モジュール

T X R X S 送信装置 S の送信 / 受信モジュール

30

【図1A】

【図1B】

【図2A】

【図2B】

【図3A】

Fig. 3A

【図3B】

Fig. 3B

【図3C】

Fig. 3C

【図4】

【図 5 A】

(従来技術)

【図 5 B】

---

フロントページの続き

(72)発明者 ブロン , トーマス

ドイツ連邦共和国 80687 ミュンヘン エルゼンハイマーシュトラーセ 48 / デア・ツヴ

アイテン シリコン・ライン・ゲー・エム・ベー・ハーネ

(72)発明者 ヤンゼン , フロリアン

ドイツ連邦共和国 80687 ミュンヘン エルゼンハイマーシュトラーセ 48 / デア・ツヴ

アイテン シリコン・ライン・ゲー・エム・ベー・ハーネ

(72)発明者 グレーブル , マルティン

ドイツ連邦共和国 87527 ゾントホーフェン / オーバーアルゴイ オストラッハシュトラー

セ 7

審査官 阿部 弘

(56)参考文献 国際公開第2008/126753 (WO , A1)

特開2008-113321 (JP , A)

特開2006-153927 (JP , A)

特開2008-160370 (JP , A)

米国特許出願公開第2009/0238576 (US , A1)

特開2006-033804 (JP , A)

特開2010-050847 (JP , A)

特開2001-103028 (JP , A)

(58)調査した分野(Int.Cl. , DB名)

H04L 25/02

H04L 25/49