(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6349856号

(P6349856)

(45) 発行日 平成30年7月4日(2018.7.4)

(24) 登録日 平成30年6月15日(2018.6.15)

(51) Int.Cl.

HO2M 1/08 (2006.01)

F 1

HO2M 1/08

A

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2014-66597 (P2014-66597)

(22) 出願日 平成26年3月27日 (2014.3.27)

(65) 公開番号 特開2015-192491 (P2015-192491A)

(43) 公開日 平成27年11月2日 (2015.11.2)

審査請求日 平成29年2月15日 (2017.2.15)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100106149

弁理士 矢作 和行

(74) 代理人 100121991

弁理士 野々部 泰平

(74) 代理人 100145595

弁理士 久保 貴則

(72) 発明者 長瀬 拓生

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 坂東 博司

最終頁に続く

(54) 【発明の名称】 駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

負荷(300)を駆動するパワースイッチング素子(200)のゲート電流を制御して、前記パワースイッチング素子をオンするオン側回路(110)と、主電源に対して前記オン側回路と直列に接続され、前記パワースイッチング素子をオフするオフ側回路(120)とを備え、前記パワースイッチング素子のゲートが前記オン側回路と前記オフ側回路との中間点に接続された駆動装置であって、

前記パワースイッチング素子のコレクタ電流の電流値に基づいて、前記パワースイッチング素子のゲート電流を制御する保護回路(130)を備え、

該保護回路は、

前記パワースイッチング素子のゲート電荷を引き抜くための定電流を規定する定電流回路(131)と、

前記定電流回路と前記パワースイッチング素子のゲートとの電気的な接続を制御する保護スイッチ(132)と、

前記パワースイッチング素子のコレクタ電流の電流値が、所定の閾値を上回ったことを検出するコレクタ電流検出部(133)と、を有し、

該コレクタ電流検出部は、前記パワースイッチング素子のコレクタ電流の電流値が、所定の閾値として前記負荷の短絡を示す第1閾値を上回ってから所定時間後に、前記オン側回路をオフして前記パワースイッチング素子を前記主電源から切り離すとともに、前記保護スイッチをオンするものであり、

10

20

前記パワースイッチング素子のコレクタ電流の閾値としての前記第1閾値に加えて、電流値が前記第1閾値よりも高い第2閾値が設定され、

前記コレクタ電流検出部は、前記パワースイッチング素子のコレクタ電流が、前記第2閾値よりも高い状態から遷移して前記第2閾値に達するまで、前記保護スイッチをオン状態とすることを特徴とする駆動装置。

**【請求項2】**

前記第1閾値は、一定のコレクタ電流のもとで予め測定された前記パワースイッチング素子のセンスエミッタ端子の電圧(S E)に対応した値に設定されることを特徴とする請求項1に記載の駆動装置。 10

**【請求項3】**

前記第2閾値は、一定のコレクタ電流のもとで予め測定された前記パワースイッチング素子のセンスエミッタ端子の電圧に対応した値に設定されることを特徴とする請求項1または請求項2に記載の駆動装置。 10

**【請求項4】**

前記パワースイッチング素子のコレクタ電流の閾値として、電流値が前記第1閾値および前記第2閾値よりも高い第3閾値が設定され、

前記コレクタ電流検出部は、前記パワースイッチング素子のコレクタ電流が前記第3閾値を上回ってから、予め設定されたフィルタ時間後に、前記保護スイッチをオンすることを特徴とする請求項1～3のいずれか1項に記載の駆動装置。 20

**【請求項5】**

前記保護スイッチがオンされた時刻以降に前記オフ側回路をオンする場合においては、前記保護スイッチがオンされなかった場合に較べて、前記オフ側回路のドライブ能力を低下させることを特徴とする請求項1～4のいずれか1項に記載の駆動装置。 20

**【請求項6】**

前記パワースイッチング素子のコレクタ電流の電流値が、前記第1閾値を上回ってから所定時間後に、前記オン側回路をオフして前記パワースイッチング素子を前記主電源から切り離す場合において、

前記オン側回路を完全にオフすることなく、前記主電源から前記パワースイッチング素子のゲートに、前記保護回路における前記定電流回路により供給される電流よりも小さい電流を注入することを特徴とする請求項1～5のいずれか1項に記載の駆動装置。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、パワースイッチング素子のオンオフ制御および異常時の保護を行う駆動装置に関する。

**【背景技術】**

**【0002】**

パワースイッチング素子により駆動される負荷が短絡すると、パワースイッチング素子に急峻に過大な電流が流れる。この過電流からパワースイッチング素子を保護するための回路が種々提案されている。しかしながら、このような保護回路が備えられた駆動回路は、パワースイッチング素子のスイッチングノイズ等に起因して保護回路が誤って動作し、パワースイッチング素子の駆動が意図せず停止するという問題も生じる。 40

**【0003】**

これに対して、特許文献1に記載の保護回路は、負荷の短絡が検出されると、パワースイッチング素子のゲート電圧を抵抗分圧により低下させて電流を抑制する。そして、短絡検出用の閾値以上の電流が所定時間継続して流れている場合に負荷の短絡と判断し、パワースイッチング素子の駆動を停止させる。

**【0004】**

しかしながら、特許文献1に記載の保護回路では、短絡保護に際して、ゲート電圧を一律に低下させるため、パワースイッチング素子の製造ばらつきに起因する閾値電圧のばら 50

つきにより、パワースイッチング素子に流れる電流にばらつきが生じてしまう。この電流値のばらつきによって、上記所定時間内に、電流値が短絡検出用の閾値を下回ってしまうと、短絡保護動作が誤って解除されてしまう。この誤解除を防止するために、短絡検出用の閾値を大きく設定しなければならず、パワースイッチング素子へのストレスが大きくなってしまう。

#### 【0005】

また、分圧用の抵抗とパワースイッチング素子のゲート容量によってゲート電圧の波形がなまり、ゲート電圧抑制時の時定数が大きくなってしまう。このため、パワースイッチング素子の電流を低下させるための所要時間が長くなってしまい、ストレスが大きい。

#### 【0006】

一方、特許文献2に記載の電力変換装置は、短絡の検出時において、パワースイッチング素子のゲート電圧をツェナーダイオードにより抑制する方式を採用している。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献1】特開平3-40517号公報

【特許文献2】特開2010-154595号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

20

特許文献2に記載の方式では、ゲート電圧を急峻に低下させることができ、ゲート電圧抑制時の時定数の問題は解決できる。しかし、一般に、ツェナーダイオードは温度や製造ばらつきに起因する特性のばらつきが大きく、短絡保護動作の誤解除の問題を解決することはできない。

#### 【0009】

また、ゲート電圧抑制時にゲート電圧の下降速度を制御することが困難であるため、パワースイッチング素子の電流にリングを生じてしまい、パワースイッチング素子にサージ電圧が印加される原因となる。

#### 【0010】

本発明は、上記問題点を鑑みてなされたものであり、パワースイッチング素子のオンオフ制御および異常時の保護を行う駆動装置において、負荷短絡で過大な電流が流れたときにゲート電圧を適切に制御して保護することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0011】

ここに開示される発明は、上記目的を達成するために以下の技術的手段を採用する。なお、特許請求の範囲およびこの項に記載した括弧内の符号は、ひとつの態様として後述する実施形態に記載の具体的手段との対応関係を示すものであって、発明の技術的範囲を限定するものではない。

#### 【0012】

40

上記目的を達成するために、本発明は、負荷(300)を駆動するパワースイッチング素子(200)のゲート電流を制御して、パワースイッチング素子をオンするオン側回路(110)と、主電源に対してオン側回路と直列に接続され、パワースイッチング素子をオフするオフ側回路(120)とを備え、パワースイッチング素子のゲートがオン側回路とオフ側回路との中間点に接続された駆動装置であって、パワースイッチング素子のコレクタ電流の電流値に基づいて、パワースイッチング素子のゲート電流を制御する保護回路(130)を備え、該保護回路は、パワースイッチング素子のゲート電荷を引き抜くための定電流回路(131)と、定電流回路とパワースイッチング素子のゲートとの電気的な接続を制御する保護スイッチ(132)と、パワースイッチング素子のコレクタ電流の電流値が、所定の閾値を上回ったことを検出するコレクタ電流検出部(133)と、を有し、該コレクタ電流検出部は、パワースイッチング素子のコレクタ電流の

50

電流値が、所定の閾値として負荷の短絡を示す第1閾値を上回ってから所定時間後に、オン側回路をオフしてパワースイッチング素子を主電源から切り離すとともに、保護スイッチをオンするものであり、パワースイッチング素子のコレクタ電流の閾値としての第1閾値に加えて、電流値が第1閾値よりも高い第2閾値が設定され、コレクタ電流検出部は、パワースイッチング素子のコレクタ電流が、第2閾値より高い状態から遷移して第2閾値に達するまで、保護スイッチをオン状態とすることを特徴としている。

#### 【0013】

これによれば、短絡によるコレクタ電流の増加を抑制するためにパワースイッチング素子のゲートから電荷を引き抜く際、その引き抜き先として定電流回路が設けられている。このため、パワースイッチング素子のゲート電荷は、一定の早さで引き抜かれることになる。換言すれば、ゲート電圧ひいてはコレクタ電流を一定のスルーレートで低減することができる。したがって、ゲート電圧ひいてはコレクタ電流の波形のなまりや、これら電圧や電流が急激に減少することによるリングを抑制することができる。

#### 【図面の簡単な説明】

#### 【0014】

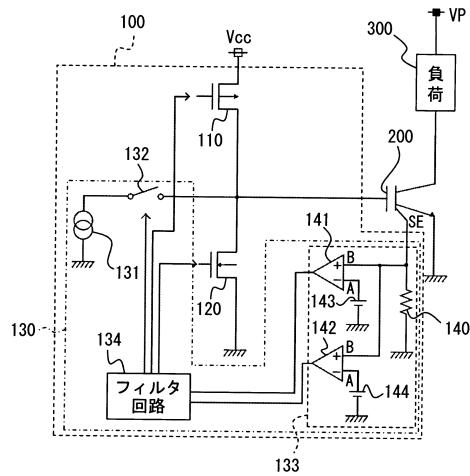

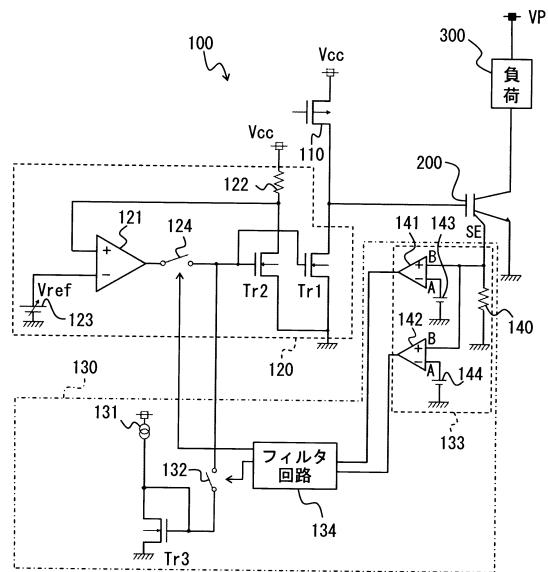

【図1】第1実施形態に係る駆動装置の概略構成を示す回路図である。

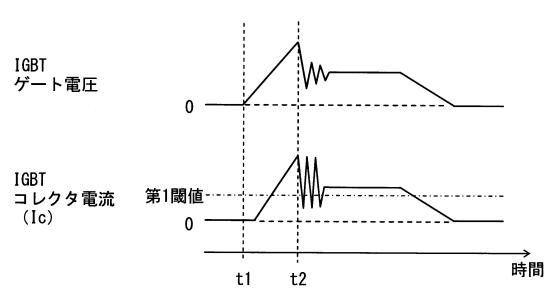

【図2】従来構成における駆動装置の駆動を示すタイミングチャートである。

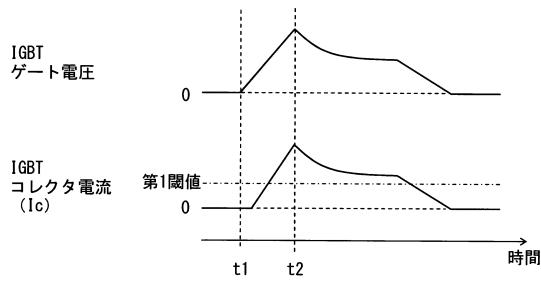

【図3】従来構成における駆動装置の駆動を示すタイミングチャートである。

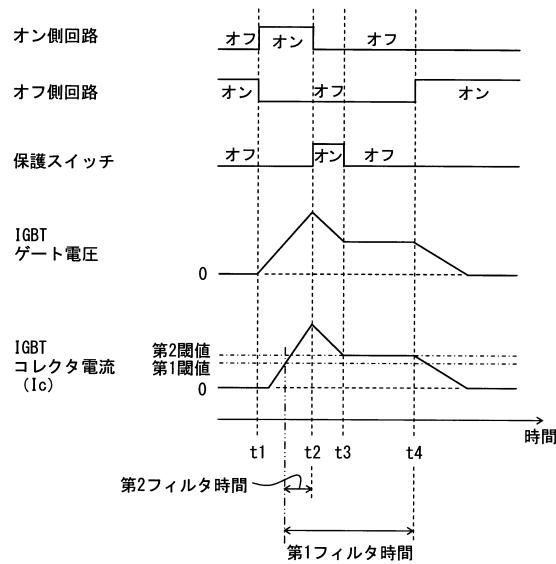

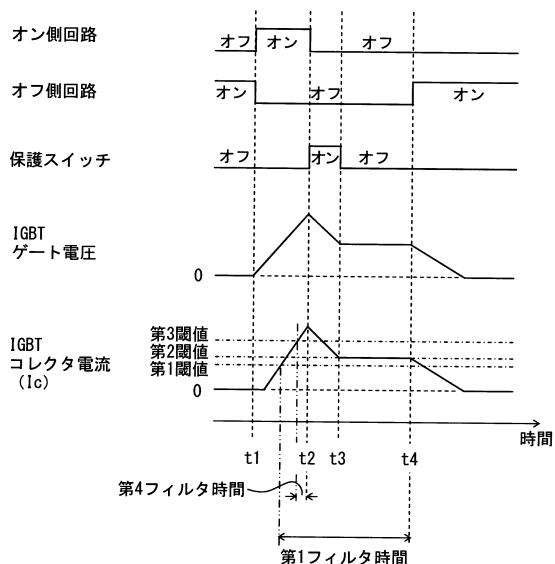

【図4】第1実施形態に係る駆動装置の駆動を示すタイミングチャートである。

【図5】変形例1に係る駆動装置の駆動を示すタイミングチャートである。

【図6】第2実施形態に係る駆動装置の概略構成を示す回路図である。

#### 【発明を実施するための形態】

#### 【0015】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

#### 【0016】

##### (第1実施形態)

最初に、図1を参照して、本実施形態に係る駆動装置の概略構成について説明する。

#### 【0017】

図1に示すように、この駆動装置100は、負荷300を駆動するパワースイッチング素子としての絶縁ゲートバイポーラトランジスタ(IGBT)200の駆動を制御するものである。

#### 【0018】

この駆動装置100は、オン側回路110と、オフ側回路120と、保護回路130と、を備えている。

#### 【0019】

オン側回路110およびオフ側回路120は主電源とGNDとの間で直列に接続され、その中間点にIGBT200のゲートが接続されている。オン側回路110は、PMOSトランジスタにより構成され、このPMOSトランジスタがオン状態のときにはIGBT200のゲートに電源電圧Vccが印加される。これによりIGBT200がオン状態になり、IGBT200のコレクタ-エミッタ間に電流が流れ、負荷300に電力が供給される。

#### 【0020】

オフ側回路120は、NMOSトランジスタにより構成され、このNMOSトランジスタがオン状態のときにはIGBT200のゲートから電荷が引き抜かれてIGBT200がオフ状態になる。

#### 【0021】

保護回路130は、IGBT200のコレクタ電流Icに基づいて、IGBT200のゲート電流、ひいてはゲート電圧を制御する。この保護回路130は、IGBT200のゲート電荷を一定の割合で引き抜くための定電流回路131と、該定電流回路131とI

10

20

30

40

50

GBT 200との電気的な接続を制御して定電流回路131の有効／無効を規定する保護スイッチ132と、IGBT 200のコレクタ電流Icを検出するコレクタ電流検出部133と、を有している。

#### 【0022】

コレクタ電流検出部133は、負荷300の短絡に起因するIGBT 200のコレクタ電流の異常を検出する回路である。このコレクタ電流検出部133は、IGBT 200のコレクタ電流Icを電圧に変換するための抵抗器140と、コンパレータ141, 142と、コンパレータ141, 142の入力端子Aに閾値となる電圧を与える電圧源143, 144と、を有している。

#### 【0023】

より詳しく説明する。図1に示すように、コンパレータ141の一方の入力端子Aには電圧源143が接続されている。そして、他方の入力端子Bは、IGBT 200のセンスエミッタ端子SEとGNDとの間に接続された抵抗器140との中間点に接続されている。すなわち、コンパレータ141における入力端子Bには、IGBT 200のセンスエミッタ端子SEからGNDに向かって流れる電流と抵抗器140の抵抗値に対応した電圧が印加されている。入力端子Bに印加される電圧は、センスエミッタ端子SEからGNDに向かって流れる電流に比例する。つまり、この電圧はIGBT 200のコレクタ電流が大きくなるほど高電圧となる。

#### 【0024】

コンパレータ141は、センスエミッタ端子SEを流れる電流に対応した電圧が、電圧源143の電圧を超えた場合、すなわち、コレクタ電流Icが所定の閾値（負荷300の短絡を示す第1閾値）を超えた場合に、後述のフィルタ回路134を介して保護スイッチ132をオンし、オン側回路110をオフするように制御信号を出力する。

#### 【0025】

コンパレータ142についても、コンパレータ141と同様の構成である。すなわち、コンパレータ142の一方の入力端子Aには電圧源144が接続されている。そして、他方の入力端子Bは、IGBT 200のセンスエミッタ端子SEとGNDとの間に接続された抵抗器140との中間点に接続されている。

#### 【0026】

そして、コンパレータ142は、センスエミッタ端子SEを流れる電流に対応した電圧が、電圧源144の電圧に到達した場合、すなわち、コレクタ電流Icが所定の閾値（特許請求の範囲に記載の第2閾値に相当）に到達した場合に、フィルタ回路134を介して保護スイッチ132をオフするように制御信号を出力する。

#### 【0027】

上記したように、電圧源143はIGBT 200にとって負荷300が短絡状態にあると判断されるような電圧が設定され、第1閾値を規定している。また、電圧源144は第1閾値よりも高い電圧が設定され、第2閾値を規定している。

#### 【0028】

先出のフィルタ回路134は、信号が入力されてから、予め設定された所定のフィルタ時間後に、入力に対応した制御信号を出力する回路である。

#### 【0029】

例えば、本実施形態におけるフィルタ回路134は、IGBT 200のコレクタ電流Icが第1閾値を上回ると、予め設定された第1フィルタ時間後にオフ側回路120をオンするように制御信号を出力する。加えて、フィルタ回路134は、IGBT 200のコレクタ電流が第1閾値を上回ると、予め設定された第2フィルタ時間後に、保護スイッチ132をオンするとともに、オン側回路110をオフするように制御信号を出力する。

#### 【0030】

また、本実施形態におけるフィルタ回路134は、IGBT 200のコレクタ電流Icが第2閾値よりも高い状態から第2閾値に到達すると、予め設定された第3フィルタ時間後に保護スイッチ132をオフするように制御信号を出力する。なお、後述する、駆動装

10

20

30

40

50

置 1 0 0 の動作の説明において、この第 3 フィルタ時間は、便宜上ゼロに設定されている。すなわち、フィルタ回路 1 3 4 は、IGBT 2 0 0 のコレクタ電流  $I_c$  が第 2 閾値よりも高い状態から第 2 閾値に到達すると同時に、保護スイッチ 1 3 2 をオフするように制御信号を出力する。

#### 【 0 0 3 1 】

なお、このフィルタ回路 1 3 4 は、IGBT 2 0 0 のスイッチングノイズ等によって、保護回路 1 3 0 が誤って動作することを防止するために設けられている。

#### 【 0 0 3 2 】

次に、図 2 ~ 図 4 を参照して、本実施形態に係る駆動装置 1 0 0 の動作および作用効果について説明する。

10

#### 【 0 0 3 3 】

まず、従来技術において、IGBT 2 0 0 の保護動作が行われた場合の挙動について説明する。

#### 【 0 0 3 4 】

特許文献 1 に記載の保護回路は、低下させた後のゲート電圧の値を抵抗分圧によって規定する方式を採用している。このため、図 2 に示すように、時刻  $t_2$  において保護回路が動作し、ゲート電圧の低下が開始されても、長い時定数のため、コレクタ電流  $I_c$  の大きな状態が維持されてしまう。その結果、IGBT 2 0 0 へのストレスが大きくなってしまう。また、ゲート電圧の値を抵抗分圧により一定値に規定する方式であるため、IGBT 2 0 0 のゲート容量ばらつきに起因してゲート電流にばらつきが生じてしまう。

20

#### 【 0 0 3 5 】

また、特許文献 2 に記載の電力変換装置は、ゲート電圧の値をツェナーダイオードにより規定する方式を採用している。このため、図 3 に示すように、時刻  $t_2$  において保護回路が動作するとゲート電圧が急激に減少して、ゲート電圧およびコレクタ電流  $I_c$  にリンクギングが発生してしまう。コレクタ電流  $I_c$  にリンクギングが発生すると、コレクタ電圧に大きなサーボ電圧が印加されてしまう。

#### 【 0 0 3 6 】

次いで、図 4 を参照して、本実施形態に係る駆動装置 1 0 0 による保護動作が行われた場合の挙動について説明する。

#### 【 0 0 3 7 】

30

図 4 において、時刻  $t_1$  以前は IGBT 2 0 0 がオフの状態である。すなわち、オフ側回路 1 2 0 がオン（有効）状態、かつ、オン側回路 1 1 0 がオフ（無効）状態であり、IGBT 2 0 0 のゲートには電圧が印加されていない。

#### 【 0 0 3 8 】

時刻  $t_1$  において、図示しない制御部により IGBT 2 0 0 をオンする旨の制御信号を受けると、駆動装置 1 0 0 におけるオン側回路 1 1 0 がオンされ、オフ側回路 1 2 0 がオフされる。これにより、IGBT 2 0 0 のゲート電圧が上昇を始める。ゲート電圧が IGBT 2 0 0 に固有の閾値電圧（いわゆる  $V_{th}$ ）を超えると、IGBT 2 0 0 にコレクタ電流  $I_c$  が流れ始める。

#### 【 0 0 3 9 】

40

ここで、負荷 3 0 0 が短絡していた場合、IGBT 2 0 0 には過大なコレクタ電流  $I_c$  が流れることになる。コレクタ電流  $I_c$  が電圧源 1 4 3 により規定された第 1 閾値を超えると、フィルタ回路 1 3 4 が第 1 フィルタ時間のカウントを開始する。また、本実施形態では、第 1 フィルタ時間のカウントと同時に、第 2 フィルタ時間のカウントも開始される。

#### 【 0 0 4 0 】

コレクタ電流  $I_c$  が第 1 閾値を超えてから第 2 フィルタ時間後である時刻  $t_2$  において、保護スイッチ 1 3 2 がオンされると同時に、オン側回路 1 1 0 がオフされる。これにより、IGBT 2 0 0 のゲートは主電源および GND から切り離された状態となり、ゲート電荷は定電流回路 1 3 1 のみによって引き抜かれる。換言すれば、ゲートからの電荷の引

50

き抜きが、定電流回路 131 によって一定の早さで行われる。これによれば、ゲート電圧を一定のスルーレートで低減することができる。したがって、ゲート電圧の波形のなまりや、ゲート電圧が急激に減少することによるリンギングを抑制することができる。

#### 【0041】

I G B T 2 0 0 のゲートから電荷が引き抜かれることにより、ゲート電流が第 2 闘値よりも高い状態から下降して第 2 闘値に到達する（時刻  $t_3$ ）と、保護スイッチ 132 がオフされる。これにより、I G B T 2 0 0 のゲートは電気的にフローティングとなる。仮に、負荷 3 0 0 の短絡が偽であった場合にはコレクタ電流  $I_c$  は第 1 闘値を下回るため、オン側回路 110 がオンされ、I G B T 2 0 0 は通常動作に戻る。負荷 3 0 0 の短絡が真であつた場合には、ゲート電圧は一定であり、コレクタ電流  $I_c$  も一定値を維持する。

10

#### 【0042】

そして、コレクタ電流  $I_c$  が第 1 闘値を超えてから第 1 フィルタ時間後である時刻  $t_4$ において、オフ側回路 120 がオン状態となり、I G B T 2 0 0 は動作を停止する。これにより、I G B T 2 0 0 は過大な電流から保護される。

#### 【0043】

このように、コレクタ電流検出部 133 が I G B T 2 0 0 のコレクタ電流  $I_c$  をモニタし、その電流値が第 2 闘値に達した時点でゲートがフローティングとされるため、コレクタ電流  $I_c$  を I G B T 2 0 0 のゲート容量ばらつきに依存せず一定に維持することができる。つまり、保護スイッチ 132 をオフした後も、コレクタ電流  $I_c$  のばらつきを抑制することができる。これにより、第 2 闘値を第 1 闘値にできるだけ近い値に設定することができる。第 2 闘値が第 1 闘値に対して大きい値の場合、コレクタ電流  $I_c$  が高い状態で維持されて、I G B T 2 0 0 へのストレスが大きくなってしまう。これに対して、本実施形態では、従来の構成に較べて第 2 闘値を第 1 闘値に近づけることができるため、I G B T 2 0 0 へのストレスを小さくすることができる。

20

#### 【0044】

##### （変形例 1）

上記した第 1 実施形態においては、コレクタ電流  $I_c$  の闘値として、負荷 3 0 0 の短絡を示す第 1 闘値と、第 1 闘値よりも高い値に設定された第 2 闘値を有する例について説明した。第 1 実施形態に較べてノイズ耐量を向上させるものとして、第 2 闘値よりも電流値の高い第 3 闘値を設定することもできる。

30

#### 【0045】

第 1 実施形態においては、コレクタ電流  $I_c$  が第 1 闘値を超えた場合に、オフ側回路 120 をオンするための第 1 フィルタ時間、および、保護スイッチ 132 をオンするための第 2 フィルタ時間のカウントが開始されるように構成されていた。これに対して、本変形例では、図 5 に示すように、コレクタ電流  $I_c$  が第 1 闘値を超えた場合には、第 1 フィルタ時間のみがカウントを開始される。そして、コレクタ電流  $I_c$  が第 3 闘値を超えると、保護スイッチ 132 をオンするための第 4 フィルタ時間のカウントが開始される。

#### 【0046】

これによれば、I G B T 2 0 0 を保護するための保護スイッチ 132 をオンする闘値が、第 1 闘値および第 2 闘値よりも高い第 3 闘値に設定されるから、コレクタ電流  $I_c$  に、第 1 闘値を超えるようなパルスノイズが発生した場合でも、誤って保護スイッチ 132 がオンされることを回避することができる。したがって、第 1 実施形態に較べてノイズ耐量を向上させることができる。

40

#### 【0047】

##### （変形例 2）

保護スイッチ 132 がオンされた時刻以降にオフ側回路 120 をオンする場合においては、保護スイッチ 132 がオンされなかった場合に較べて、オフ側回路 120 のドライブ能力を低下させるおくことが好ましい。つまり、例えば図 4 において、保護スイッチ 132 が動作した時刻  $t_2$  以降の時刻  $t_4$  において、オフ側回路 120 をオンする場合には、保護スイッチ 132 が動作しない、すなわち負荷 3 0 0 の短絡が生じていない通常駆動の

50

場合に較べて、オフ側回路 120 のドライブ能力を低下させておくと良い。

#### 【0048】

負荷 300 が短絡した状態では、IGBT200 のコレクタ電流  $I_c$  が定格を大きく超えている。このため、通常動作と同じドライブ能力を以ってオフ側回路 120 をオンすると、コレクタ電圧が急激に上昇して過大なサージ電圧が発生する虞があり、IGBT200 の故障の原因となる。上記したように、負荷 300 に短絡が発生して保護スイッチ 132 が動作した場合には、負荷 300 の短絡が生じていない通常駆動の場合に較べて、オフ側回路 120 のドライブ能力を低下させておくことによって、コレクタ電圧のサージを抑制することができる。

#### 【0049】

10

##### (変形例 3)

また、IGBT200 のコレクタ電流  $I_c$  の電流値が、第 1 閾値を上回ってから所定時間後（例えば、第 1 実施形態においては第 2 フィルタ時間後）に、オン側回路 110 をオフして IGBT200 を主電源から切り離す場合において、オン側回路 110 を完全にオフすることなく、主電源から IGBT200 のゲートに、定電流回路 131 により供給される電流よりも小さい電流を注入するようにすることが好ましい。

#### 【0050】

20

具体的には、図 4 および図 5 における時刻  $t_2$  において、IGBT200 のゲート電荷を定電流回路 131 によって引き抜くと同時に、オン側回路 110 を構成するMOSトランジスタのゲートに閾値電圧近傍の電圧を印加して、主電源からゲートに対して微小電流を供給する。これによれば、ゲート電流およびゲート電圧のスルーレートを小さくして、これら電流および電圧の低下に伴うアンダーシュートを抑制することができる。したがって、上記した第 1 実施形態およびその変形例に較べて、時刻  $t_3$  後のコレクタ電流  $I_c$  のばらつきを抑制することができる。

#### 【0051】

30

##### (第 2 実施形態)

第 1 実施形態およびその各変形例では、保護回路 130 における定電流回路 131 が IGBT200 のゲートに直接接続されることによってゲート電荷を引き抜く例について説明した。しかしながら、保護回路 130 は、コレクタ電流  $I_c$  に基づいて、IGBT200 のゲート電流を制御可能に構成されなければよい。

#### 【0052】

30

例えば、図 6 に示すように、IGBT200 のゲート電流を、オフ側回路 120 を介して引き抜く構成としてもよい。以下、具体的に説明する。なお、コレクタ電流検出部 133 およびフィルタ回路 134 は第 1 実施形態と同様の構成であるため、その説明を割愛する。

#### 【0053】

40

この駆動装置 100 は、オフ側回路 120 として、2 つのN MOSトランジスタ ( $T_{r1}, T_{r2}$ ) を有している。これら N MOSトランジスタは、出力トランジスタとしてのメインMOSトランジスタ  $T_{r1}$  と、メインMOSトランジスタ  $T_{r1}$  のドレイン電流を規定するセンスMOSトランジスタ  $T_{r2}$  とから構成されている。本実施形態では、メインMOSトランジスタ  $T_{r1}$  が、センスMOSトランジスタ  $T_{r2}$  に対してカレントミラーを構成するようになっている。具体的には、メインMOSトランジスタ  $T_{r1}$  のゲートはセンスMOSトランジスタ  $T_{r2}$  のゲートと共にされ、ソースが共通して GND に接続されている。メインMOSトランジスタ  $T_{r1}$  のドレインは IGBT200 のゲートに接続されている。

#### 【0054】

このような構成では、メインMOSトランジスタ  $T_{r1}$  には、センスMOSトランジスタ  $T_{r2}$  とのサイズ比と同一の電流比でドレイン電流が流れる。

#### 【0055】

また、オフ側回路 120 は、センスMOSトランジスタ  $T_{r2}$  のドレイン電流を制御す

50

るためのオペアンプ 121 と、該オペアンプ 121 の出力を規定するための基準抵抗 122 と、該オペアンプ 121 の一つの入力端子に参照電位  $V_{ref}$  を与える参照電源 123 と、を有している。オペアンプ 121 は、図示しない制御部などから IGBT 200 をオフさせることを示す制御信号が入力されると、センス MOS ドランジスタ Tr2 のゲートに電圧を印加することで、IGBT 200 のゲートから一定の電流が引き抜かれるようになっている。

#### 【0056】

基準抵抗 122 は、シャント抵抗であり、センス MOS ドランジスタ Tr2 のドレイン電流の電流値を規定する。ひいては、IGBT 200 のゲートから引き抜かれる電流の電流値を規定する。IGBT 200 のゲートから引き抜かれる電流は、メイン MOS ドランジスタ Tr1 に流れるドレイン電流である。そして、メイン MOS ドランジスタ Tr1 はセンス MOS ドランジスタ Tr2 とともにカレントミラーを構成しているので、IGBT 200 のゲートから引き抜かれる電流はセンス MOS ドランジスタ Tr2 のドレイン電流に依存する。

10

#### 【0057】

このような構成では、IGBT 200 をオフさせることを示す制御信号が入力されると、オペアンプ 121 が駆動されてセンス MOS ドランジスタ Tr2 にゲート電圧が印加される。このときのドレイン電流は基準抵抗 122 の抵抗値 R により規定される。そして、その電流値は、基準抵抗 122 とセンス MOS ドランジスタ Tr2との間の接続点の電位が、参照電位  $V_{ref}$  に近づくように、オペアンプ 121 の出力が調整されることによりフィードバック制御される。これにより、センス MOS ドランジスタ Tr2 のドレイン電流が高精度に一定の値 ( $= (V_{cc} - V_{ref}) / R$ ) に制御される。よって、IGBT 200 のゲートから引き抜かれる電流も、高精度に一定電流とされる。

20

#### 【0058】

なお、オフ側回路 120 は、オペアンプ 121 によるメイン MOS ドランジスタ Tr1 への電流供給をオンオフする制御スイッチ 124 を有している。この制御スイッチ 124 がオン状態であれば、オペアンプ 121 からセンス MOS ドランジスタ Tr2 にゲート電圧が印加されてオフ側回路 120 がオン状態となる。

#### 【0059】

また、この駆動装置 100 は、第 1 実施形態と同様に、定電流回路 131 を有している。ただし、本実施形態における定電流回路 131 は、図 6 に示すように、オフ側回路 120 におけるメイン MOS ドランジスタ Tr1 とカレントミラーを構成する NMOS ドランジスタ Tr3 にドレイン電流を与えるように接続されている。メイン MOS ドランジスタ Tr1 と NMOS ドランジスタ Tr3 は、互いのゲートがスイッチを介して接続されている。このスイッチがオン状態であれば、メイン MOS ドランジスタ Tr1 と NMOS ドランジスタ Tr3 がカレントミラーを構成し、定電流回路 131 により規定される電流が Tr1 のドレイン電流として流れ、IGBT 200 のゲート電荷を引き抜くようになっている。すなわち、このスイッチが上記した第 1 実施形態およびその変形例における保護スイッチ 132 に相当する。

30

#### 【0060】

本実施形態のように構成すれば、保護回路 130 による保護のための IGBT 200 からのゲート電流の引き抜きと、オフ側回路 120 によるオフ動作のための IGBT 200 からのゲート電流の引き抜きについて、一つの NMOS ドランジスタ、つまりメイン MOS ドランジスタ Tr1 を共用することができる。

40

#### 【0061】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上記した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

#### 【0062】

50

第1閾値および第2閾値について、一定のゲート電圧のもとで予め測定されたパワースイッチング素子のコレクタ電流に対応した値に設定されることが好ましい。図示しないが、駆動装置100にメモリ回路を設け、駆動装置100の出荷前検査（製造後に行われる特性検査）において測定されたIGBT200の所定のコレクタ電流Icに対するセンスエミッタ端子SEの電圧に対応した閾値をメモリに記憶するようにする。具体的には、センスエミッタ端子SEの電圧が大きいほど第1閾値および第2閾値の値を大きく設定し、通常のスイッチング動作時のノイズで、誤って短絡保護動作する誤動作を防止できる。また、第2閾値を出来る限り第1閾値に近づけるように設定することができるため、IGBT200のストレスを軽減することができる。

#### 【0063】

10

また、上記した各実施形態では、負荷300が短絡した場合の保護動作について記載したが、これに加えて、負荷300の短絡ほどではないにせよ、IGBT200のコレクタの定格以上の過大な電流が流れる過電流の状態においても、本発明を適用することができる。この場合は、第1閾値、第2閾値および第3閾値を、短絡の場合に較べて小さな値に設定する。

#### 【0064】

上記した各実施形態では、パワースイッチング素子としてIGBT200を例示したが、この例に限定されない。例えば、パワースイッチング素子として、パワーMOSトランジスタ等についても本発明を適用することができる。

#### 【符号の説明】

20

#### 【0065】

- 100・・・駆動装置

- 110・・・オン側回路

- 120・・・オフ側回路

- 130・・・保護回路

- 131・・・定電流回路

- 132・・・保護スイッチ

- 133・・・コレクタ電流検出部

- 200・・・パワースイッチング素子(IGBT)

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開2012-105088(JP,A)

特開2012-23899(JP,A)

特開2013-102694(JP,A)

特開2013-169102(JP,A)

特開平5-276761(JP,A)

特開2005-39573(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/08