(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

27 December 2002 (27.12.2002)

(10) International Publication Number

WO 02/103904 A2

(51) International Patent Classification<sup>7</sup>: H03K 17/00

(21) International Application Number: PCT/GB02/02732

(22) International Filing Date: 14 June 2002 (14.06.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

0114675.2 15 June 2001 (15.06.2001) GB

(71) Applicant (for all designated States except US): MARCONI APPLIED TECHNOLOGIES LIMITED [GB/GB]; Waterhouse Lane, Chelmsford, Essex CM1 2QU (GB).

(72) Inventors; and

(75) Inventors/Applicants (for US only): ISKANDER, Stephen, Mark [GB/GB]; 54 First Avenue, Chelmsford, Essex CM1 1RU (GB). RICHARDSON, Robert [GB/GB]; 42 King Edwards Road, South Woodham Ferrers, Chelmsford, Essex CM3 5PQ (GB). GOOCHE, Paul, Andrew [GB/GB]; Aviemore, Cock Road, Little Maplestead, Halstead, Essex CO9 2SH (GB).

(74) Agent: HUCKER, Nerys; Marconi Intellectual Property, Marrible House, The Vineyards, Great Baddow, Chelmsford, Essex CM2 7QS (GB).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: HIGH VOLTAGE SWITCHING APPARATUS

(57) Abstract: A switching arrangement for a high voltage load provides high voltage pulses to the load. The switching arrangement includes switching modules, where n is typically (75). A load capacitance is Cd is required to avoid voltage overshoot at the load and is provided by a capacitance of nCd arranged in parallel with each switch.

**HIGH VOLTAGE SWITCHING APPARATUS**

This invention relates to high voltage switching apparatus, and in particular, but not exclusively to a switching apparatus for providing pulses to a pulse switched load.

Our UK patent applications GB9929074.5 and GB9928049.7 describe a pulsed switching apparatus for an eht load such as a magnetron. A stack of FET switch modules are arranged in an oil filled chamber surrounded by four capacitors which are mounted within a plastics housing. The switch stack receives an eht supply, typically at about -55kV and delivers a series of eht pulses to the magnetron. The switch also includes various control circuitry which operates at 1t voltages. This circuitry controls functions such as triggering of the FET switches.

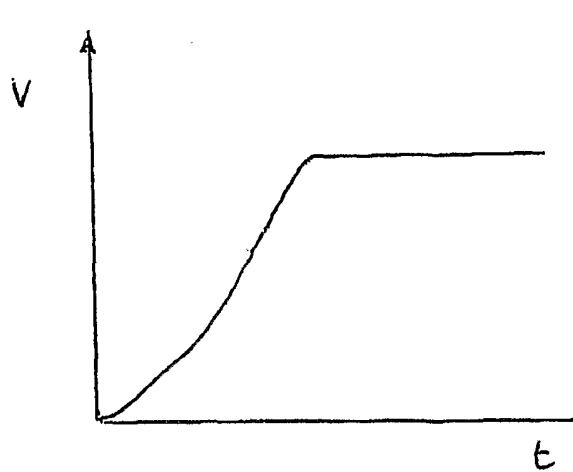

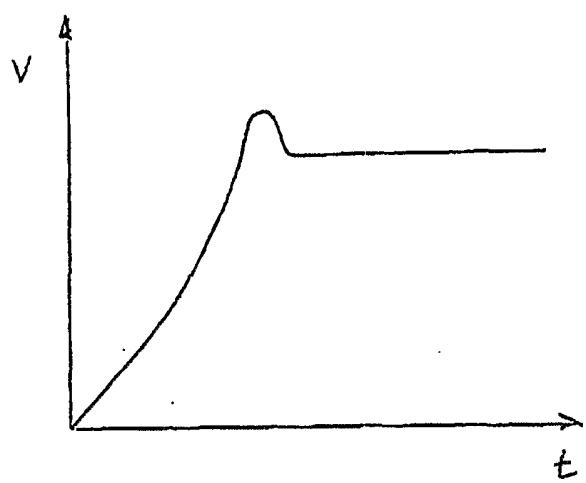

In these devices, when the load is switched, it is desirable for the voltage to rise smoothly to the operating voltage as shown in Figure 1. In practice, however, there is a tendency to a voltage overshoot as shown in Figure 2. This is because the load is not a purely resistive load but is of a non-linear nature and includes a capacitive component.

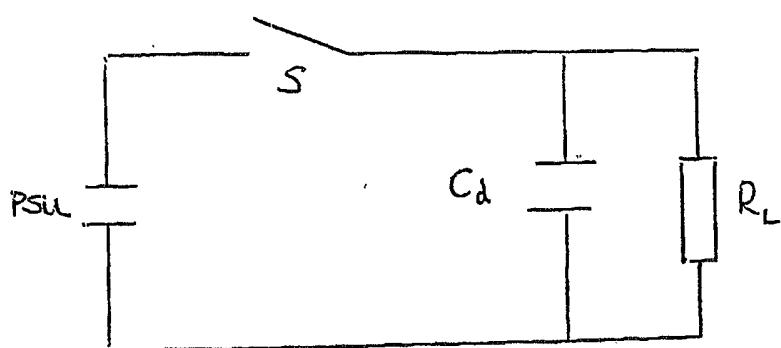

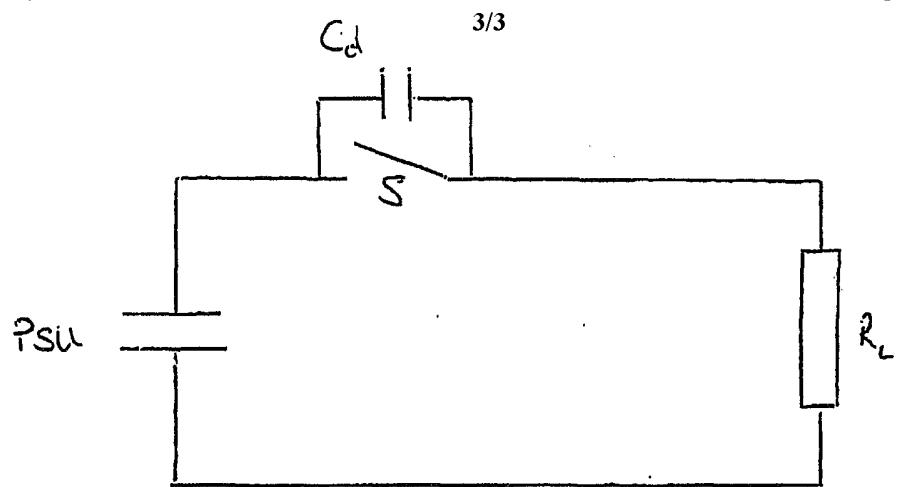

A known way of correcting for this voltage overshoot is to include a further capacitance in parallel with the load as shown in Figure 3. In that figure, the load is shown as  $R_L$ , the switch as S and the added capacitance as  $C_d$ . The problem with this approach is that the added capacitance is large, typically in the order of 200pF, expensive and very large in size. It is therefore desirable to find an alternative way of compensating for voltage overshoot.

In its broadest form, the invention distributes the load capacitance over the switches of the switch stack. More specifically, there is provided a high voltage switching arrangement for applying a pulse across a load, comprising a capacitor for providing electrical energy to the load and a switch stack for connecting the capacitor to the load, the

- 2 -

switch stack comprising a plurality of switches arranged in series, and a plurality of load capacitances in parallel across the switches.

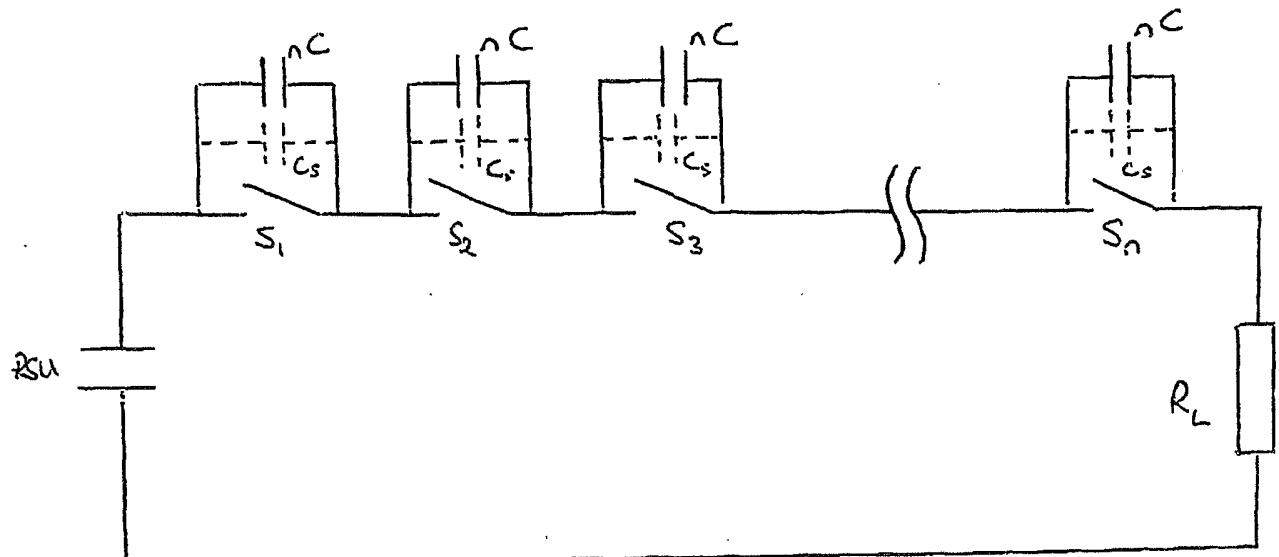

5 Preferably, each switch has a capacitance  $nCd$  in parallel across the switch, where  $Cd$  is the required additional capacitance across the load and  $n$  is the number of switches...

10 By arranging a capacitance  $nC$ , where  $n$  is the number of switches, across each switch in the switch stack, the effects of stray capacitances in the stack are avoided as the stray capacitances are swamped. This enables the voltage at each switch to be more closely controlled which is advantageous. Furthermore, the arrangement enables small cheap capacitors to be used with the switches instead of a 15 single expensive and very bulky load capacitor.

An embodiment of the invention will now be described, by way of example, and with reference to the accompanying drawings, in which:

20 Figure 1 (referred to previously) is a graph of voltage/time showing an ideal rise in load voltage when a switch is closed;

Figure 2 (referred to previously) is a similar graph to Figure 1 showing actual voltage rise including overshoot;

25 Figure 3 (referred to previously) is a circuit diagram if a known solution to the problem;

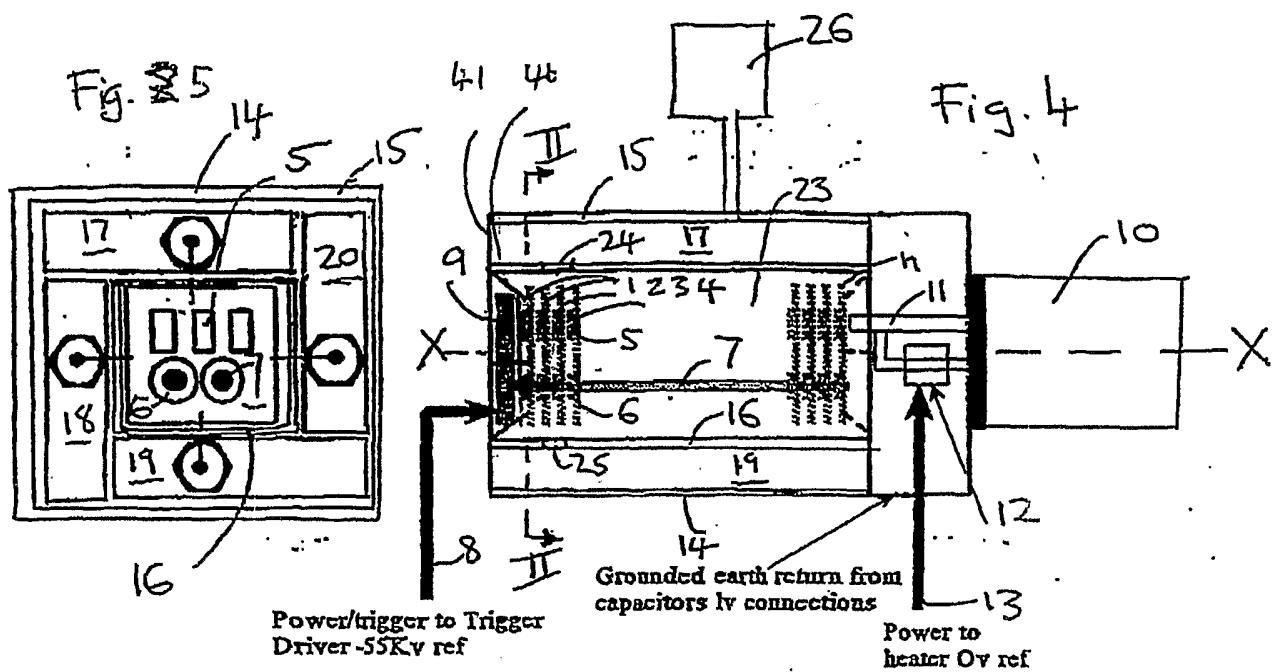

Figure 4 is a schematic longitudinal view of a high voltage switching mechanism;

30 Figure 5 is a schematic cross-section of the line V-V in Figure 4;

Figure 6 is a circuit diagram of an equivalent representation of the known circuit of Figure 3; and

35 Figure 7 shows how the capacitance of Figure 6 may be distributed in accordance with an embodiment of the invention.

35 Figures 4 and 5 show the switching mechanism disclosed in our earlier applications GB9928074.5 and GB9928049.7. The mechanism provides high voltage pulses to a high voltage

- 3 -

load, such as a magnetron, by switching a capacitance. The switching is triggered by trigger pulses derived from a high voltage supply and the capacitance is also charged by that supply.

The switching arrangement shown in Figures 4 and 5 comprises a switch stack arranged within a chamber surrounded by a plurality of capacitances. The switch stack comprises a number of FET modules 1, 2, 3, 4,...n, each of which includes one or more FET switches. There may be, for 10 example, 75 FET modules in the stack and each module may include three FET switches arranged in parallel. The modules are mounted in close proximity to one another and are stacked along the axis in Figure 1. As well as the FET switch, each module includes a secondary transformer winding 6 with a common primary winding 7 extending along the length of the axis to act as the primary for each module. The primary is used to provide power to the FET switches. Power to the switching arrangement is applied from a source 8 to a trigger driver 9 at the high voltage end of the stack which is maintained at -55kV. The trigger driver is formed 15 as a module of similar dimensions to the FET modules and forms the end module of the stack. The load 10, for example a magnetron, is connected to an output 11 of the switching mechanism to receive pulses from the switching mechanism. The output 11 also provides an output 12 to a heater transformer for heating the magnetron cathode. The power for 20 the transformer is provided from a power source 12.

The switching mechanism is arranged within a housing 14. The housing is formed of a non-conductive material such 25 as a plastics material and comprises outer and inner walls 15, 16 defining an annular chamber therebetween, and an interior chamber 23 bounded by the inner walls and in which the switching stack is arranged. The annular chamber and the interior chamber 23 communicate via apertures 24, 25 in the inner wall 16.

As can be seen from Figure 2, the housing and the annular and interior chambers are rectangular in cross

- 4 -

section. Four capacitors 17, 18, 19, 20 are arranged in the annular chamber, one on each side, and extend along the length of the chamber shielding the switching mechanism. The capacitors are connected at the high voltage end to the 5 first switch module and to the load 10 at the low voltage end, which may be at ground. The capacitors each comprise a plurality of parallel plates forming capacitor elements which are interconnected so that a nominally linear voltage gradient appears from the power supply end to the zero volt 10 end. The capacitors may each be 0.15  $\mu$ f.

The unit is oil filled for heat dissipation and insulation. Oil can pass between the annular and inner chambers through passageways 24, 25. An expansion tank 26 is connected to the chambers which includes a diaphragm, and 15 which moves with the changes in oil volume, for example due to temperature changes.

The switching stack also comprises a control module 40 which is mounted on the stack between the trigger driver module and the first FET module 1 and which is of similar 20 dimensions to the FET modules. The control module controls triggering of the FET switches and floats at the high voltage of -55kV but has its own 11 power supply to operate the control circuitry.

Figure 6 shows an equivalent circuit to the known 25 voltage overshoot solution in Figure 3. In this arrangement, the compensating capacitance is placed in parallel with the switch S.

It will be appreciated from the above description that 30 the switch is not a single switch but a series of switches. In a typical switch stack, there may be 75 switch modules. Each of these switches have their own capacitance  $C_s$  which may vary from switch to switch.

A capacitor may be placed across each of the switch 35 modules instead of a single capacitor across the load. However, to obtain the same capacitance, the value of each capacitor must be  $nC_d$ , where  $n$  is the number of switch modules, or looking at it another way, the number of series

- 5 -

connected capacitors. The value of  $nCd$  is such that the applied capacitance greatly exceeds and swamps any stray capacitances generated at the switch.

5 Figure 7 shows this arrangement. In Figure 7, each of the switches  $S_1, S_2 - S_n$  are shown with a capacitance  $nCd$  in parallel and a further capacitance  $C_s$  in phantom as the effect is minimal compared to the effect of  $nCs$ .

10 The arrangement described has a number of advantages. First, the provision of a large number of switch capacitor reduces costs as small surface mounted capacitors may be used which are more common place and very cheap, typically in the order of about 20p each. In contrast, a simple capacitance used in parallel with a magnetron is physically very big and expensive, typically in the order of about £50.

15 Furthermore, by placing the load capacitance across the switches, the value greatly exceeds the value of any stray capacitance, which overwhelms any effect that might be caused by those stray capacitances. This enables the voltage at each switch to be the same which is highly desirable.

20 Various modifications to the embodiment described are possible and will occur to those skilled in the art without departing from the invention. For example, in the embodiment described, a capacitance of  $nCd$  is arranged in parallel across each switch, or switch module. As in a preferred, 25 each switch module comprises a number  $M$  of switches arranged in parallel, the capacitance  $nCd$  may be distributed as  $nCd/M$  across each of the parallel switches. In practical realisations, this makes for a more flexible layout. The number of switches and the number of switch modules may vary as may the value of load capacitance required, depending on 30 the nature of the load and the operating conditions.

- 6 -

**CLAIMS**

1. A high voltage switching arrangement for applying a pulse across a load, comprising a capacitor for providing electrical energy to the load and a switch stack for connecting the capacitor to the load, the switch stack comprising a plurality of switch modules arranged in series, and a plurality of load capacitances in parallel across the switch modules.

5

2. A switching arrangement according to claim 1 wherein each switch module has a capacitance  $nC_d$  in parallel across the switch, where  $C_d$  is the capacitance of the load and  $n$  is the number of switch modules.

10

3. A switching arrangement according to claim 2, wherein the parallel load capacitance  $nC_d$  are chosen such that  $nC_d \gg C_s$ , where  $C_s$  is the stray capacitance of each switch module.

15

4. A switching arrangement according to claim 1, 2 or 3, wherein the switch module comprise FET switches.

20

5. A switching arrangement according to claim 4, wherein the FET switches are arranged on circuit boards, with the load capacitances, and the circuit boards are stacked in close proximity to each other.

25

6. A switching arrangement according to any preceding claim, wherein each switch module comprises a plurality of switches arranged in parallel and a capacitance of  $nC_d/M$  is arranged across each switch where  $M$  is the number of switches.

- 7 -

7. A high voltage switching arrangement substantially as herein described with reference to Figures 4 to 7 of the accompanying drawings.

Figure 1

Figure 2

Figure 3 (Prior Art)

Figure 6

Figure 7