(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-252670

(P2012-252670A)

(43) 公開日 平成24年12月20日(2012.12.20)

(51) Int.Cl.

G06F 9/38 (2006.01)

G06F 9/32 (2006.01)

F 1

G06F 9/38 330J

G06F 9/32 320F

テーマコード(参考)

5B013

5B033

審査請求 未請求 請求項の数 5 O L (全 13 頁)

(21) 出願番号

(22) 出願日特願2011-127130 (P2011-127130)

平成23年6月7日(2011.6.7)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(74) 代理人 100112656

弁理士 宮田 英毅

(72) 発明者 日向 文彦

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 吉川 宜史

東京都港区芝浦一丁目1番1号 株式会社

東芝内

F ターム(参考) 5B013 BB17

5B033 AA02 CA09

(54) 【発明の名称】演算装置およびプログラム

(57) 【要約】

**【課題】**複数の分岐条件を含む分岐構造の処理に要する命令数およびサイクル数を低減可能な演算装置およびプログラムを提供する。

**【解決手段】**実施形態の演算装置は、演算部と第1記憶部と読み出し部と出力部とを備える。演算部は、少なくとも2以上の分岐条件の各々について、当該分岐条件の判定を行い、当該分岐条件が成立した場合に行われる演算を実行する。第1記憶部は、判定の判定結果と、演算が有効であるか否かを示す演算情報とを対応付けて記憶する。読み出し部は、演算部の判定により得られた判定結果に対応する演算情報を第1記憶部から読み出す。出力部は、読み出し処理で読み出された演算情報によって有効であることが示された演算の結果を示す演算結果を出力する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

少なくとも 2 以上の分岐条件の各々について、当該分岐条件の判定を行い、当該分岐条件が成立した場合に行われる演算を実行する演算部と、

前記判定の判定結果と、前記演算が有効であるか否かを示す演算情報とを対応付けて記憶する第 1 記憶部と、

前記演算部の前記判定により得られた前記判定結果に対応する前記演算情報を前記第 1 記憶部から読み出す読み出し処理を実行する読み出し部と、

前記読み出し処理で読み出された前記演算情報によって有効であることが示された前記演算の演算結果を出力する出力部と、を備える、

ことを特徴とする演算装置。

**【請求項 2】**

前記第 1 記憶部は、複数の前記分岐条件をそれぞれが含む複数種類の分岐構造ごとに、前記判定結果と前記演算情報とが対応付けられたテーブルを格納し、

前記読み出し部は、前記分岐構造に対応する前記テーブルを用いて前記読み出し処理を実行する、

ことを特徴とする請求項 1 に記載の演算装置。

**【請求項 3】**

複数の前記演算部の各々に何れかの前記分岐条件が対応付けられ、各前記演算部は、当該演算部に対応する前記分岐条件が成立した場合に行われる前記演算を実行し、

前記第 1 記憶部は、前記演算部ごとに、前記判定結果と、当該演算部で実行される前記演算が有効であるか否かを示す前記演算情報とが対応付けられたテーブルを格納し、

前記読み出し部は、前記演算部ごとに、前記判定結果に対応する前記演算情報を前記テーブルから読み出す、

ことを特徴とする請求項 1 に記載の演算装置。

**【請求項 4】**

前記判定結果を記憶する第 2 記憶部と、

前記第 2 記憶部に記憶された複数の前記判定結果のうち、前記読み出し処理に用いられる前記判定結果を選択する選択部と、をさらに備え、

前記読み出し部は、選択された前記判定結果に対応する前記演算情報を前記第 1 記憶部から読み出す、

ことを特徴とする請求項 1 に記載の演算装置。

**【請求項 5】**

少なくとも 2 以上の分岐条件の各々について、当該分岐条件の判定を行う第 1 ステップと、

前記分岐条件の各々について、当該分岐条件が成立した場合に行われる演算を実行する第 2 ステップと、

前記判定の結果を示す判定結果と、前記演算が有効であるか否かを示す演算情報を対応付けて記憶する第 1 記憶部から、前記第 1 ステップで得られた前記判定結果に対応する前記演算情報を読み出す第 3 ステップと、

前記第 3 ステップで読み出された前記演算情報によって有効であることが示された前記演算の結果を示す演算結果を出力する第 4 ステップと、をコンピュータに実行させるためのプログラム。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明の実施形態は、演算装置およびプログラムに関する。

**【背景技術】****【0 0 0 2】**

プロセッサなどの演算装置が実行する命令の一種に分岐命令がある。分岐命令とは、所

定の分岐条件を満たしているか否かを判定し、その判定結果に応じて次に実行すべき命令を決定する命令である。分岐命令を実行する場合、条件判定を終えるまで次に実行すべき命令は分からない。そのため、命令の実行と次の命令の取得を同時に使うプロセッサでは、分岐命令を実行中に、次の命令を正しく取得することができず（分岐ハザード）、プロセッサの性能が低下する。

### 【0003】

分岐ハザードによる性能低下を抑制する技術として、プレディケーション（Predicated Execution）と呼ばれる技術が知られている。この技術では、分岐命令を実行中に、次の命令の候補を取得しておき、分岐命令の実行結果（判定結果）を示す分岐フラグをフラグ記憶装置に格納する。そして、次の命令の候補を投機的に実行し、その実行結果を、分岐フラグの真偽に応じて選択する。これにより、分岐ハザードによる性能低下が抑制される。

10

### 【先行技術文献】

### 【非特許文献】

### 【0004】

【非特許文献1】J. R. Allen, K. Kennedy, C. Porterfield, and J. Warren: "Conversion of control dependence to data dependence" In Proceedings of the 10th ACM Symposium on Principles of Programming Languages, pp 177-189, January 1983

20

### 【発明の概要】

### 【発明が解決しようとする課題】

### 【0005】

しかしながら、従来の技術では、複数の分岐条件を含む分岐構造を処理する場合は、次の命令の候補の実行結果の何れを選択するかを確定するために、複数の分岐条件のそれぞれの判定結果を用いた論理演算が必要となる。これにより、実行する命令の数およびサイクル数が増大するので、プロセッサの性能を十分に向上させることができないという問題がある。本発明が解決しようとする課題は、複数の分岐条件を含む分岐構造の処理に要する命令数およびサイクル数を低減可能な演算装置およびプログラムを提供することである。

30

### 【課題を解決するための手段】

### 【0006】

実施形態の演算装置は、演算部と第1記憶部と読み出し部と出力部とを備える。演算部は、少なくとも2以上の分岐条件の各々について、当該分岐条件の判定を行い、当該分岐条件が成立した場合に行われる演算を実行する。第1記憶部は、判定の判定結果と、演算が有効であるか否かを示す演算情報を対応付けて記憶する。読み出し部は、演算部の判定により得られた判定結果に対応する演算情報を第1記憶部から読み出す。出力部は、読み出し処理で読み出された演算情報によって有効であることが示された演算の結果を示す演算結果を出力する。また、実施形態のプログラムは、少なくとも2以上の分岐条件の各々について、当該分岐条件の判定を行う第1ステップと、分岐条件の各々について、当該分岐条件が成立した場合に行われる演算を実行する第2ステップと、判定の結果を示す判定結果と、演算が有効であるか否かを示す演算情報を対応付けて記憶する第1記憶部から、第1ステップで得られた判定結果に対応する演算情報を読み出す第3ステップと、第3ステップで読み出された演算情報によって有効であることが示された演算の結果を示す演算結果を出力する第4ステップと、をコンピュータに実行させるためのプログラムである。

40

### 【図面の簡単な説明】

### 【0007】

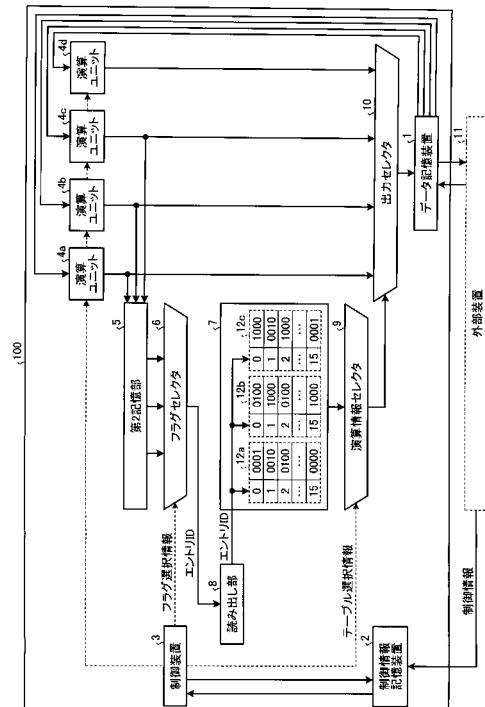

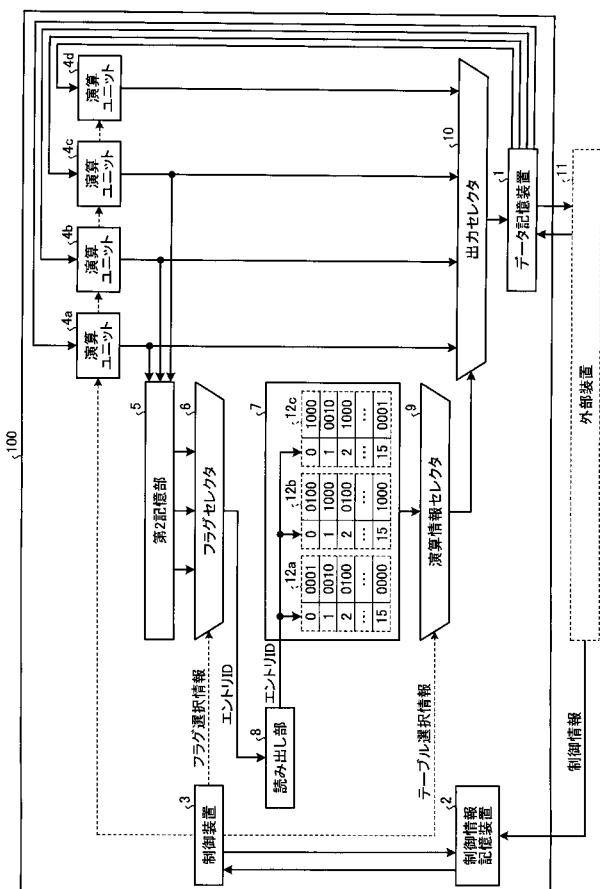

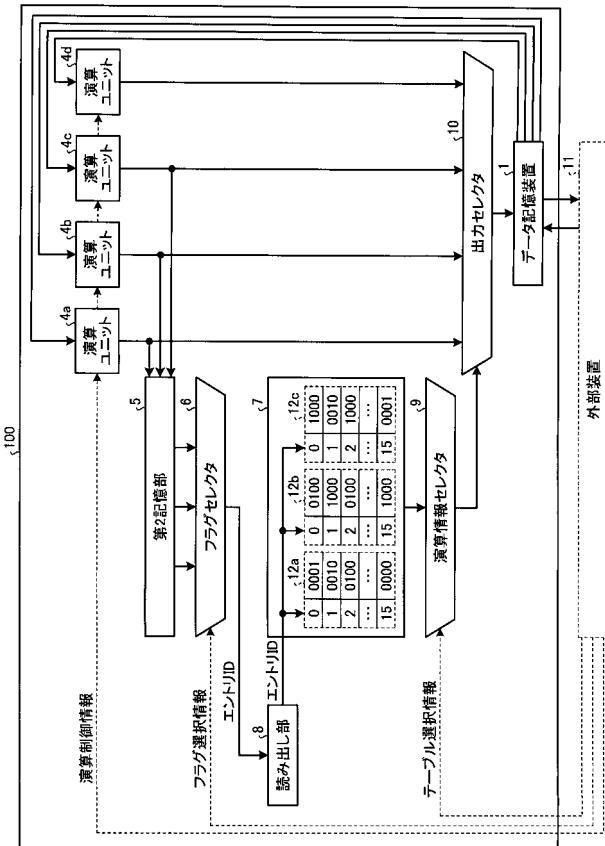

【図1】実施形態に係る演算装置のブロック図。

【図2】分岐構造の一例を示す図。

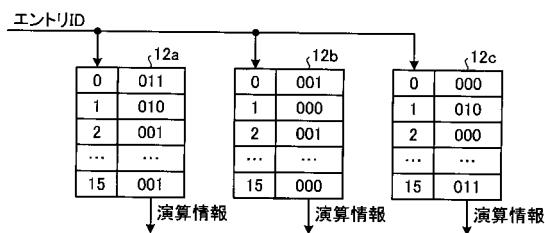

【図3】テーブルの構成例を示す図。

【図4】分岐処理で実行される命令の一例を示す図。

50

【図5】対比例における分岐処理で実行される命令の一例を示す図。

【図6】変形例に係る演算装置のプロック図。

【図7】変形例に係るテーブルの構成例を示す図。

【図8】変形例に係るテーブルの構成例を示す図。

【発明を実施するための形態】

【0008】

以下、添付図面を参照しながら、本発明に係る演算装置およびプログラムの実施の形態を詳細に説明する。図1は、本実施形態に係る演算装置100の概略構成例を示すプロック図である。この演算装置100は、複数の分岐条件を含む分岐構造を処理する分岐処理を実行する半導体装置である。図1に示すように、演算装置100は、データ記憶装置1と、制御情報記憶装置2と、制御装置3と、複数の演算ユニット4a～4dと、第2記憶部5と、フラグセレクタ6と、第1記憶部7と、読み出し部8と、演算情報セレクタ9と、出力セレクタ10とを備える。なお、各演算ユニット4a～4dを区別する必要が無い場合は、単に演算ユニット4と表記する。

10

【0009】

データ記憶装置1には、各演算ユニット4で実行される処理に必要なデータ（「入力データ」と呼ぶ）が格納される。入力データは、外部装置11から供給される。制御情報記憶装置2には、分岐処理の実行に必要な各種の制御情報が格納される。各種の制御情報は、外部装置11から供給される。

20

【0010】

制御装置3は、演算ユニット4、フラグセレクタ6および演算情報セレクタ9の各々の動作を制御する。本実施形態では、制御装置3は、制御情報記憶装置2に格納された各種の制御情報を読み出し、その読み出した制御情報を、演算ユニット4、フラグセレクタ6および演算情報セレクタ9へ転送することで、これらの動作を制御する。図1に示すように、各演算ユニット4には演算制御情報が供給され、フラグセレクタ6にはフラグ選択情報が供給され、演算情報セレクタ9にはテーブル選択情報が供給される。

30

【0011】

演算ユニット4a～4dの各々には、分岐処理の対象となる分岐構造に含まれる複数の分岐条件のうちの何れかが対応付けられ、各演算ユニット4は、制御装置3の制御の下、当該演算ユニット4に対応する分岐条件に関する条件判定を実行する。また、各演算ユニット4は、制御装置3の制御の下、当該演算ユニット4に対応する分岐条件が成立した場合に行われる演算を実行する。

30

【0012】

いま、図2に例示される分岐構造が分岐処理の対象である場合を想定する。図2に示す分岐構造には、4つの分岐条件が含まれる。図2の例では、第1番目の分岐条件I1(if(x))は、xが0ではないことである。そして、第1番目の分岐条件I1が成立した場合は、入力値bに1を加える演算が実行されることが示されている。第2番目の分岐条件I2(else if(y))は、第1番目の分岐条件が不成立であって、かつ、yが0ではないことである。そして、第2番目の分岐条件I2が成立した場合は、入力値bに2を加える演算が実行されることが示されている。第3番目の分岐条件I3(else if(z))は、第1番目の分岐条件I1および第2番目の分岐条件I2が不成立であって、かつ、zが0ではないことである。そして、第3番目の分岐条件I3が成立した場合は、入力値bに3を加える演算が実行されることが示されている。第4番目の分岐条件I4(else)は、第1番目～第3番目の各々の分岐条件I1～I3が不成立であることである。そして、第4番目の分岐条件I4が成立した場合は、入力値bに4を加える演算が実行されることが示されている。

40

【0013】

ここでは、演算ユニット4aには、第1番目の分岐条件I1が対応付けられ、演算ユニット4bには、第2番目の分岐条件I2が対応付けられ、演算ユニット4cには、第3番目の分岐条件I3が対応付けられ、演算ユニット4dには、第4番目の分岐条件I4が対

50

応付けられる。また、各演算ユニット4は、当該演算ユニット4に対応する分岐条件が成立した場合に行われる演算を実行する。また、図2に示す分岐構造を処理する分岐処理が実行される期間は、サイクルAと、次のサイクルBとに分けられる。サイクルAにおいて、各演算ユニット4は条件判定を実行する一方、サイクルBにおいて、各演算ユニット4は演算を実行する。より具体的には、以下のとおりである。

#### 【0014】

演算ユニット4aには、入力データとして、xおよびbのそれぞれの値がデータ記憶装置1から供給される。条件判定を行うサイクルAにおいて、演算ユニット4aは、入力されたxの値が0であるか否かを判定し、その判定結果を示す判定フラグを第2記憶部5へ書き込む。xの値が0でない場合は、判定フラグは「1」に設定される一方、xの値が0である場合は、判定フラグは「0」に設定される。そして、次のサイクルBにおいて、b+1の演算を行い、データ記憶装置1への書き込みアドレスを指定して、その演算結果を出力セレクタ10へ供給する。10

#### 【0015】

演算ユニット4bには、入力データとして、yおよびbのそれぞれの値が供給される。前述のサイクルAにおいて、演算ユニット4bは、入力されたyの値が0であるか否かを判定し、その判定結果を第2記憶部5へ書き込む。yの値が0でない場合は、判定フラグは「1」に設定される一方、yの値が0である場合は、判定フラグは「0」に設定される。そして、次のサイクルBにおいて、演算ユニット4bは、b+2の演算を行い、データ記憶装置1への書き込みアドレスを指定して、その演算結果を出力セレクタ10へ供給する。20

#### 【0016】

演算ユニット4cには、入力データとして、zおよびbのそれぞれの値が供給される。前述のサイクルAにおいて、演算ユニット4cは、入力されたzの値が0であるか否かを判定し、その判定結果を第2記憶部5へ書き込む。zの値が0でない場合は、判定フラグは「1」に設定される一方、zの値が0である場合は、判定フラグは「0」に設定される。そして、次のサイクルBにおいて、b+3の演算を行い、データ記憶装置1への書き込みアドレスを指定して、その演算結果を出力セレクタ10へ供給する。

#### 【0017】

演算ユニット4dには、入力データとして、bの値が供給される。演算ユニット4dは、前述のサイクルAにおいては何もせずに、次のサイクルBにおいてb+4の演算を行い、データ記憶装置1への書き込みアドレスを指定して、その演算結果を出力セレクタ10へ供給する。30

#### 【0018】

図1に示すフラグセレクタ6は、制御装置3から供給されるフラグ選択情報に従って、第2記憶部5に格納された判定フラグを読み出す。フラグ選択情報は、フラグセレクタ6が読み出すべき判定フラグを指定する情報である。ここでは、一例として、フラグ選択情報は、前述のサイクルAにおいて演算ユニット4a～4cによって第2記憶部5に書き込まれた3つの判定フラグを指定する情報である。

#### 【0019】

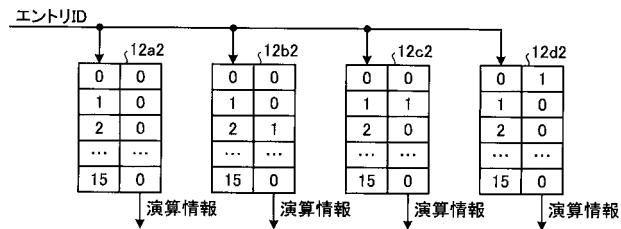

第1記憶部7は、各演算ユニット4による判定の結果を示す判定結果と、各演算ユニット4による演算が有効であるか否かを示す演算情報を対応付けて記憶する。本実施形態では、第1記憶部7は、それぞれが複数の分岐条件を含む複数種類の分岐構造ごとに、判定結果と演算情報を対応関係を示すテーブル12を記憶する。本実施形態では、第1記憶部7は、3種類のテーブル12a～12cを記憶する。なお、各テーブル12a～12cを区別する必要が無い場合は、単にテーブル12と表記する。図3は、ある分岐構造に対応するテーブル12aの一例を示す図である。ここでは、テーブル12aを例に挙げてその構成を説明するが、他のテーブル12bおよび12cも同様の構成である。なお、本実施形態では、テーブル12の内容は、外部装置12によって変更可能である。外部装置12は、テーブル12の内容を、処理すべき分岐構造に応じた内容に予め書き換えておく

ことができる。

#### 【0020】

図3に示すように、テーブル12aでは、フラグセレクタ6で選択される3つの判定フラグの値で識別されるエントリIDと、各演算ユニット4a～4dによる演算の各々について、当該演算が有効であるか否かを示す演算情報とが対応付けられている。例えば演算ユニット4aの判定により得られた判定フラグが「0」、演算ユニット4bの判定により得られた判定フラグが「1」、演算ユニット4cの判定により得られた判定フラグが「1」である場合は、エントリIDは、この順に並べた「011」の左端にさらに「0」を付加した2進数表記「0011」で表され、その値は「3」となる。図3の例では、エントリIDは、「0」～「15」のうちの何れかの値をとり得る。なお、これに限らず、エントリIDの決め方は任意である。要するに、エントリIDは、各演算ユニット4の判定結果に応じて識別されるものであればよい。

10

#### 【0021】

また、図3に示すように、演算情報は4ビットで表される。左から数えて第1番目のビットは演算ユニット4aに対応し、当該第1番目のビットが「1」の場合は、演算ユニット4aによる演算が有効であることを示し、当該第1番目のビットが「0」の場合は、演算ユニット4aによる演算が無効であることを示す。また、演算情報における第2番目のビットは演算ユニット4bに対応し、当該第2番目のビットが「1」の場合は、演算ユニット4bによる演算が有効であることを示し、当該第2番目のビットが「0」の場合は、演算ユニット4bによる演算が無効であることを示す。また、演算情報における第3番目のビットは演算ユニット4cに対応し、当該第3番目のビットが「1」の場合は、演算ユニット4cによる演算が有効であることを示し、当該第3番目のビットが「0」の場合は、演算ユニット4cによる演算が無効であることを示す。さらに、演算情報における第4番目のビットは演算ユニット4dに対応し、当該第4番目のビットが「1」の場合は、演算ユニット4dによる演算が有効であることを示し、当該第4番目のビットが「0」の場合は、演算ユニット4dによる演算が無効であることを示す。なお、これに限らず、演算情報の決め方は任意である。要するに、演算情報は、各演算ユニット4による演算が有効であるか否かを示すものであればよい。

20

#### 【0022】

フラグセレクタ6は、フラグ選択情報に従って読み出した3つの判定フラグの値で識別されるエントリIDを、読み出し部8へ供給する。読み出し部8は、テーブル12ごとに、フラグセレクタ6から供給されたエントリIDに対応する演算情報を読み出す読み出し処理を実行する。読み出し部8は、読み出し処理によって読み出した3つの演算情報を演算情報セレクタ9へ供給する。

30

#### 【0023】

演算情報セレクタ9に供給されるテーブル選択情報は、第1記憶部7に格納された3つのテーブル12a～12cのうちの何れかを指定する情報である。演算情報セレクタ9は、テーブル選択情報で指定されるテーブル12から読み出された演算情報を選択し、その選択した演算情報を出力セレクタ10へ供給する。

40

#### 【0024】

出力セレクタ10は、演算情報セレクタ9から供給される演算情報によって有効であることが示された演算の結果を示す演算結果を選択（取得）し、その選択した演算結果を、データ記憶装置1のうち書き込みアドレスで特定される領域に書き込む。例えば、演算情報セレクタ9から供給された演算情報が「0100」である場合、出力セレクタ10は、演算ユニット4bによる演算結果を選択し、その選択した演算結果を、データ記憶装置1のうち書き込みアドレスで特定される領域に書き込む。データ記憶装置1は、出力セレクタ10により書き込まれた演算結果を外部装置11へ供給する。

#### 【0025】

次に、演算装置100が実行する分岐処理の一例を具体的に説明する。ここでは、図2に示す分岐構造を処理する場合について説明する。この場合に実行される命令は、図4に

50

示す 7 つの命令 C 1 ~ C 7 である。命令 C 1 は、入力された  $x$  の値が 0 であるか否かの判定の実行を指示する命令であり、命令 C 2 は、入力された  $y$  の値が 0 であるか否かの判定の実行を指示する命令であり、命令 C 3 は、入力された  $z$  の値が 0 であるか否かの判定の実行を指示する命令である。

#### 【 0 0 2 6 】

命令 C 4 は、データ記憶装置 1 のレジスタ  $r_2$  に格納されたデータに 1 を加える演算の実行を指示する命令である。本実施形態では、レジスタ  $r_2$  には  $b$  の値が格納される。したがって、命令 C 4 は、入力された  $b$  の値に 1 を加える演算の実行を指示する命令であると捉えることができる。また、命令 C 5 は、データ記憶装置 1 のレジスタ  $r_2$  に格納されたデータに 2 を加える演算の実行を指示する命令である。命令 C 5 は、入力された  $b$  の値に 2 を加える演算の実行を指示する命令であると捉えることができる。また、命令 C 6 は、データ記憶装置 1 のレジスタ  $r_2$  に格納されたデータに 3 を加える演算の実行を指示する命令である。命令 C 6 は、入力された  $b$  の値に 3 を加える演算の実行を指示する命令であると捉えることができる。さらに、命令 C 7 は、データ記憶装置 1 のレジスタ  $r_2$  に格納されたデータに 4 を加える演算の実行を指示する命令である。命令 C 7 は、入力された  $b$  の値に 4 を加える演算の実行を指示する命令であると捉えることができる。なお、図 4 に示す「 ; ; 」は、当該「 ; ; 」と、直前の「 ; ; 」との間に複数の命令が存在する場合は、それらの命令間には依存関係が無いことを示し、命令の数だけ演算ユニット 4 があれば、それらの命令を 1 サイクルで実行できることを示す。

10

#### 【 0 0 2 7 】

一例として、 $x = 0$ 、 $y = 1$ 、 $z = 3$ 、 $b = 2$  である場合を想定する。まず、条件判定を行うサイクル A において、制御装置 3 は、命令 C 1 の実行を指示する演算制御情報を演算ユニット 4 a に供給し、命令 C 2 の実行を指示する演算制御情報を演算ユニット 4 b に供給し、命令 C 3 の実行を指示する演算制御情報を演算ユニット 4 c に供給する。これにより、演算ユニット 4 a は命令 C 1 を実行する。この例では、 $x = 0$  であるので、演算ユニット 4 a による判定の結果は偽となり、演算ユニット 4 a は、「 0 」に設定した判定フラグを、第 2 記憶部 5 に書き込む。説明の便宜上、第 2 記憶部 5 のうち、演算ユニット 4 a による判定結果を示す判定フラグが格納される領域をフラグ番号 0 と呼ぶ。

20

#### 【 0 0 2 8 】

また、演算ユニット 4 b は命令 C 2 を実行する。この例では、 $y = 1$  であるので、演算ユニット 4 b による判定の結果は真となり、演算ユニット 4 b は、「 1 」に設定した判定フラグを、第 2 記憶部 5 に書き込む。説明の便宜上、第 2 記憶部 5 のうち、演算ユニット 4 b による判定結果を示す判定フラグが格納される領域をフラグ番号 1 と呼ぶ。

30

#### 【 0 0 2 9 】

さらに、演算ユニット 4 c は命令 C 3 を実行する。この例では、 $z = 3$  であるので、演算ユニット 4 c による判定の結果は真となり、演算ユニット 4 c は、「 1 」に設定した判定フラグを、第 2 記憶部 5 に書き込む。説明の便宜上、第 2 記憶部 5 のうち、演算ユニット 4 c による判定結果を示す判定フラグが格納される領域をフラグ番号 2 と呼ぶ。なお、演算ユニット 4 d は、サイクル A においては何も行わない。

40

#### 【 0 0 3 0 】

次に、サイクル B において、制御装置 3 は、命令 C 4 の実行を指示する演算制御情報を演算ユニット 4 a に供給し、命令 C 5 の実行を指示する演算制御情報を演算ユニット 4 b に供給し、命令 C 6 の実行を指示する演算制御情報を演算ユニット 4 c に供給し、命令 C 7 の実行を指示する演算制御情報を演算ユニット 4 d に供給する。これにより、演算ユニット 4 a は命令 C 4 を実行する。ここでは、 $b$  の値は「 2 」であるので、演算ユニット 4 a による演算の結果は「 3 」となる。この例では、演算ユニット 4 a は、データ記憶装置 1 への書き込みアドレスとして addressA を指定し、演算結果「 3 」を出力セレクタ 1 0 へ出力する。

#### 【 0 0 3 1 】

演算ユニット 4 b は命令 C 5 を実行する。ここでは、 $b$  の値は「 2 」であるので、演算

50

ユニット4 bによる演算の結果は「4」となる。この例では、演算ユニット4 bは、データ記憶装置1への書き込みアドレスとしてaddressAを指定し、演算結果「4」を出力セレクタ10へ出力する。また、演算ユニット4 cは命令C6を実行する。ここでは、bの値は「2」であるので、演算ユニット4 cによる演算の結果は「5」となる。この例では、演算ユニット4 cは、データ記憶装置1への書き込みアドレスとしてaddressAを指定し、演算結果「5」を出力セレクタ10へ出力する。さらに、演算ユニット4 dは命令C7を実行する。ここでは、bの値は「2」であるので、演算ユニット4 dによる演算の結果は「6」となる。この例では、演算ユニット4 dは、データ記憶装置1への書き込みアドレスとしてaddressAを指定し、演算結果「6」を出力セレクタ10へ出力する。

## 【0032】

10

また、サイクルBにおいて、制御装置3は、第2記憶部5のうちフラグ番号0、1および2の各々に格納された判定フラグを選択することを示す選択情報をフラグセレクタ6へ供給する。これにより、フラグセレクタ6は、フラグ番号0、1および2の各々に格納された判定フラグを第2記憶部5から読み出し、その読み出した3つの判定フラグの値で識別されるエントリIDを読み出し部8へ供給する。この例では、フラグ番号0に格納された判定フラグは「0」、フラグ番号1に格納された判定フラグは「1」、フラグ番号2に格納された判定フラグは「1」であるので、エントリIDは、「0011」の2進数表記で表され、その値は「3」となる。そして、読み出し部8は、テーブル12ごとに、エントリID「3」に対応する演算情報を読み出す。

## 【0033】

20

さらに、サイクルBにおいて、制御装置3は、図2の分岐構造に対応するテーブル12を選択することを示すテーブル選択情報を演算情報セレクタ9へ供給する。ここでは、図2の分岐構造に対応するテーブル12は、図3のテーブル12aであるとする。これにより、演算情報セレクタ9は、テーブル12aから読み出された、エントリID「3」に対応する演算情報「0100」(図3参照)を選択して出力セレクタ10へ出力する。したがって、出力セレクタ10は、演算ユニット4bの演算結果「6」を取得し、その取得した演算結果「6」を、データ記憶装置1のうちaddressAで特定される領域に書き込む。そして、データ記憶装置1は、addressAで特定される領域に書き込まれた演算結果「6」を、外部装置11へ出力する。以上で、図2に例示された分岐構造を処理する分岐処理が終了する。

30

## 【0034】

以上に説明したように、本実施形態では、第1記憶部7には、各演算ユニット4による判定結果で識別されるエントリIDと、演算情報とが対応付けられたテーブル12が格納される。そして、複数の分岐条件を含む分岐構造を処理する場合において、演算装置100は、各演算ユニット4による判定結果で識別されるエントリIDに対応する演算情報をテーブル12から読み出し、その読み出した演算情報によって有効であることが示された演算の結果を示す演算結果を出力するので、複数の分岐条件を含む分岐構造を処理する場合における命令数およびサイクル数を低減できるという有利な効果を奏する。

## 【0035】

40

ここで、前述のテーブル12を用いずに、図2の分岐構造を処理する場合を想定する。この場合に実行される命令は、図5に示す11個の命令C11～Cb6である。命令C11は、入力されたxの値が0であるか否かの判定の実行を指示する命令であり、判定の結果、xの値が0でない場合は、フラグP1は「1」、フラグP2は「0」にセットされる一方、xの値が0である場合は、フラグP1は「0」、フラグP2は「1」にセットされることを示す。命令C22は、入力されたyの値が0であるか否かの判定の実行を指示する命令であり、判定の結果、yの値が0でない場合は、フラグP3は「1」、フラグP4は「0」にセットされる一方、yの値が0である場合は、フラグP3は「0」、フラグP4は「1」にセットされることを示す。命令C33は、入力されたzの値が0であるか否かの判定の実行を指示する命令であり、判定の結果、zの値が0でない場合は、フラグP5は「1」、フラグP6は「0」にセットされる一方、zの値が0である場合は、フラグ

50

P 5 は「0」、フラグ P 6 は「1」にセットされることを示す。

#### 【0036】

命令 C 4 4 は、図 2 の第 2 番目の分岐条件 I 2 ( 第 1 番目の分岐条件 I 1 が不成立であって、かつ、y が 0 でない ) が成立するか否かの判定の実行を指示する命令である。より具体的には、フラグ P 2 およびフラグ P 3 の論理積の実行を指示する命令である。第 1 番目の分岐条件 I 1 が不成立で、かつ、第 2 番目の分岐条件 I 2 が成立する場合は、フラグ P 1 = 0、フラグ P 2 = 1、フラグ P 3 = 1、フラグ P 4 = 0 となる。この場合、フラグ P 2 およびフラグ P 3 の論理積は「1」となり、フラグ P 7 = 1、フラグ P 8 = 0 となる。すなわち、フラグ P 7 = 1、フラグ P 8 = 0 の場合は、第 2 番目の分岐条件 I 2 は成立すると判定される。一方、フラグ P 7 = 0、フラグ P 8 = 1 の場合は、第 2 番目の分岐条件 I 2 は成立しないと判定される。なお、命令 C 4 4 は、命令 C 1 1 および命令 C 2 2 の実行結果を用いるので、これらの命令と並列に実行することはできない。

10

#### 【0037】

命令 C 5 5 は、第 1 番目の分岐条件 I 1 および第 2 番目の分岐条件 I 2 の両方が不成立であるか否かの判定の実行を指示する命令である。より具体的には、フラグ P 2 およびフラグ P 4 の論理積の実行を指示する命令である。第 1 番目の分岐条件 I 1 が不成立であって、かつ、第 2 番目の分岐条件 I 2 も不成立であった場合は、フラグ P 1 = 0、フラグ P 2 = 1、フラグ P 3 = 0、フラグ P 4 = 1 となる。この場合、フラグ P 2 およびフラグ P 4 の論理積は「1」となり、フラグ P 9 = 1、フラグ P 10 = 0 となる。すなわち、フラグ P 9 = 1、フラグ P 10 = 0 の場合は、第 1 番目の分岐条件 I 1 および第 2 番目の分岐条件 I 2 の両方が不成立であると判定される。一方、フラグ P 9 = 0、フラグ P 10 = 1 の場合は、第 1 番目の分岐条件 I 1 および第 2 番目の分岐条件 I 2 のうちの何れかが成立していると判定される。なお、命令 C 5 5 は、命令 C 1 1 および命令 C 2 2 の実行結果を用いるので、これらの命令と並列に実行することはできない。

20

#### 【0038】

命令 C 6 6 は、図 5 の第 3 番目の分岐条件 I 3 ( 第 1 番目の分岐条件 I 1 および第 2 番目の分岐条件 I 2 の両方が不成立であって、かつ、z が 0 でない ) が成立するか否かの判定の実行を指示する命令である。より具体的には、フラグ P 9 およびフラグ P 5 の論理積の実行を指示する命令である。第 1 番目の分岐条件 I 1 および第 2 番目の分岐条件 I 2 の両方が不成立で、かつ、第 3 番目の分岐条件 I 3 が成立する場合は、フラグ P 9 = 1、フラグ P 5 = 1 となる。この場合、フラグ P 9 およびフラグ P 5 の論理積は「1」となり、フラグ P 11 = 1、フラグ P 12 = 0 となる。すなわち、フラグ P 11 = 1、フラグ P 12 = 0 の場合は、第 3 番目の分岐条件 I 3 が成立すると判定される。一方、フラグ P 11 = 0、フラグ P 12 = 1 の場合は、第 3 番目の分岐条件 I 3 は成立しないと判定される。なお、命令 C 6 6 は、命令 C 3 3 および命令 C 5 5 の実行結果を用いるので、これらの命令と並列に実行することはできない。

30

#### 【0039】

命令 C 7 7 は、図 5 の第 4 番目の分岐命令 I 4 ( 第 1 番目の分岐条件 I 1 、第 2 番目の分岐条件 I 2 、および、第 3 番目の分岐条件 I 3 が何れも不成立 ) が成立するか否かの判定の実行を指示する命令である。より具体的には、フラグ P 9 およびフラグ P 6 の論理積の実行を指示する命令である。第 1 番目の分岐条件 I 1 、第 2 番目の分岐条件 I 2 、および、第 3 番目の分岐条件 I 3 の何れも不成立の場合は、フラグ P 9 = 1、フラグ P 6 = 1 となる。この場合、フラグ P 9 およびフラグ P 6 の論理積は「1」となり、フラグ P 13 = 1、フラグ P 14 = 0 となる。すなわち、フラグ P 13 = 1、フラグ P 14 = 0 の場合は、第 4 番目の分岐条件 I 4 が成立すると判定される。一方、フラグ P 13 = 0、フラグ P 14 = 1 の場合は、第 4 番目の分岐条件 I 4 は成立しないと判定される。なお、命令 C 7 7 は、命令 C 3 3 および命令 C 5 5 の実行結果を用いるので、これらの命令と並列に実行することはできない。

40

#### 【0040】

命令 C 8 8 は、データ記憶装置 1 のレジスタ r 2 に格納されたデータに 1 を加える演算

50

の実行を指示する命令である。命令 C 9 9 は、データ記憶装置 1 のレジスタ r 2 に格納されたデータに 2 を加える演算の実行を指示する命令である。命令 C a a は、データ記憶装置 1 のレジスタ r 2 に格納されたデータに 3 を加える演算の実行を指示する命令である。命令 C b b は、データ記憶装置 1 のレジスタ r 2 に格納されたデータに 4 を加える演算の実行を指示する命令である。

#### 【 0 0 4 1 】

この場合の分岐処理では、第 1 番目のサイクルにおいて命令 C 1 1 ~ C 3 3 が実行され、第 2 番目のサイクルにおいて命令 C 4 4 および命令 C 5 5 が実行され、第 3 番目のサイクルにおいて命令 C 6 6 および命令 C 7 7 が実行され、第 4 番目のサイクルにおいて命令 C 8 8 ~ 命令 C b b が実行される。つまり、分岐処理に必要な命令数は 1 1 、サイクル数は 4 となる。10

#### 【 0 0 4 2 】

これに対して、本実施形態によれば、図 2 の分岐構造を処理する分岐処理に必要な命令数は 7 、サイクル数は 2 つで済むので、テーブル 1 2 を用いずに分岐処理を実行する場合に比べて、命令数およびサイクル数を低減できるという利点がある。

#### 【 0 0 4 3 】

なお、上述の実施形態において、演算装置 1 0 0 で実行される各種プログラム（分岐処理用の制御プログラム等）を、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成してもよい。また当該各種プログラムを、インストール可能な形式又は実行可能な形式のファイルで C D - R O M 、フレキシブルディスク（ F D ）、 C D - R 、 D V D ( Digital Versatile Disk ) 等のコンピュータで読み取り可能な記録媒体に記録してコンピュータプログラムプロダクトとして提供するように構成してもよい。20

#### 【 0 0 4 4 】

##### （変形例）

以上、本発明の実施形態を説明したが、この実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。以下に変形例を記載する。なお、以下に記載する変形例のうちの 2 以上を任意に組み合わせることもできる。30

#### 【 0 0 4 5 】

##### （変形例 1 ）

上述の実施形態では、演算装置 1 0 0 内に、外部装置 1 1 から供給される各種の制御情報を、各演算ユニット 4 、フラグセレクタ 6 および演算情報セレクタ 9 へ転送するための制御情報記憶装置 2 および制御装置 3 が設けられているが、これに限らず、制御情報記憶装置 2 および制御装置 3 が演算装置 1 0 0 内に設けられない構成であってもよい。例えば図 6 に示すように、外部装置 1 1 が、各演算ユニット 4 、フラグセレクタ 6 および演算情報セレクタ 9 の各々に対して、制御情報を直接供給する構成であってもよい。要するに、制御情報に関する転送方法、生成方法、記憶方法などは任意である。40

#### 【 0 0 4 6 】

##### （変形例 2 ）

上述の実施形態では、第 1 記憶部 7 に格納されるテーブル 1 2 のデータは、書き換え可能であるが、これに限らず、第 1 記憶部 7 に格納されるテーブル 1 2 のデータは、書き換え不可能であってもよい。また、第 1 記憶部 7 に記憶されるテーブル 1 2 の数は任意である。例えば第 1 記憶部 7 は、ひとつのテーブル 1 2 のみを格納し、当該ひとつのテーブル 1 2 のデータは、処理対象の分岐構造に応じて書き換えられる構成であってもよい。この書き換えを行う主体は任意であり、外部装置 1 2 が行ってもよいし、制御装置 3 が行ってもよい。また、第 1 記憶部 7 に格納されるテーブル 1 2 が 1 つのみの場合、演算情報セレ50

クタ9は不要となるので、構成が簡素化される。

#### 【0047】

##### (変形例3)

また、テーブル12は、各演算ユニット4による判定結果と演算情報との対応関係を示すものであればよく、その構成は任意である。例えばテーブル12は、図7に示す構成であってもよい。図7の構成では、演算情報は3ビットの2進数表記で表される。一例として、演算情報の値が「0」の場合(2進数表記で「000」の場合)は、演算ユニット4aによる演算が有効であることを示し、演算情報の値が「1」の場合(2進数表記で「001」の場合)は、演算ユニット4bによる演算が有効であることを示し、演算情報の値が「2」の場合(2進数表記で「010」の場合)は、演算ユニット4cによる演算が有効であることを示し、演算情報の値が「3」の場合(2進数表記で「011」の場合)は、演算ユニット4dによる演算が有効であることを示す。

10

#### 【0048】

また、演算情報の値が「5」の場合(2進数表記で「101」の場合)は、演算ユニット4aおよび演算ユニット4bのそれぞれによる演算が有効であることを示し、演算情報の値が「6」の場合(2進数表記で「110」の場合)は、演算ユニット4a、演算ユニット4bおよび演算ユニット4cのそれぞれによる演算が有効であることを示し、演算情報の値が「7」の場合(2進数表記で「111」の場合)は、演算ユニット4a、演算ユニット4b、演算ユニット4cおよび演算ユニット4dのそれぞれによる演算が有効であることを示す構成であってもよい。

20

#### 【0049】

出力セレクタ10は、1つの演算結果のみを選択することもできるし、書き込み先が異なる場合は、複数の演算結果を選択することもできるので、演算情報によって有効であることが示される演算の数は任意であり、1つに限られるものではない。

#### 【0050】

##### (変形例4)

また、上述の実施形態では、複数種類の分岐構造ごとに、当該分岐構造に対応するテーブル12が設けられているが、これに限らず、例えば演算ユニット4ごとに、当該演算ユニット4に対応するテーブル12が設けられる構成であってもよい。図8は、この構成の一例を示す図であり、図8の例では、演算ユニット4aに対応するテーブル12a2と、演算ユニット4bに対応するテーブル12b2と、演算ユニット4cに対応するテーブル12c2と、演算ユニット4dに対応するテーブル12d2とが設けられ、第1記憶部7(不図示)に格納される。各テーブル12では、エントリIDと、当該テーブル12に対応する演算ユニット4が実行する演算が有効であるか否かを示す1ビットの演算情報とが対応付けられている。

30

#### 【0051】

##### (変形例5)

第2記憶部5に記憶される判定フラグの数は、少なくとも2以上であればよく、その数は任意である。また、演算ユニット4の数に応じた効果を得るために、演算ユニット4の数以上の判定フラグを第2記憶部5に格納しておくことが好ましい。また、第2記憶部5に記憶される判定フラグの数が、エントリIDの特定に必要なビット数と同一の場合は、フラグセレクタ6は不要となる。一方、第2記憶部5に記憶される判定フラグの数が、エントリIDの特定に必要なビット数と異なる場合は、重複も含めて必要な判定フラグを選択するためにフラグセレクタ6が必要となる。

40

#### 【0052】

##### (変形例6)

上述の実施形態では、演算ユニット4の数は4つであるが、これに限らず、演算ユニット4の数は任意であり、例えば演算ユニット4の数は1つのみであってもよい。要するに、少なくとも2以上の分岐条件の各自について、当該分岐条件の判定を行い、当該分岐条件が成立した場合に行われる演算を実行するための演算ユニット4が1以上設けられてい

50

ればよい。

### 【0053】

#### (変形例7)

上述の実施形態では、演算ユニット4による判定結果が真の場合は判定フラグが「1」に設定される一方、判定結果が偽の場合は判定フラグが「0」に設定されるが、これに限らず、例えば演算ユニット4による判定結果が真の場合は判定フラグが「0」に設定される一方、判定結果が偽の場合は判定フラグが「1」に設定されてもよい。

#### 【符号の説明】

### 【0054】

1 データ記憶装置

2 制御情報記憶装置

3 制御装置

4 演算ユニット

5 第2記憶部

6 フラグセレクタ

7 第1記憶部

8 読み出し部

9 演算情報セレクタ

10 出力セレクタ

11 外部装置

12 テーブル

100 演算装置

10

20

【図1】

【図2】

【図3】

| エントリID | 演算情報 |

|--------|------|

| 0      | 0001 |

| 1      | 0010 |

| 2      | 0100 |

| 3      | 0100 |

| 4      | 1000 |

| 5      | 1000 |

| 6      | 1000 |

| 7      | 1000 |

| 8      | 0000 |

| 9      | 0000 |

| 10     | 0000 |

| 11     | 0000 |

| 12     | 0000 |

| 13     | 0000 |

| 14     | 0000 |

| 15     | 0000 |

【図4】

|    |                        |

|----|------------------------|

| C1 | cmp.neq P1=x,0         |

| C2 | cmp.neq P2=y,0         |

| C3 | cmp.neq P3=z,0;;       |

| C4 | (ptable 0) add r1=r2,1 |

| C5 | (ptable 0) add r1=r2,2 |

| C6 | (ptable 0) add r1=r2,3 |

| C7 | (ptable 0) add r1=r2,4 |

【図6】

【図5】

|     |                         |

|-----|-------------------------|

| C11 | cmp.neq P1,P2=x,0       |

| C22 | cmp.neq P3,P4=y,0       |

| C33 | cmp.neq P5,P6=z,0;;     |

| C44 | cmp.and P7,P8=P2,P3     |

| C55 | cmp.and P9,P10=P2,P4;;  |

| C66 | cmp.and P11,P12=P9,P5   |

| C77 | cmp.and P13,P14=P9,P6;; |

| C88 | (P1) add r1=r2,1        |

| C99 | (P7) add r1=r2,2        |

| Caa | (P11) add r1=r2,3       |

| Cbb | (P13) add r1=r2,4       |

【図7】

【図8】