(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 03 319 T2 2006.03.16

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 442 161 B1

(21) Deutsches Aktenzeichen: 602 03 319.5

(86) PCT-Aktenzeichen: PCT/US02/35910

(96) Europäisches Aktenzeichen: 02 802 884.3

(87) PCT-Veröffentlichungs-Nr.: WO 03/040436

(86) PCT-Anmeldetag: 08.11.2002

(87) Veröffentlichungstag

der PCT-Anmeldung: 15.05.2003

(97) Erstveröffentlichung durch das EPA: 04.08.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 16.03.2005

(47) Veröffentlichungstag im Patentblatt: 16.03.2006

(51) Int Cl.<sup>8</sup>: C25D 5/50 (2006.01)

H01L 21/20 (2006.01)

H01L 23/522 (2006.01)

(30) Unionspriorität:

986263 08.11.2001 US

(84) Benannte Vertragsstaaten:

DE, GB

(73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif.,

US

(72) Erfinder:

NGO, Van, Minh, Fremont, US; PATON, Eric,

Morgan Hill, US

(74) Vertreter:

Patentanwälte von Kreisler, Selting, Werner et col.,

50667 Köln

(54) Bezeichnung: VERFAHREN ZUR ENTFERNUNG VON HOHLRÄUMEN IN WOLFRAMSTIFTFEN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft ein Verfahren zur Herstellung von Halbleitervorrichtungen mit genau ausgebildeten Submikrometermerkmalen. Die vorliegende Erfindung ist insbesondere bei der Herstellung von hochdichten Mehrebenen-Flash-Speicher-Halbleitervorrichtungen mit zuverlässigen niederohmigen Kontakten/Durchkontakten anwendbar.

**STAND DER TECHNIK**

**[0002]** Da die Geometrien integrierter Schaltungen immer tiefer in den Submikrometerbereich eindringen, wird die präzise Herstellung diskreter Halbleitervorrichtungen mit der erforderlichen Zuverlässigkeit und Schaltungsgeschwindigkeit immer schwieriger. Die Durchführung wird besonders problematisch bei der Herstellung von Flash-Speicher-Vorrichtungen mit einem Entwurfsmaß von weniger als etwa 0,15 Mikrometer und darunter, z.B. weniger als etwa 0,12 Mikrometer und darunter.

**[0003]** Herkömmliche Halbleitervorrichtungen weisen ein Halbleitersubstrat, in dem verschiedene Elemente, wie beispielsweise Transistoren, ausgebildet sind, und eine Vielzahl von darüberliegenden sequentiell gebildeten Zwischenschichtdielektrika und Leiterstrukturen, in denen ein Verbindungssystem mit Leitbahnen ausgebildet ist, auf. Üblicherweise sind Leiterstrukturen auf unterschiedlichen Ebenen, d.h. oberen und unteren Ebenen, mittels eines ein Durchkontaktloch füllenden leitfähigen Steckers elektrisch verbunden, wobei ein ein Kontaktloch füllender leitfähiger Stecker einen elektrischen Kontakt mit einem aktiven Bereich auf einem Halbleitersubstrat, wie beispielsweise einem Source-/Drain-Bereich, herstellt. Ein einen Durchkontakt füllender leitfähiger Stecker wird üblicherweise durch Ablagern eines Zwischenschichtdielektrums (ILD) auf einer leitfähigen Ebene mit mindestens einem leitfähigen Merkmal, Bilden einer Öffnung durch das ILD mittels herkömmlicher Photolithographie- und Ätztechniken und Füllen der Öffnung mit einem leitfähigen Material gebildet. Überflüssiges leitfähiges Material oder die Überlast auf der Oberfläche des ILD wird üblicherweise durch chemisch-mechanisches Polieren (CMP) entfernt. Ein derartiges Verfahren ist als Damaszenerverfahren bekannt und umfaßt grundsätzlich das Bilden einer Öffnung in dem ILD und das Füllen der Öffnung mit einem Metall. Doppeldamaszenertechniken umfassen das Bilden einer Öffnung mit einem unteren Kontaktloch- oder Durchkontaktlochabschnitt, der mit einem oberen Grabenabschnitt in Verbindung steht, wobei die Öffnung mit einem leitfähigen Material, üblicherweise einem Metall, gefüllt wird, um gleichzeitig einen leitfähigen Stecker zu bilden, der in elektrischem Kontakt mit einer oberen Leiterbahn ist.

**[0004]** Da die Geometrien tief in den Submikrometerbereich eindringen, wird die Bildung zuverlässiger niederohmiger Kontakte und Zwischenverbindungen besonders problematisch. Da der Durchmesser von Kontakt-/Durchkontaktöffnungen verringert und das Seitenverhältnis (Tiefe/Durchmesser) erhöht wird, z.B. auf etwa 4:1 und höher, werden die Öffnungen anfälliger für Defekte, z.B. Nähte und Kristallseigerung in Form von Porosität oder Hohlräumen, die durch den zentralen Teil des Kontakts oder Durchkontakte verlaufen. Solche Hohlräume haben eine hohe und instabile Kontaktwiderstandsverteilung zur Folge, erzeugen Defekte und verringern den Elektromigrationswiderstand sowohl in den Flash-Speicher-Vorrichtungen als auch in den Mikroprozessoren.

**[0005]** Demnach besteht Bedarf an einer Methodik, die die Herstellung von Halbleitervorrichtungen mit besserer Zuverlässigkeit, einschließlich MOS-Transistoren sowie Flash-Speicher-Vorrichtungen enthaltende Halbleitervorrichtungen, wie beispielsweise elektrisch löschräumbare programmierbare Nur-Lese-Speicher-(EEPROM-)Vorrichtungen, ermöglicht. Besonderer Bedarf besteht an einer Methodik, die die Herstellung von Halbleitervorrichtungen mit Merkmalen im tiefen Submikrometerbereich, die zuverlässige und niederohmige Kontakte und Durchkontakte mit besserer Elektromigrationsleistung enthalten, ermöglicht.

**OFFENBARUNG DER ERFINDUNG**

**[0006]** Ein Vorteil der vorliegenden Erfindung besteht in einem Verfahren zur Herstellung einer Halbleitervorrichtung mit Merkmalen tief im Submikrometerbereich mit hoch zuverlässigen Durchkontakten und Kontakten, die eine geringe und stabile Kontaktwiderstandsverteilung und eine verbesserte Elektromigrationsleistung zeigen.

**[0007]** Weitere Vorteile und andere Merkmale der vorliegenden Erfindung sind in der folgenden Beschreibung angeführt und ergeben sich zum Teil für den Durchschnittsfachmann auf dem Gebiet bei Überprüfung des Folgenden oder aus der Ausübung der vorliegenden Erfindung. Die Vorteile der vorliegenden Erfindung können so, wie dies insbesondere in den angefügten Ansprüchen hervorgehoben wird, realisiert und erzielt werden.

**[0008]** Gemäß der vorliegenden Erfindung umfaßt das Verfahren das Bilden einer Öffnung in einer dielektrischen Schicht, das Ablagern von Wolfram (W) zum Füllen der Öffnung und das Laser-Erhitzen des W in der Öffnung zum Schmelzen und erneuten Verflüssigen des W in der Öffnung.

**[0009]** Ausführungsbeispiele der vorliegenden Erfindung umfassen das Bilden einer Öffnung in einer

## BESCHREIBUNG DER ERFINDUNG

Oxiddielektrumsschicht, wie beispielsweise bor-phosphor-dotiertes Silikatglas (BPSG), oder einer Verbundoxidschicht mit einer BPSG-Schicht mit einer darauf befindlichen Siliziumoxidschicht, die aus darauf befindlichem Tetraethylorthosilikat (TEOS) stammt, Ablagern einer Ausgangssperrsenschicht aus Titan (Ti) und anschließendes Ablagern wenigstens einer Schicht, z.B. dreier Schichten, aus Titannitrid auf der Titanschicht. Dann wird die Öffnung mit W gefüllt. In einer Ausführungsform der vorliegenden Erfindung wird das Laser-Erhitzen durch Abstrahlen eines auf die gefüllte Öffnung gerichteten Laserlichtstrahls auf das abgelagerte W in Stickstoff (N<sub>2</sub>), und zwar üblicherweise mit einer Strahlungsfluenz von etwa 0,78 bis etwa 1,10 Joule/cm<sup>2</sup>, über einen kurzen Zeitraum, z.B. etwa 10 bis etwa 100 Nanosekunden, zum Erhöhen der Temperatur des W in der Öffnung, wodurch das W in der gefüllten Öffnung geschmolzen und erneut verflüssigt wird, z.B. bei einer Temperatur von etwa 3000°C bis etwa 3600°C. Dann wird das chemisch-mechanische Polieren (CMP) durchgeführt. In einer anderen Ausführungsform der vorliegenden Erfindung wird das CMP vor dem Laser-Erhitzen durchgeführt.

**[0010]** Weitere Vorteile der vorliegenden Erfindung sind für den Fachmann auf dem Gebiet aus der folgenden detaillierten Beschreibung leicht ersichtlich, in welcher Ausführungsformen der vorliegenden Erfindung einfach durch Darstellung dessen, das als beste Art zur Ausführung der Erfindung angesehen wird, beschrieben sind. Wie deutlich wird, kann die vorliegende Erfindung in anderen und verschiedenen Ausführungsformen ausgeführt werden, und ihre mehreren Details können in verschiedener naheliegender Hinsicht modifiziert werden, ohne von der vorliegenden Erfindung abzuweichen. Demnach sind die Zeichnungen und die Beschreibung als veranschaulichend und nicht als einschränkend anzusehen.

## KURZBESCHREIBUNG DER ZEICHNUNGEN

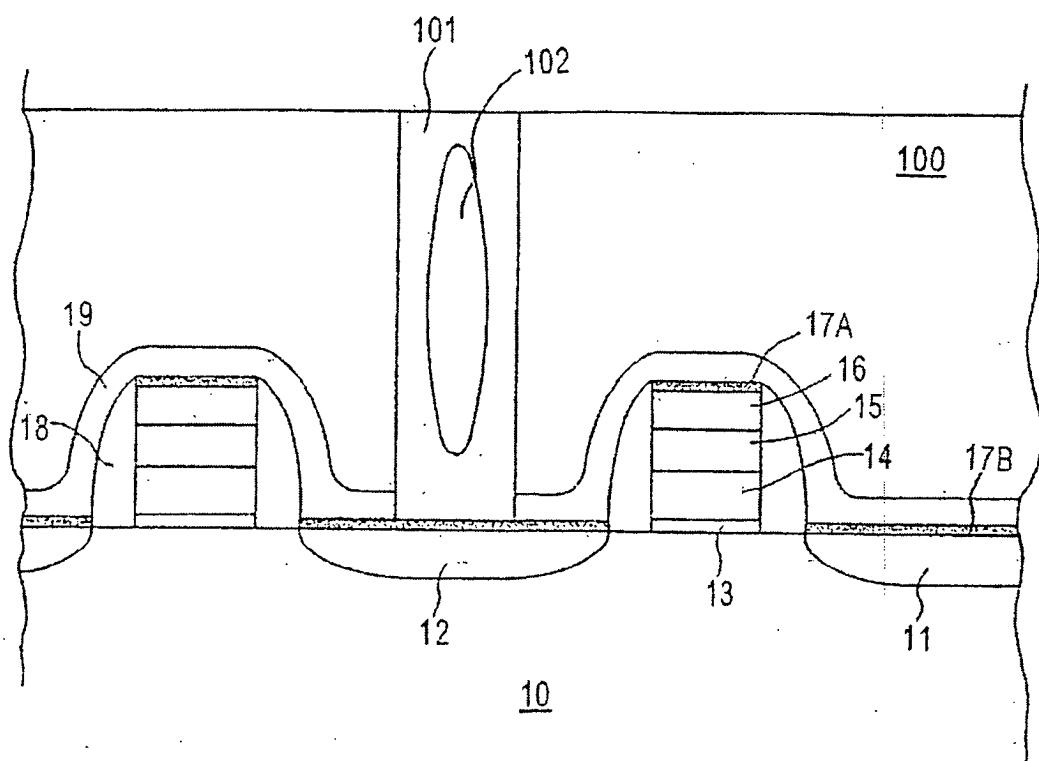

**[0011]** [Fig. 1](#) stellt schematisch das Problem eines W-Stopfen-Hohlraums dar, das von der vorliegenden Erfindung angegangen und gelöst wird.

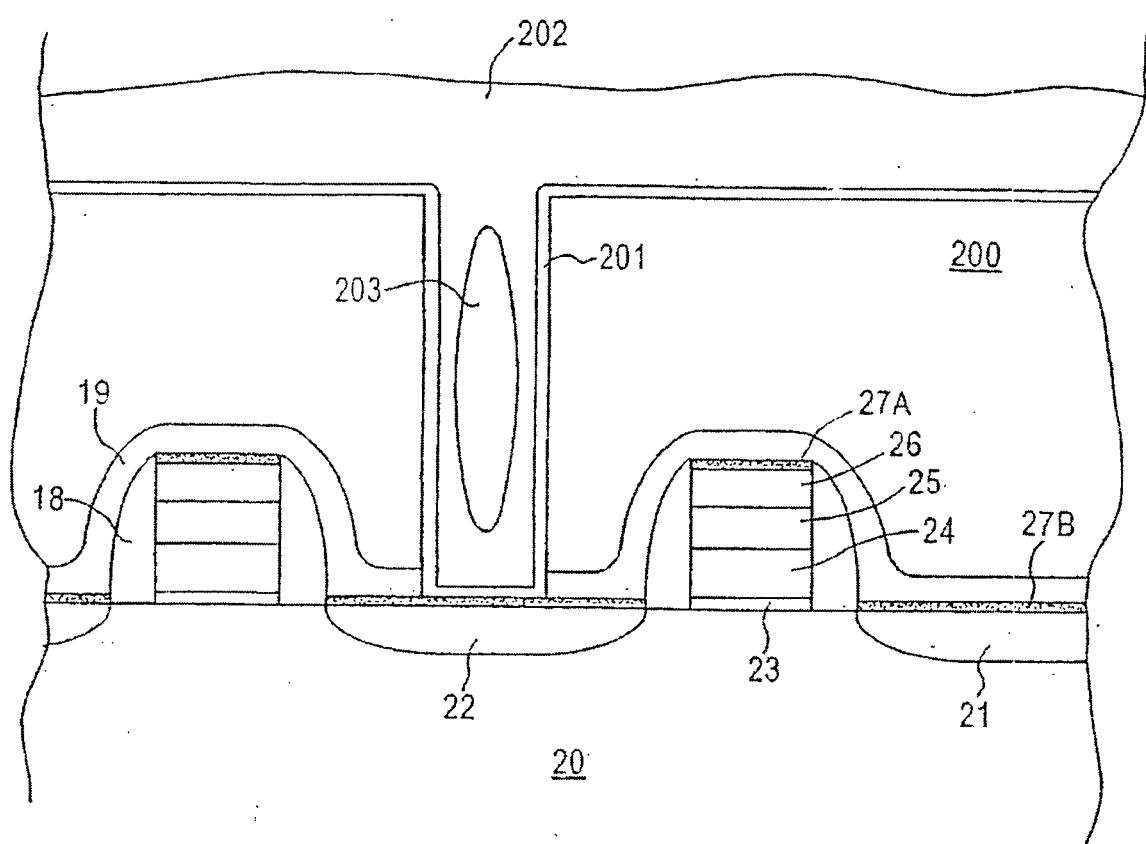

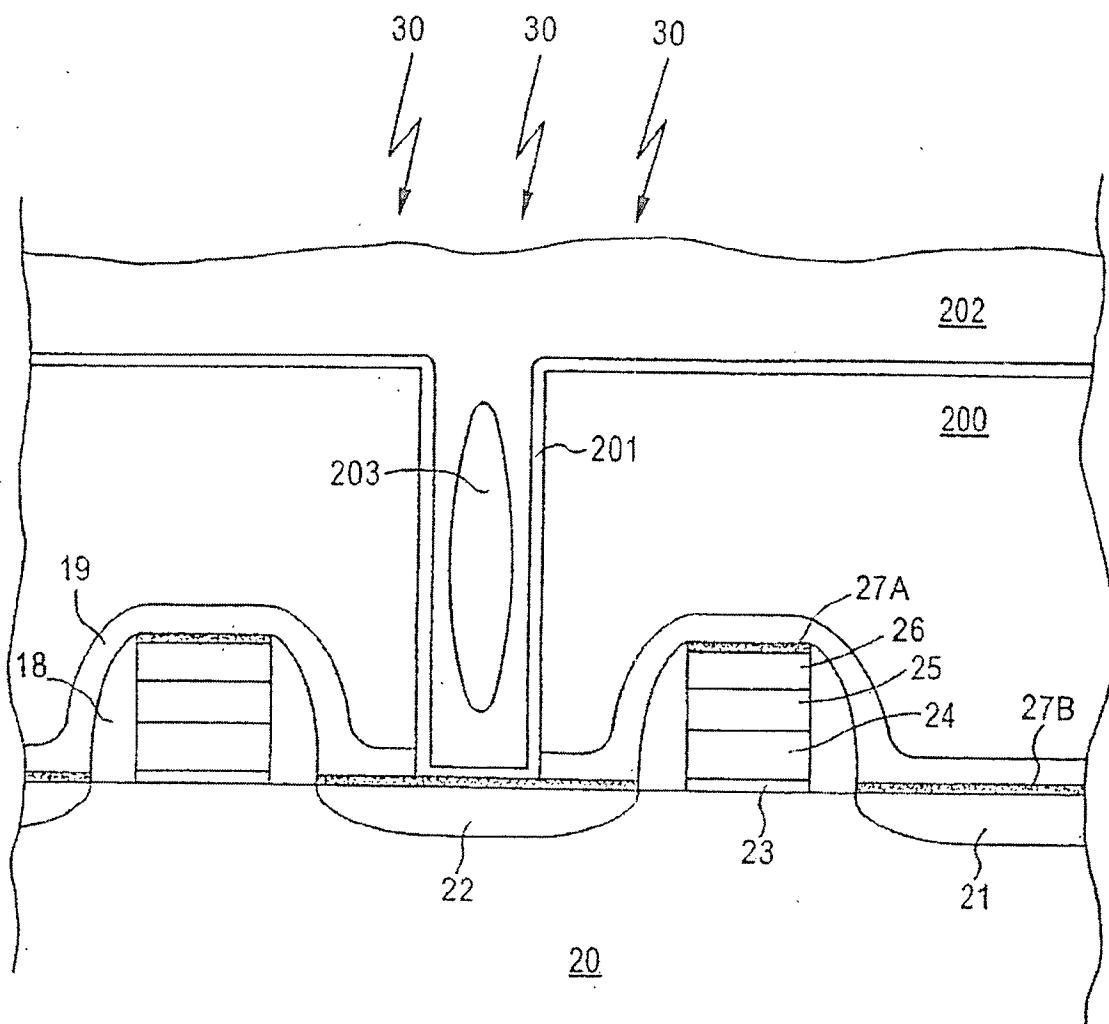

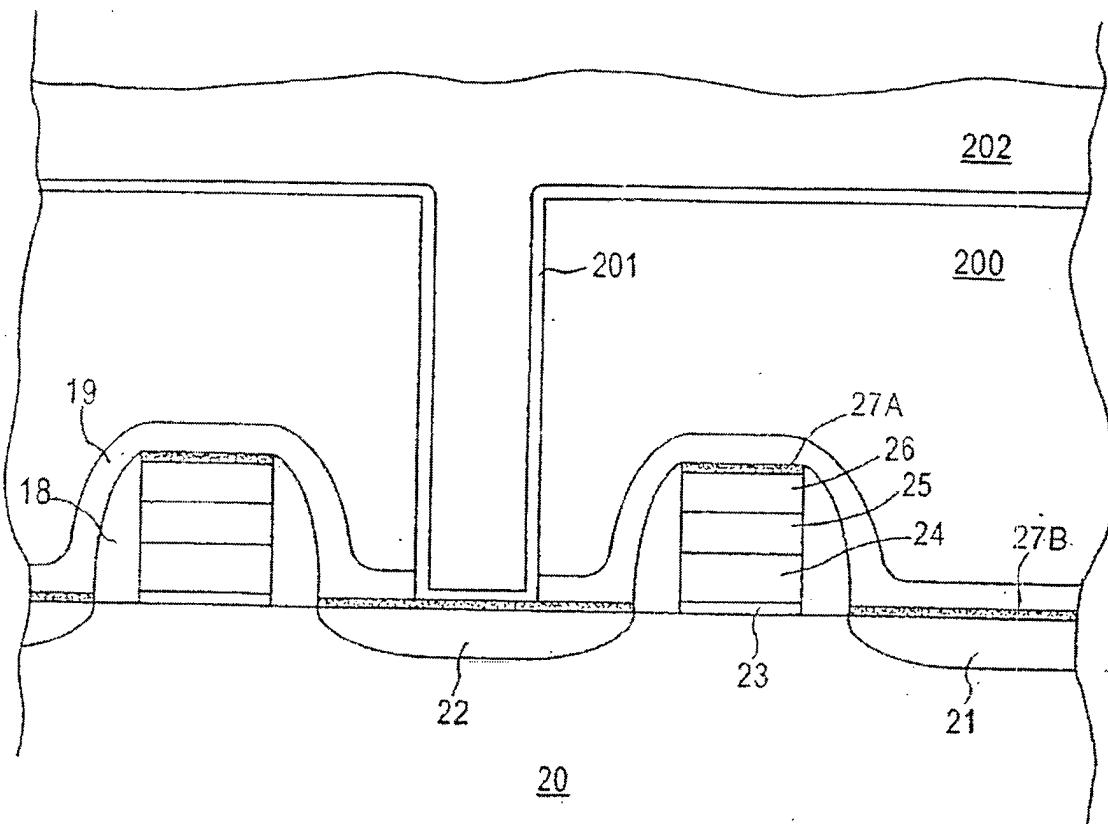

**[0012]** [Fig. 2](#) bis [Fig. 5](#) stellen schematisch aufeinanderfolgende Phasen eines Verfahrens gemäß einer Ausführungsform der vorliegenden Erfindung dar.

**[0013]** [Fig. 6](#) bis [Fig. 8](#) stellen schematisch aufeinanderfolgende Phasen eines Verfahrens gemäß einer anderen Ausführungsform der vorliegenden Erfindung dar.

**[0014]** In den [Fig. 2](#) bis [Fig. 8](#) sind ähnliche Elemente oder Merkmale mit denselben Bezugszeichen bezeichnet.

**[0015]** Die vorliegende Erfindung geht W-Kontakt-/Durchkontaktuverlässigkeitsprobleme, die sich aus der unerwünschten Bildung von Löchern mit damit einhergehender hoher und instabiler Kontaktwiderstandsverteilung und schlechter Elektromigrationsleistung, insbesondere bei Verkleinerung der Vorrichtungsgeometrien bis weit in den Submikrometerbereich hinein, ergeben, an und löst sie. Wird beispielsweise die Breite einer Kontakt-/Durchkontaktoffnung auf etwa 0,225 bis etwa 0,257 Mikrometer, z.B. etwa 0,25 Mikrometer, verringert und die Tiefe der Kontakt-/Durchkontaktoffnung auf etwa 0,81 bis etwa 0,99 Mikrometer, z.B. etwa 0,90 Mikrometer oder mehr, vergrößert und die Seitenverhältnisse nähern sich 4:1 und mehr an, wird es äußerst schwierig, die Kontakt-/Durchkontaktoffnungen zu füllen, ohne Hohlräume zu erzeugen. Die vorliegende Erfindung geht dieses Problem an und löst es, indem sie weiterhin auf herkömmliche Weise die Kontakt-/Durchkontaktoffnungen mit hohen Seitenverhältnissen auf herkömmliche Weise füllt, um einen W-Stecker mit Hohlräumen zu bilden. Die vorliegende Erfindung weicht von den herkömmlichen Praktiken ab, indem sie eine effiziente Methodik vorsieht, die die Beseitigung der beim Füllen einer Kontakt-/Durchkontaktoffnung mit einem hohen Seitenverhältnis gebildeten Hohlräume ermöglicht, wodurch der Kontaktwiderstand verringert wird, wobei sich eine enge Widerstandsverteilung ergibt und die Elektromigrationsleistung verbessert wird.

**[0016]** Gemäß den Ausführungsbeispielen der vorliegenden Erfindung wird in einer dielektrischen Schicht, wie beispielsweise einer Oxidschicht, z.B. BPSG- oder aus TEOS gewonnenes Siliziumoxid, eine Kontakt-/Durchkontaktoffnung gebildet. Dann wird ein die Öffnung auskleidendes Sperrsichtverbundmaterial gebildet. Gemäß den Ausführungsformen der Erfindung wird eine dünne Ti-Ausgangsschicht zur Auskleidung der Öffnung abgelagert, und eine Titannitridschicht wird auf die Ti-Ausgangsschicht aufgebracht. W wird dann auf herkömmliche Weise abgelagert, wobei sich eine Überlast ergibt. Zu diesem Zeitpunkt enthält das die Kontakt-/Durchkontaktoffnung füllende W unerwünschte Hohlräume oder Poren, die negative Auswirkungen auf die Leistung der Vorrichtung, einschließlich der Elektromigrationsleistung, haben.

**[0017]** Gemäß den Ausführungsformen der vorliegenden Erfindung wird das die Öffnung füllende W durch Abstrahlen eines auf das W in der Öffnung gerichteten gepulsten Laserlichtstrahls mit einer Strahlungsfluenz von etwa 0,78 bis etwa 1,10 Joule/cm<sup>2</sup> laser-erhitzt, wobei N<sub>2</sub> z.B. mit einer Fließrate von etwa 200 bis etwa 2000 ccm/s fließt. Während des Laser-Erhitzens wird die Temperatur des W in der Öffnung auf etwa 3000°C bis etwa 3600°C erhöht, was

ein Schmelzen und erneutes Verflüssigen bewirkt, wodurch die Hohlräume beseitigt werden. Anschließend kann das CMP auf herkömmliche Weise derart induziert werden, daß die Oberseite des die Öffnung füllenden W im wesentlichen komplanar mit der Oberseite der dielektrischen Schicht ist. In einer anderen Ausführungsform wird das CMP vor dem Laser-Erhitzen durchgeführt.

**[0018]** Die Anwendung des Laser-Erhitzens gemäß den Ausführungsformen der vorliegenden Erfindung zur Verringerung von Hohlräumen bei Zwischenverbindungen und zur Minderung des Kontaktwiderstands bietet einige Vorteile. Das Laser-Erhitzen z.B. ermöglicht höchste Genauigkeit beim Zielen auf das die Öffnung füllende W, wodurch das unnötige Erhöhen der Temperatur anderer Teile des Wafers, das verschiedene Probleme, wie beispielsweise ein übermäßiges Eindiffundieren von Fremdatomen, verursacht, vermieden wird.

**[0019]** Bei der Durchführung der Ausführungsformen der vorliegenden Erfindung können beliebige der verschiedenen im Handel erhältlichen Laserwerkzeuge verwendet werden, z.B. jene, die eine Laserquelle verwenden, die imstande ist, bei Energien von etwa 10 bis etwa 2000 mJ/cm<sup>2</sup>/Impuls, z.B. etwa 100 bis etwa 400 mJ/cm<sup>2</sup>/Impuls, zu arbeiten. Es gibt im Handel erhältliche Werkzeuge, die ein derartiges Laser-Erhitzen, entweder mit oder ohne Maske, durchführen können. Das Verdant Technologies-Lasererhitzungswerkzeug ist nur ein Beispiel und arbeitet bei einer Belichtungswellenlänge von 308 nm.

**[0020]** Ein von der vorliegenden Erfindung angegangenes Problem hinsichtlich eines W-Stecker-Hohlräums ist in [Fig. 1](#) dargestellt, in der auf einem Substrat **10** Transistoren gebildet sind. Die Transistoren können MOS-Transistoren und/oder Doppelgatespeicherzelltransistoren mit Floating- und Steuergates mit einer dazwischen angeordneten dielektrischen Interpoly-(ONO)-Schicht aufweisen. Die Transistoren können beispielsweise ein Tunneloxid **13**, eine Floating-Gate-Elektrode **14**, ein ONO-Stapel-Interpoly-Dielektrikum **15** und ein Steuergate **16** aufweisen. Auf der Oberseite des Gateelektrodenstapels ist eine Schicht aus Metallsilicid **17A** gebildet, während auf den Source-/Drainbereichen **11**, **12** eine Schicht aus Metallsilicid **17B** gebildet ist. An den Seitenflächen der Gateelektrode ist ein dielektrischer Seitenwandabstandhalter **18**, wie beispielsweise Siliziumoxid, Siliziumoxynitrid oder Siliziumnitrid, gebildet, und üblicherweise ist auf diesem eine Siliziumnitridätzstoppsschicht **19** abgelagert. Es wird eine dielektrische Schicht **100**, wie beispielsweise BPSG oder ein Verbundmaterial aus BPSG und aus darauf befindlichem TEOS stammendem Siliziumoxid, beispielsweise mit einer Dicke von etwa 7500 Å bis etwa 8500 Å, z.B. etwa 8000 Å, abgelagert.

**[0021]** Dann werden zur Bildung einer Kontaktöffnung in der dielektrischen Schicht **100**, wobei der Source-/Drainbereich **12** freigelegt wird, herkömmliche Photolithographie- und Ätztechniken angewandt. Danach wird zum Füllen der Kontaktöffnung W abgelagert, wobei eine Überlast gebildet wird, und dann wird CMP durchgeführt, wobei der W-Stecker **101** mit einem unerwünschten Porositätsgrad **102** hinterlassen wird. Die vorliegende Erfindung löst dieses bestimmte Problem effektiv auf effiziente Weise, wodurch derartige Hohlräume bedeutend verringert oder beseitigt werden, wobei damit eine Verbesserung der Elektromigrationsleistung und der Vorrichtungsuverlässigkeit einhergeht.

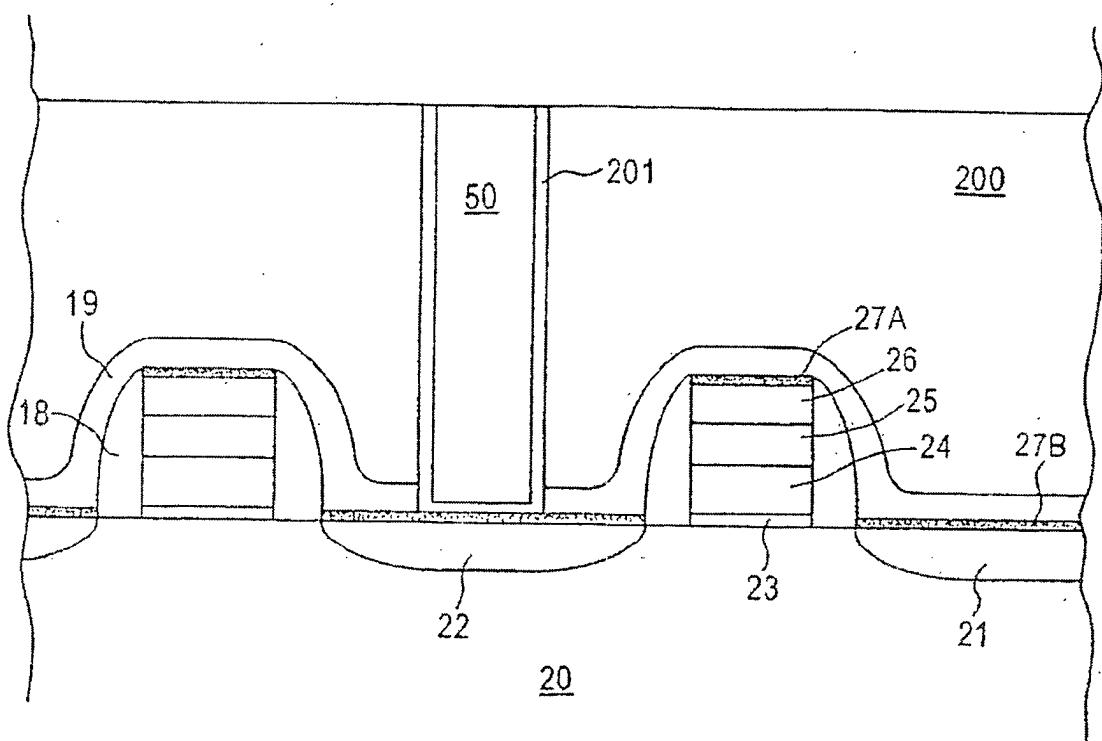

**[0022]** Eine Ausführungsform der vorliegenden Erfindung ist in den [Fig. 2](#) bis [Fig. 5](#) schematisch dargestellt. Gemäß [Fig. 2](#) sind auf einem Substrat **20** Transistoren gebildet. Der Transistor kann MOS-Transistoren und/oder Doppelgatespeicherzelltransistoren mit Floating- und Steuergates mit einer dazwischen angeordneten dielektrischen Interpoly-(ONO)-Schicht aufweisen. Der Transistor kann beispielsweise ein Tunneloxid **23**, eine Floating-Gate-Elektrode **24** und ein ONO-Stapel-Interpoly-Dielektrikum **25** und ein Steuergate **26** aufweisen. Auf der Oberseite des Gateelektrodenstapels ist eine Schicht aus Metallsilicid **27A**, z.B. Nickelsilicid, gebildet, während auf den Source-/Drainbereichen **21**, **22** ein Schichtmetallsilicid **27B**, z.B. Nickelsilicid, gebildet ist. An den Seitenflächen der Gateelektrode ist ein dielektrischer Seitenwandabstandhalter **28**, wie beispielsweise Siliziumoxid, Siliziumoxynitrid oder Siliziumnitrid, gebildet, und üblicherweise ist darauf eine Siliziumnitridätzstoppsschicht **29** abgelagert. Eine dielektrische Schicht **200**, wie beispielsweise BPSG, oder ein Verbundmaterial aus BPSG und aus dem darauf befindlichen TEOS stammenden Siliziumoxid, wird beispielsweise mit einer Dicke von etwa 7500 Å bis etwa 8500 Å, z.B. etwa 8000 Å, abgelagert.

**[0023]** Dann werden herkömmliche Photolithographie- und Ätztechniken zur Bildung einer Kontaktöffnung in der dielektrischen Schicht **200** durchgeführt, wobei der Source-/Drainbereich **22** freigelegt wird. Üblicherweise hat die Kontaktöffnung ein Seitenverhältnis (Tiefe/Durchmesser) von etwa 4:1 oder mehr.

**[0024]** Anschließend wird zur Auskleidung der Öffnung eine Verbundsperrsenschicht **201**, wie beispielsweise eine Ausgangsschicht aus Ti und eine darauf befindliche Titanitritidschicht, aufgebracht. Danach wird zur Füllung der Öffnung und Bildung einer Überlast **202** W abgelagert. Aufgrund des hohen Seitenverhältnisses der Kontaktöffnung entsteht in dem W-Stecker ein bedeutender Hohlräumanteil **203**.

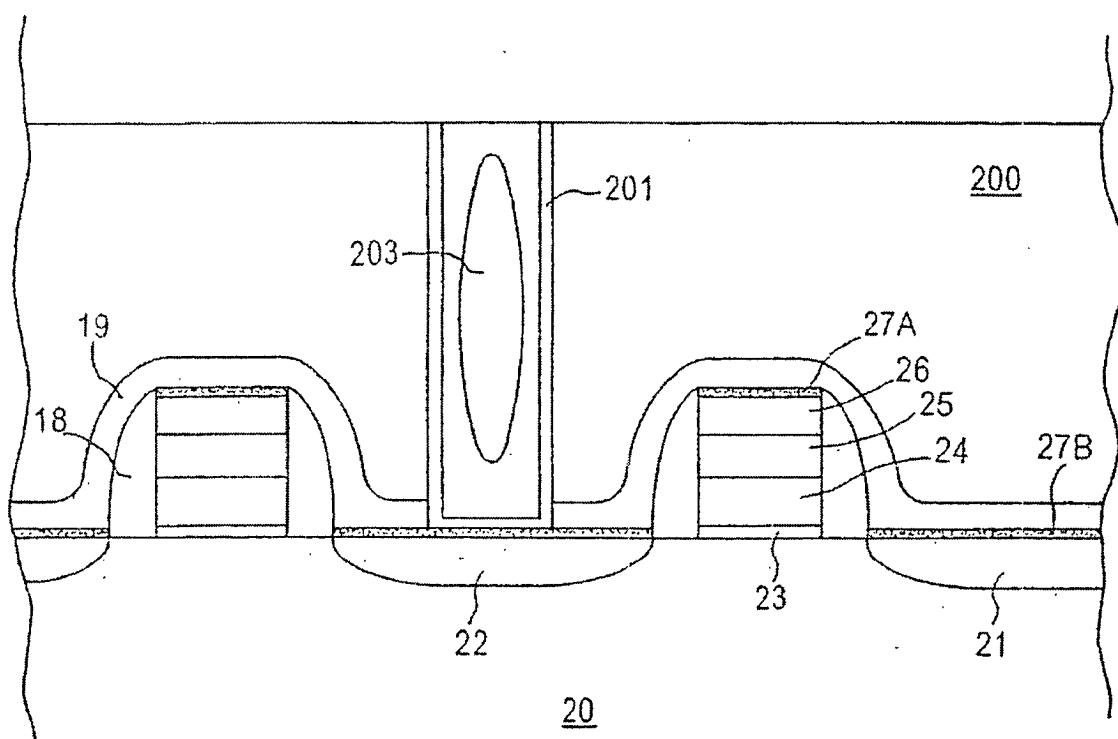

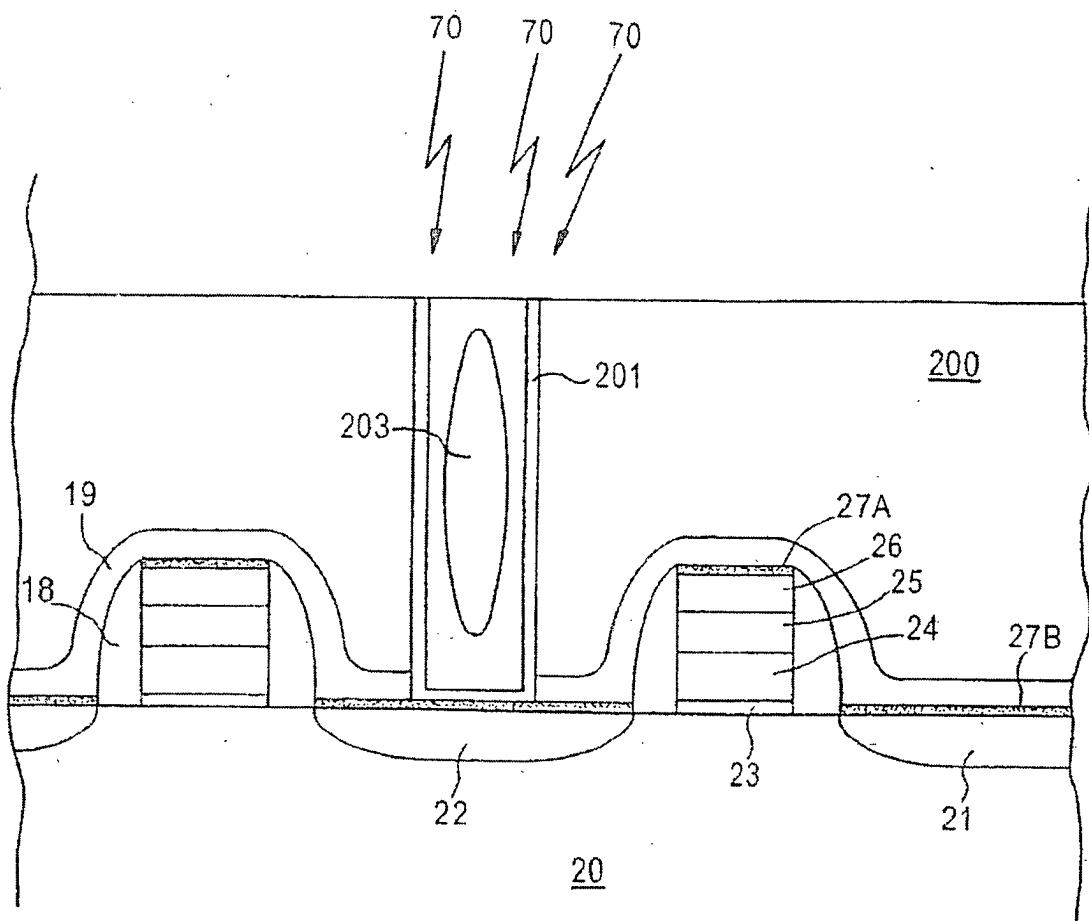

**[0025]** Gemäß einer Ausführungsform der vorliegenden Erfindung wird, wie in [Fig. 3](#) dargestellt, das

Laser-Erhitzen durch Abstrahlen eines auf den gefüllten Kontakt gerichteten gepulsten Laserlichtstrahls auf das abgelagerte W, wie dies durch die Pfeile **30** schematisch dargestellt ist, üblicherweise mit einer Strahlungsfluenz von etwa 0,78 bis etwa 1,10 Joule/cm<sup>2</sup>, über einen Zeitraum von etwa 10 bis etwa 100 Nanosekunden durchgeführt, wodurch die Temperatur des W in dem Stecker auf etwa 3000 bis etwa 3600°C erhöht wird, wodurch, wie schematisch in **Fig. 4** dargestellt, ein Schmelzen und erneutes Verflüssigen zur Beseitigung der Hohlräume bewirkt wird. Dann wird CMP durchgeführt, was die in **Fig. 5** dargestellte Struktur zur Folge hat, bei der der Wolframstecker **50** keine Hohlräume aufweist.

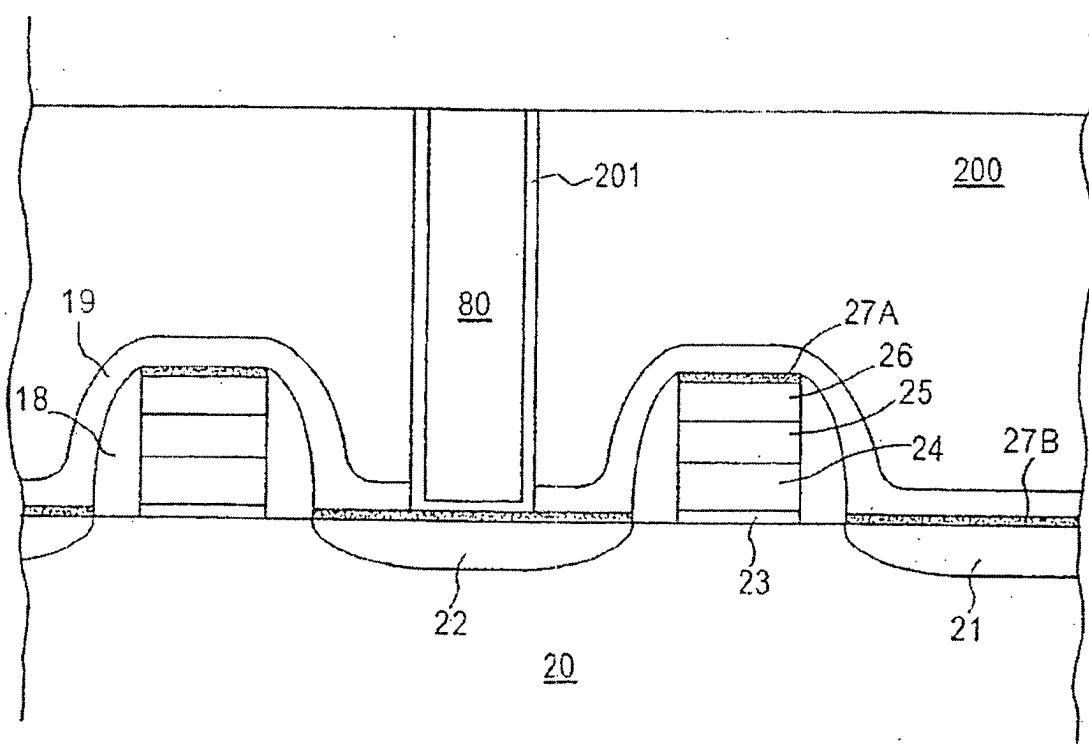

**[0026]** Wie in den **Fig. 6** bis **Fig. 8** schematisch dargestellt, wird gemäß einer anderen Ausführungsform der vorliegenden Erfindung das CMP vor dem Laser-Erhitzen durchgeführt. Gemäß **Fig. 6** ist die dargestellte Struktur diejenige, die sich aus der Durchführung des CMP an der in **Fig. 2** schematisch dargestellten Struktur ergibt. Dann wird das Laser-Erhitzen, wie in **Fig. 7** dargestellt, durch Abstrahlen eines auf den W-Stecker gerichteten gepulsten Laserlichtstrahls durchgeführt, wodurch ein erneutes Verflüssigen und das Beseitigen des Hohlräums bewirkt wird. Die daraus folgende Struktur ist in **Fig. 8** schematisch dargestellt und weist einen W-Stecker **80** ohne Hohlräume auf.

**[0027]** Die vorliegende Erfindung sieht eine Methodik vor, die die Bildung von Zwischenverbindungen mit W-Kontakten und/oder -Durchkontakten mit großen Seitenverhältnissen, z.B. 4 oder größer, mit kleinen oder wesentlich reduzierten Hohlräumen ermöglicht, wodurch der Kontaktwiderstand verringert und die Kontaktwiderstandsverteilung stabilisiert wird, um für eine engere Widerstandsverteilung zu sorgen, wobei die Zuverlässigkeit der Vorrichtung und die Elektromigrationsleistung verbessert werden. Die vorliegende Erfindung genießt industrielle Anwendbarkeit bei der Herstellung einer beliebigen von verschiedenen Arten von Halbleitervorrichtungen mit verbesserter Zuverlässigkeit und erhöhter Schaltungsgeschwindigkeit. Die vorliegende Erfindung lässt sich insbesondere bei der Herstellung von Halbleitervorrichtungen mit Gestaltungsmerkmalen weit im Submikrometerbereich, wie beispielsweise von Flash-Speicher-Vorrichtungen, z.B. EEPROMs, mit einem Entwurfsmaß von etwa 0,12 Mikrometer und darunter, mit bedeutend verbesserter Zuverlässigkeit, erhöhter Schaltungsgeschwindigkeit, verbesserter Elektromigrationsleistung und verbessertem Herstellungs durchsatz, anwenden.

**[0028]** In der vorstehenden detaillierten Beschreibung wird die vorliegende Erfindung mit Bezug auf bestimmte beispielhafte Ausführungsformen derselben beschrieben. Es ist jedoch offensichtlich, daß verschiedene Modifizierungen und Veränderungen

daran vorgenommen werden können, ohne vom breiteren Umfang der vorliegenden Erfindung, wie er in den Ansprüchen angegeben ist, abzuweichen. Die Beschreibung und die Zeichnungen sind daher als veranschaulichend und nicht als einschränkend anzusehen. Es sei darauf hingewiesen, daß die vorliegende Erfindung in verschiedenen anderen Kombinationen und Umgebungen verwendbar und innerhalb des Umfangs des erforderlichen Konzepts in der hier ausgedrückten Form veränderbar oder modifizierbar ist.

## Patentansprüche

1. Verfahren zur Herstellung einer Halbleitervorrichtung mit den folgenden Schritten:

Bilden einer Öffnung in einer dielektrischen Schicht (**200**);

Ablagern von Wolfram (W) (**202**) zum Füllen der Öffnung; und

Laser-Erhitzen (**30**) des abgelagerten W zum Schmelzen und erneuten Verflüssigen des W in der Öffnung.

2. Verfahren nach Anspruch 1, mit dem Schritt des Laser-Erhitzens durch Abstrahlen eines gepulsten Laserlichtstrahls (**30**) auf das die Öffnung füllende abgelagerte W (**202**) mit einer Strahlungsfluenz von ungefähr 0,78 bis ungefähr 1,10 Joule/cm<sup>2</sup>.

3. Verfahren nach Anspruch 2, mit dem Schritt des Laser-Erhitzens (**30**), um das die Öffnung füllende W auf eine Temperatur von ungefähr 3000°C bis ungefähr 3600°C zu erwärmen, wodurch das W in der Öffnung wieder verflüssigt wird.

4. Verfahren nach Anspruch 1, mit dem Schritt des Laser-Erhitzens (**30**) in Stickstoff (N<sub>2</sub>).

5. Verfahren nach Anspruch 4, mit dem Schritt des Laser-Erhitzens (**30**) unter Verwendung einer N<sub>2</sub>-Fließrate von ungefähr 200 bis ungefähr 2000 ccm/min.

6. Verfahren nach Anspruch 1, mit dem Schritt des Ablagerns einer Sperrsicht (**201**), welche die Öffnung vor dem Ablagern des W auskleidet.

7. Verfahren nach Anspruch 1, mit dem Schritt des Durchführens eines chemisch-mechanischen Polierens (CMP) nach dem Laser-Erhitzen, derart daß die Oberseite des in der Öffnung befindlichen W (**50**) im wesentlichen komplanar mit der Oberseite der dielektrischen Schicht (**200**) ist.

8. Verfahren nach Anspruch 1, mit dem Schritt des Durchführens eines chemisch-mechanischen Polierens (CMP) vor dem Laser-Erhitzen, derart daß die Oberseite des in der Öffnung befindlichen W (**80**) im wesentlichen komplanar mit der Oberseite der di-

elektrischen Schicht (**200**) ist.

9. Verfahren nach Anspruch 4, mit dem Schritt des Laser-Erhitzens durch Abstrahlen eines gepulsten Laserlichtstrahls (**30**) auf das die Öffnung füllende abgelagerte W (**202**) mit einer Strahlungsfluenz von ungefähr 0,78 bis ungefähr 1,10 Joule/cm<sup>2</sup>.

10. Verfahren nach Anspruch 9, mit dem Schritt des Laser-Erhitzens (**30**), um das die Öffnung füllende W (**202**) auf eine Temperatur von ungefähr 3000°C bis ungefähr 3600°C zu erwärmen, wodurch das W in der Öffnung wieder verflüssigt wird.

Es folgen 8 Blatt Zeichnungen

Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8