|                                     |                        |

|-------------------------------------|------------------------|

| <b>DOMANDA DI INVENZIONE NUMERO</b> | <b>102021000030134</b> |

| <b>Data Deposito</b>                | <b>29/11/2021</b>      |

| <b>Data Pubblicazione</b>           | <b>29/05/2023</b>      |

Classifiche IPC

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| H              | 03            | M                  | 1             | 08                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| H              | 03            | M                  | 1             | 74                 |

| <b>Sezione</b> | <b>Classe</b> | <b>Sottoclasse</b> | <b>Gruppo</b> | <b>Sottogruppo</b> |

|----------------|---------------|--------------------|---------------|--------------------|

| H              | 03            | M                  | 1             | 78                 |

Titolo

Circuito convertitore digitale-analogico

**DESCRIZIONE** dell'invenzione industriale dal titolo:

"Circuito convertitore digitale-analogico"

di: STMicroelectronics S.r.l., di nazionalità italiana, via C. Olivetti, 2 - 20864 Agrate Brianza (MB) - Italia

Inventori designati: Agatino Massimo MACCARRONE, Antonino CONTE, Francesco TOMAIUOLO, Michelangelo PISASALE, Marco RUTA

Depositata il: 29 novembre 2021

\*\*\*\*

**TESTO DELLA DESCRIZIONE**

Campo tecnico

La descrizione si riferisce a convertitori digitale-analogico a pilotaggio di corrente (IDAC) che possono essere applicati, per esempio, a dispositivi di memoria quali dispositivi di memoria a cambiamento di fase (PCM, "Phase-Change Memory") e/o microcontrollori "general purpose" (GP MCU).

Sfondo tecnologico

La memoria a cambiamento di fase è un tipo di memoria non volatile (NVM, "Non-Volatile Memory"), in particolare un tipo di memoria ad accesso casuale (RAM, "Random-Access Memory") non volatile. Il materiale di una cella di memoria a cambiamento di fase convenzionale è tipicamente una lega di calcogenuro composta da germanio (Ge), antimonio (Sb) e tellurio (Te), denominata GST (per esempio, avente composizione  $Ge_2Sb_2Te_5$ ). La lega di calcogenuro è in grado di cambiare fase (cristallina o amorfa) in modo reversibile e controllato per mezzo di una corrente di programmazione che passa attraverso la cella di memoria e induce il

cambiamento di fase riscaldando in modo appropriato la lega di calcogenuro (cioè l'elemento di memorizzazione della memoria).

Conventionalmente, il calore prodotto dal passaggio della corrente di programmazione è utilizzato per riscaldare e raffreddare rapidamente la lega, rendendola amorfa (stato RESET e impulso di corrente di programmazione RESET), o per mantenere la lega nel suo intervallo di temperatura di cristallizzazione per qualche tempo, passando così a uno stato (poli)cristallino (stato SET e impulso di corrente di programmazione SET). L'impiego di due diverse fasi della lega di calcogenuro in una cella di memoria si basa sul riconoscimento che la fase cristallina ha una bassa resistenza elettrica (per esempio, corrispondente per convenzione al valore logico 1 o stato SET) e la fase amorfa ha un'elevata resistenza elettrica (per esempio, corrispondente per convenzione al valore logico 0 o stato RESET).

Pertanto, le operazioni SET e RESET di una cella di memoria in una memoria a cambiamento di fase sono utilizzate per modificare il contenuto della cella da "0" a "1" e viceversa, applicando una corrente di programmazione controllata con una forma definita per consentire all'elemento di memorizzazione della memoria di cambiare il suo stato da non conduttore (con un'elevata resistenza elettrica) a conduttore (con una bassa resistenza elettrica) e viceversa, modificando la sua morfologia da amorfa a (poli)cristallina e viceversa.

Durante gli impulsi SET e RESET, la corrente di programmazione attraverso la cella di memoria dovrebbe avere un comportamento temporale definito (per esempio, una forma definita degli impulsi di corrente SET e/o RESET) in

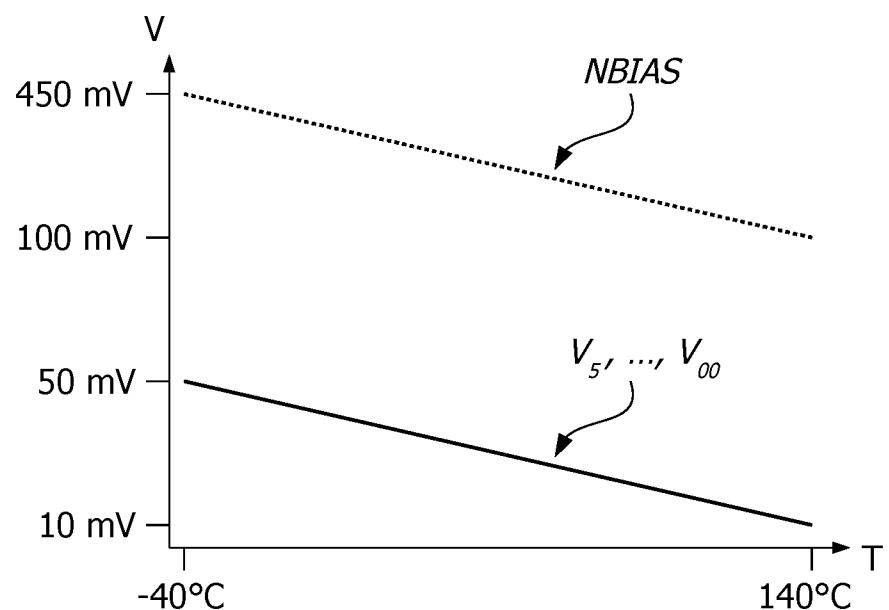

modo da produrre una variazione controllata della temperatura dell'elemento di memorizzazione della memoria. Per esempio, la figura 1 è un diagramma temporale esemplificativo del comportamento atteso della corrente di programmazione  $I_{CELL}$  di una cella di memoria a cambiamento di fase durante l'impulso SET, che dovrebbe produrre una variazione costante del gradiente di temperatura e consentire all'elemento di memorizzazione della memoria di passare a uno stato policristallino. La corrente di programmazione  $I_{CELL}$  durante l'impulso SET dovrebbe aumentare rapidamente da zero a un valore di plateau  $I_1$ , mantenere il valore  $I_1$  per un intervallo di tempo  $t_{1P}$ , e successivamente tornare lentamente (per esempio, scendere) a zero durante un intervallo di tempo  $t_{1F}$  con un tasso di diminuzione costante (per esempio, linearmente).

Pertanto, un circuito di pilotaggio è convenzionalmente utilizzato per iniettare la corrente desiderata nell'elemento di memorizzazione della memoria, a partire da una corrente di riferimento generata da un convertitore digitale-analogico a pilotaggio di corrente.

I convertitori digitale-analogico a pilotaggio di corrente secondo un'architettura "W-2W" sono convenzionalmente utilizzati in tali applicazioni, poiché occupano una piccola area di silicio. Il documento Gupta, Shantanu Sen et al., "W-2W Current Steering DAC for Programming Phase Change Memory", 2009 IEEE Workshop on Microelectronics and Electron Devices (2009): 1-4, è esemplificativo di tale approccio convenzionale.

Tuttavia, a causa della loro topologia, i circuiti IDAC W-2W possono soffrire di un errore sistematico che colpisce alcuni transistori dell'architettura, e possono quindi non riuscire a produrre un impulso di corrente di

uscita con la forma corretta prevista durante un impulso SET (cioè, linearmente decrescente).

Pertanto, c'è la necessità nella tecnica di fornire convertitori digitali-analogici W-2W a pilotaggio di corrente migliorati in grado di produrre impulsi di corrente di uscita con la forma e la linearità desiderate.

#### Scopo e sintesi

Uno scopo di una o più forme di attuazione è contribuire a fornire tali convertitori digitali-analogici a pilotaggio di corrente migliorati secondo un'architettura W-2W.

Secondo una o più forme di attuazione, tale scopo può essere raggiunto da un circuito avente le caratteristiche esposte nelle rivendicazioni che seguono.

Le rivendicazioni sono parte integrante dell'insegnamento tecnico qui fornito in relazione alle forme di attuazione.

In una o più forme di attuazione, un circuito comprende un transistore MOS connesso a diodo che ha un terminale di drain connesso a un nodo di ingresso e un terminale di source connesso a un nodo di tensione di riferimento. Il transistore MOS connesso a diodo è configurato per fare passare una corrente di riferimento dal nodo di ingresso al nodo di tensione di riferimento. Una pluralità di transistori MOS di mirroring ordinati hanno rispettivi terminali di gate connessi a un terminale di gate del transistore MOS connesso a diodo e rispettivi terminali di drain accoppiabili alternativamente a un primo nodo di corrente o a un secondo nodo di corrente in funzione di una pluralità di rispettivi segnali di controllo ordinati. Un primo transistore MOS di mirroring

nella pluralità di transistori MOS di mirroring ordinati ha un terminale di source direttamente connesso al nodo di tensione di riferimento. Una pluralità di transistori MOS di controllo di corrente hanno rispettivi terminali di gate connessi al terminale di gate del transistore MOS connesso a diodo, e ogni transistore MOS di controllo di corrente è disposto tra i terminali di source di due transistori MOS di mirroring consecutivi nella pluralità di transistori MOS di mirroring. Il transistore MOS connesso a diodo e i transistori MOS di mirroring hanno tutti le stesse dimensioni di canale, e i transistori MOS di controllo di corrente hanno tutti le stesse dimensioni di canale. Il canale dei transistori MOS di controllo di corrente presenta la stessa lunghezza e il doppio della larghezza del canale del transistore MOS connesso a diodo. I transistori MOS di mirroring il cui terminale di source non è direttamente connesso al nodo di tensione di riferimento hanno i rispettivi terminali di bulk configurati per ricevere uno o più segnali di compensazione aventi rispettivi valori che diminuiscono con l'aumentare della temperatura.

Una o più forme di attuazione possono quindi facilitare la compensazione dell'effetto di body ("body effect") dei transistori MOS di mirroring in un convertitore digitale-analogico W-2W a pilotaggio di corrente.

In una o più forme di attuazione, l'uno o più segnali di compensazione dipendono linearmente dalla temperatura.

In una o più forme di attuazione, il circuito comprende un circuito di compensazione configurato per produrre l'uno o più segnali di compensazione. Il circuito di compensazione comprende una configurazione di generatore

di corrente proporzionale alla temperatura assoluta configurata per produrre un segnale di tensione di compensazione che diminuisce linearmente in funzione dell'aumento della temperatura; un circuito partitore di tensione; e uno stadio buffer configurato per fornire il segnale di tensione di compensazione al circuito partitore di tensione. L'uno o più segnali di compensazione sono prodotti in uno o più nodi intermedi del circuito partitore di tensione.

In una o più forme di attuazione, la configurazione di generatore di corrente proporzionale alla temperatura assoluta comprende un primo transistore MOS a canale p e un primo transistore MOS a canale n disposti in serie tra un nodo di tensione di alimentazione e il nodo di tensione di riferimento; e un secondo transistore MOS a canale p e un secondo transistore MOS a canale n disposti in serie tra il nodo di tensione di alimentazione e il nodo di tensione di riferimento. Il primo transistore MOS a canale n ha un terminale di source accoppiato al nodo di tensione di riferimento, un terminale di drain accoppiato a un terminale di drain del primo transistore MOS a canale p, e un terminale di gate configurato per ricevere una tensione di riferimento di bandgap. Il primo transistore MOS a canale p ha un terminale di source accoppiato al nodo di tensione di alimentazione e un terminale di gate accoppiato al suo terminale di drain. Il secondo transistore MOS a canale p ha un terminale di source accoppiato al nodo di tensione di alimentazione, un terminale di drain accoppiato a un terminale di drain del secondo transistore MOS a canale n, e un terminale di gate accoppiato al terminale di gate del primo transistore MOS a canale p. Il secondo transistore MOS a canale n ha un terminale di source

accoppiato al nodo di tensione di riferimento e un terminale di gate accoppiato al suo terminale di drain. Il segnale di tensione di compensazione è prodotto al terminale di gate del secondo transistore MOS a canale n.

In una o più forme di attuazione, lo stadio buffer comprende un circuito amplificatore che ha un terminale di uscita accoppiato al circuito partitore di tensione, un terminale di ingresso non invertente configurato per ricevere il segnale di tensione di compensazione, e un terminale di ingresso invertente accoppiato al suo terminale di uscita.

In una o più forme di attuazione, i transistori MOS di mirroring il cui terminale di source non è direttamente connesso al nodo di tensione di riferimento possono comprendere (per esempio, sono costituiti da) transistori MOS a triplo pozzo a canale n.

In una o più forme di attuazione, un terminale di source di un ultimo transistore MOS di mirroring nella pluralità di transistori MOS di mirroring ordinati è direttamente connesso a un terminale di source di un penultimo transistore MOS di mirroring nella pluralità di transistori MOS di mirroring ordinati.

In una o più forme di attuazione, l'ultimo transistore MOS di mirroring e il penultimo transistore MOS di mirroring hanno i rispettivi terminali di bulk configurati per ricevere lo stesso segnale di compensazione.

In una o più forme di attuazione, un terminale di drain di un ultimo transistore MOS di mirroring nella pluralità di transistori MOS di mirroring ordinati e un terminale di drain di un penultimo transistore MOS di mirroring nella pluralità di transistori MOS di mirroring ordinati sono costantemente accoppiati al secondo nodo di

corrente.

In una o più forme di attuazione, i terminali di drain della pluralità di transistori MOS di mirroring ordinati sono accoppiabili alternativamente al primo nodo di corrente o al secondo nodo di corrente tramite rispettivi interruttori attivabili in funzione dei rispettivi segnali di controllo ordinati.

In una o più forme di attuazione, il transistore MOS connesso a diodo, la pluralità di transistori MOS di mirroring e la pluralità di transistori MOS di controllo di corrente comprendono (per esempio, sono costituiti da) transistori a canale n.

In una o più forme di attuazione, il circuito comprende un primo transistore MOS di uscita connesso a diodo che ha un terminale di drain connesso al primo nodo di corrente e un terminale di source connesso a un nodo di tensione di alimentazione, e un secondo transistore MOS di uscita connesso a diodo che ha un terminale di drain connesso al secondo nodo di corrente e un terminale di source connesso al nodo di tensione di alimentazione.

#### Breve descrizione delle figure

Una o più forme di attuazione saranno ora descritte, solo a titolo di esempio, con riferimento alle figure allegate, in cui:

- la figura 1, precedentemente presentata, è un diagramma temporale esemplificativo del comportamento atteso della corrente di programmazione di una cella di memoria a cambiamento di fase durante un impulso SET;

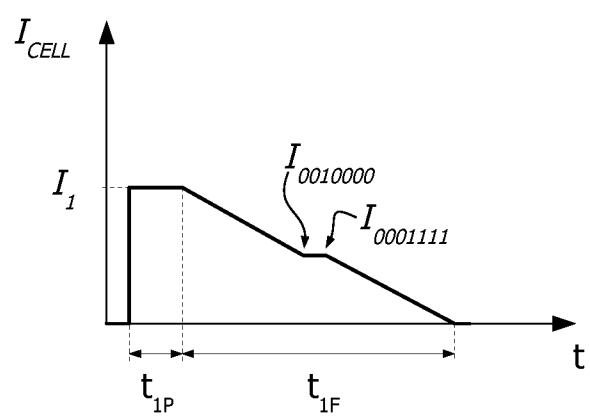

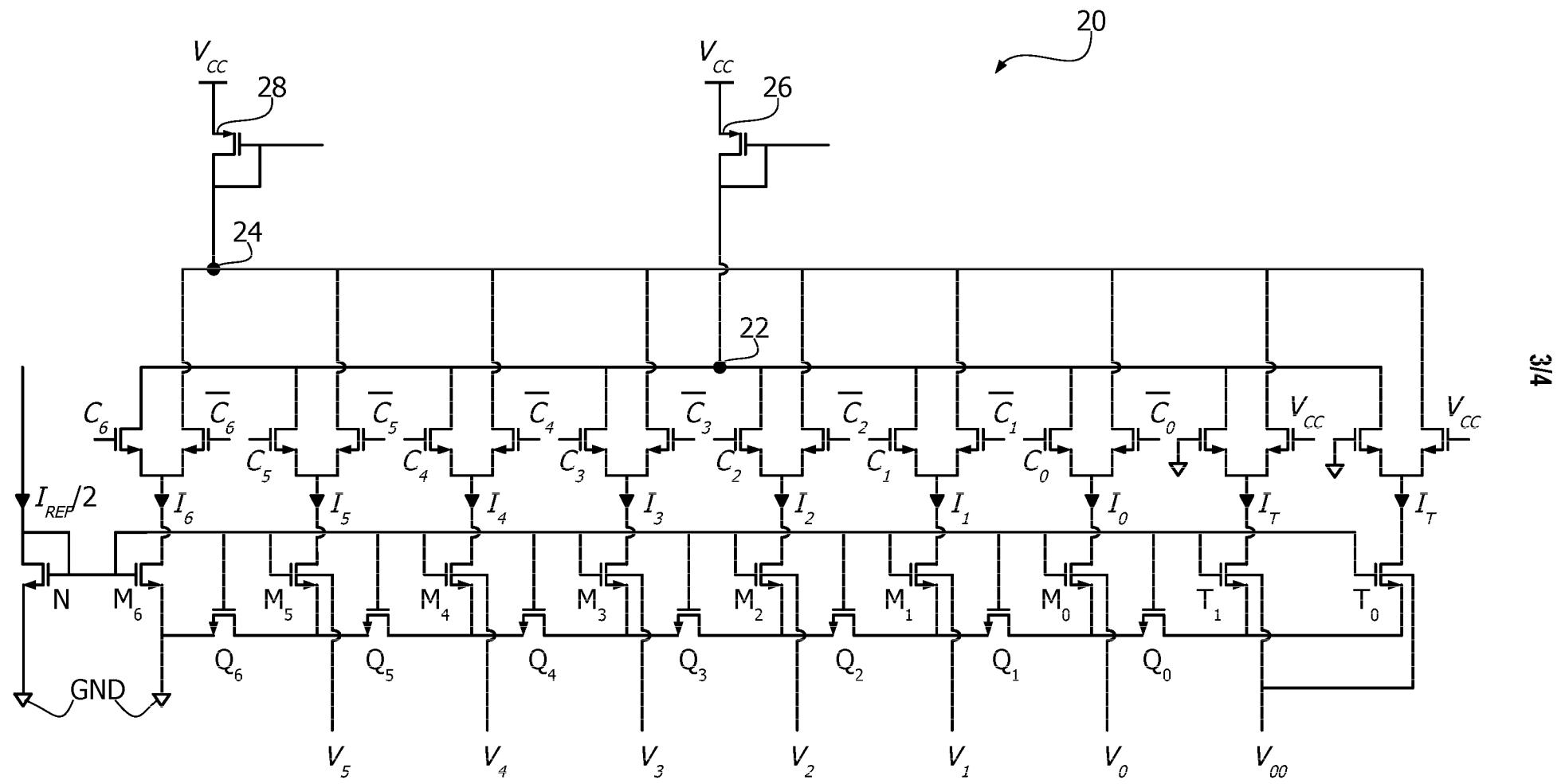

- la figura 2 è uno schema circuitale esemplificativo di un convertitore digitale-analogico (IDAC) basato su un'architettura a specchio di corrente W-2W;

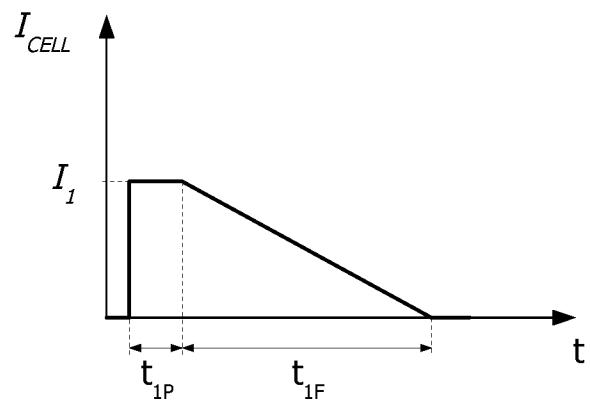

- la figura 3 è un diagramma temporale esemplificativo del possibile comportamento della corrente di programmazione di una cella di memoria a cambiamento di fase durante un impulso SET, prodotta dal circuito DAC della figura 2;

- la figura 4 è uno schema circuitale esemplificativo di un convertitore digitale-analogico a pilotaggio di corrente (IDAC) basato su un'architettura a specchio di corrente W-2W secondo una o più forme di attuazione della presente descrizione;

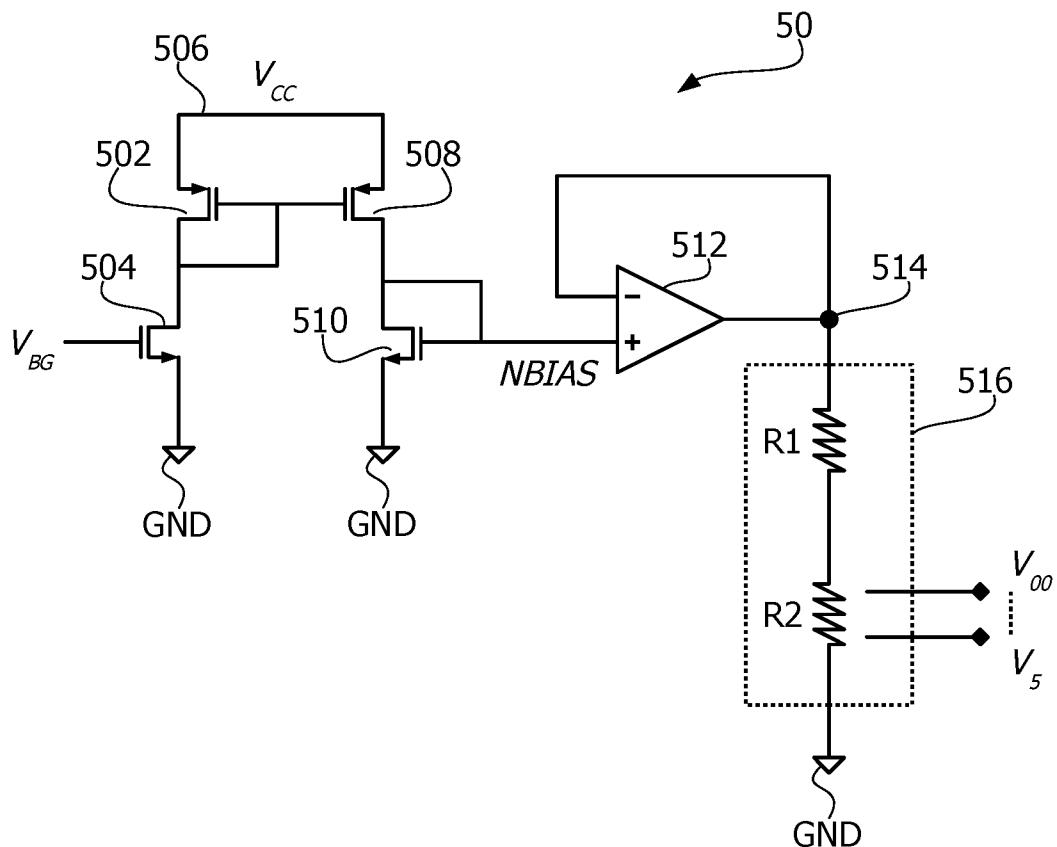

- la figura 5 è uno schema circuitale esemplificativo di un circuito di compensazione per un convertitore digitale-analogico a pilotaggio di corrente (IDAC) secondo una o più forme di attuazione della presente descrizione; e

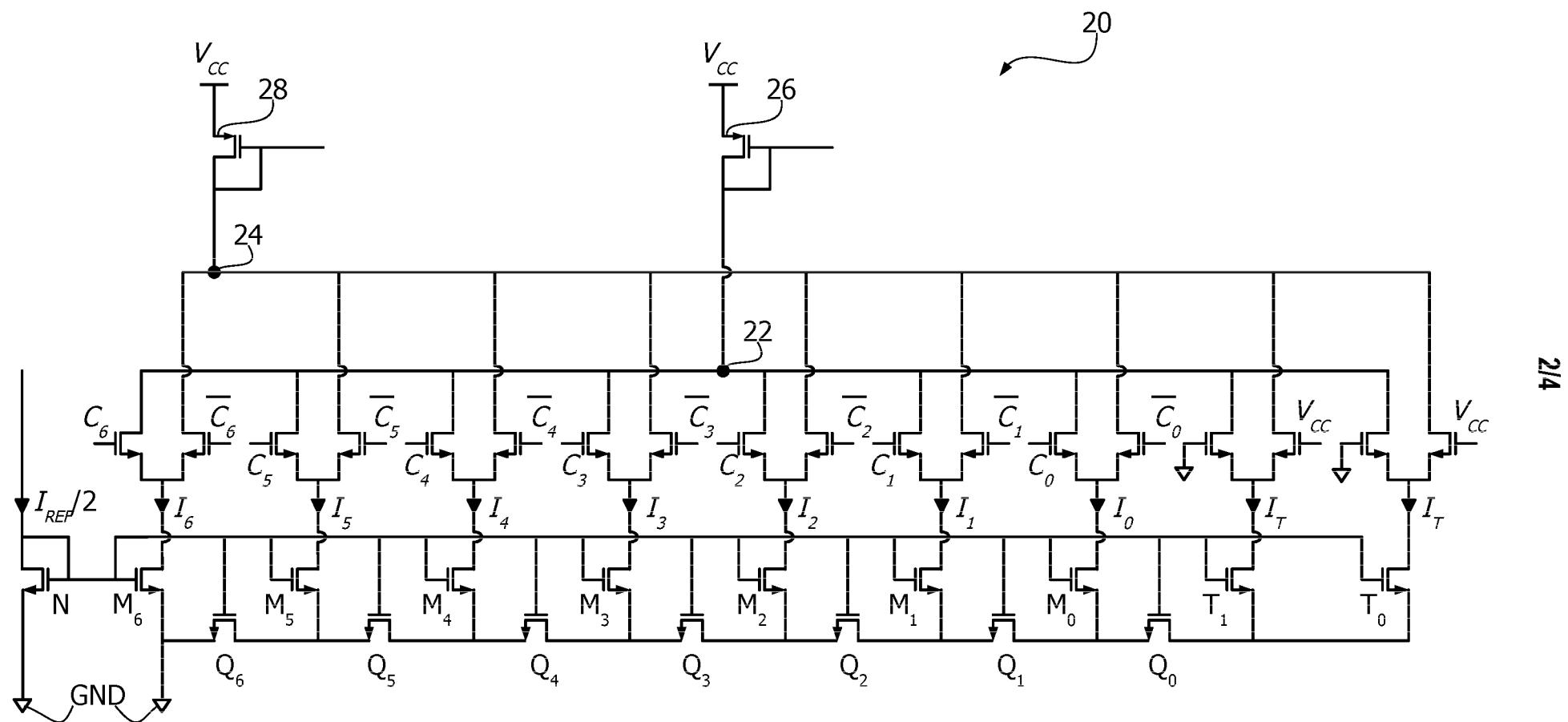

- la figura 6 è un diagramma tensione-temperatura esemplificativo della dipendenza dalla temperatura di uno o più segnali di compensazione prodotti dal circuito di compensazione della figura 5.

Descrizione dettagliata di forme di attuazione esemplificative

Nella descrizione che segue, sono illustrati uno o più dettagli specifici allo scopo di fornire una comprensione approfondita di esempi di forme di attuazione secondo questa descrizione. Le forme di attuazione possono essere ottenute senza uno o più degli specifici dettagli, o con altri procedimenti, componenti, materiali, ecc. In altri casi, strutture, materiali o operazioni note non sono illustrate o descritte in dettaglio in modo che vari aspetti delle forme di attuazione non saranno offuscati.

Il riferimento a "una forma di attuazione" o "una sola forma di attuazione" nel quadro della presente descrizione

è inteso a indicare che una particolare configurazione, struttura, o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Quindi, frasi come "in una forma di attuazione", "in una sola forma di attuazione" che possono essere presenti in uno o più punti della presente descrizione non si riferiscono necessariamente a una stessa e unica forma di attuazione. Inoltre, particolari configurazioni, strutture, o caratteristiche possono essere combinate in qualsiasi modo adeguato in una o più forme di attuazione.

Le intestazioni/riferimenti qui fornite sono solo per comodità e non definiscono l'estensione di protezione o la portata delle forme di attuazione.

In tutte le figure qui allegate, se non diversamente indicato dal contesto, parti o elementi simili sono indicati con riferimenti/numeri simili e una descrizione corrispondente non sarà ripetuta per brevità.

A titolo di introduzione alla descrizione dettagliata di forme di attuazione esemplificative, inizialmente si può fare riferimento alla figura 2, che è uno schema circuitale esemplificativo di un convertitore digitale-analogico a pilotaggio di corrente (IDAC) 20 a 7 bit basato sull'architettura a specchio di corrente W-2W nota, per esempio, dal documento Gupta et al. precedentemente citato.

Uno specchio di corrente W-2W può essere utilizzato per implementare un DAC a pilotaggio di corrente a pesatura binaria ("binary-weighted") da utilizzare, per esempio, come circuito di pilotaggio di scrittura per la programmazione di una memoria a cambiamento di fase. Esso si basa sul riconoscimento che se due transistori a effetto di campo metallo-ossido-semiconduttore (MOSFET) con lo

stesso rapporto larghezza-lunghezza (in breve, W/L) sono connessi in parallelo, si comportano come un transistore equivalente di dimensioni 2W/L, mentre se connessi in serie si comportano come un transistore equivalente di dimensioni W/2L.

Un circuito IDAC W-2W 20 comprende un transistore master connesso a diodo N (per esempio, un transistore MOS a canale n) che ha un terminale di drain configurato per ricevere una corrente  $I_{REF}/2$  e un terminale di source accoppiato a un nodo di tensione di riferimento GND (o massa locale). Il transistore N è configurato per fare passare una corrente  $I_{REF}/2$ , la corrente  $I_{REF}$  essendo possibilmente uguale a 64  $\mu$ A. Il circuito IDAC W-2W 20 comprende un insieme di transistori slave  $T_0$ ,  $T_1$ ,  $M_0$ , ...,  $M_6$  (per esempio, transistori MOS a canale n) che hanno i rispettivi terminali di gate connessi al terminale di gate del transistore master N, in modo che la tensione di gate del transistore master N sia fornita ai terminali di gate di ciascuno dei transistori slave  $T_0$ ,  $T_1$ ,  $M_0$ , ...,  $M_6$ . Il transistore master N e i transistori slave  $T_0$ ,  $T_1$ ,  $M_0$ , ...,  $M_6$  hanno tutti la stessa dimensione di canale (per esempio, lo stesso rapporto larghezza-lunghezza W/L, possibilmente con la stessa larghezza W e la stessa lunghezza L). Il terminale di source di un primo transistore slave  $M_6$  è connesso direttamente al nodo di tensione di riferimento GND, in modo che il transistore  $M_6$  faccia passare una corrente  $I_6$  che è la stessa della corrente  $I_{REF}/2$  passata dal transistore master N ( $I_6 = I_{REF}/2$ ). Il terminale di source di un secondo transistore slave  $M_5$  è connesso al terminale di source del primo transistore slave  $M_6$  (per esempio, al nodo di tensione di riferimento GND) tramite un primo transistore di controllo di corrente  $Q_6$ . Il terminale

di source di un terzo transistore slave  $M_4$  è connesso al terminale di source del secondo transistore slave  $M_5$  tramite un secondo transistore di controllo di corrente  $Q_5$  e così via fino al terminale di source di un penultimo (per esempio, ottavo) transistore slave  $T_1$  che è connesso al terminale di source di un terzultimo (per esempio, settimo) transistore slave  $M_0$  tramite un ultimo (per esempio, settimo) transistore di controllo di corrente  $Q_0$ . I transistori di controllo di corrente da  $Q_6$  a  $Q_0$  hanno tutti una stessa dimensione di canale, che è largo due volte il canale dei transistori  $N$ ,  $M_6$ , ...,  $M_0$ ,  $T_1$ ,  $T_0$  (per esempio, i transistori di controllo di corrente possono presentare lo stesso rapporto larghezza-lunghezza  $2*W/L$ , possibilmente con la stessa larghezza  $2*W$  e la stessa lunghezza  $L$ ). I transistori di controllo di corrente da  $Q_6$  a  $Q_0$  hanno tutti i loro terminali di gate connessi al terminale di gate del transistore master  $N$  per ricevere la stessa tensione di gate. Il terminale di source di un ultimo (per esempio, nono) transistore slave  $T_0$  può essere connesso direttamente al terminale di source del penultimo transistore slave  $T_1$ .

Nella disposizione esemplificata nella figura 2, la corrente che passa attraverso ciascuno dei transistori  $M_5$ , ...,  $M_0$ ,  $T_1$ ,  $T_0$  è forzata a passare attraverso il transistore  $Q_6$ . Il transistore  $Q_6$  cerca di fare passare una corrente  $I_{REF}/2$ , che è fornita tramite i transistori  $M_5$  e  $Q_5$ . Le tensioni di gate dei transistori  $M_5$  e  $Q_5$  sono le stesse, quindi la corrente è divisa equamente tra i due percorsi in cui si trovano questi transistori. Di conseguenza, il transistore  $M_5$  fa passare una corrente  $I_5 = I_{REF}/4$ . In modo analogo, il transistore  $M_4$  fa passare una corrente  $I_4 = I_{REF}/8$ , il transistore  $M_3$  fa passare una corrente  $I_3 = I_{REF}/16$ , il transistore  $M_2$  fa passare una

corrente  $I_2 = I_{REF}/32$ , il transistore  $M_1$  fa passare una corrente  $I_1 = I_{REF}/64$ , il transistore  $M_0$  fa passare una corrente  $I_0 = I_{REF}/128$ , e i transistori  $T_1$  e  $T_0$  fanno passare ciascuno una corrente  $I_T = I_{REF}/256$ .

Come esemplificati nella figura 2, i terminali di drain dei primi sette transistori slave dello specchio di corrente (da  $M_6$  a  $M_0$ ) possono essere accoppiati selettivamente a un primo nodo 22 o a un secondo nodo 24, tramite rispettivi interruttori (per esempio, transistori MOS). Per esempio, il terminale di drain del transistore  $M_x$  (con  $X$  compreso tra 0 e 6) può essere accoppiato selettivamente al nodo 22 tramite un rispettivo interruttore attivabile da un rispettivo segnale di controllo  $C_x$  (per esempio, l'interruttore essendo conduttivo in risposta al fatto che il rispettivo segnale di controllo  $C_x$  è asserito), e può essere accoppiato selettivamente al nodo 24 tramite un ulteriore rispettivo interruttore attivabile dal negato del rispettivo segnale di controllo  $C_x$  (per esempio, l'ulteriore interruttore essendo conduttivo in risposta al fatto che il rispettivo segnale di controllo  $C_x$  è de-asserito, ossia, in risposta al fatto che il negato  $\overline{C_x}$  del segnale di controllo è asserito).

Come esemplificato nella figura 2, i terminali di drain dei transistori  $T_0$  e  $T_1$  possono essere sempre accoppiati al nodo 24 tramite rispettivi interruttori sempre accesi (per esempio, transistori MOS a canale n che hanno i loro terminali di gate accoppiati a una tensione di alimentazione  $V_{CC}$ ). Interruttori sempre spenti (per esempio, transistori MOS a canale n aventi i loro terminali di gate accoppiati al nodo di tensione di riferimento GND) possono anche essere forniti tra i terminali di drain dei

transistori  $T_0$  e  $T_1$  e il nodo 22, per esempio, per migliorare il matching del circuito.

I segnali di controllo  $C_0, \dots, C_6$  rappresentano i segnali di ingresso digitali del circuito IDAC W-2W (per esempio, ogni segnale di controllo fornendo un bit di un segnale digitale a 7 bit  $C$ ,  $C_0$  essendo il bit meno significativo (LSB) e  $C_6$  essendo il bit più significativo (MSB)). Il segnale di uscita analogico (per esempio, corrente di uscita) del circuito IDAC W-2W è fornito da una corrente a terminazione singola (single-ended) che scorre attraverso il nodo 22. Per esempio, la corrente di uscita può essere emessa dal circuito IDAC 20 tramite uno specchio di corrente PMOS accoppiato al nodo 22, come esemplificato dal transistore MOS a canale p 26 connesso a diodo accoppiato tra il nodo 22 e la tensione di alimentazione  $V_{cc}$ . Il percorso di corrente attraverso il nodo 24 (e attraverso il transistore MOS a canale p 28 connesso a diodo accoppiato tra il nodo 24 e la tensione di alimentazione  $V_{cc}$ ) fornisce un percorso di corrente in corrente continua per i transistori da  $M_5$  a  $M_0$  e permette che la corrente che scorre attraverso la struttura IDAC sia costante, indipendentemente dal valore dei segnali digitali di ingresso  $C_0, \dots, C_6$ . Ciò permette anche che i terminali di drain dei transistori da  $M_5$  a  $M_0$  siano polarizzati correttamente quando il segnale digitale di ingresso commuta per modificare il valore di corrente IDAC, migliorando la precisione e il tempo di assestamento della corrente di uscita IDAC.

La presenza dei transistori  $T_0$  e  $T_1$  produce sostanzialmente un offset nel segnale di corrente di uscita, che può vantaggiosamente evitare il funzionamento a corrente di uscita nulla quando il segnale digitale di

ingresso  $C$  (cioè l'insieme dei segnali di controllo  $C_0, \dots, C_6$ ) è uguale a zero.

In un circuito IDAC W-2W a 7 bit esemplificativo secondo l'architettura qui considerata, la corrente  $I_{0010000}$  (cioè, la corrente di uscita corrispondente al segnale di ingresso digitale  $C = 0010000$ ) dovrebbe essere uguale a  $I_{REF}/8$  e quindi dovrebbe essere maggiore di  $I_{0001111} = I_{REF}/16 + I_{REF}/32 + I_{REF}/64 + I_{REF}/128$  di un fattore  $I_{REF}/128$ . Ciò avverrebbe se la tensione di source di tutti i transistori slave  $M_6, \dots, M_0, T_1, T_0$  fosse la stessa, dando luogo così alla stessa tensione di bulk per tutti i transistori slave. Tuttavia, a causa della presenza dei transistori  $Q_6, \dots, Q_0$  e a causa della corrente che vi scorre, la tensione di source  $V_s$  dei transistori slave  $M_6, \dots, M_0, T_1, T_0$  potrebbe non essere la stessa. In particolare,  $V_{s,T_0} = V_{s,T_1} > V_{s,M_0} > V_{s,M_1} > V_{s,M_2} > V_{s,M_3} > V_{s,M_4} > V_{s,M_5} > V_{s,M_6}$ . Pertanto, l'entità della corrente che scorre attraverso i transistori  $M_5, \dots, M_0, T_1, T_0$  può essere influenzata dall'effetto body, risultante da tensioni bulk-source dei transistori  $M_5, \dots, M_0, T_1, T_0$  diverse rispetto alla tensione bulk-source dei transistori  $M_6$  e  $N$ . In particolare, l'effetto body può alterare la tensione di soglia dei transistori  $M_5, \dots, M_0, T_1, T_0$ , e quindi le corrispondenti correnti drain-source.

Per esempio, la figura 3 è un diagramma temporale esemplificativo di un possibile comportamento (per esempio, forma) della corrente di programmazione  $I_{CELL}$  di una cella di memoria a cambiamento di fase durante l'impulso SET, prodotto da un circuito IDAC W-2W come esemplificato nella figura 2. Durante la fase di caduta di corrente (periodo  $t_{1F}$ ), potrebbero esserci gradini imprevisti (per esempio, una porzione crescente quando si passa da  $C = 0010000$  a

$C = 0001111$ ) a causa del funzionamento del circuito IDAC W-2W discusso in precedenza. Ciò può influire sulla forma della corrente di programmazione  $I_{CELL}$  e quindi sul gradiente di temperatura applicato all'elemento di memorizzazione della memoria.

Pertanto, in una o più forme di attuazione come esemplificate nella figura 4, i terminali di bulk (o di corpo) dei transistori slave  $M_5, \dots, M_0, T_1, T_0$  il cui terminale di source non è allo stesso livello di tensione del nodo di tensione di riferimento GND (per esempio, non è direttamente connesso al nodo di tensione di riferimento GND) possono essere controllati da rispettivi segnali di compensazione  $V_5, \dots, V_0, V_{00}$  che facilitano la mitigazione (per esempio, la compensazione) dell'effetto body. I transistori  $T_1$  e  $T_0$  possono ricevere lo stesso segnale di compensazione  $V_{00}$  ai loro terminali di bulk, poiché i loro terminali di source sono direttamente accoppiati l'uno all'altro e ricevono la stessa tensione (cioè, possono essere influenzati dall'effetto body nella stessa misura).

In una o più forme di attuazione, i segnali di compensazione  $V_5, \dots, V_0, V_{00}$  possono essere diversi l'uno dall'altro. In alcune forme di attuazione, i transistori slave  $M_5, \dots, M_0, T_1, T_0$  possono essere divisi in sottoinsiemi e ogni sottoinsieme può ricevere lo stesso segnale di compensazione. In alcune forme di attuazione, lo stesso segnale di compensazione può essere fornito a tutti i transistori slave  $M_5, \dots, M_0, T_1, T_0$ .

In una o più forme di attuazione, i transistori slave  $M_5, \dots, M_0, T_1, T_0$  possono quindi essere progettati in modo da fornire un terminale di bulk accessibile e selettivamente controllabile. Per esempio, in una o più forme di attuazione i transistori slave  $M_5, \dots, M_0, T_1, T_0$

possono comprendere o consistere in transistori NMOS a triplo pozzo. In un transistore NMOS a triplo pozzo, il pozzo P del transistore è incorporato all'interno di un pozzo profondo N per creare un corpo isolato dal substrato P. Questo isola il corpo dal substrato e consente di polarizzare separatamente il corpo del transistore e il pozzo profondo N.

In una o più forme di attuazione, l'entità dell'effetto body che agisce sui transistori slave  $M_5, \dots, M_0, T_1, T_0$  può dipendere dalla temperatura. In particolare, ad alta temperatura (per esempio,  $140^\circ\text{C}$ ) l'effetto body può essere quasi interamente compensato dalla temperatura stessa, in modo che la corrente di uscita prodotta dal circuito IDAC W-2W 20 abbia la forma prevista. A bassa temperatura (per esempio,  $-40^\circ\text{C}$ ), l'effetto body potrebbe non essere compensato e la corrente di uscita potrebbe non avere la forma prevista, come esemplificato nella figura 3 in cui è prodotto un gradino o un ginocchio nella corrente di uscita quando si passa da  $I_{0010000}$  a  $I_{0001111}$ . Pertanto, in una o più forme di attuazione il segnale/i segnali di compensazione  $V_5, \dots, V_0, V_{00}$  può/possono presentare un'ampiezza che dipende dalla temperatura, in modo da fornire una forte compensazione a basse temperature e una compensazione lieve alle alte temperature (per esempio, fino a una compensazione nulla).

La figura 5 è uno schema circuitale esemplificativo di una possibile implementazione di un circuito di compensazione 50 configurato per produrre uno o più segnali di compensazione  $V_5, \dots, V_0, V_{00}$  per un circuito IDAC W-2W 20 come esemplificato nella figura 4, dove i segnali di compensazione dipendono dalla temperatura.

Un circuito di compensazione 50 può comprendere una

configurazione di generatore di corrente proporzionale alla temperatura assoluta (PTAT, "Proportional-To-Absolute-Temperature") (IPTAT) configurato per produrre un segnale di tensione NBIAS che diminuisce (per esempio, linearmente) in funzione della temperatura, come esemplificato nei diagrammi tensione-temperatura della figura 6. In particolare, il circuito di compensazione 50 può comprendere un transistore MOS a canale p 502 disposto in serie con un transistore MOS a canale n 504 tra un nodo di tensione di alimentazione 506 che fornisce la tensione di alimentazione  $V_{cc}$  e il nodo di tensione di riferimento GND. Il transistore 504 può presentare un terminale di source accoppiato al nodo di tensione di riferimento GND, un terminale di drain accoppiato al terminale di drain del transistore 502, e un terminale di gate configurato per ricevere una tensione di riferimento di bandgap  $V_{BG}$ . Il transistore 502 può presentare un terminale di source accoppiato al nodo di tensione di alimentazione 506, un terminale di drain accoppiato al terminale di drain del transistore 504, e un terminale di gate accoppiato al suo terminale di drain (cioè, potrebbe essere in una configurazione di connessione a diodo). Il circuito di compensazione 50 può inoltre comprendere un transistore MOS a canale p 508 disposto in serie con un transistore MOS a canale n 510 tra il nodo di tensione di alimentazione 506 e il nodo di tensione di riferimento GND. Il transistore 508 può avere un terminale di source accoppiato al nodo di tensione di alimentazione 506, un terminale di drain accoppiato al terminale di drain del transistore 510, e un terminale di gate accoppiato al terminale di gate del transistore 502 (per esempio, in una configurazione a specchio di corrente con il transistore 502). Il

transistore 510 può avere un terminale di source accoppiato al nodo di tensione di riferimento GND, un terminale di drain accoppiato al terminale di drain del transistore 508, e un terminale di gate accoppiato al terminale di drain (cioè, può essere in una configurazione di connessione a diodo). Un segnale *NBIAS* che ha una dipendenza dalla temperatura come esemplificata nella figura 6 (per esempio, lineare) può quindi essere prodotto al terminale di gate del transistore 510.

Il circuito di compensazione 50 può inoltre comprendere un circuito buffer di tensione 512 che ha un ingresso non invertente configurato per ricevere il segnale *NBIAS* (per esempio, accoppiato al terminale di gate del transistore 510) e un ingresso invertente accoppiato al nodo di uscita 514 del buffer di tensione 512. Il buffer 512 può comprendere o consistere in un amplificatore operazionale. Un circuito partitore di tensione 516 (per esempio, un partitore di tensione resistivo o una scala resistiva) può essere accoppiato tra il nodo di uscita 514 del buffer di tensione 512 e il nodo di tensione di riferimento GND. Il buffer di tensione 512 disaccoppia quindi i terminali di gate e di drain del transistore 510 (nodo *NBIAS*) dal circuito partitore di tensione 516 e fornisce una corrente al circuito partitore di tensione 516.

Uno o più segnali di compensazione  $V_5, \dots, V_0, V_{00}$  possono quindi essere forniti in uno o più nodi intermedi del circuito partitore resistivo 516, da fornire ai terminali di bulk dei transistori slave  $M_5, \dots, M_0, T_1, T_0$  nel circuito IDAC W-2W 20 come esemplificato nella figura 4. In particolare, la tensione  $V_{00}$  destinata alla polarizzazione del bulk dei transistori  $T_1$  e  $T_0$  può essere

maggiore della tensione  $V_0$  destinata alla polarizzazione del bulk del transistore  $M_0$ , la tensione  $V_0$  può essere maggiore della tensione  $V_1$  destinata alla polarizzazione del bulk del transistore  $M_1$ , la tensione  $V_1$  può essere maggiore della tensione  $V_2$  destinata alla polarizzazione del bulk del transistore  $M_2$ , e così via fino alla tensione  $V_5$  destinata alla polarizzazione del bulk del transistore  $M_5$  che è quella più bassa.

Pertanto, in un circuito di compensazione 50 come esemplificato nella figura 5, un generatore IPTAT può essere utilizzato per generare un segnale  $NBIAS$  che ha un profilo dipendente dalla temperatura come esemplificato nella figura 6. A basse temperature (per esempio,  $-40^{\circ}\text{C}$ ) la corrente IPTAT che scorre attraverso i transistori 502 e 504 è maggiore della corrente che scorre ad alte temperature (per esempio,  $140^{\circ}\text{C}$ ). Di conseguenza, anche il segnale di tensione  $NBIAS$  è più alto a  $-40^{\circ}\text{C}$  e più basso a  $140^{\circ}\text{C}$  (per esempio, il segnale  $NBIAS$  può diminuire linearmente rispetto alla temperatura). Modificando la dimensione del canale (larghezza  $W$  e lunghezza  $L$ ) del transistore 510, la pendenza del segnale  $NBIAS$  (cioè il suo coefficiente di dipendenza dalla temperatura) può essere modificata. Il segnale  $NBIAS$  è replicato nel nodo di uscita 514 del circuito buffer di tensione 512, che alimenta il partitore di tensione 516 per produrre il segnale/i segnali di compensazione desiderato/desiderati  $V_5, \dots, V_0, V_{00}$ . Per esempio, nel caso in cui lo stesso segnale di compensazione sia applicato a tutti i transistori slave  $M_5, \dots, M_0, T_1, T_0$ , esso potrebbe essere prodotto in un punto intermedio tra i resistori  $R1$  e  $R2$  del circuito partitore 516.

In una o più forme di attuazione, l'applicazione di uno o più segnali di compensazione dipendenti dalla

temperatura  $V_5, \dots, V_0, V_{00}$  ai terminali di bulk (o di corpo) dei transistori slave  $M_5, \dots, M_0, T_1, T_0$  può quindi facilitare la compensazione dell'effetto body di questi transistori, consentendo così la produzione di impulsi di corrente aventi il comportamento (lineare) previsto per la programmazione delle celle di memoria di una memoria a cambiamento di fase sfruttando al contempo la bassa area di silicio dell'architettura del circuito IDAC W-2W.

Senza pregiudizio per i principi sottostanti, i dettagli e le forme di attuazione possono variare, anche in modo significativo, rispetto a quanto è stato descritto solo a titolo di esempio, senza allontanarsi dall'estensione di protezione.

L'estensione di protezione è determinata dalle rivendicazioni allegate.

## RIVENDICAZIONI

### 1. Circuito (20), comprendente:

un transistore MOS connesso a diodo (N) avente un terminale di drain connesso a un nodo di ingresso e un terminale di source connesso a un nodo di tensione di riferimento (GND), il transistore MOS connesso a diodo (N) essendo configurato per fare passare una corrente di riferimento ( $I_{REF}/2$ ) da detto nodo di ingresso a detto nodo di tensione di riferimento (GND);

una pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0, T_1, T_0$ ) aventi rispettivi terminali di gate connessi a un terminale di gate di detto transistore MOS connesso a diodo (N) e rispettivi terminali di drain accoppiabili alternativamente a un primo nodo di corrente (22) o a un secondo nodo di corrente (24) in funzione di una pluralità di rispettivi segnali di controllo ordinati ( $C_6, \dots, C_0, \overline{C_6}, \dots, \overline{C_0}$ ), in cui un primo transistore MOS di mirroring ( $M_6$ ) in detta pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) ha un terminale di source direttamente connesso a detto nodo di tensione di riferimento (GND);

una pluralità di transistori MOS di controllo di corrente ( $Q_6, \dots, Q_0$ ) aventi rispettivi terminali di gate connessi a detto terminale di gate di detto transistore MOS connesso a diodo (N), in cui ogni transistore MOS di controllo di corrente ( $Q_6, \dots, Q_0$ ) è disposto tra i terminali di source di due transistori MOS di mirroring consecutivi in detta pluralità di transistori MOS di mirroring ( $M_6, \dots, M_0, T_1, T_0$ ),

in cui detto transistore MOS connesso a diodo (N) e detti transistori MOS di mirroring ( $M_6, \dots, M_0, T_1, T_0$ )

hanno tutti le stesse dimensioni di canale, e in cui detti transistori MOS di controllo di corrente ( $Q_6, \dots, Q_0$ ) hanno tutti le stesse dimensioni di canale, il canale di detti transistori MOS di controllo di corrente ( $Q_6, \dots, Q_0$ ) avendo la stessa lunghezza e il doppio della larghezza del canale di detto transistore MOS connesso a diodo (N);

in cui i transistori MOS di mirroring ( $M_5, \dots, M_0, T_1, T_0$ ) il cui terminale di source non è direttamente connesso a detto nodo di tensione di riferimento (GND) hanno rispettivi terminali di bulk configurati per ricevere uno o più segnali di compensazione ( $V_5, \dots, V_0, V_{00}$ ), detti uno o più segnali di compensazione ( $V_5, \dots, V_0, V_{00}$ ) avendo rispettivi valori che diminuiscono con l'aumentare della temperatura.

**2.** Circuito (20) secondo la rivendicazione 1, in cui detti uno o più segnali di compensazione ( $V_5, \dots, V_0, V_{00}$ ) dipendono linearmente dalla temperatura.

**3.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, comprendente un circuito di compensazione (50) configurato per produrre detti uno o più segnali di compensazione ( $V_5, \dots, V_0, V_{00}$ ), il circuito di compensazione (50) comprendendo:

una configurazione di generatore di corrente proporzionale alla temperatura assoluta (502, 504, 506, 508) configurata per produrre un segnale di tensione di compensazione (NBIAS) che diminuisce linearmente in funzione dell'aumento della temperatura;

un circuito partitore di tensione (516); e

uno stadio buffer (512) configurato per alimentare detto segnale di tensione di compensazione (NBIAS) a detto

circuito partitore di tensione (516),

in cui detti uno o più segnali di compensazione ( $V_5$ , ...,  $V_o$ ,  $V_{oo}$ ) sono prodotti in uno o più nodi intermedi di detto circuito partitore di tensione (516).

4. Circuito (20) secondo la rivendicazione 3, in cui detta configurazione di generatore di corrente proporzionale alla temperatura assoluta (502, 504, 506, 508) comprende:

un primo transistore MOS a canale p (502) e un primo transistore MOS a canale n (504) disposti in serie tra un nodo di tensione di alimentazione (506,  $V_{cc}$ ) e detto nodo di tensione di riferimento (GND); e

un secondo transistore MOS a canale p (508) e un secondo transistore MOS a canale n (510) disposti in serie tra detto nodo di tensione di alimentazione (506,  $V_{cc}$ ) e detto nodo di tensione di riferimento (GND);

in cui detto primo transistore MOS a canale n (504) ha un terminale di source accoppiato a detto nodo di tensione di riferimento (GND), un terminale di drain accoppiato a un terminale di drain di detto primo transistore MOS a canale p (502), e un terminale di gate configurato per ricevere una tensione di riferimento di bandgap ( $V_{BG}$ );

in cui detto primo transistore MOS a canale p (502) ha un terminale di source accoppiato a detto nodo di tensione di alimentazione (506) e un terminale di gate accoppiato al proprio terminale di drain;

in cui detto secondo transistore MOS a canale p (508) ha un terminale di source accoppiato a detto nodo di tensione di alimentazione (506,  $V_{cc}$ ), un terminale di drain accoppiato a un terminale di drain di detto secondo transistore MOS a canale n (510), e un terminale di gate

accoppiato al terminale di gate di detto primo transistore MOS a canale p (502);

e in cui detto secondo transistore MOS a canale n (510) ha un terminale di source accoppiato a detto nodo di tensione di riferimento (GND) e un terminale di gate accoppiato al proprio terminale di drain;

in cui detto segnale di tensione di compensazione (NBIAS) è prodotto in detto terminale di gate di detto secondo transistore MOS a canale n (510).

**5.** Circuito (20) secondo la rivendicazione 3 o la rivendicazione 4, in cui detto stadio buffer (512) comprende un circuito amplificatore (512) che ha un terminale di uscita accoppiato a detto circuito partitore di tensione (516), un terminale di ingresso non invertente configurato per ricevere detto segnale di tensione di compensazione (NBIAS), e un terminale di ingresso invertente accoppiato al proprio terminale di uscita.

**6.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, in cui detti transistori MOS di mirroring ( $M_5, \dots, M_0, T_1, T_0$ ) il cui terminale di source non è direttamente connesso a detto nodo di tensione di riferimento (GND) comprendono transistori MOS a triplo pozzo a canale n.

**7.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, in cui un terminale di source di un ultimo transistore MOS di mirroring ( $T_0$ ) in detta pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) è direttamente connesso a un terminale di source di un penultimo transistore MOS di mirroring ( $T_1$ ) in detta

pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) .

**8.** Circuito (20) secondo la rivendicazione 7, in cui detto ultimo transistore MOS di mirroring ( $T_0$ ) e detto penultimo transistore MOS di mirroring ( $T_1$ ) hanno i rispettivi terminali di bulk configurati per ricevere uno stesso segnale di compensazione ( $V_{00}$ ) .

**9.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, in cui un terminale di drain di un ultimo transistore MOS di mirroring ( $T_0$ ) in detta pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) e un terminale di drain di un penultimo transistore MOS di mirroring ( $T_1$ ) in detta pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) sono costantemente accoppiati a detto secondo nodo di corrente (24) .

**10.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, in cui i terminali di drain di detta pluralità di transistori MOS di mirroring ordinati ( $M_6, \dots, M_0$ ) sono accoppiabili alternativamente a detto primo nodo di corrente (22) o a detto secondo nodo di corrente (24) tramite rispettivi interruttori attivabili in funzione di detti rispettivi segnali di controllo ordinati ( $C_6, \dots, C_0, \overline{C_6}, \dots, \overline{C_0}$ ) .

**11.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, in cui detto transistore MOS connesso a diodo (N), detta pluralità di transistori MOS di mirroring ( $M_6, \dots, M_0$ ) e detta pluralità di transistori

MOS di controllo di corrente ( $Q_6, \dots, Q_0$ ) comprendono transistori a canale n.

**12.** Circuito (20) secondo una qualsiasi delle rivendicazioni precedenti, comprendente un primo transistore MOS di uscita connesso a diodo (26) avente un terminale di drain connesso a detto primo nodo di corrente (22) e un terminale di source connesso a un nodo di tensione di alimentazione ( $V_{CC}$ ), e un secondo transistore MOS di uscita connesso a diodo (28) avente un terminale di drain connesso a detto secondo nodo di corrente (24) e un terminale di source connesso a detto nodo di tensione di alimentazione ( $V_{CC}$ ).

FIG. 1

FIG. 3

FIG. 2

FIG. 4

FIG. 5

FIG. 6