## US005732165A

## United States Patent [19]

### Suzuki et al.

#### [54] WHITE LEVEL INFORMATION CORRECTION APPARATUS FOR IMAGE READING APPARATUS AND IMAGE READING APPARATUS WITH WHITE LEVEL INFORMATION CORRECTION APPARATUS

- [75] Inventors: Akio Suzuki; Yoshio Tabata; Yukako Murai; Keiichi Saito; Tamio Amagai. all of Kawasaki, Japan

- [73] Assignee: Fujitsu Limited, Kawasaki, Japan

- [21] Appl. No.: 405,031

- [22] Filed: Mar. 16, 1995

#### [30] Foreign Application Priority Data

- Apr. 7, 1994 [JP] Japan ..... 6-069310

- [51] Int. Cl.<sup>6</sup> ...... G06K 9/54

- - 395/889

#### [56] **References Cited**

#### **U.S. PATENT DOCUMENTS**

| 5,027,117 | 6/1991 | Yoshida et al. | 341/132 |

|-----------|--------|----------------|---------|

| 5,198,909 | 3/1993 | Ogiwara et al  | 358/412 |

| 5,285,290 | 2/1994 | Sakai et al.   | 358/404 |

| 5,383,031 | 1/1995 | Kida et al.    | 358/444 |

| 5,513,018 | 4/1996 | Nishimura      | 358/474 |

| 5,515,180 | 5/1996 | Maeda et al.   | 358/458 |

| 5,596,427 | 1/1997 | Honma et al    | 358/515 |

#### FOREIGN PATENT DOCUMENTS

0 275 143 A 7/1988 European Pat. Off. .

# [11] Patent Number: 5,732,165

## [45] Date of Patent: Mar. 24, 1998

| 27 48 325 A1 | 12/1978 | Germany |

|--------------|---------|---------|

| 56-157575    | 12/1981 | Japan . |

| 56-157576    | 12/1981 | Japan . |

| 61-30866     | 2/1986  | Japan . |

| 61-30867     | 2/1986  | Japan . |

| 62-230265    | 10/1987 | Japan . |

Primary Examiner-Joseph Mancuso

Assistant Examiner-Jayanti K. Patel

Attorney, Agent, or Firm-Nikaido, Marmelstein, Murray & Oram LLP

#### [57] ABSTRACT

The invention provides a white level information correction apparatus for an image reading apparatus suitably used as an image scanner, which is improved in that analog to digital conversion can be performed effectively for originals of different ground colors with a high degree of accuracy. In the image reading apparatus, image information of a paper sheet being transported along a paper transport path is optically read at a fixed location of the paper transport path using an optical image reading unit and analog data obtained by the optical image reading unit are converted into digital data using white level information of the image information as an index to a conversion reference. The white level information correction apparatus comprises a plurality of storage apparatus for storing a plurality of pieces of white level information to be used as indices to the conversion reference, a data magnification variation apparatus for multiplying white level information from a storage apparatus by a coefficient to vary the magnification of the data, and a data write control apparatus for storing white level information varied in magnification by the data magnification variation apparatus into a storage apparatus to update the stored data.

#### 14 Claims, 30 Drawing Sheets

F I G. 3

FIG.II(A)

FIG. 26

NOTE 1 : FOR ONE FACE READING, READ COMPLETE IS RETURNED WHEN V-GATE IS TURNED OFF

- NOTE 2 : FOR ONE FACE READING, CLUTCH IS ENGAGED SIMULTANEOUSLY WITH TURNING OFF OF V-GATE

- NOTE 3: AFTER PS1 PULSES AFTER PAPER LEADING END PASSES SF1, DECELERATION IS STARTED, & DECELERATION IS CONTINUED TO V12

- NOTE 4: WHEN NO READ COMMAND IS RECEIVED WITHIN PS2(>PS1) PULSES AFTER PAPER LEADING END PASSES SF1, TRANSPORTATION IS STOPPED TO WAIT READ COMMAND. WHEN READ COMMAND IS RECEIVED WITHIN THAT PERIOD, MOTOR IS ACCELERATED OR DECELERATED IN RESPONSE TO READING SPEED.

F IG. 30

F I G. 3

#### WHITE LEVEL INFORMATION CORRECTION APPARATUS FOR IMAGE **READING APPARATUS AND IMAGE READING APPARATUS WITH WHITE** LEVEL INFORMATION CORRECTION APPARATUS

#### BACKGROUND OF THE INVENTION

#### 1) Field of the Invention

This invention relates to a white level information correction apparatus for an image reading apparatus which is suitably applied to an image scanner and an image reading apparatus with such white level information correction apparatus.

2) Description of the Related Art

In recent years, image reading apparatus or image inputting apparatus such as image scanners have been and are being developed in order to input image information to a computer (host computer) or a like apparatus.

In an image reading apparatus of the type mentioned, an analog image signal is converted into a digital signal to be sent out to a host computer. In order to convert an analog image signal into a digital signal, an analog to digital (A/D) converter is used in which an analog signal of a white level <sup>25</sup> is used as a reference value for an upper limit and another analog signal of a black level is used as a reference value for a lower limit.

Generally, the level of black is fixed corresponding to a 30 value obtained when the output of, for example, a charge coupled device (CCD) is "0". Accordingly, one of those of analog signals obtained from charge coupled devices by scanning an image which belong to a range (bits) within which photosensitive portions of the charge coupled devices are masked is held by a capacitor or a like element, that is, <sup>35</sup> sampled and held, to use it as the level of black. In contrast, the level of white must be corrected since it is influenced significantly by the quantity of light of a lamp (the quantity of light relies upon the position of the lamp, the ambient temperature, the elapsed time after starting of emission of light and so forth) or the level of the back ground of the original.

In order to correct the white level, concentration designation or the like is performed to vary the slice levels between the white level and the black level.

However, the conventional technique has a subject to be solved in that it is not sufficiently effective when the: color of the ground of the original is dark such as a blue print original and consequently analog to digital (A/D) conversion 50 cation variation means may be variable. cannot be performed with a high degree of accuracy.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide a white level information correction apparatus for an image reading 55 apparatus and an image reading apparatus with a white level information correction apparatus wherein analog to digital conversion can be performed effectively for originals of different ground colors.

an aspect of the present invention, there is provided a white level information correction apparatus for an image reading apparatus wherein image information of a paper sheet being transported along a paper transport path is optically read at a fixed location of the paper transport path using an optical 65 image reading unit and analog data obtained by the optical image reading unit are converted into digital data using

white level information of the image information as an index to a conversion reference, comprising a plurality of storage means for storing a plurality of pieces of white level information to be used as indices to the conversion 5 reference, data magnification variation means for multiplying white level information from one of the storage means by a coefficient to vary the magnification of the data, and data write control means for storing white level information varied in magnification by the data magnification variation means into one of the storage means to update the stored 10 data.

With the White level information correction apparatus. since it comprises the plurality of storage means for storing a plurality of pieces of white level information to be used as

<sup>15</sup> indices to the conversion reference, the data magnification variation means for multiplying white level information from one of the storage means by a coefficient to vary the magnification of the data, and the data write control means for storing white level information varied in magnification 20 by the data magnification variation means into one of the storage means to update the stored data, even in such a case that, for example, paper sheets whose ground color is white have been read till now and blue print paper sheets of a different ground color are to be read subsequently, the white level information correction apparatus copes with this sufficiently and can perform analog to digital conversion of image data with a high degree of accuracy.

The storage means may be constituted from memory circuits independent of each other and capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference.

Where the storage means are constituted from memory circuits independent of each other and capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference, control of white level information is facilitated.

Alternatively, the plurality of storage means may be constructed from a single memory circuit having a plurality of storage areas capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference.

Where the storage means are constituted from a single memory circuit having a plurality of storage areas capable of 45 storing a plurality of pieces of white level information to be used as indices to the conversion reference, a plurality of independent memory circuits need not be prepared and easy handling is achieved.

The magnification rate of variation of the data magnifi-

Where the magnification rate of variation of the data magnification variation means is variable, a high degree of freedom is provided for correction of a white level.

The data write control means may include selection means for storing white level information varied in magnification by the data magnification variation means into a selected one of the storage means to update the stored data.

Where the data write control means includes the selection In order to attain the object described above, according to 60 means for storing white level information varied in magnification by the data magnification variation means into a selected one of the storage means to update the stored data, the stored contents of any one of the plurality of storage means can be updated readily.

> The data write control means includes first selection means for selectively outputting white level information varied in magnitude by the data magnification variation

5

25

means or white level information from one of the storage means, a white level algorithm circuit for comparing white level information selected by the first selection means and data obtained from the optical image reading unit with each other and correcting the white level information in response to a result of the comparison, and second selection means for storing an output of the white level algorithm circuit into a selected one of the plurality of storage means to update the stored data.

Where the data write control means includes the first 10 selection means for selectively outputting white level information varied in magnitude by the data magnification variation means or white level information from one of the storage means, the white level algorithm circuit for comparing white level information selected by the first selection means and data obtained from the optical image reading unit with each other and correcting the white level information in response to a result of the comparison, and the second selection means for storing the output of the white level algorithm circuit into a selected one of the plurality of 20 storage means to update the stored data, the white level can be corrected between paper sheets having a same ground color.

The white level information correction apparatus may further comprise switching control means for determining based on data obtained from the optical image reading unit whether white level information should be varied in magnitude by the data magnification variation means and automatically controlling selective switching of the first selection means.

Where the white level information correction apparatus further comprises the switching control means for determining based on data obtained from the optical image reading unit whether white level information should be varied in magnitude by the data magnification variation means and 35 automatically controlling selective switching of the first selection means, even when a paper sheet to be read changes from the last paper sheet, variation of the white level can be automatically performed rapidly.

The white level algorithm circuit may include a digital 40 comparison circuit for comparing digital white level information selected by the first selection means and digital data obtained by the optical image reading unit with each other, and a white level information correction circuit for correcting the white level information in response to a result of 45 comparison by the digital comparison circuit.

Where the white level algorithm circuit includes the digital comparison circuit for comparing digital white level information selected by the first selection means and digital data obtained by the optical image reading unit with each 50 other and the white level information correction circuit for correcting the white level information in response to a result of comparison by the digital comparison circuit, analog circuits in the entire circuitry and patterns on a printed circuit board of the image inputting apparatus can be mini- 55 mized. Further, since the correction of the white level is based on digital processing, oscillations, which often occur with an analog comparator, do not occur in a high frequency band. Accordingly, the advantage that an increase in stability of operation and in efficiency and certainty in designing can 60 be achieved is achieved. Further, in this instance, since the digital circuit portion of the white level algorithm circuit can be constructed only from ordinary logical OR and AND gate circuits, it can be included readily into a large scale integrated circuit (LSI). 65

Alternatively, the white level algorithm circuit may include a control signal production circuit for comparing Δ

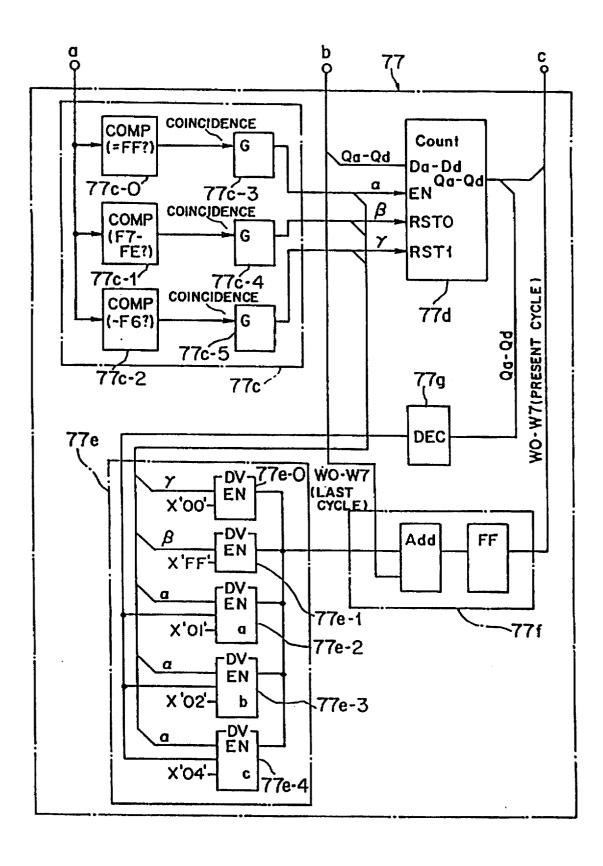

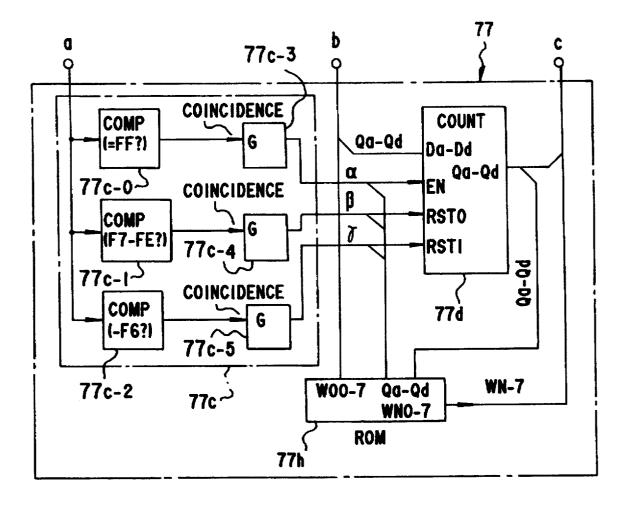

digital white level information selected by the first selection circuit and digital data obtained by the optical image reading unit with each other and outputting, in response to a result of the comparison, a control signal indicating that the digital data has a predetermined value, a counting circuit for counting the number of times by which a control signal is outputted successively in a direction of a line from the control signal production circuit, and a white level information correction circuit for correcting the white level information in response to a count value of the counting circuit.

Where the white level algorithm circuit includes the control signal production circuit for comparing digital white level information selected by the first selection circuit and digital data obtained by the optical image reading unit with 15 each other and outputting, in response to a result of the comparison, a control signal indicating that the digital data has a predetermined value, the counting circuit for counting the number of times by which a control signal is outputted successively in a direction of a line from the control signal production circuit, and the white level information correction circuit for correcting the white level information in response to a count value of the counting circuit, similarly as described above, analog circuits in the entire circuitry and patterns on a printed circuit board of the image inputting apparatus can be minimized. Further, since the correction of the white level is based on digital processing, oscillations, which often occur with an analog comparator, do not occur in a high frequency band. Accordingly, the advantage that an increase in stability of operation and in efficiency and certainty in designing can be achieved is achieved. Further, in this instance, since the digital circuit portion of the white level algorithm circuit can be constructed only from ordinary logical 015 and AND gate circuits, it can be included readily into a large scale integrated circuit (LSI).

According to another aspect of the present invention, there is provided an image reading apparatus, comprising a paper transport path along which a paper sheet from which an image is to be read is transported, an optical image reading unit for optically reading, at a predetermined location of the paper transport path, image information from a paper sheet being transported along the paper transport path, analog to digital conversion means for converting analog data obtained by the optical image reading unit into digital data using white level information of the image information as an index to a conversion reference, and a white level information correction apparatus for correcting white level information to be used as an index to the conversion reference of the analog to digital conversion means, the white level information correction apparatus including a plurality of storage means for storing a plurality of pieces of white level information to be used as indices to the conversion reference, data magnification variation means for multiplying white level information from one of the storage means by a coefficient to vary the magnification of the data, and data write control means for storing white level information varied in magnification by the data magnification variation means into one of the storage means to update the stored data.

Further objects, features and advantages of the present invention will become apparent from the following detailed description when read in conjunction with the accompanying drawings in which like parts or elements are denoted by like reference characters.

#### BRIEF DESCRIPTION OF THE DRAWINGS

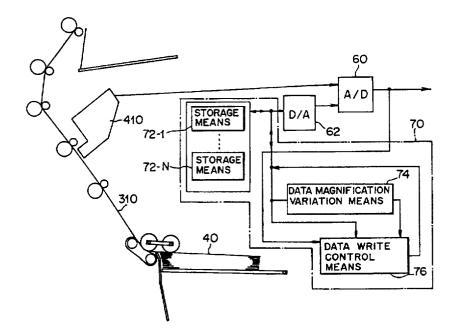

FIG. 1 is a block diagram illustrating an aspect of the present invention;

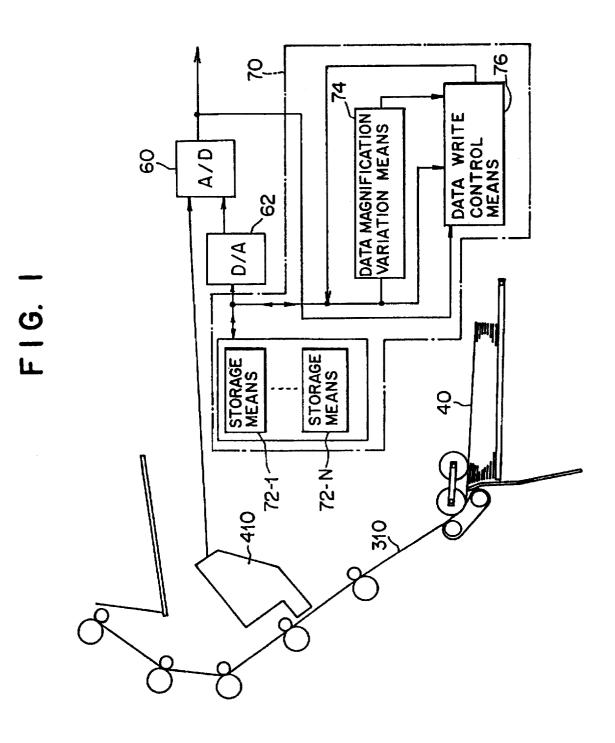

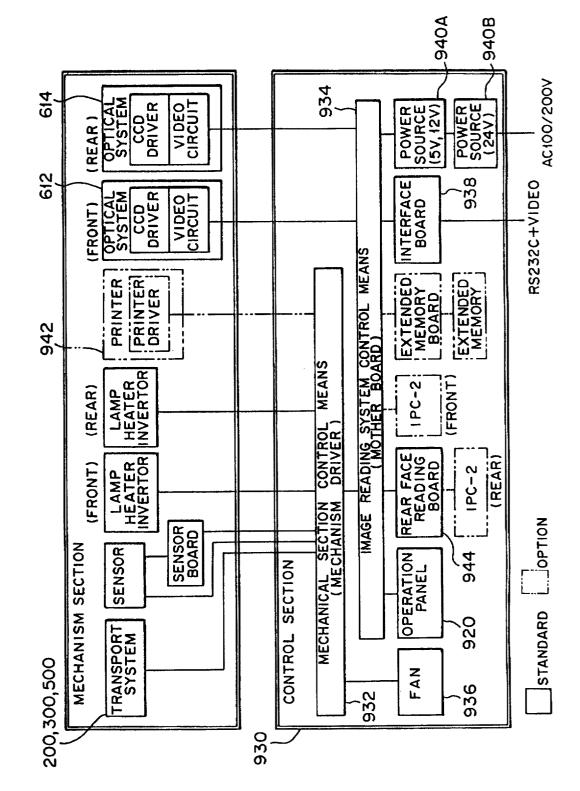

FIG. 2 is a block diagram showing an image data processing system of an image reading apparatus to which the present invention is applied;

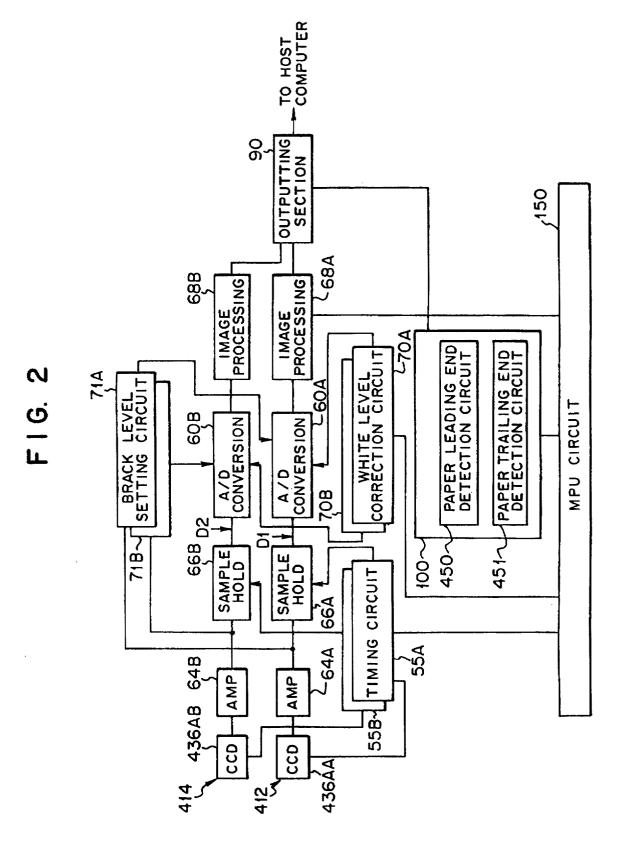

FIG. 3 is a block diagram schematically showing the construction of a control system of the image reading 5 apparatus to which the present invention is applied;

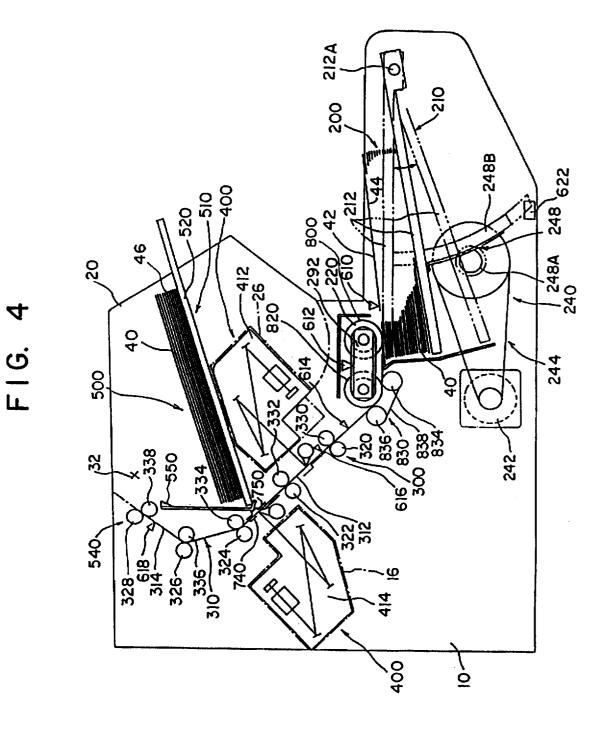

FIG. 4 is a schematic side elevational sectional view of the image reading apparatus to which the present invention is applied;

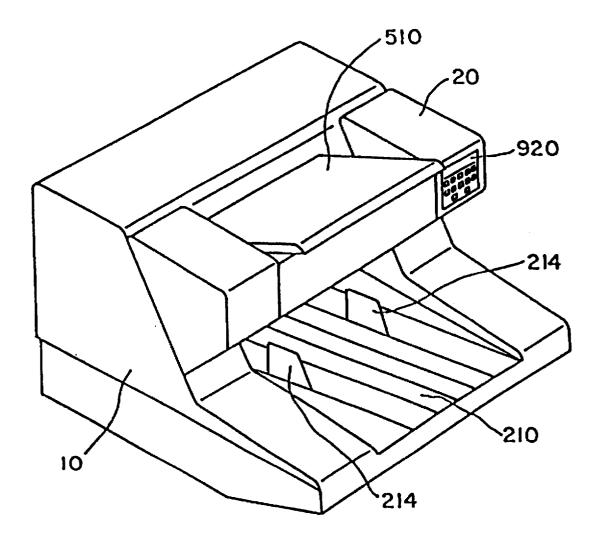

FIG. 5 is a perspective view showing an outer profile of  $^{10}$  the image reading apparatus of FIG. 4;

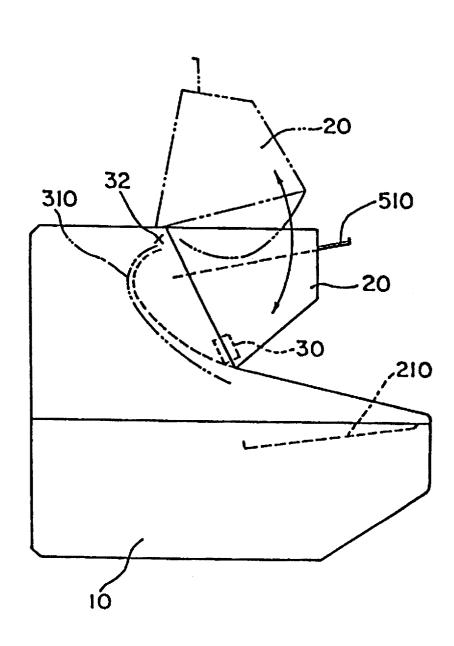

FIG. 6 is a schematic side elevational view showing an outer profile of the image reading apparatus of FIG. 4;

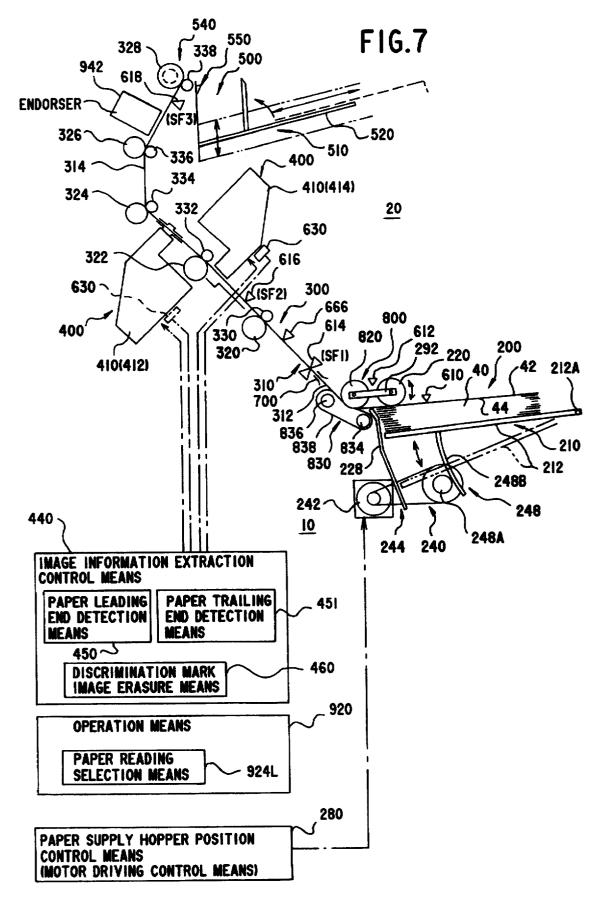

FIG. 7 is a diagrammatic view schematically showing, in side elevation, an arrangement of principal components of <sup>15</sup> the image reading apparatus of FIG. 4;

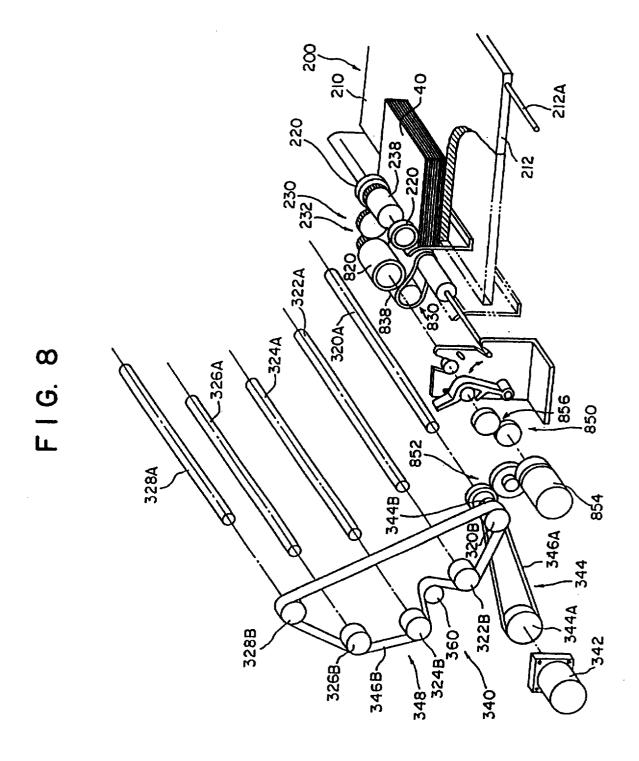

FIG. 8 is an exploded perspective view schematically showing a driving system of the image reading apparatus of FIG.

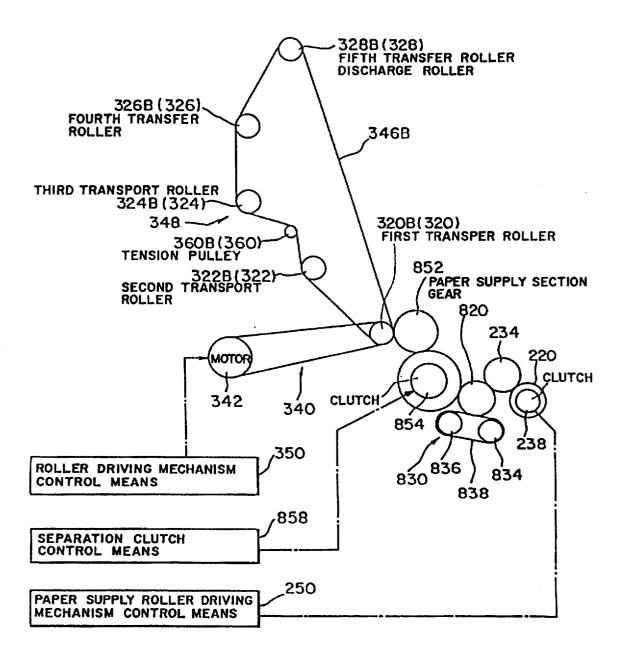

FIG. 9 is a diagrammatic view schematically showing, in side elevation, the driving system shown in FIG. 8;

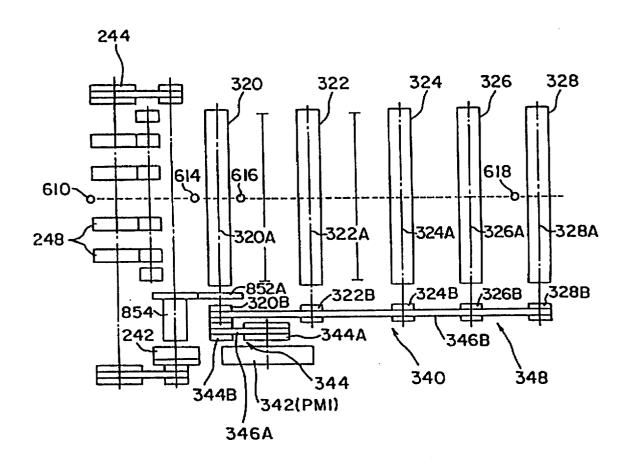

FIG. 10 is a diagrammatic view schematically showing. in plan, the driving system shown in FIG. 8;

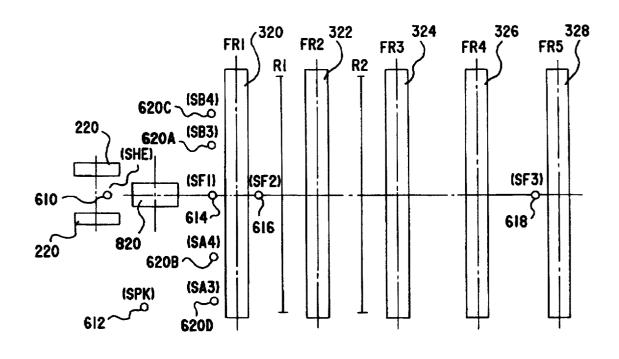

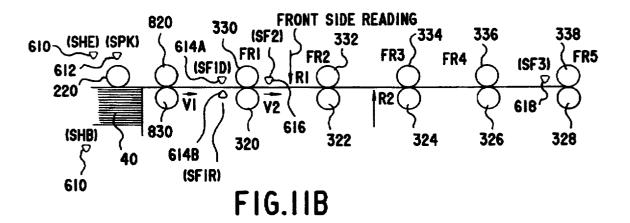

FIGS. 11(A) and 11(B) are a schematic plan view and a  $_{25}$  schematic side elevational view, respectively, showing a paper transport system of the image reading apparatus of FIG. 4;

FIG. 12 is a schematic side elevational view showing the construction of an image reading mechanism of the image 30 reading apparatus of FIG. 4;

FIG. 13 is a diagrammatic view schematically showing the construction of the optical image reading mechanism shown in FIG. 12;

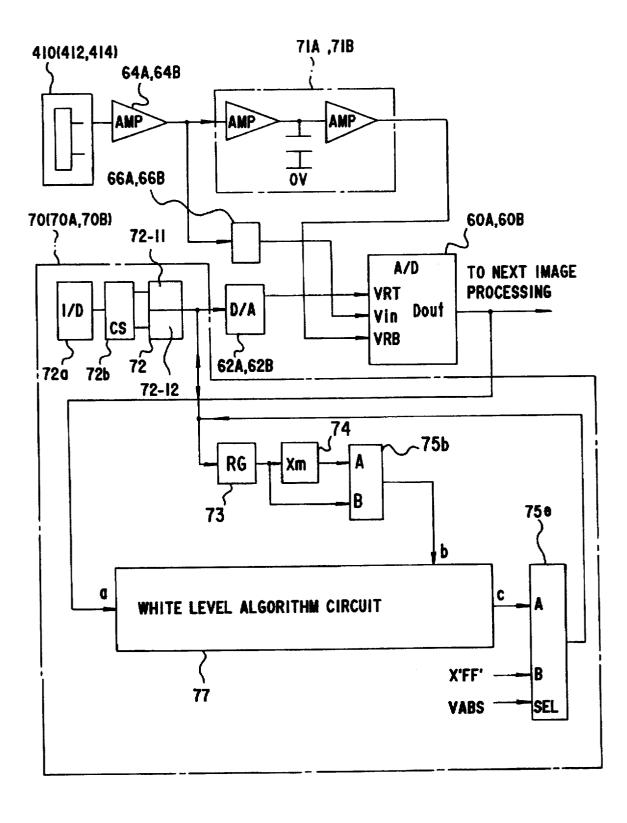

FIG. 14 is a block diagram showing the construction of a <sup>35</sup> white level information correction apparatus to which the present invention is applied together with several associated elements;

FIG. 15 is a block diagram showing a white level algorithm circuit of the white level information correction appa-<sup>40</sup> ratus shown in FIG. 14;

FIG. 16 is a block diagram showing another form of the white level algorithm circuit of the white level information correction apparatus shown in FIG. 14;

FIG. 17 is a block diagram showing a further form of the <sup>45</sup> white level algorithm circuit of the white level information correction apparatus shown in FIG. 14;

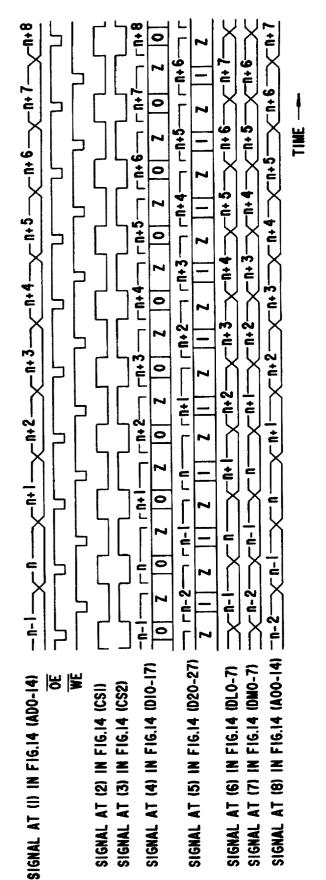

FIG. 18 is a time chart illustrating operation of the while level information correction apparatus shown in FIG. 14;

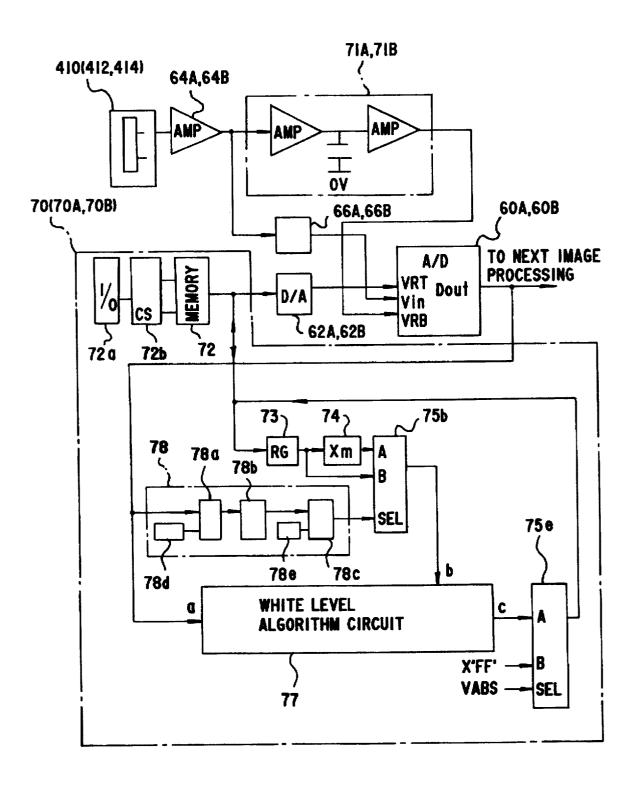

FIG. 19 is a block diagram showing the construction of another white level information correction apparatus to which the present invention is applied together with several associated elements;

FIG. 20 is a block diagram showing the construction of a 55 further white level information correction apparatus to which the present invention is applied together with several associated elements;

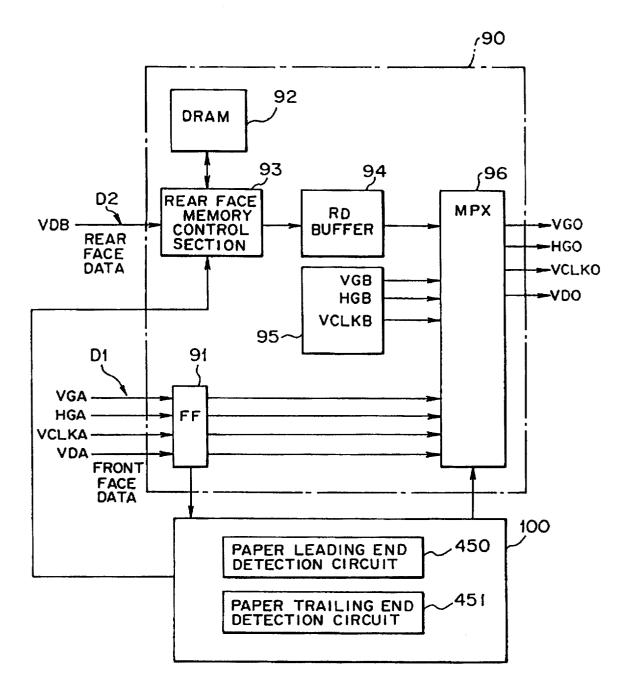

FIG. 21 is a block diagram showing the construction of an outputting section and an output control circuit of the image  $_{60}$  data processing system shown in FIG. 2;

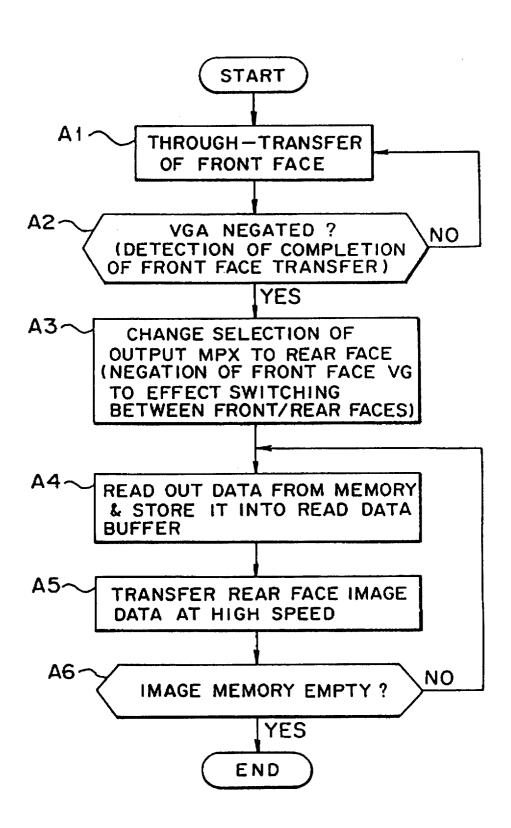

FIG. 22 is a flow chart illustrating operation of the outputting section and the output control section shown in FIG. 21;

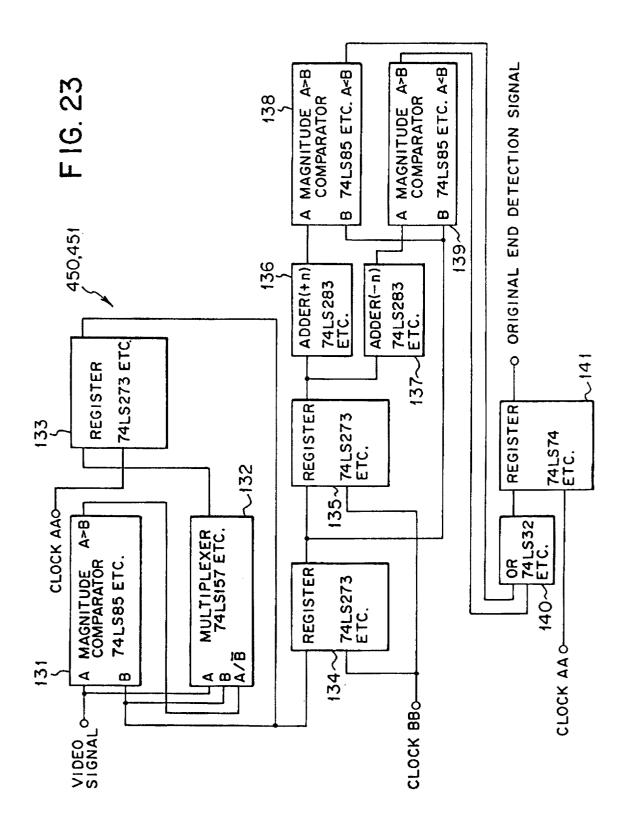

FIG. 23 is a block diagram showing the construction of an 65 original end detection circuit of the image data processing system shown in FIG. 2;

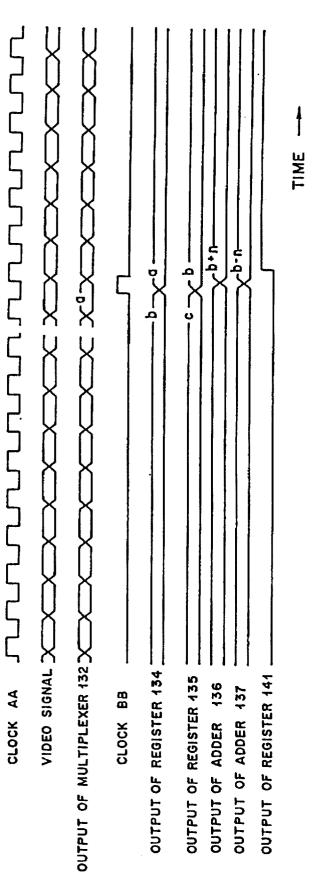

FIG. 24 is a time chart illustrating operation of the original end detection circuit shown in FIG. 23;

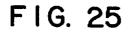

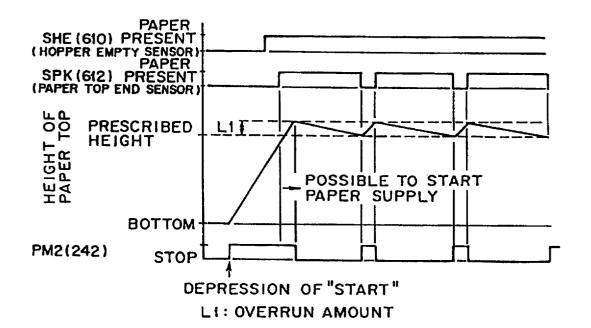

FIG. 25 is a sequence diagram illustrating initialization operation of a hopper system of the image reading apparatus of FIG. 4;

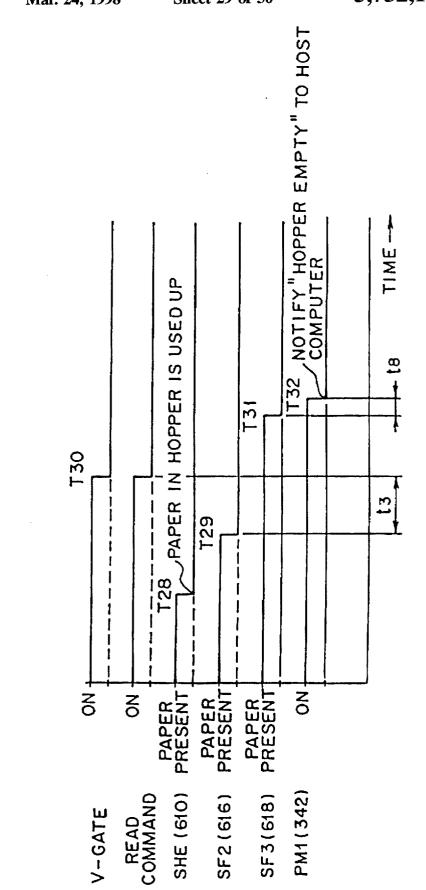

FIG. 26 is a sequence diagram illustrating operation of the hopper system in an automatic reading mode;

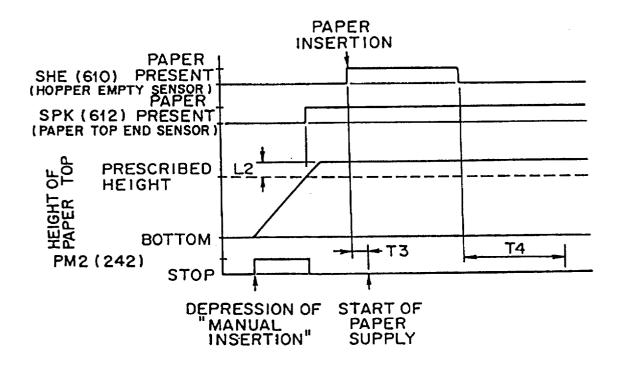

FIG. 27 is a sequence diagram illustrating operation of the hopper system in a manual insertion mode;

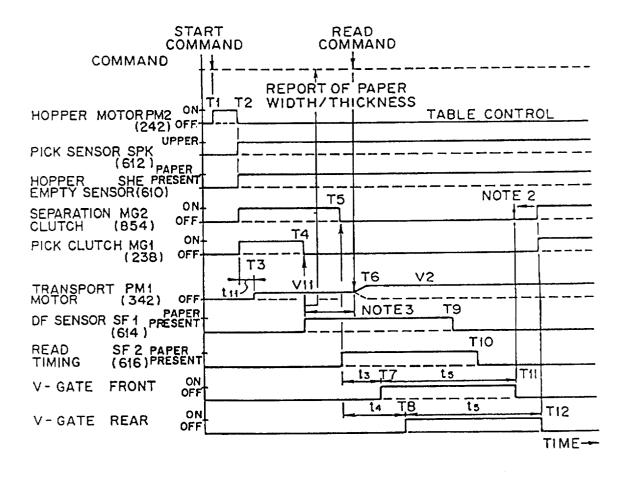

FIG. 28 is a sequence diagram illustrating operation of a transport system of the image reading apparatus of FIG. 4;

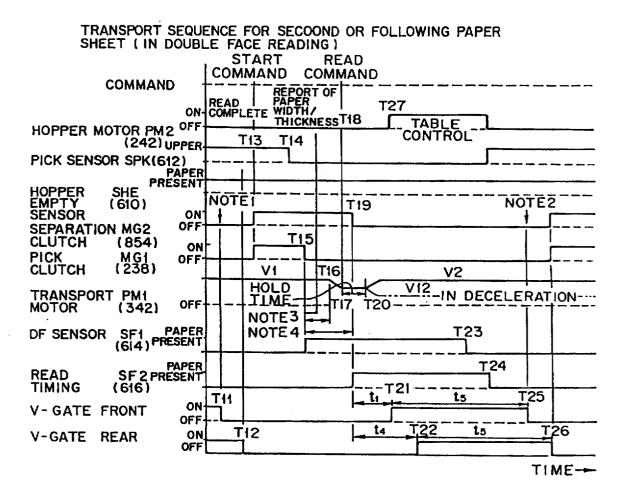

FIG. 29 is a similar view but illustrating operation of the transport system at a different stage;

FIG. 30 is a similar view but illustrating operation of the transport system at another different stage; and

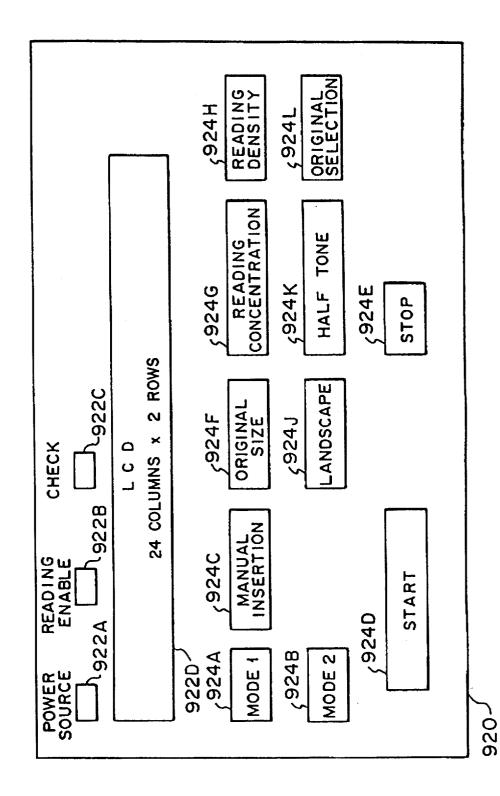

FIG. 31 is a front elevational view showing an operation panel of the image reading apparatus shown in FIG. 4.

#### DESCRIPTION OF THE PREFERRED EMBODIMENT

a. Aspect of the Invention

Referring first to FIG. 1, there is shown an image reading apparatus in which a white level information correction apparatus is incorporated according to an aspect of the present invention. The image reading apparatus includes a paper transport path 310 along which a paper sheet 40 from which an image is to be read is transported, and an optical image reading unit 410 which optically reads, at a predetermined location of the paper transport path 310, image information from a paper sheet 40 being transported along the paper transport path 310.

The image reading apparatus further includes analog to digital conversion means (A/D conversion means) 60 for converting analog data obtained by the optical image reading unit 410 into digital data using white level information of the image information as an index to a conversion reference, and a white level information correction apparatus 70 for correcting white level information to be used as an index to the conversion reference of the analog to digital conversion means 60.

It is to be noted that digital to analog conversion means (D/A conversion means) 62 is provided to convert white level information from the white level information correction apparatus 70 by digital to analog conversion and provide a resulted analog signal as an index to the conversion reference to the analog to digital conversion means

The white level information correction apparatus 70 includes a plurality of storage means 72-1 to 72-N (N is an 50 integral number equal to or greater than 2) for storing a plurality of pieces of white level information to be used as indices to the conversion reference, data magnification variation means 74 for multiplying white level information from one 72-i (i =1, 2, ..., N) of the storage means 72-1 to 72-N by a coefficient to vary the magnification of the data, and data write control means 76 for storing white level information variation means 74 into one 72-i of the storage means 72-1 to 72-N to update the stored data.

The storage means 72-1 to 72-N may be constituted from memory circuits independent of each other and capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference or alternatively from a single memory circuit having a plurality of storage areas capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference.

35

The magnification rate of variation of the data magnification variation means 74 may be variable.

The data write control means 76 may include selection means for storing white level information varied in magnification by the data magnification variation means 74 into a <sup>5</sup> selected one 72-i of the storage means 72-1 to 72-N to update the stored data.

The data write control means 76 may include first selection means for selectively outputting white level information varied in magnitude by the data magnification variation <sup>10</sup> means 74 or white level information from one 72-i of the storage means 72-1 to 72-N, a white level algorithm circuit for comparing white level information selected by the first selection means and data obtained from the optical image reading unit 410 with each other and correcting the white level information in response to a result of the comparison, and second selection means for storing an output of the white level algorithm circuit into a selected one 72-i of the plurality of storage means 72-1 to 72-N to update the stored data.

The white level information correction apparatus may further comprise switching control means for determining based on data obtained from the optical image reading unit **410** whether white level information should be varied in magnitude by the data magnification variation means **74** and automatically controlling selective switching of the first selection means.

The white level algorithm circuit may include a digital comparison circuit for comparing digital white level information selected by the first selection means and digital data obtained by the optical image reading unit **410** with each other, and a white level information correction circuit for correcting the white level information in response to a result of comparison by the digital comparison circuit.

Alternatively, the white level algorithm circuit may include a control signal production circuit for comparing digital white level information selected by the first selection circuit and digital data obtained by the optical image reading unit **410** with each other and outputting, in response to a result of the comparison, a control signal indicating that the digital data has a predetermined value, a counting circuit for counting the number of times by which a control signal is outputted successively in a direction of a line from the control signal production circuit, and a white level information correction circuit for correcting the white level information in response to a count value of the counting circuit.

In the image reading apparatus shown in FIG. 1. image information of a paper sheet 40 being transported along the paper transport path 310 is optically read by the optical 50 image reading unit 410 at the predetermined location of the paper transport path 310, and analog data thus obtained by the optical image reading unit 410 are converted into digital data by the analog to digital conversion means 60 using white level information of the image information as an index 55 to a conversion reference. In this instance, the white level information correction apparatus 70 corrects the white level information to be used as an index to the conversion reference of the analog to digital conversion means 60.

In particular, in the white level information correction 60 apparatus 70, a plurality of pieces of white level information to be used as indices to the conversion reference are stored in the plurality of storage means 72-1 to 72-N (which may be memory circuits independent of each other or a plurality of storage areas of a single memory circuit). Thus, in such 65 a case that the ground color a paper sheet 40 varies significantly from that of the last paper sheet 40, the data magni-

fication variation means 74 multiplies white level information from one 72-i (i=1,2,...,N) of the storage means 72-1 to 72-N by a desired coefficient to vary the magnification of the data, and the data write control means 76 stores the white level information varied in magnification by the data magnification variation means 74 into one 72-i of the storage means 72-1 to 72-N to update the stored data.

When necessary, the magnification rate of variation of the data magnification variation means 74 is made variable.

Where the data write control means 76 includes the selection means, when the white level information varied in magnification by the data magnification variation means 74 is to be stored into one 72-i of the storage means 72-1 to 72-N to update the stored data, the one storage means 72-i is selected by the selection means.

Where the data write control means 76 includes the first selection means, the white level algorithm circuit and the second selection means, when the white level information varied in magnification by the data magnification variation means 74 is to be stored into one 72-i of the storage means 72-1 to 72-N by the data write control means 76, white level information varied in magnitude by the data magnification variation means 74 or white level information from one 72-i of the storage means 72-1 to 72-N is selectively outputted by 25 the first selection means, and the white level information selected by the first selection means is compared with data obtained from the optical image reading unit 410 and the white level information is corrected in response to a result of the comparison by the white level algorithm circuit. Then, 30 the output of the white level algorithm circuit is stored into one 72-i of the plurality of storage means 72-1 to 72-N selected by the second selection means to update the stored data.

Where the white level information correction apparatus further comprises the switching control means, the switching control means determines, based on data obtained from the optical image reading unit **410**, whether the white level information should be varied in magnitude by the data magnification variation means **74** and automatically controls selective switching of the first selection means.

Where the white level algorithm circuit includes the digital comparison circuit and the white level information correction circuit, the digital comparison circuit compares digital white level information selected by the first selection means and digital data obtained by the optical image reading unit **410** with each other, and the white level information correction circuit corrects the white level information in response to a result of comparison by the digital comparison circuit.

Where the white level algorithm circuit alternatively includes the control signal production circuit, the counting circuit and the white level information correction circuit described above, the control signal production circuit compares digital white level information selected by the first selection circuit and digital data obtained by the optical image reading unit 410 with each other and outputs. in response to a result of the comparison, a control signal indicating that the digital data has a predetermined value, and the counting circuit counts the number of times by which a control signal is outputted successively in a direction of a line from the control signal production circuit. Further, the white level information correction circuit corrects the white level information in response to a count value of the counting circuit.

Accordingly, the following effects or advantages can be anticipated with the white level information correction apparatus and/or the image reading apparatus according to the present invention.

1. Since the white level information correction apparatus comprises the plurality of storage means 72-1 to 72-N for storing a plurality of pieces of white level information to be 5 used as indices to the conversion reference, the data magnification variation means 74 for multiplying white level information from one of the storage means 72-1 to 72-N by a coefficient to vary the magnification of the data, and the data write control means 76 for storing white level infor- 10 mation varied in magnification by the data magnification variation means 74 into one of the storage means 72-1 to 72-N to update the stored data, even in such a case that, for example, paper sheets whose ground color is white have been read till now and blue print paper sheets of a different 15 ground color are to be read subsequently, the white level information correction apparatus copes with this sufficiently and can perform analog to digital conversion of image data with a high degree of accuracy.

2. Where the storage means 72-1 to 72-N are constituted <sup>20</sup> from memory circuits independent of each other and capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference, control of white level information is facilitated.

3. Where the storage means 72-1 to 72-N are constituted from a single memory circuit having a plurality of storage areas capable of storing a plurality of pieces of white level information to be used as indices to the conversion reference, a plurality of independent memory circuits need not be prepared and easy handling is achieved. 30

4. Where the magnification rate of variation of the data magnification variation means 74 is variable, a high degree of freedom is provided for correction of a white level.

5. Where the data write control means 76 includes the 35 selection means for storing white level information varied in magnification by the data magnification variation means 74 into a selected one 72-i of the storage means 72-1 to 72-N to update the stored data, the stored contents of any one of the plurality of storage means can be updated readily.

6. Where the data write control means 76 includes the first selection means for selectively outputting white level information varied in magnitude by the data magnification variation means 74 or white level information from one 72-i of the storage means 72-1 to 72-N, the white level algorithm  $_{45}$  circuit for comparing white level information selected by the first selection means and data obtained from the optical image reading unit 410 with each other and correcting the white level information in response to a result of the comparison, and the second selection means for storing the  $_{50}$  output of the white level algorithm circuit into a selected one 72-i of the plurality of storage means 72-1 to 72-N to update the stored data, the white level can be corrected between paper sheets having a same ground color.

7. Where the white level information correction apparatus 55 further comprises the switching control means for determining based on data obtained from the optical image reading unit 410 whether white level information should be varied in magnitude by the data magnification variation means 74 and automatically controlling selective switching of the first 60 selection means, even when a paper sheet to be read changes from the last paper sheet, variation of the white level can be automatically performed rapidly.

8. Where the white level algorithm circuit includes the digital comparison circuit for comparing digital white level 65 information selected by the first selection means and digital data obtained by the optical image reading unit **410** with

each other and the white level information correction circuit for correcting the white level information in response to a result of comparison by the digital comparison circuit, analog circuits in the entire circuitry and patterns on a printed circuit board of the image inputting apparatus can be minimized. Further, since the correction of the white level is based on digital processing, oscillations, which often occur with an analog comparator, do not occur in a high frequency band. Accordingly, the advantage that an increase in stability of operation and in efficiency and certainty in designing can be achieved is achieved. Further, in this instance, since the digital circuit portion of the white level algorithm circuit can be constructed only from ordinary logical OR and AND gate circuits, it can be included readily into a large scale integrated circuit (LSI).

9. Where the white level algorithm circuit includes the control signal production circuit for comparing digital white level information selected by the first selection circuit and digital data obtained by the optical image reading unit 410 with each other and outputting, in response to a result of the comparison, a control signal indicating that the digital data has a predetermined value, the counting circuit for counting the number of times by which a control signal is outputted successively in a direction of a line from the control signal production circuit, and the white level information correction circuit for correcting the white level information in response to a count value of the counting circuit, similarly as described in paragraph 8 above, analog circuits in the entire circuitry and patterns on a printed circuit board of the image inputting apparatus can be minimized. Further, since the correction of the white level is based on digital processing, oscillations, which often occur with an analog comparator, do not occur in a high frequency band. Accordingly, the advantage that an increase in stability of operation and in efficiency and certainty in designing can be achieved is achieved. Further, in this instance, since the digital circuit portion of the white level algorithm circuit can be constructed only from ordinary logical OR and AND gate circuits, it can be included readily into a large scale inte-40 grated circuit (LSI).

b. Embodiment of the Invention

An image reading apparatus according to a preferred embodiment of the present invention will be described in detail below with reference to the accompanying drawings. 1. General Construction of the Image Reading Apparatus

Referring first to FIGS. 4 to 7, there is shown an image reading apparatus according to a preferred embodiment of the present invention. The general structure of the image reading apparatus shown can be divided into an apparatus body 10 and an apparatus lid unit 20. The apparatus lid unit 20 is mounted for pivotal motion around a fulcrum 32 to open or close the apparatus body 10. When the image reading apparatus is used, the apparatus lid unit 20 is fixed to such a closing condition as indicated by solid lines in FIGS. 4 to 6 by a body-lid unit locking mechanism 30. Various other components of the image reading apparatus lid unit 20.

Referring to FIGS. 4 and 7, the image reading apparatus includes, as components thereof, a paper supply mechanism 200 which can successively supply paper sheets 40 accommodated therein, a paper transport mechanism 300 for transporting a paper sheet 40 supplied from the paper supply mechanism 200, an optical image reading mechanism 400 for optically reading information on a paper sheet 40 being transported by the paper transport mechanism 300, and a paper stacking mechanism 500 for receiving a paper sheet

40 discharged from the paper transport mechanism 300 to stack such paper sheets 40.

The paper supply mechanism 200 includes a paper supply hopper 210 which can accommodate therein paper sheets 40 to be read, a paper supply roller 220 located above the paper supply hopper 210 for supplying one of paper sheets 40 accommodated in the paper supply hopper 210 toward the paper transport mechanism 300, a paper supply roller driving mechanism 230 for driving the paper supply roller 220 to rotate, a paper supply hopper driving mechanism 240 for 10 driving the paper supply hopper 210 to an inclined position in response to the amount of paper sheets 40 accommodated in the paper supply hopper 210, and a paper separation mechanism 800 for preventing two or more paper sheets supplied by the paper supply roller 220 from being fed to the 15 paper transport mechanism 300.

The paper supply hopper 210 includes a hopper table 212 supported for pivotal motion on a rotatable shaft 212A located at a rear end portion (right end portion in FIGS. 4 and 7) of the image reading apparatus. The hopper table 212 20 is driven at an end portion (left end portion in FIGS. 4 and 7) thereof by a rack-and-pinion mechanism 248 (including a pinion 248A and a rack 248B) of the paper supply hopper driving mechanism 240 so that it is pivoted upwardly and downwardly and adjusted to a predetermined inclined posi- 25 tion. The hopper table 212 includes, as shown in FIG. 5, a pair of tiltable paper edge guide members 214 for guiding the opposite side edges of the paper sheets 40 accommodated in the paper supply hopper 210.

The paper supply hopper driving mechanism 240 30 includes, as a driving source, a hopper motor 242 constituted from a stepper motor. The driving force of the hopper motor 242 is transmitted to the rack-and-opinion mechanism 248 by way of a belt-and-pulley mechanism 244.

Meanwhile, the paper supply roller 220 is supported for 35 rocking motion around an axis of a separation roller 820 by way of a rockable arm 292 such that it can be retracted upwardly from a space above the paper supply hopper 210 by a paper supply roller retraction mechanism 270. Such upward retraction of the paper supply roller 220 can be 40 performed artificially. However, in a normal condition wherein no artificial force is applied to the paper supply roller 220, the paper supply roller 220 remains at a position suitably moved down by the weight of the paper supply roller 220 itself or by means of a spring not shown, at which 45 the paper supply roller 220 is received by the hopper table 212 below. Then, when the paper supply hopper 210 is pivoted, the paper supply roller 220 is moved upwardly by a required amount in response to the position of the upper face of the paper sheets 40 accommodated in the hopper 50 table 212 which is moved upwardly or downwardly by pivotal motion of the paper supply hopper 210.

Referring now to FIGS. 4, 7, 8 and 9, the paper supply roller driving mechanism 230 for driving the paper supply roller 220 to rotate includes, as a driving source, a transport 55 motor 342 constituted from a stepper motor. The paper supply roller driving mechanism 230 further includes a first belt-and-pulley mechanism 344 and first to third gear mechanisms 852, 856 and 232 interposed between the transport motor 342 and the paper supply roller 220. A pick 60 clutch 238 constituted from an electromagnetic clutch is provided at an inputting portion of the driving force to the paper supply roller 220 from the third gear mechanism 232.

The paper supply roller driving mechanism 230 is controlled by paper supply roller driving mechanism control 65 means 250 in response to the paper supplying position (hopper paper supplying position) of the paper supply hop-

per 210. More particularly, the paper supply roller driving mechanism control means 250 controls the pick clutch 238 between on and off states to control operation of the paper supply roller driving mechanism 230, that is, the rotation condition of the paper supply roller 220.

The paper separation mechanism 800 includes a separation roller 820, a rotation member 830 disposed in an opposing relationship to the separation roller 820 with a small gap left therebetween, and a separation roller driving mechanism 850 for driving the separation roller 820 to rotate.

The rotation member 830 is located below the separation roller 820, that is, nearer to the apparatus body 10 than the separation roller 820, with a small gap left therebetween. The rotation member 830 includes a pair of pulleys 834 and 836 disposed in a spaced relationship from each other in the paper transporting direction and an endless belt 838 wound between and around the pulleys 834 and 836.

The separation roller driving mechanism 850 is constituted from components substantially common to those of the paper supply roller driving mechanism 230 described hereinabove. In particular, as shown in FIGS. 4, 7, 8 and 9, the separation roller driving mechanism 850 includes the transport motor 342 described hereinabove as a driving source and further includes the first belt-and-pulley mechanism 344 and the first and second gear mechanisms 852 and 856 interposed between the transport motor 342 and the paper supply roller 220. A separation clutch 854 constituted from an electromagnetic clutch is interposed in the first gear mechanism 852. In short, the paper supply roller driving mechanism 230 has a construction wherein the third gear mechanism 232 is provided in addition to the separation roller driving mechanism 850. It is to be noted that operation of the separation clutch 854 is controlled by separation clutch control means 858.

Meanwhile, the paper transport mechanism 300 includes a paper transport path 310 for transporting a paper sheet 40 supplied thereto from the paper supply mechanism 200, a plurality of paper transporting rollers 320 to 328 disposed along the paper transport path 310, a roller driving mechanism 340 for driving the paper transporting rollers 320 to 328, and roller driving mechanism control means 350 for controlling the roller driving mechanism 340. Idler rollers 330 to 338 are provided corresponding to the paper transporting rollers 320 to 328, respectively.

The paper transport path 310 includes an inclined transport path 312 for transporting a paper sheet supplied thereto from the paper supply mechanism 200 in an inclined condition, and a paper reversing transport path 314 provided contiguously to the inclined transport path 312 for reversing the paper sheet 40 transported by the inclined transport path 312.

Due to the construction of the paper transport path 310, the posture of one of the paper sheets 40 supplied from the paper supply hopper 210 is changed first from a substantially horizontal posture in the paper supply hopper 210 to a rearwardly inclined posture in the inclined transport path 312 and is then reversed by the paper reversing transport path 314, and then, in this posture, the paper sheet 40 is discharged to the paper stacking mechanism 500.

Consequently, a paper sheet which is directed upwardly in the paper supply hopper 210 is directed downwardly in the paper stacking mechanism 500, and the paper sheets 40 accommodated one on another in the paper supply hopper 210 are successively stacked into the paper stacking mechanism 500 without changing the order of them.

Meanwhile, the paper transporting rollers 320 to 328 and the idler rollers 330 to 338 are disposed in a condition

Sec. 84

distributed discretely at a distance smaller than the length of the paper sheets 40 in the transporting direction as seen from FIGS. 4, 7, 8 and 9.

The roller driving mechanism 340 includes the transport motor 342 described above as a driving source and further 5 includes a second belt-and-pulley mechanism 348 in addition to the first belt-and-pulley mechanism 344. The first and second belt-and-pulley mechanism 344 and 348 will be described here. The first belt-and-pulley mechanism 344 includes a pulley 344A mounted on a rotary shaft of the 10 transport motor 342, another pulley 344B mounted on a rotary shaft 320A of the paper transporting roller 320, and a belt 346A wound between and around the pulleys 344A and 344B. The second belt-and-pulley mechanism 348 includes pulleys 320B to 328B mounted on the rotary shafts 320A to 15 328A of the paper transporting rollers 320 to 328, respectively, and a belt 346B wound between and around the pulleys 320B to 328B.

Accordingly, when the transport motor 342 operates, the driving force is transmitted from the rotary shaft of the 20 transport motor 342 to the pulley 344B by way of the pulley 344A and the belt 346A so that the rotary shaft 320A of the paper transporting roller 320 is driven to rotate. Further, from the pulley 320B, the rotary shafts 322A to 328A of the other paper transporting rollers 322 to 328 are driven to 25 rotate by way of the belt 346A and the pulleys 322B to 328B so that the paper transporting rollers 320 to 328 are driven to rotate simultaneously.

It is to be noted that reference numeral **360** denotes a tension pulley.

The paper transport mechanism 300 described above is schematically shown in FIGS. 10 and 11. Referring to FIGS. 10 and 11, the components are shown such that the paper supply hopper 210 is positioned on the left side while a paper stacker 510 is positioned on the right side and a paper 35 sheet 40 is transported from the left to the right side reversely to those in FIGS. 4 to 9 so as to conform to time charts which will be hereinafter described.

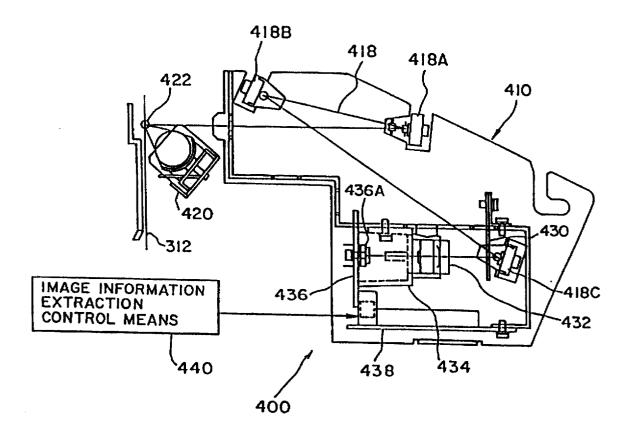

Referring now to FIG. 12, the optical image reading mechanism 400 includes an optical image reading unit 410 40 having a reading point 422 located intermediately of the inclined transport path 312 for optically reading information on a paper sheet 40, and image information extraction control means 440 for controlling extraction of image information read by the optical image reading unit 410. 45

Referring 1:0 FIGS. 4 and 7, the optical image reading unit 410 includes, in the arrangement shown, two units of a first optical image reading unit 412 and a second optical image reading unit 414. The optical image reading units 412 and 414 are located intermediately of the inclined transport path 50 312, and the first optical image reading unit 412 optically reads information on the front face 42 of a paper sheet 40 while the second optical image reading unit 414 optically reads information on the rear face 44 of the paper sheet 40.

Here, each of the optical image reading units **412** and **414** 55 is constituted as an image reading unit of common specifications. For example, FIG. **12** is a schematic side elevational view showing the construction of the image reading unit of common specifications. Referring to FIG. **12**, the optical image reading unit **410** shown includes a fluorescent lamp 60 unit **429** serving as a lighting element for irradiating light upon the reading point **422** on the inclined transport path **312**, a CCD (charge coupled device) circuit board **436** including a CCD array **436**A (CCD array **436**A denotes a plurality of CCDs arranged in an array) for optically reading 65 information on a paper sheet **40**, and a video circuit board **438** for processing information from the CCD array **436**A.

It is to be noted that reference numeral **434** in FIG. **12** denotes a black box.

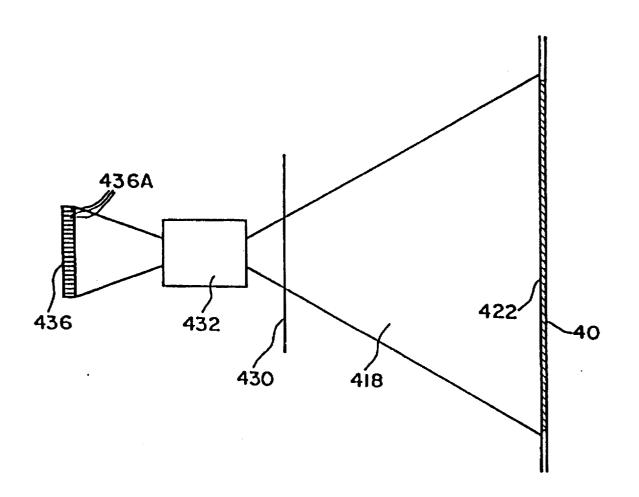

A light path 418 from the reading point 422 to the CCD array 436A is constituted from a plurality of (in the arrangement shown, three, first to third) mirrors 418A, 418B and 418C for reflecting light. A shading plate 430 and a lens 432 are located intermediately of the light path 418 between the mirror 418C and the CCD array 436A so that an image from the mirror 418C may be introduced into the CCD array 436A by way of the lens 432 after it is corrected, particularly at peripheral portions thereof, by the shading plate 430.

Since the light path 418 is formed by the plurality of mirrors 418A, 418B and 418C for reflection of light, the light path 418 can have a sufficient length while the reading point 422 and the CCD circuit board 436 are located at comparatively near locations to each other. Consequently, even where the lens 432 has a great focal length, the reading point 422 can be disposed at a focus position of the lens 432.

A paper sheet 40 from which information has been read by the optical image reading mechanism 400 in this manner is discharged from the paper transport mechanism 300 to the paper stacking mechanism 500. Here, at the terminal end of the paper transport mechanism 300, a paper discharge roller mechanism 540 is located so that the paper sheet 40 may be discharged to the paper stacking mechanism 500 while being driven by the paper discharge roller mechanism 540.

The paper stacking mechanism 500 includes a stacker table 520 having, at the bottom thereof, the paper stacker 510 on which paper sheets 40 can be stacked. A paper trailing end guide mechanism 550 for guiding the rear end 48 of a paper sheet 40 to be stacked into the paper stacker 510.

Referring back to FIGS. 4, 7 and 11, several sensors 610 to 618, 620A to 620D and 622 are provided. Thus, operaitions of the driving systems described above, that is, operations of the hopper motor 242 of the paper supply hopper driving mechanism 240, the pick clutch 238 of the paper supply roller driving mechanism 230. the separation clutch 854 and the roller driving mechanism 340 of the separation roller driving mechanism 850, and the transport motor 342 for the separation roller driving mechanism 230 and extraction operations of the image information extraction control means 440 of the first optical image reading unit 412 and the second optical image reading unit 414 are controlled in response to detection signals from the sensors 610 to 618 and 620A to 620D.

The sensor (SHE) **610** is a hopper empty sensor for detecting whether or not the paper supply hopper **210** is empty. The sensor (SPK) **612** is a paper supply sensor for detecting whether or not the posture of the paper supply hopper **210** is in an optimum condition (that is, a hopper paper supplying position) for supplying a paper sheet. Here, since the paper supply roller **220** is put into a paper supplying position (optimum condition) in response to the paper supplying position of the paper supply hopper **210**, the sensor **612** actually detects whether or not the paper supply hopper **210** and the paper supply roller **220** are in their individual paper supplying positions. The hopper empty sensor **610** and the paper supply sensor **612** may each be constituted from, for example, a photo-interrupter.

The sensor (SF1) 614 and the sensor (SF2) 616 are transport sensors for detecting a paper sheet 40 is transported by the paper transport mechanism 300. The sensor (SF3) 618 is a discharge sensor for detecting whether or not a paper sheet 40 is discharged from the paper transport mechanism 300 to the paper stacking mechanism 500. The transport sensors 614 and 616 and the discharge 618 may each be constituted from, for example, a photo-sensor. Here, the transport sensor 614 is a transmission type photo-sensor which includes a light emitting element and a light receiving element located on the opposite sides of the paper transport mechanism 300, and each of the transport sensor 616 and the discharge sensor 618 is a reflection type sensor wherein a light emitting element and a light receiving element are provided as a unitary member.

The sensor (SB5) 620A, the sensor (SA4) 620B, the 10 sensor (SB4) 620C and the sensor (SA3) 620D are sheet width detection sensors. The sensor 620A is a B5 width detection sensor provided for detection of a paper width of a paper sheet of the "B5 size"; the sensor 620B is an A4/LT width detection sensor provided for detection of a paper 15 width of a paper sheet of the "A4 size" or "LT size"; the sensor 620C is a B4 width detection sensor provided for detection of a paper width of a paper sheet of the "B4 size"; and the sensor 620D is an A4/DL width sensor provided for detection of a paper width of a paper sheet of the "A3 size" 20 or "DL size". The sensors 620A to 620D may each be constituted from, for example, a photo-sensor (in the arrangement shown, a reflection type photo-sensor is employed).

criminating whether or not the hopper table 212 of the paper supply hopper 210 is at its lowermost position (bottom position). The sensor 622 may be, for example, a photointerrupter.

For starting and stopping operations, setting of an opera-30 tion condition and so forth of the image reading apparatus described above, an operation panel 920 is provided at the front of the image reading apparatus as shown, for example, in FIG. 5.

2. Image Reading Mechanism

The optical image reading unit 410 includes, in the arrangement shown, two units of the first optical image reading unit 412 and the second optical image reading unit 414 as described hereinabove. The optical image reading units 412 and 414 are located intermediately of the inclined 40 transport path 312, and the first optical image reading unit 412 optically reads information on the front face 42 of a paper sheet 40 while the second optical image reading unit 414 optically reads information on the rear face 44 of the 45 paper sheet 40.

As described above, since the optical image reading units 412 and 414 are constructed as image reading units of common specifications, when there is no necessity of distinguishing them from each other in the description of each optical image reading unit, the optical image reading unit is 50 represented by the optical image reading unit 10. In particular, the light path 418 from the reading point 422 to the CCD circuit board 436 in the optical image reading unit 410 is schematically shown in FIG. 13 wherein the light path 418 is generally represented as a straight line omitting the 55 reflections by the mirrors 418A, 418B and 418C. Referring to FIG. 13, pieces of image information arranged in the widthwise direction of a paper sheet 40 are collected by the lens 432 and come to the CCD circuit board 436. The CCD circuit board 436 is constituted from a plurality of CCDs 60 arranged in a juxtaposed relationship to each other so as to catch the pieces of information arranged in the widthwise direction.

The shading plate 430 located forwardly of the lens 432 corrects the image information since the image information 65 is distorted by an increasing amount toward the opposite left and right ends and of the paper sheet 40.

The CCD array 436A operates under the control of respective CCD drivers to catch image information, and the image information is sent to and processed by a video circuit provided on the video circuit board 438.

By the way, in each of the optical image reading units 410, the fluorescent lamp unit 420 is provided in order to make the reading point 422 light.

It is to be noted that a heater (not shown) is provided along the rear face of the fluorescent lamp of the fluorescent lamp unit 420. When the temperature is low, the heater is rendered operative, and after it is started, the fluorescent lamp is warmed up rapidly so that the reading point 422 can be illuminated with a sufficient amount of light.

3. Read Image Data Processing

3-1. Outline of the Read Image Data Processing System

Referring to FIG. 2, the image reading apparatus includes a first image data processing system D1 for processing image data read by the first optical image reading unit 412 for reading information on the front face of a paper sheet, and a second image data processing system D2 for processing image data read by the second optical image reading unit 414 for reading information on the rear face of the paper sheet.

The first image data processing system D1 includes a Meanwhile, the sensor 622 is a bottom sensor for dis- 25 CCD array 436AA of the first optical image reading unit 412, an amplification circuit (AMP) 64A, a sample hold circuit 66A, an analog to digital (A/D conversion circuit 60A, and an image processing section 68A. Meanwhile, the second image data processing system D2 includes a CCD array 436AB of the second optical image reading unit 414. an amplification circuit 64B, a sample hold circuit 66B, an analog to digital conversion circuit 60B and an image processing section 68B.

The CCD arrays 436AA and 436AB read image data of a 35 paper sheet by way of the image reading units 412 and 414, respectively, as described hereinabove. The amplification circuits 64A and 64B amplify the image data of the paper sheet obtained from the CCD arrays 436AA and 436AB. respectively, and the sample hold circuits 66A and 66B sample and hold the image data of the paper sheet after amplified by the amplification circuits 64A and 64B, respectively.

The analog to digital conversion circuits 60A and 60B convert analog data obtained from the image reading units 412 and 414 into digital data using white level information and black level information of the image information of the paper sheet as indices for a conversion criterion. The image processing sections 68A and 68B process the digital data from the analog to digital conversion circuits 60A and 60B. respectively, by various processes such as binary digitization, emphasis and smoothing.

The image data processing system further includes an outputting section 90 for selectively sending out paper front face image data and paper rear face image data to a host computer (not shown) in response to an instruction from an output control circuit 100 which is part of the image information extraction control means 440. In particular, in the present embodiment, since the image reading units 412 and 414 are provided in the proximity of each other, it sometimes occurs that the image reading units 412 and 414 read images simultaneously. Therefore, information from the second optical image reading unit 414 for reading information on the rear face of a paper sheet is stored once into a buffer storage apparatus (DRAW) of the rear face reading board 944 (refer to FIG. 3) and, after information from the first optical image reading unit 412 is sent to the host computer. the information from the second optical image reading unit 414 is sent from the buffer storage apparatus to the host computer. Such control means is provided in the outputting section 90, and details of the same will be hereinafter described.

In this manner, image information read by the image 5 reading units 412 and 414 is read out under the control of the output control circuit 100 of the image information extraction control means 440 as seen from FIG. 7. In this instance, in the image information extraction control means 440. transfer control of image information to the host computer 10 and like control are performed in response to results of detection of a paper leading end detection circuit (paper leading end detection means) 450 and a paper trailing end detection circuit (paper trailing end detection means) 451. It is to be noted that the paper leading end detection circuit 450 and the paper trailing end detection circuit 4S1 will be  $^{15}$ hereinafter described.

In particular, the paper leading end detection circuit 450 detects the paver leading end 46 from a variation of the output of each of the optical image reading units 410, and the rarer trailing end detection circuit 451 detects the paper 20 trailing end 48 from a variation of the output of each of the optical image reading units 410. The paper lead end detection circuit 450 and the paper trailing end detection circuit 4S1 are both provided in the image information extraction control means. It is to be noted that also the raper leading 25 end detection circuit 450 and the paper trailing end detection circuit 451 will be hereinafter described.

Further, the image information extraction control means 440 controls extraction of image information obtained from the first optical image reading unit 412 and the second 30 embodiment, the first optical image reading unit 412 and the optical image reading unit 414 in response to a result of selection by the original selection switch 924L serving as the paper reading selection means and a discrimination mark (not shown) applied to a paper sheet 40.

In particular, it can be selected by the original selection 35 switch 924L whether both face reading should be performed or one face reading should be performed, and the image information extraction control means 440 performs reading control in response to a result of the selection by the original selection switch 924L. However, paver sheets which require 40 includes detection means (front/rear face detection means) both face reading and paver sheets which allow one face reading may possibly be present in a mixed condition. In this instance, when paper sheets should be read in a different manner from other paper sheets in which the paper sheets are mixed, a discrimination mark is applied to each of the paper 45 sheets so that they may be read in a different manner. The discrimination mark is provided for discrimination whether the paper sheet should be read by one face reading or by both face reading, and is applied to a location outside an original reading area such as, for example, a corner of the leading 50 end of the paper sheet 40 so that it may be distinguished from image information in the original reading area which should originally be read.

Therefore, for example, when one face reading originals are mixed in both face reading originals, if a discrimination 55 mark which designates one face reading is applied to each of the one face reading originals the quantity of which is smaller than that of the both face reading originals and it is selectively set by way of the original selection switch 924L that both faces of each paper sheet 40 should usually be read. 60 then image information on both faces of a paper sheet is normally read by both of the first optical image reading unit 412 and the second optical image reading unit 414. However, when a discrimination mark 50 is detected, image information only on the front face or the rear face of the 65 paper sheet 40 is read by the first optical image reading unit 412 or the second optical image reading unit 414.

On the contrary, when both face reading originals are mixed in one face reading originals, if a discrimination mark which designates double face reading is applied to each of the double face reading originals the quantity of which is smaller than that of the one face reading originals and it is selectively set by way of the original selection switch 924L that one face of each paper sheet 40 should usually be read. then image information only on the front face or the rear face of a paper sheet is normally read by the first optical image reading unit 412 or the second optical image reading unit 414. However, when a discrimination mark is detected, image information on the both faces of the paper sheet is read by both of the first optical image reading unit 412 and the second optical image reading unit 414.

The image information extraction control means 440 further includes discrimination mark image erasure means 460 so that the image of such discrimination mark applied to a paper sheet 40 may be erased and only image information to be read originally may be outputted.

By the way, the apparatus body 10 or the apparatus lid 20 assures an upper mounting space (space for the front face reading unit) 26 and a lower mounting space (space for the rear face reading unit) 16 having substantially similar sizes and shapes to each other to allow the optical image reading units 412 and 414 to be mounted in them, respectively (refer to FIG. 4). In the meantime, the optical image reading unit 410 is prepared by a plural number having different specifications having different performances but having substantially common sizes and profiles.

While, in the image reading apparatus of the present second optical image reading unit 414 are constructed with common specifications, it is easy to construct the first optical image reading unit 412 and the second optical image reading unit 414 so as to have different specifications such that, for example, the optical image reading unit for front face reading of the construction described above has higher performances than the optical image reading unit for rear face reading of the construction described above.

Further, each of the optical image reading units 410 630 which can detect that it is installed as a unit for front face reading when it is installed in the upper mounting space 26 but detect that it is installed as a unit for rear face reading when it is installed in the lower mounting space 16. The detection means 630 may be constructed such that, for example, a front surface detection projection (not shown) is provided only in the upper mounting space 26 while a rear face detection projection (not shown) is provided only in the lower mounting space 16, and a front face detection switch (not shown) which is automatically contacted, when it is installed in the upper mounting space 26, by the front face detection projection to switch to an on-state and a rear face detection switch (not shown) which is automatically contracted, when it is installed in the lower mounting space 16, by the rear face detection projection to switch to an on-state are provided on each of the optical image reading units 410.

Information detected by the detection means 630 in this manner is sent to the image information extraction control means 440 and used for extraction control of image information.

The image data processing system shown in FIG. 2 further includes a pair of timing circuits 55A and 55B which define. for example, sample holding timings of the sample hold circuits 66A and 66B, respectively.

3-2. White Level Information Used upon Analog to Digital Conversion of Image Data and Associated Factors

As shown in FIG. 2, each of the analog to digital conversion circuits 60A and 60B includes a white level information correction circuit (white level information correction apparatus) 70A or 70B and a black level setting circuit 61A or 61B.

The white level information correction circuits 70A and 70B individually set white level information to be used as indices for a conversion criterion of the analog to digital conversion circuits 60A and 60B, respectively, and suitably correct the thus set while level information. The black level 10 setting circuits 61A and 61B individually set black level information to be used as indices for a conversion criterion of the analog to digital conversion circuits 60A and 60B, respectively. It is to be noted that the black level setting circuits 61A and 61B are each constructed as a sample hold 15 circuit.

The white level information correction circuits 70A and 70B will be described in more detail below. Here, since the white level information correction circuits 70A and 70B have a same construction, reference characters to components of the white level information correction circuits 70A and 70B are not distinguished between A and B.

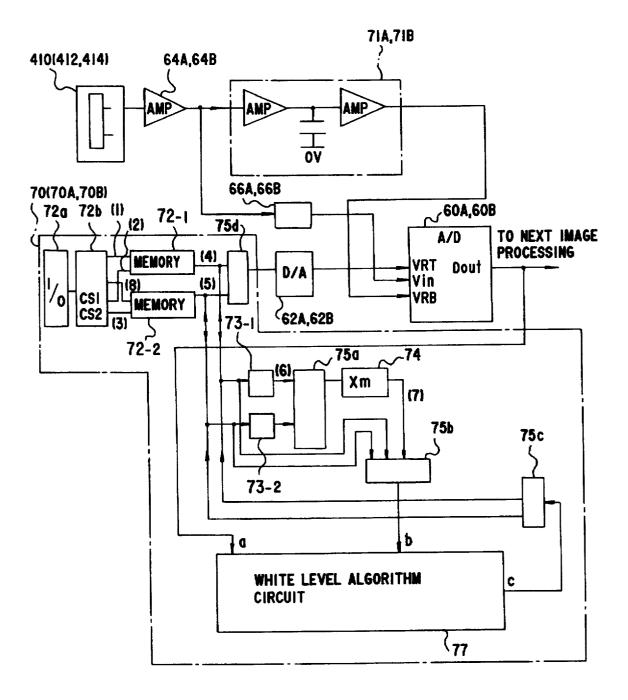

In particular, referring to FIG. 14, the white level information correction circuit 70 includes a plurality of (for example, two) memory circuits 72-1 and 72-2 and registers 25 73-1 and 73-2, selection circuits 75*a*, 75*b*, 75*c* and 75*d*, a data magnification variation circuit 74, a white level algorithm circuit 77, and so forth.

The memory circuits 72-1 and 72-2 store a plurality of pieces of white level information (individual pieces of white 30 level information correspond to originals having different ground colors) to be used as indices for a conversion criterion. Write/read control of each of the memory circuits 72-1 and 72-2 is performed in response to an instruction which is received from an MPU (microprocessor unit) 35 circuit 150 by an address controller 72b by way of an input/output port (I/O port) 72a. It is to be noted that a RAM (random access memory) may be employed for the memory circuits 72-1 and 72-2.

The registers 73-1 and 73-2 serve as buffer circuits for 40 temporarily storing the outputs of the memory circuits 72-1 and 72-2, respectively. Each of the selection circuits 75a, 75b, 75c and 75d, selectively outputs desired data to a required output line. For example, a multiplexer is used for the selection circuits 75a, 75b, 75c and 75d. 45

In particular, the selection circuit 75a selectively outputs data from the register 73-1 or 73-2 to the data magnification variation circuit 74 side. The selection circuit 75b selectively outputs white level information varied by magnification variation by the data magnification variation circuit 74 or 50 white level information from the memory circuit 72-1 or 72-2. The selection circuit 75c stores the output of the white level algorithm circuit 77 into and updates a required one of the memory circuits 72-1 and 72-2. The selection circuit 75d supplies the output of one of the memory circuits 72-1 and 55 72-2 to the analog to digital conversion circuit 60 side by way of a digital to analog conversion circuit 62 (actually, analog to digital conversion circuits 62A and 62B are provided in the data processing systems D1 and D2, respectively). 60

The data magnification variation circuit 74 varies data by magnification variation by multiplying white level information from the memory circuit 72-1 or 72-2 by a desired coefficient (m: in order to lower the white level, a value between 1 and 0 is selected for m, but in order to raise the 65 white level, a value higher than 1 is selected for m). For example, a digital multiplier is used for the data magnifi-

cation variation circuit 74. Further, the magnification variation coefficient m of the data magnification variation circuit 74 can be varied by an instruction from the MPU circuit 150.

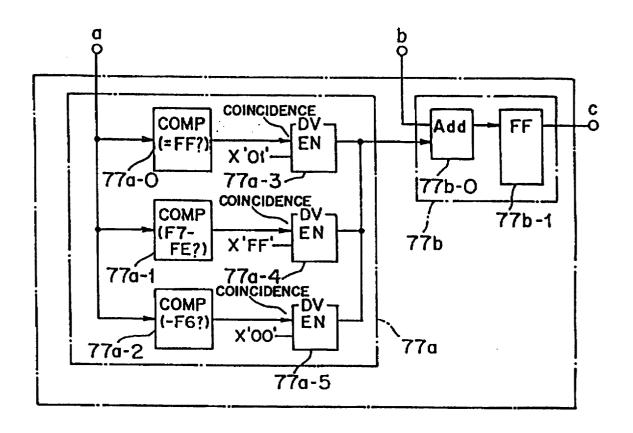

The white level algorithm circuit 77 compares white level information and data obtained from the optical image reading unit **410** with each other and corrects the white level information in accordance with a result of the comparison. Referring to FIG. 1S, the white level algorithm circuit 77 includes a video signal comparator 77*a* serving as a digital comparison circuit for comparing digital white level information selected by the selection circuit 75*b* and digital data obtained from the optical image reading unit **410** with each other, and an addition circuit 77*b* serving as a white level information correction circuit for correcting the white level information in accordance with a result of the comparison by the video signal comparator 77*a*.

The white level information correction circuit 70 will be described in more detail.

Referring first to FIG. 14, analog video signals from the CCD arrays 436AA and 436AB are amplified by the amplification circuits 64A and 64B, respectively, and, for example, those analog video signals of the outputs of the amplification circuits 64A and 54B in portions (bits) in which photosensitive portions of the CCD arrays 436AA and 436AB are masked are sampled and held by black level setting circuits (sample hold circuits) 71A and 71B, respectively. The thus held analog video signals are connected as reference signals for a black level to the lower limit sides (VRB) of the analog to digital conversion circuits 60A and 60B. Meanwhile, reference signals for a white level are obtained by converting white level values in lines obtained in the last scanning cycle and stored in the memory circuit 72-1 or 72-2 into analog signals by means of the digital to analog conversion circuits 62A and 62B, and are connected to the upper limit sides (VRT) of the analog to digital 35 conversion circuits 60A and 60B, respectively.

Consequently, the analog to digital conversion circuits 60A and 50B output digital signals on the scale of 256 gradations between the white reference level (VRT) and the black reference level (VRB). In this instance, for the white reference level, an analog value of a white level produced corresponding to a white level obtained in the last scanning cycle for an image is used, and for the black reference level, an analog value of a dot at which the photosensitive portion of the CCD array 436AA or 436AB is masked is used.

By the way, white reference level data extracted from the memory circuit 72-1 or 72-2 is fetched into the corresponding register 73-1 or 73-2, and one of the outputs of the registers 73-1 and 73-2 is selected by the selection circuit 75a and then multiplied by m by the data magnification variation circuit 74.

Further, the output of the data magnification variation circuit 74 or data extracted from the memory circuit 72-1 or 72-2 is selected by the selection circuit 75b and inputted to the terminal b of the white level algorithm circuit 77.

Meanwhile, a digital value of a video signal which is the output of the analog to digital conversion circuit 60 is inputted to the other terminal a of the white level algorithm circuit 77. Consequently, the thus inputted digital value is inputted to comparators (COMP) 77a-0 to 77a-2 of the video signal comparator 77a shown in FIG. 15 and then outputted from the video signal comparator 77a as one of, for example, three different outputs including X"FF" (white represented by X"FF" by the 256 gradation representation), X"F7" to X"FE" (a little dark white represented by X"F6" or less (white represented by X"F6" or less by the 256 gradation representation).

In the video signal comparator 77a, when the comparators (COMP) 77a-0 to 77a-2 detect that the digital output of the analog to digital conversion circuit **60** is X"FF" mentioned above (that is, when a coincidence output is obtained), it is recognized that the analog video signal obtained by scanning of the current scanning line of the image is equal to or much higher than a white level obtained by scanning in the last scanning cycle, and the white level value of the preceding cycle is incremented, for example, by one.

However, when it is detected that the digital output of the 10 analog to digital conversion circuit **60** falls within the range from X"FE" to X"F7", it is recognized that the analog video signal is a little lower than the white level obtained in the last scanning cycle, and the white level value of the last cycle is incremented by, for example, "-1", that is, decremented by 15 one. Particularly, since no carry need be taken into consideration, X"FF", which is a complementary number on 2, should be added.

When it is detected that the digital output of the analog to digital conversion circuit 60 is equal to or lower than X"F6". 20 it is recognized that not the white level varies but the image now is on the gray level and is considered that it is not related to correction of the white level, and such control as to perform nothing (particular, to add X"00") is performed to calculate a new white level and determine the new white 25 level as a correction value for scanning of the present scanning line.