(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-14875

(P2004-14875A)

(43) 公開日 平成16年1月15日(2004.1.15)

(51) Int.C1.<sup>7</sup>

**H01L 21/8238**

**H01L 27/092**

**H01L 29/78**

F 1

**H01L 27/08** 321E

**H01L 29/78** 301G

テーマコード (参考)

**5F048**

**5F140**

審査請求 未請求 請求項の数 10 O L (全 19 頁)

(21) 出願番号 特願2002-167637 (P2002-167637)

(22) 出願日 平成14年6月7日 (2002.6.7)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 齋木 孝志

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

F ターム (参考) 5F048 AC03 BA01 BB05 BB11 BC05

BC06 BD04 BE03 BF11 BG14

DA23 DA24 DA25 DA27

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【要約】

【課題】レジスト膜を除去する際の半導体基板の酸化及びアニール時の不純物の外方拡散を防止して良好な特性、例えば低いエクステンション抵抗を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】Pウェル2及びNウェル3の表面並びにゲート電極6の上面及び側面に、膜厚が3nm以下のシリコン窒化膜7を形成する。シリコン窒化膜7は、例えば、マグネットロンR I E装置を使用して、窒素ガスを含むプラズマに、Pウェル2及びNウェル3の表面並びにゲート電極6の上面及び側面を晒すことにより形成することができる。その後、シリコン窒化膜7を残したまま、ポケット層、エクステンション層及びソース・ドレイン拡散層を形成する。この方法によれば、イオン注入時のマスクとしてレジスト膜を使用しても、その除去時に半導体基板1の表面は酸化しない。また、不純物導入後のアニールによっても不純物の外方拡散が防止される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜と、

該ゲート絶縁膜上に形成されたゲート電極と、

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板に形成され、該一導電型とは異なる反対導電型の一对の不純物層と、

を有することを特徴とする半導体装置。

**【請求項 2】**

10

一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜と、

該ゲート絶縁膜上に形成されたゲート電極と、

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板に形成され、該一導電型とは異なる反対導電型の一对の不純物層と、

該ゲート電極に自己整合して該半導体基板に形成された、一对の一導電型不純物層と、

を有することを特徴とする半導体装置。

**【請求項 3】**

20

一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜と、

該ゲート絶縁膜上に形成されたゲート電極と、

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板から第1の深さに形成され、該一導電型とは異なる第1の反対導電型不純物層と、

該ゲート電極に自己整合して該半導体基板に形成された、一对の一導電型不純物層と、

該第1の窒素導入層を介して、該ゲート電極の側面に形成されたサイドウォールと、

該サイドウォール及び該ゲート電極に自己整合して該半導体基板に形成され、該半導体基板から該第1の深さよりも深い第2の深さに形成された、第2の反対導電型不純物層と、

を有することを特徴とする半導体装置。

**【請求項 4】**

前記サイドウォールと前記半導体基板との間に形成された、第2の窒素導入層を有することを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

**【請求項 5】**

前記ゲート絶縁膜は、シリコン酸窒化膜を含むことを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置。

**【請求項 6】**

一導電型の半導体基板上に、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜を形成する工程と、

該ゲート絶縁膜を介してゲート電極を形成する工程と、

該半導体基板及び該ゲート電極の表面に、窒素を導入する工程と、

次いで、該ゲート電極の両側の該半導体基板に、該一導電型とは異なる反対導電型の一对の不純物層を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

**【請求項 7】**

一導電型の半導体基板上に、一導電型領域及び該一導電型とは異なる反対導電型の反対導電型領域を形成する工程と、

該一導電型領域上に、シリコン酸化膜よりも誘電率が高い材料からなる第1のゲート絶縁膜を形成する工程と、

該反対導電型領域上に、第2のゲート絶縁膜を形成する工程と、

10

20

30

40

50

該第1のゲート絶縁膜上に第1のゲート電極を形成する工程と、

該第2のゲート絶縁膜上に第2のゲート電極を形成する工程と、

該第1及び第2のゲート電極の表面に、窒素を導入する工程と、

次いで、該反対導電型領域を選択的に覆う第1のマスク層を形成する工程と、該第1のゲート電極及び該第1のマスク層をマスクにして、該第1のゲート電極の両側の該半導体基板に、該反対導電型の不純物層を形成する工程と、

次いで、該第1のマスク層を除去する工程と、

次いで、該一導電型領域を選択的に覆う第2のマスク層を形成する工程と、

該第2のゲート電極及び該第2のマスク層をマスクにして、該第2のゲート電極の両側の該半導体基板に、該一導電型の不純物層を形成する工程と、

次いで、第2のマスク層を除去する工程と、

を含むことを特徴とする半導体装置の製造方法。

10

## 【請求項8】

一導電型の半導体基板上にゲート絶縁膜を形成する工程と、

該ゲート絶縁膜を介してゲート電極を形成する工程と、

該半導体基板及び該ゲート電極の表面に、窒素を含むガスのプラズマ又はラジカルに晒して、窒素を導入する工程と、

次いで、該ゲート電極の両側の該半導体基板に、該一導電型とは異なる反対導電型の一対の不純物層を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

20

## 【請求項9】

該窒素を導入する工程の後に、該ゲート電極の両側の該半導体基板に、該一導電型の不純物層を形成する工程を含むことを特徴とする請求項6乃至8のいずれか1項に記載の半導体装置の製造方法。

## 【請求項10】

該窒素を導入する工程により形成される窒素を含む層の厚さを3nm以下とすることを特徴とする請求項6乃至9のいずれか1項に記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

30

本発明は、CMOS (complementary metal-oxide semiconductor)トランジスタに好適な半導体装置及びその製造方法に関する。

## 【0002】

## 【従来の技術】

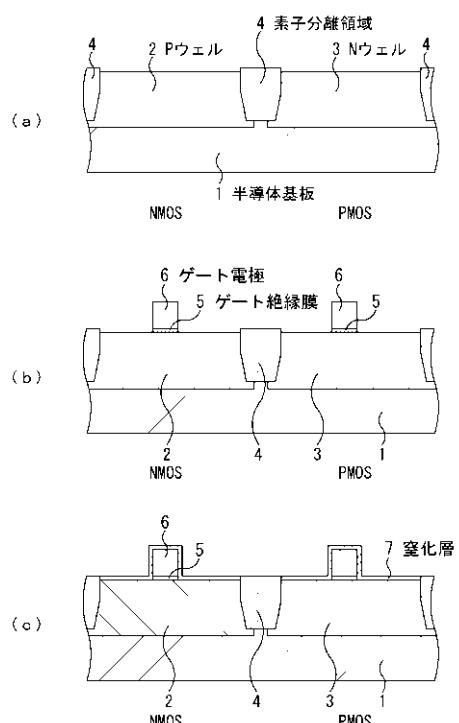

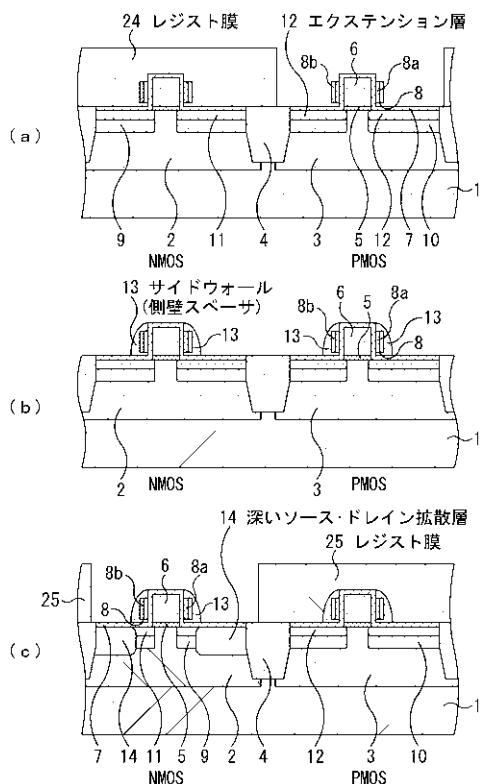

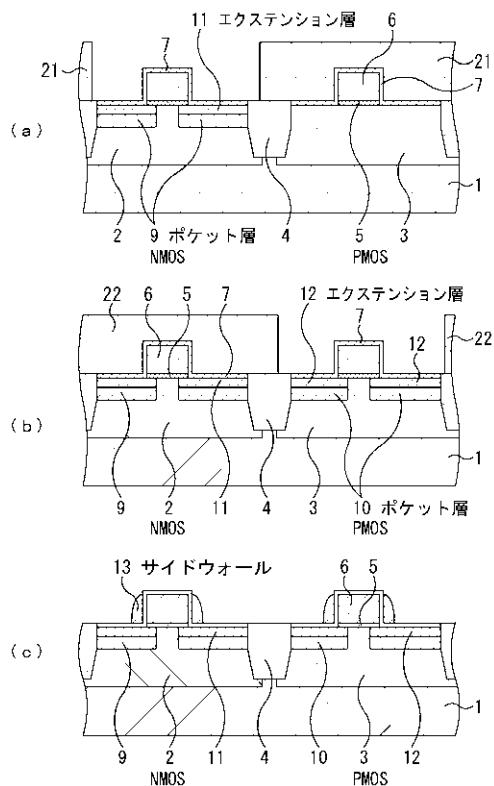

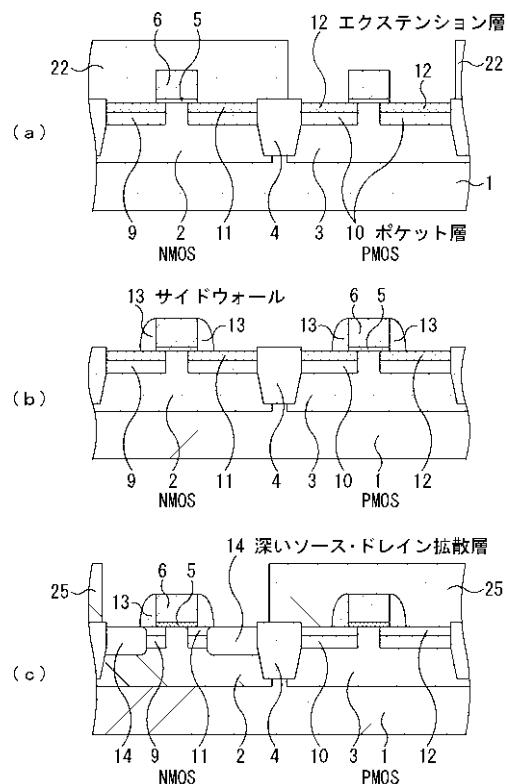

従来、CMOSトランジスタは、次のようにして製造されている。図15乃至図17は、CMOSトランジスタの従来の製造方法を工程順に示す断面図である。

## 【0003】

先ず、図15(a)に示すように、P型半導体基板1の表面に素子分離領域4を形成し、この素子分離領域4により区画された素子領域内にウェルを形成する。このとき、NチャネルMOS(NMOS)領域にはPウェル2を形成し、PチャネルMOS(PMOS)領域にはNウェル3を形成する。

40

## 【0004】

次に、図15(b)に示すように、素子領域内において、半導体基板1上に絶縁膜及び多結晶シリコン膜を形成し、これらをパターニングすることにより、ゲート絶縁膜5及びゲート電極6を形成する。

## 【0005】

次いで、図15(c)に示すように、PMOS領域を覆いNMOS領域を露出するレジスト膜21を半導体基板1上に形成する。そして、このレジスト膜21及びゲート電極6をマスクとして、高濃度に砒素をイオン注入することにより、エクステンション層11を形成し、ボロン又はインジウムをイオン注入することにより、ポケット層9を形成する。な

50

お、ボロン又はインジウムのイオン注入は、半導体基板1の表面に対して垂直な方向又は傾斜した方向から行われる。

【0006】

続いて、図16(a)に示すように、レジスト膜21を除去した後、NMO�領域を覆いPMOS領域を露出するレジスト膜22を半導体基板1上に形成する。そして、このレジスト膜22及びゲート電極6をマスクとして、高濃度にボロンをイオン注入することにより、エクステンション層12を形成し、砒素をイオン注入することにより、ポケット層10を形成する。なお、砒素のイオン注入は、半導体基板1の表面に対して垂直な方向又は傾斜した方向から行われる。

【0007】

次に、図16(b)に示すように、レジスト膜22を除去した後、全面に絶縁膜を形成し、ゲート電極6の側方にのみこの絶縁膜が残るように、異方性エッチングを施すことにより、サイドウォール13を形成する。

【0008】

次いで、図16(c)に示すように、PMOS領域を覆いNMO�領域を露出するレジスト膜25を半導体基板1上に形成する。そして、このレジスト膜25、ゲート電極6及びサイドウォール13をマスクとして、高濃度に砒素をイオン注入することにより、深いソース・ドレイン拡散層14を形成する。

【0009】

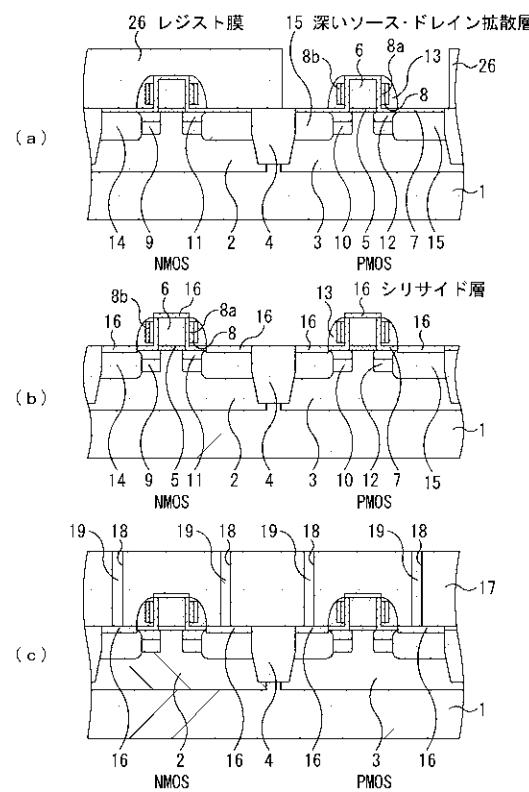

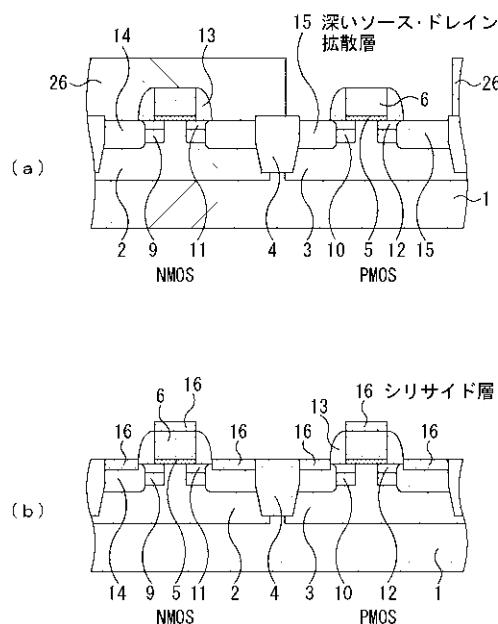

その後、図17(a)に示すように、レジスト膜25を除去した後、NMO�領域を覆いPMOS領域を露出するレジスト膜26を半導体基板1上に形成する。そして、このレジスト膜26、ゲート電極6及びサイドウォール13をマスクとして、高濃度にボロンをイオン注入することにより、深いソース・ドレイン拡散層15を形成する。

【0010】

続いて、図17(b)に示すように、レジスト膜26を除去した後、コバルトシリサイド層等のシリサイド層16を、ゲート電極6並びにソース・ドレイン拡散層14及び15上に形成する。

【0011】

このようにして、CMOSトランジスタを製造することができる。

【0012】

【発明が解決しようとする課題】

しかしながら、このような製造方法においては、ポケット層及びエクステンション層を形成する際のマスクとして使用するレジスト膜21及び22をこれらの層を形成した後に、アッシング及びウェット処理により除去する必要があり、この除去の工程の際に、シリコン基板が酸化されてしまうという問題点がある。シリコン基板が酸化されると、注入した不純物が喪失するため、所望の濃度及びプロファイルを得ることができなくなってしまう。また、シリコン基板の酸化により、エクステンション層がゲート部よりも沈み込んだ状態となるため、エクステンション層の接合が実質的に深くなる。このため、ショートチャネル効果等の特性劣化が生ずることもある。

【0013】

また、上述の製造方法においては、ソース・ドレイン拡散層15を形成した後に、その不純物を活性化させるためにアニール処理を行う必要があり、このアニール処理の際に、チャネルに存在する不純物の外方拡散が発生して空乏化が生じたり、ソース・ドレイン拡散層15内の不純物の外方拡散が発生したりすることができるという問題点もある。

【0014】

この外方拡散を抑制するための技術として、RTO(酸素窒素アニール)による酸化膜キャップ技術が知られている。また、外方拡散防止膜として、CVD法により100nm程度の厚さで窒化膜を成膜する技術も知られている。しかし、酸化膜キャップ技術においては、酸素による増速拡散により、ソース・ドレイン拡散層のプロファイルが深くなってしまうという問題点がある。また、CVD法により100nm程度の窒化膜をゲート電極の

側壁に形成した場合には、ストレスが増加しやすく、また、異常拡散が発生しやすいという問題点がある。

#### 【0015】

本発明は、かかる問題点に鑑みてなされたものであって、レジスト膜を除去する際の半導体基板の酸化及びアニール時の不純物の外方拡散を防止して良好な特性、例えば低いエクステンション抵抗を得ることができる半導体装置及びその製造方法を提供することを目的とする。

#### 【0016】

##### 【課題を解決するための手段】

本願発明者は、鋭意検討の結果、以下に示す発明の諸態様に想到した。

10

#### 【0017】

本発明に係る半導体装置の製造方法においては、一導電型の半導体基板上に、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜を形成し、該ゲート絶縁膜を介してゲート電極を形成した後に、該半導体基板及び該ゲート電極の表面に、窒素を導入し、次いで、該ゲート電極の両側の該半導体基板に、該一導電型とは異なる反対導電型の一対の不純物層を形成する工程と、を含むことを特徴とする。

#### 【0018】

本発明においては、ゲート絶縁膜及びゲート電極を形成した後に半導体基板及びゲート電極の表面に窒素を導入しているので、その後にレジスト膜の形成及び除去を行ったとしても、窒素が導入された領域の酸化が防止される。また、アニールの実施を、半導体基板及びゲート電極の表面に窒素が導入された状態で行うことにより、既に導入されている不純物の外方拡散を防止することができる。

20

#### 【0019】

##### 【発明の実施の形態】

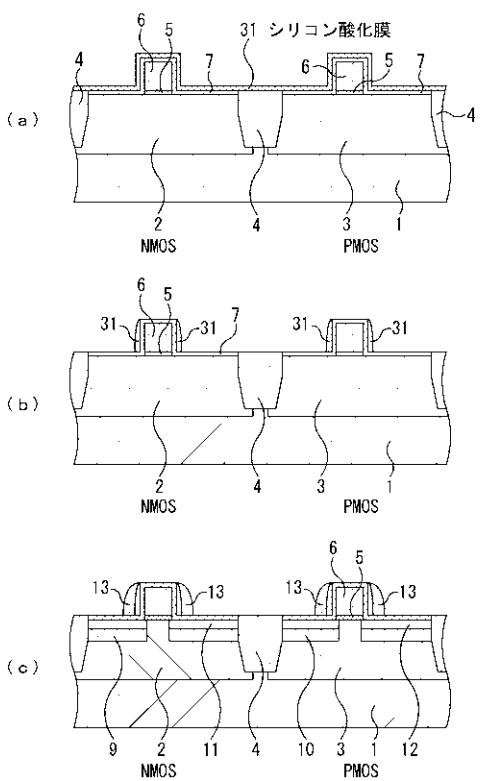

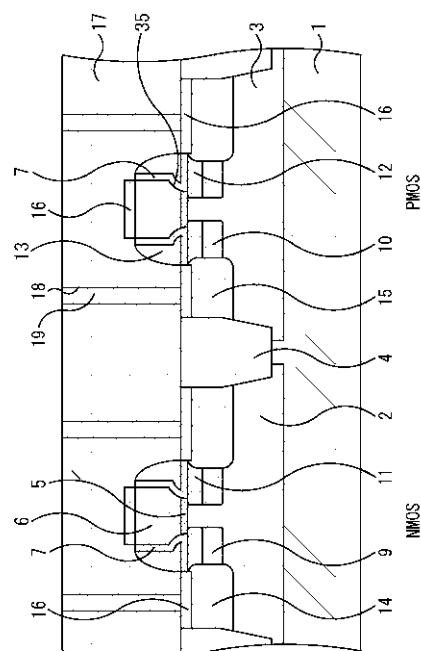

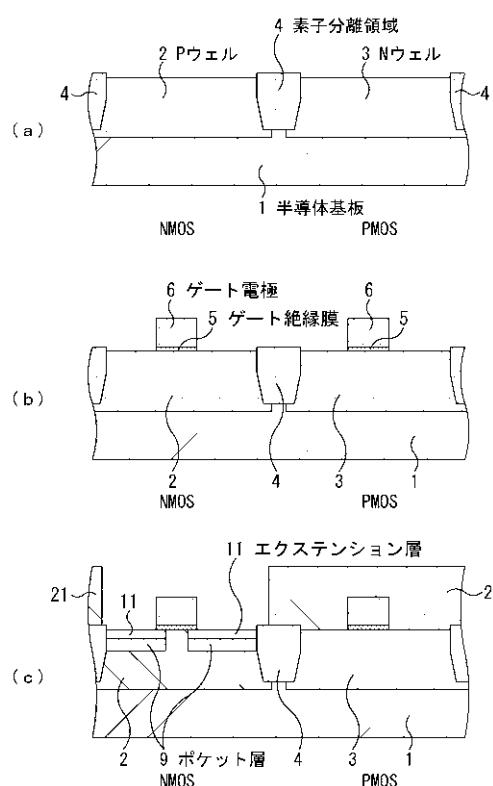

以下、本発明の実施の形態に係る半導体装置及びその製造方法について添付の図面を参照して具体的に説明する。図1乃至図5は、本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

#### 【0020】

第1の実施形態では、先ず、図1(a)に示すように、例えばP型のシリコン基板等の半導体基板1の表面に素子分離領域4を形成し、この素子分離領域4により区画された素子領域内にウェルを形成する。このとき、NチャネルMOS(NMOS)領域にはPウェル(チャネル)2を形成し、PチャネルMOS(PMOS)領域にはNウェル(チャネル)3を形成する。

30

#### 【0021】

次に、図1(b)に示すように、素子領域内において、半導体基板1上に絶縁膜及び多結晶シリコン膜を形成し、これらをパターニングすることにより、ゲート絶縁膜5及びゲート電極6を形成する。なお、ゲート絶縁膜5は、例えばシリコン酸窒化膜から構成されていることが好ましいが、シリコン酸化膜から構成されていてもよい。

#### 【0022】

次いで、図1(c)に示すように、Pウェル2及びNウェル3の表面並びにゲート電極6の上面及び側面に、膜厚が例えば3nm以下のシリコン窒化膜(窒素導入層)7を形成する。シリコン窒化膜7は、例えば、マグнетロンRIE装置を使用して、窒素ガスを含むプラズマに、Pウェル2及びNウェル3の表面並びにゲート電極6の上面及び側面を晒すことにより形成することができる。このときの条件として、例えば、ガス圧を10mTorr(約 $1.33 \times 10^{-1}$ Pa)とし、RFパワーを100Wとし、N<sub>2</sub>流量を50sccmとし、処理時間を2秒間とし、処理温度を15としてよい。また、マグネットロンRIE装置を使用して、窒素とアルゴンとの混合ガスを含むプラズマに、Pウェル2及びNウェル3の表面並びにゲート電極6の上面及び側面を晒すことによりシリコン窒化膜7を形成してもよい。また、他の成膜方法として、リモートプラズマ装置を使用して、窒素を含むガス(例えば、窒素とヘリウムとの混合ガス)を含むラジカルに、Pウェル2及

40

50

びNウェル3の表面並びにゲート電極6の上面及び側面を晒すことによりシリコン窒化膜7を形成してもよい。このときの条件としては、例えば、処理温度を550乃至800とし、処理時間を30乃至60秒間とし、パワーを3kWとし、窒素とヘリウムとの混合比をHe:90体積%、N<sub>2</sub>:10体積%としてもよい。

【0023】

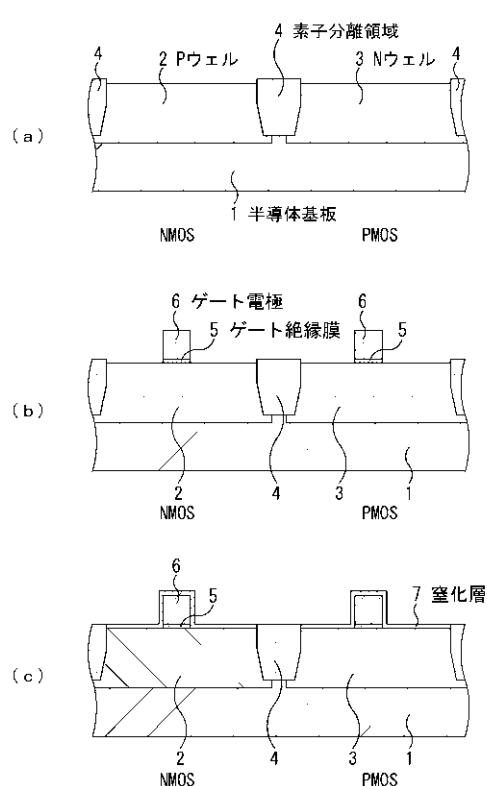

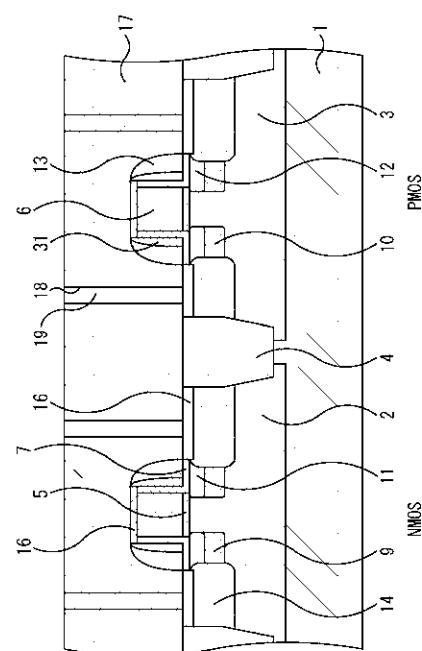

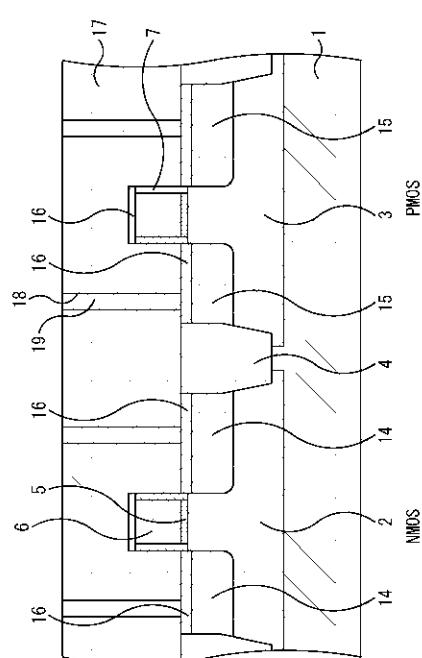

その後、図2(a)に示すように、全面に順次シリコン酸化膜8a及びシリコン窒化膜8bを順次形成する。

【0024】

続いて、図2(b)に示すように、シリコン窒化膜8bに異方性エッティングを施すことにより、ゲート電極6の側方にのみシリコン窒化膜8bを残す。

10

【0025】

次に、シリコン酸化膜8aにウェット処理を施す。この結果、図2(c)に示すように、シリコン酸化膜8a及びシリコン窒化膜8bからなる積層膜の下端部が除去されて、ノッチ8が形成される。

【0026】

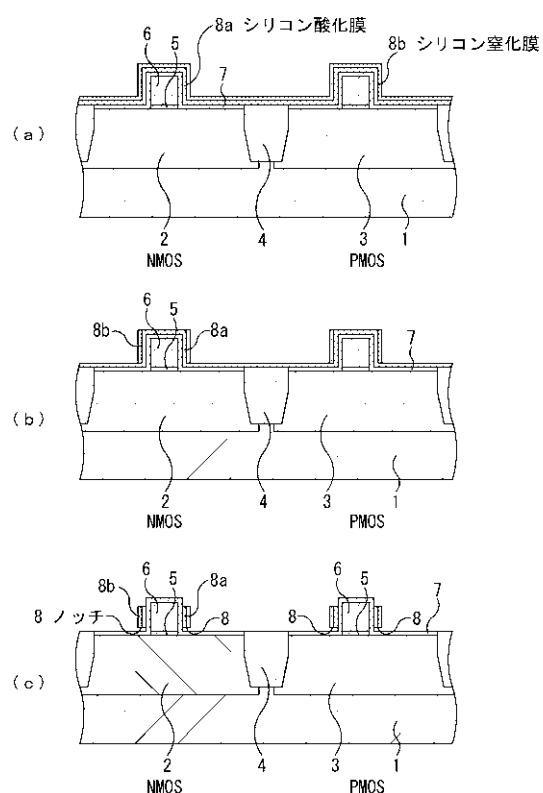

次いで、図3(a)に示すように、PMOS領域を覆いNMOS領域を露出するレジスト膜21を半導体基板1上に形成する。そして、このレジスト膜21及びゲート電極6をマスクとして、P型不純物、例えばインジウム及びボロンをイオン注入することにより、Pウェル2の表面にP型のポケット層9を形成する。このイオン注入は、例えば平面視で互いに直交する4方向からの斜めイオン注入により行う。また、インジウムのイオン注入においては、例えば、注入エネルギーを60乃至90keVとし、ドーズ量を $5 \times 10^{12}$ 乃至 $1.2 \times 10^{13} \text{ cm}^{-2}$ とする。ボロンのイオン注入においては、例えば、注入エネルギーを8乃至12keVとし、ドーズ量を $2 \times 10^{12}$ 乃至 $7 \times 10^{12} \text{ cm}^{-2}$ とする。これらのイオン注入の後、レジスト膜21を除去し、アニールを行うことにより、注入された不純物を活性化させる。このアニールは、例えばN<sub>2</sub>雰囲気下での950乃至1050のスパイクアニールとしてもよい。レジスト膜21の除去では、例えばアッシング処理及びウェット処理を行う。アッシング処理では、例えば、ダウンフローの装置で、O<sub>2</sub>の流量を1000sccm、CF<sub>4</sub>の流量を10sccm、フォーシングガスの流量を600sccmとし、処理温度を250とする。また、ウェット処理では、例えば硫酸過水を使用する。以下のレジスト膜の除去も、同様の方法により行うことができる。

20

【0027】

その後、図3(b)に示すように、NMOS領域を覆いPMOS領域を露出するレジスト膜22を半導体基板1上に形成する。そして、このレジスト膜22及びゲート電極6をマスクとして、N型不純物、例えばアンチモンをイオン注入することにより、Nウェル3の表面にN型のポケット層10を形成する。このイオン注入は、例えば平面視で互いに直交する4方向からの斜めイオン注入により行う。また、例えば、注入エネルギーを50乃至70keVとし、ドーズ量を $1.0 \times 10^{13}$ 乃至 $1.5 \times 10^{13} \text{ cm}^{-2}$ とする。このイオン注入の後、レジスト膜22を除去する。

30

【0028】

続いて、図3(c)に示すように、PMOS領域を覆いNMOS領域を露出するレジスト膜23を半導体基板1上に形成する。そして、このレジスト膜23、ゲート電極6、シリコン酸化膜8a及びシリコン窒化膜8bをマスクとして、N型不純物、例えば砒素をイオン注入することにより、ポケット層9の表面にN型のエクステンション層11を形成する。このイオン注入は、例えば半導体基板1の表面に垂直な方向から行う。また、例えば、注入エネルギーを2乃至4keVとし、ドーズ量を $1.0 \times 10^{15}$ 乃至 $1.5 \times 10^{15} \text{ cm}^{-2}$ とする。このイオン注入の後、レジスト膜23を除去し、アニールを行うことにより、注入された不純物を活性化させる。このアニールは、例えばN<sub>2</sub>雰囲気下での950乃至1050のスパイクアニールとしてもよい。

40

【0029】

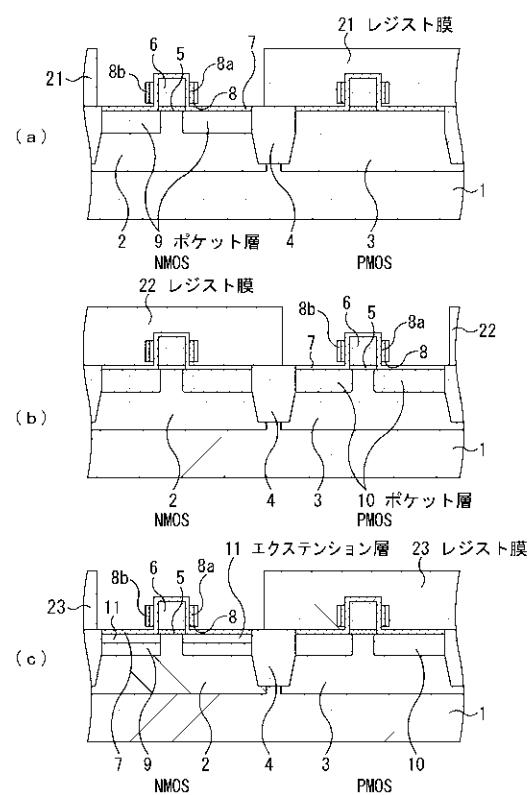

次に、図4(a)に示すように、NMOS領域を覆いPMOS領域を露出するレジスト膜

50

24を半導体基板1上に形成する。そして、このレジスト膜24、ゲート電極6、シリコン酸化膜8a及びシリコン窒化膜8bをマスクとして、P型不純物、例えばボロンをイオン注入することにより、ポケット層10の表面にP型のエクステンション層12を形成する。このイオン注入は、例えば半導体基板1の表面に垂直な方向から行う。また、例えば、注入エネルギーを0.2乃至0.4keVとし、ドーズ量を $1.0 \times 10^{15}$ 乃至 $1.5 \times 10^{15} \text{ cm}^{-2}$ とする。このイオン注入の後、レジスト膜24を除去する。

#### 【0030】

次いで、全面に絶縁膜、例えばシリコン酸化膜を形成した後、ゲート電極6の側方にのみこの絶縁膜が残るよう、異方性エッチングを施すことにより、図4(b)に示すように、サイドウォール13を形成する。シリコン酸化膜8a及びシリコン窒化膜8bは、例えばサイドウォール13に覆われる。

#### 【0031】

その後、図4(c)に示すように、PMOS領域を覆いNMOS領域を露出するレジスト膜25を半導体基板1上に形成する。そして、このレジスト膜25、ゲート電極6及びサイドウォール13をマスクとして、N型不純物、例えば燐を高濃度でイオン注入することにより、Pウェル2の表面にN型の深いソース・ドレイン拡散層14を形成する。このイオン注入は、例えば半導体基板1の表面に垂直な方向から行う。また、例えば、注入エネルギーを5乃至9keVとし、ドーズ量を $5 \times 10^{15}$ 乃至 $8 \times 10^{15} \text{ cm}^{-2}$ とする。このイオン注入の後、レジスト膜25を除去する。

#### 【0032】

続いて、図5(a)に示すように、NMOS領域を覆いPMOS領域を露出するレジスト膜26を半導体基板1上に形成する。そして、このレジスト膜26、ゲート電極6及びサイドウォール13をマスクとして、P型不純物、例えばボロンを高濃度でイオン注入することにより、Nウェル3の表面にP型の深いソース・ドレイン拡散層15を形成する。このイオン注入は、例えば半導体基板1の表面に垂直な方向から行う。また、例えば、注入エネルギーを2乃至5keVとし、ドーズ量を $3 \times 10^{15}$ 乃至 $5 \times 10^{15} \text{ cm}^{-2}$ とする。このイオン注入の後、レジスト膜26を除去する。このレジスト膜26の除去の後、アニールを行うことにより、注入された不純物を活性化させる。このアニールは、例えばN<sub>2</sub>雰囲気下での1025乃至1070のスパイクアニールとしてもよい。

#### 【0033】

次に、図5(b)に示すように、露出しているシリコン窒化膜7を除去し、コバルトシリサイド層等のシリサイド層16を、ゲート電極6並びにソース・ドレイン拡散層14及び15上に形成する。

#### 【0034】

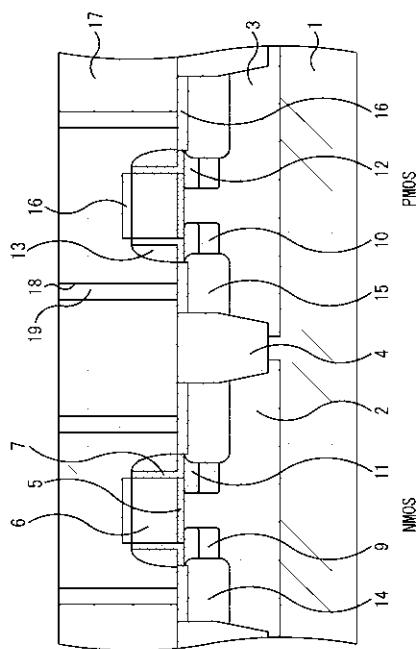

そして、図5(c)に示すように、層間絶縁膜17の形成、この層間絶縁膜17に対するソース・ドレイン拡散層14及び15まで到達するコンタクトホール18の開口、及びこのコンタクトホール18への導電材19の埋め込み、配線の形成等を行ってCMOSトランジスタを完成させる。

#### 【0035】

このようにして製造された半導体装置は、図5(c)に示す構造を備えている。

#### 【0036】

このような本発明の第1の実施形態によれば、ゲート電極6の形成(図1(b))と、ソース・ドレイン拡散層14及び15における不純物の活性化のためのアニール(図5(b))との間に、少なくともゲート電極6の側面並びにPウェル2及びNウェル3の表面にシリコン窒化膜7を形成しているので、アニールによっても、チャネル内の不純物の外方拡散並びにソース・ドレイン拡散層14及び15内の不純物の外方拡散を抑制することができる。このため、従来のような空乏化を抑制することができる。

#### 【0037】

また、ポケット層の形成、エクステンション層の形成及びソース・ドレイン拡散層の形成の度にレジスト膜の形成及び除去を行っているが、これらを行う前に少なくともPウェル

10

20

30

40

50

2 及び N ウェル 3 の表面にシリコン窒化膜 7 を形成しているので、レジスト膜の除去のためのアッシング又はウェット処理の際にも、P ウェル 2 及び N ウェル 3 の表面（半導体基板 1 の表面）は酸化されない。このため、不純物の減少並びに濃度及びプロファイルの変動が防止される。また、エクステンション層の沈み込みも発生しないため、浅い接合を確保することができる。

## 【 0 0 3 8 】

更に、ノッチ 8 を形成した後に、ポケット層を半導体基板 1 の表面に対して傾斜した方向からのイオン注入により形成し、エクステンション層を半導体基板 1 の表面に対して垂直な方向からのイオン注入により形成しているため、平面視において、ポケット層とゲート電極とのオーバーラップを広く確保しながら、エクステンション層とゲート電極とのオーバーラップを狭く抑えることができる。

## 【 0 0 3 9 】

次に、本発明の第 2 の実施形態について説明する。第 2 の実施形態では、2 重サイドウォール構造を CMOS トランジスタに適用する。図 6 は、本発明の第 2 の実施形態に係る半導体装置の製造方法を工程順に示す断面図であり、図 7 は、本発明の第 2 の実施形態により製造された CMOS トランジスタを示す断面図である。

## 【 0 0 4 0 】

第 2 の実施形態においては、先ず、第 1 の実施形態と同様にして、素子分離領域 4 の形成（図 1（a））からシリコン窒化膜 7 の形成（図 1（c））までの工程を行う。

## 【 0 0 4 1 】

次に、図 6（a）に示すように、全面に順次シリコン酸化膜 3 1 を順次形成する。

## 【 0 0 4 2 】

次いで、図 6（b）に示すように、シリコン酸化膜 3 1 に異方性エッティングを施すことにより、ゲート電極 6 の側方にのみシリコン酸化膜 3 1 を残す。

## 【 0 0 4 3 】

その後、第 1 の実施形態と同様にして、レジスト膜 2 1 の形成（図 3（a））からエクステンション層 1 2 の形成（図 4（a））までの工程を行う。

## 【 0 0 4 4 】

続いて、全面に絶縁膜、例えばシリコン酸化膜を形成した後、ゲート電極 6 の側方にのみこの絶縁膜が残るよう、異方性エッティングを施すことにより、図 6（c）に示すように、サイドウォール 1 3 を形成する。シリコン酸化膜 3 1 は、例えばサイドウォール 1 3 に覆われる。

## 【 0 0 4 5 】

そして、第 1 の実施形態と同様にして、レジスト膜 2 5 の形成（図 4（c））以降の工程を行うことにより、図 7 に示す CMOS トランジスタを完成させる。

## 【 0 0 4 6 】

このような第 2 の実施形態によっても、第 1 の実施形態と同様に、外方拡散の抑制及びレジスト膜を除去する際の半導体基板 1 の酸化の防止という効果が得られる。

## 【 0 0 4 7 】

次に、本発明の第 3 の実施形態について説明する。第 3 の実施形態では、ゲート電極にノッチが形成された構造を CMOS トランジスタに適用する。図 8 乃至図 9 は、本発明の第 3 の実施形態に係る半導体装置の製造方法を工程順に示す断面図であり、図 10 は、本発明の第 3 の実施形態により製造された CMOS トランジスタを示す断面図である。

## 【 0 0 4 8 】

第 3 の実施形態においては、先ず、第 1 の実施形態と同様にして、素子分離領域 4、P ウェル 2 及び N ウェル 3 の形成（図 1（a））の工程を行う。

## 【 0 0 4 9 】

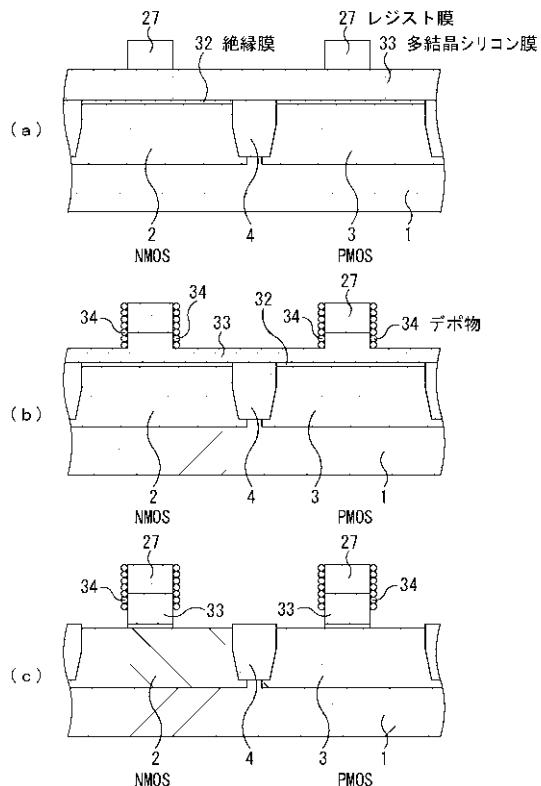

次に、図 8（a）に示すように、素子領域内において、半導体基板 1 上に絶縁膜 3 2 及び多結晶シリコン膜 3 3 を形成し、この多結晶シリコン膜 3 3 上に、ゲート電極を形成する領域を覆うレジスト膜 2 7 を形成する。

10

20

30

40

50

## 【0050】

次いで、レジスト膜27をマスクとし、HBr及びO<sub>2</sub>を含むガスを用いて多結晶シリコン膜33の上部をエッティングする。但し、このエッティングは、エッティングにより発生するデポ物が、多結晶シリコン膜33の上部のエッティング後に残る部位の側面に付着しやすい条件で行う。このようなエッティングの結果、図8(b)に示すように、デポ物34が残存する。

## 【0051】

その後、レジスト膜27をマスクとして、多結晶シリコン膜33の下部をエッティングする。但し、このエッティングは、エッティングにより発生するデポ物が、多結晶シリコン膜33の下部のエッティング後に残る部位の側面に付着しにくい条件で行う。このようなエッティングの結果、図8(c)に示すように、デポ物34は多結晶シリコン膜33の上部及びレジスト膜27の側面に残存する。

10

20

20

## 【0052】

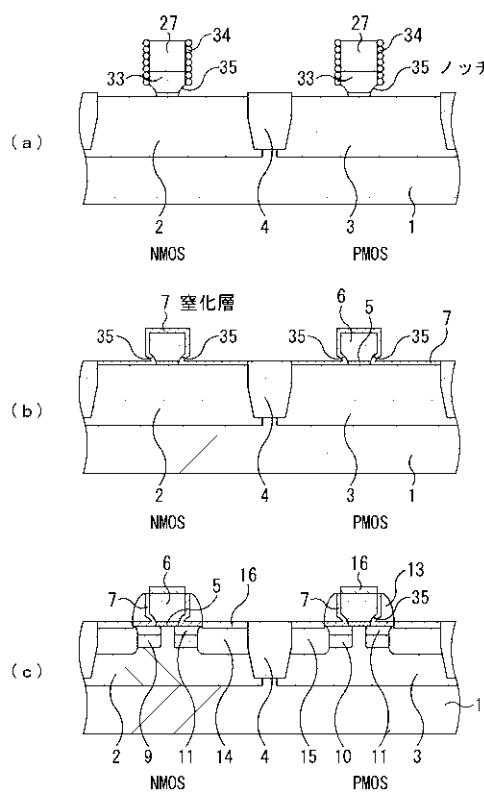

続いて、レジスト膜27をマスクとして、多結晶シリコン膜33の等方性エッティングを行う。この等方性エッティングにおいては、多結晶シリコン膜33の上部は厚いデポ物34に保護されているため、ほとんど除去されない。一方、多結晶シリコン膜34の下部にはほとんどデポ物34が付着していないので、この僅かなデポ物34が除去された後、多結晶シリコン膜33の下部の除去が進行する。この結果、図9(a)に示すように、ゲート絶縁膜5の縁部及びゲート電極6の下縁部に、テープ状のノッチ35が形成される。ゲート電極6は、残存する多結晶シリコン膜33及びデポ物34から構成される。

20

## 【0053】

次に、Pウェル2及びNウェル3の表面、ゲート電極6の上面及び側面並びにノッチ35の側面に、図9(b)に示すように、膜厚が例えば3nm以下のシリコン窒化膜7を形成する。シリコン窒化膜7は、第1の実施形態と同様にして形成することができる。

## 【0054】

その後、第1の実施形態と同様にして、レジスト膜21の形成(図3(a))からエクステンション層12の形成(図4(a))までの工程を行う。

30

## 【0055】

続いて、全面に絶縁膜、例えばシリコン酸化膜を形成した後、ゲート電極6の側方にのみこの絶縁膜が残るよう、異方性エッティングを施すことにより、図9(c)に示すように、サイドウォール13を形成する。

30

## 【0056】

そして、第1の実施形態と同様にして、レジスト膜25の形成(図4(c))以降の工程を行うことにより、図10に示すCMOSトランジスタを完成させる。

## 【0057】

このような第3の実施形態によっても、第1の実施形態と同様に、外方拡散の抑制及びレジスト膜を除去する際の半導体基板1の酸化の防止という効果が得られる。

## 【0058】

次に、本発明の第4の実施形態について説明する。第4の実施形態では、所謂シングルドレイン構造をCMOSトランジスタに適用したものである。図11は、本発明の第4の実施形態に係る半導体装置の製造方法により製造されたCMOSトランジスタを示す断面図である。

40

## 【0059】

図11に示すCMOSトランジスタにおいては、図5(c)に示すCMOSトランジスタと比較して、NチャネルMOSトランジスタ及びPチャネルMOSトランジスタのいずれにおいても、ソース・ドレイン領域に、ポケット層及びエクステンション層が形成されていない。また、サイドウォール13も形成されていない。

## 【0060】

このような構成のCMOSトランジスタは、図1乃至図5に示す工程において、ポケット層又はエクステンション層を形成する工程及びこれに付随するマスクの形成及び除去に關

50

する工程を省略することにより、形成することができる。但し、図1(c)に示すシリコン窒化膜7を形成する工程が必須の工程であることはいうまでもない。

【0061】

このような第4の実施例によつても、第1の実施形態と同様に、外方拡散の抑制及びレジスト膜を除去する際の半導体基板1の酸化の防止という効果が得られる。

【0062】

次に、本発明の第5の実施例について説明する。第5の実施例では、ノッチ8又は32が存在しない構造をCMOSトランジスタに適用したものである。図12は、本発明の第5の実施形態に係る半導体装置の製造方法を工程順に示す断面図であり、図13は、本発明の第4の実施形態により製造されたCMOSトランジスタを示す断面図である。

10

【0063】

第5の実施形態においては、先ず、第1の実施形態と同様にして、素子分離領域4の形成(図1(a))からシリコン窒化膜7の形成(図1(c))までの工程を行う。

【0064】

次に、図2(a)乃至(c)に示す工程を行うことなく、図12(a)に示すように、レジスト膜21を形成する。そして、このレジスト膜21及びゲート電極6をマスクとして、P型のポケット層9の形成及びN型のエクステンション層11の形成を行う。

【0065】

次いで、図12(b)に示すように、レジスト膜21を除去し、レジスト膜22を形成する。そして、このレジスト膜22及びゲート電極6をマスクとして、N型のポケット層10の形成及びP型のエクステンション層12の形成を行う。

【0066】

その後、レジスト膜22を除去し、第1の実施形態と同様にして、サイドウォール13の形成(図4(b))以降の工程を行うことにより、図13に示すCMOSトランジスタを完成させる。

【0067】

このような第5の実施形態によつても、第1の実施形態と同様に、外方拡散の抑制及びレジスト膜を除去する際の半導体基板1の酸化の防止という効果が得られる。

【0068】

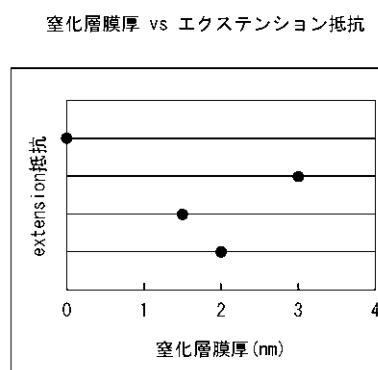

なお、本発明においては、窒化膜の厚さは3nm以下であること、特に2nmであること 30 が好ましい。図14は、窒化膜の厚さとエクステンション層の抵抗(extension resistance)との関係を示すグラフ図である。図14に示すように、窒化膜の存在により、エクステンション層の抵抗が低くなるが、窒化膜の厚さが厚くなりすぎると、エクステンション層の抵抗が上昇する傾向がある。従って、窒化膜の厚さは3nm以下であることが好ましい。

【0069】

なお、上述の実施形態に示されたCMOSトランジスタは、インバータ等に適用することが可能である。但し、本発明に係る半導体装置は、CMOSトランジスタへの適用に限定されるものではない。

【0070】

また、上述の実施形態では、レジスト膜をマスクとしてイオン注入を行つてはいるが、ステンシルマスクを用いてイオン注入を行う場合にも、本発明は有効である。これは、ステンシルマスクを用いる場合には、レジスト膜の除去という工程は必要ないが、従来の方法では、アニールに伴うチャネルの空乏化が発生する虞があるためである。

【0071】

以下、本発明の諸態様を付記としてまとめて記載する。

【0072】

(付記1) 一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材料からなるゲート絶縁膜と、

40

該ゲート絶縁膜上に形成されたゲート電極と、

50

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板に形成され、該一導電型とは異なる反対導電型の一

対の不純物層と、

を有することを特徴とする半導体装置。

【0073】

(付記2) 一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材

料からなるゲート絶縁膜と、

該ゲート絶縁膜上に形成されたゲート電極と、

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板に形成され、該一導電型とは異なる反対導電型の一

対の不純物層と、 10

該ゲート電極に自己整合して該半導体基板に形成された、一対の一導電型不純物層と、

を有することを特徴とする半導体装置。

【0074】

(付記3) 前記第1の窒素導入層を介して、前記ゲート電極の側面及び前記半導体基板

上に形成されたサイドウォールを有することを特徴とする付記1又は2に記載の半導体裝

置。 20

【0075】

(付記4) 一導電型の半導体基板上に形成され、シリコン酸化膜よりも誘電率が高い材

料からなるゲート絶縁膜と、

該ゲート絶縁膜上に形成されたゲート電極と、

該ゲート電極の側壁に形成された第1の窒素導入層と、

該ゲート電極の両側で、該半導体基板から第1の深さに形成され、該一導電型とは異なる

第1の反対導電型不純物層と、

該ゲート電極に自己整合して該半導体基板に形成された、一対の一導電型不純物層と、

該第1の窒素導入層を介して、該ゲート電極の側面に形成されたサイドウォールと、

該サイドウォール及び該ゲート電極に自己整合して該半導体基板に形成され、該半導体基

板から該第1の深さよりも深い第2の深さに形成された、第2の反対導電型不純物層と、

を有することを特徴とする半導体装置。 30

【0076】

(付記5) 前記サイドウォールと前記半導体基板との間に形成された、第2の窒素導入

層を有することを特徴とする付記3又は4に記載の半導体装置。

【0077】

(付記6) 前記第2の反対導電型不純物層が形成された前記半導体基板の表面に、シリ

サイド層を有することを特徴とする付記5に記載の半導体装置。

【0078】

(付記7) 前記ゲート絶縁膜は、シリコン酸化膜を含むことを特徴とする付記1乃至

6のいずれか1項に記載の半導体装置。

【0079】

(付記8) 一導電型の半導体基板上に、シリコン酸化膜よりも誘電率が高い材料からな

るゲート絶縁膜を形成する工程と、 40

該ゲート絶縁膜を介してゲート電極を形成する工程と、

該半導体基板及び該ゲート電極の表面に、窒素を導入する工程と、

次いで、該ゲート電極の両側の該半導体基板に、該一導電型とは異なる反対導電型の一

対の不純物層を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【0080】

(付記9) 一導電型の半導体基板上に、一導電型領域及び該一導電型とは異なる反対導

電型の反対導電型領域を形成する工程と、

該一導電型領域上に、シリコン酸化膜よりも誘電率が高い材料からなる第1のゲート絶縁 50

膜を形成する工程と、

該反対導電型領域上に、第2のゲート絶縁膜を形成する工程と、

該第1のゲート絶縁膜上に第1のゲート電極を形成する工程と、

該第2のゲート絶縁膜上に第2のゲート電極を形成する工程と、

該第1及び第2のゲート電極の表面に、窒素を導入する工程と、

次いで、該反対導電型領域を選択的に覆う第1のマスク層を形成する工程と、該第1のゲート電極及び該第1のマスク層をマスクにして、該第1のゲート電極の両側の該半導体基板に、該反対導電型の不純物層を形成する工程と、

次いで、該第1のマスク層を除去する工程と、

次いで、該一導電型領域を選択的に覆う第2のマスク層を形成する工程と、

該第2のゲート電極及び該第2のマスク層をマスクにして、該第2のゲート電極の両側の該半導体基板に、該一導電型の不純物層を形成する工程と、

次いで、第2のマスク層を除去する工程と、

を含むことを特徴とする半導体装置の製造方法。

#### 【0081】

(付記10) 前記窒素を導入する工程は、窒素を導入する予定の領域を、窒素を含むガスのプラズマ又はラジカルに晒す工程を含むことを特徴とする付記8又は9に記載の半導体装置の製造方法。

#### 【0082】

(付記11) 一導電型の半導体基板上にゲート絶縁膜を形成する工程と、

該ゲート絶縁膜を介してゲート電極を形成する工程と、

該半導体基板及び該ゲート電極の表面に、窒素を含むガスのプラズマ又はラジカルに晒して、窒素を導入する工程と、

次いで、該ゲート電極の両側の該半導体基板に、該一導電型とは異なる反対導電型の一対の不純物層を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

#### 【0083】

(付記12) 該窒素を導入する工程の後に、該ゲート電極の両側の該半導体基板に、該一導電型の不純物層を形成する工程を含むことを特徴とする付記8乃至11に記載の半導体装置の製造方法。

#### 【0084】

(付記13) 該窒素を導入する工程の後に、該窒素を導入する工程により形成された窒素を含む層を介して、該ゲート電極の側面にサイドウォールを形成する工程を有することを特徴とする付記8乃至12のいずれか1項に記載の半導体装置の製造方法。

#### 【0085】

(付記14) 該窒素を導入する工程により形成される窒素を含む層の厚さを3nm以下とすることを特徴とする付記8乃至13のいずれか1項に記載の半導体装置の製造方法。

#### 【0086】

(付記15) 該ゲート絶縁膜をシリコン酸窒化膜から形成することを特徴とする付記8乃至14のいずれか1項に記載の半導体装置の製造方法。

#### 【0087】

(付記16) 前記不純物層の表面にシリサイド層を形成する工程を含むことを特徴とする付記8乃至15のいずれか1項に記載の半導体装置の製造方法。

#### 【0088】

#### 【発明の効果】

以上詳述したように、本発明よれば、ゲート絶縁膜及びゲート電極を形成した後に窒素の導入を行っているので、その後にレジスト膜の形成及び除去を行ったとしても、窒素が導入された領域の酸化を防止することができる。また、アニールの実施を、窒素が導入された状態で行うことにより、既に導入されている不純物の外方拡散を防止することができる。従って、従来の方法で生じていたようなチャネルの空乏化を防止することができる。こ

10

20

30

40

50

これらの結果、良好な特性の半導体装置を得ることができる。

【図面の簡単な説明】

【図 1】本発明の第 1 の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 2】同じく、本発明の第 1 の実施形態に係る半導体装置の製造方法を工程順に示す図であって、図 1 に示す工程の次工程を示す断面図である。

【図 3】同じく、本発明の第 1 の実施形態に係る半導体装置の製造方法を工程順に示す図であって、図 2 に示す工程の次工程を示す断面図である。

【図 4】同じく、本発明の第 1 の実施形態に係る半導体装置の製造方法を工程順に示す図であって、図 3 に示す工程の次工程を示す断面図である。

【図 5】同じく、本発明の第 1 の実施形態に係る半導体装置の製造方法を工程順に示す図であって、図 4 に示す工程の次工程を示す断面図である。

【図 6】本発明の第 2 の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 7】本発明の第 2 の実施形態により製造された C M O S トランジスタを示す断面図である。

【図 8】本発明の第 3 の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 9】同じく、本発明の第 3 の実施形態に係る半導体装置の製造方法を工程順に示す図であって、図 8 に示す工程の次工程を示す断面図である。

【図 10】本発明の第 3 の実施形態により製造された C M O S トランジスタを示す断面図である。

【図 11】本発明の第 4 の実施形態に係る半導体装置の製造方法により製造された C M O S トランジスタを示す断面図である。

【図 12】本発明の第 5 の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 13】本発明の第 4 の実施形態により製造された C M O S トランジスタを示す断面図である。

【図 14】窒化膜の厚さとエクステンション層の抵抗 ( e x t e n s i o n 抵抗 ) との関係を示すグラフである。

【図 15】C M O S トランジスタの従来の製造方法を工程順に示す断面図である。

【図 16】同じく、C M O S トランジスタの従来の製造方法を工程順に示す図であって、図 15 に示す工程の次工程を示す断面図である。

【図 17】同じく、C M O S トランジスタの従来の製造方法を工程順に示す図であって、図 16 に示す工程の次工程を示す断面図である。

【符号の説明】

1 ; 半導体基板

2 ; P ウェル

3 ; N ウェル

4 ; 素子分離領域

5 ; ゲート絶縁膜

6 ; ゲート電極

7 ; 窒化膜

8 ; ノッチ

8 a ; シリコン酸化膜

8 b ; シリコン窒化膜

9、10 ; ポケット層

11、12 ; エクステンション層

13 ; サイドウォール

14、15 ; ソース・ドレイン拡散層

10

20

30

40

50

- 1 6 ; シリサイド層

1 7 ; 層間絶縁膜

1 8 ; コンタクトホール

1 9 ; 導電材

2 1 、 2 2 、 2 3 、 2 4 、 2 5 、 2 6 、 2 7 ; レジスト膜

3 1 ; シリコン酸化膜

3 2 ; 絶縁膜

3 3 ; 多結晶シリコン膜

3 4 ; デポ物

3 5 ; ノッチ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【図9】

【 図 1 0 】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

## フロントページの続き

F ターム(参考) 5F140 AA00 AA10 AA21 AB03 BA01 BD09 BF01 BF04 BF11 BF18

BF51 BG08 BG09 BG10 BG12 BG14 BG34 BG45 BG50 BG52

BG53 BG54 BG58 BH14 BH21 BH36 BJ01 BJ08 BJ11 BJ15

BK02 BK10 BK13 BK25 BK34 CB01 CB08 CF04