(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6145203号

(P6145203)

(45) 発行日 平成29年6月7日(2017.6.7)

(24) 登録日 平成29年5月19日(2017.5.19)

(51) Int.Cl.

F 1

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| HO 1 L 29/786 | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| HO 1 L 21/20  | (2006.01) | HO 1 L | 29/78 | 6 2 0   |

| HO 1 L 29/41  | (2006.01) | HO 1 L | 29/78 | 6 2 6 A |

| HO 1 L 29/417 | (2006.01) | HO 1 L | 21/20 |         |

|               |           | HO 1 L | 29/44 | L       |

請求項の数 2 (全 39 頁) 最終頁に続く

(21) 出願番号 特願2016-143366 (P2016-143366)

(22) 出願日 平成28年7月21日 (2016.7.21)

(62) 分割の表示 特願2014-256927 (P2014-256927)

の分割

原出願日 平成22年11月16日 (2010.11.16)

(65) 公開番号 特開2016-201562 (P2016-201562A)

(43) 公開日 平成28年12月1日 (2016.12.1)

審査請求日 平成28年8月2日 (2016.8.2)

(31) 優先権主張番号 特願2009-265028 (P2009-265028)

(32) 優先日 平成21年11月20日 (2009.11.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 河江 大輔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

酸化物半導体膜と、

前記酸化物半導体膜の下方の、第1の電極と、

前記酸化物半導体膜の上方の、第2の電極と、

前記酸化物半導体膜の側面及び上面の、絶縁膜と、を有し、

前記酸化物半導体膜の側面側の表層部は、結晶領域を有し、

前記結晶領域は、前記酸化物半導体膜の側面側の表面に対して、垂直な方向と沿うように、c軸が配向した結晶を有することを特徴とする半導体装置。

## 【請求項 2】

酸化物半導体膜と、

前記酸化物半導体膜の下方の、第1の電極と、

前記酸化物半導体膜の上方の、第2の電極と、

前記酸化物半導体膜の側面及び上面の、絶縁膜と、を有し、

前記酸化物半導体膜の側面側の表層部は、結晶領域を有し、

前記結晶領域は、前記酸化物半導体膜の側面側の表面に対して、垂直な方向と沿うように、c軸が配向した結晶を有し、

前記酸化物半導体膜の側面側の表層部のキャリア移動度は、他の部分のキャリア移動度より高くなることを特徴とする半導体装置。

## 【発明の詳細な説明】

10

20

**【技術分野】****【0001】**

開示する発明の技術分野は、酸化物半導体を用いたトランジスタ及び当該トランジスタを有する半導体装置に関するものである。

**【背景技術】****【0002】**

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタは液晶テレビに代表されるような表示装置に用いられている。薄膜トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が公知であるが、その他の材料として酸化物半導体が注目されている。

10

**【0003】**

酸化物半導体の材料としては、酸化亜鉛又は酸化亜鉛を成分とするものが知られている。そして、電子キャリア密度が  $10^{18} \text{ cm}^{-3}$  未満である非晶質酸化物（酸化物半導体）なるもので形成された薄膜トランジスタが開示されている（特許文献1乃至3）。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2006-165527号公報

【特許文献2】特開2006-165528号公報

【特許文献3】特開2006-165529号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

ところで、大電力用途の半導体装置に用いるトランジスタは、高耐圧、高変換効率、高速スイッチングなどの特性が必要となる。現在、これらの半導体装置の半導体材料としてはシリコンが採用されているが、上述の観点から、さらなる特性の向上が可能な新たな半導体材料が求められている。

**【0006】**

上述の諸特性を向上させる可能性がある半導体材料としては、例えば、炭化シリコンを挙げることができる。炭化シリコンは、Si-C結合の原子間距離が約0.18nmと短く、結合エネルギーが高く、シリコンと比較して約3倍と大きなバンドギャップを有するため、半導体装置の耐圧向上、電力損失の低減などに有利であることが知られている。

30

**【0007】**

ところが、炭化シリコンは、その性質上溶融させることができないため、シリコンウェハを製造する際に用いられるチョクラルスキー法（CZ法）などの生産性の高い方法を用いて製造することができないという問題がある。また、炭化シリコンには、マイクロバイブと呼ばれる欠陥の問題が存在する。これらの問題から、炭化シリコンを用いた半導体装置の実用化は遅れている。

**【0008】**

上述に鑑み、開示する発明の一態様では、生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供することを目的の一とする。

40

**【課題を解決するための手段】****【0009】**

本発明の一形態は、酸化物半導体中で電子供与体（ドナー）となりうる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい酸化物半導体でチャネル形成領域が形成される縦型トランジスタであり、酸化物半導体の厚さが  $1 \mu\text{m}$  以上、好ましくは  $3 \mu\text{m}$  より大、より好ましくは  $10 \mu\text{m}$  以上であり、酸化物半導体に接する電極の一方の端部が、酸化物半導体の端部より内側にあることを特徴とする。

50

## 【0010】

また、本発明の一形態は、酸化物半導体中で電子供与体（ドナー）となりうる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい酸化物半導体でチャネル形成領域が形成される縦型トランジスタであり、酸化物半導体の厚さが $1 \mu\text{m}$ 以上、好ましくは $3 \mu\text{m}$ より大、より好ましくは $10 \mu\text{m}$ 以上であり、酸化物半導体に接する電極の一方の端部が、酸化物半導体の端部より内側にあり、酸化物半導体においてゲート絶縁膜に接する領域に結晶領域が形成される。

## 【0011】

すなわち、本発明の一形態は、酸化物半導体に含まれる水素を低減し、好ましくは水素濃度を $1 \times 10^{-6} \text{ cm}^{-3}$ 以下とし、酸化物半導体に含まれる水素若しくはOH基を除去し、キャリア密度を $1 \times 10^{-4} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{-2} \text{ cm}^{-3}$ 未満、さらに好ましくは測定限界以下の $1 \times 10^{-1} \text{ cm}^{-3}$ 未満とした酸化物半導体膜でチャネル形成領域が形成される縦型トランジスタである。

10

## 【0012】

酸化物半導体のバンドギャップは $2 \text{ eV}$ 以上、好ましくは $2.5 \text{ eV}$ 以上、より好ましくは $3 \text{ eV}$ 以上として、ドナー水素等の不純物を極力低減し、キャリア密度を $1 \times 10^{-4} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{-2} \text{ cm}^{-3}$ 未満、さらに好ましくは測定限界以下の $1 \times 10^{-1} \text{ cm}^{-3}$ 未満となるようにする。

## 【0013】

20

このように高純度化された酸化物半導体を、トランジスタのチャネル形成領域に用いることで、ゲート絶縁膜と接する酸化物半導体の表面だけでなく、酸化物半導体の内部（酸化物半導体膜全体）においてもチャネルを形成することが可能である。また、オフ状態においては、空乏層が酸化物半導体の内部のより深い領域まで広がるため、オフ状態に流れるオフ電流を低減することができる。更には、耐圧が高くなると共に、ホットキャリア劣化が生じにくくなり、高電圧が印加される大電力用の半導体装置を作製することができる。

## 【0014】

なお、本発明の一形態において、トランジスタのゲート電極は、環状であり、ゲート絶縁膜を介して、ソース電極、酸化物半導体膜、及びドレイン電極を囲んでいる。このため、チャネル幅は大きい。

## 【0015】

30

また、本発明の一形態のトランジスタは、絶縁ゲート電界効果トランジスタ（Insulated-Gate Field-Effect Transistor (IGFET)）、パワーMOSFETを含む。

## 【発明の効果】

## 【0016】

本発明の一形態によれば、水素濃度が低減され高純度化された酸化物半導体を用いることで、トランジスタの動作を良好なものとすることができる。特に、耐圧を高め、ショートチャネル効果を抑制し、オンオフ比を高めることができる。このため、当該トランジスタを用いることで、大電力用の半導体装置を作製することができる。

## 【図面の簡単な説明】

40

## 【0017】

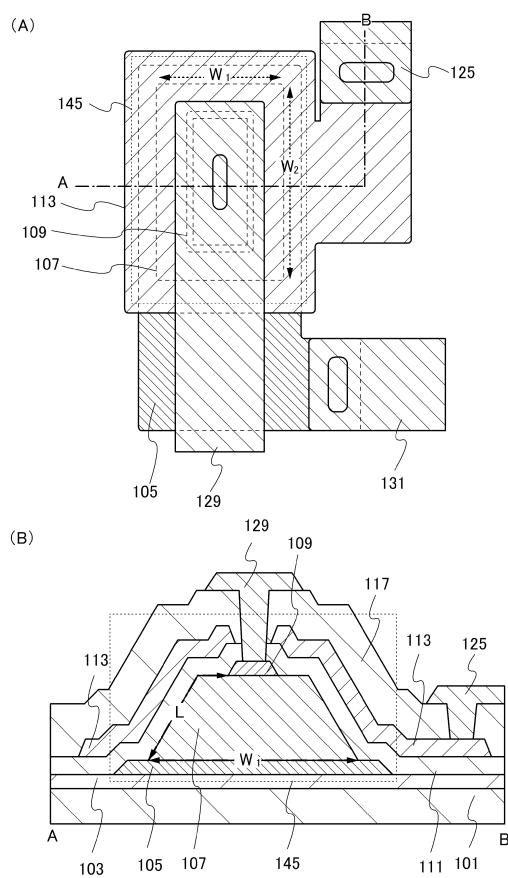

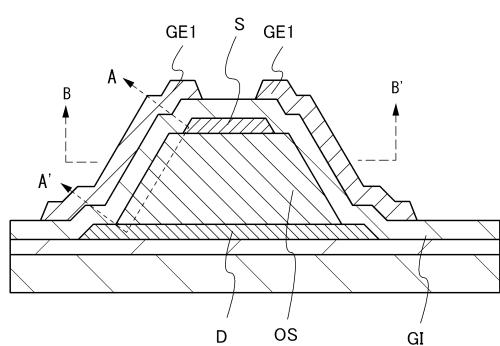

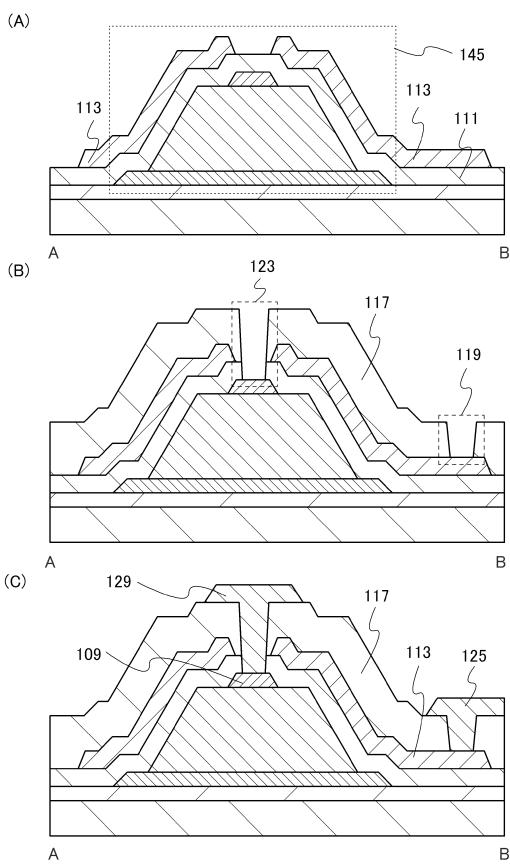

【図1】トランジスタを説明する上面図及び断面図である。

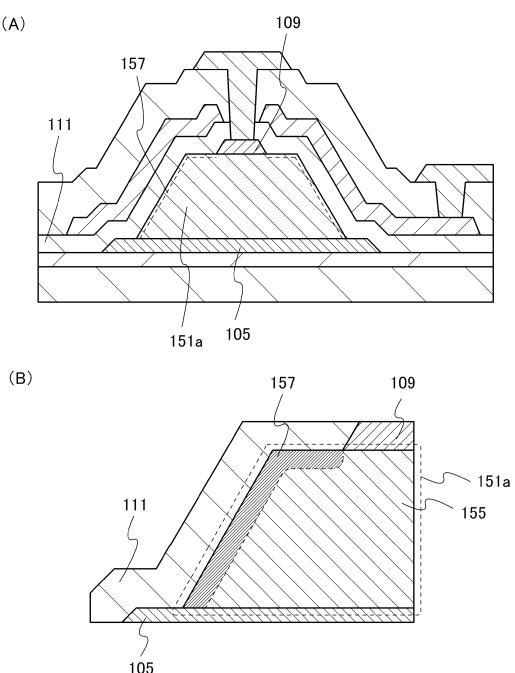

【図2】トランジスタを説明する断面図である。

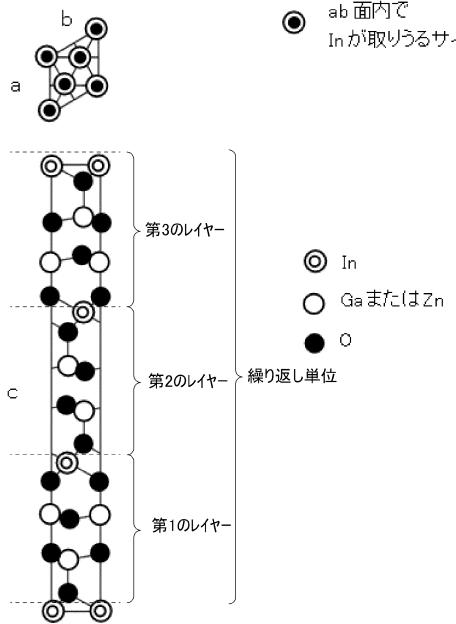

【図3】InGaZnO<sub>4</sub>の結晶構造を示す図である。

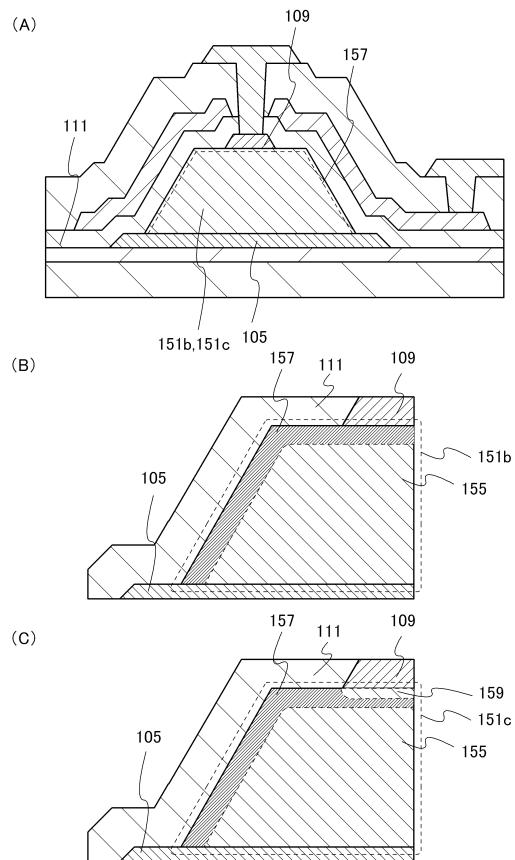

【図4】トランジスタを説明する断面図である。

【図5】酸化物半導体を用いた縦型のトランジスタの縦断面図である。

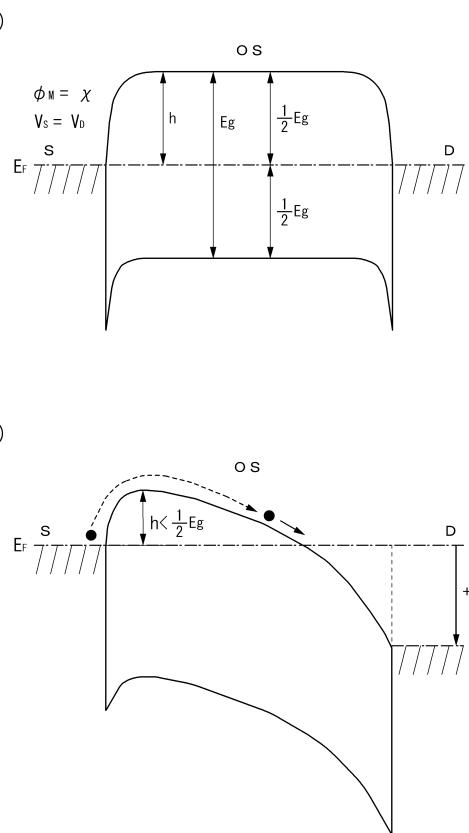

【図6】図5に示すA-A'断面におけるエネルギー・バンド図（模式図）である。

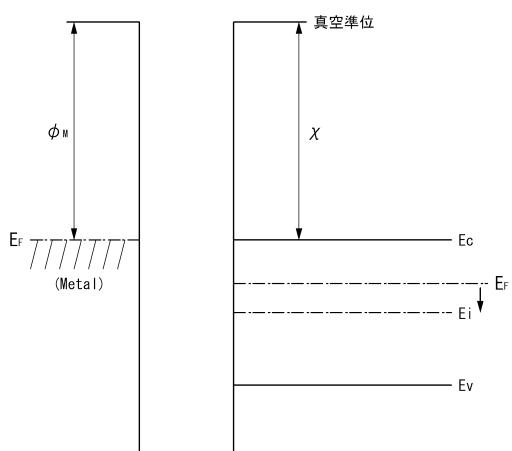

【図7】真空準位と金属の仕事関数（M）、酸化物半導体の電子親和力（）の関係を示す図である。

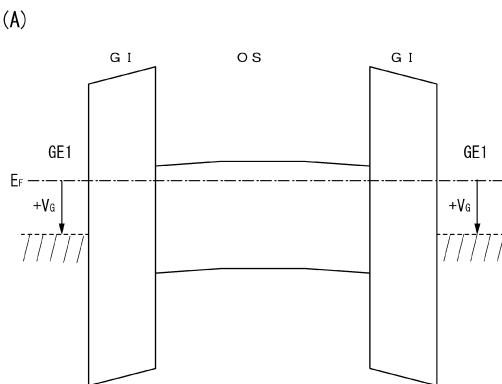

【図8】図5におけるB-B'の断面におけるエネルギー・バンド図である。

50

【図9】(A)ゲート(G1)に正の電位(+VG)が印加された状態を示し、(B)ゲート(G1)に負の電位(-VG)が印加された状態を示す図である。

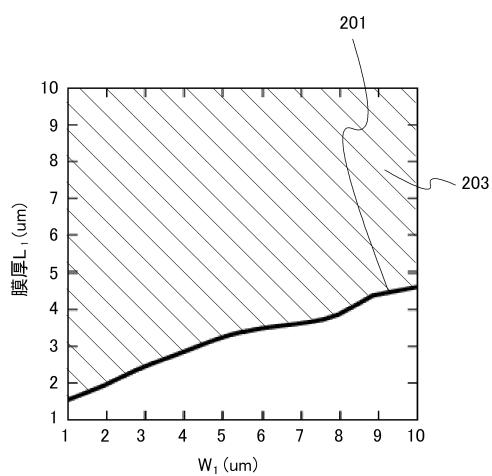

【図10】最大空乏層幅及びデバイ長の計算結果を説明する図である。

【図11】トランジスタの作製方法を説明する断面図である。

【図12】トランジスタの作製方法を説明する断面図である。

【図13】トランジスタの作製方法を説明する断面図である。

【図14】トランジスタの作製方法を説明する断面図である。

【図15】デバイスシミュレータにより計算した結果を説明する図である。

【図16】デバイスシミュレータにより計算した結果を説明する図である。

【図17】デバイスシミュレータにより計算した結果を説明する図である。

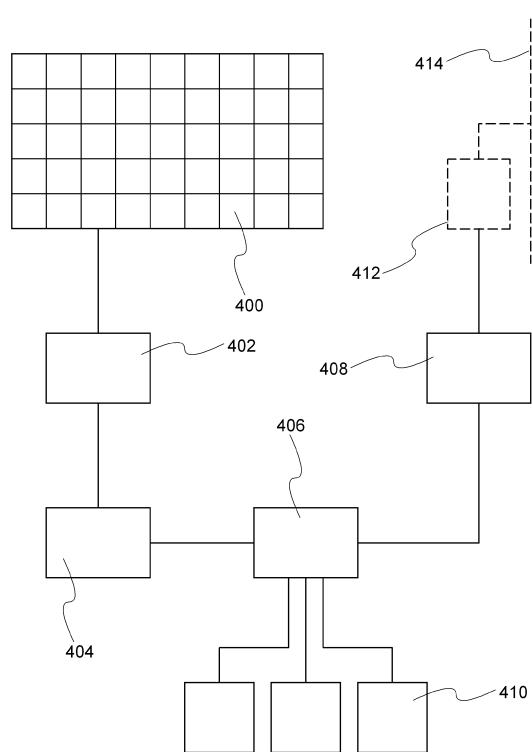

【図18】太陽光発電システムの一例を説明する図である。

【図19】CV測定を説明する図である。

【図20】CV測定の結果を説明する図である。

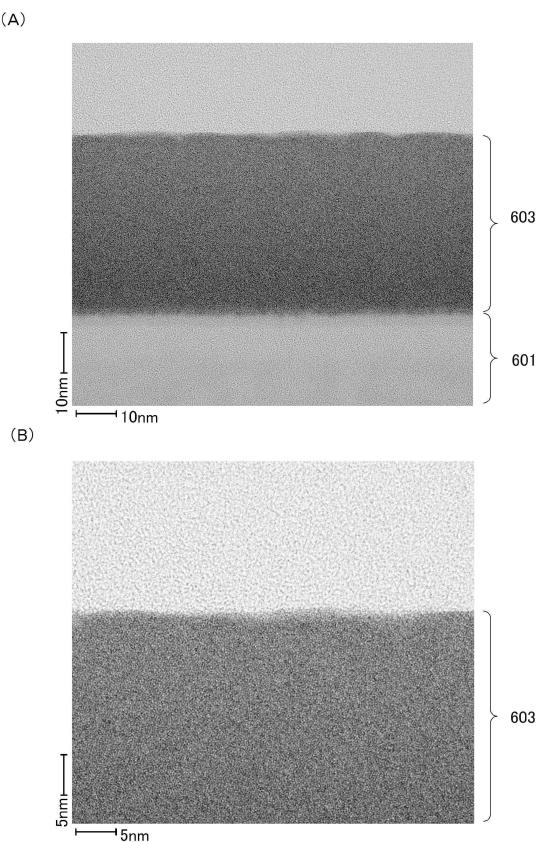

【図21】酸化物半導体膜の断面TEM写真である。

【図22】酸化物半導体膜の断面TEM写真である。

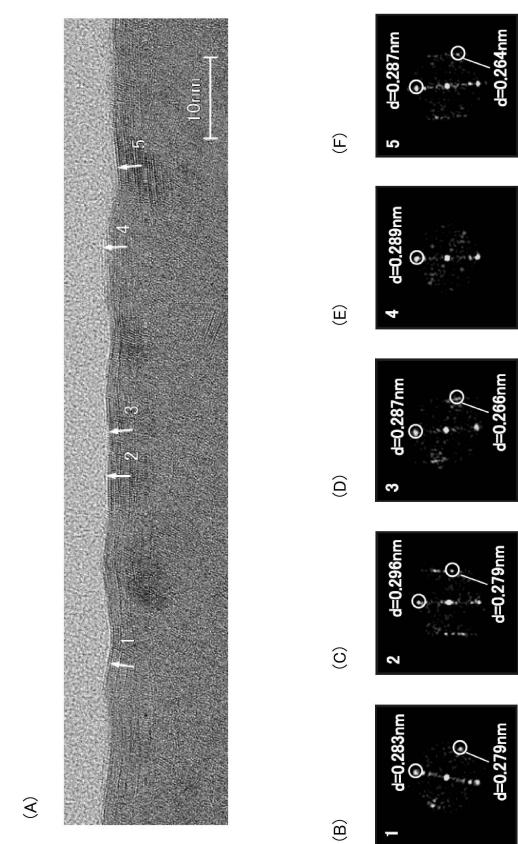

【図23】酸化物半導体膜の断面TEM写真及び電子線回折パターンである。

【発明を実施するための形態】

【0018】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0019】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0020】

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

【0021】

また、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー(電気的な位置エネルギー)のことをいう。ただし、一般的に、ある一点における電位と基準となる電位(例えば接地電位)との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。

【0022】

(実施の形態1)

本実施の形態では、トランジスタの構造について、図1を用いて説明する。

【0023】

図1(A)はトランジスタ145の上面図であり、図1(B)は図1(A)の一点鎖線A-Bの断面図に相当する。

【0024】

図1(B)に示すように、基板101上に形成された絶縁膜103上に、第1の電極105、酸化物半導体膜107、及び第2の電極109が積層される。なお、第2の電極109の端部は、酸化物半導体膜107端部の内側に位置する。また、第1の電極105、酸化物半導体膜107、及び第2の電極109を覆うように、ゲート絶縁膜111が設けら

10

20

30

40

50

れている。ゲート絶縁膜 111 上には、少なくとも酸化物半導体膜及び第 2 の電極の側面と対向するように、第 3 の電極 113 が設けられている。ゲート絶縁膜 111 及び第 3 の電極 113 上には層間絶縁膜として機能する絶縁膜 117 が設けられている。絶縁膜 117 上には、開口部が形成されており、開口部において第 1 の電極 105 と接続する配線 131 (図 1 (A) 参照)、第 2 の電極 109 と接続する配線 129、第 3 の電極 113 と接続する配線 125 が形成される。なお、本明細書においては、膜の上面とは、基板 101 と平行な一対の面において、基板 101 と反対側に設けられる面のことをいう。

#### 【0025】

第 1 の電極 105 は、トランジスタ 145 のソース電極及びドレイン電極の一方として機能する。第 2 の電極 109 は、トランジスタ 145 のソース電極及びドレイン電極の他方として機能する。第 3 の電極 113 は、トランジスタ 145 のゲート電極として機能する。

10

#### 【0026】

本実施の形態では、ゲート電極として機能する第 3 の電極 113 が環状であることを特徴とする。ゲート電極として機能する第 3 の電極 113 を環状とすることで、トランジスタのチャネル幅を大きくすることができる。本実施の形態のトランジスタにおいて、チャネル長 L は、断面構造において、酸化物半導体膜がゲート絶縁膜と接する領域における、第 1 の電極 105 及び第 2 の電極 109 方向の距離である。また、チャネル幅 W は第 1 の電極または第 2 の電極に接する酸化物半導体膜の端部の長さである。なお、ここでは、第 1 の電極または第 2 の電極において、面積の広い方と酸化物半導体膜の接する酸化物半導体膜の端部の長さを W とする。本実施の形態では、トランジスタの酸化物半導体膜の上面形状は  $W_1$  と  $W_2$  を辺とする長方形であるため、チャネル幅 W は  $2W_1$  及び  $2W_2$  の和である。なお、トランジスタの酸化物半導体膜の上面形状が円形の場合は、酸化物半導体膜の半径 r とした場合、チャネル幅 W は  $2\pi r$  である。

20

#### 【0027】

また、酸化物半導体膜 107 の厚さが、1 μm 以上、好ましくは 3 μm より大、より好ましくは 10 μm 以上である。

#### 【0028】

また、本実施の形態のトランジスタは、酸化物半導体膜が真性であり、真性キャリア密度がきわめて低いため、最大空乏層幅が極めて広くなり、空乏層が酸化物半導体膜の内部に広がるトランジスタとなる。

30

#### 【0029】

なお、トランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル形成領域を有しており、ドレイン領域とチャネル形成領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件などによって変わるために、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインとよばない場合がある。その場合、一例としては、それぞれを第 1 の端子、第 2 の端子と表記する場合がある。あるいは、それぞれを第 1 の電極、第 2 の電極と表記する場合がある。あるいは、第 1 の領域、第 2 の領域と表記する場合がある。

40

#### 【0030】

基板 101 は、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。基板 101 としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

#### 【0031】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 ℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。一般に酸化ホウ素 ( $B_2O_3$ ) と比較して酸化バリウム ( $BaO$ ) を多く含ませること

50

で、より実用的な耐熱ガラスが得られる。このため、B<sub>2</sub>O<sub>3</sub>よりBaOを多く含むガラス基板を用いることが好ましい。

【0032】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラス基板などを用いることができる。

【0033】

絶縁膜103は、酸化シリコン膜、酸化窒化シリコン膜など酸化物絶縁膜、または窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、または窒化酸化アルミニウムなどの窒化物絶縁膜で形成する。また、絶縁膜103は積層構造でもよく、例えば、基板101側から上記した窒化物絶縁膜のいずれか一つ以上と、上記した酸化物絶縁膜のいずれか一つ以上との積層構造とすることができる。10

【0034】

第1の電極105及び第2の電極109は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチルから選ばれた金属元素、または上述した金属元素を成分とする合金、上述した金属元素を組み合わせた合金などで形成する。また、マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか一または複数から選択された金属元素を用いることができる。また、第1の電極105は、単層構造、または二層以上の積層構造とすることができる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タンクスチル膜上にチタン膜を積層する二層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などが挙げられる。また、アルミニウムに、チタン、タンタル、タンクスチル、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を単数、または複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。20

【0035】

また、第1の電極105及び第2の電極109として、インジウム錫酸化物、酸化タンクスチルを含むインジウム酸化物、酸化タンクスチルを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。30

【0036】

酸化物半導体膜107としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O膜や、三元系金属酸化物であるIn-Ga-Zn-O膜、In-Sn-Zn-O膜、In-Al-Zn-O膜、Sn-Ga-Zn-O膜、Al-Ga-Zn-O膜、Sn-Al-Zn-O膜や、二元系金属酸化物であるIn-Zn-O膜、Sn-Zn-O膜、Al-Zn-O膜、Zn-Mg-O膜、Sn-Mg-O膜、In-Mg-O膜や、In-O膜、Sn-O膜、Zn-O膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜中にSiO<sub>2</sub>を含んでもよい。

【0037】

また、酸化物半導体膜107は、InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される構造の酸化物半導体膜のうち、MとしてGaを含む構造の酸化物半導体を、上記したIn-Ga-Zn-O酸化物半導体とよび、その薄膜をIn-Ga-Zn-O膜ともよぶこととする。40

【0038】

本実施の形態で用いる酸化物半導体膜107は、酸化物半導体膜に含まれる水素を低減し、好ましくは、酸化物半導体膜に含まれる水素が除去されている。即ち、酸化物半導体膜の主成分以外の不純物が極力含まれないように高純度化されている。このときの酸化物半導体膜107の水素濃度は、1×10<sup>-6</sup>cm<sup>-3</sup>以下が好ましい。また、酸化物半導体

膜 107 のキャリア密度が  $1 \times 10^{14} \text{ cm}^{-3}$  未満、好ましくは  $1 \times 10^{12} \text{ cm}^{-3}$  未満、さらに好ましくは測定限界以下の  $1 \times 10^{11} \text{ cm}^{-3}$  未満である。即ち、酸化物半導体膜のキャリア密度は、限りなくゼロに近い。また、バンドギャップは 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である。なお、酸化物半導体膜中の水素濃度測定は、二次イオン質量分析法 (S I M S : Secondary Ion Mass Spectroscopy) で行うことができる。キャリア密度は、ホール効果測定により測定することができる。

#### 【 0039 】

酸化物半導体膜 107 の厚さは、1  $\mu\text{m}$  以上、好ましくは 3  $\mu\text{m}$  より大、より好ましくは 10  $\mu\text{m}$  以上とする。酸化物半導体膜 107 の厚さを厚くすることで、ショートチャネル効果 (しきい値の変動、オンオフ比の低減) を低減することができ、大電力用の半導体装置を作製することができる。

10

#### 【 0040 】

ゲート絶縁膜 111 は、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、または酸化アルミニウム膜を単層または積層して形成することができる。ゲート絶縁膜 111 は、酸化物半導体膜 107 と接する部分が酸素を含むことが好ましく、特に好ましくは酸化シリコン膜により形成する。酸化シリコン膜を用いることで、酸化物半導体膜 107 に酸素を供給することができ、特性を良好にすることができます。

#### 【 0041 】

また、ゲート絶縁膜 111 として、ハフニウムシリケート ( $\text{HfSiO}_x$  ( $x > 0$ ))、N が添加されたハフニウムシリケート ( $\text{HfSiO}_x\text{N}_y$  ( $x > 0$ ,  $y > 0$ ))、ハフニウムアルミネート ( $\text{HfAlO}_x$  ( $x > 0$ ))、酸化ハフニウム、酸化イットリウムなどの  $h_i g h - k$  材料を用いることでゲートリーク電流を低減できる。さらには、 $h_i g h - k$  材料と、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、または酸化アルミニウム膜のいずれか一以上との積層構造とすることができます。ゲート絶縁膜 111 の厚さは、50 nm 以上 500 nm 以下とするとい。ゲート絶縁膜 111 の厚さを厚くすることで、ゲートリーク電流を低減することができる。

20

#### 【 0042 】

ゲート電極として機能する第 3 の電極 113 は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金膜などを用いて形成することができる。また、マンガン、マグネシウム、ジルコニウム、ベリリウムのいずれか一または複数から選択された金属元素を用いてもよい。また、第 3 の電極 113 は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造などがある。また、アルミニウムに、チタン、タンタル、タンクステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

30

#### 【 0043 】

また、ゲート電極として機能する第 3 の電極 113 は、インジウム錫酸化物、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

40

#### 【 0044 】

次に、酸化物半導体膜 107 を有するトランジスタの動作についてエネルギーバンド図を用いて説明する。

#### 【 0045 】

50

図5は、酸化物半導体を用いた縦型のトランジスタの縦断面図を示す。ドレイン電極(D)上に酸化物半導体層(OS)が設けられ、酸化物半導体層(OS)上にソース電極(S)が設けられ、ドレイン電極、酸化物半導体層、及びソース電極上にゲート絶縁膜(GI)が設けられ、その上にゲート電極(GE1)が設けられている。

【0046】

図6は、図5に示すA-A'断面におけるエネルギーバンド図(模式図)を示す。図6(A)はソースとドレインの間の電圧を等電位(VD=0V)とした場合を示し、図6(B)は図5において、ゲート電圧に正の電圧(VG>0)を加え、ソースに対しドレインに正の電位(VD>0)を加えた場合を示す。

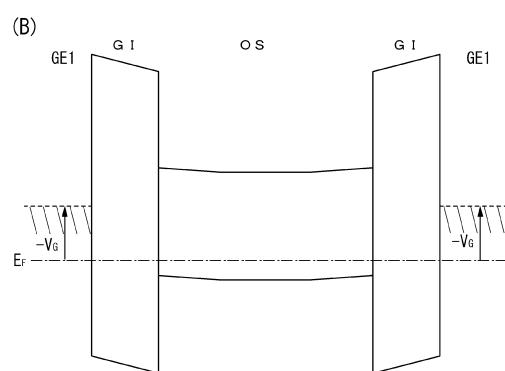

【0047】

図8は、図5におけるB-B'の断面におけるエネルギーバンド図(模式図)を示し、ゲート電圧が0Vの場合の状態を示す。図9(A)はゲート(G1)に正の電位(+VG)が印加された状態であり、ソース及びドレイン間にキャリア(電子)が流れるオン状態を示している。また、図9(B)は、ゲート(G1)に負の電位(-VG)が印加された状態であり、オフ状態である場合を示す。

【0048】

図7は、真空準位と金属の仕事関数(M)、酸化物半導体の電子親和力( )の関係を示す。

【0049】

室温において金属の自由電子縮退状態にあり、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は一般にn型であり、その場合のフェルミ準位(Ef)は、バンドギャップ中央に位置する真性フェルミ準位(Ei)から離れて、伝導帯寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなりn型化する一つの要因であることが知られている。

【0050】

これに対して本発明に係る酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性(i型)とし、又は真性型とせんとしたものである。すなわち、不純物を添加してi型化するのではなく、水素や水等の不純物を極力除去したことにより、高純度化されたi型(真性半導体)又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位(Ef)は真性フェルミ準位(Ei)と同じレベルにまですることができる。

【0051】

酸化物半導体のバンドギャップ(Eg)が3.15eVである場合、電子親和力( )は4.3eVと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力( )とほぼ等しい。この場合、金属-酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

【0052】

すなわち、金属の仕事関数(M)と酸化物半導体の電子親和力( )がほぼ等しい場合、両者が接触すると図6(A)で示すようなエネルギーバンド図(模式図)が示される。

【0053】

図6(B)において黒丸( )は電子を示し、ドレインに正の電位が印加されると、電子はバリア(h)をこえて酸化物半導体に注入され、ドレインに向かって流れる。この場合、バリア(h)の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加された場合には、電圧印加のない図6(A)のバリア(h)の高さすなわちバンドギャップ(Eg)の1/2よりもバリア(h)の高さは小さい値となる。

【0054】

酸化物半導体層の厚さは1μm以上、好ましくは3μmより大、より好ましくは10μm以上であり、また真性キャリア密度が少ない。このため、ゲート(G1)に正の電位(+VG)が印加された状態では、図9(A)に示すように、酸化物半導体層の表面におけるバンドの曲がりが少なく、伝導帯の下端がフェルミ準位に近づき、酸化物半導体層全体に

10

20

30

40

50

おいてエネルギー的に安定となる。このため、ゲート絶縁膜の近傍のみでなく、酸化物半導体全体においても電子が流れやすくなり、酸化物半導体全体にチャネルが形成され、より多くの電流を流すことができる。一方、ゲート(G1)に負の電位(-VG)が印加された状態では、少数キャリアであるホールは実質的にゼロであるため、電流は限りなく低く、チャネルの単位面積あたりの電流が100aA/μm以下、好ましくは10aA/μm以下、より好ましくは1aA/μm以下とゼロに近い値となる。

## 【0055】

ここで、酸化物半導体の真性キャリア密度について説明する。

## 【0056】

半導体に含まれる真性キャリア密度 $n_i$ は、フェルミ・ディラック統計によるフェルミ・ディラック分布をボルツマン分布の式で近似することで、求められる(式1参照)。

10

## 【0057】

## 【数1】

$$n_i = \sqrt{N_C N_V} \exp\left(-\frac{E_g}{2kT}\right)$$

## 【0058】

近似式により求められる真性キャリア密度 $n_i$ は、伝導帯における実効状態密度 $N_c$ 、価電子帯における実効状態密度 $N_v$ 、及びバンドギャップ $E_g$ の関係式であり、式1からシリコンの真性キャリア密度 $n_i$ は $1.4 \times 10^{10} \text{ cm}^{-3}$ 、酸化物半導体(ここでは、In-Ga-Zn-O膜)の真性キャリア密度 $n_i$ は $1.2 \times 10^{-7} \text{ cm}^{-3}$ となる。シリコンと比較して、酸化物半導体の真性キャリア密度が極端に低いことが分かる。

20

## 【0059】

次に、ゲート(G1)に負の電位(-VG)を印加した場合の空乏層幅及びデバイ長について、以下に説明する。

## 【0060】

ドナー密度 $N_d$ の半導体と、絶縁物と、金属とで構成されるMOSトランジスタに電圧を印加したときに、半導体中に形成される最大空乏層幅 $T_{D_{MAX}}$ は、式2で求められる。

30

## 【0061】

## 【数2】

$$T_{D_{MAX}} = \sqrt{\frac{2\epsilon_s \epsilon_0 (2\phi_F)}{qN_d}}$$

## 【0062】

最大空乏層幅はドナー密度及びフェルミポテンシャルの関数で表され、フェルミポテンシャル $\phi_F$ は式3で求められる。

## 【0063】

## 【数3】

$$\phi_F = \frac{kT}{q} \ln \frac{N_d}{n_i}$$

40

## 【0064】

また、MOSトランジスタのデバイ長 $L_D$ は式4で求められる。

## 【0065】

## 【数4】

$$L_D = \sqrt{\frac{\epsilon_s \epsilon_0 kT}{q^2 N_d}}$$

## 【0066】

なお、 $\epsilon_s$  は酸化物半導体の比誘電率、 $\epsilon_0$  は真空の誘電率、 $N_d$  はドナー密度、 $q$  は素電荷、 $k$  はボルツマン定数、 $T$  は温度を示す。

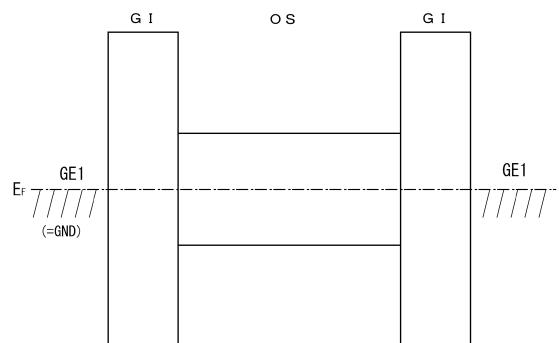

## 【0067】

シリコンの $n_i$  (真性キャリア密度) を $1.4 \times 10^{10} \text{ cm}^{-3}$ 、 $\epsilon_s$  を $11.9$  とし、酸化物半導体の $n_i$  を $1.2 \times 10^{-7} \text{ cm}^{-3}$ 、 $\epsilon_s$  を $10$  として、シリコンを用いたMOSトランジスタ、酸化物半導体を用いたトランジスタ、それぞれの最大空乏層幅、デバイ長を計算した結果を図10に示す。ここでトランジスタは、チャネルが基板表面に対して平行に形成される横型MOSトランジスタの構造を用いて計算した。また、ここで最大空乏層幅は、基板に対して垂直方向に広がる空乏層の幅に相当する。なお、横型トランジスタの空乏層の広がりは、縦型MOSトランジスタにおいても同様の傾向がみられるとしている。

## 【0068】

なお、シリコンの場合、ドナー密度は不純物 (P) の密度に相当する。酸化物半導体の場合、ドナーとしては酸素欠陥や水素が寄与する。

## 【0069】

図10 (A) は、ドナー密度が $1 \times 10^{12} \text{ cm}^{-3}$  から $1 \times 10^{18} \text{ cm}^{-3}$  までの範囲における酸化物半導体 (OSと示す。) 及びシリコン (Siと示す。) の最大空乏層幅及びデバイ長を示す。太実線161は酸化物半導体の最大空乏層幅を示し、太一点鎖線163はシリコンの最大空乏層幅を示す。また、細実線165は酸化物半導体のデバイ長を示し、細一点鎖線167はシリコンのデバイ長を示す。

## 【0070】

図10 (B) は、ドナー密度が $1 \times 10^{-5} \text{ cm}^{-3}$  から $1 \times 10^{-1} \text{ cm}^{-3}$  までの範囲における酸化物半導体の最大空乏層幅及びデバイ長を示す。なお、この密度範囲は、シリコンの真性キャリア密度 ( $n_i = 1.4 \times 10^{10} \text{ cm}^{-3}$ ) を下回るので、酸化物半導体のみの計算結果を示す。太実線は酸化物半導体の最大空乏層幅を示し、細実線は酸化物半導体のデバイ長を示す。

## 【0071】

図10より、ドナー密度が低いほど、最大空乏層が広がり、デバイ長が増大することが分かる。また、最大空乏層幅 $T_{D_{MAX}}$  は真性キャリア密度 $n_i$  に依存し、 $n_i$  が少ない酸化物半導体の方がシリコンよりも空乏層が広がることがわかる。また、酸化物半導体が $n$ 型から $i$ 型になればなるほど、即ちドナー密度 ( $N_d$ ) が低減するほど、図10 (B) に示すように、最大空乏層幅が数十 $\mu\text{m}$  から数千 $\mu\text{m}$ 、デバイ長が数 $\mu\text{m}$  から数百 $\mu\text{m}$  と大幅に増大し、空乏層が酸化物半導体全体に広がることがわかる。

## 【0072】

以上のことから、酸化物半導体は、バンドギャップが広く、真性キャリア密度が低いため、最大空乏層及びデバイ長が増大し、オフ状態においては酸化物半導体全体に空乏層が広がるため、オフ電流を低減することができ、限りなくゼロに近くなる。

## 【0073】

なお、このように酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性 ( $i$ 型) とし、又は実質的に真性型とすることで、ゲート絶縁膜との界面特性は顕在化する。そのためゲート絶縁膜は、酸化物半導体と良好な界面を形成できるものが好ましい。例えば、VHF帯～マイクロ波帯の電源周波数で生成される高密度プラズマを用いたCVD法で作製される緻密な絶縁膜、又はスパッタリング法で作製される絶縁膜を用いることが好ましい。さらには、ゲート絶縁膜とゲート電極との界面を良好にすること、ゲート絶縁膜の表面に、VHF帯～マイクロ波帯の電源周波数で生成される高密

10

20

30

40

50

度プラズマを用いたCVD法で作製される緻密な絶縁膜を形成してもよい。

【0074】

このように、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、オン電流が高く、オフ電流が低く、オンオフ比の高い、良好な動作特性を有するトランジスタとなる。

【0075】

ここで、酸化物半導体を用いたトランジスタのドレイン耐性について説明する。

【0076】

半導体中の電界があるしきい値に達すると、衝突イオン化が生じ、空乏層内で高電界により加速されたキャリアが結晶格子に衝突し、電子と正孔の対を生成する。さらに電界が高くなると、衝突イオン化により発生した電子と正孔の対もさらに電界によって加速され、衝突イオン化を繰り返し、電流が指数関数的に増加するアバランシェ降伏が生じる。衝突イオン化は、キャリア（電子、正孔）が半導体のバンドギャップ以上の運動エネルギーを有することにより発生する。衝突イオン化の起こりやすさを示す衝突イオン化係数とバンドギャップには相関があり、バンドギャップが大きいほど衝突イオン化係数が小さくなる傾向が知られている。

10

【0077】

酸化物半導体のバンドギャップは、3.15 eVであり、シリコンのバンドギャップの1.12 eVとくらべると、大きいため、アバランシェ降伏が起こりにくく期待される。このため、酸化物半導体を用いたトランジスタはドレイン耐圧が高くなり、高電界が印加されてもオン電流の指数関数的急上昇が生じにくく期待される。

20

【0078】

次に、酸化物半導体を用いたトランジスタのホットキャリア劣化について説明する。

【0079】

ホットキャリア劣化とは、高速に加速された電子がチャネル中のドレイン近傍でゲート酸化膜中に注入されて固定電荷となったり、ゲート絶縁膜界面にトラップ準位を形成することにより、しきい電圧の変動やゲートリーク等のトランジスタ特性の劣化が生じることであり、ホットキャリア劣化の要因としては、チャネルホットエレクトロン注入（CHE注入）とドレインアバランシェホットキャリア注入（DAHC注入）がある。

30

【0080】

シリコンはバンドギャップが狭いため、アバランシェ降伏によって雪崩的に電子が発生しやすく、ゲート絶縁膜への障壁を越えられるほど高速に加速される電子数が増加する。しかしながら、本実施の形態で示す酸化物半導体は、バンドギャップが広いため、アバランシェ降伏が生じにくく、シリコンと比べてホットキャリア劣化の耐性が高い。なお、高耐圧材料の一つであるシリコンカーバイドのバンドギャップと酸化物半導体のバンドギャップは同等であるため、SiCと同等の耐圧が期待される。

【0081】

以上のことから、酸化物半導体を用いたトランジスタはドレイン耐圧が高く、具体的には100V以上、好ましくは500V、好ましくは1kV以上のドレイン耐圧を有することが可能である。

40

【0082】

ここで、トランジスタの代表例であるシリコンカーバイドと酸化物半導体の比較について以下に示す。ここでは、シリコンカーバイドとして、4H-SiCを用いる。

【0083】

酸化物半導体と4H-SiCはいくつかの共通点を有している。真性キャリア密度はその一例である。常温におけるフェルミ・ディラック分布を用いると、酸化物半導体の真性キャリア密度は $10^{-7} \text{ cm}^{-3}$ 程度と見積もられるが、これは、4H-SiCにおける $6.7 \times 10^{-11} \text{ cm}^{-3}$ と同様、極めて低い値である。

【0084】

また、酸化物半導体のエネルギー・バンドギャップは3.0~3.5 eVであり、4H-S

50

i C のエネルギー・バンドギャップは  $3.26\text{ eV}$  であるから、ワイドギャップ半導体という点においても、酸化物半導体とシリコンカーバイドとは共通している。

#### 【0085】

しかしながら、酸化物半導体及びシリコンカーバイドにおいて、プロセス温度が大きく異なる。シリコンカーバイドは例えば  $1500 \sim 2000$  の活性化熱処理を必要とする。一方、酸化物半導体は、 $300 \sim 500$  (ガラス転移温度以下、最大でも  $700$  程度) の熱処理で作製することが可能であり、大面積基板上にトランジスタを作製することができる。また、スループットを高めることができる。

#### 【0086】

SiC - MOSFET の作製工程においては、ドナーまたはアクセプターとなりうる不純物 (リン、ボロン等) のドーピング工程、及び活性化のための高温熱処理工程を含む。ところで、酸化物半導体はその電子親和力が比較的大きい。そのため、適切な仕事関数を持つ金属を電極として選択することで、トランジスタ作製工程において不純物を添加しなくとも電極とのオーミック接触を形成することができ、コンタクト部に  $n^+$  領域を形成しやすい点で工程の簡略化を図れる。

10

#### 【0087】

なお、酸化物半導体において、バンドギャップ内の DOS (density of states) 等の物性研究は多くなされているが、これらの研究は、DOS そのものを十分に減らすという思想を含まない。本実施の形態では、エネルギー・ギャップ中の DOS の原因たり得る水や水素を酸化物半導体中より除去することで、高純度化した酸化物半導体を作製する。これは、DOS そのものを十分に減らすという思想に基づくものである。そして、これによって極めて優れた工業製品の製造を可能とするものである。

20

#### 【0088】

さらに、酸素欠乏により発生する金属の未結合手に対して酸素を供給し、酸素欠陥による DOS を減少させることにより、いっそう高純度化された (i型の) 酸化物半導体とすることも可能である。たとえば、チャネル形成領域に密接して酸素過剰の酸化膜を形成し、当該酸化膜から酸素を供給して、酸素欠陥による DOS を減少させることができる。

#### 【0089】

酸化物半導体の欠陥は、過剰な水素による伝導帯の下  $0.1 \sim 0.2\text{ eV}$  の浅い準位や、酸素の不足による深い準位、などに起因するものとされている。これらの欠陥を無くすために、水素を徹底的に除去し、酸素を十分に供給する、という技術思想は正しいものであろう。

30

#### 【0090】

また、酸化物半導体は一般に n型とされているが、本実施の形態では、不純物、特に水や水素を除去することにより i型化を実現する。この点、シリコンなどのように不純物を添加しての i型化ではなく、従来にない技術思想を含むものといえる。

#### 【0091】

また、酸化物半導体を i型化することにより、トランジスタの温度特性が良好であり、代表的には、-25 から 150 までの温度範囲において、トランジスタの電流電圧特性において、オン電流、オフ電流、電界効果移動度、S 値、及びしきい値電圧の変動がほとんどなく、温度による電流電圧特性の変動がほとんどない。

40

#### 【0092】

なお、本実施の形態で示す酸化物半導体を用いたトランジスタは、シリコンカーバイドを用いたトランジスタと比較して、チャネル移動度がやや低いが、ドレイン電圧を高くする、チャネル幅 (W) を大きくすることで、トランジスタの電流値を高め、デバイス特性を向上させることができる。

#### 【0093】

本実施の形態の技術思想は、酸化物半導体中に、さらに不純物を加えることをせずに、逆に不本意に存在する水、水素という不純物を意図的に除去することにより、酸化物半導体自体を高純度化することである。すなわち、ドナー準位を構成する水または水素を除去し

50

、さらに酸素欠陥を低減し、酸化物半導体を構成する主成分材料の酸素を十分に供給することにより、酸化物半導体を高純度化することである。

【0094】

酸化物半導体を成膜することで  $10^{20} \text{ cm}^{-3}$  のレベルの水素が SIMS (二次イオン質量分析) で測定される。このドナー準位の原因となる水または水素を意図的に除去し、さらに水または水素の除去に伴い同時に減少してしまう酸素 (酸化物半導体の成分の一つ) を酸化物半導体に加えることにより、酸化物半導体を高純度化し、電気的に  $i$  型 (真性) 半導体とする。

【0095】

また、本実施の形態においては、酸化物半導体中の水、水素の量は少なければ少ないほど好ましく、キャリアも少なければ少ないほど良い。すなわち、キャリア密度は  $1 \times 10^{14} \text{ cm}^{-3}$  未満、好ましくは  $1 \times 10^{12} \text{ cm}^{-3}$  未満、さらに好ましくは測定限界以下の  $1 \times 10^{11} \text{ cm}^{-3}$  未満が求められる。更には本実施の形態の技術思想的には、ゼロに近いまたはゼロが理想である。酸化物半導体のキャリアを低減し、好ましくは無くしてしまうことで、トランジスタにおいて酸化物半導体はソースから供給されたキャリア (電子) を通過させる通路 (パス) として機能させる。その結果、酸化物半導体は高純度化した  $i$  型 (真性) 半導体であり、キャリアがない、または極めて少なくせしめることにより、トランジスタのオフ状態ではオフ電流を極めて低くできるというのが本実施の形態の技術思想である。

【0096】

また、酸化物半導体は通路 (パス) として機能し、酸化物半導体自体がキャリアを有さない、または極めて少ないように高純度化した  $i$  型 (真性) とすると、キャリアは電極のソース、ドレインにより供給される。供給の程度は、酸化物半導体の電子親和力 およびフェルミレベル、理想的には真性フェルミレベルと一致したフェルミレベルとソース、ドレインの電極の仕事関数よりも、バリアハイド (障壁高さ) が主に寄与する。

【0097】

ところで、チャネルが基板と概略平行に形成される横型トランジスタにおいては、チャネルのほかにソース及びドレインを設ける必要があり、基板におけるトランジスタの占有面積が大きくなってしまい、微細化の妨げとなる。しかしながら、縦型トランジスタにおいては、ソース、チャネル、及びドレインを積層するため、基板表面における占有面積を低減することができる。この結果、トランジスタの微細化が可能である。

【0098】

このように、酸化物半導体膜の主成分以外の不純物、代表的には水素、水、水酸基または水素化物などが極力含まれないように高純度化することにより、トランジスタの動作を良好なものとすることができます。特に、耐圧を高め、ショートチャネル効果を抑制し、オンオフ比を高めることができます。

【0099】

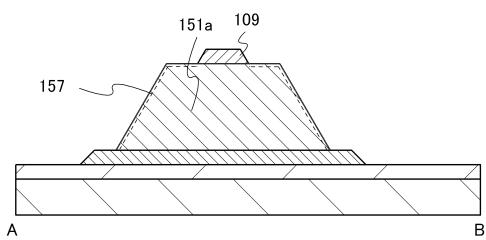

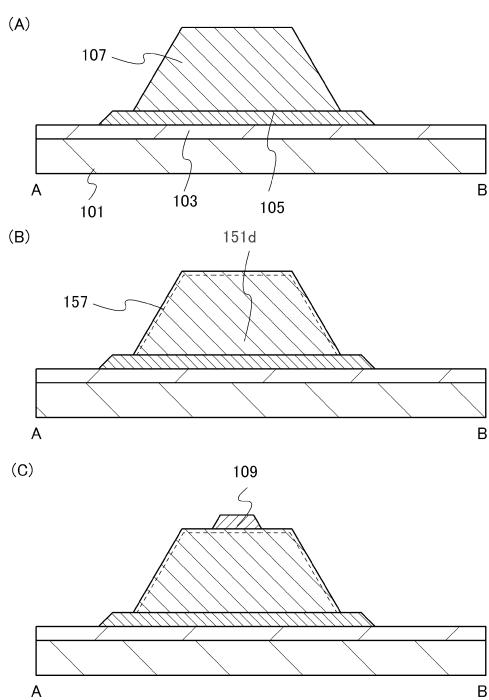

(実施の形態 2 )

本実施の形態では、実施の形態 1 と比較して、信頼性が高く、電界効果移動度が高いトランジスタの構造について、図 2 及び図 3 を用いて説明する。

【0100】

本実施の形態では、図 2 (A) に示すような第 1 の電極 105 及び第 2 の電極 109 の間に設けられる酸化物半導体膜 151a において、ゲート絶縁膜 111 と接する表層部に結晶領域 157 を有することを特徴とする。酸化物半導体膜 151a 及びゲート絶縁膜 111 の界面近傍の拡大図を図 2 (B) に示す。

【0101】

酸化物半導体膜 151a は、非晶質を主たる構成とする非晶質領域 155 と、酸化物半導体膜 151a の表層部に形成される結晶領域 157 とを有する。なお、表層部とは、表面からの距離 (深さ) が酸化物半導体膜の厚さの 10% 以下である領域である。

【0102】

10

20

30

40

50

ここで、非晶質領域 155 は、非晶質酸化物半導体膜を主たる構成としている。なお、「主たる」とは、例えば、50%以上を占める状態をいい、この場合には、非晶質酸化物半導体膜が体積%（または重量%）で50%以上を占める状態をいうものとする。つまり、非晶質酸化物半導体膜以外にも、酸化物半導体膜の結晶などを含むことがあるが、その含有率は体積%（または重量%）で50%未満であることが望ましいがこれらの範囲に限定される必要はない。

#### 【0103】

酸化物半導体膜の材料として In - Ga - Zn - O 酸化物半導体膜を用いる場合には、上記の非晶質領域 155 の組成は、Zn の含有量（原子%）が、In または Ga の含有量（原子%）以上となるようにするのが好適である。このような組成とすることにより、所定の組成の結晶領域 157 を形成することが容易になるためである。 10

#### 【0104】

表層部の結晶領域 157 の結晶は、酸化物半導体膜 151a の表面に対して略垂直な方向に c 軸（c - axis）が配向した結晶であり、当該結晶が隣接している。例えば、In - Ga - Zn - O 系の酸化物半導体材料を用いる場合には、結晶領域 157 の結晶は、InGaZnO<sub>4</sub> 結晶の c 軸が酸化物半導体膜 151a の表面に対して略垂直な方向に配向したものとなる。なお、「表層部（表面の近傍）」とは、例えば、表面からの距離（深さ）が 20 nm 以下の領域をいう。

#### 【0105】

上記 InGaZnO<sub>4</sub> の結晶は、In、Ga、Zn のいずれかを含有し、a 軸（a - axis）および b 軸（b - axis）に平行なレイヤーの積層構造として捉えることができる（図 3 参照）。すなわち、InGaZnO<sub>4</sub> の結晶は、In を含有する第 1 のレイヤーと、In を含有する第 2 のレイヤーと、In を含有する第 3 のレイヤーとが c 軸方向に積層された構造を備える。 20

#### 【0106】

InGaZnO<sub>4</sub> 結晶の電気伝導は、主として In によって制御されるため、In を含有する第 1 のレイヤー乃至第 3 のレイヤーの、a 軸および b 軸に平行な方向に関する電気特性は良好である。これは、In を含有する第 1 のレイヤー乃至第 3 のレイヤーのいずれか一以上では、一の In の 5s 軌道が、隣接する In の 5s 軌道と重なりを有することにより、キャリアパスが形成されるためである。 30

#### 【0107】

このような結晶が配向することで、酸化物半導体膜 151a の電気的特性にも影響が現れる。具体的には、例えば、酸化物半導体膜 151a の表面と平行な方向の電気特性が向上する。これは、InGaZnO<sub>4</sub> 結晶の c 軸が酸化物半導体膜 151a の表面に対して略垂直な方向に配向しており、InGaZnO<sub>4</sub> 結晶において、a 軸および b 軸に平行な方向に電流が流れるためである。

#### 【0108】

なお、結晶領域 157 の結晶構造は上記に限定されず、他の結晶構造の結晶を含んでいても良い。例えば、In - Ga - Zn - O 系の酸化物半導体材料を用いる場合には、InGaZnO<sub>4</sub> の結晶に加え、In<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub>、InGaZn<sub>5</sub>O<sub>8</sub> 等の結晶などを含んでいても良い。もちろん、結晶領域 157 全体に渡って InGaZnO<sub>4</sub> の結晶が存在する場合には、より効果的であり、好適である。 40

#### 【0109】

以上において説明したように、酸化物半導体膜 151a では、表層部に結晶領域 157 を有することで、良好な電気特性を実現できる。特に、結晶領域 157 が、InGaZnO<sub>4</sub> 結晶の c 軸が酸化物半導体膜 151a の表面に対して略垂直な方向に配向したものを含んで構成される場合には、InGaZnO<sub>4</sub> 結晶の電気特性によって、酸化物半導体膜 151a 表層部におけるキャリア移動度が上昇する。このため、当該酸化物半導体膜 151a を有するトランジスタの電界効果移動度が上昇し、良好な電気特性を実現できる。

#### 【0110】

10

20

30

40

50

また、結晶領域 157 は、非晶質領域 155 と比較して安定であるため、これを酸化物半導体膜 151a の表層部に有することで、非晶質領域 155 に不純物（例えば水素、水、水酸基または水素化物など）が取り込まれることを低減することができる。このため、酸化物半導体膜 151a の信頼性を向上させることができる。

【0111】

以上の工程により酸化物半導体膜中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に低く、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧が高く、ショートチャネル効果に強く、オンオフ比の高いトランジスタを作製することができる。

【0112】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0113】

（実施の形態 3）

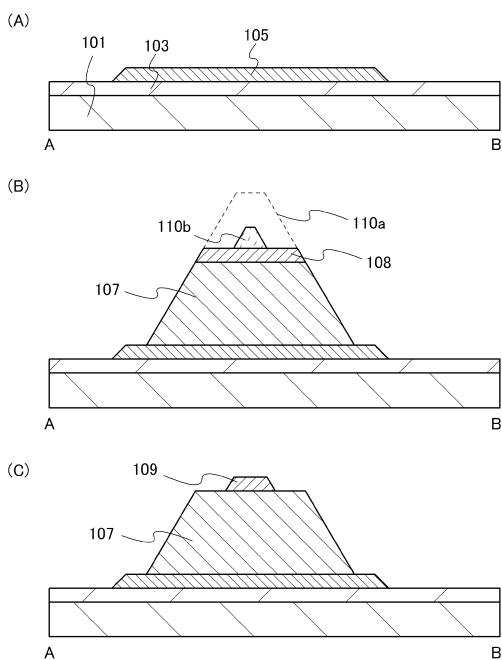

本実施の形態では、実施の形態 1 と比較して、信頼性が高く、電界効果移動度が高いトランジスタの構造について、図 4 を用いて説明する。

【0114】

本実施の形態では、図 4 (A) に示すような第 1 の電極 105 及び第 2 の電極 109 の間に設けられる酸化物半導体膜において、ゲート絶縁膜 111 及び第 2 の電極 109 に接する表層部に結晶領域 157 を有することを特徴とする。酸化物半導体膜 151b、151c 近傍の拡大図を図 4 (B) 及び図 4 (C) に示す。

【0115】

図 4 (B) は、酸化物半導体膜 151b においてゲート絶縁膜 111 及び第 2 の電極 109 に接する表層部に結晶領域 157 を有することを特徴とする。

【0116】

また、図 4 (C) は、酸化物半導体膜 151c においてゲート絶縁膜 111 と接する領域と、第 2 の電極 109 から所定の距離離れた領域に結晶領域 157 を有することを特徴とする。なお、酸化物半導体膜 151c において、第 2 の電極 109 と接する領域には非晶質領域 159 が形成される。

【0117】

本実施の形態における結晶領域 157 は、実施の形態 2 に示す結晶領域 157 と同様に、酸化物半導体膜 151b、151c の表面に対して略垂直な方向に c 軸 (c-axis) が配向した結晶領域である。このため、酸化物半導体膜 151b、151c の表面と平行な方向の電気特性が向上する。以上のことから、当該酸化物半導体膜 151b、151c を有するトランジスタの電界効果移動度が上昇し、良好な電気特性を実現できる。

【0118】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0119】

（実施の形態 4）

本実施の形態では、耐熱性の高いトランジスタについて、図 1 を用いて説明する。

【0120】

図 1 に示す基板 101 において、放熱性の高い基板を用いることで、耐熱性の高いトランジスタを作製することができる。放熱性の高い基板としては、半導体基板、金属基板、プラスチック等があり、半導体基板の代表例としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板等がある。金属基板の代表例としては、アルミニウム基板、銅基板、ステンレス基板等がある。

10

20

30

40

50

プラスチック基板の代表例としては、カーボン繊維、金属繊維、金属片等を有するプラスチックがある。なお、半導体基板、金属基板、及びプラスチック基板は、これらに限定されず放熱性の高いものであれば、適宜用いることができる。

【0121】

また、図1に示す絶縁膜103として、熱伝導率の高い絶縁膜を形成することで、耐熱性の高いトランジスタを作製することができる。熱伝導率の高い絶縁膜としては、窒化アルミニウム膜、窒化酸化アルミニウム膜、窒化シリコン膜等がある。

【0122】

また、図1に示す第1の電極105と絶縁膜103の間に半導体膜を設けてもよい。半導体膜の代表例としては、シリコン膜、ゲルマニウム膜、シリコンカーバイド膜、DLC (Diamond Like Carbon) 膜等がある。

10

【0123】

なお、以上の構成のいずれか一つ以上を用いることで、耐熱性の高いトランジスタを作製することができる。

【0124】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0125】

(実施の形態5)

本実施の形態では、第1の電極105及び第2の電極109において、仕事関数の異なる材料を用いて形成することを特徴とするトランジスタについて説明する。

20

【0126】

本実施の形態では、第1の電極105及び第2の電極109の一方が、酸化物半導体の電子親和力以下の仕事関数の導電材料で形成され、第1の電極105及び第2の電極109の他方が、酸化物半導体の電子親和力より大きい仕事関数の導電材料で形成される。

【0127】

例えば、酸化物半導体の電子親和力( )が4.3eVである場合、酸化物半導体の電子親和力よりも大きい仕事関数の導電性材料の例として、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、鉄(Fe)、酸化インジウム錫(ITO)などを用いることができる。また、仕事関数が酸化物半導体の電子親和力以下である導電性材料の例として、チタン(Ti)、イットリウム(Y)、アルミニウム(Al)、マグネシウム(Mg)、銀(Ag)、ジルコニウム(Zr)などを用いることができる。

30

【0128】

はじめに、ドレインとして機能する電極を酸化物半導体の電子親和力より仕事関数の大きい導電性材料で形成し、ソースとして機能する電極を酸化物半導体の電子親和力以下の仕事関数の導電性材料で形成する場合について、説明する。

【0129】

ドレインとして機能する電極を形成する導電性材料の仕事関数を $m_d$ とし、ソースとして機能する電極を形成する導電性材料の仕事関数 $m_s$ とし、仕事関数 $m_s$ 、電子親和力 $\chi$ 、及び仕事関数 $m_d$ の関係が、数式5で示す関係となるようにする。

40

$$m_s < m_d \quad (\text{数5})$$

【0130】

このように、ソースとして機能する電極の仕事関数が、酸化物半導体の電子親和力以下であるため、トランジスタがオン状態における障壁(例えば図6(B)の $h$ )を低減でき、低いゲート電圧でオン状態となり、大電流を流すことができる。

【0131】

一方、仕事関数 $m_d$ 、電子親和力 $\chi$ 、及び仕事関数 $m_s$ の関係が、数式6で示す関係となるようにする。

$$m_d < m_s \quad (\text{数6})$$

【0132】

50

このように、ソースとして機能する電極の仕事関数が、酸化物半導体の電子親和力より大きいため、トランジスタの障壁が高くなる。このため、オフ状態における電流を低減することができる。

【0133】

なお、ソースとして機能する電極を第1の電極105及び第2の電極109の一方とし、ドレインとして機能する電極を第1の電極105及び第2の電極109の他方とすることができる。

【0134】

以上のことから、第1の電極105及び第2の電極109の一方が、酸化物半導体の電子親和力以下の仕事関数の導電材料で形成され、第1の電極105及び第2の電極109の他方が、酸化物半導体の電子親和力より大きい仕事関数の導電材料で形成されることで、トランジスタのオン特性またはオフ特性を向上させることができる。

【0135】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0136】

(実施の形態6)

本実施の形態では、図1または図2に示すトランジスタの製造工程について、図11を用いて説明する。

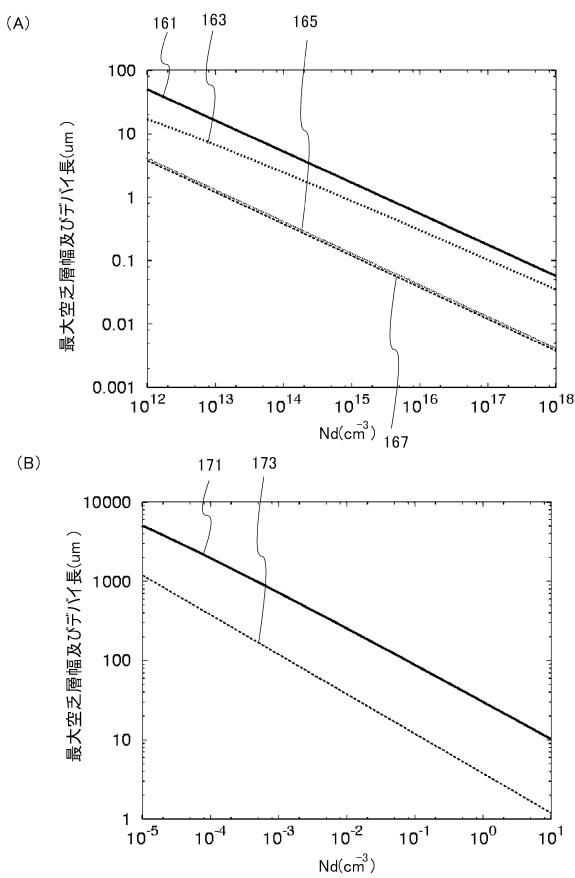

【0137】

図11(A)に示すように、基板101上に絶縁膜103を形成し、絶縁膜103上に第1の電極105を形成する。第1の電極105は、トランジスタのソース電極及びドレイン電極の一方として機能する。

【0138】

絶縁膜103は、スパッタリング法、CVD法、塗布法などで形成することができる。

【0139】

なお、スパッタリング法で絶縁膜103を形成する場合、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ絶縁膜103を形成することが好ましい。これは、絶縁膜103に水素、水、水酸基または水素化物などが含まれないようにするためである。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。吸着型の真空ポンプとしては、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室では、不純物、特に水素、水、水酸基または水素化物などが排気されるため、当該処理室で絶縁膜103を形成すると、絶縁膜103に含まれる不純物の濃度を低減できる。

【0140】

また、絶縁膜103を形成する際に用いるスパッタガスは、水素、水、水酸基または水素化物などの不純物が濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0141】

スパッタリング法にはスパッタ用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、さらにパルス的にバイアスを与えるパルスDCスパッタリング法がある。RFスパッタリング法は主に絶縁膜を形成する場合に用いられ、DCスパッタリング法は主に金属膜を形成する場合に用いられる。

【0142】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料の膜を積層形成することも、同一チャンバーで複数種類の材料を同時に放電させて形成することもできる。

【0143】

10

20

30

40

50

また、チャンバー内部に磁石機構を備えたマグнетロンスパッタリング法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるE C Rスパッタリング法を用いるスパッタ装置がある。

【0144】

また、スパッタリング法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法を用いることもできる。

【0145】

本明細書のスパッタリングにおいては、上記したスパッタリング装置及びスパッタリング方法を適宜用いることができる。

10

【0146】

本実施の形態では、基板101を処理室へ搬送し、水素、水、水酸基または水素化物などが除去された高純度酸素を含むスパッタガスを導入し、シリコンターゲットを用いて、基板101に絶縁膜103として、酸化シリコン膜を形成する。なお、絶縁膜103を形成する際は、基板101は加熱されていてもよい。

【0147】

例えば、石英（好ましくは合成石英）を用い、基板温度108、基板とターゲットとの間との距離（T-S間距離）を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン（酸素流量25sccm：アルゴン流量25sccm=1:1）雰囲気下でRFスパッタリング法により酸化シリコン膜を形成する。膜厚は100nmとするとよい。なお、石英（好ましくは合成石英）に代えてシリコンターゲットを用いることができる。なお、スパッタガスとして、酸素、または酸素及びアルゴンの混合ガスを用いて行う。

20

【0148】

また、絶縁膜103を積層構造で形成する場合、例えば、酸化シリコン膜と基板との間に水素、水、水酸基または水素化物などが除去された高純度窒素を含むスパッタガス及びシリコンターゲットを用いて窒化シリコン膜を形成する。この場合においても、酸化シリコン膜と同様に、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ窒化シリコン膜を形成することが好ましい。なお、当該工程において、基板101は加熱されていてもよい。

【0149】

30

絶縁膜103として窒化シリコン膜及び酸化シリコン膜を積層する場合、窒化シリコン膜と酸化シリコン膜を同じ処理室において、共通のシリコンターゲットを用いて形成することができる。先に窒素を含むスパッタガスを導入して、処理室内に装着されたシリコンターゲットを用いて窒化シリコン膜を形成し、次に酸素を含むスパッタガスに切り替えて同じシリコンターゲットを用いて酸化シリコン膜を形成する。窒化シリコン膜及び酸化シリコン膜を大気に曝露せずに連続して形成することができるため、窒化シリコン膜表面に水素、水、水酸基または水素化物などの不純物が吸着することを防止することができる。

【0150】

第1の電極105は、基板101上に導電膜をスパッタリング法、CVD法、または真空蒸着法で形成し、当該導電膜上にフォトリソグラフィ工程によりレジストマスク形成し、当該レジストマスクを用いて導電膜をエッチングして、形成することができる。または、フォトリソグラフィ工程を用いず、印刷法、インクジェット法で第1の電極105を形成することで、工程数を削減することができる。なお、第1の電極105の端部をテーパ形状とすると、後に形成されるゲート絶縁膜の被覆性が向上するため好ましい。第1の電極105の端部と絶縁膜103のなす角の角度を30°以上60°以下、好ましくは40°以上50°以下とすることで、後に形成されるゲート絶縁膜の被覆性を向上させることができる。

40

【0151】

本実施の形態では、第1の電極105となる導電膜として、スパッタリング法により膜厚50nmのチタン膜を形成し、厚さ100nmのアルミニウム膜を形成し、厚さ50nm

50

のチタン膜を形成する。次に、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、第1の電極105を形成する。

【0152】

次に、図11(B)に示すように、第1の電極105上に酸化物半導体膜107及び第2の電極となる導電膜108を形成する。酸化物半導体膜107はトランジスタのチャネル形成領域として機能する。

【0153】

ここで、酸化物半導体膜107及び第2の電極となる導電膜108の作製方法について、説明する。

【0154】

基板101及び第1の電極105上にスパッタリング法、塗布法、印刷法等により酸化物半導体膜を形成する。次に、酸化物半導体膜上に導電膜を形成する。本実施の形態では、スパッタリング法により酸化物半導体膜を形成する。

10

【0155】

酸化物半導体膜107に水素がなるべく含まれないようにするために、前処理として、スパッタリング装置の予備加熱室で第1の電極105が形成された基板101を予備加熱し、基板101に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に形成するゲート絶縁膜111の形成前の基板101に行ってもよいし、後に形成する第3の電極113形成前の基板101に行ってもよい。

20

【0156】

なお、酸化物半導体膜をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、第1の電極105の表面に付着しているパーティクルを除去することで、第1の電極105及び酸化物半導体膜の界面における抵抗を低減することができるため好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に高周波電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。

30

【0157】

本実施の形態では、In-Ga-Zn-O系金属酸化物ターゲットを用いたスパッタリング法により酸化物半導体膜を形成する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて形成してもよい。

【0158】

酸化物半導体膜を形成する際に用いるスパッタガスは水素、水、水酸基または水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

40

【0159】

酸化物半導体膜をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及びZnを含む金属酸化物ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol数比])を用いることができる。また、In、Ga、及びZnを含む金属酸化物ターゲットとして、In : Ga : Zn = 1 : 1 : 2 [atom比]、またはIn : Ga : Zn = 1 : 1 : 4 [atom比]の組成比を有するターゲットを用いることができる。金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いて形成した酸化物半導体膜は緻密な膜となる。

50

## 【0160】

酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内に残留する水を除去しつつ、水素、水、水酸基または水素化物などが除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板101上に酸化物半導体膜を形成する。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素、水、水酸基または水素化物など（より好ましくは炭素原子を含む化合物も含む。）が排気されるため、酸化物半導体膜に含まれる不純物の濃度を低減できる。

10 また、基板を加熱しながら酸化物半導体膜を形成してもよい。

## 【0161】

本実施の形態では、酸化物半導体膜の成膜条件の一例として、基板温度は室温、基板とターゲットとの距離を110mm、圧力0.4Pa、直流(DC)電源0.5kW、酸素及びアルゴン（酸素流量15sccm：アルゴン流量30sccm）雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう。）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の厚さは、1μm以上、好ましくは3μmより大、より好ましくは10μm以上とする。なお、適用する酸化物半導体膜材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

20

## 【0162】

第2の電極となる導電膜108は、第1の電極105の材料及び手法を適宜用いることができる。ここでは、第2の電極となる導電膜108として、厚さ50nmのチタン膜、厚さ100nmのアルミニウム膜、及び厚さ50nmのチタン膜を順に積層する。

## 【0163】

次に、フォトリソグラフィ工程により導電膜上にレジストマスクを形成し、当該レジストマスクを用いて第2の電極となる導電膜108及び酸化物半導体膜107となる酸化物半導体膜をエッティングして、島状の第2の電極となる導電膜108及び島状の酸化物半導体膜107を形成する。なお、フォトリソグラフィ工程により形成したレジストマスクの代わりに、インクジェット法を用いてレジストマスクを作製することで、工程数を削減することができる。当該エッティングにより、第2の電極となる導電膜108及び酸化物半導体膜107の端部と、第1の電極105の表面となす角の角度を30°以上60°以下、好ましくは40°以上50°以下とすることで、後に形成されるゲート絶縁膜の被覆性向上させることができるため好ましい。

30

## 【0164】

なお、ここでの導電膜及び酸化物半導体膜のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。所望の形状の酸化物半導体膜107及び第2の電極となる導電膜108を形成するために、材料に合わせてエッティング条件（エッティング液、エッティング時間、温度など）を適宜調節する。

## 【0165】

なお、第2の電極となる導電膜108及び酸化物半導体膜と、第1の電極105とのエッティングレートが異なる場合は、第1の電極105のエッティングレートが低く、第2の電極となる導電膜108及び酸化物半導体膜のエッティングレートの高い条件を選択する。または、酸化物半導体膜のエッティングレートが低く、導電膜108のエッティングレートの高い条件を選択して、導電膜108をエッティングした後、第1の電極105のエッティングレートが低く、酸化物半導体膜のエッティングレートの高い条件を選択する。

40

## 【0166】

酸化物半導体膜をウェットエッティングするエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液、アンモニア過水（過酸化水素：アンモニア水：水=5:2:2）などを用いることができる。また、ITO07N（関東化学社製）を用いてもよい。

50

## 【0167】

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体膜に含まれるインジウムなどの材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

## 【0168】

また、酸化物半導体膜をドライエッティングする際に用いるエッティングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、塩化硼素（BCl<sub>3</sub>）、塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）が好ましい。

10

## 【0169】

また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（CF<sub>4</sub>）、六弗化硫黄（SF<sub>6</sub>）、三弗化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）など）、臭化水素（HBr）、酸素（O<sub>2</sub>）、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。

## 【0170】

ドライエッティング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度など）を適宜調節する。

20

## 【0171】

本実施の形態では、エッチャントとしてアンモニア過水を用いて、第2の電極となる導電膜108をエッティングした後、磷酸と酢酸と硝酸を混ぜた溶液で酸化物半導体膜をエッティングして、酸化物半導体膜107を形成する。

## 【0172】

次に、酸化物半導体膜107及び第2の電極となる導電膜108を形成したレジストマスク（破線110aで示す。）を後退させて、レジストマスク110bを形成する。（図11（B）参照）。ここでは、レジストマスクをアッシングして、レジストマスク110bを形成する。次に、レジストマスク110bを用いて導電膜108をエッティングして、第2の電極109を形成する（図11（C）参照。）第2の電極109はトランジスタのソース電極及びドレイン電極の他方として機能する。

30

## 【0173】

導電膜108のエッティング方法としては、第1の電極105及び酸化物半導体膜107のエッティングレートが低く、導電膜108のエッティングレートの高い条件を選択する。

## 【0174】

次に、本実施の形態では、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜に対して窒素、希ガスなどの不活性ガス雰囲気下において450、1時間の加熱処理を行った後、大気に触れさせないことで、酸化物半導体膜への水素、水、水酸基または水素化物などの再侵入を防ぐことが可能であり、水素濃度が低減され高純度化され、i型化または実質的にi型化された酸化物半導体膜を得ることができる。即ち、この第1の加熱処理によって酸化物半導体膜107の脱水化及び脱水素化の少なくとも一方を行うことができる。

40

## 【0175】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴンなどの希ガスに、水素、水、水酸基または水素化物などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.99999%）以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

50

## 【0176】

また、第1の加熱処理の条件、または酸化物半導体膜の材料によっては、酸化物半導体膜が結晶化せず、図1(B)に示す酸化物半導体膜107となる。このような条件の一つは、加熱温度が400以上550未満、好ましくは400以上500未満である。また、このような条件の一つは、スパッタリング法により形成されるIn-Ga-Zn-O系の酸化物半導体の場合は、ターゲットのInの含有量(原子%)及びGaの含有量(原子%)に対して、Znの含有量(原子%)が1未満(代表的にはIn:Ga:Zn=1:1:0.5)の場合、酸化物半導体膜は結晶化せず、図1(B)に示す酸化物半導体膜107となる。

## 【0177】

10

また、第1の加熱条件、または酸化物半導体膜の材料によっては、酸化物半導体膜は結晶化し、結晶を有する酸化物半導体膜となる場合もある。例えば、結晶化率が90%以上、または80%以上の結晶を有する酸化物半導体膜となる場合もある。

## 【0178】

また、第1の加熱条件、または酸化物半導体膜の材料によっては、非晶質の酸化物半導体膜の表層部に結晶領域が形成される酸化物半導体膜となる場合もある。このような条件の一つは、加熱温度が500以上750以下、好ましくは550以上基板の歪み点未満である。また、このような条件の一つは、スパッタリング法により形成されるIn-Ga-Zn-O系の酸化物半導体の場合は、ターゲットのInの含有量(原子%)及びGaの含有量(原子%)に対して、Znの含有量(原子%)が1以上(代表的にはIn:Ga:Zn=1:1:1)の場合、図2(B)に示すような、酸化物半導体膜の表層部に結晶領域157を有する酸化物半導体膜151aとなる。

20

## 【0179】

また、酸化物半導体膜の第1の加熱処理は、島状の酸化物半導体膜を形成する前の酸化物半導体膜に行っててもよい。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0180】

30

なお、酸化物半導体膜に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体膜を形成した後、酸化物半導体膜上に第2の電極となる導電膜を積層した後、第1の電極、酸化物半導体膜及び第2の電極上にゲート絶縁膜を形成した後、またはゲート電極を形成した後のいずれで行ってもよい。

## 【0181】

次に、図12(A)に示すように、第1の電極105、酸化物半導体膜107、第2の電極109上にゲート絶縁膜111を形成し、ゲート絶縁膜111上にゲート電極として機能する第3の電極113を形成する。

## 【0182】

不純物を除去することによりi型化または実質的にi型化された酸化物半導体膜(水素濃度が低減され高純度化された酸化物半導体膜)は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁膜111との界面は重要である。そのため高純度化された酸化物半導体膜に接するゲート絶縁膜111は、高品質化が要求される。

40

## 【0183】

例えば、μ波(2.45GHz)を用いた高密度プラズマCVDにより、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。水素濃度が低減され高純度化された酸化物半導体膜と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

## 【0184】

もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、ゲート絶縁膜の形成後の加熱処理によってゲート絶縁膜の膜質、酸化物半導体膜との界面特性が改質される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であること

50

は勿論のこと、酸化物半導体膜との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0185】

さらに、 $85$ 、 $2 \times 10^6$  V / cm、12時間のゲートバイアス・熱ストレス試験 (BT試験) においては、不純物が酸化物半導体膜に添加されていると、不純物と酸化物半導体膜の主成分との結合が、強電界 (B:バイアス) と高温 (T:温度) により切断され、生成された未結合手がしきい値電圧 (V<sub>th</sub>) のドリフトを誘発することとなる。

【0186】

これに対して、酸化物半導体膜の不純物、特に水素や水などを極力除去し、上記のようにゲート絶縁膜との界面特性を良好にすることにより、BT試験に対しても安定なトランジスタを得ることを可能としている。

10

【0187】

スパッタリング法でゲート絶縁膜111を形成することでゲート絶縁膜111中の水素濃度を低減することができる。スパッタリング法により酸化シリコン膜を形成する場合には、ターゲットとしてシリコンターゲットまたは石英ターゲットを用い、スパッタガスとして酸素または、酸素及びアルゴンの混合ガスを用いて行う。

【0188】

なお、酸化物半導体膜に接して設けられる絶縁膜にハロゲン元素 (例えば、フッ素または塩素) を含ませ、または酸化物半導体膜を露出させた状態でハロゲン元素を含むガス雰囲気中でのプラズマ処理によって酸化物半導体膜にハロゲン元素を含ませ、酸化物半導体膜または該酸化物半導体膜に接して設けられる絶縁膜との界面に存在しうる、水素、水、水酸基又は水素化物 (水素化合物ともいう) などの不純物を排除してもよい。絶縁膜にハロゲン元素を含ませる場合には、該絶縁膜中におけるハロゲン元素濃度は、 $5 \times 10^{-8}$  cm<sup>-3</sup> ~  $1 \times 10^{-7}$  cm<sup>-3</sup> 程度とすればよい。

20

【0189】

また、上記したように酸化物半導体膜中または酸化物半導体膜とこれに接する絶縁膜との界面にハロゲン元素を含ませ、酸化物半導体膜と接して設けられた絶縁膜が酸化物絶縁膜である場合には、酸化物半導体膜と接しない側の酸化物絶縁膜を、窒素物絶縁膜で覆うことが好ましい。すなわち、酸化物半導体膜に接する酸化物絶縁膜の上に接して窒化シリコン膜などを設ければよい。このような構造とすることで、水素、水、水酸基又は水素化物などの不純物が酸化物絶縁膜に侵入することを低減することができる。

30

【0190】

ゲート絶縁膜111は、第1の電極105、酸化物半導体膜107、及び第2の電極109側から酸化シリコン膜と窒化シリコン膜を積層した構造とすることもできる。例えば、第1のゲート絶縁膜として膜厚5 nm以上300 nm以下の酸化シリコン膜 (SiO<sub>x</sub> (x > 0)) を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜としてスパッタリング法により膜厚50 nm以上200 nm以下の窒化シリコン膜 (SiN<sub>y</sub> (y > 0)) を積層して、膜厚100 nmのゲート絶縁膜としてもよい。本実施の形態では、圧力0.4 Pa、高周波電源1.5 kW、酸素及びアルゴン (酸素流量25 sccm : アルゴン流量25 sccm = 1 : 1) 雰囲気下でRFスパッタリング法により膜厚100 nmの酸化シリコン膜を形成する。

40

【0191】

次に、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理 (好ましくは200以上400以下、例えば250以上350以下) を行う。当該加熱処理により、第1の加熱処理で発生した酸素欠陥に酸素を供給することで、ドナーとなる酸素欠陥を低減し、化学量論比を満たす構成とすることが可能であり、酸化物半導体膜107をi型化または実質的にi型化にすることができる。なお、当該第2の加熱処理は、第3の電極113、絶縁膜117、または配線125、129のいずれかを形成した後に行ってもよい。当該加熱処理により、酸化物半導体膜中に含まれる水素若しくは水をゲート絶縁膜に拡散させることができる。

50

## 【0192】

第3の電極113は、ゲート絶縁膜111上に第3の電極113となる導電膜をスパッタリング法、CVD法、または真空蒸着法で形成し、当該導電膜上にフォトリソグラフィ工程によりレジストマスクを形成し、当該レジストマスクを用いて導電膜をエッチングして、形成することができる。

## 【0193】

本実施の形態では、厚さ150nmのチタン膜をスパッタリング法により形成した後、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、第3の電極113を形成する。

## 【0194】

以上の工程で、水素濃度が低減され高純度化された酸化物半導体膜107を有するトランジスタ145を形成することができる。

10

## 【0195】

次に、図12(B)に示すように、ゲート絶縁膜111及び第3の電極113上に絶縁膜117を形成した後、コンタクトホール119、123を形成する。

## 【0196】

絶縁膜117は、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの酸化物絶縁膜、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などの窒化物絶縁膜を用いる。または、酸化物絶縁膜及び窒化物絶縁膜の積層とすることもできる。

20

## 【0197】

絶縁膜117は、スパッタリング法、CVD法などで形成する。なお、スパッタリング法で絶縁膜117を形成する場合、基板101を100～400の温度に加熱し、水素、水、水酸基または水素化物などが除去された高純度窒素を含むスパッタガスを導入しシリコンターゲットを用いて絶縁膜を形成してもよい。この場合においても、処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ絶縁膜を形成することが好ましい。

## 【0198】

なお、絶縁膜117の形成後、さらに、大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって表示装置や半導体装置の信頼性を向上できる。

30

## 【0199】

コンタクトホール119、123は、フォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁膜111及び絶縁膜117の一部を除去して、第1の電極105、第2の電極109、及び第3の電極113に達するコンタクトホール119、123を形成する。

## 【0200】

次に、ゲート絶縁膜111、及びコンタクトホール119、123上に導電膜を形成した後、フォトリソグラフィ工程により形成したレジストマスクを用いてエッチングして、配線125、129を形成する(図12(C)参照)。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを削減できる。

40

## 【0201】

配線125、129は、第1の電極105と同様に形成することができる。

## 【0202】

なお、第3の電極113及び配線125、129の間に平坦化のための平坦化絶縁膜を設けてもよい。平坦化絶縁膜の代表例としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシなどの、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-K材料)、シロキサン系樹脂、PSG(リ

50

ンガラス)、BPSG(リンボロンガラス)などがある。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁膜を形成してもよい。

#### 【0203】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いてもよい。また、有機基はフルオロ基を有してもよい。

#### 【0204】

平坦化絶縁膜の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷など)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティングなどを用いることができる。

10

#### 【0205】

上記のように酸化物半導体膜中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧が高く、ショートチャネル効果に強く、オンオフ比の高いトランジスタを作製することができる。

20

#### 【0206】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0207】

##### (実施の形態7)

本実施の形態では、実施の形態2に示すトランジスタの作製方法について、図11及び図13を用いて説明する。

#### 【0208】

実施の形態6と同様に、図11(A)に示すように、基板101上に絶縁膜103及び第1の電極105を形成する。次に、図11(B)の工程を経て、及び図11(C)に示すように、第1の電極105上に酸化物半導体膜107及び第2の電極109を形成する。

30

#### 【0209】

次に、第1の加熱処理を行う。本実施の形態における第1の加熱処理は、上記実施の形態における第1の加熱処理とは異なるものであり、当該加熱処理によって、図13に示すように、表層部に結晶領域157が形成される酸化物半導体膜151aを形成することができる。

#### 【0210】

本実施の形態では、抵抗発熱体などの発熱体からの熱伝導及び熱輻射の少なくとも一方によって被処理物を加熱する装置を用いて第1の加熱処理を行う。ここで、加熱処理の温度は500以上750以下、好ましくは550以上基板の歪み点未満とすることが好適である。なお、加熱処理温度の上限に関し、発明の本質的な部分からの要求はないが、加熱処理温度の上限は基板101の耐熱性の範囲内とする必要がある。また、加熱処理の時間は、1分以上10分以下とすることが好適である。上述のようなRTA処理を適用することで、短時間に加熱処理を行うことができるため、基板101に対する熱の影響を小さくすることができる。つまり、加熱処理を長時間行う場合と比較して、加熱処理温度の上限を引き上げることが可能である。また、酸化物半導体膜の表面近傍に、所定の構造の結晶領域を選択的に形成することができる。

40

#### 【0211】

本実施の形態で用いることができる加熱装置としては、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal

50

1 Anneal) 装置などの R T A (R a p i d T h e r m a l A n n e a l) 装置などがある。 L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。 G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性ガスが用いられる。

【0212】

例えば、第1の加熱処理として、650 ~ 700 の高温に加熱した窒素または希ガスなどの不活性ガス雰囲気に基板を移動し、数分間加熱した後、高温に加熱した不活性ガス中から基板を出す G R T A を行ってもよい。 G R T A を用いると短時間での高温加熱処理が可能となる。

10

【0213】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴンなどの希ガスに、水素、水、水酸基または水素化物などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6 N (99.9999%) 以上、好ましくは 7 N (99.99999%) 以上、(即ち不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下) とすることが好ましい。

【0214】

なお、上記の加熱処理は、酸化物半導体膜を形成した後であればいずれのタイミングで行ってもよいが、脱水化または脱水素化を促進させるためには、酸化物半導体膜 107 の表面に他の構成要素を設ける前に行うのが好適である。また、上記の加熱処理は、一回に限らず、複数回行っても良い。

20

【0215】

この後、実施の形態 6 と同様に、ゲート絶縁膜と、ゲート電極として機能する第3の電極を形成してトランジスタを作製する。

【0216】

酸化物半導体膜 151a の表面に結晶領域 157 を有することで、ソース及びドレイン間の抵抗が低減すると共に、酸化物半導体膜 151a 表面におけるキャリア移動度が向上する。このため、当該酸化物半導体膜 151a を有するトランジスタの電界効果移動度が高く、良好な電気特性を実現できる。

30

【0217】

また、結晶領域 157 は、非晶質領域 155 と比較して安定であるため、これを酸化物半導体膜 151 の表面近傍に有することで、非晶質領域 155 に不純物(例えば水素、水、水酸基または水素化物など)が取り込まれることを低減することができる。このため、酸化物半導体膜 151a の信頼性を向上させることができる。

【0218】

以上の工程により酸化物半導体膜中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧が高く、ショートチャネル効果に強く、オンオフ比の高いトランジスタを作製することができる。

40

【0219】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

【0220】

(実施の形態 8)

本実施の形態では、図 4 に示すトランジスタの作製方法について、図 4 及び図 14 を用いて説明する。

50

## 【0221】

実施の形態6と同様に、図14(A)に示すように、基板101上に絶縁膜103を成膜し、島状の第1の電極105を形成し、島状の第1の電極105上に島状の酸化物半導体膜107を形成する。

## 【0222】

次に、第1の加熱処理を行い、表層部に結晶領域157を有する酸化物半導体膜151dを形成する。

## 【0223】

ここでの第1の加熱処理は、実施の形態6に示す第1の加熱処理において、酸化物半導体膜の表層部に結晶領域を形成する条件、または実施の形態7に示す第1の加熱処理を適宜用いればよい。

10

## 【0224】

次に、絶縁膜103、第1の電極105、酸化物半導体膜151d上に導電膜を形成した後、フォトリソグラフィ工程により形成されたレジストマスクを用いて導電膜をエッチングして、図14(C)に示すように、第2の電極109を形成する。

## 【0225】

次に、実施の形態6と同様に、ゲート絶縁膜と、ゲート電極として機能する第3の電極を形成する。なお、実施の形態6に示す第2の加熱処理において、第2の電極109と酸化物半導体膜151dの酸素が反応しなければ、図4(B)に示すように、ゲート絶縁膜111及び第2の電極109と接する表層部において結晶領域157を有する酸化物半導体膜151bが形成される。

20

## 【0226】

一方、なお、実施の形態6に示す第2の加熱処理において、第2の電極109と酸化物半導体膜151dの酸素が反応すると、酸化物半導体膜の表層部の結晶領域から酸素が脱離し、当該領域が非晶質構造となる。この結果、図4(C)に示すように、ゲート絶縁膜111と接する表層部と、第2の電極109から所定の距離離れた領域に結晶領域157を有し、第2の電極109と接する表層部において非晶質領域159を有する酸化物半導体膜151cが形成される。

## 【0227】

以上の工程により、電界効果移動度が高く、良好な電気特性を有するトランジスタを作製することができる。

30

## 【0228】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0229】

## (実施の形態9)

本実施の形態では、図1に示すトランジスタの製造工程について、図11を用いて説明する。

## 【0230】

実施の形態6と同様に、図11(A)に示すように、基板101上に絶縁膜103を形成し、絶縁膜103上に第1の電極105を形成する。

40

## 【0231】

次に、図11(B)の工程を経て、図11(C)に示すように、第1の電極105上に酸化物半導体膜107及び第2の電極109を形成する。

## 【0232】

なお、酸化物半導体膜をスパッタリング法により形成する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、第1の電極105の表面に付着しているパーティクルを除去することで、第1の電極105及び酸化物半導体膜の界面における抵抗を低減することができるため好ましい。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。

50

## 【0233】

基板101及び第1の電極105上にスパッタリング法により酸化物半導体膜を形成する。次に、酸化物半導体膜上に導電膜を形成する。

## 【0234】

本実施の形態では、酸化物半導体膜をIn-Ga-Zn-O系金属酸化物ターゲットを用いたスパッタリング法により形成する。本実施の形態では、減圧状態に保持された処理室内に基板を保持し、基板を室温以上400未満の温度に加熱する。処理室内に残留する水素、水、水酸基または水素化物などを除去しつつ、水素、水、水酸基または水素化物などが除去されたスパッタガスを導入し、金属酸化物をターゲットとして基板101及び第1の電極105上に酸化物半導体膜を形成する。処理室内に残留する水素、水、水酸基または水素化物などを除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素、水、水酸基または水素化物（より好ましくは炭素原子を含む化合物も含む。）などが排気されるため、当該処理室で形成した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、クライオポンプにより処理室内に残留する水素、水、水酸基または水素化物などを除去しながらスパッタリングを行うことで、基板温度が室温から400未満でも、ドナーとなる水素原子、水などの不純物を低減することが可能であり、化学量論比を満たす構成であるi型または実質的にi型の酸化物半導体膜を形成することができる。

10

20

## 【0235】

本実施の形態では、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素（酸素流量比率100%）雰囲気下での成膜条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう。）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは30nm以上3000nm以下とする。なお、適用する酸化物半導体膜材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

## 【0236】

次に、図12(A)に示すように、実施の形態6と同様に、第1の電極105、酸化物半導体膜107、第2の電極109上にゲート絶縁膜111を形成する。なお、本実施の形態では、酸化物半導体膜中に含まれる水素濃度が低減されているため、ゲート絶縁膜111を形成する前に、実施の形態6に示す第1の加熱処理は行わなくともよい。ゲート絶縁膜111は、酸化物半導体膜107との界面特性が良好なものとすることが好ましく、μ波(2.45GHz)を用いた高密度プラズマCVDで緻密なゲート絶縁膜111を形成することで、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。また、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の形成方法を適用することができる。さらには、スパッタリング法やプラズマCVD法で形成した絶縁膜の表面に、μ波(2.45GHz)を用いた高密度プラズマを照射することで、更に緻密で絶縁耐圧の高い高品質なゲート絶縁膜を形成できるので好ましい。

30

40

## 【0237】

なお、ゲート絶縁膜111を形成する前に逆スパッタを行い、少なくとも酸化物半導体膜107の表面に付着しているレジスト残渣などを除去することが好ましい。

## 【0238】

また、ゲート絶縁膜111を形成する前にN<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理によって露出している酸化物半導体膜の表面に付着した水素、水、水酸基または水素化物などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体膜の一部に接するゲート絶縁膜111を形成することが好ましい。

## 【0239】

50

また、ゲート絶縁膜 111 に、水素、水、水酸基または水素化物などがあるべく含まれないようにするために、前処理として、スパッタリング装置の予備加熱室で第 1 の電極 105 から第 2 の電極 109 まで形成された基板 101 を予備加熱し、基板 101 に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。または、ゲート絶縁膜 111 を形成した後、基板 101 を、スパッタリング装置の予備加熱室で予備加熱して、基板 101 に吸着した水素、水、水酸基または水素化物などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100 以上 400 以下好ましくは 150 以上 300 以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。

## 【0240】

10

ゲート絶縁膜 111 は、第 1 の電極 105、酸化物半導体膜 107、及び第 2 の電極 109 側から酸化シリコン膜と窒化シリコン膜とを積層した構造とすることもできる。例えば、第 1 のゲート絶縁膜としてスパッタリング法により膜厚 5 nm 以上 300 nm 以下の酸化シリコン膜 (SiO<sub>x</sub> (x > 0)) を形成し、第 1 のゲート絶縁膜上に第 2 のゲート絶縁膜として膜厚 50 nm 以上 200 nm 以下の窒化シリコン膜 (SiN<sub>y</sub> (y > 0)) を積層して、ゲート絶縁膜とする。

## 【0241】

次に、図 12 (A) に示すように、実施の形態 6 と同様に、ゲート絶縁膜 111 上にゲート電極として機能する第 3 の電極 113 を形成する。

## 【0242】

20

以上の工程で、水素濃度が低減された酸化物半導体膜 107 を有するトランジスタ 145 を形成することができる。

## 【0243】

上記のように酸化物半導体膜を形成する際に、反応雰囲気中に残留する水素、水、水酸基または水素化物などを除去することで、該酸化物半導体膜中の水素濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

## 【0244】

次に、図 12 (B) に示すように、実施の形態 6 と同様に、ゲート絶縁膜 111 及び第 3 の電極 113 上に絶縁膜 117 を形成した後、コンタクトホール 119、123 を形成する。なお、絶縁膜 117 の形成後、さらに、実施の形態 6 と同様に、大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。この加熱処理によって、ノーマリーオフとなるトランジスタを得ることができる。よって表示装置や半導体装置の信頼性を向上できる。

30

## 【0245】

次に、図 12 (C) に示すように、実施の形態 6 と同様に、配線 125、129 を形成する。

## 【0246】

なお、第 3 の電極 113 及び配線 125、129 の間に平坦化のための平坦化絶縁膜を設けてもよい。

## 【0247】

40

上記のように酸化物半導体膜を形成するに際し、反応雰囲気中に残留する水素、水、水酸基または水素化物などを除去することで、該酸化物半導体膜中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体膜の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体膜を形成することができる。このため、大面積基板を用いてトランジスタを作製することができるため、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体膜を用いることで、耐圧が高く、ショートチャネル効果に強く、オンオフ比の高いトランジスタを作製することができる。

## 【0248】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

50

である。

【0249】

(実施の形態10)

実施の形態1乃至実施の形態9に示すトランジスタを有する回路を用いた形態について説明する。

【0250】

実施の形態1乃至実施の形態9に示すトランジスタは、オンオフ比が高く、耐圧が高く、劣化が少ないため、エアコン、冷蔵庫、炊飯器、太陽光発電システムなどのインバータ技術を応用した家電製品、ノート型のコンピュータをはじめとするバッテリ駆動型携帯情報端末機器、ストロボなどの電力增幅装置、電気自動車、DC/DC(直流/直流)コンバータ回路、モータ制御回路、オーディオ増幅器、ロジック回路、スイッチ回路、高周波リニア増幅器などに用いることができる。

10

【0251】

ここで、実施の形態1乃至実施の形態9に示すトランジスタを用いて構成されるインバータを備えた太陽光発電システムの一例について、図18を参照して説明する。なお、ここでは、住宅等に設置される太陽光発電システムの構成の一例について示す。

【0252】

図18に示す住宅用の太陽光発電システムは、太陽光発電の状況に応じて、電力の供給方式を変更するシステムである。例えば、晴天時など太陽光発電が行われる状況においては、太陽光発電により生じた電力を家庭内で消費し、また、余剰電力は電力会社からの配電線414に供給する。一方、太陽光発電による電力が不足する夜間や雨天時には、配電線414から電気の供給を受けて、それを家庭内で消費する。

20

【0253】

図18に示す住宅用の太陽光発電システムは、太陽光を電力(直流)に変換する太陽電池パネル400や、その電力を直流から交流に変換するインバータ404などを含む。インバータ404から出力される交流電力は、各種の電気器具410を動作させる電力として使用される。

【0254】

余分な電力は、配電線414を通じて家庭外に供給される。すなわち、当該システムを利用して電力の売却が可能である。直流開閉器402は、太陽電池パネル400とインバータ404との接続または遮断を選択するために設けられている。また、交流開閉器408は、配電線414と接続されるトランス412と、分電盤406との接続または遮断を選択するために設けられている。

30

【0255】

上記のインバータに、開示する発明の半導体装置を適用することで、信頼性が高く、安価な太陽光発電システムを実現することができる。

【0256】

本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

【実施例1】

40

【0257】

本実施例では、オンオフ比の高いトランジスタの酸化物半導体膜の厚さ及びチャネル幅について二次元デバイスシミュレータを用いて計算した結果を、図1、図15乃至図17を用いて説明する。なお、ここでは、デバイスシミュレータとしてSilvaco社のAtlasを用いた。

【0258】

はじめに、計算を行ったトランジスタの構造について、図1(A)を用いて説明する。第1の電極105及び第2の電極109は、酸化物半導体膜107とオーミック接触が可能な材料(代表的にはチタン)を想定し、仕事関数を4.3eVとした。酸化物半導体膜107をIn-Ga-Zn-O膜とし、電子親和力を4.3eVとした。ゲート絶縁膜11

50

1を厚さ100nmのSiO<sub>2</sub>とした。また、酸化物半導体膜107の厚さをL<sub>1</sub>とし、図1(A)のW<sub>2</sub>を1μmに固定し、W<sub>1</sub>及びL<sub>1</sub>を変化させて計算を行った。

#### 【0259】

デバイスシミュレータにより、オンオフ比を計算し、オンオフ比が1×10<sup>7</sup>の動作を示すL<sub>1</sub>及びW<sub>1</sub>の関係を直線201で示し、オンオフ比が1×10<sup>7</sup>以上の動作を示すL<sub>1</sub>及びW<sub>1</sub>の領域をハッキング203で示した(図15参照)。

#### 【0260】

図15のハッキング203で示す領域を満たすL<sub>1</sub>及びW<sub>1</sub>の関係を満たすことで、トランジスタのオンオフ比を高めることができる。

#### 【0261】

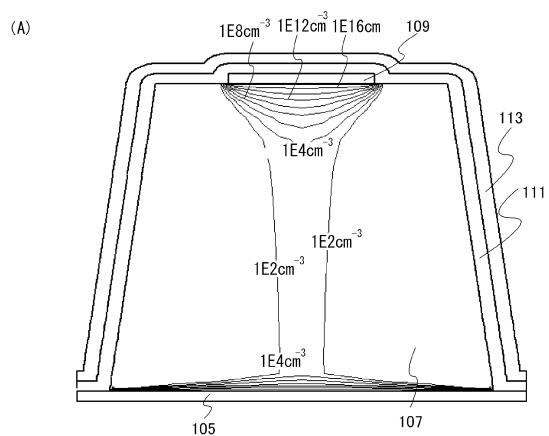

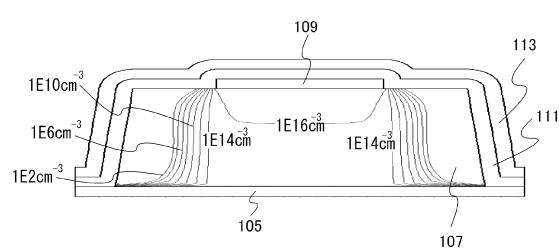

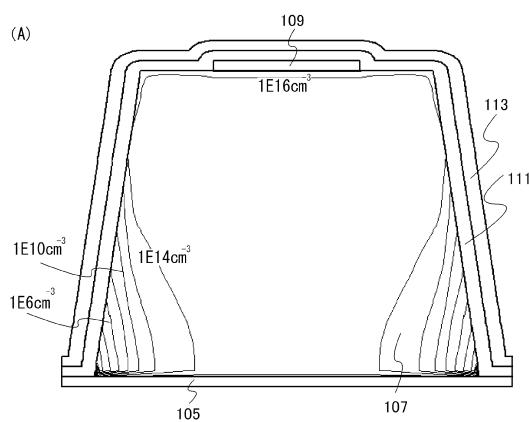

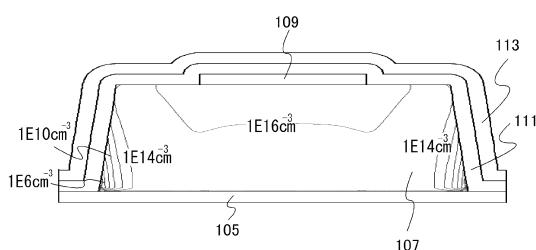

次に、図16(A)および図17(A)に、L<sub>1</sub>を3μm、W<sub>1</sub>を2μm、第2の電極109の幅1μmとしたときの酸化物半導体におけるキャリア密度分布を示し、図16(B)及び図17(B)にL<sub>1</sub>を1μm、W<sub>1</sub>を2μm、第2の電極109の幅1μmとしたときの酸化物半導体におけるキャリア密度分布を示す。なお、図16はV<sub>GS</sub>(ゲートソース電圧)を-2Vとしたオフ状態のキャリア密度分布を示し、図17はV<sub>GS</sub>(ゲートソース電圧)を+2Vとしたオン状態のキャリア密度分布を示す。また、第3の電極113が第2の電極109上をゲート絶縁膜111を介して覆っているが、これはシミュレーションの図形を簡略化するためであり、シミュレーション結果には影響はない。

#### 【0262】

図16(A)に示すトランジスタは、キャリア密度の低い領域(キャリア密度1×10<sup>2</sup>~1×10<sup>4</sup>cm<sup>-3</sup>)が酸化物半導体膜107の中央まで広がっており、キャリア密度の高い領域が、第1の電極105及び第2の電極109側それぞれに分離されているため、図16(B)と比較してオフ状態においてオフ電流を低減することができる。図17(A)及び図17(B)はそれぞれ、酸化物半導体膜107の表面だけでなく中央においても電子密度が高く、ゲート絶縁膜と接する酸化物半導体膜の表面だけでなく、酸化物半導体膜の内部にまでチャネル形成領域が形成されていることが分かる。また、第1の電極105より第2の電極109側においてキャリア密度の高い領域が広がっている。以上のことから、本実施例に示すトランジスタは、オン電流を高めることができることが分かる。

#### 【実施例2】

#### 【0263】

本実施例では、酸化物半導体のキャリア密度について、図19及び図20を用いて説明する。

#### 【0264】

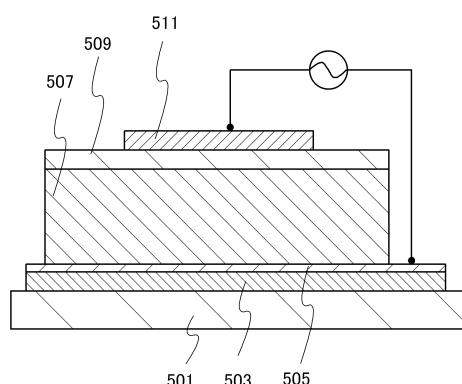

はじめに、容量電圧(CV)測定に用いた試料の構造について、図19を用いて説明する。

#### 【0265】

ガラス基板501上に厚さ300nmのチタン膜503をスパッタリング法により形成し、その上に厚さ100nmの窒化チタン膜505をスパッタリング法により形成した。

#### 【0266】

窒化チタン膜505上に酸化物半導体膜507として、厚さ2000nmのIn-Ga-Zn-O膜をスパッタリング法により形成した。このときの堆積条件は、スパッタガスとして流量30sccmのAr、流量15sccmの酸素を用い、ターゲット及び基板間隔を60mmとし、直流(DC)電源0.5kW、成膜温度を室温とした。

#### 【0267】

次に、CV法により厚さ300nmの酸化窒化シリコン膜509を形成し、その上に厚さ300nmの銀膜511を形成した。

#### 【0268】

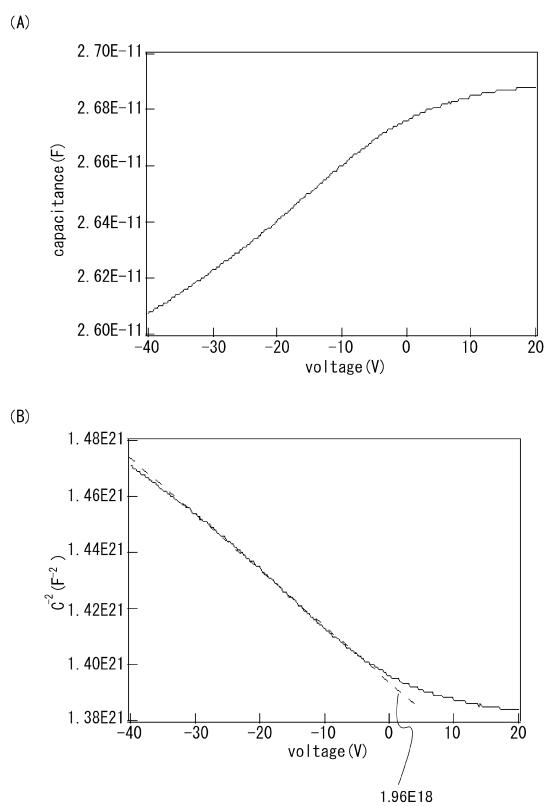

次に、当該試料をCV測定した結果を図20(A)に示し、図20(A)に示す測定結果から電圧に対するC<sup>-2</sup>の曲線を図20(B)に示す。ここで、試料の弱反転状態でのC

10

20

30

40

50

$C^{-2}$  の曲線の傾きを数式 7 に代入することで、キャリア密度を求めることができる。なお、図 20 (B) において  $C^{-2}$  の曲線を実線で示し、弱反転状態での  $C^{-2}$  の傾きを破線で示す。傾きは  $1.96 \times 10^{-8} C^{-2} V^{-1}$  であった。

【0269】

【数 7】

$$n = - \left( \frac{2}{e \epsilon_0 \epsilon_s} \right) \left/ \frac{d(1/C)^2}{dV} \right.$$

【0270】

なお、 $e$  は素電荷、 $\epsilon_s$  は酸化物半導体の比誘電率、 $\epsilon_0$  は真空の誘電率、 $n$  はキャリア密度である。 10

【0271】

数式 7 から、本実施例の酸化物半導体のキャリア密度は、 $6 \times 10^{-10} \text{ cm}^{-3}$  であった。このことから、本実施例に示す酸化物半導体のキャリア密度が極めて低いことがわかる。 。

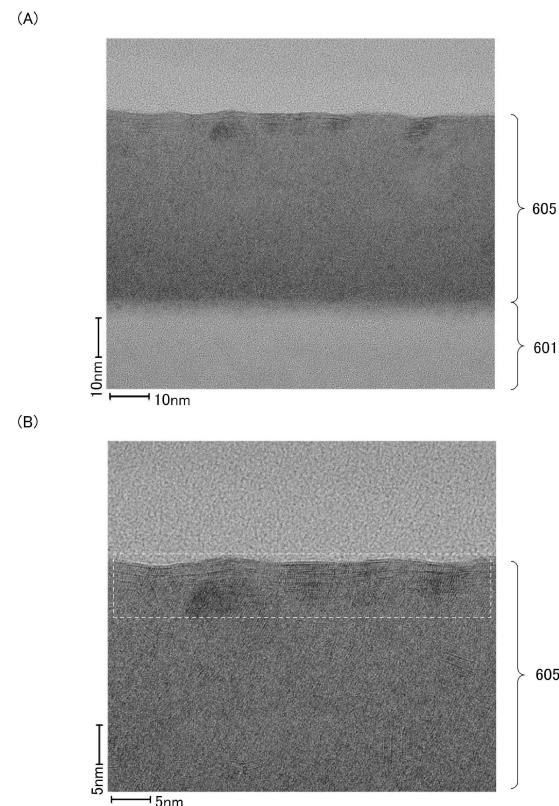

【実施例 3】

【0272】

本実施例では、加熱処理により脱水化または脱水素化した酸化物半導体膜について、TEM 分析法を用いて解析した結果について図 21 乃至図 23 を用いて説明する。 20

【0273】

はじめに試料の作製方法について、説明する。

【0274】

基板 601 上にスパッタリング法により酸化物半導体膜を成膜した。

【0275】

ここでは、基板 601 として、EagleXG 基板（コーニング社製）を用いた。酸化物半導体膜は、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$  の金属酸化物ターゲットを使用して、In-Ga-Zn-O 膜 603 を堆積した。当該試料を比較例である試料 B とする。

【0276】

次に、電気炉装置を用い窒素ガス雰囲気中で 650 、60 分間の加熱処理を行った。加熱処理を行った酸化物半導体膜を酸化物半導体膜 605 とする。当該試料を試料 A とする。 30

【0277】

それぞれの試料の結晶状態を調べるために、高分解能透過電子顕微鏡（日立製作所製「H9000-NAR」：TEM）を用いて、加速電圧を 300 kV とし、断面の結晶状態の観察を行った。図 21 に試料 A の断面写真を示し、図 22 に試料 B の断面写真を示す。なお、図 21 (A)、図 22 (A) は低倍写真（200 万倍）、図 21 (B)、図 22 (B) は高倍写真（400 万倍）である。

【0278】

図 21 に示す 650 で 60 分間、電気炉での加熱処理を行った試料 A は、その断面において、表層部に連続した格子像が観察された。特に図 21 (B) の高倍写真では、白枠で囲んだ領域に明瞭な格子像が観察され、揃った結晶の存在が示唆されている。このことから、650 で 60 分間、電気炉での加熱処理において In-Ga-Zn-O 膜の表層部は結晶化し、結晶領域を有するようになることが明らかとなった。なお、表層部を除くその他の領域においては、連続した明瞭な格子像は観察されず、非晶質領域の所々に微結晶粒子が浮いている様子が確認された。微結晶の粒子サイズは 2 nm 以上 4 nm 以下の所謂ナノクリスタルであった。 40

【0279】

一方、図 22 (試料 B) の断面写真からは膜厚方向のどの領域においても明瞭な格子像は観察されず、非晶質であることが確認された。 50

## 【0280】

次に、650℃で60分間、電気炉での加熱処理を行った試料Aの表層部の拡大写真を図23(A)に示し、結晶領域の電子線回折パターンを図23(B)~図23(F)に示す。表層部の拡大写真(図23(A))には、格子像が並ぶ方向を示した1~5の矢印が示してあり、膜の表面に対して垂直方向に結晶が成長していることがわかる。図23(B)、(C)、(D)、(E)、(F)に示す電子線回折パターンはそれぞれ、矢印番号の1、2、3、4、5の位置で観測されたもので、C軸方向の配向が確認されている。また、この電子線回折パターンと既知の格子定数を比較した結果、結晶構造は $InGaZnO_4$ であることが判明した。

## 【0281】

以上の解析結果により、650℃で60分間、電気炉での加熱処理を行った試料は、その表層部に結晶領域が存在することが確認できた。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

(B)

【図17】

(B)

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 29/50

M

(56)参考文献 特開2005-294571 (JP, A)

特開昭60-012769 (JP, A)

特開2007-123861 (JP, A)

米国特許出願公開第2010/0136743 (US, A1)

特開2003-298062 (JP, A)

特開2009-167087 (JP, A)

米国特許出願公開第2009/0152506 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01L 29/786

H 01L 21/336