(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6613044号

(P6613044)

(45) 発行日 令和1年11月27日(2019.11.27)

(24) 登録日 令和1年11月8日(2019.11.8)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1333 (2006.01)

G02F 1/1333

請求項の数 7 (全 40 頁)

(21) 出願番号 特願2015-80608 (P2015-80608)

(22) 出願日 平成27年4月10日 (2015.4.10)

(65) 公開番号 特開2016-1301 (P2016-1301A)

(43) 公開日 平成28年1月7日 (2016.1.7)

審査請求日 平成30年4月9日 (2018.4.9)

(31) 優先権主張番号 特願2014-88200 (P2014-88200)

(32) 優先日 平成26年4月22日 (2014.4.22)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(31) 優先権主張番号 特願2014-88223 (P2014-88223)

(32) 優先日 平成26年4月22日 (2014.4.22)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 楠 純慈

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 石谷 哲二

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 初見 亮

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置、表示モジュール、及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板と、第2の基板と、液晶層と、を有する表示装置であって、

第1のトランジスタと、第1の容量素子と、第1の配線と、第2の配線と、第1の電極と、第2のトランジスタと、第2の電極と、第2の容量素子と、第3の電極と、を有し、

前記液晶層は、前記第1の電極と、前記第3の電極との間に設けられ、

前記第1のトランジスタと、前記第1の容量素子と、前記第1の配線と、前記第1の電極とは、前記第1の基板に設けられ、

前記第1のトランジスタは、前記第1の電極に電気的に接続され、

前記第1の電極は、前記液晶層の画素電極としての機能を有し、

10

前記第1の容量素子の一方の電極は、前記第1の電極に電気的に接続され、

前記第1の容量素子の他方の電極は、前記第1の配線に電気的に接続され、

前記第1の配線は、第1の信号が与えられる機能を有し、

前記第2のトランジスタと、前記第2の電極と、前記第2の容量素子と、前記第3の電極とは、前記第2の基板に設けられ、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の電極に電気的に接続され、

前記第2の電極は、前記第2の容量素子の一方の電極としての機能を有し、

前記第3の電極は、前記第2の容量素子の他方の電極としての機能を有し、

前記第3の電極は、前記液晶層の対向電極としての機能を有し、

20

前記第3の電極は、前記第2の配線に電気的に接続され、

前記第2の配線は、第2の信号が与えられる機能を有し、

前記第2の信号は、前記第1の信号と同期して変動する信号である、ことを特徴とする表示装置。

**【請求項2】**

請求項1において、

前記第2の基板は、第3のトランジスタと、第4のトランジスタと、を有し、

前記第3のトランジスタのゲートは、前記第2の電極に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第3の配線に電気的に接続され、

10

前記第3の配線は、定電位が与えられる機能を有し、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、第4の配線に電気的に接続され、

20

前記第4の配線は、前記第2の電極の電位に従って電位が変化する機能を有する、ことを特徴とする表示装置。

**【請求項3】**

請求項2において、

前記第2のトランジスタは、半導体層が酸化物半導体を有し、

前記第3のトランジスタは、半導体層が酸化物半導体を有することを特徴とする表示装置。

20

**【請求項4】**

請求項2または3において、

前記第2の電極は、前記第2のトランジスタが有する半導体層と、前記第3のトランジスタが有する半導体層と、同じ層に設けられる電極である、ことを特徴とする表示装置。

**【請求項5】**

請求項1乃至4のいずれか一において、

前記第1のトランジスタは、第1の半導体層を有し、

前記第1の半導体層は、酸化物半導体を有し、

前記第1の半導体層は、第1の金属元素を有し、

前記第1の容量素子の他方の電極は、前記第1の金属元素と、酸素とを有し、

前記第1の半導体層は、第1の水素濃度である領域を有し、

前記第1の容量素子の他方の電極は、第2の水素濃度である領域を有し、

前記第1の水素濃度と、前記第2の水素濃度は、互いに異なる、ことを特徴とする表示装置。

30

**【請求項6】**

請求項1乃至5のいずれか一に記載の前記表示装置と、前記表示装置に電気的に接続されたプリント基板と、を有することを特徴とする表示モジュール。

**【請求項7】**

40

請求項6に記載の表示モジュールと、操作ボタンと、を有することを特徴とする電子機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一態様は、表示装置、表示モジュール、及び電子機器に関する。

**【0002】**

なお本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マタ

50

一)に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。

【背景技術】

【0003】

タッチセンサ機能を有する表示装置が普及している(特許文献1を参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-196023号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0005】

タッチセンサ機能を有する表示装置では、表示装置にタッチセンサ機能を付与するため、筐体が厚くなってしまうといった問題がある。また筐体を薄くすると、電極に与える信号によって、表示素子に加わる電位が変動してしまい、表示品位が低下するといった問題がある。

【0006】

本発明の一態様は、新規な表示装置等を提供することを課題の一とする。

【0007】

20

または、本発明の一態様は、薄型化を実現できる、新規な構成の表示装置等を提供することを課題の一とする。または、本発明の一態様は、表示素子に加わる電位の変動を打ち消すことのできる、新規な構成の表示装置等を提供することを課題の一とする。

【0008】

なお本発明の一態様の課題は、上記列挙した課題に限定されない。上記列挙した課題は、他の課題の存在を妨げるものではない。なお他の課題は、以下の記載で述べる、本項目で言及していない課題である。本項目で言及していない課題は、当業者であれば明細書又は図面等の記載から導き出せるものであり、これらの記載から適宜抽出することができる。なお、本発明の一態様は、上記列挙した記載、及び/又は他の課題のうち、少なくとも一つの課題を解決するものである。

30

【課題を解決するための手段】

【0009】

本発明の一態様は、第1の基板と、第2の基板と、液晶層と、を有する表示装置であって、第1のトランジスタと、第1の容量素子と、第1の配線と、第1の電極と、第2のトランジスタと、第2の電極と、第2の容量素子と、第3の電極と、を有し、液晶層は、第1の電極と、第3の電極との間に設けられ、第1のトランジスタと、第1の容量素子と、第1の配線と、第1の電極とは、第1の基板に設けられ、第1のトランジスタは、第1の電極に電気的に接続され、第1の電極は、液晶層の画素電極としての機能を有し、第1の容量素子の一方の電極は、第1の電極に電気的に接続され、第1の容量素子の他方の電極は、第1の配線に電気的に接続され、第1の配線は、第1の信号が与えられる機能を有し、第2のトランジスタと、第2の電極と、第2の容量素子と、第3の電極とは、第2の基板に設けられ、第2のトランジスタのソース又はドレインの一方は、第2の電極に電気的に接続され、第2の電極は、第2の容量素子の一方の電極としての機能を有し、第3の電極は、第2の容量素子の他方の電極としての機能を有し、第3の電極は、液晶層の対向電極としての機能を有し、第3の電極は、第2の信号が与えられる機能を有し、第2の信号は、第1の信号と同じ周期で変動する信号である表示装置である。

40

【0010】

本発明の一態様において、第2の基板は、第3のトランジスタと、第4のトランジスタと、を有し、第3のトランジスタのゲートは、第2の電極に電気的に接続され、第2のトランジスタのソース又はドレインの他方は、第2の配線に電気的に接続され、第2の配線は

50

、定電位が与えられる機能を有し、第3のトランジスタのソース又はドレインの一方は、第4のトランジスタのソース又はドレインの一方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、第3の配線に電気的に接続され、第3の配線は、第2の電極の電位に従って電位が変化する機能を有する表示装置が好ましい。

【0011】

本発明の一態様において、第2のトランジスタは、半導体層が酸化物半導体を有し、第3のトランジスタは、半導体層が酸化物半導体を有する表示装置が好ましい。

【0012】

本発明の一態様において、第2の電極は、第2のトランジスタが有する半導体層と、第3のトランジスタが有する半導体層と、同じ層に設けられる電極である表示装置が好ましい

10。

【0013】

本発明の一態様において、第1のトランジスタは、第1の半導体層を有し、第1の半導体層は、酸化物半導体を有し、第1の半導体層は、第1の金属元素を有し、第1の電極は、第1の金属元素と、酸素とを有し、第1の半導体層は、第1の水素濃度である領域を有し、第1の電極は、第2の水素濃度である領域を有し、第1の水素濃度と、第2の水素濃度は、互いに異なる表示装置が好ましい。

【0014】

なおその他の本発明の一態様については、以下で述べる実施の形態における説明、及び図面に記載されている。

20

【発明の効果】

【0015】

本発明の一態様は、新規な構成の表示装置等を提供することができる。

【0016】

または、本発明の一態様は、薄型化を実現できる、新規な構成の表示装置等を提供することができる。または、本発明の一態様は、表示素子に加わる電位の変動を打ち消すことができる、新規な構成の表示装置等を提供することができる。そのため、表示品位の向上した表示装置とすることができる。

【図面の簡単な説明】

【0017】

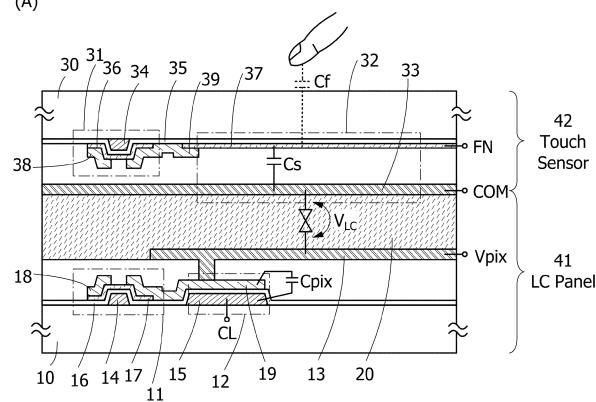

【図1】本発明の一態様を説明するための断面模式図及び波形図。

30

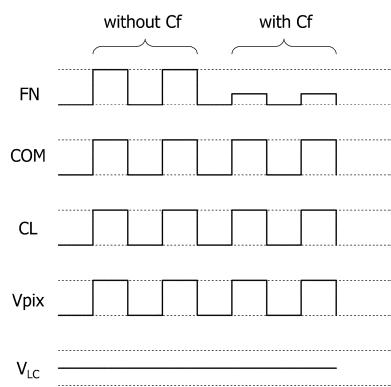

【図2】本発明の一態様を説明するための断面模式図。

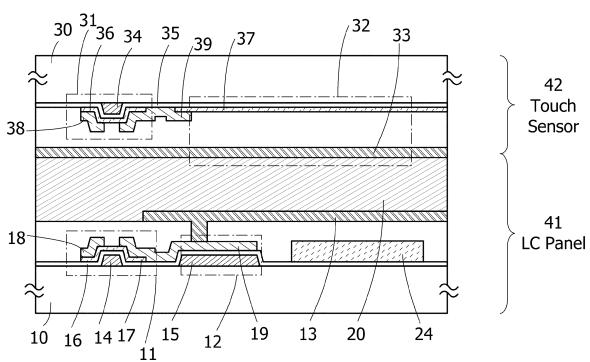

【図3】本発明の一態様を説明するための断面模式図。

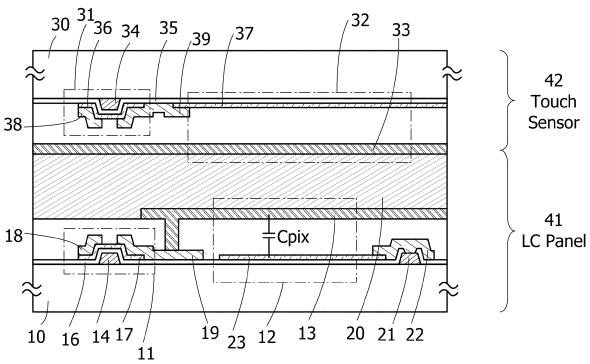

【図4】本発明の一態様を説明するための断面模式図。

【図5】本発明の一態様を説明するための断面模式図。

【図6】本発明の一態様を説明するための回路図。

【図7】本発明の一態様を説明するためのタイミングチャート。

【図8】本発明の一態様を説明するための回路図。

【図9】本発明の一態様を説明するための上面図。

【図10】本発明の一態様を説明するための断面模式図。

40

【図11】本発明の一態様を説明するための断面模式図。

【図12】本発明の一態様を説明するための上面模式図および断面模式図。

【図13】本発明の一態様を説明するための断面模式図。

【図14】本発明の一態様を説明するための断面模式図。

【図15】本発明の一態様の表示モジュールを示す図。

【図16】本発明の一態様の電子機器を示す図。

【図17】本発明の一態様を説明するための断面模式図。

【図18】本発明の一態様を説明するための断面模式図。

【図19】試料構造を説明する図。

【図20】導電率を説明する図。

50

【図21】導電率を説明する図。

【発明を実施するための形態】

【0018】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0019】

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

10

【0020】

また本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレイン領域又はドレイン電極）とソース（ソース端子、ソース領域又はソース電極）の間にチャネル領域を有しており、ドレインとチャネル領域とソースとを介して電流を流すことができるものである。

20

【0021】

ここで、ソースとドレインとは、トランジスタの構造又は動作条件等によって変わるために、いざれがソース又はドレインであるかを限定することが困難である。そこで、ソースとして機能する部分、及びドレインとして機能する部分を、ソース又はドレインと呼ばず、ソースとドレインとの一方を第1電極と表記し、ソースとドレインとの他方を第2電極と表記する場合がある。

【0022】

なお本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0023】

なお本明細書において、AとBとが接続されている、とは、AとBとが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、AとBとが電気的に接続されているとは、AとBとの間で、何らかの電気的作用を有する対象物が存在するとき、AとBとの電気信号の授受を可能とするものをいう。

30

【0024】

なお、例えば、トランジスタのソース（又は第1の端子など）が、Z1を介して（又は介さず）、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2を介して（又は介さず）、Yと電気的に接続されている場合や、トランジスタのソース（又は第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

40

【0025】

例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（又は第1の端子な

50

ど)とドレイン(又は第2の端子など)とを介して、Yと電気的に接続され、X、トランジスタのソース(又は第1の端子など)、トランジスタのドレイン(又は第2の端子など)、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース(又は第1の端子など)と、ドレイン(又は第2の端子など)とを、区別して、技術的範囲を決定することができる。なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など)であるとする。

#### 【0026】

なお本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。10

#### 【0027】

なお図面におけるブロック図の各回路ブロックの配置は、説明のため位置関係を特定するものであり、異なる回路ブロックで別々の機能を実現するよう示していても、実際の回路ブロックにおいては同じ回路ブロック内で別々の機能を実現しうるよう設けられている場合もある。また図面における各回路ブロックの機能は、説明のため機能を特定するものであり、一つの回路ブロックとして示していても、実際の回路ブロックにおいては一つの回路ブロックで行う処理を、複数の回路ブロックで行うよう設けられている場合もある。20

#### 【0028】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

#### 【0029】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0030】

##### (実施の形態1)

本実施の形態では、表示装置の構成例、動作の一例について説明する。30

#### 【0031】

本明細書等において表示装置とは、液晶素子等の表示素子を有する装置のことをいう。なお、表示装置は、複数の画素を駆動させる駆動回路等を含む。また、表示装置は、別の基板上に配置された制御回路、電源回路、信号生成回路及びバックライトモジュール等を含み、表示モジュールとよぶこともある。

#### 【0032】

##### <表示装置の断面模式図について>

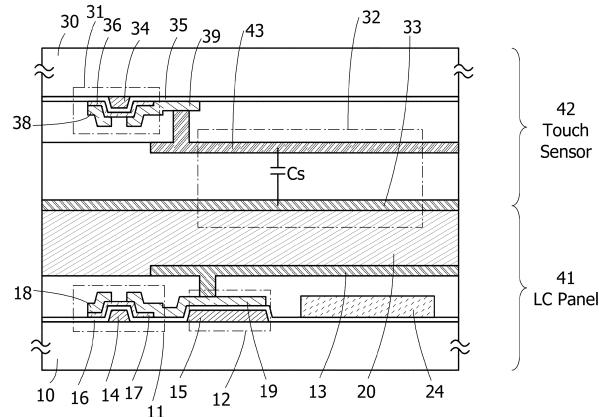

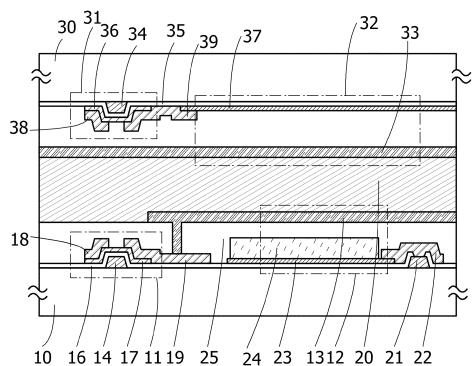

図1(A)は、本発明の一態様である表示装置の断面模式図である。表示装置は、液晶パネル41と、タッチセンサ42とに大別できる。40

#### 【0033】

液晶パネル41と、タッチセンサ42とは、基板10と基板30との間に設けられる各部材で構成される。基板10と基板30との間には、液晶層20を有する。

#### 【0034】

まず液晶パネル41側の構成について説明する。

#### 【0035】

基板10上には、トランジスタ11と、容量素子12と、電極13と、が設けられる。なお電極は、導電層で形成される。以下の説明で述べる電極と導電層を説明のため使い分けているが、電極を導電層、あるいは導電層を電極という場合がある。

#### 【0036】

50

30

40

50

トランジスタ11は、スイッチとしての機能を有する。トランジスタ11は、ソース線（導電層18）と、電極13との電気的な接続を切り替えることができる。

#### 【0037】

トランジスタ11は、導電層14と、絶縁層16と、半導体層17と、導電層18と、導電層19と、を有する。導電層14は、ゲート電極としての機能を有する。絶縁層16は、ゲート絶縁膜としての機能を有する。半導体層17は、チャネル形成領域を有する半導体層としての機能を有する。導電層18は、ソース電極又はドレイン電極としての機能を有する。導電層19は、ソース電極又はドレイン電極としての機能を有する。導電層19は、容量素子12の一部であり、導電層19は電極13と接続される。

#### 【0038】

図1(A)において、導電層14、絶縁層16、半導体層17、導電層18、又は導電層19は、単層で示したが、2層以上の積層であってもよい。2層以上の積層は、異なる材料の積層でもよいし、同じ材料の積層であってもよい。

#### 【0039】

図1(A)において図示するトランジスタ11は、ボトムゲート構造のトランジスタであるが、これに限らない。トップゲート構造のトランジスタでもよい。また、チャネルエッヂ型を図示しているが、チャネル保護型にすることもできる。

#### 【0040】

なおトランジスタ11は、酸化物半導体を半導体層に用いたトランジスタ（以下、OSトランジスタという）であることが好ましい。OSトランジスタをトランジスタ11に用いることで、非導通状態時にソースとドレインとの間に流れるオフ電流を低くすることができる。そのため、電極13を電気的に浮遊状態としやすくすることができる。また、電極13に画像データに応じた電位を保持し続けることができる。

#### 【0041】

容量素子12は、導電層15と、絶縁層16と、導電層19と、を有する。容量素子12は、Cpixで図示している。導電層15は、Cpixの一方の電極としての機能を有する。CLは、導電層15に与えられる信号を表している。導電層19は、Cpixの他方の電極としての機能を有する。導電層15と、導電層19との間には、絶縁層16が設けられる。導電層19は、トランジスタ11及び電極13と接続される。

#### 【0042】

容量素子12は、透光性を有する導電層で形成してもよい。該構成とすることで画素の開口率の向上を図ることができる。開口率の向上により、バックライトの光を弱めても同じ輝度による表示が得られるため、低消費電力化を図ることができる。

#### 【0043】

電極13は、液晶層20の画素電極としての機能を有する。電極13は、透光性を有する材料で形成してもよいし、反射性を有する材料で形成してもよい。Vpixは、電極13の電位を表している。電極13は、導電層19でトランジスタ11及び容量素子12と接続される。

#### 【0044】

液晶層20は、縦電界方式の液晶層を有する。縦電界方式の液晶層としては、例えば、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、VA(Vertical Alignment)モード、MVA(Multi-domain Vertical Alignment)モード等が代表的である。以下、本発明の一態様では、TNモードの液晶層として説明を行う。

#### 【0045】

電極13は、基板30側にある電極33との間に電界を生じさせる。電極33は、対向電極としての機能を有する。電界は、VLCで図示している。VLCによって液晶層20が有する液晶分子の配向を制御することができる。なお電極13、33の間に、液晶層20を備える構成を、液晶素子ともいう。

#### 【0046】

10

20

30

40

50

以上が、液晶パネル41側の説明である。

**【0047】**

次いで、タッチセンサ42側の構成について説明する。

**【0048】**

基板30上には、トランジスタ31と、容量素子32と、電極33と、電極37と、が設けられる。

**【0049】**

トランジスタ31は、スイッチとしての機能を有する。トランジスタ31は、配線（導電層38）と、電極37との電気的な接続を切り替えることができる。

**【0050】**

トランジスタ31は、導電層34と、絶縁層35と、半導体層36と、導電層38と、導電層39と、を有する。導電層34は、ゲート電極としての機能を有する。絶縁層35は、ゲート絶縁膜としての機能を有する。半導体層36は、チャネル形成領域を有する半導体層としての機能を有する。導電層38は、ソース電極又はドレイン電極としての機能を有する。導電層39は、ソース電極又はドレイン電極としての機能を有する。導電層39は、電極37と接続される。

10

**【0051】**

トランジスタ31は、トランジスタ11と同様に、ボトムゲート構造以外の構造、各層を積層して設ける等、の変形を行うことができる。

**【0052】**

なおトランジスタ31は、トランジスタ11と同様に、OSトランジスタであることが好みしい。OSトランジスタをトランジスタ31に用いることで、電極37を電気的に浮遊状態としやすくすることができる。また、電極37に一度与えた電位を保持し続けることができる。

20

**【0053】**

また、トランジスタ31をOSトランジスタとすることで、半導体層36と同層に設けられる電極37を半導体層36と同じ材料で形成することができる。電極37は、酸化物半導体で構成されることで、半導体層36を形成後に、導電性を有する電極37に変質させることができる。

**【0054】**

30

容量素子32は、電極37と、電極33とによって構成される。容量素子32は、Csで図示している。電極37は、Csの一方の電極としての機能を有する。FNは、電極37の電位を表している。電極33は、Csの他方の電極としての機能を有する。電極33と、電極37との間には、カラーフィルタ（図示せず）や層間絶縁層等が設けられる。電極37は、トランジスタ31と接続される。

**【0055】**

なお電極37は、半導体層36と同層に形成される。電極37は、半導体層36と同時に形成し、形成後に導電性を付与する構成とする。該構成とすることで、製造コストの削減を図ることができる。また、電極37は、透光性を有する。そのため、電極37は、半導体層36と同層に設ける構成に限らない。例えば、透光性を有する導電層を電極37として、トランジスタ31に接続されるように設ける構成としてもよい。

40

**【0056】**

なお電極37は、マトリクス状に配置される。なお電極37は、数ミリ角の大きさを有する。電極37は、画素電極として機能する電極13よりも専有面積を大きく設計される。1つの電極37は、複数の電極13と重畳する。

**【0057】**

電極33は、液晶層20の対向電極としての機能を有する。電極33は、透光性を有する。COMは、電極33に与えられる信号を表している。

**【0058】**

なお電極33は、複数の電極37及びトランジスタ31と重畳するように、配置される。

50

遮光層を配置することで、電極 3 3 を分断して配置することもできる。

**【0059】**

以上が、タッチセンサ 4 2 側の説明である。

**【0060】**

図 1 ( A ) に示す表示装置の断面模式図を用いて、動作を説明し、本発明の一態様による利点を詳述する。図 1 ( A ) の表示装置は、静電容量方式のタッチセンサとしての機能を有する。そのため、図 1 ( A ) では、検出対象との間に生じる容量成分を  $C_f$  として示している。 $C_f$  がある場合、タッチしたとして検出でき、 $C_f$  がない場合、タッチしていないと検出できる。

**【0061】**

10

図 1 ( B ) は、電極 3 7 の電位  $F_N$  、電極 3 3 に与えられる信号  $C_{OM}$  、導電層 1 5 に与えられる信号  $C_L$  、電極 1 3 の電位  $V_{pix}$  、電界  $V_{LC}$  の、 $C_f$  がある場合とない場合についての、変化について説明する図である。

**【0062】**

$C_f$  がない場合、すなわちタッチしていない場合を説明する。

**【0063】**

まず電位  $F_N$  は、トランジスタ 3 1 を導通状態として予め所定の電位にしておく。そしてトランジスタ 3 1 を非導通状態として、電極 3 7 を電気的に浮遊状態しておく。電極 3 7 が電気的に浮遊状態となることで電位  $F_N$  は、 $C_s$  の容量結合によって、信号  $C_{OM}$  の変化に追随する。 $C_f$  がない場合、電極 3 7 に寄生する容量は小さい。そのため、例えば図 1 ( B ) に示すように、信号  $C_{OM}$  を一定の周期で振動させることで、電位  $F_N$  の追随した変化を検出できる ( *with*  $C_f$  )。

20

**【0064】**

$C_f$  がある場合、すなわちタッチする場合を説明する。

**【0065】**

$C_f$  がある場合は、 $C_f$  がない場合と同様であるが、異なる点として電極 3 7 に寄生する容量が増える。この場合、信号  $C_{OM}$  を一定の周期で振動させても、 $C_f$  は増えた分、電位  $F_N$  の追随した変化が小さくなっている検出される ( *with*  $C_f$  )。

**【0066】**

$C_f$  の有無に関わらず、タッチを検出するため、信号  $C_{OM}$  を変化させる。信号  $C_{OM}$  を変化させると、電界  $V_{LC}$  が変化してしまう。電界  $V_{LC}$  が変化すると、液晶層 2 0 が有する液晶分子の配向が良好な表示品位が得られない。

30

**【0067】**

そのため、本発明の一態様では、信号  $C_{OM}$  の変化に連動して、導電層 1 5 に与えられる信号  $C_L$  を変化させる。

**【0068】**

なお信号  $C_L$  を変化させる際は、電位  $V_{pix}$  が電気的に浮遊状態としておく。具体的には、トランジスタ 1 1 を導通状態として、電位  $V_{pix}$  を画像データに応じた電位にしておく。そしてトランジスタ 1 1 を非導通状態として、電極 1 3 を電気的に浮遊状態としておく。電極 1 3 が電気的に浮遊状態となることで電位  $V_{pix}$  は、 $C_{pix}$  の容量結合によって、信号  $C_L$  の変化に追随する。

40

**【0069】**

信号  $C_L$  の変化によって、電位  $V_{pix}$  を変動させることができる。信号  $C_L$  は、信号  $C_{OM}$  による電位の変化による電界  $V_{LC}$  の変化を、電位  $V_{pix}$  の変化によって打ち消すように、変化させる。具体的には、信号  $C_L$  は、信号  $C_{OM}$  と同じ周期で変動させる構成とする。

**【0070】**

該構成とすることで、電位  $V_{pix}$  の変化を、信号  $C_{OM}$  の変化に連動させ、電界  $V_{LC}$  を一定にすることができる。電界  $V_{LC}$  を一定にすることで、良好な表示品位を得ることができる。

50

**【 0 0 7 1 】**

また本発明の一形態によって、一対の基板間に表示素子、タッチセンサを駆動するための素子を設けることができる。一対の基板間では、他の基板等の部材を削減することができる。従って、タッチセンサ 4 2 の薄型化を実現することができる。

**【 0 0 7 2 】**

なお本実施の形態で説明した表示装置の構成は、一例として液晶素子を有する表示装置に適用して動作させる場合を示したが、本発明の一態様は、これに限定されない。場合によつては、または、状況に応じて、本発明の一態様は、液晶素子以外の表示素子を有する表示装置に適用することができる。液晶素子以外の表示素子としては、例えば、発光素子、あるいは電気泳動素子を挙げることができる。

10

**【 0 0 7 3 】**

または、本実施の形態で説明したトランジスタとして、酸化物半導体を有するトランジスタを用いた場合の例を示したが、本発明の一態様は、これに限定されない。場合によつては、または、状況に応じて、本発明の一態様は、酸化物半導体とは異なる半導体材料を用いたトランジスタを用いてもよい。そのようなトランジスタとして、例えば、本発明の一態様は、シリコンやゲルマニウムなどを有するトランジスタを用いてもよい。

**【 0 0 7 4 】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

**【 0 0 7 5 】**

20

**( 実施の形態 2 )**

本実施の形態では、実施の形態 1 で説明した表示装置の変形例について説明する。

**【 0 0 7 6 】**

< 断面模式図の変形例について（表示パネル）>

図 2 には、図 1 ( A ) で説明した断面模式図の変形例を示す。

**【 0 0 7 7 】**

図 1 ( A ) では、 C p i x を導電層 1 5 と導電層 1 9 とで形成したが、別の構成としてもよい。例えば、図 2 の構成とすることができる。

**【 0 0 7 8 】**

図 2 では、 C p i x の一方の電極として、導電層 2 2 を介して導電層 2 1 に接続された、電極 2 3 を示している。

30

**【 0 0 7 9 】**

導電層 2 1 は、導電層 1 4 と同層に形成される。導電層 2 2 は、導電層 1 8 , 1 9 と同層に形成される。電極 2 3 は、半導体層 1 7 と同層に形成される。

**【 0 0 8 0 】**

また、トランジスタ 1 1 を O S トランジスタとすることで、半導体層 1 7 と同層に設けられる電極 2 3 を半導体層 1 7 と同じ材料で形成することができる。この場合、電極 2 3 は、半導体層 1 7 と同時に形成された膜を加工して形成される。このため、電極 2 3 は、半導体層 1 7 と同様の元素を有する。また、半導体層 1 7 と同様の結晶構造、または異なる結晶構造を有する。しかしながら、半導体層 1 7 と同時に形成された膜に、不純物または酸素欠損を有せしめることで、導電性を付与することが可能である。この結果、半導体層 1 7 と同時に形成された膜は、電極 2 3 となる。電極 2 3 に含まれる不純物の代表例としては、希ガス、水素、ホウ素、窒素、フッ素、アルミニウム、およびリンの一以上がある。希ガスの代表例としては、ヘリウム、ネオン、アルゴン、クリプトンおよびキセノンがある。

40

**【 0 0 8 1 】**

このため、半導体層 1 7 及び電極 2 3 は共に、絶縁層 1 6 上に形成されるが、不純物濃度が異なる。具体的には、半導体層 1 7 と比較して、電極 2 3 の不純物濃度が高い。例えば、半導体層 1 7 において、二次イオン質量分析法により得られる水素濃度は、  $5 \times 10^{-1}$

<sup>9</sup> atoms / cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、好ましく

50

は  $1 \times 10^{-8}$  atoms/cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{-7}$  atoms/cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{-6}$  atoms/cm<sup>3</sup> 以下である。一方、電極 23において、二次イオン質量分析法により得られる水素濃度は、 $8 \times 10^{-9}$  atoms/cm<sup>3</sup> 以上、好ましくは  $1 \times 10^{-8}$  atoms/cm<sup>3</sup> 以上、好ましくは  $5 \times 10^{-8}$  atoms/cm<sup>3</sup> 以上である。また、半導体層 17と比較して、電極 23に含まれる水素濃度は2倍、または10倍以上である。

#### 【0082】

半導体層 17の水素濃度を上記範囲とすることで、半導体層 17におけるキャリアである電子の生成を抑制することが可能である。

#### 【0083】

また、電極 23は、半導体層 17より抵抗率が低い。電極 23の抵抗率が、半導体層 17の抵抗率の  $1 \times 10^{-8}$  倍以上  $1 \times 10^{-1}$  倍未満であることが好ましく、代表的には  $1 \times 10^{-3}$  cm以上  $1 \times 10^{-4}$  cm未満、または抵抗率が  $1 \times 10^{-3}$  cm以上  $1 \times 10^{-1}$  cm未満であるとよい。

#### 【0084】

電極 23は、半導体層 17と同時に形成し、形成後に導電性を付与する構成とする。該構成とすることで、製造コストの削減を図ることができる。

#### 【0085】

また、電極 13及び電極 23は、透光性を有する。Cpixを、透光性を有する容量素子とすることができます。透光性を有するため、Cpixの容量を大きくとることができます。

#### 【0086】

また別の構成として図 1(A)は、液晶パネル 41側にカラーフィルタを設けた構成としてもよい。

#### 【0087】

図 3では、液晶パネル 41側にカラーフィルタ 24を設けた構成を示している。該構成とすることで、タッチセンサ 42側の部材を削減し、電極 33表面の平坦性を向上させることができる。

#### 【0088】

なお図 3の構成において、電極 23を Cpixの一方の電極に用いる図 2の構成を適用してもよい。この場合の断面模式図の構成を図 17に示す。

#### 【0089】

<断面模式図の変形例について(タッチセンサ)>

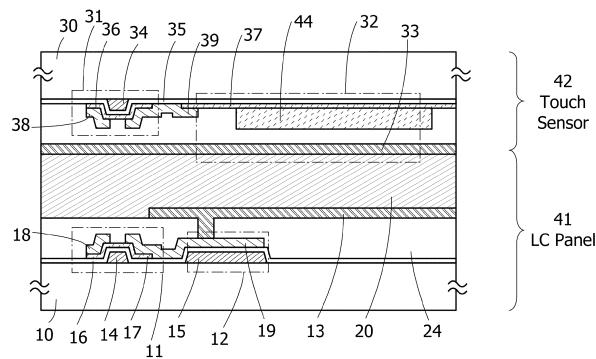

また別の構成として、図 4には、図 1(A)で説明した断面模式図の変形例を示す。

#### 【0090】

図 1(A)では、Csを電極 37と電極 33とで形成したが、別の構成としてもよい。例えば、図 4の構成とすることができます。

#### 【0091】

図 4では、Csの一方の電極を、別途設けた電極 43とする。そして、Csを電極 43と電極 33とで形成する構成とする。該構成とすることで、Csをトランジスタ 31と異なる層に形成することができる。そのため、Csの容量を大きくとることができます。

#### 【0092】

なお電極 43は、透光性を有する導電層である。例えば電極 13と同じ材料で形成することができます。

#### 【0093】

また別の構成として図 1(A)は、タッチセンサ 42側にカラーフィルタを設けた構成としてもよい。

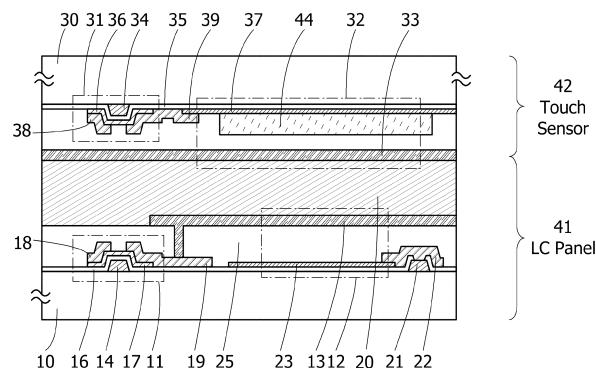

#### 【0094】

図 5では、タッチセンサ 42側にカラーフィルタ 44を設けた構成を示している。該構成とする場合、電極 33の表面の平坦性を確保するため、カラーフィルタ 44と電極 33との間に平坦化膜等を設けることが好ましい。

10

20

30

40

50

**【0095】**

なお図5の構成において、電極23をCpixの一方の電極に用いる図2の構成を適用してもよい。この場合の断面模式図の構成を図18に示す。

**【0096】**

<液晶パネル、タッチセンサの回路図について>

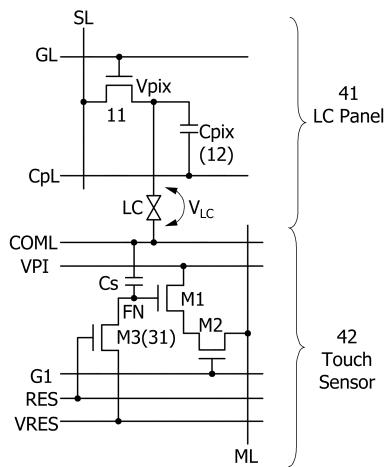

次いで、図1(A)で図示したトランジスタ11を含む液晶パネル41の画素回路と、図1(A)で図示したトランジスタ31を含むタッチセンサ42の回路構成とを併せた回路の一例、及び動作の一例について説明する。

**【0097】**

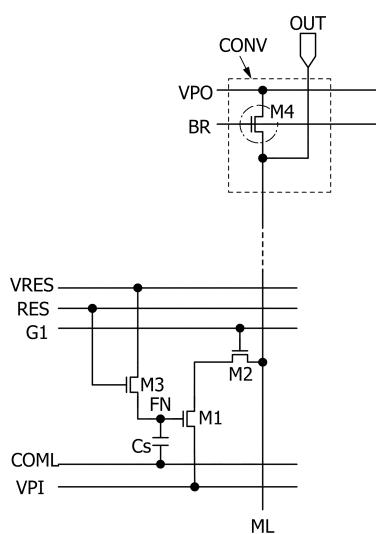

図6は、液晶パネル41の画素回路図と、タッチセンサ42の回路図と、を併せた回路図である。液晶パネル41の画素回路図と、タッチセンサ42の回路図とは、液晶素子LCを挟んで、上下に示している。10

**【0098】**

液晶パネル41側の回路図では、図1(A)の構成で説明した符号を付している。また図6では、ゲート線GL、ソース線SL、容量線CPLを併せて示している。容量線CPLは、信号CLが与えられる配線である。

**【0099】**

タッチセンサ42の回路図では、図1(A)の構成で説明した符号を付している。また図6では、トランジスタM1乃至M3、コモン線COML、定電位である読み出し電位VPIを与える配線、リセット電位VRESを与える配線、リセット線RESET、読み出し選択線G1、読み出し線MLを併せて示している。コモン線COMLは、信号COMが与えられる配線である。トランジスタM3は、図1(A)のトランジスタ31に相当する。20

**【0100】**

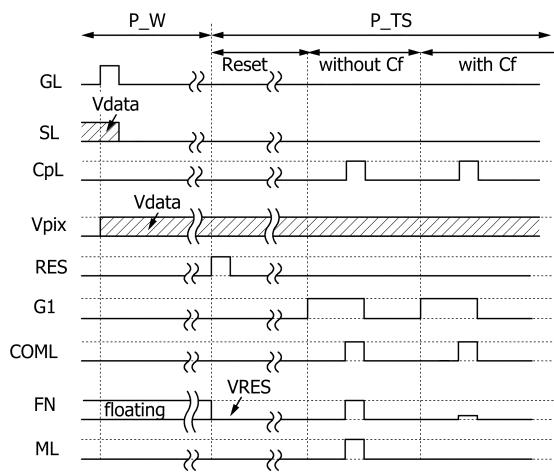

次いで図7では、図6の回路図のタイミングチャートの一例を示す。

**【0101】**

図7では、画像データ(Vdata)を書きこむ期間P\_W、検出対象を検出する期間P\_TSに分けて説明する。期間P\_TSは、さらにリセット期間RESET、非検出期間(タッチなし:without Cf)、検出期間(タッチあり:with Cf)に分けて説明する。

**【0102】**

各トランジスタは、nチャネル型として説明する。この場合、トランジスタに与える信号は、Hレベルで導通状態、Lレベルで非導通状態となる。なお電極37の電位FNは、リセット電位VRESとなることでLレベルとなるとして説明する。30

**【0103】**

まず期間P\_Wについて説明する。

**【0104】**

期間P\_Wでは、ゲート線GLをHレベルにして、Vpixを、ソース線SLに与えられたVdataと等電位にする。この間、タッチセンサの各信号はLレベル、電極37は電気的に浮遊状態となっている。

**【0105】**

VpixをVdataとして、ゲート線GLをLレベルにする。トランジスタ11のオフ電流が低いため、Vpixでは、Vdataが保持される。

**【0106】**

次いで、期間P\_TSについて説明する。

**【0107】**

リセット期間RESETでは、リセット線RESETをHレベルにして、電極37の電位FNをVRESと等電位にする。

**【0108】**

リセット線RESETをLレベルにする。トランジスタM3のオフ電流が低いため、電極37では、VRESが保持される。40

**【 0 1 0 9 】**

非検出期間  $w i t h o u t \ C f$ 、及び検出期間  $w i t h \ C f$  では、読み出し選択線  $G_1$  を H レベルにする。そしてコモン線  $C O M L$  と容量線  $C p L$  に与える信号を同じ周期で変動させる。すると、図 1 (B) で説明したように、 $C f$  の有無に従って電極 37 の電位  $F_N$  の変化に差が生じる。この差は、トランジスタ  $M 1$  の導通状態に表れる。すなわち、 $C f$  がない場合はトランジスタ  $M 1$  が導通し、 $C f$  がある場合はトランジスタ  $M 1$  が非導通となる。

**【 0 1 1 0 】**

トランジスタ  $M 2$  を導通状態とし、トランジスタ  $M 1$  も導通状態の場合には、読み出し線  $M L$  の電位が変化し、電流が流れる。この場合、 $C f$  がないと判断される。また、トランジスタ  $M 2$  を導通状態とし、トランジスタ  $M 1$  が非導通状態の場合には、読み出し線  $M L$  の電位が変化せず、電流が流れない。この場合、 $C f$  があると判断される。10

**【 0 1 1 1 】**

図 8 には、読み出し線  $M L$  に流れる電流を電圧に変換する、読み出しひ回路の回路図を示す。

**【 0 1 1 2 】**

図 8 には、図 6 で説明したタッチセンサの回路図と併せて、読み出しひ回路  $C O N V$  の一例を図示している。読み出しひ回路  $C O N V$  は、トランジスタ  $M 4$  を有する。

**【 0 1 1 3 】**

トランジスタ  $M 4$  を有する読み出しひ回路  $C O N V$  は、ソースフォロワとして機能させる。20

電位  $V P O$  は、高電源電位である。信号  $B R$  は、読み出し線  $M L$  の電位を読み出すタイミングでトランジスタ  $M 4$  を導通状態とするよう制御する。トランジスタ  $M 4$  に流れる電流に応じて、出力端子  $O U T$  では、タッチセンサに流れる電流を電圧に変換することができる。

**【 0 1 1 4 】**

なおタッチセンサは、容量素子  $C s$  を構成する電極と、読み出し線  $M L$  とを別の層で形成することができる。

**【 0 1 1 5 】**

一例としては、図 9 に示すように、容量素子の一方の電極 37 と読み出し線  $M L$  とを別の層で形成し、読み出し線  $M L$  を細い幅で形成する。該構成とすることで、寄生容量を小さくできる。これにより、タッチセンサの検出感度の低下を抑制できる。30

**【 0 1 1 6 】**

本発明の一態様の構成では、コモン線  $C O M L$  と容量線  $C p L$  に与える信号を同じ周期で変動させる。そのため、液晶素子  $L C$  に加わる  $V d a t a$  を変動させることなく、 $C f$  の検出を行うことができる。液晶素子において配向の乱れはなく、良好な表示品位とすることができる。

**【 0 1 1 7 】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

**【 0 1 1 8 】****( 実施の形態 3 )**

本実施の形態では、実施の形態 1、2 で説明した表示装置の断面図の詳細について説明する。

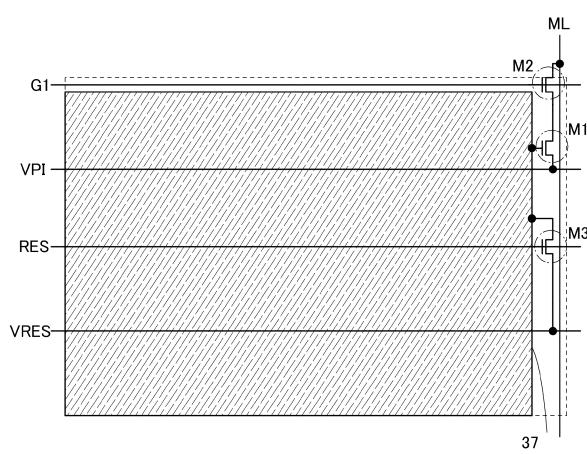

**【 0 1 1 9 】****< タッチパネルの断面構成例 >**

図 10 に本発明の一態様の表示装置の断面模式図を示す。図 10 に示す表示装置は、一対の基板間にタッチセンサ及び液晶素子を有するため、薄型化を図ることができる。

**【 0 1 2 0 】**

図 10 は、表示装置に含まれる、端子部 250a、250b、駆動回路部 250d、及び画素部 250p の断面図を示す。また、画素部 250p は、R (赤)、G (緑)、B (青)40

)の3色の画素で1つの色を表現する構成とする。なお、ここでは、画素部250pにおいて、R(赤)の画素Pr及びG(緑)の画素Pgの断面図を示し、B(青)の画素を省略する。R(赤)の画素Prは、液晶素子201rを有し、G(緑)の画素Pgは、液晶素子201gを有する。

#### 【0121】

また、表示装置は、液晶パネルとタッチセンサとが積層されている。液晶パネルとタッチセンサそれぞれに含まれる駆動回路が、駆動回路部250dで重なる。また、液晶パネルに含まれる液晶素子と、タッチセンサに含まれるトランジスタ及び容量素子とが画素部250pで重なる。

#### 【0122】

なお、表示装置は、例えば、R(赤)、G(緑)、B(青)の3色の画素で1つの色を表現する構成の他、R(赤)、G(緑)、B(青)、W(白)の4色の画素で1つの色を表現する構成、R(赤)、G(緑)、B(青)、Y(黄)の4色の画素で1つの色を表現する構成等を適用できる。色要素としては特に限定はなく、RGBWY以外の色を用いてもよく、例えば、シアン、マゼンタを有してもよい。

#### 【0123】

はじめに、液晶パネル側の構成について説明する。液晶パネルは、端子部250aと、駆動回路部250dと、液晶素子を含む画素部250pとを有する。

#### 【0124】

基板200a上には、トランジスタ202r、202g、204aと、容量素子206r、206gと、電極208r、208gと、接続電極220aとが設けられる。接続電極220aは、端子部250aに設けられる。トランジスタ204aは駆動回路部250dに設けられる。トランジスタ202r、容量素子206r、及び電極208rは、R(赤)の画素Prに設けられる。トランジスタ202g、容量素子206g、及び電極208gは、G(緑)の画素Pgに設けられる。

#### 【0125】

トランジスタ202r、202gは、スイッチとしての機能を有する。なお、トランジスタ202r、202gは同じ構造とすることができます。また、容量素子206r、206gは同じ構造とすることができます。または、トランジスタ202r、202gは異なる構造であってもよい。また、容量素子206r、206gは異なる構造であってもよい。

#### 【0126】

図10において図示するトランジスタ202r、202g、204aは、ボトムゲート構造のトランジスタを図示しているが、これに限らない。トップゲート構造のトランジスタでもよい。また、チャネルエッチ型を図示しているが、チャネル保護型にすることもできる。

#### 【0127】

トランジスタ202r、202g、204a上に絶縁層210aを有し、絶縁層210a上に絶縁層212aを有する。

#### 【0128】

絶縁層210aとしては、トランジスタのチャネル領域を保護する機能を有する。なお、絶縁層210aを設けない構成としてもよい。

#### 【0129】

また、絶縁層212aは、平坦化膜としての機能を有する。絶縁層212aは、ポリイミド樹脂、アクリル樹脂、ポリイミドアミド樹脂、ベンゾシクロブテン樹脂、ポリアミド樹脂、エポキシ樹脂等の耐熱性を有する有機材料を用いて形成される。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層212aを形成してもよい。また、絶縁層212aを設けない構成としてもよい。

#### 【0130】

電極208rは、液晶素子201rの画素電極としての機能を有し、電極208gは、液晶素子201gの画素電極としての機能を有する。電極208r、208gは、絶縁層2

10

20

30

40

50

12a 上に形成される。また、電極 208r は、絶縁層 210a、212a の開口部において、トランジスタ 202r 及び容量素子 206r と電気的に接続される。また、電極 208g は、絶縁層 210a、212a の開口部において、トランジスタ 202g 及び容量素子 206g と電気的に接続される。

#### 【0131】

電極 208r、208g は、可視光において透光性のある導電膜、または可視光において反射性のある導電膜を用いて形成される。可視光において透光性のある導電膜としては、例えば、インジウム (In)、亜鉛 (Zn)、錫 (Sn) の中から選ばれた少なくとも一種を含む材料を用いるとよい。また、可視光において透光性のある導電膜としては、代表的には、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを含むインジウム錫酸化物などの導電性酸化物を用いることができる。可視光において反射性のある導電膜としては、例えば、アルミニウム、または銀を含む材料を用いることができる。

10

#### 【0132】

なお、電極 208r、208g が、可視光において反射性のある導電膜を用いて形成される場合、絶縁層 212a の一部が凹凸状であることで、電極 208r、208g が凹凸状となる。この結果、外光が電極 208r、208g に入射した場合において、電極 208r、208g の表面で光を乱反射することが可能となり、視認性を向上させることができる。

20

#### 【0133】

電極 208r、208g と、基板 200b に設けられた電極 214 との間に生じる電界により、液晶層 228 に含まれる液晶分子の配向を制御することができる。

#### 【0134】

液晶層 228 は、縦電界方式の液晶層を有する。縦電界方式の液晶層としては、例えば、TN (Twisted Nematic) モード、STN (Super Twisted Nematic) モード、VA (Vertical Alignment) モード、MVA (Multi-domain Vertical Alignment) モード等が代表的である。以下、本発明の一態様では、TN モードの液晶層として説明を行う。

#### 【0135】

30

また、液晶層 228 は、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

#### 【0136】

端子部 250a において、接続電極 220a、異方性導電膜 222a、及び FPC 224a を有する。なお、接続電極 220a は、トランジスタ 202r、202g、204a のソース電極及びドレイン電極としての機能を有する導電層と同じ工程で形成される。また、接続電極 220a は、FPC 224a が有する端子と異方性導電膜 222a を介して、電気的に接続される。

40

#### 【0137】

次に、タッチセンサ側の構成について説明する。

#### 【0138】

基板 200b 上には、トランジスタ 202t、204b と、容量素子 206t と、接続電極 220b とが設けられる。接続電極 220b は、端子部 250b に設けられる。トランジスタ 204b は駆動回路部 250d に設けられる。センサの一部であるトランジスタ 202t 及び容量素子 206t は画素部 250p に設けられる。

#### 【0139】

トランジスタ 202t は、スイッチとしての機能を有する。

#### 【0140】

50

トランジスタ 202t は、トランジスタ 202r、202g と同様の構造を適宜用いることができる。または、トランジスタ 202t は、トランジスタ 202r、202g と同様に、ボトムゲート構造のトランジスタを図示しているが、これに限らない。トップゲート構造のトランジスタでもよい。また、チャネルエッチ型を図示しているが、チャネル保護型にすることもできる。

#### 【0141】

トランジスタ 202t、204b 上に絶縁層 210b を有し、絶縁層 210b 上に絶縁層 211 を有する。なお、絶縁層 210b は、電極 238 を露出する開口部を有する。

#### 【0142】

容量素子 206t は、電極 238 と、誘電体層と、電極 214 とで構成される。また、電極 238 は、トランジスタ 202t と接続される。10

#### 【0143】

ここでは、絶縁層 211 と、遮光層 BM と、着色層 CFr、CFG と、絶縁層 212b とで、容量素子 206t の誘電体層を構成する。なお、容量素子 206t の誘電体層は、絶縁層 211、遮光層 BM、着色層 CFr、CFG、及び絶縁層 212b の一以上を有すればよい。

#### 【0144】

液晶素子 201r と重なる位置に、着色層 CFr が設けられ、液晶素子 201g と重なる位置に、着色層 CFG が設けられる。駆動回路部 250d のトランジスタ 204b、204a と重なる領域、及び画素部 250p のトランジスタ 202r、202g、202t と重なる領域に、遮光層 BM が設けられている。なお、遮光層 BM の代わりに、着色層を設けてもよい。20

#### 【0145】

遮光層 BM は、バックライト及び表示装置の外側からトランジスタ 202r、202g、202t、204a、204b に照射される光を遮光する。この結果、光照射による、トランジスタ 202r、202g、202t、204a、204b の電気特性の変動を抑制することができる。遮光層 BM としては、バックライトや表示装置の外側からの光を遮る材料を用いることができ、例えば、金属材料や顔料や染料を含む樹脂材料を用いて遮光層 BM を形成すればよい。

#### 【0146】

着色層は特定の波長帯域の光を透過する層である。例えば、赤色の波長帯域の光を透過する赤色 (R) の着色層、緑色の波長帯域の光を透過する緑色 (G) の着色層、青色の波長帯域の光を透過する青色 (B) の着色層などを用いることができる。ここでは、赤色 (R) の着色層 CFr 及び緑色 (G) の着色層 CFG を図示する。30

#### 【0147】

また、絶縁層 212b は、遮光層 BM 及び着色層 CFr、CFG を覆うオーバーコート層としての機能を有する。絶縁層 212b を設けることで、遮光層 BM 及び着色層 CFr、CFG に含有された不純物等が液晶層 228 へ拡散することを防ぐことができる。絶縁層 212b は、透光性を有する材料を用いて形成すればよく、例えば窒化シリコン、酸化シリコン等を用いた無機絶縁膜や、アクリル樹脂、ポリイミド等を用いた有機絶縁膜を用いて形成することができる。さらには、有機絶縁膜及び無機絶縁膜の積層構造としてもよい。40

#### 【0148】

電極 238 は、マトリクス状に配置される。なお、電極 238 は、画素電極としての機能を有する電極 208r、208g より面積を大きくすることができる。例えば、1つの電極 238 は、数百乃至数千個の画素に設けられた画素電極としての機能を有する電極と重畳するように設けることができる。

#### 【0149】

電極 214 は、液晶素子 201r、201g の対向電極としての機能を有する。電極 214 は、透光性を有する。電極 214 は、可視光において透光性のある導電膜と同様の材料50

を適宜用いることができる。

**【0150】**

なお、電極214は、マトリクス状に配置された複数の電極238及びトランジスタ202tと重畳するように、配置される。

**【0151】**

端子部250bは、接続電極220b、異方性導電膜222b、及びFPC224bを有する。なお、接続電極220bは、トランジスタ202t、204bのソース電極及びドレイン電極としての機能を有する導電膜と同じ工程で形成される。また、接続電極220bは、FPC224bが有する端子と異方性導電膜222bを介して、電気的に接続される。

10

**【0152】**

また、基板200a及び基板200bの間には、スペーサ216が設けられる。スペーサ216は、絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層228の厚さ(セルギャップ)を制御するために設けられる。なお、スペーサ216として、球状のスペーサを用いていてもよい。

**【0153】**

なお、液晶パネルにおいて、絶縁層212aおよび電極208r、208g上に配向膜としての機能を有する絶縁層226aを有する。また、タッチセンサにおいて、絶縁層212b及び電極214上に配向膜としての機能を有する絶縁層226bを有する。なお、絶縁層226a、226bは、液晶層228を構成する液晶材料次第では、設けなくてもよい。

20

**【0154】**

また、図示しないが、表示装置は、基板200bと基板200aがシール材によって固定されている。また、表示装置は、基板200b、基板200a、及びシール材で囲まれた領域に液晶層228を有する。

**【0155】**

なお、ここでは、液晶パネル及びタッチセンサそれぞれにおいて、基板200b、200a上に駆動回路部を形成した構成を示したが、駆動回路の一部を基板200b、200a上に形成し、駆動回路の他部として、別途用意された駆動回路基板(例えば、単結晶半導体膜、多結晶半導体膜で形成された駆動回路)を基板200b、200a上に実装してもよい。

30

**【0156】**

また、別途形成した駆動回路基板の接続方法は、特に限定されるものではなく、COG(Chip On Glass)方法、ワイヤボンディング方法などを用いることができる。なお、本明細書中における表示装置とは、画像表示デバイス、もしくは光源(照明装置なども含む)を指す。また、コネクター、例えばFPC、TCP(Tape Carrier Package)が取り付けられたモジュール、TCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG方式により駆動回路基板、またはIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

**【0157】**

40

また、本実施の形態で用いるトランジスタは、高純度化し、酸素欠損の形成を抑制した酸化物半導体層を有する。このようなトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。例えば、このような高速駆動が可能なトランジスタを表示装置に用いることで、画素部のスイッチングトランジスタと、駆動回路部に使用するドライバトランジスタを同一基板上に形成することができる。すなわち、別途駆動回路として、シリコンウェハ等により形成された半導体装置を用いる必要がないため、半導体装置の部品点数を削減することができる。また、画素部においても、高速駆動が可能なトランジスタを用いることで、高画質な画像を提供することができる。

**【0158】**

なお、図10において、画素部250pに含まれるトランジスタ202r、202gと、

50

駆動回路部 250d に含まれるトランジスタ 204a は、同一のサイズの構成としているが、これに限定されない。画素部 250p 及び駆動回路部 250d に用いるトランジスタは、サイズ (L / W)、または用いるトランジスタ数などを適宜変えることができる。

#### 【0159】

また、図 10 に図示しないが、表示装置に、偏光部材、位相差部材、反射防止部材などの光学部材（光学基板）などは適宜設けてよい。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライト、フロントライトなどを用いてもよい。

#### 【0160】

次に、基板 200a、200b に設けられるトランジスタ及び容量素子の詳細な構造について説明する。ここでは、トランジスタとして、代表してトランジスタ 202r を用いて説明する。また、トランジスタに含まれる半導体層として酸化物半導体層を用いて説明する。

10

#### 【0161】

<トランジスタ 202r 及び容量素子 206r の構造>

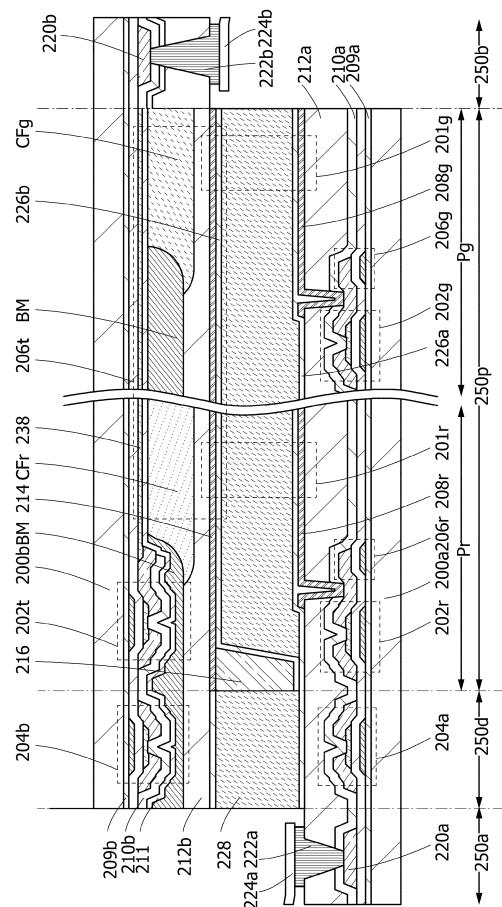

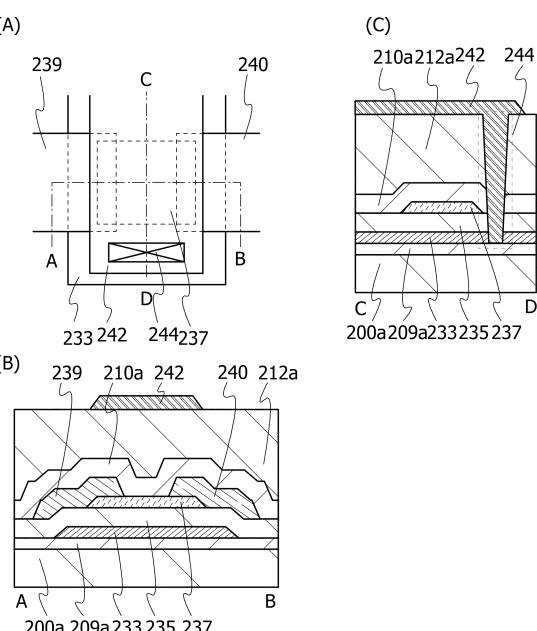

図 11 (A) 乃至 図 11 (C) に、トランジスタ 202r 及び容量素子 206r の上面模式図及び断面模式図を示す。図 11 (A) はトランジスタ 202r 及び容量素子 206r の上面模式図であり、図 11 (B) は、図 11 (A) の一点鎖線 A - B 間の断面模式図、図 11 (C) は、図 11 (A) の一点鎖線 C - D 間の断面模式図である。なお、図 11 (A) では、明瞭化のため、基板 200a、絶縁層 209a、絶縁層 235、絶縁層 210aなどを省略している。

20

#### 【0162】

図 11 (A) 乃至 図 11 (C) に示すトランジスタ 202r は、絶縁層 209a 上のゲート電極としての機能を有する導電層 233 と、導電層 233 上であってゲート絶縁膜としての機能を有する絶縁層 235 と、絶縁層 235 を介して、導電層 233 と重なる酸化物半導体層 237 と、酸化物半導体層 237 に接する一対の導電層 239、240 とを有する。絶縁層 209a は、基板 200a 上に形成される。なお、絶縁層 209a は基板 200a 上に設けなくともよい。また、絶縁層 235、酸化物半導体層 237、及び一対の導電層 239、240 上には、保護膜としての機能を有する絶縁層 210a が形成されてよい。

30

#### 【0163】

基板 200a の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。

#### 【0164】

基板 200a として、例えば、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、SOI (Silicon on Insulator) 基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンゲステン基板、タンゲステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、繊維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニオホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板、貼り合わせフィルム、基材フィルムなどの一例としては、以下のものがあげられる。例えば、ポリエチレンテレフタート (PET)、ポリエチレンナフタート (PEN)、ポリエーテルサルフォン (PES) に代表されるプラスチックがある。または、一例としては、アクリル等の合成樹脂などがある。または、一例としては、ポリプロピレン、ポリエチレン、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。または、一例としては、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又は SOI 基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さい

40

50

トランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

#### 【0165】

また、基板200aとして、可撓性基板を用い、可撓性基板上に直接、トランジスタ202rを形成してもよい。または、基板200aとトランジスタ202rの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板200aより分離し、他の基板に転載するのに用いることができる。その際、トランジスタ202rは耐熱性の劣る基板や可撓性の基板にも転載できる。なお、上述の剥離層には、例えば、タングステン膜と酸化シリコン膜との無機膜の積層構造の構成や、基板上にポリイミド等の有機樹脂膜が形成された構成等を用いることができる。

10

#### 【0166】

トランジスタが転載される基板の一例としては、上述したトランジスタを形成することができる基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

#### 【0167】

なお、下地膜としての機能を有する絶縁層209aは、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウム等を用いて形成される。なお、絶縁層209aとして、窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム等を用いることで、基板200aから不純物、代表的にはアルカリ金属、水、水素等の酸化物半導体層237への拡散を抑制することができる。

20

#### 【0168】

ゲート電極としての機能を有する導電層233は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、ニッケル、鉄、コバルト、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成される。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いて形成されてもよい。また、導電層233は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、マンガンを含む銅膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜を積層する二層構造、マンガンを含む銅膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造、マンガンを含む銅膜上に銅膜を積層し、さらにその上にマンガンを含む銅膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数組み合わせた合金膜、もしくは窒化膜を用いててもよい。

30

#### 【0169】

また、導電層233は、電極208r、208gと同様に、可視光において透光性のある導電膜を用いて形成されてもよい。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

#### 【0170】

また、絶縁層235として、酸素、水素、水等のプロッキング効果を有する膜を設けることで、酸化物半導体層237からの酸素の外部への拡散と、外部から酸化物半導体層237への水素、水等の侵入を防ぐことができる。酸素、水素、水等のプロッキング効果を有する膜は、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム

40

50

、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いて形成される。

#### 【0171】

また、絶縁層235は、ハフニウムシリケート( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート( $HfSi_xO_yN_z$ )、窒素が添加されたハフニウムアルミネート( $HfAl_xO_yN_z$ )、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用い形成されることで、トランジスタのゲートリークを低減できる。

#### 【0172】

絶縁層235の厚さは、5nm以上400nm以下、より好ましくは10nm以上300nm以下、より好ましくは50nm以上250nm以下とするよい。

10

#### 【0173】

酸化物半導体層237は、少なくともIn若しくはZnを含む金属酸化物で形成され、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)等で形成される。

#### 【0174】

なお、酸化物半導体層237がIn-M-Zn酸化物で形成されるとき、InおよびMの和を100atomic%としたときInとMの原子数比率は、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%未満とする。

#### 【0175】

酸化物半導体層237は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ202rのオフ電流を低減することができる。

20

#### 【0176】

酸化物半導体層237の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

#### 【0177】

酸化物半導体層237がIn-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)を用いて形成される場合、In-M-Zn酸化物を形成するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M-Zn-Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=3:1:2、In:M:Zn=4:1:4.1が好ましい。なお、形成される酸化物半導体層237の金属元素の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。

30

#### 【0178】

また、スパッタリングターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。なお多結晶ターゲットを用いることで、後述するCAC-O<sub>S</sub>膜および微結晶酸化物半導体膜を形成することが可能である。

#### 【0179】

酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子(または酸素が脱離した部分)に酸素欠損を形成する。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。

40

#### 【0180】

このため、酸化物半導体層237は酸素欠損と共に、水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体層237において、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得

50

られる水素濃度を、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。この結果、トランジスタ202rは、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）を有する。

#### 【0181】

また、酸化物半導体層237において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体層237において酸素欠損が増加し、n型化してしまう。このため、酸化物半導体層237におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。この結果、トランジスタ202rは、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）を有する。

10

#### 【0182】

また、酸化物半導体層237において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms/cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体層237のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。この結果、トランジスタ202rは、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）を有する。

20

#### 【0183】

また、酸化物半導体層237に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、トランジスタはノーマリーオン特性となりやすい。従って、酸化物半導体層237において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下にすることが好ましい。

#### 【0184】

酸化物半導体層237の不純物を低減することで、酸化物半導体層237のキャリア密度を低減することができる。このため、酸化物半導体層237は、キャリア密度が $1 \times 10^{17}$ 個/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ 個/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{11}$ 個/cm<sup>3</sup>以下であることが好ましい。

30

#### 【0185】

なお、酸化物半導体層237は金属元素の原子数比の異なる酸化物半導体層が複数積層されていてもよい。例えば、図14(A)に示すように、絶縁層235上に酸化物半導体層237、248が順に積層されてもよい。または、図14(B)に示すように、絶縁層235上に酸化物半導体層249、237、248が順に積層されてもよい。酸化物半導体層248、249は、酸化物半導体層237と金属元素の原子数比が異なる。

#### 【0186】

40

酸化物半導体層237として、不純物濃度が低く、欠陥準位密度の低い酸化物半導体を用いることで、さらに優れた電気特性を有するトランジスタを作製することができる。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体を用いて形成された酸化物半導体層237にチャネル領域が形成されるトランジスタは、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）になりやすい。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体を用いて酸化物半導体層237が形成

50

されたトランジスタは、オフ電流が著しく小さく、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$ A以下という特性を得ることができる。従って、当該酸化物半導体層237にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。

#### 【0187】

なお、酸化物半導体層237の代わりに、シリコンまたはシリコングルマニウムで形成される半導体層を形成してもよい。シリコンまたはシリコングルマニウムで形成される半導体層は、適宜非晶質構造、多結晶構造、単結晶構造とすることができます。

#### 【0188】

一对の導電層239、240は、ソース電極及びドレイン電極としての機能を有する。一对の導電層239、240は、ゲート電極としての機能を有する導電層233の材料を適宜用いて形成される。

#### 【0189】

なお、本実施の形態では、一对の導電層239、240を酸化物半導体層237及び絶縁層210aの間に設けたが、絶縁層235及び酸化物半導体層237の間に設けてもよい。

#### 【0190】

絶縁層210aは、トランジスタのチャネル領域を保護する機能を有する。絶縁層210aは、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等の酸化物絶縁膜、窒化シリコン、窒化アルミニウム等の窒化物絶縁膜を用いて形成される。絶縁層210aは、単層構造または積層構造とすることができます。

#### 【0191】

なお、絶縁層210aとして、酸素、水素、水等のブロッキング効果を有する絶縁膜を設けることで、酸化物半導体層237からの酸素の外部への拡散と、外部から酸化物半導体層237への水素、水等の侵入を防ぐことができる。酸素、水素、水等のブロッキング効果を有する絶縁膜は、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いて形成される。

#### 【0192】

また、絶縁層210aは、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成されることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、TDS (Thermal Desorption Spectroscopy) 分析において、膜の表面温度が100以上700以下、または100以上500以下の範囲における酸素原子の脱離量が $1.0 \times 10^{-8}$ atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{-9}$ atoms/cm<sup>3</sup>以上である酸化物絶縁膜である。加熱処理により絶縁層210aに含まれる酸素を酸化物半導体層237に移動させることができ、酸化物半導体層237の酸素欠損を低減することができる。

#### 【0193】

次に、容量素子206rの構造について説明する。容量素子206rは、絶縁層209a上に設けられる容量配線としての機能を有する導電層234と、絶縁層235と、絶縁層235を介して導電層234と重なる導電層240とを有する。

#### 【0194】

導電層234は、トランジスタ202rの導電層233と同時に形成される。絶縁層235は、トランジスタ202rのゲート絶縁膜としての機能を有すると共に、容量素子206rの誘電体層としての機能を有する。導電層240は、トランジスタ202rのソース

10

20

30

40

50

電極またはドレイン電極の機能と共に、容量素子 206r の容量電極としての機能を有する。

#### 【0195】

即ち、容量素子 206r は、トランジスタ 202r の工程と同時に形成される。なお、容量素子 206r は、図 11 に示す構造に限定されない。例えば、絶縁層 235 と導電層 240との間に酸化物半導体層を有してもよい。または、導電層 234 及び導電層 240 の一以上と、図 10 に示す絶縁層 210a、212a と、電極 208r とで、容量素子を形成してもよい。

#### 【0196】

また、容量素子 206r に含まれる導電層は、可視光において透光性のある導電膜を用いて形成してもよい。該構成とすることで画素の開口率の向上を図ることができる。開口率の向上により、バックライトの光を弱めても同じ輝度による表示が得られるため、低消費電力化を図ることができる。10

#### 【0197】

<トランジスタ 202r の変形例>

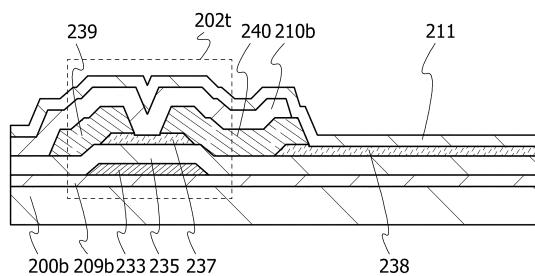

トランジスタ 202r の変形例を図 12 を用いて説明する。図 12 に示すトランジスタは、デュアルゲート構造であることを特徴とする。

#### 【0198】

図 12(A) 乃至図 12(C) に、半導体装置が有するトランジスタ 202r の上面模式図及び断面模式図を示す。図 12(A) はトランジスタの上面模式図であり、図 12(B) は、図 12(A) の一点鎖線 A - B 間の断面模式図であり、図 12(C) は、図 12(A) の一点鎖線 C - D 間の断面模式図である。なお、図 12(A) では、明瞭化のため、基板 200a、絶縁層 209a、絶縁層 235、絶縁層 210a、絶縁層 212a などを省略している。20

#### 【0199】

図 12(A) 乃至図 12(C) に示すトランジスタは、絶縁層 209a 上のゲート電極としての機能を有する導電層 233 と、導電層 233 上であってゲート絶縁膜としての機能を有する絶縁層 235 と、絶縁層 235 を介して、導電層 233 と重なる酸化物半導体層 237 と、酸化物半導体層 237 に接する一対の導電層 239、240 と、酸化物半導体層 237、一対の導電層 239、240 上の絶縁層 210a と、絶縁層 210a 上の絶縁層 212a と、絶縁層 212a 上であってゲート電極としての機能を有する導電層 242 とを有する。導電層 242 は、絶縁層 235、210a、212a の開口部 244 において、導電層 233 と接続される。30

#### 【0200】

なお、図 12(C) に示すように、チャネル幅方向において酸化物半導体層 237 の側面と導電層 242 とが対向することで、酸化物半導体層 237 において、絶縁層 235 及び絶縁層 210a と酸化物半導体層 237 界面のみでなく、酸化物半導体層 237 の内部においてもキャリアが流れるため、トランジスタにおけるキャリアの移動量が増加する。この結果、トランジスタのオン電流が大きくなると共に、電界効果移動度が高くなる。また、導電層 242 の電界が酸化物半導体層 237 の側面、または側面及びその近傍を含む端部に影響するため、酸化物半導体層 237 の側面または端部における寄生チャネルの発生を抑制することができる。40

#### 【0201】

図 12 に示すトランジスタは、図 11 に示すトランジスタに比べて電界効果移動度が高く、オン電流が大きい。このため、駆動回路部 250d に設けられるトランジスタとして、図 12 に示す構造のトランジスタを用いることで、高速動作が可能な駆動回路部を作製することができる。また、駆動回路部 250d の占有面積を小さくすることが可能であり、画素部 250p の面積を増大させることができる。また、オン電流の大きいトランジスタを画素部 250p に設けることで、大型の表示装置や、高精細な表示装置において配線数が増大しても、各配線における信号遅延を低減することが可能であり、表示むらを抑える50

ことが可能である。なお、駆動回路部 250d が有するトランジスタは、すべて同じ構造であってもよく、二種以上の構造であってもよい。また、画素部 250p が有する複数のトランジスタは、すべて同じ構造であってもよく、二種以上の構造であってもよい。

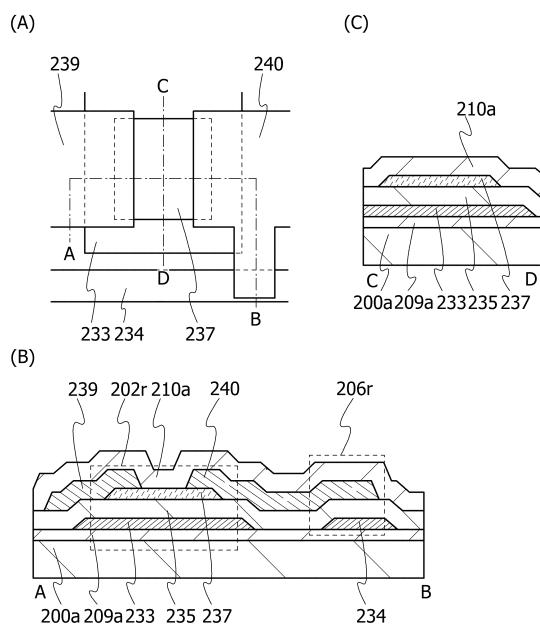

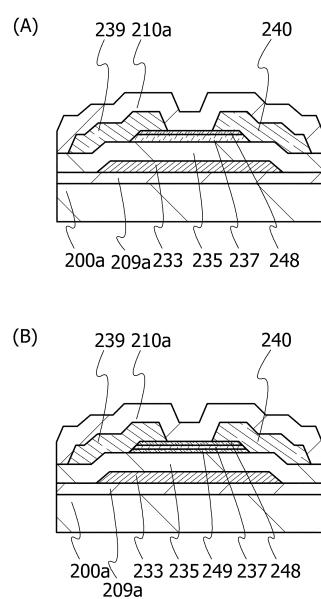

#### 【0202】

<トランジスタ 202t 及び電極 238 の構造>

図13に、タッチセンサに含まれるトランジスタ 202t 及び電極 238 の断面模式図を示す。絶縁層 209b 上にトランジスタ 202t が形成される。絶縁層 209b は、絶縁層 209a の材料を適宜用いて形成される。また、絶縁層 209b は基板 200b 上に形成される。

#### 【0203】

図13に示すトランジスタ 202t は、トランジスタ 202r と同様の構造とすることができる。

#### 【0204】

電極 238 は、絶縁層 235 上に形成される。また、電極 238 はトランジスタ 202t の導電層 240 と接続される。

#### 【0205】

また、トランジスタ 202t 上に絶縁層 210b が形成される。なお、絶縁層 210b は、電極 238 が露出する開口部を有する。また、絶縁層 210b 及び電極 238 上に絶縁層 211 が形成される。

#### 【0206】

電極 238 は、酸化物半導体層 237 と同時に形成された酸化物半導体膜を加工して形成される。このため、電極 238 は、酸化物半導体層 237 と同様の金属元素を有する。また、酸化物半導体層 237 と同様の結晶構造、または異なる結晶構造を有する。しかしながら、酸化物半導体層 237 と同時に形成された酸化物半導体層に、不純物または酸素欠損を有せしめることで、電極 238 となる。電極 238 に含まれる不純物の代表例としては、希ガス、水素、ホウ素、窒素、フッ素、アルミニウム、およびリンの一以上がある。希ガスの代表例としては、ヘリウム、ネオン、アルゴン、クリプトンおよびキセノンがある。

#### 【0207】

このため、酸化物半導体層 237 及び電極 238 は共に、絶縁層 235 上に形成されるが、不純物濃度が異なる。具体的には、酸化物半導体層 237 と比較して、電極 238 の不純物濃度が高い。例えば、酸化物半導体層 237 において、二次イオン質量分析法により得られる水素濃度は、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下、好ましくは $1 \times 10^{-6}$  atoms / cm<sup>3</sup> 以下である。一方、電極 238 において、二次イオン質量分析法により得られる水素濃度は、 $8 \times 10^{-9}$  atoms / cm<sup>3</sup> 以上、好ましくは $1 \times 10^{-8}$  atoms / cm<sup>3</sup> 以上、好ましくは $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以上である。また、酸化物半導体層 237 と比較して、電極 238 に含まれる水素濃度は 2 倍、または 10 倍以上である。

#### 【0208】

酸化物半導体層 237 の水素濃度を上記範囲とすることで、酸化物半導体層 237 におけるキャリアである電子の生成を抑制することが可能である。この結果、トランジスタ 202t は、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）を有する。

#### 【0209】

また、電極 238 は、酸化物半導体層 237 より抵抗率が低い。電極 238 の抵抗率が、酸化物半導体層 237 の抵抗率の $1 \times 10^{-8}$  倍以上 $1 \times 10^{-1}$  倍未満であることが好ましく、代表的には $1 \times 10^{-3}$  cm 以上 $1 \times 10^{-4}$  cm 未満、または抵抗率が $1 \times 10^{-3}$  cm 以上 $1 \times 10^{-1}$  cm 未満であるとよい。

#### 【0210】

10

20

30

40

50

酸化物半導体層 237 と同時に形成された酸化物半導体層をプラズマに曝すことにより、酸化物半導体層にダメージを与え、酸素欠損を形成することができる。例えば、酸化物半導体層上に、プラズマ CVD 法またはスパッタリング法で膜を成膜すると、酸化物半導体層がプラズマに曝され、酸素欠損が生成される。または、絶縁層 210a に開口部を形成するためのエッチング処理において、酸化物半導体層がプラズマに曝されることで、酸素欠損が生成される。または、酸化物半導体層が、酸素及び水素の混合ガス、水素、希ガス、アンモニア等のプラズマに曝されることで、酸素欠損が生成される。また、酸化物半導体層に不純物を添加することで、酸素欠損を形成しつつ、不純物を酸化物半導体層に添加することができる。不純物の添加方法としては、イオンドーピング法、イオン注入法、プラズマ処理法等がある。プラズマ処理法の場合、添加する不純物を含むガス雰囲気にてプラズマを発生させて、プラズマ処理を行うことによって、加速させた不純物イオンを酸化物半導体層に衝突させ、酸化物半導体層に酸素欠損を形成することができる。

10

#### 【0211】

不純物元素の添加により酸素欠損が形成された酸化物半導体層に不純物、一例として水素が含まれると、酸素欠損サイトに水素が入り伝導帯近傍にドナー準位が形成される。この結果、酸化物半導体層は、導電性が高くなり、導電体化する。導電体化された酸化物半導体層を酸化物導電体層ということができる。即ち、酸化物半導体層 237 は、酸化物半導体で形成され、電極 238 は酸化物導電体層で形成されるといえる。また、電極 238 は、導電性の高い酸化物半導体層で形成されるともいえる。また、電極 238 は、導電性の高い金属酸化物層で形成されるともいえる。

20

#### 【0212】

なお、一般に、酸化物半導体層は、エネルギーギャップが大きいため、可視光に対して透光性を有する。一方、酸化物導電体層は、伝導帯近傍にドナー準位を有する酸化物半導体層である。したがって、該ドナー準位による吸収の影響は小さく、可視光に対して酸化物半導体層と同程度の透光性を有する。

#### 【0213】

絶縁層 210b、211 は、絶縁層 210a と同様の材料を用いて形成することができる。

。

#### 【0214】

なお、絶縁層 211 は、水素を含むことが好ましい。電極 238 は、絶縁層 211 に接しているため、絶縁層 211 が水素を含むことで、絶縁層 211 の水素を、酸化物半導体層 237 と同時に形成された酸化物半導体層に拡散させることができる。この結果、酸化物半導体層 237 と同時に形成された酸化物半導体層に不純物を添加することができる。

30

#### 【0215】

さらに、絶縁層 210b が、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁層で形成され、絶縁層 211 が水素を含む絶縁層で形成されることが好ましい。絶縁層 210b に含まれる酸素がトランジスタ 202t の酸化物半導体層 237 に移動することで、酸化物半導体層 237 の酸素欠損量を低減でき、トランジスタ 202t の電気特性の変動を小さくできると共に、絶縁層 211 に含まれる水素が電極 238 に移動し、電極 238 の導電性を高めることができる。

40

#### 【0216】

なお、電極 238 は、可視光において透光性のある導電層を用いて形成してもよい。

#### 【0217】

図 13において、トランジスタの酸化物半導体層と同時に、容量素子の一方となる電極が形成される。このため、容量素子を形成するために、新たに導電層を形成する工程が不要であり、作製工程数を削減できる。

#### 【0218】

また、本実施の形態に示す表示装置は、電極 214 の電位の変化に合わせて、導電層 234 の電位を変化させることで、液晶素子に含まれる画素電極としての機能を有する電極の電位を、電極 214 の電位の変化に合わせて変化させることが可能である。この結果、液

50

晶素子に含まれる一対の電極の間の電界を一定にすることが可能であり、優れた表示品位を得ることができる。

**【0219】**

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

**【0220】**

(実施の形態4)

<酸化物半導体膜の構造>

**【0221】**

本実施の形態では、トランジスタに用いることが可能な酸化物半導体膜の構造について説明する。 10

**【0222】**

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、C AAC - OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

**【0223】**

まずは、C AAC - OS 膜について説明する。

**【0224】**

C AAC - OS 膜は、c 軸配向した複数の結晶部を有する酸化物半導体膜の一つである。 20

**【0225】**

透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって、C AAC - OS 膜の明視野像および回折パターンの複合解析像 (高分解能 TEM 像ともいう。) を観察することで複数の結晶部を確認することができる。一方、高分解能 TEM 像によっても明確な結晶部同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することが難しい。そのため、C AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0226】**

試料面と概略平行な方向から、C AAC - OS 膜の断面の高分解能 TEM 像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS 膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、C AAC - OS 膜の被形成面または上面と平行に配列する。 30

**【0227】**

一方、試料面と概略垂直な方向から、C AAC - OS 膜の平面の高分解能 TEM 像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0228】**

C AAC - OS 膜に対し、X線回折 (XRD : X-Ray Diffraction) 装置を用いて構造解析を行うと、例えばInGaN<sub>0.4</sub>O<sub>4</sub>の結晶を有するC AAC - OS 膜のout-of-plane法による解析では、回折角 ( $2\theta$ ) が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub>O<sub>4</sub>の結晶の (009) 面に帰属されることから、C AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。 40

**【0229】**

なお、InGaN<sub>0.4</sub>O<sub>4</sub>の結晶を有するC AAC - OS 膜のout-of-plane法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、C AAC - OS 膜中的一部に、c 軸配向性を有さない結晶が含まれることを示している。C AAC - OS 膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。

**【0230】**

10

20

30

40

50

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【 0 2 3 1 】

また、C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

10

#### 【 0 2 3 2 】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないとため、キャリア密度を低くすることができる。したがって、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

20

#### 【 0 2 3 3 】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【 0 2 3 4 】

次に、微結晶酸化物半導体膜について説明する。

#### 【 0 2 3 5 】

30

微結晶酸化物半導体膜は、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することが困難な領域と、を有する。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶（n c : n a n o c r y s t a l ）を有する酸化物半導体膜を、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜と呼ぶ。また、n c - O S 膜は、例えば、高分解能TEM像では、結晶粒界を明確に確認することが困難な場合がある。

#### 【 0 2 3 6 】

n c - O S 膜は、微小な領域（例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域）において原子配列に周期性を有する。また、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、n c - O S 膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 膜に対し、結晶部よりも大きいプローブ径（例えば50 nm以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S 膜に対しナノビーム電子回折を行

40

50

行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O S 膜に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

#### 【0237】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

#### 【0238】

次に、非晶質酸化物半導体膜について説明する。

10

#### 【0239】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体膜である。石英のような無定形状態を有する酸化物半導体膜が一例である。

#### 【0240】

非晶質酸化物半導体膜は、高分解能TEM像において結晶部を確認することが難しい。

#### 【0241】

非晶質酸化物半導体膜に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体膜に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体膜に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

20

#### 【0242】

なお、酸化物半導体膜は、n c - O S 膜と非晶質酸化物半導体膜との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体膜を、特に非晶質ライク酸化物半導体（amorphous-like OS : amorphous-like Oxide Semiconductor）膜と呼ぶ。

#### 【0243】

amorphous-like OS 膜は、高分解能TEM像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することが困難な領域と、を有する。amorphous-like OS 膜は、TEMによる観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質なn c - O S 膜であれば、TEMによる観察程度の微量な電子照射による結晶化はほとんど見られない。

30

#### 【0244】

なお、amorphous-like OS 膜およびn c - O S 膜の結晶部の大きさの計測は、高分解能TEM像を用いて行うことができる。例えば、InGaZnO<sub>4</sub>の結晶は層状構造を有し、In-O層の間に、Ga-Zn-O層を2層有する。InGaZnO<sub>4</sub>の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、（009）面の格子面間隔（d値ともいう。）と同程度であり、結晶構造解析からその値は0.29nmと求められている。そのため、高分解能TEM像における格子縞に着目し、格子縞の間隔が0.28nm以上0.30nm以下の箇所においては、それぞれの格子縞がInGaZnO<sub>4</sub>の結晶のa-b面に対応する。

40

#### 【0245】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、amorphous-like OS 膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

#### 【0246】

本実施の形態に示す構成は、他の実施の形態に示す構成と適宜組み合わせて用いることができる。

50

**【0247】**

(実施の形態5)

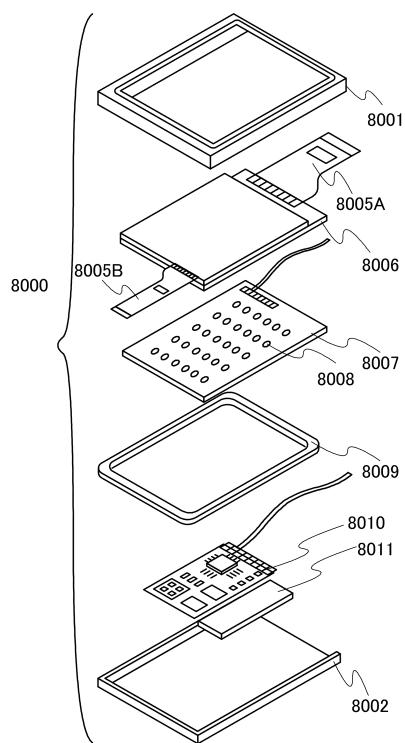

本実施の形態では、本発明の一態様の表示装置を適用した表示モジュールについて、説明する。また、本発明の一態様の表示モジュールが適用された電子機器の構成例について説明する。

**【0248】**

図15に示す表示モジュール8000は、上部カバー8001と下部カバー8002との間に、FPC8005A, 8005Bに接続された表示装置8006、バックライトユニット8007、フレーム8009、プリント基板8010、バッテリー8011を有する。なお、バックライトユニット8007、バッテリー8011、などは、設けられない場合もある。

10

**【0249】**

上部カバー8001及び下部カバー8002は、表示装置8006のサイズに合わせて、形状や寸法を適宜変更することができる。

**【0250】**

バックライトユニット8007は、光源8008を有する。光源8008をバックライトユニット8007の端部に設け、光拡散板を用いる構成としてもよい。なお、光源8008として、EL(Electro-luminescence)素子を用いることで可携性を有する光源8008とすることができる。

20

**【0251】**

また、バックライトユニット8007と表示装置8006の間に、波長変換部材を設けてもよい。波長変換部材は、蛍光顔料、蛍光染料、量子ドット等の波長変換物質を含む。波長変換物質は、バックライトユニット8007の光を吸収し、該光の一部または全部を別の波長の光に変換することができる。また、波長変換物質である量子ドットは、直径が1nm以上100nm以下の粒子である。量子ドットを有する波長変換部材を用いることでも、表示装置の色再現性を高めることができる。さらに、波長変換部材は、導光板として機能させてもよい。

**【0252】**

フレーム8009は、表示装置8006の保護機能の他、プリント基板8010の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム8009は、放熱板としての機能を有していてもよい。

30

**【0253】**

プリント基板8010は、電源回路、ビデオ信号及びクロック信号を出力するための信号処理回路を有する。プリント基板8010は、表示装置8006、バックライトユニット8007、バッテリー8011に接続される。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリー8011による電源であってもよい。バッテリー8011は、商用電源を用いる場合には、省略可能である。

**【0254】**

また、表示モジュール8000には、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。また、表示モジュール8000が有する各構成を薄型化することで、表示モジュール8000をフレキシブルな表示モジュールとすることができる。バックライトユニット8007については、導光板を用いて薄型化すればよい。

40

**【0255】**

図16は、本発明の一態様の表示モジュールを含む電子機器の外観図である。

**【0256】**

電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置、スマートフォンともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

50

## 【0257】

図16(A)は、表示部を有する携帯情報端末1400を示している。携帯情報端末1400は、筐体1401に表示部1402及び操作ボタン1403が組み込まれている。表示部1402には、本発明の一態様の表示モジュールが適用できる。そのため、薄型化と良好な表示品位の両立が図られた、携帯情報端末が実現される。

## 【0258】

図16(B)は、携帯電話機1410を示している。携帯電話機1410は、筐体1411に表示部1412、操作ボタン1413、スピーカー1414、及びマイク1415が組み込まれている。表示部1412には、本発明の一態様の表示モジュールが適用できる。そのため、薄型化と良好な表示品位の両立が図られた、携帯電話機が実現される。

10

## 【0259】

図16(C)は、音楽再生装置1420を示している。音楽再生装置1420は、筐体1421に表示部1422、操作ボタン1423、アンテナ1424が組み込まれている。またアンテナ1424からは、無線信号により情報を送受信することができる。表示部1422には、本発明の一態様の表示モジュールが適用できる。そのため、薄型化と良好な表示品位の両立が図られた、音楽再生装置が実現される。

## 【0260】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る表示装置が設けられている。このため、薄型化と良好な表示品位の両立が図られた、電子機器が実現される。

20

## 【実施例1】

## 【0261】

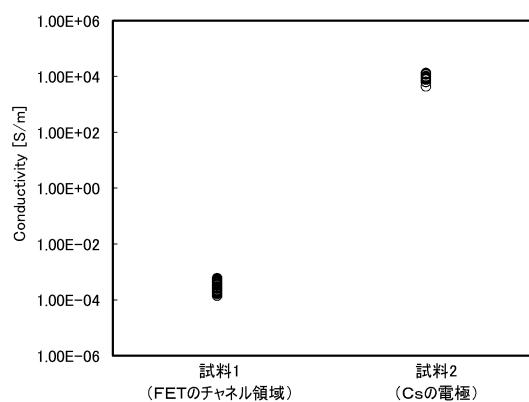

本実施例では、酸化物半導体膜の導電率について、図19乃至図21を用いて説明する。

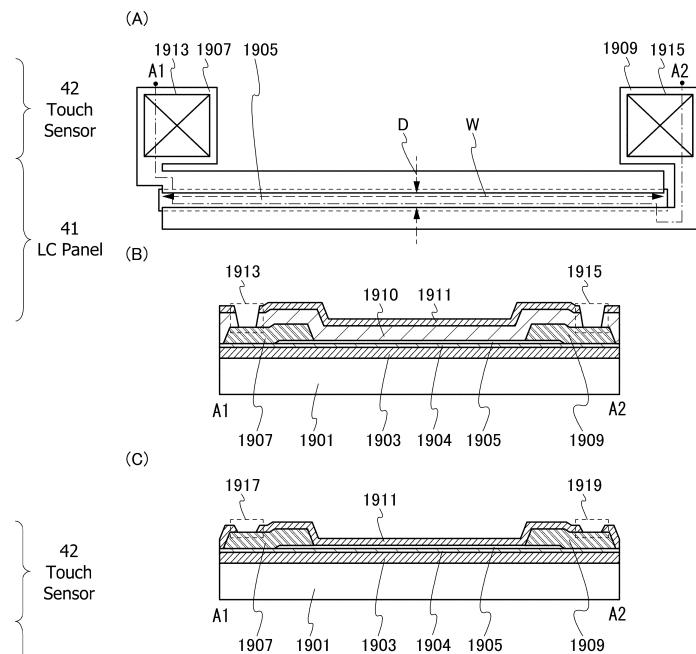

## 【0262】

はじめに、試料の構造について図19を用いて説明する。

## 【0263】

図19(A)は、試料1及び試料2の上面図であり、一点破線A1-A2の断面図を図19(B)、(C)に示す。なお、試料1及び試料2は、上面図が同一であり、断面の積層構造が異なるため、断面図が異なる。試料1の断面図を図19(B)に、試料2の断面図を図19(C)に、それぞれ示す。なお、試料1の酸化物半導体膜1905は、トランジスタ(FET)のチャネル領域に相当する。また、試料2の酸化物半導体膜1905は、容量素子(CS)の電極に相当する。

30

## 【0264】

試料1は、ガラス基板1901上に絶縁膜1903が形成され、絶縁膜1903上に絶縁膜1904が形成され、絶縁膜1904上に酸化物半導体膜1905が形成される。また、酸化物半導体膜1905の両端を、電極として機能する導電膜1907、1909が覆い、酸化物半導体膜1905及び導電膜1907、1909を絶縁膜1910、1911が覆う。なお、絶縁膜1910、1911には、開口部1913、1915が設けられており、それぞれ当該開口部において、導電膜1907、1909が露出している。

40

## 【0265】

試料2は、ガラス基板1901上に絶縁膜1903が形成され、絶縁膜1903上に絶縁膜1904が形成され、絶縁膜1904上に酸化物半導体膜1905が形成される。また、酸化物半導体膜1905の両端を電極として機能する導電膜1907、1909が覆い、酸化物半導体膜1905及び導電膜1907、1909を絶縁膜1911が覆う。なお、絶縁膜1911には、開口部1917、1919が設けられており、それぞれ当該開口部において、導電膜1907、1909が露出している。

## 【0266】

このように、試料1及び試料2は、酸化物半導体膜1905上に接する絶縁膜の構造が異なる。試料1は、酸化物半導体膜1905と絶縁膜1910が接しており、試料2は、酸化物半導体膜1905と絶縁膜1911が接している。

50

**【0267】**

次に、各試料の作製方法について説明する。

**【0268】**

はじめに、試料1の作製方法について説明する。

**【0269】**

ガラス基板1901上に、絶縁膜1903として、プラズマCVD法により厚さ400nmの窒化シリコン膜を成膜した。

**【0270】**

次に、絶縁膜1903上に、絶縁膜1904として、プラズマCVD法により厚さ50nmの酸化窒化シリコン膜を成膜した。

10

**【0271】**

次に、絶縁膜1904上に、酸化物半導体膜1905として、金属酸化物ターゲット(Indium:Gallium:Zinc = 1:1:1)を用い、スパッタリング法により厚さ35nmのIn-Ga-Zn酸化物膜(以下、IGZO膜ともいう。)を成膜した後、450°Cの窒素雰囲気で1時間の加熱処理を行い、450°Cの窒素及び酸素の混合雰囲気で1時間の加熱処理を行った。その後、フォトリソグラフィ工程により形成したマスクを用いてエッチング処理を行い、酸化物半導体膜1905を形成した。

**【0272】**

次に、絶縁膜1903及び酸化物半導体膜1905上に、スパッタリング法により厚さ50nmのタンゲステン膜、厚さ400nmのアルミニウム膜、及び厚さ100nmのチタン膜を順に積層した後、フォトリソグラフィ工程により形成したマスクを用いてエッチング処理を行い、導電膜1907及び導電膜1909を形成した。

20

**【0273】**

次に、絶縁膜1904、酸化物半導体膜1905、導電膜1907、及び導電膜1909上に、絶縁膜1910として、プラズマCVD法により厚さ450nmの酸化窒化シリコン膜を成膜した後、350°Cの窒素及び酸素の混合雰囲気で1時間の加熱処理を行った。

**【0274】**

次に、絶縁膜1910上に、絶縁膜1911として、プラズマCVD法により厚さ50nmの窒化シリコン膜を成膜した。

**【0275】**

30

次に、絶縁膜1911上に、フォトリソグラフィ工程により形成したマスクを設けた後、エッチング処理を行い、絶縁膜1910、及び絶縁膜1911に開口部1913、1915を形成した。

**【0276】**

以上の工程により試料1を作製した。

**【0277】**

次に、試料2の作製方法について説明する。

**【0278】**

試料1の絶縁膜1903、酸化物半導体膜1905、導電膜1907、及び導電膜1909上に、絶縁膜1910として、プラズマCVD法により厚さ450nmの酸化窒化シリコン膜を成膜した後、350°Cの窒素及び酸素の混合雰囲気で1時間の加熱処理を行った。その後、絶縁膜1910の除去を行った。

40

**【0279】**

次に、絶縁膜1904、酸化物半導体膜1905、導電膜1907、及び導電膜1909上に、絶縁膜1911として、プラズマCVD法により厚さ50nmの窒化シリコン膜を成膜した。

**【0280】**

次に、絶縁膜1911上に、フォトリソグラフィ工程により形成したマスクを設けた後、エッチング処理を行い、絶縁膜1911に開口部1917、1919を形成した。

**【0281】**

50

以上の工程により試料2を作製した。

【0282】

次に、試料1及び試料2に設けられた酸化物半導体膜1905の導電率を測定した。試料1においては、開口部1913の導電膜1907及び開口部1915の導電膜1909にプローブを接触させ、酸化物半導体膜1905のシート抵抗値を測定した。また、試料2においては、開口部1917の導電膜1907及び開口部1919の導電膜1909にプローブを接触させ、酸化物半導体膜1905のシート抵抗値を測定した。なお、試料1及び試料2の酸化物半導体膜1905において、導電膜1907及び導電膜1909が対向する幅Wを1mm、間隔Dを10μmとした。また、試料1及び試料2において、導電膜1907を接地電位とし、導電膜1909に1Vを印加した。次に、試料1及び試料2に含まれる酸化物半導体膜1905のシート抵抗値から導電率を計算で求めた。

10

【0283】

試料1及び試料2の導電率を図20に示す。

【0284】

試料1の平均導電率は、 $3.04 \times 10^{-4} \text{ S/m}$ であった。また、試料2の平均導電率は、 $9.91 \times 10^{-3} \text{ S/m}$ であった。

【0285】

このように、酸化物半導体膜1905に接する絶縁膜の違いにより、酸化物半導体膜1905の導電率は、異なる値を示す。

【0286】

試料1は、酸化物半導体膜1905上に接して絶縁膜1910として用いる酸化窒化シリコン膜が形成されている。酸化物半導体膜1905は絶縁膜1911として用いる窒化シリコン膜と接していない。一方、試料2は、酸化物半導体膜1905上に接して絶縁膜1911として用いる窒化シリコン膜が形成されている。このように、酸化物半導体膜1905は、絶縁膜1911として用いる窒化シリコン膜に接して設けると、酸化物半導体膜1905に欠陥、代表的には酸素欠損が形成されると共に、該窒化シリコン膜に含まれる水素が、酸化物半導体膜1905へ移動又は拡散する。これらの結果、酸化物半導体膜1905の導電率が上昇する。

20

【0287】

例えば、トランジスタのチャネル領域に酸化物半導体膜を用いる場合、試料1に示すように酸化物半導体膜に接して酸化窒化シリコン膜を設ける構成が好ましい。また、容量素子の電極としては、試料2に示すように酸化物半導体膜に接して窒化シリコン膜を設ける構成が好ましい。このような構成を用いることによって、トランジスタのチャネル領域に用いる酸化物半導体膜と、容量素子の電極に用いる酸化物半導体膜と、を同一工程で作製しても酸化物半導体膜の導電率を変えることができる。

30

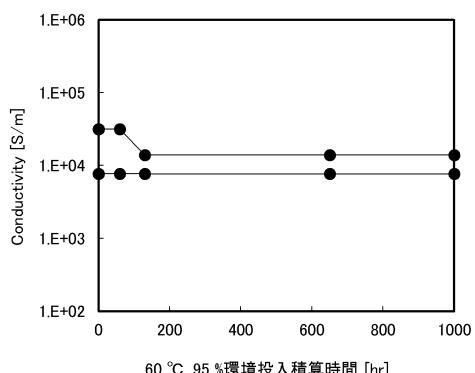

【0288】

次に、上面形状が試料2と異なり、断面形状が試料2と同じである試料3を作製した。次に、試料3において、高温高湿環境で保存した試料の導電率を求めた。

【0289】

次に、試料3に設けられた酸化物半導体膜1905のシート抵抗値を測定した。試料3においては、開口部1917及び開口部1919にプローブを接触させ、酸化物半導体膜1905のシート抵抗を測定した。なお、試料3の酸化物半導体膜1905において、上面形状において導電膜1907及び導電膜1909が対向する幅Wを1.5mm、間隔Dを10μmとした。また、試料3において、導電膜1907を接地電位とし、導電膜1909に1Vを印加した。また、温度60℃、湿度95%の雰囲気において、試料3を、60時間、130時間、650時間、及び1000時間保管した後、試料のシート抵抗値を測定した。ここでは、2つの試料3の測定を行った。次に、シート抵抗値より導電率を計算で求めた。

40

【0290】

試料3の導電率を図21に示す。

## 【0291】

図21より、試料3は、導電率が高い。また、試料3は、導電率の時間変動量が少ないことがわかる。以上のことから、窒化シリコン膜に接する酸化物半導体膜は、高温高湿環境において、導電率の変動量が少ないため、容量素子の電極として用いることができる。

## 【0292】

本実施例に示す構成は、他の実施の形態、又は実施例に示す構成と適宜組み合わせて用いることができる。

## 【符号の説明】

## 【0293】

|         |         |    |

|---------|---------|----|

| G 1     | 選択線     | 10 |

| M 1     | トランジスタ  |    |

| M 2     | トランジスタ  |    |

| M 3     | トランジスタ  |    |

| M 4     | トランジスタ  |    |

| 1 0     | 基板      |    |

| 1 1     | トランジスタ  |    |

| 1 2     | 容量素子    |    |

| 1 3     | 電極      |    |

| 1 4     | 導電層     |    |

| 1 5     | 導電層     | 20 |

| 1 6     | 絶縁層     |    |

| 1 7     | 半導体層    |    |

| 1 8     | 導電層     |    |

| 1 9     | 導電層     |    |

| 2 0     | 液晶層     |    |

| 2 1     | 導電層     |    |

| 2 2     | 導電層     |    |

| 2 3     | 電極      |    |

| 2 4     | カラーフィルタ |    |

| 3 0     | 基板      | 30 |

| 3 1     | トランジスタ  |    |

| 3 2     | 容量素子    |    |

| 3 3     | 電極      |    |

| 3 4     | 導電層     |    |

| 3 5     | 絶縁層     |    |

| 3 6     | 半導体層    |    |

| 3 7     | 電極      |    |

| 3 8     | 導電層     |    |

| 3 9     | 導電層     |    |

| 4 1     | 液晶パネル   | 40 |

| 4 2     | タッチセンサ  |    |

| 4 3     | 電極      |    |

| 4 4     | カラーフィルタ |    |

| 2 0 0 a | 基板      |    |

| 2 0 0 b | 基板      |    |

| 2 0 1 g | 液晶素子    |    |

| 2 0 1 r | 液晶素子    |    |

| 2 0 2 g | トランジスタ  |    |

| 2 0 2 r | トランジスタ  |    |

| 2 0 2 t | トランジスタ  | 50 |

|         |         |    |

|---------|---------|----|

| 2 0 4 a | トランジスタ  |    |

| 2 0 4 b | トランジスタ  |    |

| 2 0 6 g | 容量素子    |    |

| 2 0 6 r | 容量素子    |    |

| 2 0 6 t | 容量素子    |    |

| 2 0 8 g | 電極      |    |

| 2 0 8 r | 電極      |    |

| 2 0 9 a | 絶縁層     |    |

| 2 1 0 a | 絶縁層     |    |

| 2 1 0 b | 絶縁層     | 10 |

| 2 1 1   | 絶縁層     |    |

| 2 1 2 a | 絶縁層     |    |

| 2 1 2 b | 絶縁層     |    |

| 2 1 4   | 電極      |    |

| 2 1 6   | スペーサ    |    |

| 2 2 0 a | 接続電極    |    |

| 2 2 0 b | 接続電極    |    |

| 2 2 2 a | 異方性導電膜  |    |

| 2 2 2 b | 異方性導電膜  |    |

| 2 2 4 a | F P C   | 20 |

| 2 2 4 b | F P C   |    |

| 2 2 6 a | 絶縁層     |    |

| 2 2 6 b | 絶縁層     |    |

| 2 2 8   | 液晶層     |    |

| 2 3 3   | 導電層     |    |

| 2 3 4   | 導電層     |    |

| 2 3 5   | 絶縁層     |    |

| 2 3 7   | 酸化物半導体層 |    |

| 2 3 8   | 電極      |    |

| 2 3 9   | 導電層     | 30 |

| 2 4 0   | 導電層     |    |

| 2 4 2   | 導電層     |    |

| 2 4 4   | 開口部     |    |

| 2 4 8   | 酸化物半導体層 |    |

| 2 4 9   | 酸化物半導体層 |    |

| 2 5 0 a | 端子部     |    |

| 2 5 0 b | 端子部     |    |

| 2 5 0 d | 駆動回路部   |    |

| 2 5 0 p | 画素部     |    |

| 3 0 8 b | 酸化物導電体層 | 40 |

| 1 4 0 0 | 携帯情報端末  |    |

| 1 4 0 1 | 筐体      |    |

| 1 4 0 2 | 表示部     |    |

| 1 4 0 3 | 操作ボタン   |    |

| 1 4 1 0 | 携帯電話機   |    |

| 1 4 1 1 | 筐体      |    |

| 1 4 1 2 | 表示部     |    |

| 1 4 1 3 | 操作ボタン   |    |

| 1 4 1 4 | スピーカー   |    |

| 1 4 1 5 | マイク     | 50 |

|           |            |    |

|-----------|------------|----|

| 1 4 2 0   | 音楽再生装置     |    |

| 1 4 2 1   | 筐体         |    |

| 1 4 2 2   | 表示部        |    |

| 1 4 2 3   | 操作ボタン      |    |

| 1 4 2 4   | アンテナ       |    |

| 8 0 0 0   | 表示モジュール    |    |

| 8 0 0 1   | 上部カバー      |    |

| 8 0 0 2   | 下部カバー      |    |

| 8 0 0 5 A | F P C      |    |

| 8 0 0 6   | 表示装置       | 10 |

| 8 0 0 7   | バックライトユニット |    |

| 8 0 0 8   | 光源         |    |

| 8 0 0 9   | フレーム       |    |

| 8 0 1 0   | プリント基板     |    |

| 8 0 1 1   | バッテリー      |    |

【図 1】

(A)

(B)

【図 2】

【図 3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【 図 1 0 】

【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

---

フロントページの続き

(31)優先権主張番号 特願2014-106476(P2014-106476)

(32)優先日 平成26年5月22日(2014.5.22)

(33)優先権主張国・地域又は機関

日本国(JP)

審査官 鈴木 俊光

(56)参考文献 特表2009-540374 (JP, A)

特開2003-196023 (JP, A)

特開2007-048275 (JP, A)

米国特許出願公開第2011/0193816 (US, A1)

特開2012-022311 (JP, A)

特開2013-224977 (JP, A)

特開2014-063141 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                   |

|--------|-------------------|

| G 02 F | 1 / 1368          |

| G 02 F | 1 / 1343          |

| G 02 F | 1 / 1333          |

| G 06 F | 3 / 041 - 3 / 044 |