(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6312552号

(P6312552)

(45) 発行日 平成30年4月18日(2018.4.18)

(24) 登録日 平成30年3月30日(2018.3.30)

(51) Int.Cl.

F 1

|                    |                  |      |        |   |

|--------------------|------------------|------|--------|---|

| <b>H01L 33/32</b>  | <b>(2010.01)</b> | H01L | 33/32  |   |

| <b>H01L 21/308</b> | <b>(2006.01)</b> | H01L | 21/308 | G |

| <b>B23K 26/57</b>  | <b>(2014.01)</b> | B23K | 26/57  |   |

| <b>B23K 26/36</b>  | <b>(2014.01)</b> | B23K | 26/36  |   |

| <b>B23K 26/00</b>  | <b>(2014.01)</b> | B23K | 26/00  | H |

請求項の数 5 (全 22 頁)

(21) 出願番号

特願2014-161288 (P2014-161288)

(22) 出願日

平成26年8月7日(2014.8.7)

(65) 公開番号

特開2016-39242 (P2016-39242A)

(43) 公開日

平成28年3月22日(2016.3.22)

審査請求日

平成29年3月23日(2017.3.23)

(73) 特許権者 000005049

シャープ株式会社

大阪府堺市堺区匠町1番地

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 澤村 誠

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 太田 征孝

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 山本 秀一郎

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】半導体発光素子の製造方法および半導体発光素子

## (57) 【特許請求の範囲】

## 【請求項1】

成長用基板上に  $A_{1-x}G_{a_{1-x}}N$  ( $0 < x < 1$ ) 層を含む半導体発光素子部を形成する工程と、

前記半導体発光素子部上に第1電極を形成する工程と、

前記半導体発光素子部を複数に分割する溝を形成する工程と、

前記第1電極と支持基板とを接合する工程と、

前記半導体発光素子部から少なくとも前記成長用基板をレーザリフトオフにより剥離することによって前記  $A_{1-x}G_{a_{1-x}}N$  ( $0 < x < 1$ ) 層の表面を露出させる工程と、

少なくとも前記第1電極と前記支持基板との接合部および前記第1電極に窒化物絶縁保護膜を形成する工程と、

前記成長用基板を剥離することによって露出した前記  $A_{1-x}G_{a_{1-x}}N$  ( $0 < x < 1$ ) 層の前記表面を40以上フッ酸と接触させる工程と、

前記窒化物絶縁保護膜が形成されていない前記半導体発光素子部の部分をエッチングする工程と、を含む、半導体発光素子の製造方法。

## 【請求項2】

前記エッチングする工程は、少なくとも前記第1電極と前記支持基板との接合部および前記第1電極に前記窒化物絶縁保護膜が形成された状態で行われる、請求項1に記載の半導体発光素子の製造方法。

## 【請求項3】

10

20

前記接合する工程の前に、前記溝を形成する工程を行い、

前記溝を形成する工程と前記接合する工程との間に、前記溝の少なくとも一部を埋め込む拡散抑制層を形成する工程を含み、

前記接合する工程の後に、前記拡散抑制層を除去する工程を含み、

前記拡散抑制層を除去する工程の後に、前記窒化物絶縁保護膜を形成する工程を含み、

前記窒化物絶縁保護膜を形成する工程の後に、前記窒化物絶縁保護膜の一部を除去する工程を含み、

前記除去する工程の後に、前記フッ酸と接触させる工程および前記エッチングする工程をこの順に行う、請求項1または請求項2に記載の半導体発光素子の製造方法。

#### 【請求項4】

10

前記拡散抑制層を除去する工程は、前記成長用基板を貫通する貫通孔を形成することによって前記拡散抑制層を露出させる工程と、前記貫通孔から露出した前記拡散抑制層を除去する工程とを含む、請求項3に記載の半導体発光素子の製造方法。

#### 【請求項5】

前記接合する工程の後に、前記溝を形成する工程を行い、

前記溝を形成する工程は、少なくとも前記成長用基板、前記半導体発光素子部、前記第1電極および前記接合部を貫通して前記支持基板の表面まで達するように前記溝を形成する工程を含む、請求項1または請求項2に記載の半導体発光素子の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、半導体発光素子の製造方法および半導体発光素子に関する。

##### 【背景技術】

##### 【0002】

従来から、成長用基板上にGaN系の半導体成長層を結晶成長させた後に成長用基板を剥離する際には、レーザリフトオフ(LL-O)法による成長用基板の剥離方法が用いられている。

##### 【0003】

たとえば、特許文献1には、以下のLL-O法による成長用基板の剥離方法が開示されている。まず、成長用基板としてのサファイア基板上に低温GaNバッファ層、下地GaN層、n-GaN層、活性層、p-AlGaNクラッド層、p-GaN層からなる半導体成長層を形成した後に、サファイア基板の表面に向かって開口が徐々に小さくなるとともに、サファイア基板の表面に達する素子分割溝を形成する。次に、半導体成長層の表面上にp側電極を形成するとともに、サファイア基板に接しないよう素子分割溝のテーパーを覆う保護層を形成する。次に、半導体成長層の表面上のp側電極と支持体とを接合層により接合し、その後、サファイア基板側からレーザ光を照射することによって、低温GaNバッファ層および下地GaN層が金属ガリウム(Ga)および窒素ガス(N<sub>2</sub>ガス)に分解し、サファイア基板が剥離する。

##### 【0004】

30

また、たとえば、特許文献2には、以下のLL-O法による成長用基板の剥離方法が開示されている。まず、成長用基板としてのサファイア基板上に低温GaNバッファ層、下地GaN層、n-GaN層、活性層、p-AlGaNクラッド層、p-GaN層からなる半導体成長層の表面上にp電極および絶縁層を形成する。次に、p電極および絶縁層を覆うようにレジストを形成し、レジストをマスクとして反応性イオンエッチングを行うことによりレジスト間に誘導溝を形成した後に、レジストを除去する。そして、誘導溝の形成後の半導体成長層と支持体とを接合した後に、サファイア基板側からレーザ光を照射することによって、低温GaNバッファ層および下地GaN層が金属GaおよびN<sub>2</sub>ガスに分解し、サファイア基板が剥離する。

##### 【先行技術文献】

##### 【特許文献】

40

50

## 【0005】

【特許文献1】特開2012-69680号公報

【特許文献2】特開2011-100767号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、特許文献1および特許文献2に記載の方法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させることによって半導体発光素子を製造した場合には半導体発光素子の製造歩留まりが低くなるという課題があった。

## 【課題を解決するための手段】

## 【0007】

ここで開示された実施形態は、成長用基板上に  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層を含む半導体発光素子部を形成する工程と、半導体発光素子部上に第1電極を形成する工程と、半導体発光素子部を複数に分割する溝を形成する工程と、第1電極と支持基板とを接合する工程と、半導体発光素子部から少なくとも成長用基板をレーザリフトオフにより剥離することによって  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させる工程と、少なくとも第1電極と支持基板との接合部および第1電極に窒化物絶縁保護膜を形成する工程と、成長用基板を剥離することによって露出した  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を40

以上のフッ酸と接触させる工程と、窒化物絶縁保護膜が形成されていない半導体発光素子部の部分をエッチングする工程とを含む半導体発光素子の製造方法である。

## 【発明の効果】

## 【0008】

ここで開示された実施形態によれば、LLO法により成長用基板を剥離して、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させることによって半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

## 【図面の簡単な説明】

## 【0009】

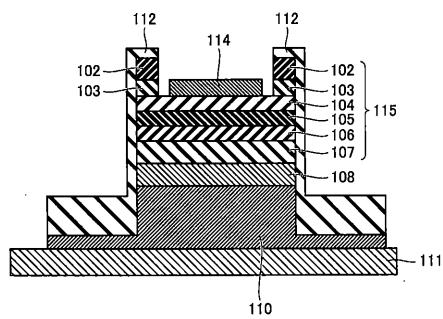

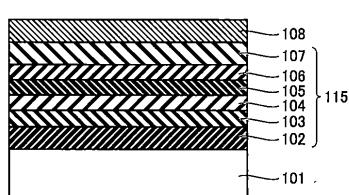

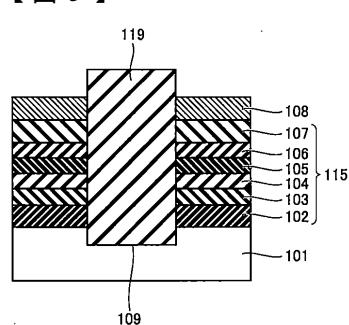

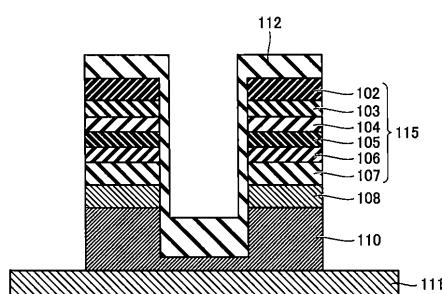

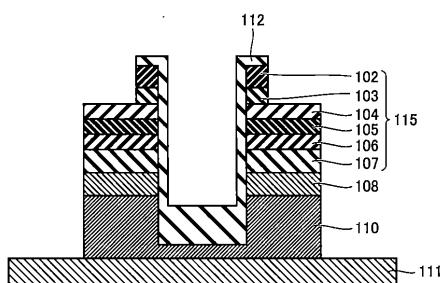

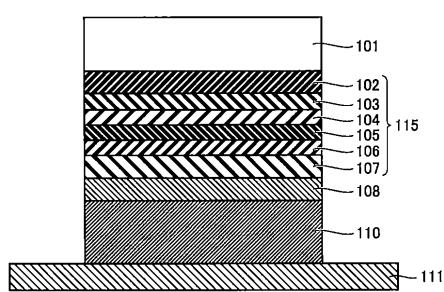

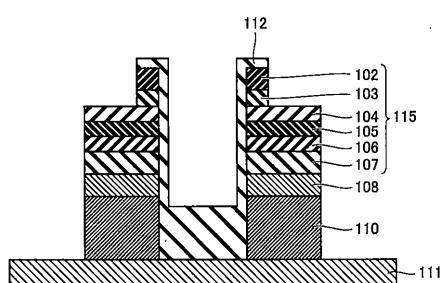

【図1】実施形態1の半導体発光素子の模式的な断面図である。

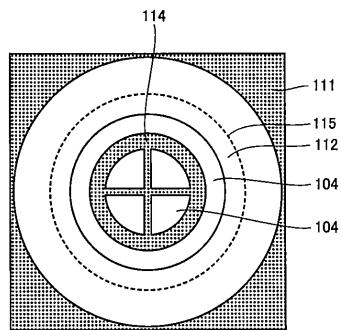

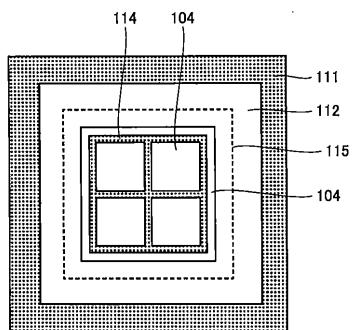

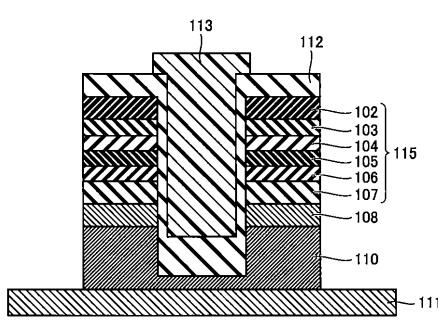

【図2】実施形態1の半導体発光素子を上面から見たときの一例の模式的な平面図である。

【図3】実施形態1の半導体発光素子を上面から見たときの他の一例の模式的な平面図である。

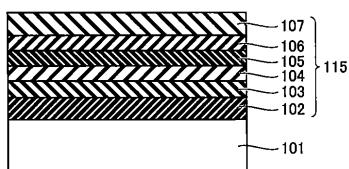

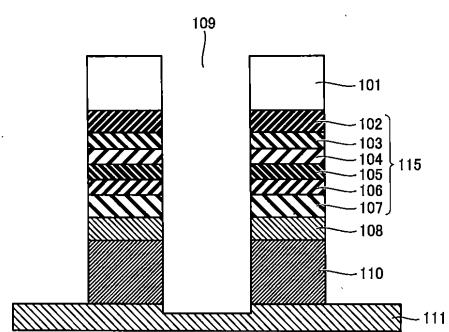

【図4】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

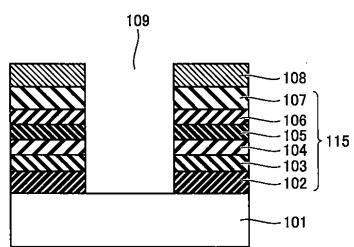

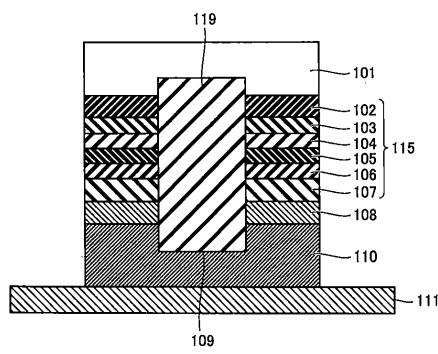

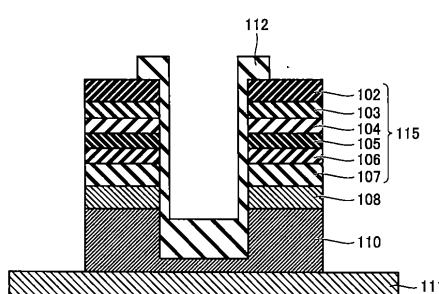

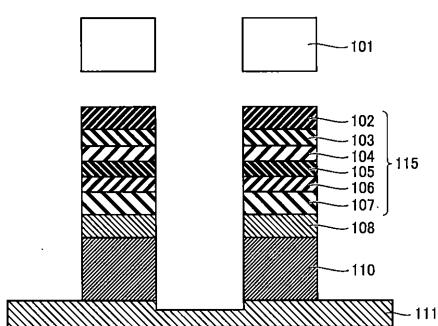

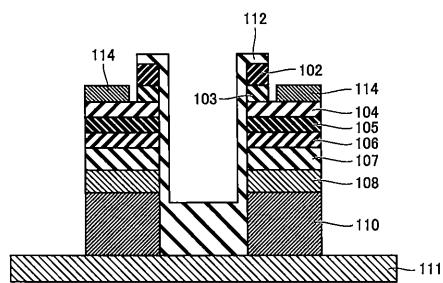

【図5】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図6】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

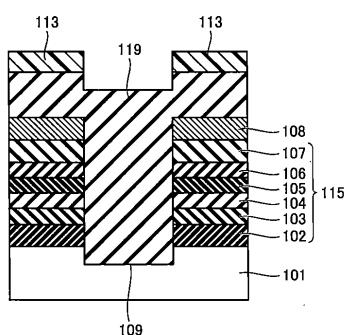

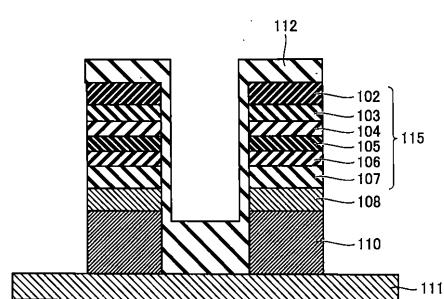

【図7】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

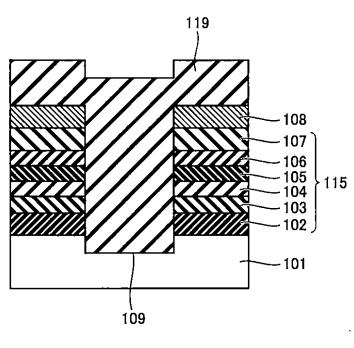

【図8】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

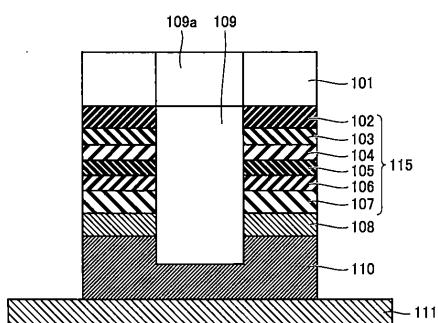

【図9】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図10】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図11】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

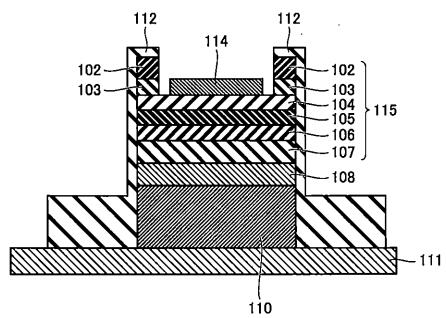

【図12】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

10

20

30

40

50

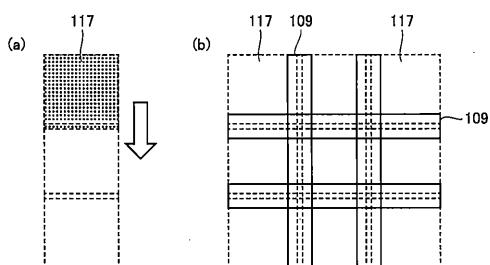

【図13】(a)および(b)は、エキシマレーザ光の照射工程の一部を図解する模式的な平面図である。

【図14】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図15】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図16】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図17】LLO法によるサファイア基板の剥離工程直後のAlN層の表面の光学顕微鏡による観察写真である。

10

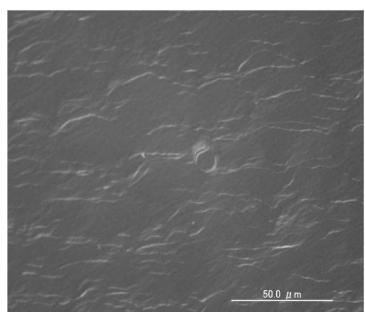

【図18】LLO法によるサファイア基板の剥離工程後に、60のフッ酸に15分間浸漬させた後のAlN層の表面の光学顕微鏡による観察写真である。

【図19】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図20】実施形態1の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図21】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図22】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

20

【図23】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図24】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図25】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図26】実施形態2の半導体発光素子の製造方法の一例の製造工程の一部を図解する模式的な断面図である。

【図27】実施形態2の半導体発光素子の模式的な断面図である。

#### 【発明を実施するための形態】

##### 【0010】

以下、実施形態について説明する。なお、実施形態の説明に用いられる図面において、同一の参照符号は、同一部分または相当部分を表わすものとする。また、以下の実施形態において、「AlGaN」は、 $Al_xGa_{1-x}N$  ( $0 < x < 1$ ) の式で表わされる窒化物を意味している。

##### 【0011】

###### 【実施形態1】

###### <半導体発光素子の構造>

図1に、実施形態1の半導体発光素子の模式的な断面図を示す。図1に示すように、実施形態1の半導体発光素子は、導電性の支持基板111と、支持基板111上の導電性の接合層110と、接合層110上のp側電極108と、p側電極108上のp型GaN層107と、p型GaN層107上のp型AlGaN層106と、p型AlGaN層106上の活性層105と、活性層105上のn型AlGaN層104と、n型AlGaN層104上のAlGaN層103と、AlGaN層103上のAlN層102と、n型AlGaN層104上のn側電極114とを備えている。

40

##### 【0012】

また、実施形態1の半導体発光素子は、n型AlGaN層104の露出している表面の領域を除く半導体発光素子部115の表面、半導体発光素子部115、p側電極108および接合層110のそれぞれの側面、ならびに接合層110の表面を覆うように窒化物絶縁保護膜112をさらに備えている。半導体発光素子部115は、p型GaN層107と

50

、p型AlGaN層106と、活性層105と、n型AlGaN層104と、AlGaN層103と、AlN層102とがこの順に積層された積層体から構成されている。

#### 【0013】

また、支持基板111と半導体発光素子部115とがp側電極108を介して接合層110により接合されている。半導体発光素子部115においては、支持基板111と反対側に、n型AlGaN層104の表面が一部露出しており、n型AlGaN層104の露出した表面にn側電極114が形成されている。

#### 【0014】

図2に、実施形態1の半導体発光素子を上面から見たときの一例の模式的な平面図を示す。また、図3に、実施形態1の半導体発光素子を上面から見たときの他の一例の模式的な平面図を示す。図2および図3に示すように、半導体発光素子部115の上面は、LLO法に適した四角形または円形の形状を有していることが好ましいが、六角形などの多角形であってもよい。特に、半導体発光素子部115は、半導体発光素子部115の上面の形状が円形に形成されることが好ましい。半導体発光素子部115の上面が円形の形状に形成される場合には、後述するLLO法による成長用基板の剥離工程で、四方に均一にガスが放出されるため、半導体発光素子部115にクラックおよび欠けが発生するのを抑制することができる。また、半導体発光素子部115の上面を円形の形状に形成にした場合には、窒化物絶縁保護膜112を均質に形成することができるため、窒化物絶縁保護膜112と半導体発光素子部115との密着性を向上させることができる。

#### 【0015】

##### <半導体発光素子の製造方法>

以下に、図面を参照して、実施形態1の半導体発光素子の製造方法の一例について説明する。

#### 【0016】

##### (半導体発光素子部の形成工程)

まず、図4の模式的断面図に示すように、成長用基板としてのサファイア基板101上にAlN層102を含む半導体発光素子部115を形成する。半導体発光素子部115の形成方法は特に限定されないが、半導体発光素子部115は、たとえば、有機金属気相成長(MOCVD)法によって成長用基板としてのサファイア基板101の表面上に、AlN層102、AlGaN層103、n型AlGaN層104、活性層105、p型AlGaN層106およびp型GaN層107を順次積層することにより形成することができる。なお、成長用基板としては、サファイア基板101の代わりに、AlN基板を用いることもできる。

#### 【0017】

##### (p側電極の形成工程)

次に、図5の模式的断面図に示すように、p型GaN層107の表面上にp側電極108を形成する。p側電極108の形成方法は特に限定されないが、p側電極108は、たとえば、電子ビーム(EB)蒸着法により、厚さ20nmの白金(Pt)層と、厚さ20nmの金(Au)層とを順次積層することによって形成することができる。なお、p側電極108としては、Pt層とAu層との積層体以外にも、たとえば、ニッケル(Ni)層とAu層との積層体などを用いてもよい。また、Pt層とAu層との積層体上、またはNi層とAu層との積層体上に反射率を向上させるためのアルミニウム(Al)層とAu層との積層体を形成してもよい。また、p側電極108の形成方法としては、EB蒸着法以外にも、たとえばスパッタ法などを用いてもよい。

#### 【0018】

上述のp側電極108を用いることによって、半導体発光素子部115との良好なオーミック特性と、支持基板111との優れた密着性とを兼ね備えることができる。また、接合層110にAgを含む熱硬化型の導電性接着剤を用いた場合には、Pt層がバリアメタルとして働き、半導体発光素子部115にAgが拡散するのを抑制することができる。

#### 【0019】

10

20

30

40

50

### (溝の形成工程)

次に、図6の模式的断面図に示すように、半導体発光素子部115を複数に分割する溝109を形成する。溝109は、たとえば、半導体発光素子部115のp側電極108側からサファイア基板101に達する深さを有するように形成することができる。また、溝109は、たとえば、後述するLLO法におけるレーザ光の照射領域と重なるとともに、半導体発光素子部115を取り囲むように形成することができる。後述するLLO法による成長用基板101の剥離工程の前に半導体発光素子部115を複数に分割する溝109を形成することによって、LLO法による成長用基板101の剥離工程において発生するN<sub>2</sub>ガスを半導体発光素子部115の外部に排出することができる。これにより、N<sub>2</sub>ガスの発生によって半導体発光素子部115にかかる圧力を低減することができるため、半導体発光素子部115にクラックおよび欠けが生じるのを抑制することができる。10

#### 【0020】

溝109は、たとえば、p側電極108の表面上に、フォトリソグラフィーによって任意のレジストパターンを形成した後、反応性イオンエッティング(RIE)などのドライエッティングにより、p側電極108および半導体発光素子部115の一部を厚さ方向に除去することによって形成されることが好ましい。ドライエッティングにより溝109を形成することによって、任意の形状で、溝109の底面および側壁に凹凸が少ない溝109を形成することができる。これにより、後述の拡散抑制層を、密着性良く形成することができる。また、溝109の形成方法としては、ドライエッティング以外にも、たとえば、レーザスクライプまたはブレードダイニングなどを用いることもできる。20

#### 【0021】

##### (拡散抑制層の形成工程)

次に、図7の模式的断面図に示すように、溝109の少なくとも一部を埋め込むように拡散抑制層119を形成する。拡散抑制層119としては、たとえば、スピノングラス(SOG)材料を半導体発光素子部115の全面に塗布することによって形成した酸化珪素(SiO<sub>2</sub>)層を用いることができる。拡散抑制層119として、SOG材料を塗布して形成したSiO<sub>2</sub>層を用いることによって、後述する接合層110によるp側電極108と支持基板111との接合時に、接合層110が半導体発光素子部115の側面に付着して、リークの原因になるのを抑制することができる。

#### 【0022】

##### (拡散抑制層のパターニング工程)

次に、図8の模式的断面図に示すように、溝109の形成領域以外の拡散抑制層119の表面上にレジスト層113を形成する。レジスト層113は、たとえばフォトリソグラフィーにより形成することができる。

#### 【0023】

次に、レジスト層113をマスクとしたフッ素系のガスを用いたドライエッティングによって、たとえば図9の模式的断面図に示すように、拡散抑制層119をパターニングする。ここで、拡散抑制層119は、所望に応じた形状に形成することができる。

#### 【0024】

##### (p側電極と支持基板との接合工程)

次に、図10の模式的断面図に示すように、p側電極108と支持基板111とを接合する。p側電極108と支持基板111との接合は、たとえば、支持基板111の表面上に接合層110を設置し、支持基板111と対向するようにp側電極108を接合層110上に設置した後に、支持基板111とp側電極108とを加熱圧着または無加圧状態での接合により行うことができる。

#### 【0025】

支持基板111としては、たとえば、CuW基板またはp型半導体がドープされたSi基板の表面上に、たとえば厚さ20nmのNi層と厚さ150nmのAu層とが順次積層してなる金属層を形成したものなどを用いることができる。

#### 【0026】

10

20

30

40

50

接合層110としては、上述したAgを含む熱硬化型の導電性接着剤を用いることもできるが、それ以外にも、たとえば、Au、Sn、Pd、In、Ti、Ni、W、Mo、Au-Sn、Sn-Pd、In-Pd、Ti-Pt-AuまたはTi-Pt-Sn等を用いることもできる。接合層110に、これらの材料を用いた場合には、共晶反応により、p側電極108との接合が可能となる。なお、共晶反応により形成された共晶形成層は、p側電極108と接合層110との接合時にこれらの層から互いに拡散して共晶を形成することにより形成される。

#### 【0027】

接合層110にAgを含む熱硬化型の導電性接着剤を用いたときの支持基板111とp側電極108との加熱圧着の条件としては、たとえば、数百N～数kN程度の加圧を行って、150～400程度に加熱し、真空雰囲気、窒素雰囲気、または大気雰囲気下で、15分程度保持する条件などを挙げることができる。無加圧状態での接合条件としては、たとえば、真空雰囲気、窒素雰囲気、または大気雰囲気下で、200程度加熱し、60分程度保持する条件などを挙げることができる。このような条件でp側電極108と支持基板111との接合を行うことにより、接合層110が溶融した後に固化して、支持基板111とp側電極108との接合が行われる。このとき、半導体発光素子部115の側面には拡散抑制層119が設置されているため、半導体発光素子部115の側面に接合層110が付着するのを抑制することができる。なお、接合条件は、接合層110の特性に合わせて適宜選択することができる。

#### 【0028】

##### (拡散抑制層の除去工程)

次に、図11の模式的断面図に示すように、拡散抑制層119を除去する。拡散抑制層119は、たとえば、サファイア基板101の裏面側から表面側まで貫通して拡散抑制層119を露出させる貫通孔109aを形成した後、貫通孔109aからフッ素系のガスを用いたドライエッキングまたはブレードダイシングなどを行うことによって除去することができる。このように、拡散抑制層119を除去することによって、溝109に空間を確保することができる。そのため、後述のLLO法によるサファイア基板101の剥離工程において発生するガスを溝109を通して外部に排出することができるため、当該ガスにより半導体発光素子部115にかかる応力を低減することができる。これにより、半導体発光素子部115にクラックおよび欠けが発生するのを抑制することができる。

#### 【0029】

なお、拡散抑制層119の除去は、上記の方法以外にも、たとえば、サファイア基板101に溝109を貫通させることなく、常温(約20)でフッ酸で処理することによっても可能である。

#### 【0030】

また、拡散抑制層119を除去する工程の前に、サファイア基板101を裏面側(支持基板111とは反対側)から研削および研磨を行うことによって、サファイア基板101を任意の厚さに加工してもよい。

#### 【0031】

##### (LLO法によるサファイア基板の剥離工程)

次に、図12の模式的断面図に示すように、半導体発光素子部115から成長用基板であるサファイア基板101をLLO法により剥離することによって、AIN層102の表面を露出させる。LLO法によるサファイア基板101の剥離工程は、たとえば、波長約193nm程度のエキシマレーザ光をサファイア基板101の裏面側から照射することによって行うことができる。このとき、エキシマレーザ光のエネルギー密度は、たとえば約500mJ/cm<sup>2</sup>～800mJ/cm<sup>2</sup>とすることができる。

#### 【0032】

エキシマレーザ光の照射は、たとえば図13(a)の模式的平面図に示すように、エキシマレーザ光の1ショット当たりの照射領域117の一部が重複するように矢印の方向に移動して繰り返し照射されることが好ましく、たとえば図13(b)の模式的平面図に示

10

20

30

40

50

すように、図13(a)に示す矢印と直交する方向にもエキシマレーザ光の1ショット当たりの照射領域117の一部が重複するように照射されることがより好ましい。この場合には、サファイア基板101の全面にエキシマレーザ光を照射することができるため、LL0法によるサファイア基板101の剥離をより確実に行うことができる。

#### 【0033】

また、エキシマレーザ光の1ショット当たりの照射領域117に溝109が含まれるようにエキシマレーザ光が照射されることが好ましい。エキシマレーザ光の照射によって、A1N層102の一部が分解することによってN<sub>2</sub>ガスが発生する。N<sub>2</sub>ガスが発生するのは、成長用基板101と半導体発光素子部115との界面である。そのため、エキシマレーザ光の1ショット当たりの照射領域117の内側に溝109を形成することによって、溝109を通してN<sub>2</sub>ガスを外部に排出することができる。これにより、発生したN<sub>2</sub>ガスの半導体発光素子部115に対する圧力が低減するため、半導体発光素子部115にクラックおよび欠けが発生するのを抑制することができる。10

#### 【0034】

##### (窒化物絶縁保護膜の形成工程)

次に、図14の模式的断面図に示すように、少なくともp側電極108と支持基板111との接合部である接合層110およびp側電極108の露出部に窒化物絶縁保護膜112を形成する。窒化物絶縁保護膜112は、たとえば、スパッタ法により、半導体発光素子部115側から形成することができる。20

#### 【0035】

窒化物絶縁保護膜112としては、A1N膜を用いることが好ましい。窒化物絶縁保護膜112としてA1N膜を用いた場合には、後述の高温フッ酸処理工程における耐性が高いため、後述の高温フッ酸処理工程において保護膜として用いることができる。20

#### 【0036】

また、窒化物絶縁保護膜112としては、活性層105の屈折率と空気の屈折率との間の屈折率を有する材質を用いることが好ましい。この場合には、活性層105から放出された光の半導体発光素子部115と窒化物絶縁保護膜112との界面における全反射および窒化物絶縁保護膜112と空気との界面における全反射を抑制することができるため、活性層105からの光を外部に高効率で取り出すことができる。たとえば、活性層105にAlGaN膜を用いた場合には、窒化物絶縁保護膜112にA1N膜を用いることが好ましい。A1Nの屈折率は1.9~2.2程度であるため、AlGaNの屈折率である2.0~2.5よりも小さく、空気の屈折率1.0よりも大きいためである。また、窒化物絶縁保護膜112にA1N膜を用いた場合には、窒化物絶縁保護膜112は、AlGaN膜からなる活性層105から放出される光に対して透光性を有するため、窒化物絶縁保護膜112における光の吸収が抑えられ、活性層105からの光の取り出し効率を高めることができる。30

#### 【0037】

次に、図15の模式的断面図に示すように、フォトリソグラフィーによってレジスト層113をパターニングし、リン酸などを用いてA1N膜などからなる窒化物絶縁保護膜112を一部除去する。これにより、図16の模式的断面図に示すように、窒化物絶縁保護膜112が溝109を覆うとともに、少なくともp側電極108と支持基板111との接合部(接合層110)およびp側電極108の露出部を覆うことができる。40

#### 【0038】

また、窒化物絶縁保護膜112の形成する前にフォトリソグラフィーによってレジスト層113をパターニング形成しておき、窒化物絶縁保護膜112を形成した後、リフトオフによって窒化物絶縁保護膜112をパターニングしてもよい。

#### 【0039】

##### (高温フッ酸処理工程)

次に、上記のLL0法によるサファイア基板101の剥離によって露出したA1N層102の表面を40以上のフッ酸と接触させる。これにより、LL0法によるサファイア

10

20

30

40

50

基板 101 の剥離後に A1N 層 102 の表面に残留した A1 を含む残留物を除去することができる。A1 を含む残留物を除去することによって、後述のエッティング工程において、A1 を含む残留物がエッティングマスクとなって、エッティング後の n 側電極 114 の形成面にピラー形状の突起物が発生することによる n 側電極 114 の形成不良の発生を抑制することができる。

#### 【0040】

上記の A1N 層 102 の表面とフッ酸との接触は、A1N 層 102 の表面を 40 以上のフッ酸、好ましくは 60 以上のフッ酸に浸漬させることにより行うことができる。なお、フッ酸への浸漬時間は、特に限定されず適宜設定することができ、たとえば、60 のフッ酸により A1N 層 102 の表面を処理する場合には、A1N 層 102 の表面のフッ酸への浸漬時間は、たとえば 15 分間とすることができる。

10

#### 【0041】

図 17 に、LLD 法によるサファイア基板 101 の剥離工程直後の A1N 層 102 の表面の光学顕微鏡による観察写真を示す。図 17 に示すように、A1N 層 102 の表面全体には、A1 を含む残留物が付着しており、A1N 層 102 ではないモフォロジーを観察することができる。

#### 【0042】

図 18 に、LLD 法によるサファイア基板 101 の剥離工程後に、60 のフッ酸に 15 分間浸漬させた後の A1N 層 102 の表面の光学顕微鏡による観察写真を示す。図 18 に示すように、フッ酸との接触後の A1N 層 102 の表面には、A1N 層 102 特有のモフォロジーが見えており、図 17 で確認されたような A1 を含む残留物が除去されている。このように、フッ酸処理を行うことによって、LLD 法により成長用基板を剥離した後の  $A1_x Ga_{1-x} N$  ( $0 < x < 1$ ) 層の表面に特有に発生する A1 を含む残留物を除去することができる。これにより、後述するエッティング工程において、当該 A1 を含む残留物がエッティングマスクとなって、エッティング後の n 側電極 114 の形成面にピラー形状の突起物が発生するのを抑制することができるため、n 側電極 114 の形成不良の発生を抑制することができる。

20

#### 【0043】

##### (エッティング工程)

次に、図 19 の模式的断面図に示すように、窒化物絶縁保護膜 112 が設置されていない半導体発光素子部 115 の部分をエッティングする。半導体発光素子部 115 のエッティングは、たとえば、パターニングされた窒化物絶縁保護膜 112 をエッティングマスクとして用いてドライエッティングを行うことによって、A1N 層 102 および A1GaN 層 103 をそれぞれ厚さ方向にエッティングし、n 型 A1GaN 層 104 の表面を露出させることにより行うことができる。A1N 層 102 および A1GaN 層 103 の厚さ方向のエッティングは、たとえば C1 ガスを用いた RIE などのドライエッティングによって行われることが好ましい。接合層 110 は窒化物絶縁保護膜 112 で保護されていることから、当該ドライエッティングによって接合層 110 がエッティングされて飛散し、半導体発光素子部 115 に付着するのを抑制することができる。

30

#### 【0044】

##### (n 側電極の形成工程)

次に、上記のエッティングによって露出した n 型 A1GaN 層 104 の表面上に n 側電極 114 を形成する。n 側電極 114 は、たとえば、フォトリソグラフィーによって任意のパターンのレジスト層（図示せず）を形成した後に所定の金属層を形成し、その後、リフトオフを行うことによって、図 20 の模式的断面図に示すような任意のパターンに形成することができる。

40

#### 【0045】

n 側電極 114 は、たとえば、厚さ 25 nm の Ti 層と厚さ 200 nm の Al 層とを EB 蒸着法で順次積層することによって形成することができる。なお、EB 蒸着法以外にもスパッタ法などを用いて n 側電極 114 を形成することもできる。

50

## 【0046】

(素子分離工程)

次に、複数の半導体発光素子に分離することによって、図1に示す実施形態1の半導体発光素子を作製する。半導体発光素子の分離は、たとえば、溝109に沿って、窒化物絶縁保護膜112、接合層110および支持基板111を切断することにより行うことができる。窒化物絶縁保護膜112、接合層110および支持基板111の切断は、たとえば、ダイヤモンドスクライブ、レーザスクライブ、ブレードダイシング、ブレードブレイク若しくはローラーブレイクの1種またはこれらの2種以上を組み合わせて行うことができる。

## 【0047】

10

<作用効果>

本発明者らは、LLO法により $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層を分解して成長用基板を剥離する場合には、LLO法により $GaN$ 層を分解して成長用基板を剥離する場合と比べて、高出力のエネルギー密度のレーザ光が必要となり、そのようなレーザ光を用いて $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層を分解した場合には $A_1$ 金属や $A_1$ を含む物質などの $A_1$ を含む非常に強固に固着した残留物が生成することを見出した。また、本発明者らは、このような $A_1$ を含む残留物が、後述の電極形成面を露出させるエッチング工程においてエッティングマスクとなり、電極形成面にピラー形状の突起物を発生させ、当該突起物により電極の形成不良が発生し、半導体発光素子の製造歩留まりを低下させることを見出した。これにより、本発明者らは、LLO法により $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層にレーザ光を照射して $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層を分解することにより成長用基板を剥離して高い製造歩留まりで半導体発光素子を作製する場合には、 $A_1$ 金属や $A_1$ を含む物質等の残留物を除外しなければならないという課題を見出した。

20

## 【0048】

そして、本発明者らが鋭意検討した結果、このような $A_1$ を含む残留物の除去には、40以上のフッ酸による処理が有効であることを見出した。そのため、電極形成面を露出させるためのエッティング工程前に $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層の表面を40以上のフッ酸と接触させることによって $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層の表面の $A_1$ を含む残留物を予め除去しておくことによって、その後の電極形成面を露出させるためのエッティング工程において、これらの残留物がエッティングマスクとなって電極形成面にピラー形状の突起物が形成されるのを抑制することができ、電極の形成不良の発生を抑制することができるため、高い製造歩留まりで半導体発光素子を作製できることを見出した。

30

## 【0049】

また、電極形成面を露出させるためのエッティング工程時に第1電極と成長用基板との接合部および第1電極が窒化物絶縁保護膜で保護されているため、当該エッティング工程時において第1電極と成長用基板との接合部および第1電極に対するエッティングにより導電性物質が生成し、半導体発光素子部の側面に付着することによってリーケパスが形成されるのを抑制することができ、第1電極と第2電極との間の絶縁性の確保をより確実なものとすることができるため、半導体発光素子の製造歩留まりを向上することができる。

## 【0050】

40

以上の理由により、本実施形態においては、LLO法により成長用基板を剥離して $A_1_x Ga_{1-x}N$  ( $0 < x < 1$ )層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

## 【0051】

なお、特許文献1および特許文献2は、 $A_1GaN$ 層にレーザ光を照射して $A_1GaN$ 層を分解することにより成長用基板を剥離する際に特有の課題については全く気づいていないため、 $A_1$ を含む残留物を除去することができない。そのため、仮に、特許文献1および特許文献2に記載の方法を用いて $A_1GaN$ 層にレーザ光を照射して $A_1GaN$ 層を分解することにより成長用基板を剥離して半導体発光素子を作製した場合でも、成長用基板の剥離後のエッティング工程において当該 $A_1$ を含む残留物がエッティングマスクとして機

50

能するため、ピラー形状の突起物が電極形成面に形成されることによって、電極の形成不良が発生する。一方、本実施形態においては、このような問題が生じないため、半導体発光素子の製造歩留まりを向上することができる。

#### 【0052】

<実施形態1の変形例>

上記においては、LLO法による成長用基板の剥離によってAlN層102の表面を露出させたが、AlGaN層103の表面を露出させてよい。

#### 【0053】

また、上記においては、n型とp型とが入れ替わっていてもよく、上記においてn型とp型とが入れ替わった場合には、p側電極108はn側電極となり、n側電極114はp側電極となる。

10

#### 【0054】

[実施形態2]

実施形態2は、半導体発光素子の製造工程が実施形態1と異なっていることを特徴としている。

#### 【0055】

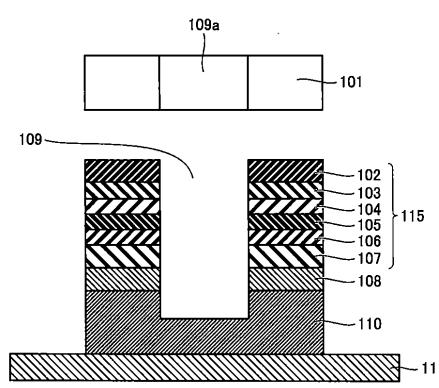

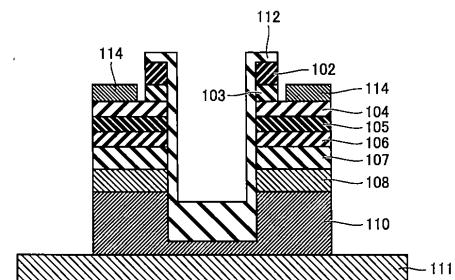

(p側電極と支持基板との接合工程)

すなわち、図21の模式的断面図に示すように、半導体発光素子部115を表側から裏側に貫通することなく、半導体発光素子部115上のp側電極108と支持基板111とを接合層110により接合する。

20

#### 【0056】

(第2の溝の形成工程)

次に、図22の模式的断面図に示すように、サファイア基板101、半導体発光素子部115、p側電極108および接合層110を貫通する溝109を形成する。溝109は、たとえば、レーザスクライプまたはブレードダイシングにより、支持基板111の表面が露出する深さ、または支持基板111の表面よりも深くなる深さまで形成することができる。これにより、後述のLLO法によるサファイア基板101の剥離工程時に発生するN<sub>2</sub>ガスを外部に排出する経路を簡易に形成することができる。なお、溝109の形成前に、サファイア基板101を裏面側から研削および研磨を行うことによって、サファイア基板101を任意の厚さに、加工してもよい。

30

#### 【0057】

(LLO法によるサファイア基板の剥離工程)

次に、図23の模式的断面図に示すように、半導体発光素子部115から成長用基板であるサファイア基板101をLLO法により剥離することによって、AlN層102の表面を露出させる。

#### 【0058】

(窒化物絶縁保護膜の形成工程)

次に、図24の模式的断面図に示すように、少なくともp側電極108と支持基板111との接合部である接合層110およびp側電極108の露出部に窒化物絶縁保護膜112を形成する。ここで、窒化物絶縁保護膜112は、実施形態1とは異なり、支持基板111の表面も覆っているため、支持基板111とp側電極108との接合強度が向上し、支持基板111とp側電極108との剥離が抑制できるとともに、窒化物絶縁保護膜112の剥離も抑制することができる。

40

#### 【0059】

(高温フッ酸処理工程)

次に、窒化物絶縁保護膜112の一部を除去して所定の形状にパターニングした後に露出したAlN層102の表面を40以上のフッ酸と接触させる。これにより、AlN層102の表面のAlを含む残留物を除去することができる。

#### 【0060】

(エッチング工程)

10

20

30

40

50

次に、図25の模式的断面図に示すように、窒化物絶縁保護膜112が設置されていない半導体発光素子部115の部分をエッティングする。これにより、n型AlGaN層104の表面を露出させる。

#### 【0061】

(n側電極の形成工程)

次に、図26の模式的断面図に示すように、上記のエッティングによって露出したn型AlGaN層104の表面上にn側電極114を形成する。

#### 【0062】

(素子分離工程)

次に、複数の半導体発光素子に分離することによって、図27に示す実施形態2の半導体発光素子を作製する。半導体発光素子の分離は、たとえば、溝109に沿って、窒化物絶縁保護膜112および支持基板111を切断することにより行うことができる。窒化物絶縁保護膜112および支持基板111の切断は、たとえば、ダイヤモンドスクライブ、レーザスクライブ、ブレードダイシング、ブレードブレイク若しくはローラーブレイクの1種またはこれらの2種以上を組み合わせて行うことができる。

#### 【0063】

実施形態2における上記以外の説明は実施形態1と同様であるため、その説明については繰り返さない。

#### 【0064】

[実施形態3]

実施形態3は、窒化物絶縁保護膜112が窒化珪素(SiN)膜から形成されている点で実施形態1と異なっていることを特徴としている。

#### 【0065】

(窒化物絶縁保護膜の形成工程)

図14に示すように、少なくともp側電極108と支持基板111との接合部である接合層110およびp側電極108の露出部にSiN膜からなる窒化物絶縁保護膜112をスパッタ法により形成する。窒化物絶縁保護膜112としてSiN膜を用いた場合にも、後述の高温フッ酸処理工程における耐性が高いため、後述の高温フッ酸処理工程において保護膜として用いることができる。

#### 【0066】

また、SiNの屈折率は1.9程度であり、AlGaNの屈折率である2.0~2.5よりも小さく、空気の屈折率1.0よりも大きい。そのため、たとえば、活性層105にAlGaN膜を用い、窒化物絶縁保護膜112にSiN膜を用いた場合には、活性層105から放出された光の半導体発光素子部115と窒化物絶縁保護膜112との界面における全反射および窒化物絶縁保護膜112と空気との界面における全反射を抑制することができるため、活性層105からの光を外部に高効率で取り出すことができる。さらに、SiN膜からなる窒化物絶縁保護膜112は、AlGaN膜からなる活性層105から放出される光に対して透光性を有するため、窒化物絶縁保護膜112における光の吸収が抑えられ、活性層105からの光の取り出し効率を高めることができる。

#### 【0067】

次に、図15に示すように、フォトリソグラフィーによってレジスト層113をパターニングし、リン酸などを用いてSiN膜からなる窒化物絶縁保護膜112を一部除去する。これにより、図16に示すように、窒化物絶縁保護膜112が溝109を覆うとともに、少なくともp側電極108と支持基板111との接合部(接合層110)およびp側電極108の露出部を覆うことができる。

#### 【0068】

(高温フッ酸処理工程)

次に、上記のLLO法によるサファイア基板101の剥離によって露出したAlN層102の表面を40℃以上のフッ酸と接触させる。これにより、LLO法によるサファイア基板101の剥離後にAlN層102の表面に残留したAlを含む残留物を除去すること

10

20

30

40

50

ができる。

**【0069】**

(エッチング工程)

次に、図19に示すように、窒化物絶縁保護膜112が設置されていない半導体発光素子部115の部分をドライエッティングすることにより、n型AlGaN層104の表面を露出させる。

**【0070】**

(n側電極の形成工程)

次に、上記のドライエッティングによって露出したn型AlGaN層104の表面上にn側電極114を形成する。n側電極114は、たとえば、フォトリソグラフィーによって任意のパターンのレジスト層(図示せず)を形成した後に所定の金属層を形成し、その後、リフトオフを行うことによって、図20に示すような任意のパターンに形成することができる。

**【0071】**

(素子分離工程)

次に、複数の半導体発光素子に分離することによって、図1に示す構造を有する実施形態3の半導体発光素子が作製される。

**【0072】**

実施形態3における上記以外の説明は実施形態1と同様であるため、その説明については繰り返さない。

**【0073】**

[実施形態4]

実施形態4は、窒化物絶縁保護膜112がSiN膜から形成されている点で実施形態2と異なっていることを特徴としている。

**【0074】**

(p側電極と支持基板との接合工程)

図21に示すように、サファイア基板101を表側から裏側に貫通する溝109を形成することなく、半導体発光素子部115上のp側電極108と支持基板111とを接合層110により接合する。

**【0075】**

(第2の溝の形成工程)

次に、図22に示すように、サファイア基板101、半導体発光素子部115、p側電極108および接合層110を貫通する溝109を形成する。

**【0076】**

(LLO法によるサファイア基板の剥離工程)

次に、図23に示すように、半導体発光素子部115から成長用基板であるサファイア基板101をLLO法により剥離することによって、AlN層102の表面を露出させる。

**【0077】**

(窒化物絶縁保護膜の形成工程)

次に、図24に示すように、少なくともp側電極108と支持基板111との接合部である接合層110およびp側電極108の露出部にSiN膜からなる窒化物絶縁保護膜112を形成する。

**【0078】**

(高温フッ酸処理工程)

次に、窒化物絶縁保護膜112の一部を除去して所定の形状にパターニングした後に露出したAlN層102の表面を40以上のフッ酸と接触させる。これにより、AlN層102の表面のAlを含む残留物を除去することができる。

**【0079】**

(エッチング工程)

10

20

30

40

50

次に、図25に示すように、窒化物絶縁保護膜112が設置されていない半導体発光素子部115の部分をドライエッティングすることにより、n型AlGaN層104の表面を露出させる。

#### 【0080】

(n側電極の形成工程)

次に、図26に示すように、上記のドライエッティングによって露出したn型AlGaN層104の表面上にn側電極114を形成する。

#### 【0081】

(素子分離工程)

次に、複数の半導体発光素子に分離することによって、図27に示す構造を有する実施形態4の半導体発光素子を作製する。 10

#### 【0082】

実施形態4における上記以外の説明は実施形態2と同様であるため、その説明については繰り返さない。

#### 【0083】

[実施形態5]

実施形態5は、窒化物絶縁保護膜112を高温フッ酸処理工程の後に除去し、酸化物絶縁保護膜112を形成する点で実施形態2と異なっていることを特徴としている。 20

#### 【0084】

(窒化物絶縁保護膜の形成工程)

図24に示すように、少なくともp側電極108と支持基板111との接合部である接合層110およびp側電極108の露出部にAlN膜などの窒化物絶縁保護膜112をスパッタ法により形成する。 20

#### 【0085】

(高温フッ酸処理工程)

次に、窒化物絶縁保護膜112の一部を除去して所定の形状にパターニングした後に露出したAlN層102の表面を40以上のフッ酸と接触させる。これにより、AlN層102の表面のAlを含む残留物を除去する。 30

#### 【0086】

(窒化物絶縁保護膜の除去工程)

次に、窒化物絶縁保護膜112をリン酸などによって除去し、その後、酸化物絶縁膜112をスパッタ法によって形成する。ここで、酸化物絶縁膜としては、SiO<sub>2</sub>膜を用いることが好ましい。 30

#### 【0087】

SiO<sub>2</sub>の屈折率は1.4~1.6であり、AlGaNの屈折率である2.0~2.5よりも小さく、空気の屈折率1.0よりも大きい。そのため、たとえば、活性層105にAlGaN膜を用い、酸化物絶縁保護膜112にSiO<sub>2</sub>膜を用いた場合にも、活性層105から放出された光の半導体発光素子部115と酸化物絶縁保護膜112との界面における全反射および酸化物絶縁保護膜112と空気との界面における全反射を抑制することができるため、活性層105からの光を外部に高効率で取り出すことができる。さらに、SiO<sub>2</sub>膜からなる酸化物絶縁保護膜112も、AlGaN膜からなる活性層105から放出される光に対して透光性を有するため、酸化物絶縁保護膜112における光の吸収が抑えられ、活性層105からの光の取り出し効率を高めることができる。 40

#### 【0088】

(エッティング工程)

次に、図25に示すように、SiO<sub>2</sub>膜からなる酸化物絶縁膜112が設置されていない半導体発光素子部115の部分をドライエッティングすることにより、n型AlGaN層104の表面を露出させる。

#### 【0089】

(n側電極の形成工程)

50

次に、図26に示すように、上記のドライエッティングによって露出したn型AlGaN層104の表面上にn側電極114を形成する。

#### 【0090】

##### (素子分離工程)

次に、複数の半導体発光素子に分離することによって、図27に示す構造を有する実施形態5の半導体発光素子を作製する。

#### 【0091】

実施形態5における上記以外の説明は実施形態2と同様であるため、その説明については繰り返さない。

#### 【0092】

##### [付記]

(1)ここで開示された実施形態は、成長用基板上に $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層を含む半導体発光素子部を形成する工程と、半導体発光素子部上に第1電極を形成する工程と、半導体発光素子部を複数に分割する溝を形成する工程と、第1電極と支持基板とを接合する工程と、半導体発光素子部から少なくとも成長用基板をレーザリフトオフにより剥離することによって $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層の表面を露出させる工程と、少なくとも第1電極と支持基板との接合部および第1電極に窒化物絶縁保護膜を形成する工程と、成長用基板を剥離することによって露出した $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層の表面を40以上フッ酸と接触させる工程と、窒化物絶縁保護膜が形成されていない半導体発光素子部の部分をエッティングする工程とを含む半導体発光素子の製造方法である。このような構成とすることにより、LLO法により $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層を分解して成長用基板を剥離する際に生じるAlを含む残留物を40以上のフッ酸により除去することができ、その後のエッティングにより露出した電極形成面のピラー形状の突起物の発生を抑制することができるため、電極の形成不良の発生を抑制することができ、半導体発光素子の製造歩留まりを向上することができる。また、電極形成面を露出させるためのエッティング工程時に第1電極と成長用基板との接合部および第1電極が窒化物絶縁保護膜で保護されているため、当該エッティング工程時において第1電極と成長用基板との接合部および第1電極に対するエッティングにより導電性物質が生成し、半導体発光素子部の側面に付着することによってリークパスが形成されるのを抑制することができ、第1電極と第2電極との間の絶縁性の確保をより確実なものとすることができますため、半導体発光素子の製造歩留まりを向上することができる。20

#### 【0093】

(2)ここで開示された実施形態は、エッティングする工程により露出した表面に第2電極を形成する工程を含むことが好ましい。この場合にも、LLO法により成長用基板を剥離して $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。30

#### 【0094】

(3)ここで開示された実施形態において、エッティングする工程は、少なくとも第1電極と支持基板との接合部および第1電極に窒化物絶縁保護膜が形成された状態で行われることが好ましい。この場合にも、LLO法により成長用基板を剥離して $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。40

#### 【0095】

(4)ここで開示された実施形態においては、窒化物絶縁保護膜を形成する工程の後に窒化物絶縁保護膜の一部を除去する工程を含み、除去する工程の後にフッ酸と接触させる工程およびエッティングする工程をこの順に行なうことが好ましい。この場合にも、LLO法により成長用基板を剥離して $Al_xGa_{1-x}N$  ( $0 < x < 1$ )層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。50

#### 【0096】

(5) ここで開示された実施形態において、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させる工程は、レーザ光の 1 ショット当たりの照射領域に前記溝が含まれるようにレーザ光を照射する工程を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

#### 【0097】

(6) ここで開示された実施形態においては、接合する工程の前に溝を形成する工程を行い、溝を形成する工程と接合する工程との間に溝の少なくとも一部を埋め込む拡散抑制層を形成する工程が含まれ、接合する工程の後に拡散抑制層を除去する工程が含まれることが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。10

#### 【0098】

(7) ここで開示された実施形態において、拡散抑制層を除去する工程は、成長用基板を貫通する貫通孔を形成することによって拡散抑制層を露出させる工程と、貫通孔から露出した拡散抑制層を除去する工程とを含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

#### 【0099】

(8) ここで開示された実施形態においては、接合する工程の後に溝を形成する工程を行い、溝を形成する工程は、少なくとも成長用基板、半導体発光素子部、第 1 電極および接合部を貫通して支持基板の表面まで達するように溝を形成する工程を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。20

#### 【0100】

(9) ここで開示された実施形態において、絶縁保護膜は、窒化物絶縁膜および酸化物絶縁膜の少なくとも一方を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。30

#### 【0101】

(10) ここで開示された実施形態において、窒化物絶縁膜は、窒化アルミニウム膜および窒化珪素膜の少なくとも一方を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

#### 【0102】

(11) ここで開示された実施形態において、酸化物絶縁膜は、酸化珪素膜を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。40

#### 【0103】

(12) ここで開示された実施形態は、窒化物絶縁保護膜を形成する工程の後に、窒化物絶縁保護膜を除去する工程を含み、窒化物絶縁保護膜を除去する工程の後に、酸化物絶縁保護膜を再度形成する工程を含むことが好ましい。この場合にも、LLO 法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

#### 【0104】

(13) ここで開示された実施形態は、支持基板と、支持基板上の接合部と、接合部上の第 1 電極と、第 1 電極上の半導体発光素子部と、半導体発光素子部上の第 2 電極と、少なくとも接合部の側面と、第 1 電極の側面と、半導体発光素子部の側面とを覆う窒化物絶50

縁保護膜とを備え、第2電極は、半導体発光素子部の支持基板と反対側の露出した表面上に設けられている半導体発光素子である。この場合にも、LLO法により成長用基板を剥離して  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させて半導体発光素子を製造する場合における半導体発光素子の製造歩留まりを向上することができる。

#### 【0105】

(14) ここで開示された実施形態は、半導体発光素子部の活性層が  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) からなり、窒化物絶縁保護膜の屈折率が  $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) の屈折率よりも小さいことが好ましい。この場合には、活性層から放出された光の半導体発光素子部と窒化物絶縁保護膜との界面における全反射および窒化物絶縁保護膜と空気との界面における全反射を抑制することができるため、活性層からの光を外部に高効率で取り出すことができる。10

#### 【0106】

以上の実施形態について説明を行なったが、上述の各実施形態の構成を適宜組み合わせることも当初から予定している。

#### 【0107】

今回開示された実施形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。20

#### 【産業上の利用可能性】

#### 【0108】

ここで開示された実施形態は、LLO法により成長用基板を剥離して、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$  ( $0 < x < 1$ ) 層の表面を露出させる半導体発光素子の製造方法および半導体発光素子に利用できる可能性がある。

#### 【符号の説明】

#### 【0109】

101 サファイア基板、102 AlN層、103 AlGaN層、104 n型AlGaN層、105 活性層、106 p型AlGaN層、107 p型GaN層、108 p側電極、109 溝、109a 貫通孔、110 接合層、111 支持基板、112 絶縁保護膜、113 レジスト層、114 n側電極、115 半導体発光素子部、117 照射領域、119 拡散抑制層。30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

---

フロントページの続き

審査官 大西 孝宣

(56)参考文献 特表2005-522873(JP,A)

国際公開第2006/104063(WO,A1)

特表2010-507262(JP,A)

特開2014-003283(JP,A)

特開2008-042143(JP,A)

特開2010-114411(JP,A)

米国特許出願公開第2010/0207123(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64