(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5633139号

(P5633139)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

(51) Int.Cl.

H02M 3/00 (2006.01)

F 1

H02M 3/00

B

請求項の数 7 (全 19 頁)

(21) 出願番号 特願2009-259647 (P2009-259647)

(22) 出願日 平成21年11月13日 (2009.11.13)

(65) 公開番号 特開2011-109746 (P2011-109746A)

(43) 公開日 平成23年6月2日 (2011.6.2)

審査請求日 平成24年11月12日 (2012.11.12)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(72) 発明者 吉江 信一

長野県諏訪市大和三丁目3番5号 セイコーエプソン株式会社内

審査官 神山 貴行

最終頁に続く

(54) 【発明の名称】情報機器

## (57) 【特許請求の範囲】

## 【請求項 1】

電源装置から直流電力が供給される第1の動作モードと、前記電源装置からの前記直流電力の供給が遮断される第2の動作モードとを有する情報機器であつて、

前記直流電力によって動作し、ラッチ開始信号を出力する制御部と、

前記電源装置に接続される入力端子、出力端子、及び前記入力端子と前記出力端子との接続状態がオン状態となる第1の姿勢と前記接続状態がオフ状態となる第2の姿勢とに切り換える操作部とを有する電源スイッチと、

前記電源スイッチの前記出力端子に接続される第1の端子及び接地される第2の端子を有する平滑コンデンサと、

前記電源スイッチの前記出力端子と前記制御部との間に接続され、前記制御部への前記直流電力の供給と遮断とを切り換えるスイッチ回路と、

前記制御部から入力された前記ラッチ開始信号をラッチするラッチ回路を有し、前記ラッチ回路における前記ラッチ開始信号のラッチ状態に基づいて前記制御部への前記直流電力の供給を遮断するスイッチ制御信号を生成し、前記スイッチ回路に前記スイッチ制御信号を出力するスイッチ制御信号生成回路と、

前記電源スイッチにおける前記接続状態を検出し、前記接続状態がオフ状態である場合に、前記ラッチ回路における前記ラッチ開始信号のラッチを解除するラッチ解除信号を前記スイッチ制御信号生成回路に出力するラッチ解除信号生成部と、を備え、

前記ラッチ回路および前記ラッチ解除信号生成部は、前記電源スイッチの前記出力端子

10

20

または前記平滑コンデンサから供給される前記直流電力によって動作可能に構成され、前記制御部は、前記第1の動作モードから前記第2の動作モードに移行するときに、前記ラッチ開始信号を前記スイッチ制御信号生成回路に出力し、

前記ラッチ回路は、前記ラッチ回路に前記ラッチ解除信号が入力されたときに、前記ラッチ開始信号のラッチを解除し、

前記スイッチ回路は、前記スイッチ制御信号が入力されているときに開状態になり、前記スイッチ制御信号が入力されていないときに閉状態になることを特徴とする情報機器。

#### 【請求項2】

前記ラッチ解除信号生成部は、前記電源スイッチの前記入力端子と前記出力端子と間の電位差を検出し、前記電位差が所定値以上である場合に、前記接続状態がオフ状態であるものとして、前記ラッチ解除信号を前記スイッチ制御信号生成回路に出力する電位差検出回路を備える請求項1に記載の情報機器。10

#### 【請求項3】

前記平滑コンデンサの前記第1の端子と前記ラッチ回路との間に、前記平滑コンデンサの残留電荷を放電させる抵抗器を備え、

前記抵抗器の抵抗値は、前記残留電荷の放電時における消費電力および放電時間に基づいて設定される請求項2に記載の情報機器。

#### 【請求項4】

前記制御部は、前記第1の動作モードである期間、前記スイッチ制御信号生成回路にラッチ解除禁止信号を出力し、前記第1の動作モードから前記第2の動作モードに移行するときに、前記ラッチ解除禁止信号の出力を停止し。20

前記スイッチ制御信号生成回路は、前記ラッチ解除禁止信号が入力されている期間、前記ラッチ回路への前記ラッチ解除信号の入力を禁止するラッチ解除禁止回路を備える請求項2または3記載の情報機器。

#### 【請求項5】

前記スイッチ制御信号生成回路は、前記ラッチ回路から前記ラッチ開始信号をラッチしていることを示す状態信号が入力されている期間および前記ラッチ解除禁止回路から前記ラッチ解除信号が入力されている期間、前記制御部への前記直流電力の供給を遮断する前記スイッチ制御信号を生成し、

前記ラッチ開始信号をラッチしていることを示す状態信号および前記ラッチ解除信号が入力されていない期間、前記制御部への前記直流電力の供給を遮断する前記スイッチ制御信号を生成しないOR回路を備え。30

前記OR回路から出力される信号を、前記スイッチ制御信号として出力する請求項4に記載の情報機器。

#### 【請求項6】

前記制御部は、エラーを検出するエラー検出部を備え、

前記エラー検出部は、前記エラーを検出したときに、前記ラッチ開始信号を前記スイッチ制御信号生成回路に出力する請求項1ないし5のいずれか1項に記載の情報機器。

#### 【請求項7】

前記情報機器は、プリンターである請求項1ないし6のいずれか1項に記載の情報機器40。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、情報機器に関するものである。

##### 【背景技術】

##### 【0002】

プリンター等のいわゆる小型情報機器には、外部に接続された電源装置から供給される直流電力によって動作するタイプのものがある。そして、近年では、消費電力を抑制するために、情報機器に対して、電源スイッチがオン状態であっても、情報機器が長時間使用50

されずに、主機能を提供しない場合には、C P Uを含む内部回路、すなわち、電力の消費量が比較的多い部位への直流電力の供給を遮断することが求められている。さらに、エネルギー使用製品に対して環境配慮設計を義務付けるE u P指令(Directive on Eco-Design of Energy Using Products)では、オフモード、すなわち、機器が商用電源につながっているものの、どのような機能も提供していない動作状態における消費電力を0.5(W)以下に抑制することが要求されている。

#### 【0003】

オフモードを備える情報機器には、内部回路への直流電力の供給を遮断するための電力供給遮断回路として、内部回路への直流電力の供給を遮断するためのスイッチ回路や、このスイッチ回路を開状態に保持するためのラッチ回路が備えられる。また、この情報機器には、電源電圧を安定化させるための平滑コンデンサや、この平滑コンデンサの残留電荷を必要に応じて放電させるための、放電抵抗を含む放電回路も備えられる。なお、平滑コンデンサとしては、比較的大容量のコンデンサが用いられる。10

#### 【0004】

このような情報機器では、内部回路へ直流電力の供給を遮断するときに、例えば、C P Uからラッチ回路にラッチ開始信号が入力され、ラッチ回路は、ラッチ開始信号をラッチする。そして、ラッチ回路は、ラッチ開始信号をラッチしている期間、スイッチ回路を開状態に保持すべきスイッチ制御信号をスイッチ回路に出力する。スイッチ回路は、このスイッチ制御信号が入力されている期間、すなわち、ラッチ回路がラッチ開始信号をラッチしている期間、開状態を保持し、内部回路への直流電力の供給を遮断する。なお、この状態から内部回路への直流電力の供給を再開させるためには、一旦、情報機器の電源スイッチをオフ状態に切り換えた後に、オン状態に戻すことが必要となる。これは、以下の通りである。20

#### 【0005】

すなわち、スイッチ回路が開状態であって、内部回路への直流電力の供給が遮断されているときに、情報機器の電源スイッチがオフ状態に切り換えられると、放電回路が動作することによって、平滑コンデンサの残留電荷が放電する。その後、この残留電荷の放電によって、平滑コンデンサの両端子間の電圧がラッチ回路の動作電圧未満に低下すると、ラッチ回路におけるラッチ開始信号のラッチが解除される(ラッチ解除)。このラッチ解除によって、スイッチ回路が閉状態になり、再度、電源スイッチがオン状態に切り換えられたときに、C P Uを含む内部回路に直流電力が供給される。30

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開2006-166561号公報

【特許文献2】特開2005-312162号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

ところで、情報機器のユーザは、上述したように、内部回路への直流電力の供給を再開させるために、電源スイッチをオフ状態に切り換えた直後にオン状態に戻す操作を行う場合がある。この場合、平滑コンデンサの残留電荷が十分に放電されずに、ラッチ回路のラッチ解除がなされない場合がある。この場合、電源スイッチがオン状態に切り換えられても、スイッチ回路は開状態のままであるので、内部回路への直流電力の供給を行うことができず、内部回路は動作することができない。このような不具合を解消するためには、放電回路に備えられる放電抵抗として、抵抗値ができるだけ小さく、許容損失ができるだけ大きい抵抗器を用いることによって、ラッチ解除に要する時間(ラッチ解除時間)を短縮することが考えられる。40

#### 【0008】

しかし、上述した特性を有する抵抗器は、一般に外形寸法が比較的大きいため、このよ50

うな抵抗器を放電抵抗として用いることは、情報機器の大型化を招く。このため、上述した特性を有する抵抗器は、情報機器への搭載には適さない。

#### 【0009】

本発明は、上述の課題を解決するためになされたものであり、CPUを含む内部回路への直流電力の供給が遮断されているときに、ラッチ回路のラッチ解除によって、直流電力の内部回路への供給が再開される情報機器において、情報機器の小型化と、ラッチ解除時間の短縮とを両立することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は適用例として実現することが可能である。 10

##### 【形態1】

電源装置から直流電力が供給される第1の動作モードと、前記電源装置からの前記直流電力の供給が遮断される第2の動作モードとを有する情報機器であって、

前記直流電力によって動作し、ラッチ開始信号を出力する制御部と、

前記電源装置に接続される入力端子、出力端子、及び前記入力端子と前記出力端子との接続状態がオン状態となる第1の姿勢と前記接続状態がオフ状態となる第2の姿勢とに切り換える操作部とを有する電源スイッチと、

前記電源スイッチの前記出力端子に接続される第1の端子及び接地される第2の端子を有する平滑コンデンサと、 20

前記電源スイッチの前記出力端子と前記制御部との間に接続され、前記制御部への前記直流電力の供給と遮断とを切り換えるスイッチ回路と、

前記制御部から入力された前記ラッチ開始信号をラッチするラッチ回路を有し、前記ラッチ回路における前記ラッチ開始信号のラッチ状態に基づいて前記制御部への前記直流電力の供給を遮断するスイッチ制御信号を生成し、前記スイッチ回路に前記スイッチ制御信号を出力するスイッチ制御信号生成回路と、

前記電源スイッチにおける前記接続状態を検出し、前記接続状態がオフ状態である場合に、前記ラッチ回路における前記ラッチ開始信号のラッチを解除するラッチ解除信号を前記スイッチ制御信号生成回路に出力するラッチ解除信号生成部と、を備え、

前記ラッチ回路および前記ラッチ解除信号生成部は、前記電源スイッチの前記出力端子または前記平滑コンデンサから供給される前記直流電力によって動作可能に構成され、 30

前記制御部は、前記第1の動作モードから前記第2の動作モードに移行するときに、前記ラッチ開始信号を前記スイッチ制御信号生成回路に出力し、

前記ラッチ回路は、前記ラッチ回路に前記ラッチ解除信号が入力されたときに、前記ラッチ開始信号のラッチを解除し、

前記スイッチ回路は、前記スイッチ制御信号が入力されているときに開状態になり、前記スイッチ制御信号が入力されていないときに閉状態になることを特徴とする情報機器。

#### 【0011】

##### 【適用例1】

電源装置から直流電力が供給される第1の動作モードと、前記電源装置からの前記直流電力の供給が遮断される第2の動作モードとを有する情報機器であって、 40

前記直流電力によって動作し、ラッチ開始信号を出力する制御部と、

前記電源装置に接続される入力端子、出力端子、及び前記入力端子と前記出力端子との接続状態がオン状態となる第1の姿勢と前記接続状態がオフ状態となる第2の姿勢とに切り換える操作部とを有する電源スイッチと、

前記電源スイッチの前記出力端子に接続される第1の端子及び接地される第2の端子を有する平滑コンデンサと、

前記電源スイッチの前記出力端子に接続され、前記制御部への前記直流電力の供給と遮断とを切り換えるスイッチ回路と、

前記制御部から入力された前記ラッチ開始信号をラッチするラッチ回路を有し、前記ラ 50

ラッチ回路における前記ラッチ開始信号のラッチ状態に基づいて前記制御部への前記直流電力の供給を遮断するスイッチ制御信号を生成し、前記スイッチ回路に前記スイッチ制御信号を出力するスイッチ制御信号生成回路と、

前記電源スイッチにおける前記接続状態を検出し、前記接続状態がオフ状態である場合に、前記ラッチ回路における前記ラッチ開始信号のラッチを解除するラッチ解除信号を前記スイッチ制御信号生成回路に出力するラッチ解除信号生成部と、を備え、

前記ラッチ回路および前記ラッチ解除信号生成部は、前記電源スイッチの前記出力端子または前記平滑コンデンサから供給される前記直流電力によって動作可能に構成され、

前記制御部は、前記第1の動作モードから前記第2の動作モードに移行するときに、前記ラッチ開始信号を前記スイッチ制御信号生成回路に出力し、

前記ラッチ回路は、前記ラッチ回路に前記ラッチ解除信号が入力されたときに、前記ラッチ開始信号のラッチを解除し、

前記スイッチ回路は、前記スイッチ制御信号が入力されているときに開状態になり、前記スイッチ制御信号が入力されていないときに閉状態になることを特徴とする情報機器。

#### 【0012】

ここで、電源スイッチの入力端子と電源装置、電源スイッチの出力端子と平滑コンデンサの第1の端子、電源スイッチの出力端子とスイッチ回路は、必ずしも直接接続されている必要はなく、それぞれの間に、抵抗器等、他の回路素子が接続されていてもよい。

#### 【0013】

適用例1の情報機器では、動作モードが第2の動作モードであって、スイッチ回路が開状態である場合に、電源スイッチの操作部の姿勢が第1の姿勢から第2の姿勢に切り換えると、入力端子と出力端子との接続状態がオフ状態にされると、ラッチ解除信号生成部が、電源スイッチがオフ状態に切り換えられたことを検出して、ラッチ解除信号を、ラッチ回路を有するスイッチ制御信号生成回路に出力する。そして、ラッチ回路は、ラッチ解除信号が入力されたときにラッチ解除を行う。このため、ラッチ回路は、平滑コンデンサの残留電荷が十分に放電されておらず、平滑コンデンサの両端子間の電圧がラッチ回路の動作電圧未満に低下していなくても、ラッチ解除を行うことができる。したがって、本適用例の情報機器では、ラッチ解除時間を短縮するために、先に説明した、抵抗値が小さく、許容損失が大きい抵抗器を放電抵抗として用いる必要がない。つまり、本適用例によって、情報機器の小型化と、ラッチ解除時間の短縮とを両立することができる。

#### 【0014】

なお、本明細書において、「電源スイッチの入力端子と出力端子との接続状態がオン状態である」（単に「電源スイッチがオン状態である」とも言う）とは、少なくとも、電源スイッチの操作部の姿勢が第1の姿勢であることを意味している。また、「電源スイッチの入力端子と出力端子との接続状態がオフ状態である」（単に「電源スイッチがオフ状態である」とも言う）とは、少なくとも、電源スイッチの操作部の姿勢が第2の姿勢であることを意味している。

#### 【0015】

##### [適用例2]

前記ラッチ解除信号生成部は、前記電源スイッチの前記入力端子と前記出力端子と間の電位差を検出し、前記電位差が所定値以上である場合に、前記接続状態がオフ状態であるものとして、前記ラッチ解除信号を前記スイッチ制御信号生成回路に出力する電位差検出回路を備える適用例1に記載の情報機器。

#### 【0016】

動作モードが第2の動作モードであって、スイッチ回路が開状態である場合に、電源スイッチの操作部の姿勢が第1の姿勢から第2の姿勢に切り換えて、入力端子と出力端子との接続状態がオフ状態になると、平滑コンデンサに直接的、あるいは、間接的に接続された回路素子の消費電流によって平滑コンデンサの残留電荷が放電されたため、平滑コンデンサの両端子間の電圧が低下し、電源スイッチの入力端子と出力端子との間には、電位差が生じる。適用例2の情報機器では、電位差検出回路が、電源スイッチの入力端子と出

10

20

30

40

50

力端子との間の電位差を検出し、この電位差が所定値以上になった場合に、電源スイッチがオフ状態に切り換えられたものとして、ラッチ解除信号を、ラッチ回路を有するスイッチ制御信号生成回路に出力することができる。

#### 【0017】

##### [適用例3]

前記平滑コンデンサの前記第1の端子と前記ラッチ回路との間に、前記平滑コンデンサの残留電荷を放電させる抵抗器を備え、

前記抵抗器の抵抗値は、前記残留電荷の放電時における消費電力および放電時間に基いて設定される適用例2に記載の情報機器。

#### 【0018】

上記抵抗器の抵抗値を比較的高い値とした場合には、動作モードが第2の動作モードである場合においても、上記抵抗器による消費電流が比較的小さくなる。その反面、電源スイッチがオフ状態に切り換えられたときの平滑コンデンサの両端子間の電圧の低下が比較的遅くなるため、電源スイッチの入力端子と出力端子との間に上記所定値以上の電位差が生じ、電位差検出回路がラッチ解除信号を出力するまでに比較的長い時間がかかる。一方、上記抵抗器の抵抗値を比較的低い値とした場合には、動作モードが第2の動作モードである場合においてのみ上記抵抗器に電流を流すようにし、電源スイッチがオフ状態に切り換えられたときの平滑コンデンサの残留電荷の放電時間を比較的短くすることができる。第1の動作モードには影響しない。その反面、動作モードが第2の動作モードである場合における上記抵抗器による消費電流が増大する。

10

#### 【0019】

適用例3の情報機器では、平滑コンデンサの残留電荷の放電時における消費電力および放電時間を考慮して上記抵抗器の抵抗値を設定することによって、動作モードが第2のモードである場合におけるラッチ回路の保持電流、すなわち、上記抵抗器を流れる電流を適切に設定するとともに、電源スイッチがオフ状態に切り換えられたときに、電位差検出時間、すなわち、電源スイッチの入力端子と出力端子との間に上記所定値以上の電位差が生じるまでの時間を適切に設定することができる。

20

#### 【0020】

上記抵抗器の抵抗値は、例えば、動作モードが第2の動作モードであって、ラッチ回路の保持電流が、第2の動作モードにおいて許容される電流値の上限値となるように設定することにより、電源スイッチがオフ状態に切り換えられたときに、電源スイッチの入力端子と出力端子との間の電位差が所定値以上となるまでの時間を短縮することができる。なお、第2の動作モードにおいて許容される電流値は、低消費電力の観点からは低いほど望ましいが、製品機能の観点では、電位差検出時間を短くしたい場合がある。また、上記上限値は、ある種の法令や規制、製品仕様によって規定される。

30

#### 【0021】

##### [適用例4]

前記制御部は、前記第1の動作モードである期間、前記スイッチ制御信号生成回路にラッチ解除禁止信号を出力し、前記第1の動作モードから前記第2の動作モードに移行するときに、前記ラッチ解除禁止信号の出力を停止し、

40

前記スイッチ制御信号生成回路は、前記ラッチ解除禁止信号が入力されている期間、前記ラッチ回路への前記ラッチ解除信号の入力を禁止するラッチ解除禁止回路を備える適用例2または3記載の情報機器。

#### 【0022】

動作モードが第1の動作モードである場合、電源スイッチの入力端子と出力端子との間の電位差は、電源スイッチがオン状態であっても、例えば、電源スイッチにおける接点部材の硫化やシロキサン付着等の接点の劣化により、接点抵抗が増大することに起因して、所定値以上になる場合がある。そして、このような場合にも、電位差検出回路は、電源スイッチがオフ状態の場合と同様に、ラッチ解除信号を出力する。このため、スイッチ制御信号生成回路が、所望しないラッチ解除信号の入力によって誤動作することがあり得る。

50

適用例 4 の情報機器では、スイッチ制御信号生成回路がラッチ解除禁止回路を備えることによって、所望しないラッチ解除信号の入力による誤動作を防止することができる。

#### 【0023】

##### [適用例 5]

前記スイッチ制御信号生成回路は、前記ラッチ回路から前記ラッチ開始信号をラッチしていることを示す状態信号が入力されている期間および前記ラッチ解除禁止回路から前記ラッチ解除信号が入力されている期間、前記制御部への前記直流電力の供給を遮断する前記スイッチ制御信号を生成し、

前記ラッチ開始信号をラッチしていることを示す状態信号および前記ラッチ解除信号が入力されていない期間、前記制御部への前記直流電力の供給を遮断する前記スイッチ制御信号を生成しないOR回路を備え、

前記OR回路から出力される信号を、前記スイッチ制御信号として出力する適用例 4に記載の情報機器。

#### 【0024】

先に説明した適用例 4 の情報機器では、動作モードが第 2 の動作モードである場合に、電源スイッチがオフ状態に切り換えられたときに、ラッチ解除信号によってラッチ回路がラッチ解除されるため、スイッチ回路は閉状態になる。このため、電源スイッチがオフ状態であっても、平滑コンデンサから制御部に電流が流れ、制御部が誤動作するおそれがある。これに対し、適用例 5 の情報機器では、スイッチ制御信号生成回路が上記OR回路を備えるので、動作モードが第 2 の動作モードである場合に、電源スイッチがオフ状態に切り換えられたときに、スイッチ制御信号生成回路において、制御部への直流電力の供給を遮断すべきスイッチ制御信号が生成され、スイッチ回路を開状態に保持することができる。したがって、上述した制御部の誤動作を防止することができる。

#### 【0025】

##### [適用例 6]

前記制御部は、エラーを検出するエラー検出部を備え、

前記エラー検出部は、前記エラーを検出したときに、前記ラッチ開始信号を前記スイッチ制御信号生成回路に出力する適用例 1ないし5のいずれか 1 例に記載の情報機器。

#### 【0026】

適用例 6 の情報機器では、エラー検出部によって所定のエラーが検出されたときに、スイッチ制御信号生成回路は、ラッチ回路がラッチ開始信号をラッチすることによって、制御部への直流電力の供給を遮断すべきスイッチ制御信号を生成する。したがって、エラー検出部によって所定のエラーが検出されたときに、スイッチ回路を開状態とし、制御部への直流電力の供給を遮断することができる。この結果、制御部において故障が発生している場合に、この故障の拡大を防止することができる。なお、エラー検出部が検出する所定のエラーとしては、例えば、過電圧エラーや、低電圧エラー、短絡エラー等、電源再投入によって復帰する可能性があるエラーが挙げられる。

#### 【0027】

##### [適用例 7]

前記情報機器は、プリンターである適用例 1ないし6のいずれか 1 項に記載の情報機器。

#### 【0028】

プリンターは、比較的小型な情報機器であるので、本適用例は好適である。

#### 【0029】

本発明は、上述の情報機器としての構成の他、情報機器の制御方法の発明として構成することもできる。

#### 【図面の簡単な説明】

#### 【0030】

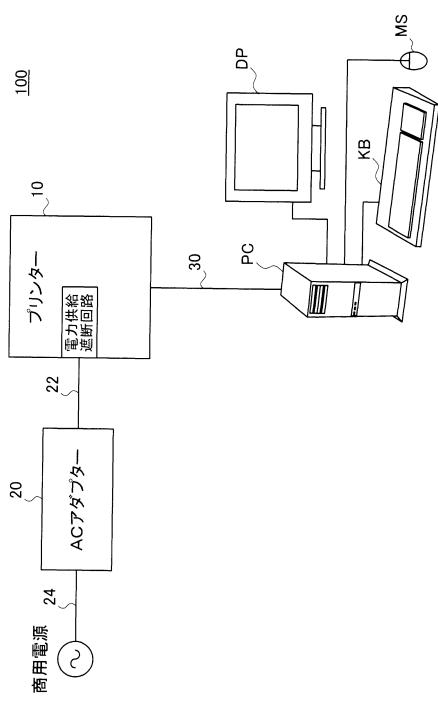

【図 1】本発明の第 1 実施例としての情報機器を含むコンピュータシステム 100 の概略構成を示す説明図である。

10

20

30

40

50

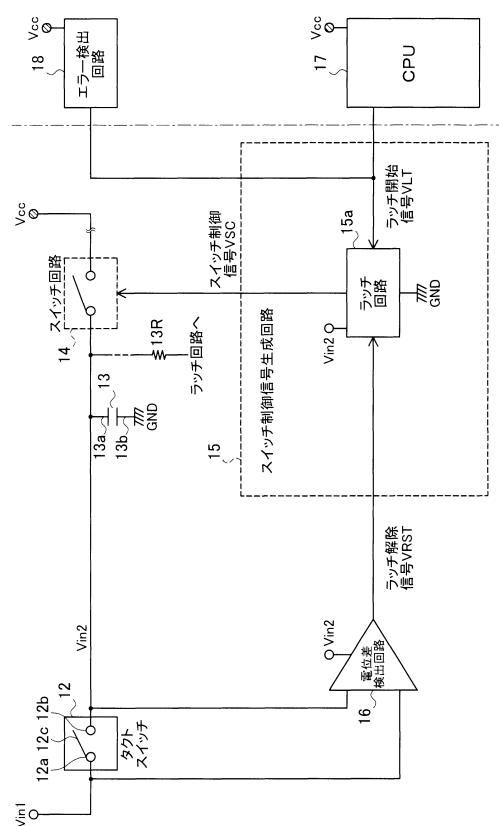

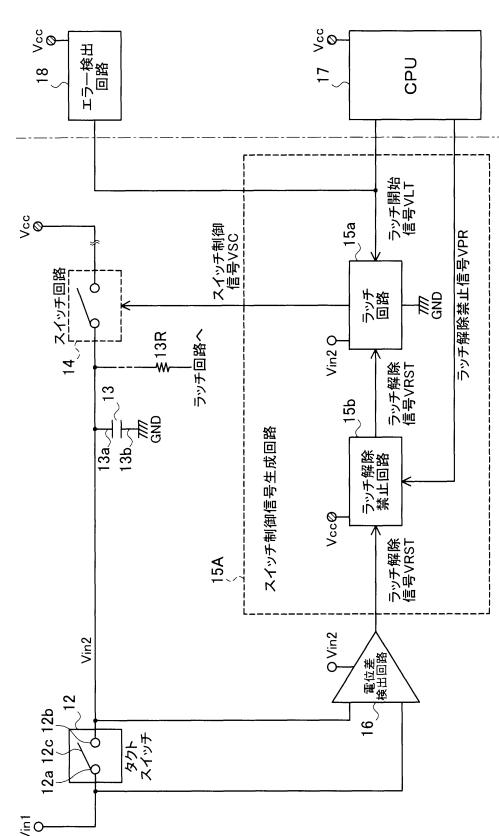

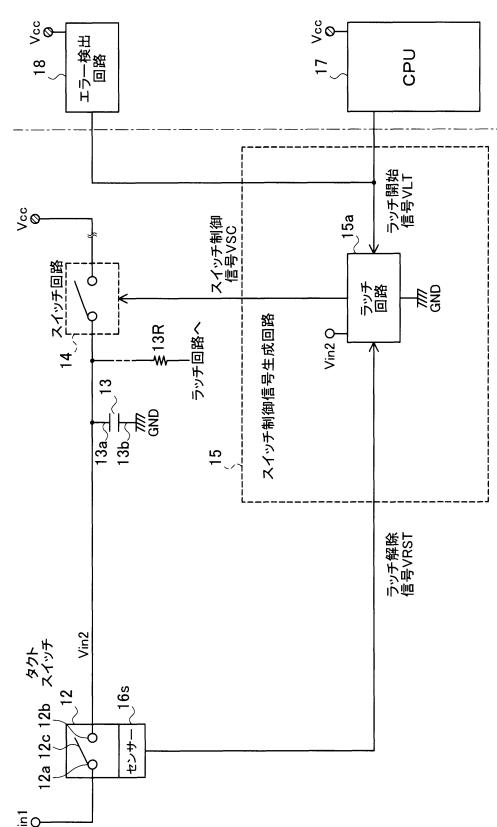

【図2】第1実施例のプリンター10が備える電力供給遮断回路の概略構成を示す説明図である。

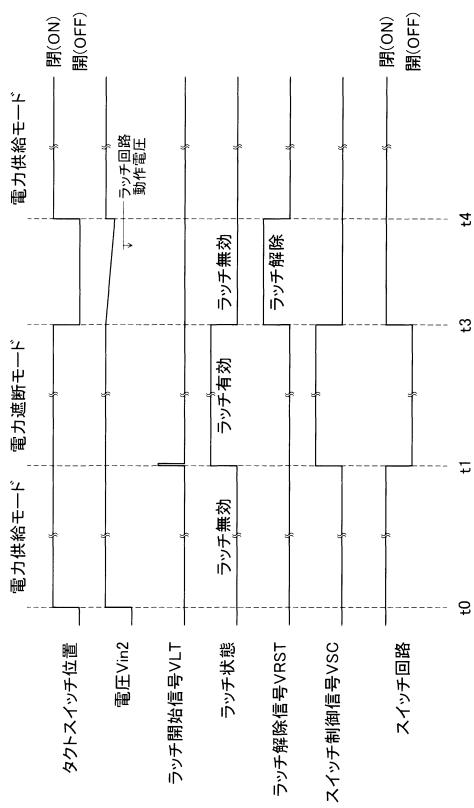

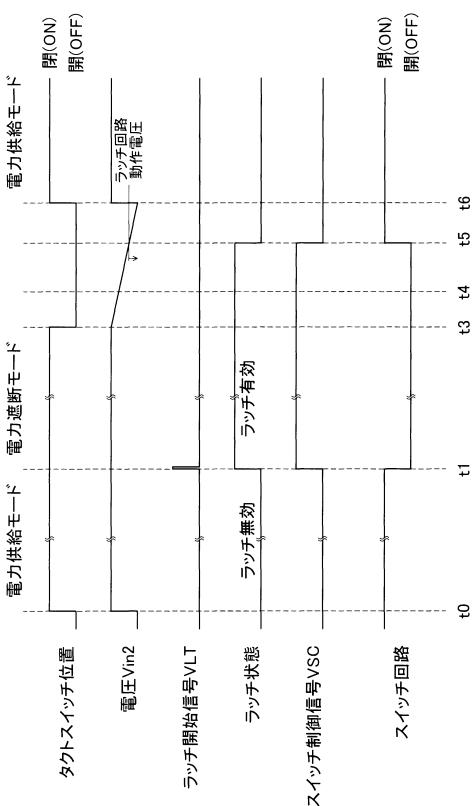

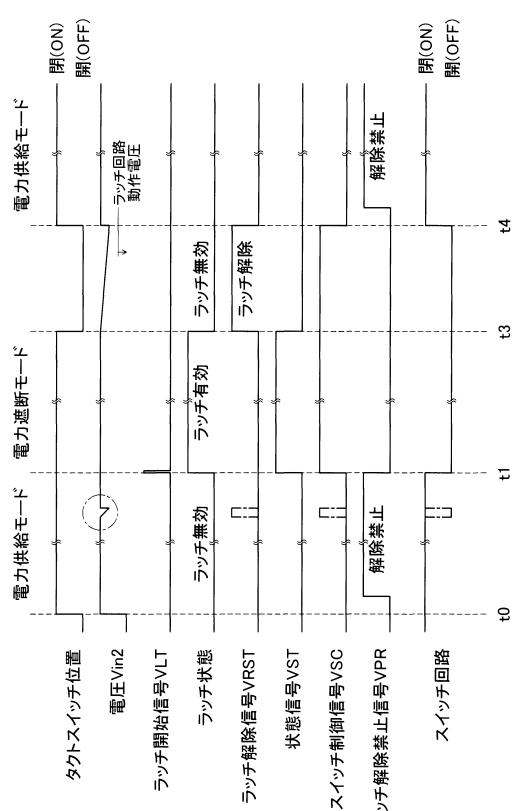

【図3】第1実施例のプリンター10における電力供給遮断回路の動作を示すタイミングチャートである。

【図4】従来のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。

【図5】従来のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。

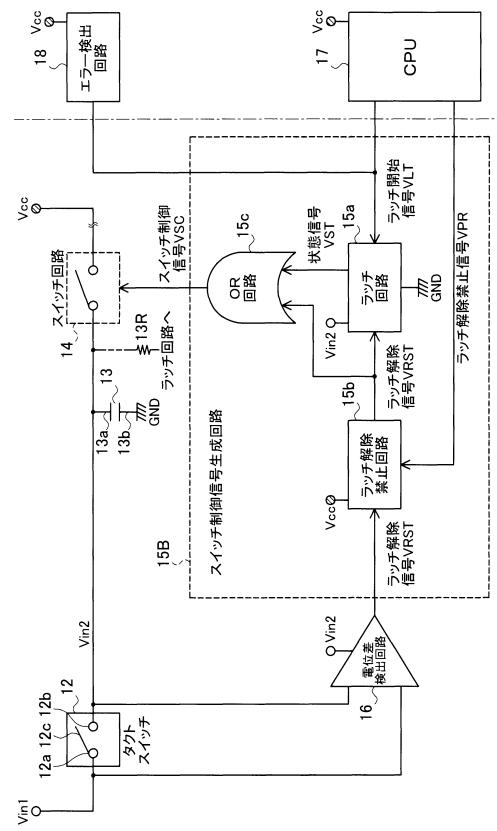

【図6】第2実施例のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。

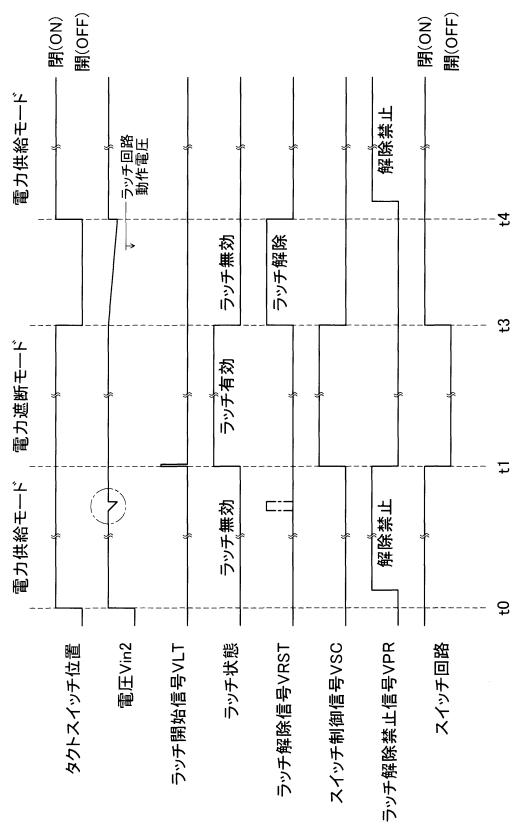

【図7】第2実施例のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。10

【図8】第3実施例のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。

【図9】第3実施例のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。

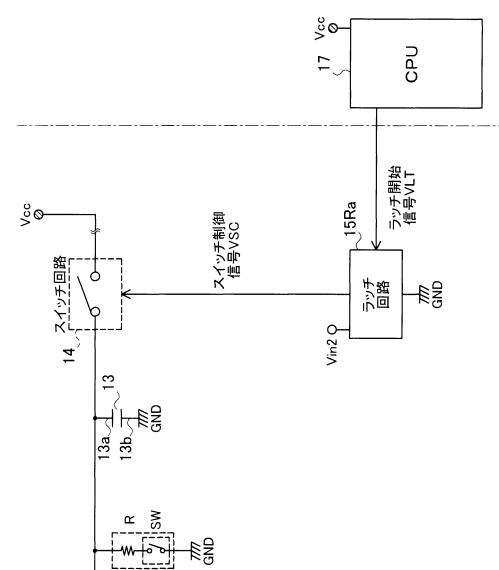

【図10】変形例のプリンターにおける電力供給遮断回路の概略構成を示す説明図である。20

#### 【発明を実施するための形態】

##### 【0031】

以下、本発明の実施の形態について、実施例に基づき説明する。

##### A. 第1実施例：

###### A1. システム構成：

図1は、本発明の第1実施例としての情報機器を含むコンピュータシステム100の概略構成を示す説明図である。このコンピュータシステム100は、パーソナルコンピュータPCと、本発明の情報機器としてのプリンター10とを備えている。

##### 【0032】

プリンター10には、電源ケーブル22を介して、ACアダプター20が接続されている。ACアダプター20は、電源ケーブル24を介して、商用電源に接続されている。ACアダプター20は、商用電源から供給される交流電力を直流電力に変換して、この直流電力をプリンター10に供給する。ACアダプター20は、[課題を解決するための手段]における電源装置に相当する。30

##### 【0033】

プリンター10には、また、プリンターケーブル30を介して、パーソナルコンピュータPCが接続されている。パーソナルコンピュータPCには、キーボードKBや、マウスマウスMSや、ディスプレイDPが接続されている。プリンター10は、パーソナルコンピュータPCから印刷ジョブが投入されたときに印刷を実行する。

##### 【0034】

本実施例のプリンター10は、消費電力を抑制するために、動作モードとして、CPUを含む内部回路にACアダプター20から供給された直流電力を供給する通常の動作モードである電力供給モードと、内部回路への直流電力の供給が遮断される電力遮断モード(オフモード)とを有している。そして、長時間、パーソナルコンピュータPCからプリンター10に印刷ジョブが投入されない場合に、動作モードが電力供給モードから電力遮断モードに切り換わる。動作モードが電力供給モードから電力遮断モードに切り換わるまでの時間は、プリンター10のユーザによって任意に設定可能である。動作モードが電力供給モードから電力遮断モードに切り換わるとときの内部回路への直流電力の供給の遮断は、電力供給遮断回路によって行われる。この電力供給遮断回路については、後から詳述する。なお、電力供給モードには、印刷実行時の比較的消費電力が高い動作モードである通常モードと、印刷実行から所定時間が経過した後に印刷ジョブの投入を待機しているときの比較的消費電力が低い動作モードである省電力モードとが含まれる。

##### 【0035】

50

20

30

40

50

## A 2 . 電力供給遮断回路の構成 :

図 2 は、第 1 実施例のプリンター 10 が備える電力供給遮断回路の概略構成を示す説明図である。図示するように、電力供給遮断回路は、タクトスイッチ 12 と、平滑コンデンサ 13 と、抵抗器 13R と、スイッチ回路 14 と、スイッチ制御信号生成回路 15 と、電位差検出回路 16 と、を備える。スイッチ制御信号生成回路 15 は、ラッチ回路 15a を備えている。ラッチ回路 15a は、接地されている。

### 【 0 0 3 6 】

タクトスイッチ 12 は、入力端子 12a と、出力端子 12b と、操作部 12c と、を備えている。タクトスイッチ 12 は、操作部 12c の姿勢を、入力端子 12a と出力端子 12b との接続状態（以下、単に接続状態とも言う）がオン状態となる第 1 の姿勢と、接続状態がオフ状態となる第 2 の姿勢との間で切り換える切換操作によって、接続状態を切り換えるための電源スイッチである。タクトスイッチ 12 は、切換操作が行われない限り、操作部 12c の姿勢、および、接続状態を保持する。入力端子 12a は、A C アダプター 20 に接続されている。

### 【 0 0 3 7 】

平滑コンデンサ 13 は、第 1 の端子 13a と、第 2 の端子 13b と、を有している。第 1 の端子 13a は、タクトスイッチ 12 の出力端子 12b に接続されており、第 2 の端子 13b は、接地されている。平滑コンデンサ 13 は、電圧 V<sub>in</sub> 2 を安定化させるためのコンデンサである。この平滑コンデンサ 13 としては、比較的大容量のコンデンサが用いられる。

### 【 0 0 3 8 】

抵抗器 13R は、平滑コンデンサ 13 の第 1 の端子 13a と、ラッチ回路 15a との間に接続されている。この抵抗器 13R は、タクトスイッチ 12 がオフ状態に切り換えられたときに、平滑コンデンサ 13 の残留電荷を、ラッチ回路 15a を介して放電させるために用いられる。そして、この抵抗器 13R の抵抗値は、平滑コンデンサ 13 の残留電荷の放電時における消費電力および放電時間を考慮して設定されている。本実施例では、抵抗器 13R の抵抗値は、上記放電時の消費電力が 0.5 (W) 以下 (EUP 指令の上限値) となる範囲内で、放電時間が最短になるように設定されている。

### 【 0 0 3 9 】

スイッチ回路 14 は、タクトスイッチ 12 の出力端子 12b に接続されている。スイッチ回路 14 は、スイッチ制御信号生成回路 15 から入力されたスイッチ制御信号 VSC に基づいて、CPU 17、および、エラー検出回路 18 を含む内部回路への直流電力の供給と遮断とを切り換える。スイッチ回路 14 は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号 VSC が入力されているときに、開状態になる。また、スイッチ回路 14 は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号 VSC が入力されていないときに、閉状態になる。スイッチ回路 14 を通過した直流電力は、図示しない DC / DC コンバータによって電圧変換され（電圧 Vcc）、CPU 17 や、エラー検出回路 18 に供給される。スイッチ回路 14 は、FET ( ; Field Effect transistor ) 等を含んでいる。

### 【 0 0 4 0 】

スイッチ制御信号生成回路 15 は、CPU 17、または、エラー検出回路 18 から入力されたラッチ開始信号 VLT と、電位差検出回路 16 から入力されたラッチ解除信号 VRS トとに基づいて、スイッチ制御信号 VSC を生成し、このスイッチ制御信号 VSC をスイッチ回路 14 に出力する。本実施例では、スイッチ制御信号生成回路 15 は、ラッチ回路 15a にラッチ開始信号 VLT が入力されて、ラッチ回路 15a にラッチ開始信号 VLT がラッチされている期間、内部回路への直流電力の供給を遮断すべきスイッチ制御信号 VSC を生成する。ラッチ回路 15a は、ラッチ解除信号 VRS トが入力されたときに、ラッチ解除する。そして、スイッチ制御信号生成回路 15 は、ラッチ回路 15a にラッチ開始信号 VLT がラッチされていない期間は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号 VSC を生成しない。なお、ラッチ回路 15a は、A C アダプター 20

10

20

30

40

50

から入力された、タクトスイッチ 12 の後段の電圧  $V_{in2}$  によって動作する。

#### 【0041】

電位差検出回路 16 は、タクトスイッチ 12 の入力端子 12a と出力端子 12b との間の電位差 ( $V_{in1} - V_{in2}$ ) を検出し、両端子間の電位差が所定値以上（例えば、1 (V) 以上）である場合に、ラッチ解除信号  $V_{RST}$  をスイッチ制御信号生成回路 15 に出力する。つまり、電位差検出回路 16 は、例えば、タクトスイッチ 12 の入力端子 12a と出力端子 12b との間の電位差が所定値以上となる、タクトスイッチ 12 がオフ状態の場合に、ラッチ解除信号  $V_{RST}$  を出力する。

#### 【0042】

CPU17 は、動作モードが電力供給モードから電力遮断モードに移行するときに、ラッチ開始信号  $V_{LT}$  を電位差検出回路 16 に出力する。エラー検出回路 18 は、プリンター 10 の動作モードが電力供給モードである場合に、プリンター 10 の内部における所定のエラーを検出し、このエラーを検出したときに、スイッチ制御信号生成回路 15 にラッチ開始信号  $V_{LT}$  を出力する。エラー検出回路 18 が検出するエラーとしては、例えば、過電圧エラーや、低電圧エラーや、短絡エラー等が挙げられる。CPU17、および、エラー検出回路 18 は、[課題を解決するための手段] における制御部に相当する。

#### 【0043】

A3. 電力供給遮断回路の動作 :

図 3 は、第 1 実施例のプリンター 10 における電力供給遮断回路の動作を示すタイミングチャートである。

#### 【0044】

タクトスイッチ 12 がオフ状態である時刻  $t_0$  において、タクトスイッチ 12 の操作部 12c の姿勢が第 2 の姿勢から第 1 の姿勢に切り換えられ、タクトスイッチ 12 がオン状態になると、電圧  $V_{in2}$  が立ち上がり、プリンター 10 の動作モードは、電力供給モードになる。

#### 【0045】

その後、CPU17 は、タイマーを参照して、パーソナルコンピュータ PC から印刷ジョブが投入されないまま所定時間が経過すると、時刻  $t_1$  において、プリンター 10 の動作モードを電力供給モードから電力遮断モードに移行するために、ラッチ開始信号  $V_{LT}$  を出力する。このラッチ開始信号  $V_{LT}$  をラッチ回路 15a がラッチすると（ラッチ状態：ラッチ有効）、スイッチ制御信号生成回路 15 は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号  $V_{SC}$  をスイッチ回路 14 に出力する。このスイッチ制御信号  $V_{SC}$  がスイッチ回路 14 に入力されると、スイッチ回路 14 は、閉状態になる。スイッチ回路 14 が閉状態になり、内部回路への直流電力の供給が遮断された後は、タクトスイッチ 12 がオフ状態に切り換えられ、再度、オン状態に切り換えられるまで、プリンター 10 の動作モードは、電力遮断モードのままである。

#### 【0046】

プリンター 10 の動作モードを電力遮断モードから電力供給モードに復帰させるために、時刻  $t_3$  において、タクトスイッチ 12 の操作部 12c の姿勢が第 1 の姿勢から第 2 の姿勢に切り換えられ、タクトスイッチ 12 がオフ状態になると、平滑コンデンサ 13 の残留電荷が、抵抗器 13R やラッチ回路 15a 等を介して放電されるため、平滑コンデンサ 13 の両端子間の電圧（電圧  $V_{in2}$ ）が低下する。このため、タクトスイッチ 12 の入力端子 12a と出力端子 12b との間には、電位差が生じる。電位差検出回路 16 は、タクトスイッチ 12 の入力端子 12a と出力端子 12b との間の電位差が所定値以上になったことを検出して、ラッチ解除信号  $V_{RST}$  をスイッチ制御信号生成回路 15 に出力する。このラッチ解除信号  $V_{RST}$  がラッチ回路 15a に入力されて、ラッチ解除されると（ラッチ状態：無効）、スイッチ制御信号生成回路 15 は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号  $V_{SC}$  の出力を停止する。スイッチ回路 14 は、内部回路への直流電力の供給を遮断すべきスイッチ制御信号  $V_{SC}$  の入力が停止されると、閉状態になる。

10

20

30

40

50

**【0047】**

そして、時刻  $t_4$ において、タクトスイッチ 12 の操作部 12c の姿勢が第 2 の姿勢から第 1 の姿勢に切り換えられ、タクトスイッチ 12 がオン状態になると、プリンター 10 の動作モードは、電力供給モードに復帰する。なお、本実施例において、上述した時刻  $t_3$  から時刻  $t_4$ までの時間間隔は、例えば、0.5 秒程度であり、タクトスイッチ 12 における操作部 12c の切り換え時間としては、比較的短い時間である。したがって、時刻  $t_3$  から時刻  $t_4$ までの期間において、平滑コンデンサ 13 の残留電荷は、抵抗器 13R やラッチ回路 15a 等を介して放電されるが、時刻  $t_4$ において、電圧  $V_{in2}$  は、ラッチ回路 15a の動作電圧未満には低下しない。

**【0048】**

なお、先に説明したように、プリンター 10 の動作モードが電力供給モードである場合、エラー検出回路 18 は、プリンター 10 の内部における所定のエラーを検出し、このエラーを検出したときに、スイッチ制御信号生成回路 15 にラッチ開始信号  $V_{LT}$  を出力する。この場合には、図示は省略しているが、電力供給遮断回路は、時刻  $t_1$ において、CPU 17 からラッチ開始信号  $V_{LT}$  が出力されたときと同様に動作し、プリンター 10 の動作モードが電力供給モードから電力遮断モードに切り換わる。

**【0049】****A 4 . 効果 :**

ここで、第 1 実施例のプリンター 10 が上述した構成を有する電力供給遮断回路を備えることによる効果を示すため、動作モードとして、電力供給モードと、電力遮断モードとを有する従来のプリンターにおける電力供給遮断回路について説明する。

**【0050】**

図 4 は、従来のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。図 4 と図 2 との比較から分かるように、この電力供給遮断回路は、放電抵抗 R とスイッチ回路 SW とを有する放電回路を備えること、電位差検出回路 16 を備えないこと、および、エラー検出回路 18 を備えていないことが、第 1 実施例のプリンター 10 が備える電力供給遮断回路と異なっている。なお、放電回路は、タクトスイッチ 12 がオン状態からオフ状態に切り換えられたときに動作して、平滑コンデンサ 13 の残留電荷を放電するための回路である。

**【0051】**

図 5 は、従来のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。時刻  $t_0$  から時刻  $t_3$  までの動作は、第 1 実施例のプリンター 10 における電力供給遮断回路の動作と同じである（図 3 参照）。

**【0052】**

従来のプリンターにおける電力供給遮断回路では、時刻  $t_3$ において、タクトスイッチ 12 がオフ状態になると、放電回路が動作して、平滑コンデンサ 13 の残留電荷が放電される。その後、時刻  $t_5$ において、平滑コンデンサ 13 の両端子間の電圧（電圧  $V_{in2}$ ）がラッチ回路 15Ra の動作電圧未満に低下すると、ラッチ回路 15Ra のラッチ解除がなされる（ラッチ状態：無効）。このラッチ解除によって、スイッチ回路 14 が閉状態になる。そして、時刻  $t_6$ において、再度、タクトスイッチ 12 がオン状態に切り換えられたときに、内部回路に直流電力が供給される。

**【0053】**

つまり、従来のプリンターにおける電力供給遮断回路では、平滑コンデンサ 13 の両端子間の電圧がラッチ回路 15Ra の動作電圧未満になるまで、ラッチ回路 15Ra がラッチ解除されず、スイッチ回路 14 は開状態のままである。したがって、平滑コンデンサ 13 の両端子間の電圧がラッチ回路 15Ra の動作電圧未満に低下する前の時刻  $t_4$ において、タクトスイッチ 12 がオン状態に切り換えられても、スイッチ回路 14 は開状態のままであり、内部回路に直流電力の供給を行うことができない。

**【0054】**

このような不具合を解消するためには、放電回路が備える放電抵抗 R として、抵抗値が

10

20

30

40

50

できるだけ小さく、許容損失ができるだけ大きい抵抗器を用いることによって、ラッチ回路 15 R a のラッチ解除時間を短縮することが考えられる。しかし、このような特性を有する抵抗器は、一般に外形寸法が比較的大きいため、このような抵抗器を放電抵抗 R として用いることは、プリンターの大型化を招く。このため、上述した特性を有する抵抗器は、プリンターへの搭載には適さない。

#### 【0055】

これに対し、第 1 実施例のプリンター 10 では、電力供給遮断回路が、電位差検出回路 16 を備えているので、平滑コンデンサ 13 の残留電荷の放電を行うことなく、電位差検出回路 16 から出力されたラッチ解除信号 V R S T によって、ラッチ回路 15 a のラッチ解除を行うことができる。したがって、第 1 実施例のプリンター 10 では、ラッチ解除時間 10 を短縮するために、先に説明した、抵抗値が小さく、許容損失が大きい抵抗器を放電抵抗 R として用いる必要がない。つまり、第 1 実施例のプリンター 10 によって、プリンタ - 10 の小型化と、ラッチ解除時間の短縮とを両立することができる。

#### 【0056】

また、第 1 実施例のプリンター 10 では、エラー検出回路 18 が、所定のエラーを検出したときに、ラッチ開始信号 V L T を出力して、内部回路への直流電力の供給を遮断することができるので、内部回路において故障が発生している場合に、この故障の拡大を防止することができる。

#### 【0057】

また、第 1 実施例のプリンター 10 では、電力供給遮断回路における抵抗器 13 R の抵抗値が、平滑コンデンサ 13 の残留電荷の放電時における消費電力および放電時間を考慮して設定されているので、動作モードが電力遮断モードである場合におけるラッチ回路 15 a の保持電流、すなわち、抵抗器 13 R を流れる電流を適切に設定するとともに、タクトスイッチ 12 がオフ状態に切り換えられたときに、電位差検出時間、すなわち、タクトスイッチ 12 の入力端子 12 a と出力端子 12 b との間に上記所定値以上の電位差が生じるまでの時間を適切に設定することができる。

#### 【0058】

##### B . 第 2 実施例 :

第 2 実施例のプリンターは、第 1 実施例のプリンター 10 と同様に、動作モードとして、電力供給モードと、電力遮断モードとを有している。ただし、第 2 実施例のプリンターは、電力供給遮断回路の構成が、第 1 実施例のプリンター 10 と異なっている。以下、第 2 実施例のプリンターにおける電力供給遮断回路の構成、および、動作について説明する。

#### 【0059】

##### B 1 . 電力供給遮断回路の構成 :

図 6 は、第 2 実施例のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。図 6 と図 2 との比較から分かるように、第 2 実施例のプリンターでは、電力供給遮断回路は、第 1 実施例におけるスイッチ制御信号生成回路 15 の代わりに、スイッチ制御信号生成回路 15 A を備えている。そして、スイッチ制御信号生成回路 15 A は、ラッチ回路 15 a に加えて、ラッチ解除禁止回路 15 b を備えている。また、C P U 17 は、プリンタ - 10 の動作モードが電力供給モードである期間、ラッチ解除禁止信号 V P R をラッチ解除禁止回路 15 b に出力し、動作モードが電力供給モードから電力遮断モードに移行するときに、ラッチ解除禁止信号 V P R の出力を停止する(図 7 参照)。ラッチ解除禁止回路 15 b は、ラッチ解除禁止信号 V P R が入力されている期間、電位差検出回路 16 から出力されたラッチ解除信号 V R S T のラッチ回路 15 a への出力を禁止する。なお、上述した構成以外は、第 1 実施例と同じである。

#### 【0060】

##### B 2 . 電力供給遮断回路の動作 :

図 7 は、第 2 実施例のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。第 2 実施例における電力供給遮断回路の動作は、第 1 実施例とほぼ同じで

10

20

30

40

50

ある。ただし、第2実施例における電力供給遮断回路では、ラッチ解除禁止回路15bを備えるので、動作モードが電力供給モードである期間、電位差検出回路16から出力されたラッチ解除信号VRSTがラッチ回路15aに入力されることはない。

#### 【0061】

動作モードが電力供給モードである場合、タクトスイッチ12の入力端子12aと出力端子12bとの間の電位差は、タクトスイッチ12がオン状態であっても、例えば、タクトスイッチ12における接点部材の硫化やシロキサン付着等の接点の劣化により、接点抵抗が増大することに起因して、図7中に一点鎖線で囲ったように、所定値以上になる場合がある。そして、このような場合にも、電位差検出回路16は、タクトスイッチ12がオフ状態の場合と同様に、ラッチ解除信号VRSTを出力する（図7のラッチ解除信号VRST参照）。このため、第1実施例におけるスイッチ制御信号生成回路15のように、ラッチ解除禁止回路15bを備えていない場合には、スイッチ制御信号生成回路15Aが、所望しないラッチ解除信号VRSTの入力によって誤動作することがあり得る。これに対し、第2実施例のプリンターでは、電力供給遮断回路におけるスイッチ制御信号生成回路15Aがラッチ解除禁止回路15bを備えることによって、所望しないラッチ解除信号の入力による誤動作を防止することができる。10

#### 【0062】

以上説明した第2実施例のプリンターによつても、第1実施例のプリンター10と同様に、放電抵抗Rを用いることなく、電位差検出回路16から出力されるラッチ解除信号VRSTによって、ラッチ回路15aのラッチ解除を行うことができるので、プリンターの小型化と、ラッチ解除時間の短縮とを両立することができる。20

#### 【0063】

C. 第3実施例：

第3実施例のプリンターは、第2実施例のプリンターと同様に、動作モードとして、電力供給モードと、電力遮断モードとを有している。ただし、第3実施例のプリンターは、電力供給遮断回路の構成が、第2実施例のプリンターと異なっている。以下、第3実施例のプリンターにおける電力供給遮断回路の構成、および、動作について説明する。

#### 【0064】

C1. 電力供給遮断回路の構成：

図8は、第3実施例のプリンターが備える電力供給遮断回路の概略構成を示す説明図である。図8と図6との比較から分かるように、第3実施例のプリンターでは、電力供給遮断回路は、第2実施例におけるスイッチ制御信号生成回路15Aの代わりに、スイッチ制御信号生成回路15Bを備えている。そして、スイッチ制御信号生成回路15Bは、ラッチ回路15a、および、ラッチ解除禁止回路15bに加えて、OR回路15cを備えている。そして、OR回路15cには、ラッチ回路15aから出力されたラッチ回路15aのラッチ状態を示す状態信号VSTと、ラッチ解除禁止回路15bを通解したラッチ解除信号VRSTとが入力される。なお、状態信号VSTは、第2実施例におけるスイッチ制御信号VSCと同じ信号である。スイッチ制御信号生成回路15Bは、OR回路15cから出力される信号をスイッチ制御信号VSCとして、スイッチ回路14に出力する。30

#### 【0065】

つまり、スイッチ制御信号生成回路15Bは、OR回路15cに、ラッチ回路15aからラッチ開始信号VLTをラッチしていることを示す状態信号VSTが入力されている期間、および、ラッチ解除禁止回路15bからラッチ解除信号VRSTが入力されている期間、内部回路への直流電力の供給を遮断すべきスイッチ制御信号VSCを生成する。また、スイッチ制御信号生成回路15Bは、OR回路15cに、ラッチ開始信号VLTをラッチしていることを示す状態信号VSTおよびラッチ解除信号VRSTの双方が入力されていない期間、内部回路への直流電力の供給を遮断すべきスイッチ制御信号VSCを生成しない。

#### 【0066】

C2. 電力供給遮断回路の動作：

50

図9は、第3実施例のプリンターにおける電力供給遮断回路の動作を示すタイミングチャートである。時刻t0から時刻t3までの動作は、第2実施例のプリンターにおける電力供給遮断回路の動作と同じである(図7参照)。

#### 【0067】

先に説明した第2実施例のプリンターにおける電力供給遮断回路では、時刻t3において、すなわち、動作モードが電力遮断モードである場合に、タクトスイッチ12がオフ状態にされたときに、ラッチ解除信号V R S Tによってラッチ回路15aがラッチ解除されるため、スイッチ回路14は閉状態になる。このため、タクトスイッチ12がオフ状態であっても、平滑コンデンサ13からC P U 17を含む内部回路に電流が流れ、内部回路が誤動作するおそれがある。

10

#### 【0068】

これに対し、第3実施例のプリンターにおける電力供給遮断回路では、時刻t3において、O R回路15cにラッチ解除信号V R S Tが入力され、このラッチ解除信号V R S Tが、スイッチ回路14を開状態とすべきスイッチ制御信号V S Cとして、スイッチ制御信号生成回路15Bからスイッチ回路14に出力されるので、スイッチ回路14を開状態に保持することができる。したがって、上述した内部回路の誤動作を防止することができる。

#### 【0069】

なお、第3実施例のプリンターにおける電力供給遮断回路において、ラッチ解除禁止回路15bを省略した場合には、図9中に一点鎖線で示したように、タクトスイッチ12の入力端子12aと出力端子12bとの間に生じる電位差が所定値以上になった場合に、電位差検出回路16からラッチ解除信号V R S Tが出力され、このラッチ解除信号V R S Tがスイッチ制御信号V S Cとしてスイッチ制御信号生成回路15B(O R回路15c)から出力される。このため、動作モードが電力供給モードである期間に、スイッチ回路14が開状態になってしまう場合がある。しかし、本実施例では、ラッチ解除禁止回路15bを備えるので、上述した不具合は生じない。

20

#### 【0070】

以上説明した第3実施例のプリンターによても、第1実施例のプリンター10や、第2実施例のプリンターと同様に、放電抵抗Rを用いることなく、電位差検出回路16から出力されるラッチ解除信号V R S Tによって、ラッチ回路15aのラッチ解除を行うことができるので、プリンターの小型化と、ラッチ解除時間の短縮とを両立することができる。

30

#### 【0071】

##### D. 変形例：

以上、本発明のいくつかの実施の形態について説明したが、本発明はこのような実施の形態になんら限定されるものではなく、その要旨を逸脱しない範囲内において種々なる態様での実施が可能である。例えば、以下のような変形が可能である。

#### 【0072】

##### D 1 . 変形例 1 :

上記第1実施例のプリンター10では、電力供給遮断回路は、電位差検出回路16を備え、この電位差検出回路16がラッチ解除信号V R S Tをスイッチ制御信号生成回路15に出力するものとしたが、本発明は、これに限られない。タクトスイッチ12の入力端子12aと出力端子12bとの接続状態を検出し、この接続状態がオフ状態である場合に、ラッチ解除信号V R S Tをスイッチ制御信号生成回路15に出力するラッチ解除信号生成部を、電力供給遮断回路が備えるようにすればよい。

40

#### 【0073】

図10は、変形例のプリンターにおける電力供給遮断回路の概略構成を示す説明図である。図10と図2との比較から分かるように、変形例のプリンターにおける電力供給遮断回路は、第1実施例における電位差検出回路16の代わりに、センサー16sを備える。このセンサー16sは、タクトスイッチ12がオフ状態にセットされているか、オン状態

50

にセットされているかを検出する。そして、センサー 16 s は、タクトスイッチ 12 がオフ状態にセットされているときに、ラッチ解除信号 V R S T をスイッチ制御信号生成回路 15 に出力する。また、センサー 16 s は、タクトスイッチ 12 がオン状態にセットされているときに、ラッチ解除信号 V R S T をスイッチ制御信号生成回路 15 に出力しない。なお、センサー 16 s は、タクトスイッチ 12 がオフ状態にセットされているか、オン状態にセットされているかを検出可能なセンサーであればよく、例えば、光学センサーや、超音波センサー等、種々のセンサーを適用可能である。電力供給遮断回路を上述した構成とすることによっても、第 1 実施例のプリンター 10 と同様の効果を奏することができる。

【0074】

10

D 2 . 変形例 2 :

上記実施例では、電力供給遮断回路が備えるラッチ回路 15 a には、エラー検出回路 18 から出力されたラッチ開始信号 V L T が入力されるものとしたが、これを省略するようにしてもよい。

【0075】

20

D 3 . 変形例 3 :

上記実施例では、電力供給遮断回路が備える電源スイッチとして、タクトスイッチ 12 を用いるものとしたが、本発明は、これに限られない。本発明において、一般に、電源スイッチは、入力端子と出力端子と操作部とを有する電源スイッチであって、操作部の姿勢を、入力端子と出力端子との接続状態がオン状態となる第 1 の姿勢と、接続状態がオフ状態となる第 2 の姿勢との間で切り換える切換操作によって、接続状態が切り換えられるとともに、切換操作が行われない限り、操作部の姿勢および接続状態が保持されるタイプのスイッチであればよい。このようなスイッチとしては、例えば、トグルスイッチや、スライドスイッチや、ロッカースイッチ等が挙げられる。

【0076】

D 4 . 変形例 4 :

上記実施例では、本発明をプリンターに適用した場合について説明したが、プリンター以外の他の情報機器に適用することも可能である。

【符号の説明】

【0077】

30

- 1 0 ... プリンター

- 1 2 ... タクトスイッチ

- 1 2 a ... 入力端子

- 1 2 b ... 出力端子

- 1 2 c ... 操作部

- 1 3 ... 平滑コンデンサ

- 1 3 a ... 第 1 の端子

- 1 3 b ... 第 2 の端子

- 1 3 R ... 抵抗器

- 1 4 ... スイッチ回路

- 1 5 , 1 5 A , 1 5 B ... スイッチ制御信号生成回路

- 1 5 a , 1 5 R a ... ラッチ回路

- 1 5 b ... ラッチ解除禁止回路

- 1 5 c ... O R 回路

- 1 6 ... 電位差検出回路

- 1 6 s ... センサー

- 1 7 ... C P U

- 1 8 ... エラー検出回路

- 2 0 ... A C アダプター

- 2 2 , 2 4 ... 電源ケーブル

40

50

3 0 ... プリンターケーブル

1 0 0 ... コンピュータシステム

V L T ... ラッチ開始信号

V R S T ... ラッチ解除信号

V S C ... スイッチ制御信号

V P R ... ラッチ解除禁止信号

V S T ... 状態信号

R ... 放電抵抗

【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(56)参考文献 特開平11-069796(JP,A)

特開2004-180433(JP,A)

特開2004-040858(JP,A)

特開2006-166580(JP,A)

特開2001-016863(JP,A)

特開2009-165288(JP,A)

特開2006-073023(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00~3/44

H02J 1/00