(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3553196号 (P3553196)

(45) 発行日 平成16年8月11日(2004.8.11)

(24) 登録日 平成16年5月14日(2004.5.14)

(51) Int.C1.<sup>7</sup>

HO1L 27/12 HO1L 27/12 B HO1L 21/304 HO1L 21/304 622G HO1L 21/306 B

FI

請求項の数 2 (全 6 頁)

(21) 出願番号 特願平7-109908

(22) 出願日 平成7年3月29日 (1995.3.29)

(65) 公開番号 特開平8-274286

(43) 公開日 平成8年10月18日 (1996.10.18) 審査請求日 平成14年3月27日 (2002.3.27) |(73) 特許権者 000184713

コマツ電子金属株式会社

神奈川県平塚市四之宮3丁目25番1号

||(74)代理人 100115325

弁理士 津田 幸宏

(74)代理人 100087228

弁理士 衞藤 彰

|(72) 発明者 中吉 雄一

宮崎県宮崎郡清武町大字木原1112番地

九州コマツ電子株式会社内

(72) 発明者 小川 正

宮崎県宮崎郡清武町大字木原1112番地

九州コマツ電子株式会社内

最終頁に続く

(54) 【発明の名称】SOI基板の製造方法

## (57)【特許請求の範囲】

#### 【請求項1】

次の工程からなることを特微とするSOI基板の製造方法。

- (1)支持基板となる半導体ウェハの両面を、両面研磨装置により同時に研磨する両面研磨工程。

- (2)両面研磨された支持基板の上面に、活性基板となる半導体ウェハを貼り合わせて貼合ウェハを得る貼り合わせ工程。

- (3) 貼合ウェハの周縁部の未接着部分を取り除く未接着部除去工程。

- (4) 未接着部分を除去された貼合ウェハの活性基板の表面を、平面研削して厚みを減ずる平面研削工程。

- (5)平面研削された活性基板の表面を、スピンエッチングによりエッチングするスピン エッチング工程。

- (6)スピンエッチングされた活性基板を、PACE加工により薄膜化するPACE加工 工程。

### 【請求項2】

次の工程からなることを特徴とするSOI基板の製造方法。

- (1)支持基板となる半導体ウェハの両面を、両面研磨装置により同時に研磨する両面研磨工程。

- (2)両面研磨された支持基板の上面に、活性基板となる半導体ウェハを貼り合わせて貼合ウェハを得る貼り合わせ工程。

- (3)貼合ウェハの周縁部の未接着部分を取り除く未接着部除去工程。

- (4) 未接着部分を除去された貼合ウェハの活性基板の表面を、平面研削して厚みを減ずる平面研削工程。

- (5)平面研削された貼合ウェハを一枚ずつトップリングにより保持して、活性基板を研磨する枚葉研磨工程。

- (6)枚葉研磨された活性基板を、PACE加工により薄膜化するPACE加工工程。

【発明の詳細な説明】

# [0001]

#### 【産業上の利用分野】

本発明は、活性基板となる半導体ウェハと支持基板となる半導体ウェハを貼り合わせて得られるSOI基板の製造方法に関するものである。

#### [0002]

#### 【従来の技術】

近年、集積回路の開発技術が向上するにともない、デバイス工程からのSOI基板製造における品質向上の要求は厳しくなる一方である。特に、集積回路の作動速度の高速化を図るために、活性層を可能な限り薄膜化させる必要がある。

従来、活性基板となる半導体ウェハと支持基板となる半導体ウェハを貼り合わせて得られるSOI基板は次の工程により製造されている。

- (1)支持基板となる半導体ウェハの表面に酸化膜を発生させ、その上面に活性基板となる半導体ウェハを貼り合わせ、さらにこの活性基板の表面にも酸化膜を発生させて貼合ウェハを得る。

- (2)次に、この貼り合せウェハの周縁部の未接着部分を研削またはエッチングにより除去する。

- (3)活性基板の表面を平面研削し、その厚みを減らす。

- (4)支持基板の裏面を貼付ブロックに貼り付けて活性基板の表面を研磨し、活性基板を さらに薄くする。

ところが、この研磨によって薄くされた活性基板はその厚さが  $2 \sim 3 \mu m$ 程度であり、高速集積回路の製造に使用される SOI 基板においては、活性基板の厚さを  $0.1 \mu m$ 程度まで薄膜化させることが要求される。この薄膜化には PACE 加工を使用している。すなわち、上記した方法により研磨された活性基板の表面をこの PACE 加工により均一に薄膜化するものである。

## [0003]

#### 【発明が解決しようとする課題】

しかしながら、このように活性基板を貼り付け研磨した後にPACE加工する方法では、研磨のために支持基板の裏面を貼付ブロックに貼り付けるため、貼付ブロックの貼付面と支持基板の裏面の間に異物や凹みがあると、研磨後の活性基板の表面に微小な凹凸が発生する。

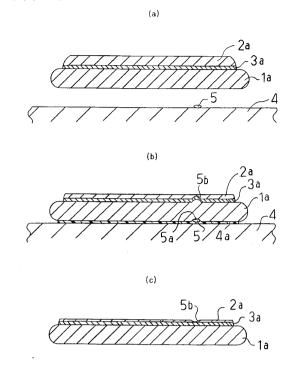

例えば、貼付ブロック4の貼付面に異物5があった場合〔図2(a)〕、この貼付面に支持基板1 aを貼り付けると、支持基板1 aの裏面に異物5による凹み5 aが発生し、この凹み5 a はさらに支持基板1 aの上面を介して酸化膜3 aと活性基板2 aにもおよび、このままの状態で活性基板2 aの上面を研磨されることとなり、活性基板2 aに極薄部分5 bが発生する〔図2(b)〕。研磨終了後に、貼付ブロック4から剥がし、ワックス4 aを除去すると、支持基板1 a は元の状態に戻り、これにより活性基板2 a の極薄部分5 b は凹んだ状態で残存することとなる〔図2(c)〕。

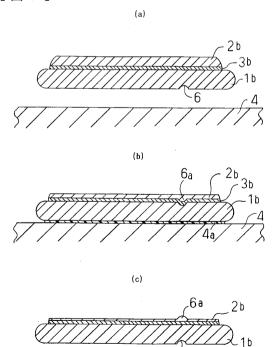

また、支持基板1bの裏面に凹み6があった場合〔図3(a)〕、この支持基板1bを貼付ブロック4に貼り付けて研磨すると、酸化膜3bと活性基板2bの凹み6に対応する部分がこの研磨圧により窪んだまま研磨され、この部分が極厚部分6aとなる〔図3(b)〕。研磨終了後に、貼付ブロック4から剥がしてワックス4aを除去すると、支持基板1bは元の状態に戻り、これにより極厚部分6aは活性基板2bの表面に突出した状態で残存することとなる〔図3(c)〕。

50

40

20

ところが、上記したような微小な凹凸が活性基板の表面に局在した場合は、PACE加工を行っても平坦化することができず、均一な厚さの活性基板を得ることができないという問題がある。

本発明は、上記問題に鑑みなされたもので、均一に薄膜化された活性基板を有するSOI 基板の製造方法を提供することを目的とするものである。

#### [0004]

## 【課題を解決するための手段】

このため本発明では、SOI基板の製造方法を、支持基板となる半導体ウェハの両面を両面研磨装置により同時に研磨し、両面研磨された支持基板の上面に活性基板となる半導体ウェハを貼り合わせて貼合ウェハを得、貼合ウェハの周縁部の未接着部分を取り除き、未接着部分を除去された貼合ウェハの活性基板の表面を平面研削して厚みを減じ、平面研削された活性基板の表面をスピンエッチングによりエッチングし、スピンエッチングされた活性基板をPACE加工により薄膜化するようにしたものである

また、SOI基板の製造方法を、支持基板となる半導体ウェハの両面を両面研磨装置により同時に研磨し、両面研磨された支持基板の上面に活性基板となる半導体ウェハを貼り合わせて貼合ウェハを得、貼合ウェハの周縁部の未接着部分を取り除き、未接着部分を除去された貼合ウェハの活性基板の表面を平面研削して厚みを減じ、平面研削された貼合ウェハを一枚ずつトップリングにより保持して活性基板を枚葉研磨し、枚葉研磨された活性基板をPACE加工により薄膜化するようにしたものである。

#### [0005]

### 【実施例】

以下、本発明の実施例を図面に基づいて説明する。

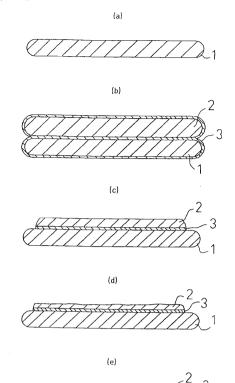

図1は本発明に係るSOI基板の製造方法の各工程における側面断面図、図2及び図3は従来技術の製造方法により製造されたSOI基板の側面断面図である。

#### [0006]

本実施例のSOI基板は次の方法に製造される。

(1)支持基板1となる半導体ウェハの両面を両面研磨装置により同時に研磨し、表裏面ともに平坦な半導体ウェハを得る〔図1(a)〕。この両面研磨された支持基板1の裏面には、最終工程である活性基板の薄膜化において悪影響を与える凹みなどの欠陥はない。(2)両面研磨された支持基板1の表面に酸化膜3を発生させ、その上面に活性基板2となる半導体ウェハを貼り合わせ、さらに活性基板2にも酸化膜3を発生させ貼り合せウェハを得る〔図1(b)〕。

(3) 貼合ウェハの周縁部の未接着部分を取り除き、活性基板2と支持基板1の間の酸化膜3以外の酸化膜を除去し、さらに活性基板2の上面を平面研削してその厚みを減ずる〔図1(c)〕。

(4)平面研削された活性基板 2 の表面をスピンエッチングによりエッチングし、活性基板 2 をさらに薄くする [ 図 1 (d) ]。このスピンエッチングでの取り代は約  $1 0.0 \sim 20.0 \mu$  m程度で、その厚さムラは取り代に対して  $\pm 5.0 \%$  以内であり、次の工程の PACE加工により除去できる厚さである。また従来技術の研磨レートが  $0.8 \mu$  m / 分であったのに対し、スピンエッチングによるエッチングレートは  $30 \mu$  m / 分と非常に速く、作業効率が著しく向上する。

(5) スピンエッチングされた活性基板 1 の表面を P A C E 加工により薄膜化する〔図 1 (e)〕。スピンエッチングで発生した厚さムラは従来技術の貼り付け研磨で発生していた小さい凹凸と違って滑らかであることから、 P A C E 加工の分解能で十分処理できるので、活性基板 1 を均一に薄膜化することができる。また、この P A C E 加工で薄膜化された活性基板 1 における厚さムラは±10.0 n m程度である。

#### [0007]

尚、上記実施例では、平面研削された活性基板2をスピンエッチングにより薄く加工していたが、これに限定されるものではなく、スピンエッチングに替わり平面研削された貼合ウェハを一枚ずつトップリングにより保持して、枚葉研磨されるものでもよい。この方法

20

30

40

においても両面研磨された半導体ウェハが支持基板として使用されるため、枚葉研磨でその裏面の不具合による活性基板への悪影響を与えることがない。

#### [00008]

#### 【発明の効果】

本発明では以上のように構成したので、PACE加工の前工程において発生する厚さムラを防止することができ、均一な薄膜化された活性基板を有するSOI基板を得られるという優れた効果がある。

また、両面研磨された半導体ウェハを支持基板として使用するため、その裏面には凹みなどの不具合は存在せず、活性基板の薄膜化において悪影響を与えることがないという優れた効果がある。

さらに、従来技術の貼り付け研磨に比較し、スピンエッチングはレートが速いため、生産 効率が良いという優れた効果がある。

#### 【図面の簡単な説明】

- 【図1】本発明に係るSOI基板の製造方法の各工程における側面断面図ある。

- 【図2】従来技術に製造方法により製造されたSOI基板の側面断面図である。

- 【図3】従来技術に製造方法により製造されたSOI基板の側面断面図である。

## 【符号の説明】

- 1 支持基板

- 1 a 支持基板

- 1 b 支持基板

- 2 活性基板

- 2 a 活性基板

- 2 b 活性基板

- 3 酸化膜

- 3 a 酸化膜

- 3 b 酸化膜

- 4 貼付ブロック

- 4 a ワックス

- 5 異物

- 5 a 凹み

- 5 b 極薄部分

- 6 凹み

- 6 a 極厚部分

10

20

# 【図1】

# 【図2】

# 【図3】

## フロントページの続き

## (72)発明者 石井 明洋

宮崎県宮崎郡清武町大字木原1112番地 九州コマツ電子株式会社内

## 審査官 宮崎 園子

# (56)参考文献 特開平05-138530(JP,A)

特開平06-176993(JP,A)

特開平05-160074(JP,A)

特開平07-066375(JP,A)

特開平03-046314(JP,A)

特開平06-061461(JP,A)

# (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 27/12

H01L 21/304 622

H01L 21/306