(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5216987号

(P5216987)

(45) 発行日 平成25年6月19日(2013.6.19)

(24) 登録日 平成25年3月15日(2013.3.15)

(51) Int.Cl.

HO3K 7/08 (2006.01)

F 1

HO3K 7/08

F

請求項の数 27 外国語出願 (全 11 頁)

(21) 出願番号 特願2007-260665 (P2007-260665)

(22) 出願日 平成19年10月4日 (2007.10.4)

(65) 公開番号 特開2008-92581 (P2008-92581A)

(43) 公開日 平成20年4月17日 (2008.4.17)

審査請求日 平成22年9月28日 (2010.9.28)

(31) 優先権主張番号 11/543,503

(32) 優先日 平成18年10月4日 (2006.10.4)

(33) 優先権主張国 米国(US)

(73) 特許権者 501315784

パワー・インテグレーションズ・インコーポレーテッド

アメリカ合衆国・95138・カリフォルニア州・サンホゼ・ヘリヤー・アベニュー

5245

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】パルス幅変調の方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の持続時間中に外部制御電流に基づいた第1の電流をコンデンサの第1の電圧に変換するための、また、第2の持続時間中に、前記第1の電圧を第2の電圧に変化させるよう第2の既知の基準電流を放電するためのコンデンサと、

前記コンデンサの出力に結合され、前記外部制御電流に応答して周期的な出力信号のパルス幅を変化させるために、前記第2の持続時間中に前記コンデンサの電圧を基準電圧と比較する比較器とを備える回路。

## 【請求項 2】

前記周期的な出力信号のパルス幅が、前記コンデンサの値から実質的に独立したものである、請求項1に記載の回路。

## 【請求項 3】

前記周期的な出力信号のパルス幅が、前記基準電圧の値から実質的に独立したものである、請求項1に記載の回路。

## 【請求項 4】

前記周期的な出力信号のパルス幅が、前記比較器の応答における遅延から実質的に独立したものである、請求項1に記載の回路。

## 【請求項 5】

前記周期的な出力信号のパルス幅が、抵抗器の値から実質的に独立したものである、請求項1に記載の回路。

10

20

## 【請求項 6】

コンデンサ電圧の変化が、前記第2の持続時間中に前記コンデンサの電圧が前記基準電圧に到達したとき終了する、請求項 1に記載の回路。

## 【請求項 7】

タイミング信号を生成するように結合された発振器をさらに備え、前記周期的な出力信号の周期が、前記発振器から受信された前記タイミング信号の周期である、請求項 1に記載の回路。

## 【請求項 8】

前記発振器から受信された前記タイミング信号が、前記出力信号の最大オン時間を決定する、請求項 7に記載の回路。

10

## 【請求項 9】

発振器と、システム入力に応答して回路の周波数およびデューティ比を変化させるように発振器からタイミング信号を受け取るように結合された制御論理とをさらに備える、請求項 1に記載の回路。

## 【請求項 10】

前記制御論理が、前記コンデンサを充放電するために、前記発振器と、回路内のスイッチのスイッチングとを制御するように、前記比較器からの出力および前記システム入力を受け取るようにさらに結合される、請求項 9に記載の回路。

## 【請求項 11】

前記制御論理が、前記発振器の出力に結合された遅延回路と、前記遅延回路の出力に結合されたANDゲートとを備え、前記制御論理が、パルス幅変調信号を出力するように前記比較器の出力に結合される、請求項 9に記載の回路。

20

## 【請求項 12】

前記第1の電流が、電流源からの電流と、前記外部制御電流に比例する電流とを含む、請求項 1に記載の回路。

## 【請求項 13】

前記外部制御電流に比例する電流を生成するために、電流ミラーをさらに備える、請求項 12に記載の回路。

30

## 【請求項 14】

集積回路に含まれる、請求項 1に記載の回路。

## 【請求項 15】

前記集積回路が、電源を制御するように結合される、請求項 14に記載の回路。

## 【請求項 16】

第1の持続時間中に、外部制御電流に基づいた第1の電流をコンデンサの第1の電圧に変換するステップと、

第2の持続時間中に、第2の既知の基準電流を放電することによって前記コンデンサの電圧を前記第1の電圧から第2の電圧に変化させるステップと、

周期的な出力信号のパルス幅を変調するために、前記第2の持続時間中に、前記コンデンサの電圧を基準電圧と比較するステップとを含む、方法。

40

## 【請求項 17】

前記第2の持続時間中に前記コンデンサの電圧が前記基準電圧に到達したとき、前記コンデンサの電圧を変化させるステップを終了するステップをさらに含む、請求項 16に記載の方法。

## 【請求項 18】

前記周期的な出力信号の周期と前記周期的な出力信号の最大パルス幅を決定するために、発振器からタイミング信号を受け取るステップをさらに含む、請求項 16に記載の方法。

## 【請求項 19】

前記周期的な出力信号のパルス幅を変調するために前記コンデンサを充放電するように

50

、対応する複数の電流源のそれぞれに結合された複数のスイッチのそれぞれをスイッチングするステップをさらに含む、請求項 1 6 に記載の方法。

【請求項 2 0】

回路であって、

コンデンサが受信した充電電流に応答して第 1 の持続時間中に第 1 の電圧を発生させ、コンデンサが提供した第 2 の既知の基準放電電流に応答して第 2 の持続時間中に第 2 の電圧を発生させるように配置されたコンデンサを備え、前記充電電流は、外部制御電流に応答して生成され、前記回路はさらに、

前記コンデンサの出力に結合され、いつ前記コンデンサが前記第 2 の電圧に到達するかを判断する比較器と、

前記比較器の出力に応答して周期的な出力信号のパルス幅を変化させるために信号を出力するように配置された制御論理とを備える、回路。

【請求項 2 1】

タイミング信号を生成するように結合された発振器をさらに備え、前記周期的な出力信号の周期が、前記発振器から受信された前記タイミング信号の周期である、請求項 2 0 に記載の回路。

【請求項 2 2】

前記発振器から受信された前記タイミング信号が、前記出力信号の最大オン時間を決定する、請求項 2 1 に記載の回路。

【請求項 2 3】

発振器をさらに備え、前記制御論理が、システム入力に応答して回路の周波数およびデューティ比を変化させるように前記発振器からタイミング信号を受け取るよう結合される、請求項 2 0 に記載の回路。

【請求項 2 4】

前記制御論理が、前記コンデンサを充放電するために、前記発振器と、回路内のスイッチのスイッチングとを制御するように、前記比較器からの出力および前記システム入力を受け取るようさらに結合される、請求項 2 3 に記載の回路。

【請求項 2 5】

前記制御論理が、前記発振器の出力に結合された遅延回路を備え、前記遅延回路の出力が、AND ゲートに結合され、前記制御論理が、パルス幅変調信号を出力するように前記比較器の出力に結合される、請求項 2 3 に記載の回路。

【請求項 2 6】

前記充電電流が、電流源からの電流と、前記外部制御電流に比例する電流とを含む、請求項 2 0 に記載の回路。

【請求項 2 7】

前記外部制御電流に比例する電流を生成するため、電流ミラーをさらに備える、請求項 2 6 に記載の回路。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、電源に関し、より具体的には、本発明は、パルス幅変調器回路に関する。

【背景技術】

【0 0 0 2】

多くのスイッチング電源が出力を調節するためにパルス幅変調を使用している。パルス幅変調器が、出力値に関連する制御信号を受信する。次いで、パルス幅変調器は、制御信号の値に従って、スイッチング周期の一部としてスイッチの導通時間を設定する。導通時間であるスイッチング周期の一部は、スイッチのデューティ比である。

【0 0 0 3】

制御信号の変化に応答するデューティ比の変化はパルス幅変調器の利得の尺度である。変調器の利得は、システムの安定性と動的応答に対して強い影響があるため、一般に、十

10

20

30

40

50

分に制御される。

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来のパルス幅変調器は、制御電圧を、発振器からの三角電圧またはのこぎり歯電圧と比較するために、電圧比較器を使用する。比較器の出力は、パルス幅変調信号である。制御信号が電圧ではなく電流である応用例では、比較器に入力するために、抵抗器が電流を電圧に変換する。抵抗器の値は、変調器の利得に正比例するため、一般に、十分に制御される。従来の技法が集積回路において使用されるとき問題が生じる。というのは、温度と作製プロセスの変動と共に変化しない正確な値を有する集積抵抗器を実装することは、コストがかかるからである。

【発明を実施するための最良の形態】

【0005】

本発明の非限定的かつ非網羅的な実施形態について、別段の指定がない限り同様の符号が様々な図全体にわたって同様の部分を指す以下の図を参照して述べる。

【0006】

電流に応答するパルス幅変調信号を提供する方法および装置。以下の説明では、本発明を徹底して理解できるように、多数の特定の詳細について述べる。しかし、本発明を実施するために、その特定の詳細を使用しなくてもよいことが当業者には明らかになるであろう。他の場合には、本発明をあいまいにすることを回避するために、周知の材料または方法について詳細に述べていない。

【0007】

本明細書全体にわたって、「一実施形態」または「実施形態」に言及したときは、その実施形態と関連して述べられている特定の機能、構造、または特徴が、本発明の少なくとも1つの実施形態に含まれることを意味する。したがって、本明細書全体にわたって様々な箇所で「一実施形態では」または「実施形態では」という句が現れたときは、必ずしもすべてが同じ実施形態に言及しているとは限らない。さらに、特定の機能、構造、または特徴は、1つまたは複数の実施形態において、任意の適切な組合せおよび/または副組合せで組み合わせることができる。さらに、本明細書と共に提供される図は、当業者に説明するためのものであり、図面は、必ずしも原寸に比例して示されていないことを理解されたい。

【0008】

本発明の教示による回路の様々な例では、電流に応答するパルス幅変調信号が提供される。例示的な方法は、集積回路内で使用するのに有益な機能を含む。具体的には、本発明の教示による例示的な回路は、スイッチング電源を制御する集積回路内で有用である。

【0009】

本発明の一態様では、制御電流をパルス幅変調信号に変換するために、抵抗器の値に実質的に依存しなくてもよい。その代わりに、様々な例によれば、本方法は、制御電流に比例する電流を使用し、発振器の周期内の既知の時間の間、コンデンサを充電する。次いで、既知の電流によって、コンデンサを放電させる。本発明の教示によれば、コンデンサの電圧が初期値から基準電圧になる時間により、デューティ比が発振器の周期の一部分として決定される。

【0010】

このようにして、例示的な回路の性質により、デューティ比は、コンデンサの値、または例えば基準電圧の値、または例えば比較器の遅延、または例えば抵抗器の値など例えば他の回路要素の値から独立したものになる。集積回路内で使用されたとき、所望の精度のパラメータを得るために電流をトリミングすることが容易である。本発明の例の他の態様は、一定の変調器利得を維持しながら、一定オン時間モード、一定オフ時間モード、一定周波数モードの間で、変調モードを変化させることができるようにすることを含む。

【0011】

10

20

30

40

50

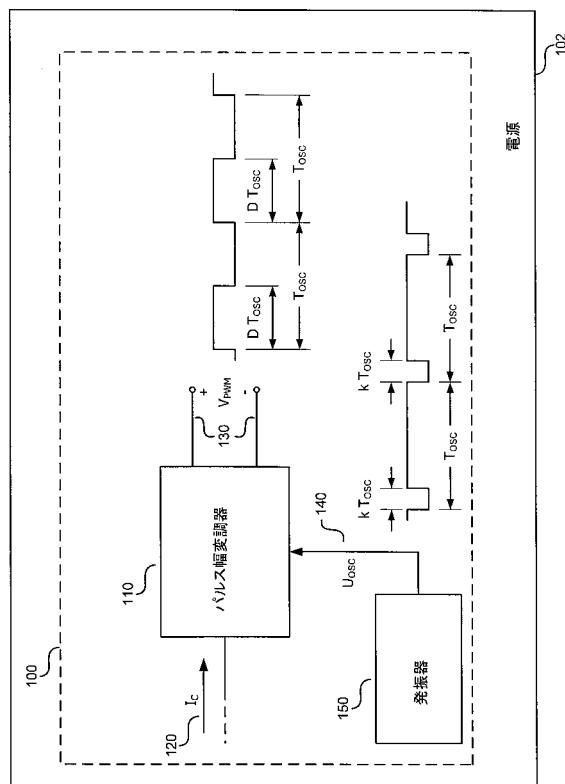

例示するために、図1は、本発明の教示による1つの例示的なデューティ比回路を示すブロック図である。図のように、デューティ比制御回路100は、パルス幅変調器回路110と発振器150を含む。図1に示されているように、一例のデューティ比制御回路100は、電源102を制御するように結合される集積回路に含まれる。パルス幅モジュール回路110は、発振器150からタイミング信号 $U_{osc}\ 1\ 4\ 0$ を受信し、図1の例では電圧 $V_{PWM}$ であるパルス幅変調信号130を生成する。タイミング信号 $U_{osc}\ 1\ 4\ 0$ は、電圧でも電流でもよい。この例では、タイミング信号 $U_{osc}\ 1\ 4\ 0$ は、周期 $T_{osc}$ を有する周期的なものである。タイミング信号 $U_{osc}$ は、周期 $T_{osc}$ の一部分kの間、LOWであり、周期 $T_{osc}$ の残りの部分の間、HIGHである。パルス幅変調信号130は、周期 $T_{osc}$ の一部分Dの間、HIGHであり、Dはデューティ比である。パルス幅変調器回路110はまた、制御電流 $I_c\ 1\ 2\ 0$ をも受け取る。一例では、制御電流 $I_c\ 1\ 2\ 0$ は、デューティ比Dを調整する。

## 【0012】

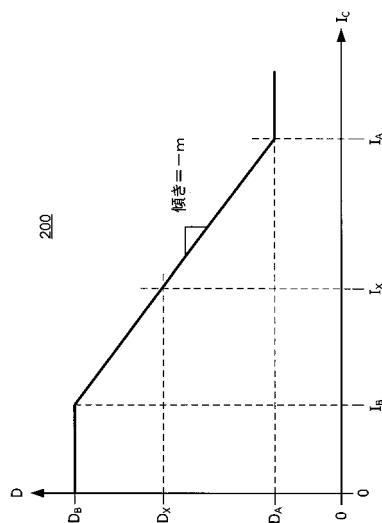

図2は、本発明の教示によるパルス幅変調器回路の所望の応答を示すグラフである。グラフ200は、デューティ比Dが制御電流 $I_c$ に応答してどのように変化するかを示す。この例では、デューティ比Dは、 $I_B$ より小さい制御電流について最大値 $D_B$ であり、 $I_A$ より大きい制御電流について最小値 $D_A$ である。デューティ比は値 $D_x$ であり、この値 $D_x$ は、制御電流が $I_A$ と $I_B$ の間にある値 $I_x$ であるとき $D_A$ と $D_B$ の間にある。制御電流 $I_A$ と $I_B$ の間のパルス幅変調器の利得は、傾き-mである。図2の例のパルス幅変調器の利得mは、逆アンペア(reciprocal ampere)の単位を有する。

## 【0013】

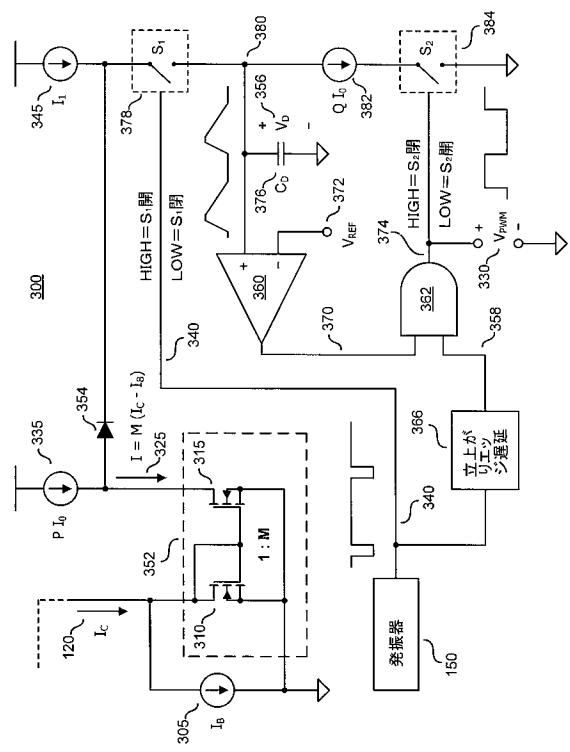

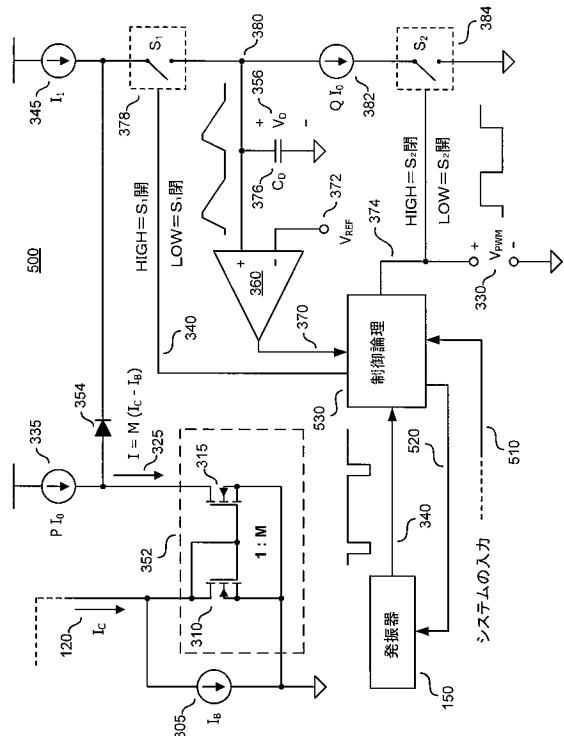

図3は、本発明の教示による、グラフ200と同様の応答を生成するデューティ比制御回路300の一例の概略図である。図のように、回路300は、制御電流 $I_c\ 1\ 2\ 0$ を受け取る。電流源305が、電流 $I_B$ を制御電流 $I_c\ 1\ 2\ 0$ から減算する。制御電流 $I_c\ 1\ 2\ 0$ と制御電流305からの電流 $I_B$ との差は、電流ミラー352の入力部で、トランジスタ310によって受け取られる。電流ミラー352のトランジスタ310、315は、それぞれの比1:Mの強さ(strength)を有し、それにより、ミラー電流325は、入力電流に倍率Mを乗じたものになる。

## 【0014】

図3の例では、発振器150は、スイッチS<sub>1</sub>378を制御するタイミング信号340を送る。タイミング信号340がLOWであるとき、スイッチS<sub>1</sub>378は閉じ、電流源345からの電流 $I_1$ と整流器354を通る電流との和である電流によってコンデンサ $C_D\ 3\ 7\ 6$ を充電する。整流器354を通る電流が、電流源335からの電流とミラー電流325との差であるのは、その差が正であるときである。整流器354を通る電流は、ミラー電流325が電流源335からの電流より大きいとき、ゼロである。一例では、整流器354はダイオードを含む。

## 【0015】

コンデンサ $C_D\ 3\ 7\ 6$ の電圧 $V_D\ 3\ 5\ 6$ は、比較器360によって基準電圧 $V_{REF}\ 3\ 7\ 2$ と比較される。比較器360の出力370は、電圧 $V_D\ 3\ 5\ 6$ が基準電圧 $V_{REF}\ 3\ 7\ 2$ より大きいときHIGHである。比較器360の出力370は、電圧 $V_D\ 3\ 5\ 6$ が基準電圧 $V_{REF}\ 3\ 7\ 2$ より小さいときLOWである。

## 【0016】

図の例に示されているように、発振器150からの信号の立上がりエッジを遅延するために、遅延回路366が結合される。この例では、遅延回路366は、一例では比較器360の応答における遅延である、比較器360の理想的でない応答を補償するために含まれる。遅延回路366からの遅延タイミング信号358と、比較器360の出力370がANDゲート362に対する入力として受け取られる。ANDゲート362の出力374が、スイッチS<sub>2</sub>384を制御する。また、ANDゲート362の出力はパルス幅変調信号330もある。ANDゲート362の出力374がHIGHであるとき、電流源382を用いてコンデンサ $C_D\ 3\ 7\ 6$ を放電するためにスイッチS<sub>2</sub>を閉じる。

## 【0017】

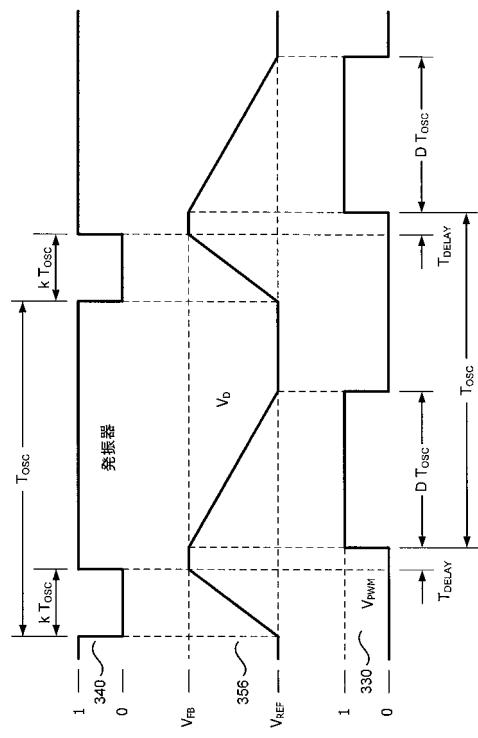

図4は、図3のデューティ比制御回路の例における3つの信号の例示的なタイミング関係を示す。この例では、図4は、発振器150からパルス幅変調器回路によって受信されたタイミング信号340、コンデンサ $C_D$ 376の電圧 $V_D$ 356の例示的な図、回路300によって生成された例示的なパルス幅変調信号330を示す。図3の例示的な回路300が動作するとき、電圧 $V_D$ 356は、コンデンサ $C_D$ 376がタイミング信号340の周期 $T_{OSC}$ の一部分kである時間中に充電されるので、値 $V_{REF}$ から値 $V_{FB}$ に増大する。この一部分kは、パルス幅変調器からの最大デューティ比に対して実質的に保証された制限を設定するように選択することができる。というのは、パルス幅変調器の出力または信号330は、周期 $T_{OSC}$ の一部分kと実質的に同じ持続時間の間、LOWでなければならないからである。 10

## 【0018】

コンデンサ $C_D$ 376は、電流源345からの電流 $I_1$ が整流器354の電流に加算されたものによって充電される。コンデンサ $C_D$ は、制御電流 $I_C$ 120が整流器354内の電流をゼロにするほど十分に大きいとき、電流 $I_1$ によって充電される。したがって、電流 $I_1$ の値は、一例では、発振器150からのタイミング信号340の各周期中に、最小限の持続時間の間、パルス幅変調器信号330がHIGHであることを保証するように選択される。

## 【0019】

発振器150からのタイミング信号340がHIGHになった後で、コンデンサ $C_D$ 376の電圧 $V_D$ 356は、遅延回路366からの遅延 $T_{DELAY}$ 中、値 $V_{FB}$ のままとなる。遅延回路366からの遅延 $T_{DELAY}$ の後で、電流源382は、基準電流 $I_0$ の一部分Qによってコンデンサ $C_D$ 376を放電させる。 20

## 【0020】

図の例からわかるように、パルス幅変調器信号330は、コンデンサ $C_D$ 376が電圧 $V_{FB}$ から電圧 $V_{REF}$ まで放電している間、HIGHである。この例では、基準電流 $I_0$ の一部分Qは、1より小さい乗数であり、最大デューティ比が発振器150からのタイミング信号340によって決定されることを実質的に保証するように十分に放電電流を低減させるための、コンデンサ $C_D$ 376からの放電電流に対する調整手段(adjustment)として、乗数P、一部分k、電流 $I_1$ の値の選択と共に選択することができる。いくつかの例では、発振器の周波数が集積回路のトリムされたパラメータである諸例において、発振器150にタイミング関係を支配させることが望ましいであろう。したがって、この例では、デューティ比Dは、コンデンサ $C_D$ 376が値 $V_{FB}$ から値 $V_{REF}$ まで放電している間の持続時間、またはタイミング信号340のHIGHレベルの持続時間のどちらか小さい方に対応する、発振器150の周期 $T_{OSC}$ の一部分である。デューティ比Dとパルス幅変調器の傾きmすなわちPMW利得は、 $I_A > I_C > I_B$ について式、 30

## 【数1】

$$D = \frac{k}{Q I_0} [P I_0 + I_1 - M (I_C - I_B)]$$

$$m = \frac{M k}{Q I_0}$$

40

によって与えられ、上式で、 $I_0$ は、集積回路の電力散逸または他の設計規則を考慮して選択されることが可能であるバイアス電流である。一例では、電流 $I_1$ 345は、それを必要とする可能性がある応用例において、パルス幅変調器信号330がHIGHとなる最小限の持続時間を決定するように選択される。この一部分kは、最大デューティ比を決定する。一例では、図3の電流源335の乗数Pは、以下のように選択される。

## 【数2】

$$P = \frac{1}{k} - 1$$

## 【0021】

したがって、デューティ比Dは、コンデンサ  $C_D$  376の値、または例えば基準電圧、または例えば抵抗値など他の回路要素から独立したものである。デューティ比D、およびPMW利得の傾きmは、コンデンサ  $C_D$  376の値から独立したものであるが、コンデンサ  $C_D$  376の値とタイプは、様々な例において、応用例の環境要件を満たすように選択される。それに応じて、パラメータQ、M、 $I_0$ を調整することができる。

## 【0022】

一例では、 $T_{osc}$ は、132kHzの発振器周波数に対応して7.58μsであり、この発振器の周波数に対して、他のパラメータは、k = 0.2、P = 4、Q = 0.975、 $I_0 = 1.0 \mu A$ 、 $I_1 = 6.10 nA$ 、M =  $1.1.21 \times 10^{-3}$ であり、図3の立上がりエッジ遅延回路366の遅延時間  $T_{DELAY}$ は、150nsである。

10

## 【0023】

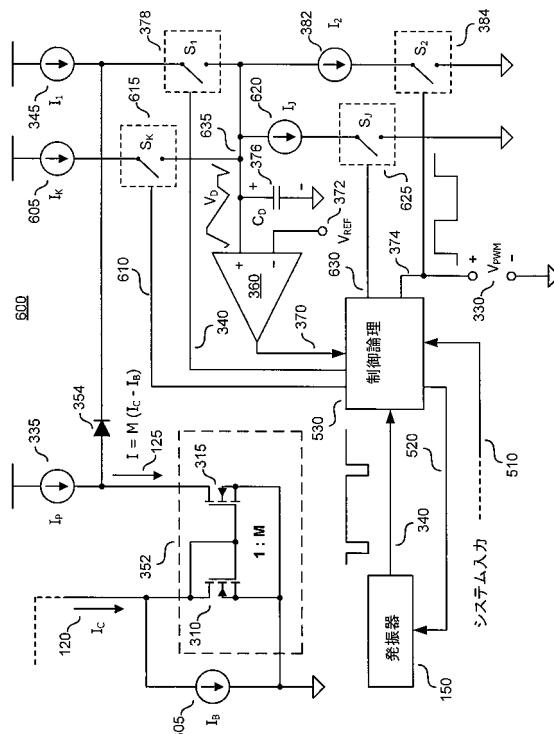

図5は、デューティ比制御回路500の例を示しており、本発明の教示によれば、制御論理530が、発振器150からのタイミング信号340、比較器360の出力370、システムからの他の信号510を受信し、発振器150を制御し、かつコンデンサ  $C_D$  376を充放電するスイッチ  $S_{1378}$  と  $S_{2384}$  のスイッチングを制御する。したがって、この例では、本発明の教示によれば、制御論理530により、パルス幅変調器信号330は、外部システムからのシステム入力510に応答して、その周波数とデューティ比を変化させることができる。

20

## 【0024】

図6は、追加のスイッチ  $S_{J625}$  と  $S_{K615}$  を含むデューティ比制御回路600の例示的な回路を示し、それぞれの電流源620と605が、コンデンサ  $C_D$  376を充放電するそれぞれの電流  $I_J$ 、 $I_K$ を有し、スイッチングは、本発明の教示による制御論理530に応答する。一例では、制御論理530により、信号610、630が、スイッチ  $S_K$  615と  $S_{J625}$  をそれぞれスイッチングする。制御論理530からの出力520により、比較器360の出力370の状態に従って、発振器150の周波数が変化する。

30

## 【0025】

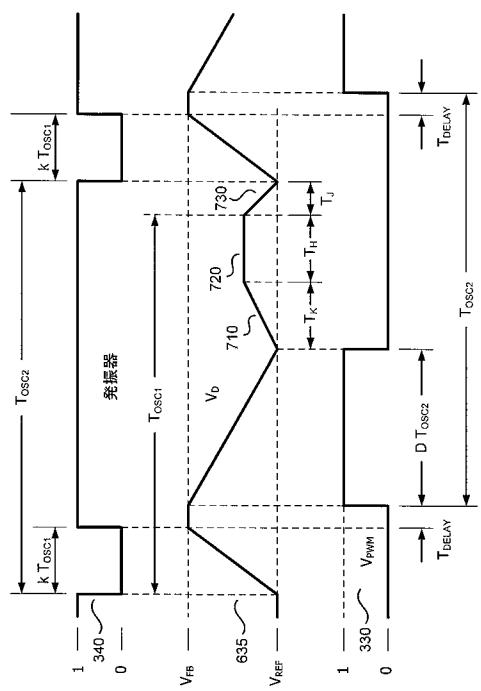

図7は、スイッチ  $S_K$  615と  $S_{J625}$  を使用してコンデンサ  $C_D$  376の充放電を変更する一例を示す。線分710は、スイッチ  $S_K$  615が閉じている間の時間  $T_K$  の間の、電圧  $V_D$  635の増大を示す。線分720は、すべてのスイッチが開いている間の時間  $T_H$  の間、 $V_{REF}$  と  $V_{FB}$  の間のある値で一定に維持される電圧  $V_D$  635を示す。線分730は、スイッチ  $S_{J625}$  が閉じている間の時間  $T_J$  の間に減少する電圧  $V_D$  635を示す。制御論理530は、比較器360の出力に応答して、発振器150の出力340が時間  $T_K$ 、 $T_H$ 、 $T_J$ の間HIGHのままとなるようにし、それにより、発振器150の周期を第1の値  $T_{osc1}$  から第2の値  $T_{osc2}$  に増大させる。したがって、パルス幅変調器は、複数の入力510に応答して、コンデンサ  $C_D$  376など、コンデンサを充放電するように、複数のスイッチと電流源を含むことができる。システムの必要に応じて、追加のスイッチと電流源により、制御電流  $I_C$  120に対するパルス幅変調器信号330の応答が修正されてもよい。

40

## 【0026】

要約書で述べられているものを含めて、本発明の、示されている諸例についての上記の説明は、網羅的なものでも、開示されているまさにその形態に限定するものでもない。本発明の特定の実施形態と例について例示のために本明細書で述べられているが、本発明のより広範な精神と範囲から逸脱することなしに、様々な均等な修正が可能である。さらによれば、特定の電圧、電流、周波数、電力範囲値、時間などは、説明のために提供されていること、他の値もまた、本発明の教示に従って、他の実施形態や例において使用することができることを理解されたい。

50

## 【0027】

これらの修正は、上記の詳細な説明に照らして、本発明の例に対して加えることができる。以下の特許請求の範囲において使用される用語は、本発明を、本明細書および特許請求の範囲において開示される特定の実施形態に限定すると解釈すべきではない。むしろ、その範囲は、以下の特許請求の範囲によって全体的に決定すべきであり、以下の特許請求の範囲は、確立されている請求項解釈の原則に従って解釈すべきである。したがって、本明細書および図は、限定ではなく、例示とみなすべきである。

## 【図面の簡単な説明】

## 【0028】

【図1】本発明の教示による例示的なデューティ比制御回路を示すプロック図である。

10

【図2】本発明の教示による例示的なデューティ比制御回路のパルス幅の変調器回路の応答を示すグラフである。

【図3】本発明の教示による、図2のグラフの応答を生成する例示的なデューティ比制御回路を示す概略図である。

【図4】図3のデューティ比制御回路の信号のタイミング関係を示す図である。

【図5】本発明の教示によるデューティ比制御回路を示す概略図である。

【図6】本発明の教示による他のデューティ比制御回路を示す他の概略図である。

【図7】本発明の教示による図6のデューティ比制御回路の信号のタイミング関係を示す図である。

## 【符号の説明】

20

## 【0029】

100 デューティ比制御回路、102 電源、110 パルス幅変調器回路、120 制御電流  $I_c$ 、130 パルス幅変調信号、140 タイミング信号  $U_{SOC}$ 、150 発振器

【図1】

【図2】

【 义 3 】

【 図 4 】

【 図 5 】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100109162

弁理士 酒井 將行

(74)代理人 100111246

弁理士 荒川 伸夫

(72)発明者 ツアオ - ジュン・ワン

アメリカ合衆国・95132・カリフォルニア州・サンノゼ・モリル アベニュー・1281

審査官 吉田 隆之

(56)参考文献 特開平9-23641 (JP, A)

特開昭63-305755 (JP, A)

特開平5-91418 (JP, A)

特開2005-185052 (JP, A)

特開2005-185053 (JP, A)

特開2006-191250 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K 7