### ${\bf (19)}\ World\ Intellectual\ Property\ Organization$

International Bureau

### ) | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1881 | 1

(43) International Publication Date 17 August 2006 (17.08.2006)

**PCT**

# (10) International Publication Number WO 2006/085326 A2

- (51) International Patent Classification: *B01D 63/00* (2006.01)

- (21) International Application Number:

PCT/IL2006/000179

(22) International Filing Date:

12 February 2006 (12.02.2006)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

60/650,861

10 February 2005 (10.02.2005) US

- (71) Applicant (for all designated States except US): SIANO MOBILE SILICON LTD. [IL/IL]; 6 Hagavish Street, Poleg Industrial Park, Netanya South, 42507 Netanya (IL).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): JASHEK, Ronen [IL/IL]; Netanya (IL). OREN, Roy [IL/IL]; Netanya (IL). IRONI, Alon [IL/IL]; Netanya (IL). MEIRI, Dror [IL/IL]; Netanya (IL).

- (74) Agents: EITAN LAW GROUP et al.; P.O. Box 2081, Industrial Zone, 46120 Herzlia (IL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(57) Abstract: A receiver is provided, which is adapted to receive MPE-FEC frames and to correct erroneous sections within a received MPE-FEC frame by detecting unreliable sections and storing in an erasure structure list ("ESL") table compressed data that includes the base address of each detected erroneous section, together with the respective section's size. The size of the ESL table may be fixed, or it may correlate, or dynamically change according, to the actual number of detected erroneous sections. The data stored in the erasure structure list may then be forwarded to a decoder to correct erroneous sections. The erroneous sections may be detected by using CRC, and the decoder may be a Reed-Solomon decoder. If the application data table of the MPE-FEC is error-free (or full of errors), in which case the erasure structure list is empty (or full), this means that no FEC reception and error corrections are required, because there are no sections to correct in the first case and the decoder is incapable of correcting too many sections in the second case. Therefore, the receiving circuitry, or at least the decoder, may be disabled to save battery power.

# SYSTEM AND METHOD FOR MITIGATING MEMORY REQUIREMENTS DURING MPE-FEC PROCESSING

#### FIELD OF THE DISCLOSURE

[001] The present disclosure relates generally to the field of mobile digital devices. More specifically, the present disclosure relates to a system and method for saving memory space in handheld and mobile devices while receiving multimedia information or data, including television ("TV") broadcasts and the like, in particular while processing Internet Protocol ("IP") datagrams that are contained within multi-protocol encapsulation ("MPE") forward error correction ("FEC") frames.

#### **BACKGROUND**

[002] The capacity of multimedia services rendered is growing rapidly, side by side with communication standards that are being continuously formulated to adapt services to handheld, and in general to various mobile wireless services rendering devices.

[003] One aspect of the rapid growth of multimedia services capacity is that many handheld digital telecommunication and/or multimedia systems are designed for multitask applications, such as audio, video and graphics capabilities, television reception and modem capabilities. Exemplary systems and devices include, without limitation, cellular phones, palm-PCs, portable media players ("PMP"), digital video cameras and digital still cameras.

[004] In addition, the deployment of mobile devices with integrated support for the reception of digital TV signals is now a reality. Until now, the feasibility of such support

has been limited by several key factors such as power consumption, performance and size. Most attempts at addressing the handheld receiver market have been based on adapting existing home set-top box solutions to the demanding environment of mobile reception. Currently, there are devices capable of receiving TV broadcasts that conform to mobile digital video broadcast terrestrial ("DVB-T") standards. VI3270T digital TV Receiver by Visson Technologies Inc. is an exemplary device for receiving DVB-T broadcast. DVB-T was not originally designed for mobile receivers.

[005] The DVB-H ("H" standing for "handheld") standard, which is a complementary terrestrial multimedia broadcasting system designed especially for portable and mobile usage, utilizes a "time-slicing" process to reduce receiver power consumption, and multiprotocol encapsulation forward error correction ("MPE-FEC") to provide an additional layer of error correction. MPE-FEC utilizes what is known as a Reed-Solomon encoder. The Reed-Solomon encoder utilized in a DVB-H transmitter takes 191 data bytes and adds 64 parity bytes of redundancy. Additionally, the DVB-H transmitter calculates and transmits a cyclic redundancy check ("CRC") data in the MPE-FEC packet header, and the receiver recalculates it to flag the MPE-FEC packet content as unreliable if the CRC check fails. In general, CRC is an error-detection technique consisting of a test performed on each block or frame of data by both sending and receiving modems, or transmitters and receivers. The sending modem, or transmitter, inserts the results of its tests in each data block in the form of a CRC code. The receiving modem (or receiver) compares its results with the received CRC code and responds with either a positive or negative acknowledgment, which is equivalent, in the field of the present disclosure, to "reliable" or "unreliable" sections in the MPE-FEC table.

[006] If the MPE-FEC packet content is unreliable, the bytes in the packet are termed "erasure" symbols, and using erasure symbols allows the Reed Solomon decoder in the receiver to correct twice the number of data bytes that could be corrected if erasures symbols (also called herein just erasures or erasures information or data) were not used. In the case where erasures are used, the Reed-Solomon decoder can correct up to 64 bytes out of a 255-byte codeword. Otherwise it can correct up to 32 bytes out of 255 byte code words.

[007] One of the prime objectives of the "time-slicing" process is to reduce the average power consumption of the terminal and enable smooth service handover. "Handover" refers to a receiver seeking and using an alternative communication channel for receiving the same station in cases where the receiver fails to receive data/information due to poor communication path. Time slicing involves sending data in bursts using significantly higher instantaneous bit rate compared to the bit rate required if the data were transmitted using traditional streaming mechanisms. Using time slicing allows inactivating, such as by "shutting-down", the receiver for considerable amount of time; that is, most of the time the DVB-H receiver is in sleep mode, and it "wakes up" only to receive the required data packets. This saves considerable amount of power in the device. The time-slicing technology enables seamless handover between different DVB-H service networks. While in sleep mode, the DVB-H receiver can be woken up to search signals from neighbor networks or frequency bands or programs. Thus no additional hardware or double receivers are needed. Time slicing is more fully described in "Television on a handheld receiver - broadcasting with DVB-H", by the Digi-TAG - The Digital Terrestrial Television Action Group", and in "Mobile TV Forum" (website

www.mobiletv.nokia.com/resources/faq/), for example.. Each burst of transmitted data creates and transmits a data structure called MPE-FEC frame. The structure and processing of a MPE-FEC frame, a notion of which is given hereinafter, are defined by the DVB-H standard and in the implementation guide. Briefly, each MPE-FEC frame consists of two parts, the application data table, which may contain, for example, a portion of a video or audio transmission, and the error correction data table. The data in each table is arranged in sections, each of which may include one or more data bytes.

[008] By "IP datagram" is meant herein an ensemble of consecutive digital bytes that represent a portion of the (or the entire) transmitted information. IP datagrams may vary in length; that is, in the number of their constituent bytes. By "section" is meant an ensemble of consecutive IP datagrams. According to telecommunication standards, different sections in a given MPE-FEC table may have different length though, for the sake of simplicity, sections in a given frame are typically characterized by having the same size. For example, a section may consist of a single MPE-FEC column, or one and a half columns, and so on. Nevertheless, current standards limit the maximal length allowed for a section to four consecutive columns.

[009] One of the prime objectives of the "MPE-FEC" methodology is to improve the "channel-to-noise" ("C/N") ratio and Doppler performance in mobile channels, and to improve the receiver's tolerance to impulse interference. This is accomplished by using an additional level of error correction, FEC, at the MPE layer. By adding parity information (parity bits), calculated from the datagrams, and sending this parity data in separate (redundant) MPE-FEC sections, error-free datagrams can be output after MPE-

FEC decoding, despite possible very bad reception conditions. Time slicing, including its use for saving electrical power, and MPE-FEC are described, for example, in "DVB-H – Mobile TV" ("Imagination Technologies 2005"); "DVB-H architecture for mobile communications systems" (by Stuart Pekowsky and Khaled Maalej, Broadcast/Satellite Communications, April 2005, World Wide Web rfdesign.com); "Digital Video Mobile Broadcast (DVB-H) specification" (Digital Video Mobile Broadcast, June 30, 2005, World Wide Web cellular.co.za/technologies/dvb-h.htm); and in "Transmission System for Handheld Terminals (DVB-H)" (Digital Video Broadcasting, DVB Document A081, June 2004), herein incorporated by reference.

[0010] MPE-FEC data sections that are received by the receiver in each data burst are analyzed one section at a time, usually on-the-fly, by using a checksum calculation process that is based on a cyclic redundancy check ("CRC") technique to detect errors in them. If the CRC analysis indicates that a given MPE-FEC table includes one or more errors, then the receiver utilizes a Reed Solomon ("RS") decoder to correct the erroneous sections within the MPE-FEC table.

[0011] Conventionally, in order for a RS decoder in a receiver to correct MPE-FEC data sections, each section is marked either as an error-free (reliable) section or as an erroneous (unreliable) section, such as by storing in a memory a corresponding binary erasure flags (a binary value 0 or 1). More specifically, if a section is determined (by a CRC check) as an unreliable section, every byte of this section is marked as unreliable. Likewise, if a section is determined (by the CRC check) as a reliable section, every byte of this section is marked as unreliable. Therefore, conventionally, the entire MPE-FEC

table (every byte in the MPE-FEC table) is assigned either a reliable flag (binary value 1, for example) or an unreliable flag (binary value 0, for example). Therefore, the memory used for storing the reliable and unreliable flags has a size that is as large as the total number of bytes in the MPE-FEC table. Only after the processing (by the RS decoder) of the reliable and unreliable flags it may be determined whether a given section is reliable or not.

[0012] Because many MPE-FEC sections are typically contained in each MPE-FEC frame that is transmitted during a transmission burst, correcting MPE-FEC data sections traditionally requires a relatively large memory, as it needs to have up to [Number\_of\_rows] x [Number\_of\_columns] bits (for example, 255Kbits). Therefore, handling MPE-FEC sections in the traditional manner significantly enlarges the memory required for MPE-FEC handling by 12.5% (255Kbits out of 2Mbits).

#### **SUMMARY**

[0013] The following embodiments and aspects thereof are described and illustrated in conjunction with systems, tools and methods, which are meant to be exemplary and illustrative, not limiting in scope. In various embodiments, one or more of the above-described problems have been reduced or eliminated, while other embodiments are directed to other advantages or improvements.

[0014] According to the present disclosure, the memory requirement is mitigated by storing in an erasure structure list ("ESL") table in a receiver, on-the-fly, data relating substantially only to sections in an MPE-FEC frame that are marked by an error detection

means (a CRC estimator or calculator, for example) in the receiver as erroneous, or unreliable, sections.

[0015] As part of the present disclosure, a method is herein disclosed for mitigating memory requirements in a receiver during processing by the receiver of a section in application data residing within a multi-protocol encapsulation forward error correction ("MPE-FEC") frame. The method may comprise receiving the MPE-FEC sections and saving in an ESL table, per erroneous section, a linear address space related to that section if it is determined that the received section contains one or more errors. The linear address space may be defined as A+S, wherein A denotes the address of the first byte in the respective detected erroneous section, referred to hereinafter as an erroneous section base address, and S denotes the byte-wise length (in number of bytes), or size, of that section. A linear space of an erroneous section may be regarded as an association between the erroneous section base address and the byte-wise length of the section.

[0016] The step of storing linear address spaces in an ESL table may be repeated in respect of additional erroneous sections, each linear address space occupying one entry in the ESL table, and the linear address spaces may be, for example, ordered in the ESL table according to the order of the reception of the erroneous sections. For example, the linear address space associated with the first detected erroneous section may occupy a first entry, the linear address space associated with a second erroneous section may occupy the second entry, and so on. This way, essentially only data relating to erroneous sections (compressed data) are stored in the ESL table.

[0017] The transmitted MPE-FEC frame may include an encoded error correction data and a receiver may mute receiving elements and sections correcting elements if, after receiving the entire application data, the ESL table meets a predefined, pre-selected, dynamic, threshold or otherwise specified criterion. If, however, the ESL table does not meet any specified criterion, erroneous sections within the MPE-FEC frame may be corrected, as by a decoder, which may decode the encoded error correction data based on the linear address spaces stored in the ESL table. The ESL table may include an entry pointer for indicating to the receiver the address(es) of the erroneous sections within the MPE-FEC frame(s).

[0018] One such decoder used for correcting unreliable sections may be a Reed-Solomon ("RS") decoder, though other decoders may be used as well, provided that the transmitter transmitting the data utilizes a suitable encoder. In some embodiments the criterion for deciding whether to use the decoder may be based on the ESL table, such as whether the ESL is either empty or full. That is, if the ESL table is either empty or full, the decoder in the receiver may be inactivated to save power. Otherwise, the decoder will be employed to correct unreliable sections. Errors in the sections may further be detected as by using a CRC technique, though other techniques may be used as well. For example, a checksum method may be used.

[0019] A receiver is also disclosed herein. The receiver may include a receiving circuitry for receiving MPE-FEC type application data and encoded error correction data; an error detection means for detecting erroneous sections in the application data; a memory for storing therein at least received MPE-FEC type application data and encoded error

correction data; a decoder for correcting erroneous sections forwarded to it from the memory; an erasure structure list ("ESL") table for storing therein linear address spaces associated with erroneous sections; and a data processing unit. The data processing unit, or data processor, may: (i) accept from the error detection means indications for erroneous sections, an indication per erroneous section; and (ii) cause linear address space(s) of erroneous section(s) to be stored in the ESL table, based on these indications.

[0020] The data processing unit may further check, per each received MPE-FEC frame, the ESL table and mute the receiving circuitry and/or the decoder if the ESL meets a predefined criterion. In some embodiments of the present disclosure, the criterion may be the ESL table being either empty or full. The data processing unit may cause the decoder in the receiver to correct erroneous sections stored in the memory, based on the linear address spaces stored in the ESL. In some embodiments of the present disclosure the error detection means may utilize a CRC for detecting errors in the MPE-FEC sections.

[0021] In some embodiments the receiver may be a DVB-H type receiver. In general, the receiver may be any receiver adapted to receive and process error-correction data, or the like.

[0022] In addition to the exemplary aspects and embodiments described above, further aspects and embodiments will become apparent by reference to the figures and by study of the following detailed description.

#### BRIEF DESCRIPTION OF THE FIGURES

[0023] Exemplary embodiments are illustrated in referenced figures. It is intended that the embodiments and figures disclosed herein are to be considered illustrative, rather than restrictive. The disclosure, however, both as to organization and method of operation, together with objects, features, and advantages thereof, may best be understood by reference to the following detailed description when read with the accompanying figures, in which:

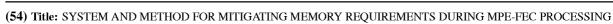

[0024] Fig. 1 schematically illustrates the general layout and functionality of the MPE-FEC related portion of a conventional DVB-H receiver circuitry capable of traditional handling of erasures;

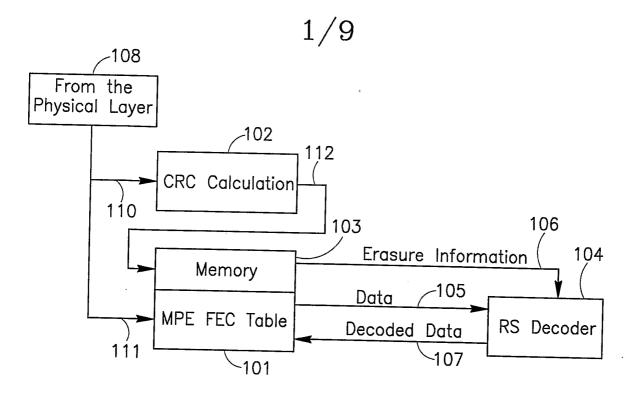

[0025] Fig. 2 schematically illustrates a typical DVB-H receiver;

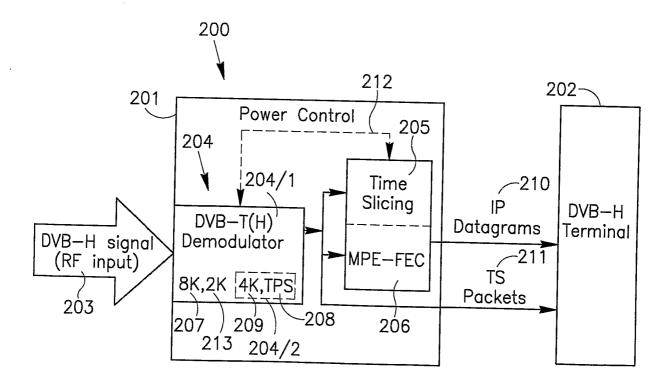

[0026] Fig. 3 schematically illustrates adding a mobile digital television ("MDTV") function to a mobile phone;

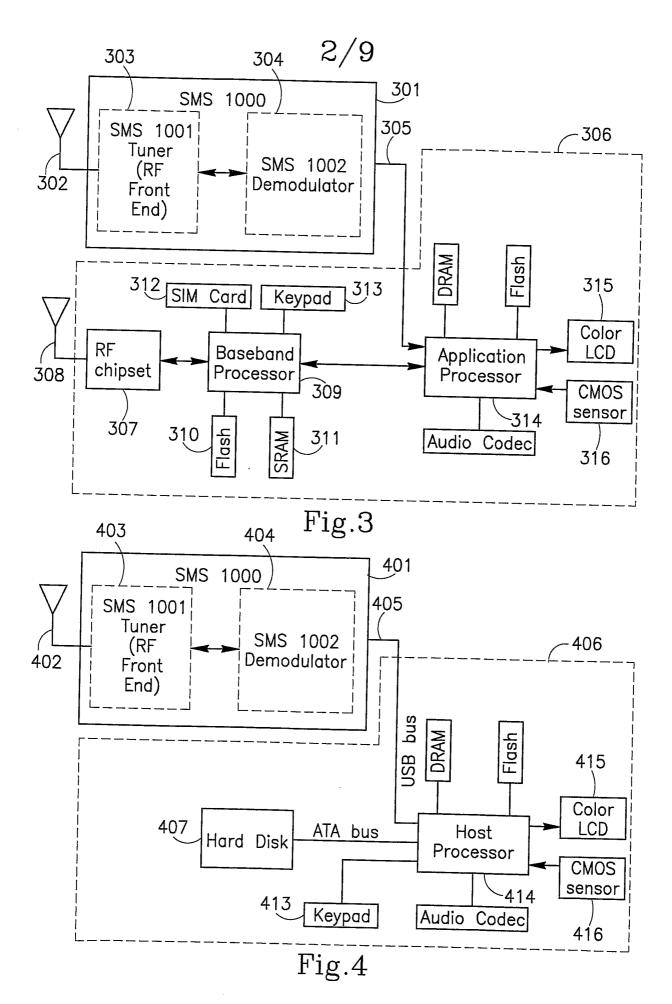

[0027] Fig. 4 schematically illustrates adding a MDTV function to a portable media player (PMP) system;

[0028] Fig. 5 schematically illustrates the structure of a MPE-FEC frame;

[0029] Fig. 6 shows in more details the application data table of Fig. 5;

[0030] Fig. 7 shows in more details the RS data table of Fig. 5;

[0031] Fig. 8 schematically illustrates the general layout and functionality of a DVB-H receiver, or modem, circuitry according to some embodiments of the present disclosure;

[0032] Fig. 9 is an exemplary flowchart for updating a fixed-size ESL table according to some embodiments of the present disclosure;

[0033] Fig. 10 is an exemplary flowchart for sending bytes and erasure flags to an RS decoder according to some embodiment of the present disclosure;

[0034] Fig. 11 is an exemplary flowchart for dynamically updating an ESL table according to some embodiments of the present disclosure;

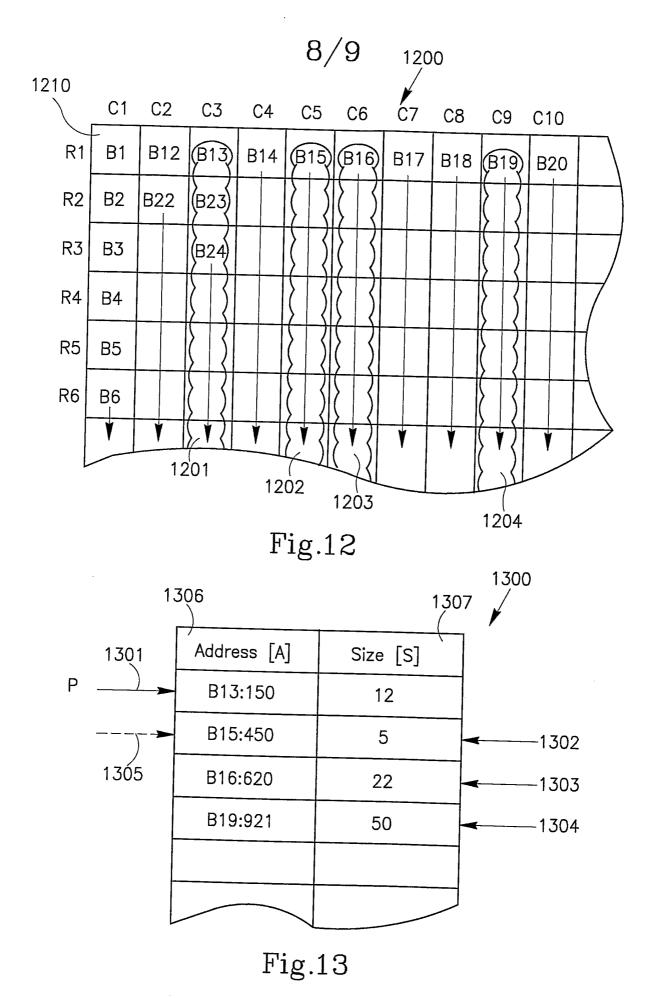

[0035] Fig. 12 schematically illustrates an exemplary partial MPE-FEC application data table;

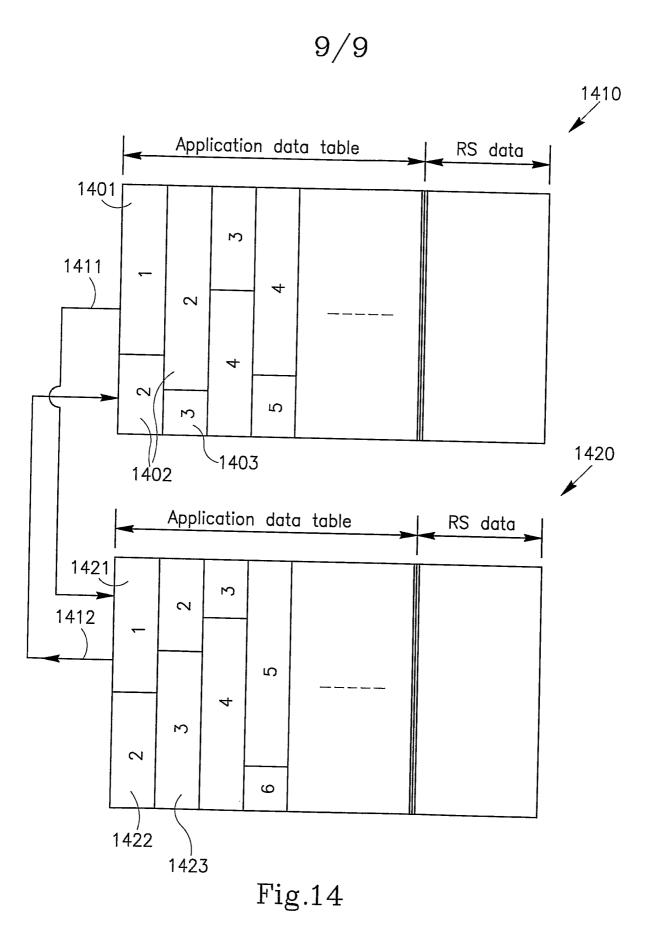

[0036] Fig. 13 schematically illustrates an exemplary partial content of an ESL table; and [0037] Fig. 14 schematically exemplifies simultaneous reception and processing of two MPE-FEC frames.

[0038] It will be appreciated that for simplicity and clarity of illustration, elements shown in the figures have not necessarily been drawn to scale. For example, the dimensions of some of the elements may be exaggerated relative to other elements for clarity. Further, where considered appropriate, reference numerals may be repeated within the figures to indicate like elements.

#### **DETAILED DESCRIPTION**

[0039] In the following detailed description, numerous specific details are set forth in order to provide a thorough understanding of the disclosure. However, it will be understood by those skilled in the art that the present disclosure may be practiced without these specific details. In other instances, well-known methods, procedures, components and circuits have not been described in detail so as not to obscure the present disclosure.

[0040] Unless specifically stated otherwise, as apparent from the following discussions, it is appreciated that throughout the specification discussions utilizing terms such as "processing", "computing", "calculating", "determining", or the like, refer to the action

and/or processes of a computer or computing system, or similar electronic computing device, that manipulate and/or transform data represented as physical, such as electronic, quantities within the computing system's registers and/or memories into other data similarly represented as physical quantities within the computing system's memories, registers or other such information storage, transmission or display devices.

[0041] The disclosure, its embodiments and its novel features, as well as items or according to the teachings, may take the form of an entirely hardware embodiment, an entirely software embodiment or an embodiment containing both hardware and software elements. In one embodiment, the disclosure is implemented in software, which includes but is not limited to firmware, resident software or microcode.

[0042] Embodiments of the present disclosure may include apparatuses for performing the operations described herein. This apparatus may be specially constructed for the desired purposes, or it may comprise a general-purpose computer selectively activated or reconfigured by a computer program stored in, or associated with, the computer.

[0043] Furthermore, the disclosure may take the form of a computer program product accessible from a computer-usable or computer-readable medium providing program code for use by or in connection with a computer or any instruction execution system. For the purposes of this description, a computer-usable or computer readable medium can be any apparatus that can contain, store, communicate, propagate, or transport the program for use by or in connection with the instruction execution system, apparatus, or device.

[0044] The medium may be an electronic, magnetic, optical, electromagnetic, infrared, or semiconductor system (or apparatus or device) or a propagation medium. Examples of a computer-readable medium include a semiconductor or solid state memory, magnetic tape, magnetic-optical disks, a removable computer diskette, a random access memory (RAM), a read-only memory (ROM), a rigid magnetic disk, an optical disk, electrically programmable read-only memories (EPROMs), electrically erasable and programmable read only memories (EEPROMs), magnetic or optical cards, or any other type of media suitable for storing electronic instructions, and capable of being coupled to a computer system bus. Current examples of optical disks include compact disk – read only memory (CD-ROM), compact disk – read/write (CD-R/W) and DVD.

[0045] A data processing system suitable for storing and/or executing program code may include at least one processor coupled directly or indirectly to memory elements through a system bus. The memory elements may include local memory employed during actual execution of the program code, bulk storage, and cache memories which provide temporary storage of at least some program code in order to reduce the number of times code has to be retrieved from bulk storage during execution. Input/output or I/O devices (including but not limited to keyboards, displays, pointing devices, or the like.) can be coupled to the system either directly or through intervening I/O controllers.

[0046] Network adapters may also be coupled to the system to enable the data processing system to become coupled to other data processing systems or remote printers or storage devices through intervening private or public networks. Modems, cable modem and

Ethernet cards are just a few of the currently available types of network adapters or the like.

[0047] The processes and displays presented herein are not inherently related to any particular computer or other apparatus. Various general-purpose systems may be used with programs in accordance with the teachings herein, or it may prove convenient to construct a more specialized apparatus to perform the desired method. At least one desired structure for a variety of these systems will appear from the description below. In addition, embodiments of the present disclosure are not described with reference to any particular programming language. It will be appreciated that a variety of programming languages may be used to implement the teachings of the disclosures as described herein.

[0048] Reed-Solomon ("RS") code is referred to throughout the description. Briefly, Reed-Solomon codes are block-based error correcting codes with a wide range of applications in digital communications and storage. Reed-Solomon codes are used to detect and correct data errors in many systems including; wireless or mobile communications (including cellular telephones, microwave links, etc), satellite communications, digital television / DVB, high-speed modems such as ADSL, xDSL, and so on. To use RS codes, a data stream is first broken into a series of code words. Each codeword may consist of several information symbols followed by several check symbols (also known as parity symbols, parity data or parity bits). Symbols can contain an arbitrary number of bits. Once data is received at a receiving end, the receiver's decoder checks for and corrects essentially all of the, errors. In cases where the number of errors exceeds the error correction capability of the decoder, the errors cannot be

corrected. More information on Reed-Solomon codes and on generator polynomials used for creating these codes may be found in "Reed-Solomon Codes: An Introduction to Reed-Solomon codes: principles, architecture implementation" (World Wide Web 4i2i.com/reed\_Solomon\_codes.htm), incorporated herein by reference.

[0049] Error correction decoding is often performed at least twice: the first time in respect of the physical layer and, the second time, in respect of the link layer (for example when evaluating errors in the MPE-FEC sections), and it might be performed also in the application layer. Reed Solomon code is typically used in conjunction with the DVB-H standard. However, in cases where other communication standards are, or will be, used (instead of, or in addition to, the DVB-H standard), other suitable coding techniques may be used as well, for example a coding technique known in the field as Turbo. In general, Turbo codes are a class of high-performance error correction codes finding use in deep-space satellite communications and other applications where designers seek to achieve maximal information transfer over a limited-bandwidth communication link in the presence of data-corrupting noise. More about Turbo codes may be found in the website http://en.wikipedia.org/wiki/Turbo\_coding. Alternatively, or additionally, any type of signal processing technique may be used, which is capable of removing at least some data errors caused by various types of communication interferences.

[0050] Referring now to Fig. 1, a received MPE-FEC section may be obtained from the physical layer 108, transferred (at 111) to and stored in MPE-FEC Table 101. Data is also transferred (at 110) to CRC Calculation unit 102, for allowing the analysis of the received

MPE-FEC section by CRC Calculation 102. If CRC Calculation 102 detects an erroneous, or unreliable, section (at 112) (which practically means that one or more errors exist in the received section), an indication of that fact is traditionally stored in a memory, such as memory 103, in respect of this section. If, however, CRC Calculation 102 does not detect errors in the MPE-FEC section, an indication of this fact is also traditionally stored in memory 103.

[0051] Data relating to erroneous and non-erroneous information or data, and/or to reliable and non-reliable data of the entire MPE-FEC table are forwarded (105) from MPE-FEC Table 101 to Reed-Solomon Decoder 104 alongside with related erasure information 106. Once Reed-Solomon Decoder 104 processes the entire MPE-FEC data forwarded to it (105), based on the related erasure information transferred to it (106), RS Decoder 104 sends (107) decoded data to MPE-FEC Table 101, to substitute therein erroneous sections with correct sections.

[0052] As stated hereinbefore, every section is traditionally assigned an erasure information, in the form of a binary marking flag(s), regardless of whether the section is a reliable section or not. This implies that, as is explained before, Memory 103 traditionally contains a corresponding binary flag (0 or 1) for every byte in the MPE FEC table, regardless of whether the byte is associated with a reliable or with an unreliable section. Since strives are constantly made to reduce the physical size of memory devices and other electronic components, it would have been beneficial to find a method that will allow to reduce the size of the memory (memory 103, for example) associated with, or required during the, processing of MPE-FEC sections by RS Decoder 104.

[0053] Fig. 2 is a block diagram of an exemplary structure of a DVB-H receiver. A DVB-H receiver typically includes a DVB-H demodulator 201 and a DVB-H terminal 202. DVB-H demodulator 201 typically includes, among the other things, a DVB-H demodulator (204) which includes a DVB-T demodulator 204/1 that is enhanced by additional functionality (marked as 204/1, for brevity), a time-slicing module (at 205) and an MPE-FEC module (at 206), the tasks of which are described hereinbefore and, additionally, hereinafter.

[0054] A DVB-H system (200) typically consists of service information and elements in the physical layer and in the link layer. DVB-H makes use of time slicing (at 205) and MPE-FEC (at 206) for the link layer, and DVB-H signaling, 8K-mode (at 207) and indepth symbol interleaver for the physical layer. DVB-H uses signaling in the Transmitter Parameter Signaling ("TPS") - bits (at 208) to enhance and speed up service discovery. Cell identifier is also carried on TPS-bits 208 to support quicker signal scan and frequency handover on mobile receivers. 4K-mode (at 209) is used by DVB-H system 200 for trading off between mobility and Single Frequency Network ("SFN") cell size, for allowing single antenna reception in medium SFNs at very high speed, adding thus flexibility in the network design.

[0055] In-depth symbol interleaver is used for the 2K and 4K-modes (213 and 209, respectively) for further improving robustness in mobile environment and impulse noise conditions. To provide DVB-H services, time slicing (205), cell identifier and DVB-H signaling (208) are mandatory, whereas other technical elements may be combined arbitrarily, according to specific needs. It is noted that the payload of DVB-H is Internet

Protocol ("IP") – datagrams (210) or other network layer datagrams encapsulated so as to form, or create, MPE-sections.

[0056] A Transport Stream ("TS") may contain data relating to video, audio, teletext, service information, conditional access information, and so on. Transport Stream consists of TS packets (211). Each packet of TS packets 211 is 188-byte long and contains a header and a payload section. The header of each TS packet 211 contains information about the contents of that packet and is intended for a TS de-multiplexer (not shown) in DVB-H terminal 202. The payload section contains the actual audio, video, teletext, and the like, data. The header typically starts with a synchronization word that is used for recognizing the start of the TS packet. Two bytes may follow the synchronization word, which contain some flags and the Packet ID ("PID").

[0057] The input signal to DVB-H demodulator 201 is a DVB-H signal (203) that includes time-sliced radio frequency ("RF") signal. As explained hereinbefore, time slicing involves sending data in bursts using a significantly higher bit rate compared to the bit rate required if the data were transmitted continuously. Within each data burst, the time to the beginning of the next burst ("delta-t") is indicated. At "off-time", which is the time between two consecutive time-sliced bursts, data relating to the elementary stream is not transmitted for allowing other elementary streams to use other allocated bit rates. This feature enables a demodulator to stay active for only a fraction of the time, during which time it may receive data bursts relating to a requested service. If a constant low bit rate is required at the handheld terminal 202, the received data bursts (203) may be buffered to meet this requirement.

[0058] A data burst creates a data structure called a MPE-FEC frame. For demodulator 204, which is designed to support FEC, the size of the MPE-FEC frame (sometimes referred to as "table") is typically 2 Mbits. A demodulator which does not require having MPE-FEC capabilities typically requires a smaller table (a table of up to about 1.5Mbits). During the processing (by MPE-FEC module 206) of data residing within MPE-FEC frame, the integrity of the entire data in the table, or at least the integrity of most of the data in the table, should be maintained. The MPE-FEC frame and the way it is processed are defined in the DVB-H standard and in the DVB-H implementation guide.

[0059] DVB-T demodulator 204 recovers Moving Picture Experts Group ("MPEG") - 2 TS packets (at 211) from the received signal 203, and forwards them (at 211) to DVB-H terminal 202 for display. DVB-T demodulator 204 offers three transmission / reception modes, 8K (at 207), 4K (at 209) and 2K (at 213). To each mode a corresponding Transmitter Parameter Signaling ("TPS") 208 is used. IP datagrams 210 include data that may be played by DVB-H Terminal 202. Time-slicing module 205 extracts from the RF signal demodulated by DVB-H demodulator 204 start and end instants of received data bursts (203) for synchronizing the processing of the MPE-FEC sections by MPE-FEC module 206. More about time-slicing, MPE-FEC, 4K mode and in-depth interleavers and DVB-H signaling may be found in "ETSI EN 302 304 v1.1.1" (2004-11), "Digital Video Broadcasting (DVB)" and in "Transmission System for Handheld Terminals (DVB-H)", the entire content of which is herein incorporated by reference.

[0060] As explained hereinbefore, MPE-FEC frames are transmitted in bursts so that the receiver, or parts thereof, can be shut down, or mute. Turning again to Fig. 2, the DVB-H

demodulator 204 may be mute (212) by Time Slicing 205 between each two consecutive MPE-FEC transmission bursts.

[0061] Referring now to Fig. 3, it shows a block diagram of a typical mobile digital television ("MDTV") demodulator (at 301), which may conform to the DVB-H standard, that is integrated with a mobile phone (at 306). A DVB-H signal may be received at antenna 302 and output by tuner 303 to demodulator 304 that may be a demodulator such as demodulator 201 of Fig. 2.

[0062] Exemplary mobile phone 306 is shown consisting of an RF chipset 307 for amplifying and filtering telephonic signals that may be received at antenna 308, and a baseband processor 309, which is coupled to Flash memory 310, serial random access memory ("SRAM") 311, SIM card 312 and keypad 313. Typical mobile phone 306 is also shown consisting of an application processor 314, which is coupled, among other things, to color liquid crystal display ("LCD") 315. Being exemplary mobile phone (at 306), each element unit or component therein may be substituted with a similar, or equivalent, element unit or component. For example, keypad 313 may be substituted with any suitable input device such as a keyboard, camera, touch screen, microphone, and so on. Likewise, display screen 315 is not necessarily color or LCD, and sensor 316 is not necessarily of the CMOS type.

[0063] MDTV demodulator 301 may forward (305) IP datagrams to application processor 314. If the IP datagrams are associated with television broadcast, then application processor 314 may generate from the IP datagrams a signal representative of

the television images and send the signal to color LCD 315 for display. By using keypad 313, for example, a user of the device may use the device as a telephone or as a television set to watch a television program on color LCD 315.

[0064] Referring now to Fig. 4, it shows a block diagram of a typical mobile digital television ("MDTV") demodulator (401), which may conform to the DVB-H standard that is integrated with a portable media player ("PMP") 406. A DVB-H signal may be received at antenna 402 and output by tuner 403 to demodulator 404 that may be a demodulator such as demodulator 201 of Fig. 2.

[0065] PMP 406 is shown comprising a hard disk (407) for storing various types of multimedia data, and a keypad (413). Typical PMP 406 is also shown comprising a host processor 414, which is coupled, among other things, to a color liquid crystal display ("LCD") 415. MDTV demodulator 401 may forward (405) IP datagrams to application processor 414. If the IP datagrams are associated with to a television broadcast, then application processor 414 may generate from the IP datagrams a signal representative of the television images and send the signal to color LCD 415 for display. By using keypad 413, for example, a user of the device may use the device as a multimedia player or as a television set to watch a television program on color LCD 415. Being exemplary portable media player (at 406), each element unit or component therein may be substituted with a similar, or equivalent, element unit or component. For example, keypad 413 may be substituted with any suitable input device such as a keyboard, camera, touch screen, microphone, and so on. Likewise, display screen 415 is not necessarily color or LCD, and sensor 416 is not necessarily of the CMOS type.

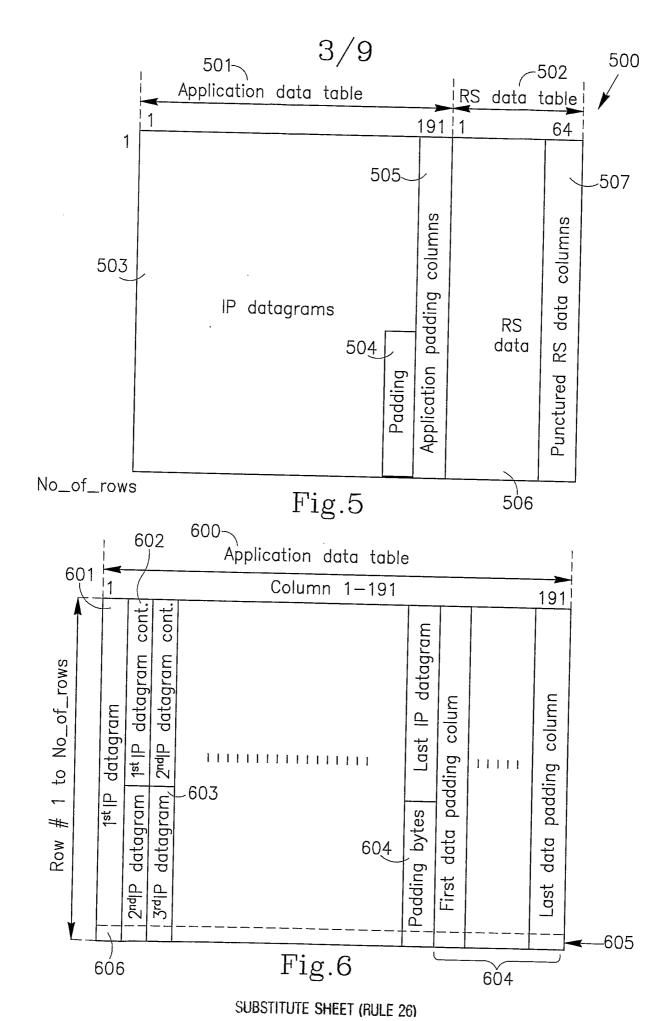

[0066] Referring to Fig. 5, an exemplary general structure of a MPE-FEC frame 500 is shown, which is arranged as a matrix with 255 columns and a dynamic, or flexible number of rows. A typical MPE-FEC frame consists of an application data table (501) and a Reed-Solomon (RS) data table (502). The application data table (501) contains 191 columns (designated 1 through 191) that contain Internet Protocol (IP) datagrams 503 relating to a multimedia content being broadcasted. Depending on the byte-wise length of IP datagrams 503, padding bytes may have to be used to complete the designated number columns in table 501. For example, application data table 501 is shown containing one column partially padded (504) and additional padded columns (505).

[0067] RS data table 502 contains 64 columns (designated 1 through 64) that contain Reed-Solomon data 506 that may be used for correcting MPE-FEC sections. Depending on the number of erroneous MPE-FEC sections detected, some of the columns in RS data table 502 may include punctured RS data columns (507). An exemplary RS data table is shown in Fig. 7 (at 700).

[0068] The number of rows may vary from 1 to a value signaled, or indicated, in the "time\_slice\_fec\_identifier\_descriptor". In general, the time\_slice\_fec\_identifier\_descriptor announces to the receiver the use of time slice and optional MPE-FEC data in the way specified in EN 301 192 [3].. The maximum allowed number of rows in MPE-FEC frame is 1024, which makes the total MPE-FEC frame as large as 2Mb. Each entry in the matrix contains an information byte. RS data 506 are dedicated for the parity information of the FEC code. Each byte entry in the application data table 501 has an address ranging from 1 to 191 x no\_of\_rows. Similarly, each byte

position in the RS data table 502 has an address ranging from 1 to 64 x no\_of\_rows. Addressing in RS table 502 is redundant because section\_length and section\_number are known.

[0069] IP datagrams are transmitted one datagram at a time, starting with the first byte of the first datagram in the upper left corner of the matrix and going downwards the first column, as exemplified in Fig. 6. The bit-wise length of IP datagrams 503 may vary arbitrarily, according to the actual data content, from one IP datagram to another, depending on the transmitted information, or multimedia content. For example, the first IP datagram ("1st IP datagram") is shown occupying about a full column (601) and a half (602). Likewise, the third IP datagram ("3rd IP datagram") is shown occupying about one half of a column (603). After the transmission of one IP datagram ends, the transmission of a following IP datagram starts. If an IP datagram does not end precisely at the end of a column, it continues at the top of the following column. When all IP datagrams have been entered into the application data table 600, any unfilled byte positions (604) are padded with zero bytes, which make the leftmost 191 columns completely filled. The number of padding columns in each MPE-FEC frame is signaled dynamically (to the receiver) in the MPE-FEC section. This signaling is typically implemented by using eight dedicated bits.

[0070] Referring again to Fig. 6, a Reed Solomon decoder corrects data in application data table 600 one row after another. The Reed Solomon decoder typically processes a plurality of rows in an application data table such as application data table 600, one exemplary row, row 605, is shown in Fig. 6. Data byte 606, therefore, resides in column 601, row 606.

[0071] With all the leftmost 191 columns filled it is now possible, for each row, to calculate the 64 parity bytes from the 191 bytes of IP data (and possible padding bits). The code used for this purpose is a code known in the field as the Reed-Solomon code (255,191), with a field generator polynomial and a code generator polynomial as defined hereinafter. Each row, then, is associated with one RS codeword. Some of the rightmost columns of the RS data table may be discarded and, therefore, not transmitted, to enable "puncturing". The exact number of punctured RS columns may change from one MPE-FEC frame to another, and it does not need to be explicitly signaled to the receiver. The RS data table (502) is also filled with punctured RS columns, to completely fill the MPE-FEC frame, as schematically shown in Fig. 7.

[0072] Referring again to Fig. 7, there is schematically exemplified a RS data table (700). RS data table 700 is shown consisting of 64 columns (1 through 64), each column containing parity bytes that are associated with a respective FEC section. The process by which the RS decoder corrects sections includes, among other things, handling one row after another in the MPE-FEC table, such that for each row in the application data table 600 in Fig. 6, the RS decoder utilizes parity bytes in the corresponding row in the RS data table 700. In general, the RS decoder corrects rows in application data table 600 by utilizing parity bytes in the respective rows in the RS data table 700. For example, the RS decoder may correct the last row (605) in application data table 600 by utilizing the parity bytes in the corresponding (last) row (705) in RS data table 700. Portion 702 of RS data table 700 may contain punctured RS columns.

[0073] An exemplary code generator polynomial may be calculated by:

$$g(x) = (x + \alpha^{0})(x + \alpha^{1})(x + \alpha^{2}),...,(x + \alpha^{63})$$

where  $\alpha = 02$  in hexadecimal (HEX) value.

An exemplary field generator polynomial may be calculated by:

$$p(x) = x^8 + x^4 + x^3 + x^2 + 1$$

[0074] IP datagrams are encapsulated in MPE sections in the standard DVB manner, regardless of whether MPE-FEC measures are used or not. This renders the reception fully backwards compatible with receivers lacking MPE-FEC capabilities. Each MPE section carries a start address for the IP datagram, which is carried within the section. This start address indicates the byte position in the application data table of the first byte of the IP datagram and is signaled in the MPE header. The receiver will then be able to put the received IP datagram in the correct byte positions in the application data table and mark these positions as reliable for the RS decoder, provided that the CRC-32 indicates that the section is correct.

[0075] The last section of the application data table contains a "table\_boundary" flag for indicating the end of the IP datagrams within the application data table. If all previous sections within the application data table have been received correctly, the receiver does not need to receive any MPE-FEC (redundant) sections and, if time slicing is used, the

receiver can go to sleep mode without receiving and decoding RS data. In cases where MPE-FEC sections are received, the exact number of padding columns in the application data table is indicated (signaled using eight dedicated bits) in the section header of the MPE-FEC sections. The number of padding columns is needed only if RS decoding is performed. The parity bytes are carried in a separate, specially defined section type, with it's own indicator ("table\_id"). Parity bytes are similar to MPE sections and are named "MPE-FEC sections". The length of an MPE-FEC section is adjusted so that there is exactly one section per column. Punctured columns are not transmitted and not signaled explicitly.

[0076] The number of rows is signaled in the time\_slice\_&\_fec\_identifier\_descriptor but can also be determined from the "section\_length" of the MPE-FEC sections, because the payload length of these sections is equal to the number of rows. In this way, there is always exactly one section per column. The number of punctured RS columns can be calculated as 64 – "last\_section\_number", because the last\_section\_number indicator indicates the number of sections and therefore the number of columns.

[0077] The receiver introduces the number of application data padding columns with zero bytes, which is indicated dynamically by the MPE-FEC sections, and marks these MPE-FEC sections as reliable sections. If the receiver receives the table\_boundary flag correctly, it can also add any remaining padding bytes and mark these as reliable. Otherwise, these MPE-FEC sections will be regarded as unreliable, in the same way as other lost data. The receiver also introduces the number of punctured RS columns as

calculated from last\_section\_number. The actual data in the punctured RS columns are irrelevant, as all punctured data are considered unreliable.

[0078] MPE and MPE-FEC sections are "protected" by a CRC-32 code, which reliably detects almost all erroneous sections. Only a negligible number of erroneous sections will not be detected by the CRC-32 code. For every correctly received section belonging to the application data table or to the RS data table, the receiver seeks in the section header for the start address of the payload within the section and is then able to put the payload in the right position in the respective table. Note that MPE sections may optionally contain a checksum procedure instead of a CRC-32. However, CRC-32 is preferred over the checksum procedure. After employing the latter procedure, there still may be lost sections; that is, there may be sections that cannot be corrected. All correctly received bytes, including application data padding, can then be marked as reliable and all byte positions in the lost sections and in the punctured RS columns can be marked as unreliable in the RS decoding.

[0079] All byte positions within the MPE-FEC frame (application data table plus RS data table) are now marked as either reliable or unreliable. With such reliability (erasure) information, the RS decoder is able to correct up to 64 such unreliable bytes per 255-byte codeword. If there are more than 64 unreliable byte positions in a row, the RS decoder will not be able to correct anything and will therefore typically just output the byte errors without error correction. After completion of the RS decoding, the receiver will reliably know the positions of any remaining erroneous byte within the MPE-FEC frame. If an IP

datagram is only partly corrected, the receiver will be able to detect this and (optionally) to discard this IP datagram.

[0080] In addition to the CRC-32, the DVB-H's RS decoder also reliably detects erroneous TS packets. If the MPEG-2 demultiplexer discards erroneous packets, it could be configured not to build sections that are suspected as containing lost TS packets. In this way, only correct (reliable) sections would be built and the role of the CRC-32 would be to provide additional error detection functionality, which normally is not needed. Seldom, it may occur that the DVB-H RS decoder will fail to detect an erroneous TS packet, which also happens to have the right Program ID, and that an erroneous section therefore could be reconstructed. In these cases, the CRC-32 would discover such a section error.

[0081] By introducing a certain number of zero-valued application data padding columns in the rightmost part of the application data table (501), it is possible to make the code stronger, meaning that more actual errors could be corrected. For example, one may autocorrect the zeros and than use the error correction for the other non-zero bytes. These padding columns are only used for the calculation of parity bytes; that is, these padding columns are not transmitted. In the receiver they are reintroduced and marked as reliable for the RS decoder. With 127 padding columns, for example, there are 64 columns left for IP data. With the 64 parity columns the effective code rate of the code becomes half, which means that, effectively, the number of parity columns equals the number of data columns. Regarding tables 600 of Fig. 6 and 700 of FIG. 7, the effective code rate is 3/4 (which is a weaker code rate than a code rate of 1/2), because there are 64 columns in the

RS data table (700) as opposed to 191 columns in the application data table (600). However, the price for this is the effective codeword length being roughly decreased by 50%, since, instead of transmitting 255-byte long code words, only 128-byte long code words can be transmitted. The number of application data padding columns is dynamic and specified in the MPE-FEC sections. The allowed range of padding columns is 0-190.

[0082] An effectively weaker code may be achieved by puncturing. "Puncturing" is performed by discarding one or more of the last RS data columns. The number of discarded (punctured) RS columns may vary dynamically between MPE-FEC frames within the range 0 to 64, and can be calculated as 64 – last\_section\_number, except for cases where no RS columns are transmitted in which case there are 64 punctured columns. Puncturing will decrease the overhead introduced by the RS data and thus decrease the needed bit rate. The drawback of puncturing lies in that it is relatively a weaker code.

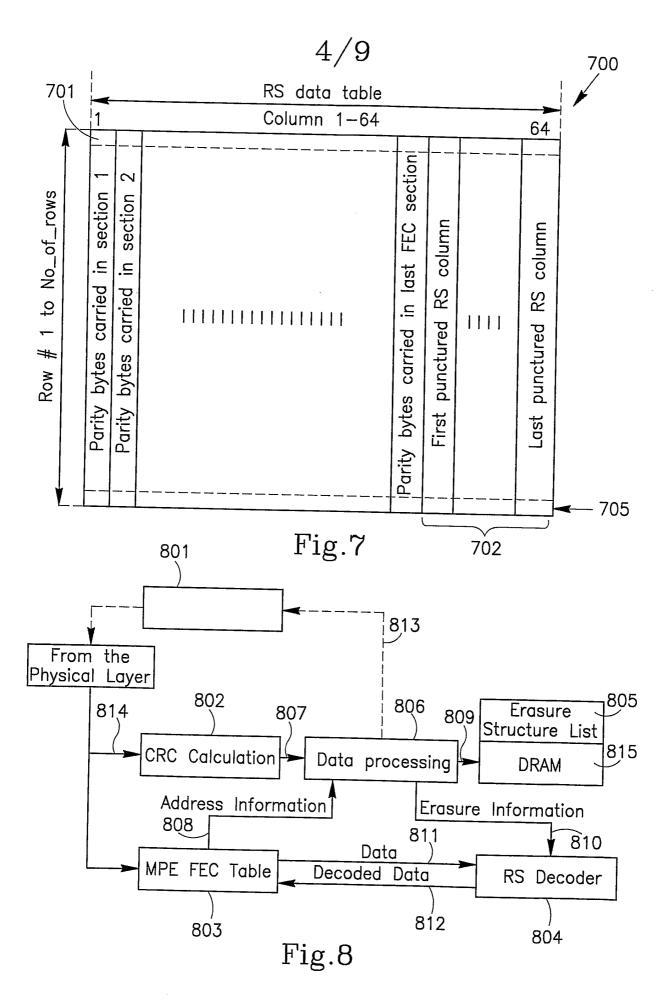

[0083] Referring now to Fig. 8, the general functionality and layout of the present disclosure is schematically illustrated. Receiving circuitry 801 may receive, among other things, MPE-FEC type application data and encoded error correction data. Receiving circuitry 801 may forward (814) application data to error detection means, such as CRC calculation 802, to detect (on-the-fly) erroneous sections in the application data. A memory, such as MPE FEC Table 803, may be used to store therein the content of a received MPE-FEC frame that contains application data and encoded error correction data. RS decoder 804 may correct rows with erroneous bytes that are forwarded (811) to RS decoder 804 from MPE FEC Table 803. In accordance with some embodiments of the

present disclosure, an Erasure structure list ("ESL") 805 is provided, which may be used for storing therein associations between the base address of each erroneous section, together with and size (bit-wise length) of the related section. For example, for a given erroneous section, Data processing 806 may receive (807) from CRC Calculation 802 an indication that the section is erroneous. Responsive to this indication, data processing unit 806 may cause (808) MPE-FEC Table 803 to forward to it (808) the relative address, or location, information of the base address of the erroneous section, and also the bit-wise length, or size, of the erroneous section (the total number of bytes in the erroneous section). Optionally, data processing 806 may seek for the section's address. Data processing 806 may then store (809) the first byte's address, or location, and also the number of bytes in the erroneous section, in ESL 805, by using direct random access memory ("DRAM") 815 or any other type of memory. The process of storing erroneous section base addresses and associated sections' size in ESL 805 may repeat, on-the-fly, for each received erroneous section.

[0084] As opposed to the prior art methods where substantially each byte in the entire MPE-FEC table is marked by a binary flag (0 or 1) and stored in a memory, according to the present disclosure only the base address (A) of each erroneous section, together with the number of bytes (S) in the respective section, are stored in a memory, shown as Erasure Structure List 805 in Fig. 8, for example. Therefore, by employing the principles disclosed in the present disclosure, a significant reduction is obtained in the size of the memory that is required for storing erasure related data. When comparing the prior art methods to the novel method disclosed herein, it might be said that the present disclosure teaches a way for compressing erasure-related data, whereby to facilitate reduction of

memory requirements. At the appropriate time, the compressed erasure-related data may be "decompressed" in order for it to be used by a decoder to correct erroneous sections.

[0085] After the reception of an entire MPE-FEC frame is completed, data processor 806 may cause (808) MPE FEC Table 803 to forward (811) to RS decoder 804 rows, one row at a time, and RS Decoder 804 to correct these rows based on corresponding erasure information that data processor 806 forwards (810) to RS Decoder 804. More specifically, Data processing unit 806 retrieves, or fetches, from ESL table 805 erasure data (linear address spaces) and translates the erasure data to corresponding binary flags, or marks, which are associated, per respective row in the application data table (600), with data bytes in corresponding rows. Then, Data processing unit 806 forwards (810) the resulting corresponding binary flags, or marks, to RS decoder 804, which utilizes the binary flags, or marks, to correct erroneous row(s) forwarded (811) to it. RS decoder 804 then forwards corresponding (corrected) decoded data (812) to MPE FEC table 803, to replace the erroneous row(s) with corrected row(s). Once the last erroneous row in the application data table (600) has been corrected by RS Decoder 804, a substantially error-free MPE-FEC table is obtained.

[0086] Data processing 806 may check, per received MPE-FEC frame, the content of ESL 805 and shut down, or mute, the receiving circuitry 801 and the decoder if the content of ESL table 805 meets a predefined criterion. The predefined criterion may be the ESL table 805 being either empty or full. The receiving circuitry 801 may be muted (813) by data processing 806 because if ESL table 805 is empty, this means that every received section is error-free and, therefore, there is no need to further receive encoded

error correction data. If ESL table 805 is full, this means that the number of the erroneous sections is too large for decoder 804 to correct and, therefore, there is no point in receiving the encoded error correction data. In other words, the encoded error correction data is useless in cases where the number of erroneous sections in a single frame is too large. CRC Calculation 802 may utilize a cyclic redundancy check ("CRC") technique for detecting erroneous sections, though other methods may also be used. A receiver exploiting the principles and method disclosed herein may conform to the DVB-H standard, though other standards, which may be devised in the future, whether they are modifications of the DVB-H standard or different communication standards, may exploit the principles and method disclosed herein.

[0087] According to some embodiments of the present disclosure, the size of the ESL table may be fixed. According to some other embodiments of the present disclosure, the size of the ESL table may dynamically change according, or correlate, to the actual detected unreliable (erroneous) sections.

#### Fixed size ESL

[0088] The fixed size ESL approach may be utilized in cases where the minimal size, or bit-wise length, of each of the MPE sections is at least as long as a column in the MPE FEC table. In such cases, the ESL table, for example ESL 805 shown in Fig. 8, may have a fixed size of 64 entries because a 65<sup>th</sup> unreliable MPE section and onwards (if such section(s) exist) will essentially render an MPE-FEC table uncorrectable.

[0089] Referring now to Fig. 13, each entry in the ESL table consists of two fields; A(1306), which is an address field allocated for addresses of unreliable sections, and S

(1307), which is a size field allocated for the size of the unreliable sections. The address field (1306) may be represented by 18 bits and its value may be calculated as follows:

$$A=C*NUM_OF_ROWS+R$$

(1)

where C is the current column number, NUM\_OF\_ROWS is the number of rows which form a single burst (defined also as a column size) and R is the current row number. For example, the byte located at the 51<sup>st</sup> row and 73<sup>rd</sup> column in a MPE-FEC table of 1024 rows will have the following linear address:

[0090] The maximal address in a 1024-row table is: 254\*1024+1024=261120. Alternatively, the base address (A) of an erroneous section may be the instantaneous value of an up counter that is reset at the MPE-FEC table first byte and auto-incremented for each received byte. The field S (1307) is represented by a number of bits that may be calculated as follows:

$$\log_2(\max imum\_size\_of\_a\_\sin gle\_MPE\_section)$$

(2)

For example, S (1307) may be represented by 12 bits to correspond to sections having a maximum length of 4Kbyte.

[0091] At initialization (after completing the processing of an MPE-FEC frame and before receiving the following MPE-FEC frame), all the entries in the ESL table are initially reset to a null value, for example to {A,S}={-1,-1}. The ESL table (ESL 805 of Fig. 8, for example) may be updated during MPE-FEC frame reception, starting from the first entry and possibly until the last entry and depending on whether errors are detected in the sections of the received MPE-FEC frame. If all the entries in the ESL table have a value other than the initial null value (for example, -1), the list is considered full. When all the entries still maintain their null value after completing the processing of the entire MPE-FEC frame, the list is considered empty.

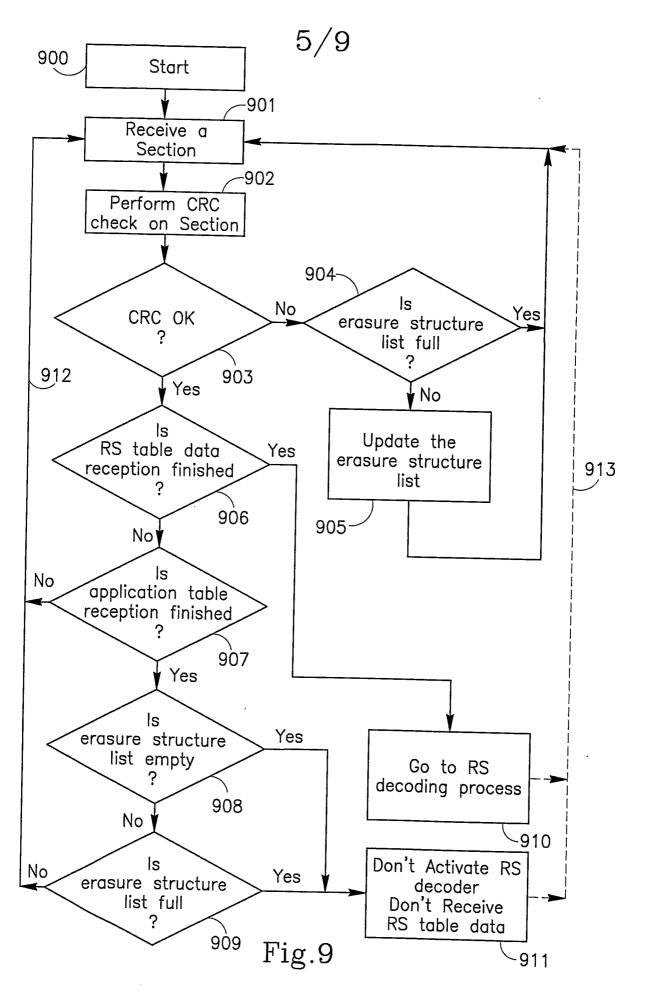

[0092] Reference will be made now to Figs. 9, 12 and 13. Fig. 9 schematically illustrates an exemplary process for handling a fixed-size ESL and a MPE-FEC table according to some embodiments of the present disclosure, whereas Fig. 12 shows an exemplary MPE-FEC table. In Fig. 9, control is transferred from START 900 to Receive a section 901 for each MPE section that is received by the receiver. Each received MPE section is CRC'd (CRC is calculated for the section) at step 902 to detect errors in the MPE section (if errors exist). If the CRC detects an error in the section, it means that the entire MPE section is unreliable (erroneous). In other words, a CRC check can tell whether the entire section is erroneous or not without knowing how many errors there are in the checked MPE section and how the errors are distributed in the MPE section. Therefore, if an erroneous MPE section is found, the ESL table is checked (at 904). If the ESL table is not full, the ESL table is updated (at 905), that is, the starting section's linear address in the MPE-FEC frame and the section's size (associated to one another) are stored in the ESL table. For example, an erroneous section may consist of bytes B13, B23, B24 and so on

(the bytes designated as 1201, Fig. 12) and its staring (base) address (the exemplary linear address, 150, of its exemplary first byte B13) and the section's size in bytes, 12 in this example, may be registered in the ESL table. If section 1201 (Fig. 12) is the first detected erroneous section, its staring address, 150 (in this example), and byte size, 12 (in this example), will form the first non-null value in the ESL table, as exemplified in Fig. 13.

[0093] If the ESL table is full, or overflows, and additional erroneous sections are detected (by the CRC checks, at step 903), the ESL table is not updated anymore and additional sections are received (at 901) and processed (to seek for error(s) therein). Nevertheless, CRC calculations may continue even though the ESL table overflows, in order to support other processes relating to signal quality diagnostics and reports, for example.

[0094] ESL table 805 of Fig. 8 (similar to table 1300 of Fig. 13) does not contain any data relating to reliable sections, a feature that saves a considerable amount of memory space in the ESL (and thus in the receiver). In accordance with the principles disclosed in the present disclosure, and assuming that the minimal sections' size is a single column, a typical size of the ESL table may be as large as about 2 Kbits, as opposed to up to 256 Kbits in traditional receivers. In general, the more columns constitute the sections, the smaller the memory capacity that is required for storing erasure information. For example, for minimal sections' size of two columns the maximal size of the ESL table is half the size of one-column-size sections (1 Kbits in the latter case, as opposed to 2Kbits).

[0095] Because sections of the application data of the MPE-FEC are received before the Reed-Solomon ("RS") sections, the RS table remains empty as long as the sections of application data are being received. Therefore, step 906 is skipped during the reception of the application data.

[0096] According to step 907 of Fig. 9, if all of the MPE sections in a same MPE-FEC frame that correspond to the application data (the portion of the MPE-FEC table representing the information data) have been received, the ESL table is checked again (908). If, at this stage, the ESL table is still empty, this means that all of the IP datagrams in all of the sections are reliable. Therefore, the receiver may send the IP datagrams to a host (after IP filtering) and switch over to "sleep" mode of operation (911) until the next burst (new MPE frame) is received, for which loop 913 may iterate as sections of the new MPE frame are received one section after another. By "host" is generally meant a processor that accepts IP datagrams from a DVB-H decoder. Essentially, these IP datagrams are forwarded to the host from the MPE-FEC table, such as MPE FEC Table 803. By "sleep mode" is generally meant muting, or shutting down, all, or pre-selected, circuit and/or software elements that are responsible for receiving and/or processing data bursts, and possibly additional circuit elements (a decoder, for example) that are responsible for correcting erroneous sections. However, this type of "sleep mode" should not be confused with the traditional "sleep" mode. The traditional sleep mode involves entering that mode only between each two consecutive MPE-FEC frames. In contradistinction, according to the present disclosure, the receiver may enter a sleep mode at other instances within each MPE-FEC frame, in accordance with the content of the ESL table, as described herein. The receiver may switch over to sleep mode because

there is no need for the receiver to receive the RS table data and to activate the RS decoder (911), because all of the IP datagrams in all of the sections are reliable (error-free). As was explained hereinbefore, the RS table data is the portion of the MPE-FEC frame that corresponds to the parity data; the data used to correct erroneous MPE sections.

[0097] The receiver may also enter into a sleep mode of operation (at 911) if the ESL table overflows (according to step 909 of Fig. 9). A ESL table is said to overflow if all of its 64 entries already have a value other than the initial null value and there is an attempt to add error-related data to the already exhausted ESL table. An overflowing ESL table means that essentially all RS code words contain at least 65 unreliable bytes and therefore the RS decoder is incapable of correcting the erroneous sections/IP datagrams. Therefore, if the ESL table is full, which is often an indication of table overflow, there is no point in receiving the RS table data and in activating the RS decoder (911). In the latter case, the receiver sends the detected reliable IP datagrams (if there are any) to the host (after IP filtering) and goes to "sleep mode" until receiving the next data burst. Although the MPE-FEC is uncorrectable in this particular case, diagnostics and reports on the number of CRC failures can be generated and possibly sent to the host for further processing, monitoring and for statistics calculations. If an ESL table is full (the ESL table contains 64 entries that contain non-null data) but the ESL table does not overflow, then the MPE frame involved is correctable. However, an overflowing ESL table (65 or more errors were found) implies that the associated MPE frame is not correctable.

[0098] In some embodiments of the present disclosure, the receiver may be allowed to receive two or more consecutive frames and only then enter into a sleep mode of operation. In some other embodiments the receiver may be allowed to receive two or more consecutive frames in parallel and only then enter into a sleep mode of operation. In such cases, another frame may be received before the previous frame's reception has finished. In some other embodiments the receiver may be allowed to receive two or more consecutive frames one after another and only then enter into a sleep mode of operation. In such cases, another frame may be received following reception of the previous frame.

[0099] After receiving all of the sections of the application data, and provided that the ESL table is neither empty nor full, the receiver may start receiving sections of the RS table. After all the RS table data is received (906) at the receiver, the entire ESL table may be checked once again because if the ESL table overflows now, there is no point in activating the RS decoder. If the ESL overflows, it means that essentially all of the RS code words contain more than 64 unreliable bytes and hence they are un-correctable. In this case, the receiver may send reliable IP datagrams to the host (after IP filtering) and go to "sleep mode" until it receives the next transmission burst. This means that the receiver does not employ, again, the RS decoder.

[00100] If the ESL table does not comply with the above described criterion; that is, the ESL table is neither empty nor full, this means that at least one of the code words in the received MPE-FEC sections is correctable and, therefore, the RS decoder may be employed at least once (at step 910). Accordingly, the receiver may process the MPE-FEC table row by row, as is described in connection with Fig. 10.

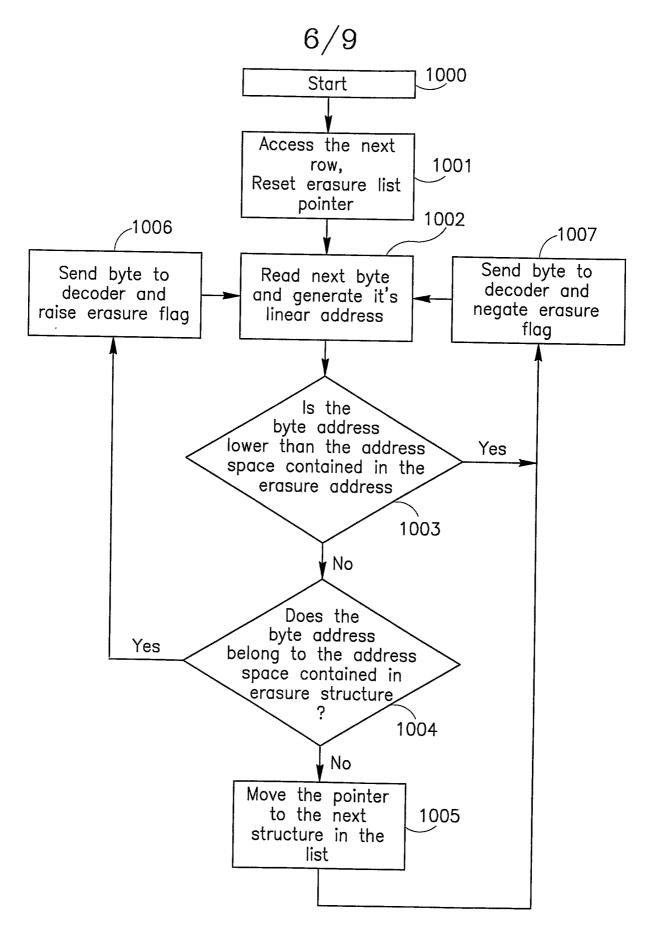

[00101] Referring now to Fig. 10, it shows the processing of rows of bytes in a MPE-FEC table. In general, each erroneous section, for example, section 1201 shown in Fig. 12, is indicated in the ESL table by having its linear address (the address of the first byte in the section) and size stored in the ESL table, as exemplified in Fig. 13. Therefore, the first entry of the ESL table indicates the first detected erroneous section, the second entry of the ESL table indicates the second detected erroneous section, and so on. It may occur that one or more reliable bytes in a given row will reside between two erroneous bytes, and the process illustrated by Fig. 10 is intended to locate the unreliable bytes and to send them to the decoder for rectification.

[00102] The following explanation refers to the first row in the received MPE-FEC table. However, all of the other rows in the MPE-FEC table may be handled in a similar manner. The way a row in a MPE-FEC table is processed according to the flowchart shown in Fig. 10 is hereinafter exemplified in association with Figs. 12 and 13.

[00103] Before starting processing rows in MPE-FEC frame 1200 (see Fig. 12), control is transferred from START 1000 to Access the next row 1001 to reset a pointer to the entries of the ESL for pointing to the first entry in the ESL table (shown as 1301 in Fig. 13). The first byte, "B1", in the first row (R1) is read and its linear address, A, is calculated, at step 1002, by using, for example, formula (1).

[00104] In the exemplary MPE-FEC frame (1200) and ESL table (1300), it is assumed, for the sake of the explanation, that each section is consisted of one column. For example, section 1201 is shown in Fig. 12 consisting of one column. It is also

assumed that four erroneous sections were detected by using CRC (upon their receipt by the receiver); sections 1201, 1202, 1203 and 1204. Therefore, the address of the first byte of each one of sections 1201 through 1204 is registered in the ESL table 1300. For example, pointer 1301 is shown pointing to the first entry of the ESL 1300, which contains the linear address (address 150) of the first byte (B13) of the first detected erroneous section 1201. Being the second detected erroneous section, the linear address of the first byte (B15) of section 1202 is shown registered in the second entry (1302) of ESL table 1300. ESL table 1300 contains additional third and fourth entries, 1303 and 1304, which correspond to the third and fourth detected erroneous sections 1203 and 1204, respectively.

[00105] The combination of a first (linear) address of the first byte in an erroneous section and the number of bytes in that section (section's size S in bytes), in a given entry in ESL table 1300 (for example, first linear address 150 and S being equal to 12 bytes) defines a "linear address space" for the corresponding section. For example, referring to the first entry (1301) of ESL table1300, which corresponds to the first detected erroneous section 1201, the linear address space for that section (1201) starts with the address 150 and includes all addresses up to the address 162 (150+12). Referring to the third entry of ESL table 1300, which corresponds to erroneous section 1203 and is shown pointed at by 1304, the linear address space associated with section 1203 starts with the address 620 and includes all addresses up to the address 644 (620+22). Linear address spaces may vary in size and shift in the addresses domain in accordance with the corresponding erroneous section(s), such that each entry in the ESL table 1300 will have a different linear address space, as exemplified in Fig. 13.

[00106] For the sake of the explanation, it is assumed that the calculated linear address of the first byte (B1) 1210 is 1. Accordingly, because the calculated linear address (1, for example) of the first byte (B1) is lower than the minimal address (150), in the first entry in the ESL, a condition that is checked at step 1003 in Fig. 10, it means that though errors were not detected in respect of this section, byte B1 is to be forwarded to the decoder, at step 1007 (in Fig. 10), together with an indication that this byte is surely reliable. That is, an erasure flag is not raised in respect of this byte. Then, the second byte (B12) of the same row R1 is read (at step 1002), and because its linear address is also lower than 150 (the first entry in the ESL table 1300), this byte is treated in the same way as byte B1, and the next byte (B13) of the same row R1 is read.

[00107] Because the linear address of byte B13 (linear address 150) is contained within, or belong to, the linear address space defined by 150+12 (see step 1004, Fig. 10), byte B13 is forwarded to the decoder with an indication to raise a corresponding erasure flag (at step 1006). Then, the next byte (B14) in the same row R1 is read (at step 1002). By "contained within, or belong to, the linear address space" is meant an address (linear\_address) that is calculated in respect of a currently read byte, which meets condition (3) for any positive i < 64, where i is the index, or the position of pointer 1301 in respect, of the entries of the ESL table 1300, and 64 refers to the discussed exemplary case:

$$Ai < linear address < Ai + Si$$

(3)

where Ai is the linear address of the first byte in a given section and Ai+Si is the address of the last byte in this section, the difference therebetween corresponding to the section size S, in number of bytes.

[00108] At this point, the pointer 1301 is still pointing at the first entry of ESL table 1300, and therefore to the linear address space, or range, defined by addresses 150 through 162 (150+12). Therefore, byte B14 has linear address (395, for example) that is not lower than the address (150+12=) 162 (step 1003), and it is not contained within the linear address space defined by addresses 150 through (150+12=) 162. Therefore, the pointer 1301 is moved so as to point at the next entry (1305) in the ESL table 1300, and, after checking whether byte B14 is contained or not in the linear address space related to entry 1302 in the ESL1300, byte B14 is forwarded to the decoder without raising an erasure flag.

[00109] If a given byte address is larger than anyone of the addresses defined by the corresponding linear address space (see step 1004, Fig. 10), this byte is considered reliable, and, since there is no point, at least not at this stage, in testing the rest of the bytes in, or belonging to, this row (because these bytes are not referred to, or included, in the ESL table), the pointer of the ESL table is incremented (moved) to point at the next entry in the ESL, at step 1005, and the current byte is checked again against the new linear address space created by the current entry in the ESL. If the current byte address being checked is smaller than (not resides within) the linear address space against which it is compared, or checked, then the current byte is sent to the RS decoder and an erasure flag is not raised, at step 1007. However, if the current byte address being checked

resides within the linear address space against which it is compared, the byte is sent to the RS decoder and an erasure flag is raised (from 0 to 1).

In a case where more than 64 unreliable bytes are detected in the same row and notified to the decoder (an erasure flag is raised for each unreliable byte), the decoder stops the decoding and skips to the next row. Otherwise, after decoding, the corrected codeword is written back into the MPE-FEC table memory, to override the original erroneous codeword. The latter process can be implemented in few different architectures or algorithms. However, the latter described implementation enables an efficient, low cost and low size implementation.

In accordance with the principles disclosed herein, the required memory size (Ms) for the ESL table equals the number of entries (Ne, an entry per section) multiplied by the sum of the address precision (Ap) and the size precision (Sp) in bits. By "address precision" is meant  $\log_2\{address\_domain\}$ , where address\\_domain refers to the entire address space of the MPE-FEC table. Assuming Ne=64 entries (one entry per column of a total of 64 entries in the RS data table 700 in Fig. 7), Ap=18 and Sp=12 bits as before, the required memory size is:

Ms= Ne \*

$$(Ap + Sp) = 64*(18+12)=1,920$$

bits (4)

[00112] Note that if the MPE section has a fixed length of one column (for example), which means that the size precision is 10 bits and not 12 bits, then the memory required for the ESL table is 64\*(18+10)=1,792 bits. If, according to another example,

the MPE section has a fixed length of 4 columns (which implies 64/4=16 entries), then the memory required for the ESL table is 16\*(18+12)=480 bits. If each section is consisted of 4 columns and there are more than 16 (rather than 64) erroneous sections, this means that there are more than 64 erasures, and hence the ESL table overflows.

[00113] When all the bytes of a currently processed row (row R1 in Fig. 12, for example), are checked in the way described hereinbefore, the ESL pointer 1301 is reset (moved to the first entry of the ESL table) and the bytes of the next row (row R2 in Fig. 12, for example) are read and processed, one byte after another, in the way described hereinbefore. This way, the entire rows of the MPE FEC table (for example MPE FEC table 1200 of Fig. 12) are processed, one row after another.

## Dynamically sized ESL table