(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-3389

(P2010-3389A)

(43) 公開日 平成22年1月7日(2010.1.7)

(51) Int.Cl.

G 1 1 C 29/50 (2006.01)

G 1 1 C 11/401 (2006.01)

F

G 1 1 C 29/00 6 7 1 M

G 1 1 C 11/34 3 7 1 A

### テーマコード（参考）

特開2010-3389

(P2010-3389A)

(21) 出願番号

(22) 出願日

特願2008-163499 (P2008-163499)

平成20年6月23日 (2008. 6. 23)

(71) 出願人 500174247

エルピーダメモリ株式会社

東京都中央区八重洲2-2-1

(74) 代理人 100123788

弁理士 宮崎 昭夫

(74) 代理人 100106138

弁理士 石橋 政幸

(74) 代理人 100127454

弁理士 緒方 雅昭

(72) 発明者 稲葉 秀雄

東京都中央区八重洲2-2-1 エルピー

ダメモリ株式会社内

F ターム (参考) 5L106 AA01 DD32 EE05 FF04 FF05

GG03

5M024 BB07 BB35 BB36 DD73 MM04

PP01 PP02 PP07

(54) 【発明の名称】半導体記憶装置および半導体記憶装置の試験方法

(57) 【要約】

【課題】アドレスを縮退した試験の際にも、 $t_{RCD}$ の実力を正確に評価することが可能な、半導体記憶装置の試験方法を提供する。

【解決手段】タイミングT1のアクティブコマンドの入力時、ロウアドレスがアドレスバッファに入力されるが、ロウデコーダは動作せず、ワード線は選択されない。ライトコマンドが入力されたタイミングT2では、カラムアドレスがアドレスバッファに入力されるが、カラムデコーダは動作せず、Yスイッチは選択されない。タイミングT3、T4に、バンクアドレス信号BA1をハイとしてアクティブコマンド、ライトコマンドを入力する。ロウデコーダは動作し、タイミングT1でラッチしたアドレスにてデコードされたワード線が選択され、タイミングT4では、Yスイッチが選択される。

【選択図】図 6

## 【特許請求の範囲】

## 【請求項 1】

ワード線とビット線とに接続されたメモリセルを有し、通常動作モードとテスト動作モードとを設定可能な半導体記憶装置であって、

前記テスト動作モード時に、

外部から入力されるアクティブコマンドに応じて、外部から入力されるロウアドレス信号の取り込みを行い、前記ワード線の選択は行なわない第1のロウ系動作を実行する手段と、

前記第1のロウ系動作の実行後に外部から入力されるアクティブコマンドに応じて、前記ロウアドレス信号の更新は行わずに前記ロウアドレス信号に対応する前記ワード線を選択する第2のロウ系動作を実行する手段と

を備えることを特徴とする半導体記憶装置。

## 【請求項 2】

複数の前記メモリセルを備える複数のバンクを有し、

外部から入力される信号であり、前記通常動作モード時には所定の前記バンクを選択するバンクアドレス信号を、前記テスト動作モード時には前記第1のロウ系動作と前記第2のロウ系動作とを切り替える信号として用い、

前記バンクアドレス信号が第1の論理レベルの場合、前記第1のロウ系動作を実行し、前記バンクアドレス信号が第2の論理レベルの場合、前記第2のロウ系動作を実行するよう構成される

ことを特徴とする、請求項1に記載の半導体装置。

## 【請求項 3】

前記ロウアドレス信号を保持すると共に、前記ロウアドレス信号をデコードして前記ロウアドレス信号に対応する前記ワード線を選択するロウデコーダ部を有し、

前記バンクアドレス信号が前記第1の論理レベルの場合、前記ロウデコーダ部が保持する前記ロウアドレス信号の更新を行い前記デコード動作は行わず、

前記バンクアドレス信号が前記第2の論理レベルの場合、前記ロウアドレス信号の更新は行なわず前記デコード動作を行う

ことを特徴とする、請求項2に記載の半導体記憶装置。

## 【請求項 4】

前記アクティブコマンドと前記バンクアドレス信号とを受けて、前記ロウデコーダ部の前記更新動作を制御する第1のロウ系制御信号と、前記ロウデコーダ部の前記デコード動作を制御する第2のロウ系制御信号とを前記ロウデコーダ部に供給するコマンドデコーダ部を有することを特徴とする、請求項3に記載の半導体記憶装置。

## 【請求項 5】

前記コマンドデコーダ部は、前記アクティブコマンドの活性化と前記バンクアドレスの第1の論理レベルとに応じて前記第1のロウ系制御信号を活性化し、前記アクティブコマンドの活性化と前記バンクアドレスの第2の論理レベルとに応じて前記第2のロウ系制御信号を活性化することを特徴とする、請求項4に記載の半導体記憶装置。

## 【請求項 6】

前記ロウデコーダ部が、前記ロウアドレス信号を保持するロウラッチ回路と、前記ロウラッチ回路に保持された前記ロウアドレス信号をデコードし前記ロウアドレス信号に対応する前記ワード線を選択するロウデコーダ回路と、を有することを特徴とする、請求項3から5のいずれか一項に記載の半導体記憶装置。

## 【請求項 7】

前記コマンドデコーダ部は、所定のアドレスを受けて前記半導体記憶装置が前記テスト動作モードであることを示すテストモード信号を活性化し、

前記テストモード信号が活性化している期間のみ、前記バンクアドレス信号の前記第1および第2の論理レベルに応じて、前記第1のロウ系動作または前記第2のロウ系動作を実行するように制御される

10

20

30

40

50

ことを特徴とする、請求項 4 から 6 のいずれか一項に記載の半導体装置。

【請求項 8】

外部から入力されるリードまたはライトコマンドに応じて、外部から入力されるカラムアドレス信号の取り込みを行い、前記ビット線の選択は行なわない第 1 のカラム系動作を実行する手段と、

前記第 1 のカラム系動作の実行後に外部から入力されるリードまたはライトコマンドに応じて、前記カラムアドレス信号の更新は行わずに前記カラムアドレス信号に対応する前記ビット線を選択する第 2 のカラム系動作を実行する手段と

を備えることを特徴とする、請求項 1 から 7 のいずれか一項に記載の半導体記憶装置。

【請求項 9】

複数 の前記メモリセルを有する複数のバンクと、

外部から入力される信号であり、前記通常動作モード時には所定の前記バンクを選択するバンクアドレス信号を、前記テスト動作モード時には前記第 1 のロウ系動作と前記第 2 のロウ系動作および前記第 1 のカラム系動作と前記第 2 のカラム系動作とをそれぞれ切り替える信号として用い、

前記バンクアドレス信号が第 1 の論理レベルの場合、前記第 1 のカラム系動作を実行し、前記バンクアドレス信号が第 2 の論理レベルの場合、前記第 2 のカラム系動作を実行する

ように構成されることを特徴とする、請求項 8 に記載の半導体装置。

【請求項 10】

前記カラムアドレス信号を保持すると共に、前記カラムアドレス信号をデコードして前記カラムアドレス信号に対応する前記ビット線を選択するカラムデコーダ部を有し、

前記バンクアドレス信号が前記第 1 の論理レベルの場合、前記カラムデコーダ部が保持する前記カラムアドレス信号の更新を行い前記デコード動作は行わず、前記バンクアドレス信号が前記第 2 の論理レベルの場合、前記カラムアドレス信号の更新は行なわず前記デコード動作を行う

ことを特徴とする、請求項 9 に記載の半導体記憶装置。

【請求項 11】

前記リードまたはライトコマンドと前記バンクアドレス信号とを受けて、前記カラムデコーダ部の前記更新動作を制御する第 1 のカラム系制御信号と、前記カラムデコーダ部の前記デコード動作を制御する第 2 のカラム系制御信号とを前記カラムデコーダ部に供給するコマンドデコーダ部を有することを特徴とする、請求項 10 に記載の半導体記憶装置。

【請求項 12】

前記コマンドデコーダ部は、前記リードまたはライトコマンドの活性化と前記バンクアドレスの第 1 の論理レベルとに応じて前記第 1 のカラム系制御信号を活性化し、前記リードまたはライトコマンドの活性化と前記バンクアドレスの第 2 の論理レベルとに応じて前記第 2 のカラム系制御信号を活性化することを特徴とする、請求項 4 に記載の半導体記憶装置。

【請求項 13】

前記カラムデコーダ部が、前記カラムアドレス信号を保持するカラムラッチ回路と、前記カラムラッチ回路に保持された前記カラムアドレス信号をデコードし前記カラムアドレス信号に対応する前記ビット線を選択するカラムデコーダ回路と、を有することを特徴とする、請求項 10 から 12 のいずれか一項に記載の半導体記憶装置。

【請求項 14】

前記コマンドデコーダ部は、所定のアドレスを受けて前記半導体記憶装置が前記テスト動作トモードであることを示すテストモード信号を活性化し、

前記テストモード信号が活性化している期間のみ、前記バンクアドレス信号の前記第 1 および第 2 の論理レベルに応じて、前記第 1 のカラム系動作または前記第 2 のカラム系動作を実行するように制御される

ことを特徴とする、請求項 11 から 13 のいずれか一項に記載の半導体装置。

10

20

30

40

50

**【請求項 15】**

外部から入力されるクロック信号の一方のエッジに同期した第1のクロックパルス信号と他方のエッジに同期した第2のクロックパルス信号とを発生するクロックジェネレータ部と、

外部から入力され前記メモリセルを選択するアドレスを前記クロック信号に同期して取り込むアドレスバッファ部と

を有し、

前記テストモード信号が非活性の期間は前記第1のクロックパルス信号にのみ同期して前記アドレスバッファ部が前記メモリセルを選択するアドレスを取り込み、

前記テストモード信号が活性の期間は前記第1のクロックパルスと前記第2のクロックパルス信号とに同期して前記アドレスバッファが前記メモリセルを選択するアドレスを取り込む

10

ことを特徴とする、請求項7に記載の半導体記憶装置。

**【請求項 16】**

前記第1のクロックパルス信号の活性または非活性状態が、前記バンクアドレス信号の論理レベルによって制御されることを特徴とする、請求項15に記載の半導体記憶装置。

**【請求項 17】**

ワード線とビット線とに接続されたメモリセルと、複数の前記メモリセルを有する複数のバンクとを有し、通常動作モードとテスト動作モードとを設定可能な半導体記憶装置において、アクティブコマンドが入力されてからリードまたはライトコマンドが入力されるまでの時間である $t_{RCD}$ を測定する前記半導体記憶装置の試験方法であって、

外部から入力されるアクティブコマンドに応じて、外部から入力されるロウアドレス信号の取り込みを行い、前記ワード線の選択は行なわない第1のロウ系動作工程と、

前記第1のロウ系制御動作後に外部から入力されるアクティブコマンドに応じて、前記ロウアドレス信号の更新は行わずに前記ロウアドレス信号に対応する前記ワード線を選択する第2のロウ系動作工程と

20

を備え、

外部から入力される信号であり、前記通常動作モード時には所定の前記バンクを選択するバンクアドレス信号を用いて、前記第1のロウ系動作と前記第2のロウ系動作とを切り替えを行い、

30

前記バンクアドレス信号が第1の論理レベルの場合、前記第1のロウ系動作工程が実行され、

前記バンクアドレス信号が第2の論理レベルの場合、前記第2のロウ系動作工程が実行される

ことを特徴とする半導体記憶装置の試験方法。

**【請求項 18】**

外部から入力されるリードまたはライトコマンドに応じて、外部から入力されるカラムアドレス信号の取り込みを行い、前記ビット線の選択は行なわない第1のカラム系動作工程と、

40

前記第1のカラム系動作工程の後に外部から入力されるリードまたはライトコマンドに応じて、前記カラムアドレス信号の更新は行わずに前記カラムアドレス信号に対応する前記ビット線を選択する第2のカラム系動作工程と

を備え、

前記バンクアドレス信号が前記第1の論理レベルの場合、前記第1のカラム系動作工程が実行され、

前記バンクアドレス信号が前記第2の論理レベルの場合、前記第2のカラム系動作工程が実行される

ことを特徴とする、請求項17に記載の半導体記憶装置の試験方法。

**【請求項 19】**

前記第1のロウ系動作工程の後に前記第1のカラム系動作工程が行われ、

50

前記第1のカラム系動作工程の後に前記第2のロウ系動作工程が行われ、

前記第2のロウ系動作工程の後に前記第2のカラム系動作工程が行われ、

前記第2のロウ系動作工程と前記第2のカラム系動作工程との間の時間を前記t R C Dとして測定する

ことを特徴とする、請求項17または18に記載の半導体記憶装置の試験方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ワード線とビット線とに接続されたメモリセルを有し、通常動作モードとテスト動作モードとを設定可能な半導体記憶装置に関する。

10

【背景技術】

【0002】

近年の半導体記憶装置に対しては、CPUによる処理の高速化に伴ってデータの書き込み／読み出し処理の高速化要求が高まっている。そのため、動作クロックの高速化だけでなく、あるコマンドを入力してから次にコマンドが入力可能になるまでの時間の短縮化が要求されている。

【0003】

このような、あるコマンド入力から次のコマンド入力までに所定の時間是有する例として、SDRAM (Synchronous DRAM) で用いられるアクティブコマンドの入力からデータを読み出すためのリードコマンドまたはデータを書き込むためのライトコマンドの入力が可能になるまでの時間t R C D がある。

20

【0004】

一般に、半導体記憶装置では、アクティブコマンドの入力からt R C D時間経過後にリードコマンドあるいはライトコマンドを入力し、該半導体記憶装置が正常に動作するかどうか否かを判定する試験（以下、この試験をt R C D試験と称す）が行われる。

【0005】

t R C D試験の方法としては、例えば、特許文献1に記載された方法がある。特許文献1の実施例1には、モードセットコマンド入力後のプリチャージコマンドP R Eの入力時にアクティブアドレスを入れ、また、実施例2では、アクティブコマンドA C Tに対し、コマンドP A C T（ロウアドレスラッチのみを行うコマンド）を入力することでもアクティブコマンドA C T時にはアドレスを入力せずにすむので、t R C Dのタイミングチェックができると記載されている。

30

しかしながら、特許文献1の実施例1の場合、アドレス全組み合わせチェック毎にモードセットコマンドとプリチャージコマンドを入力する必要があり、テスト時間が冗長となってしまう。また、特許文献1の実施例2の別コマンド入力とする場合、R A S, C A S, W E, C Sの組み合わせでコマンドを作ることになるが、残る組み合わせはC Sをロウ以外（ハイにしたときでの組み合わせ）しか残っていない。このため、特に、ウエハー試験のように複数のチップを同時にチェックするためにC Sをロウに固定している場合、特許文献1の実施例2の方法を実現することができない。

【特許文献1】特開2003-346497号公報

40

【発明の開示】

【発明が解決しようとする課題】

【0006】

ところで、上述のt R C D試験は、ウエハー選別試験の一環として行われている。そして、近年、ウエハー選別試験で同測数を増やすために、1チップに割り当てられるテスターのドライバーピンを削減するためアドレスをクロックC L Kの立ち上がり、立ち下がりの両エッジでラッチすることで、異なるアドレスを共通のドライバーピンから入力する（アドレス縮退）試験方法が提案されている。

【0007】

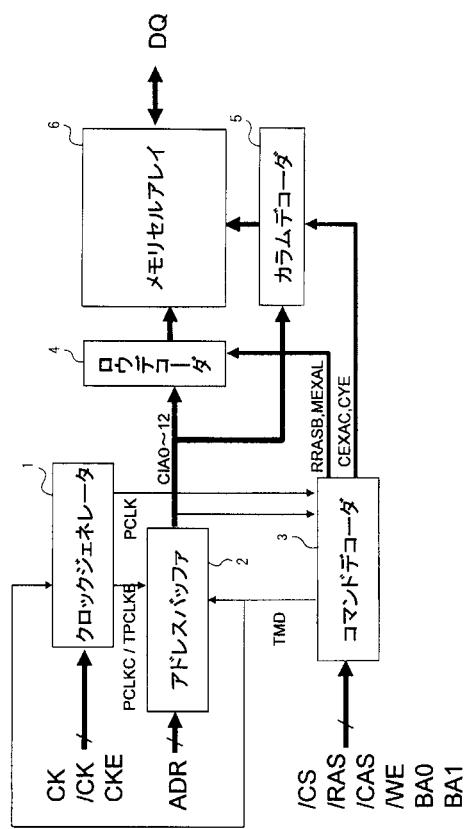

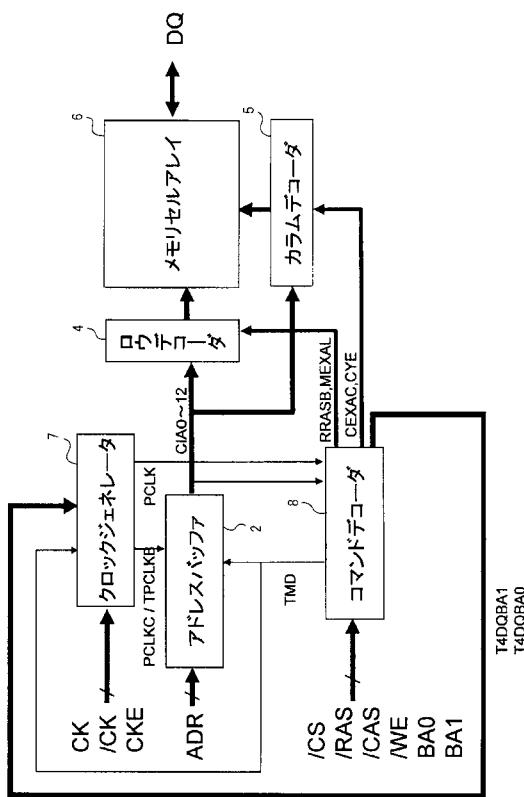

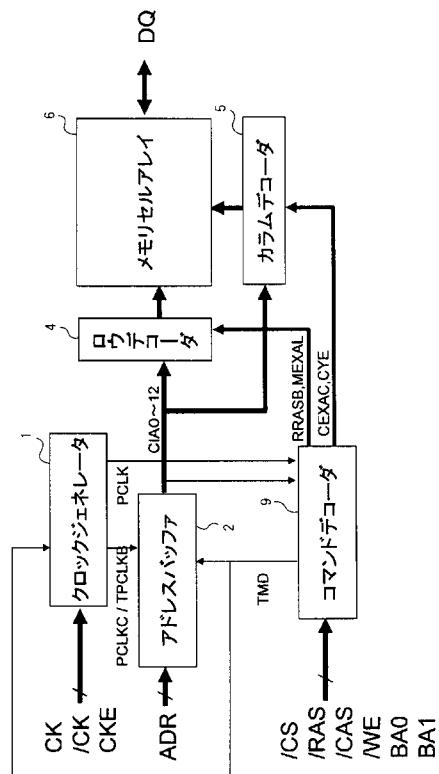

図11は、このようなt R C D試験が行われる半導体記憶装置のブロック図である。こ

50

の半導体記憶装置はクロックジェネレータ1とアドレスバッファ2とコマンドデコーダ9とロウデコーダ4とカラムデコーダ5とメモリセルアレイ6を有している。

【0008】

メモリセルアレイ6は、周知のメモリセルアレイと同一の構造であり、メモリセル、ワード線、ピット線、センスアンプ等を有する。また、所定のピット線のデータを外部に出力するためのYスイッチをも有する。所定のメモリセルの選択は、外部から入力されるロウアドレスに対応するワード線を選択し、外部から入力されるカラムアドレスに対応するピット線を選択する、つまり対応するYスイッチをオンすることで行なわれる。

【0009】

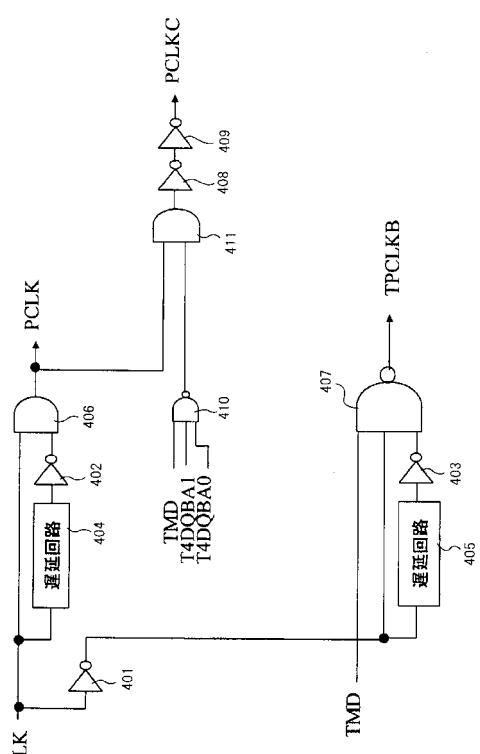

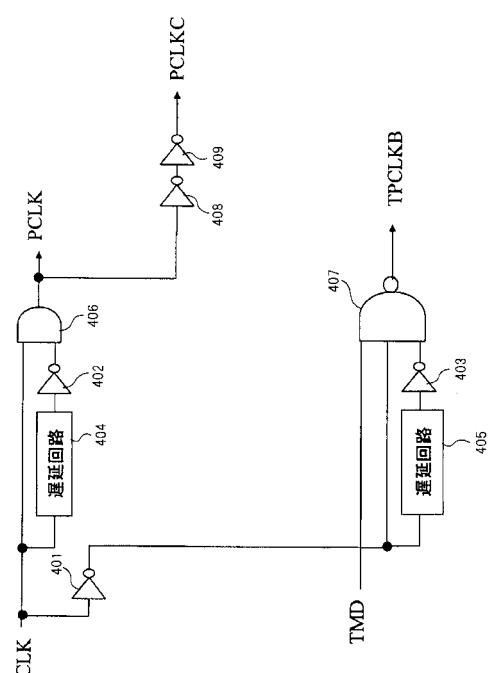

クロックジェネレータ1は、クロックCK、/CK、クロックイネーブル信号CKE、テストモード信号TMDを入力して、信号PCLK、PCLKC、TPCLKBを出力する。信号PCLKは、クロックCLKの立ち上がりエッジから作られるワンショット信号で、コマンド入力をラッチするパルスとして使われる。信号PCLKCもクロックCLKの立ち上がりエッジから作られるワンショット信号であるが、外部からアドレスバッファ2に入力されたアドレスをラッチするパルスとして使われる。信号の出力先であるアドレスバッファ2とコマンドデコーダ9が互いに離れているため、信号PCLKとは分離して信号PCLKCが出力される。信号TPCLKBはクロックCLKの立ち下がりエッジから作られるワンショット信号で、アドレスバッファ2に入力されたアドレスをラッチするパルスとして使われる。テストモード信号TMDは、tRCD試験のときハイになる信号である。図12に示すように、クロックジェネレータ1は、インバータ401～403と、遅延回路404、405と、ANDゲート406と、NANDゲート407と、インバータ408、409からなる。

【0010】

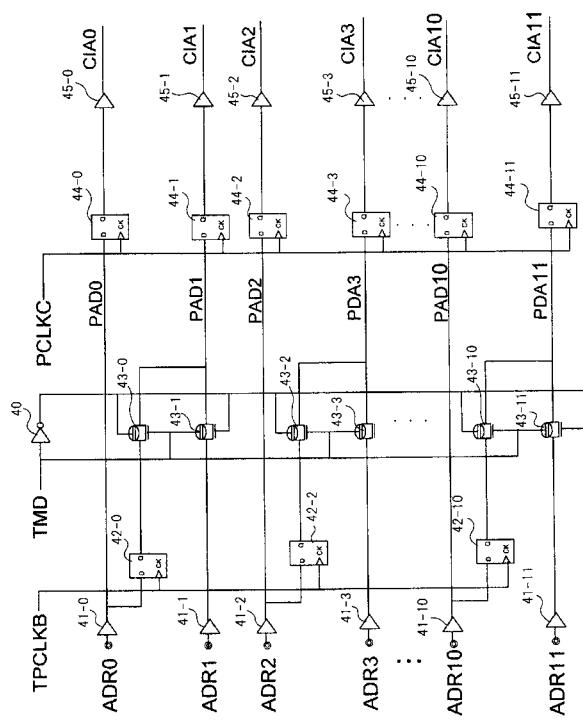

アドレスバッファ2は、12ビットのアドレスADRと、テストモード信号TMDと、信号PCLKC、TPCLKBを入力し、アドレス信号CIA0～CIA11を出力する。図13に示すように、アドレスバッファ2は、インバータ40と、バッファ41-0、41-1、…、41-11と、Dフリップフリップ42-0、42-2、…、42-10と、トランスマルチゲート43-0、43-1、…、43-11と、Dフリップフリップ44-0、44-1、…、44-11と、バッファ45-0、45-1、…、45-11を有している。通常動作時、テストモード信号TMDはロウであり、トランスマルチゲート43-0、43-2、43-10はオフ、トランスマルチゲート43-1、43-3、43-11はオンしている。したがって、アドレス端子ADR0、ADR1、…、ADR11から入力されたアドレス信号PAD0、PAD1、…、PAD11は信号PCLKCでそれぞれDフリップフロップ44-0、44-1、…、44-11にラッチされ、それぞれバッファ45-0、45-1、…、45-11を経てアドレス信号CIA0、CIA1、…、CIA11としてロウデコーダ4およびカラムデコーダ5に出力される。tRCK試験時、テストモード信号TMDはハイとなるため、トランスマルチゲート43-0、43-2、43-10はオン、トランスマルチゲート43-1、43-3、43-11はオフする。したがって、アドレス端子ADR0、ADR2、…、ADR10から入力されたアドレス信号は信号TPCLKBでそれぞれDフリップフロップ42-0、42-2、…、42-10にラッチされた後、それぞれトランスマルチゲート43-0、43-2、…、43-10を通過して信号PCLKCでDフリップ44-1、44-3、…、44-11にもラッチされる。すなわち、tRCK試験時には、偶数のアドレス入力端子ADR0、ADR2、…、ADR10からのみアドレスが入力されて、Dフリップ44-1、44-3、…、44-11にそれぞれDフリップフロップ44-0、44-2、…、44-10と同じアドレス信号がラッチされ、出力される。

【0011】

コマンドデコーダ9はチップセレクト信号/CS、ロウアドレスストローブ信号/RA S、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WE、バンクアド

10

20

20

30

30

40

40

50

レス信号 B A 0、B A 1、信号 P C L K と、アドレス C I A 0 ~ C I A 1 2 を入力し、テストモード信号 T M D、信号 R R A S B、M E X A L、C E X A C、C Y E を出力する。ここで、バンクアドレス信号が B A 0、B A 1 と 2 つなのは、図 1 1 の半導体記憶装置が 4 バンク構成であるからである。信号 R R A S B はアクティブコマンド A C T が入力されてからプリチャージコマンド P R E が入るまでの間ロウとなっている信号である。信号 M E X A L は、アクティブコマンド A C T が入力された際、そのとき入力されたアドレスをロウ系選択信号としてラッチするために使われる信号である。信号 C E X A C は、リード / ライトコマンドが入力された際、そのとき入力されたアドレスをカラム系選択信号としてラッチするために使われる信号である。信号 C Y E は、リード / ライトコマンドが入力された際、Yスイッチの選択時間として使われる信号である。

10

## 【 0 0 1 2 】

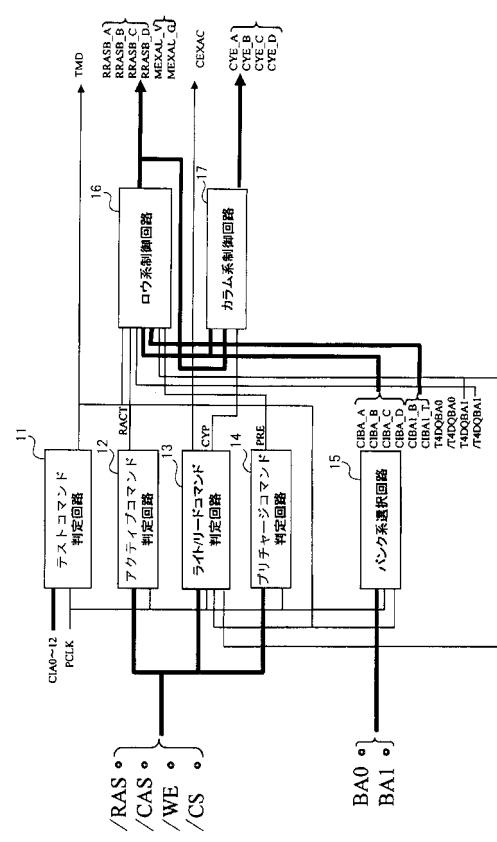

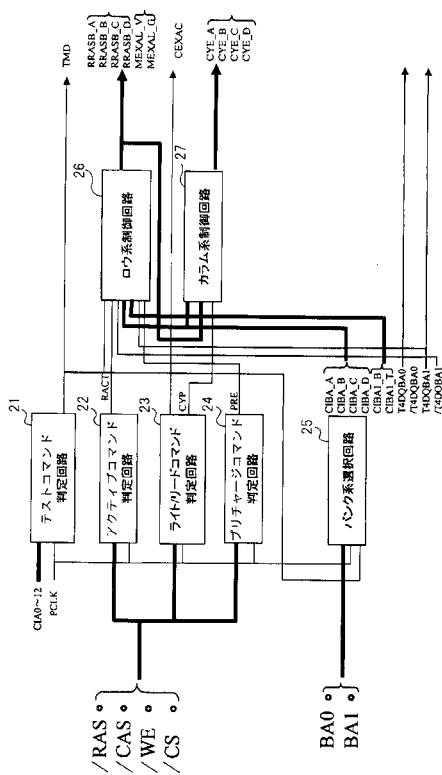

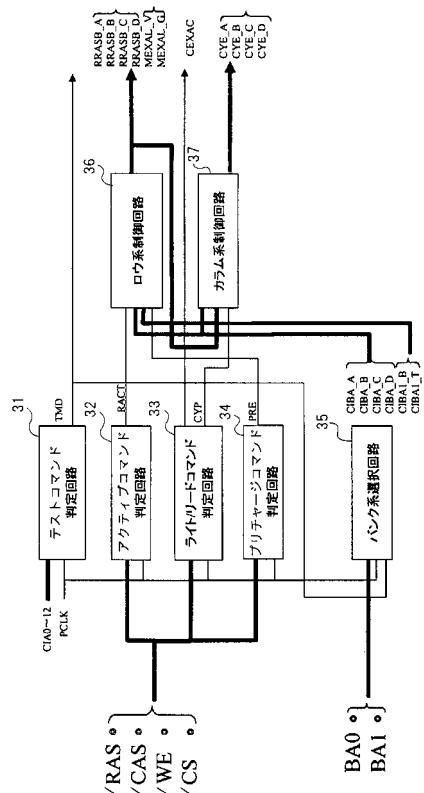

コマンドデコーダ 9 は、図 1 4 に示すように、テストコマンド判定回路 3 1 と、アクティブコマンド判定回路 3 2 と、ライト / リードコマンド判定回路 3 3 と、プリチャージコマンド判定回路 3 4 と、バンク系選択回路 3 5 と、ロウ系制御回路 3 6 と、カラム系制御回路 3 7 を有する。

## 【 0 0 1 3 】

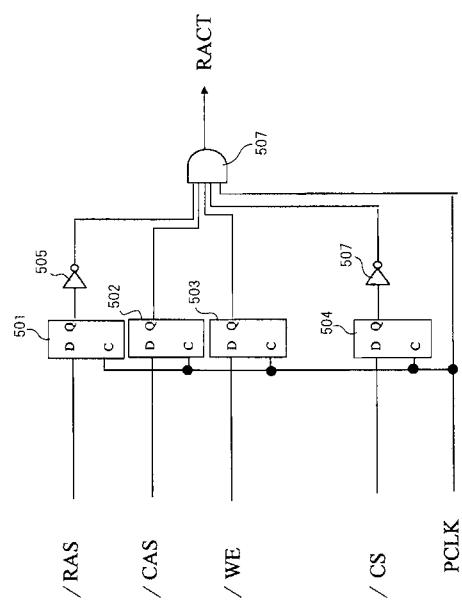

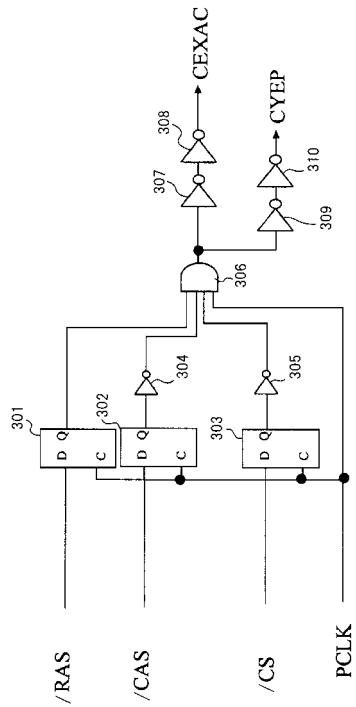

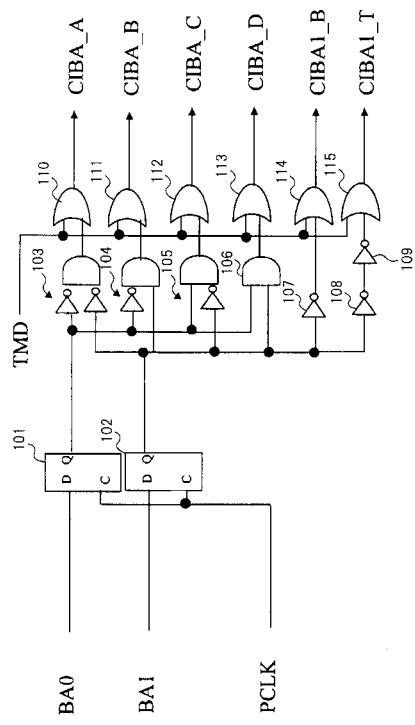

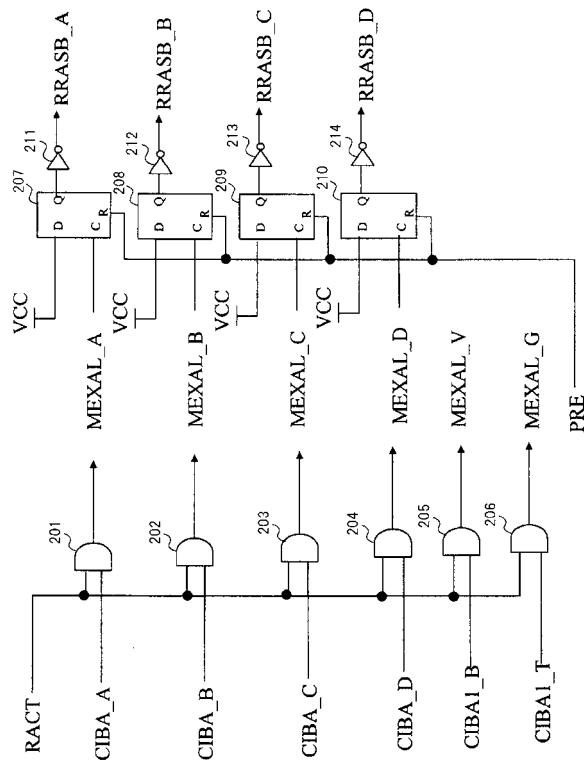

テストコマンド判定回路 3 1 はアドレス信号 C I A 0 ~ C I A 1 1 と信号 P C L K を入力し、テストモード信号 T M D を出力する。アクティブコマンド判定回路 3 2 は、チップセレクト信号 / C S、ロウアドレスストローブ信号 / R A S、カラムアドレスストローブ信号 / C A S、ライトイネーブル信号 / W E を入力し、アクティブコマンド条件が揃ったときにラッチ信号 P C L K の区間にハイとなる信号 R A C T を出力する。図 1 5 に示すように、アクティブコマンド判定回路 3 2 は、D フリップフロップ 5 0 1 ~ 5 0 4 と、インバータ 5 0 5、5 0 6 と、A N D ゲート 5 0 7 とからなる。ライト / リードコマンド判定回路 3 3 は、チップセレクト信号 / C S、ロウアドレスストローブ信号 / R A S、カラムアドレスストローブ信号 / C A S を入力し、信号 C E X A C と信号 C Y E P を出力する。信号 C E X A C は、リード / ライトコマンドが入力された際、そのとき入力されたアドレスをカラム系選択信号としてラッチするために使われる。信号 C Y E P は、信号 C E X A C と同じリード / ライトコマンドが入力された際に出力されるパルスで、C Y E 専用として（時間調整がしやすいように）別バスとしている。図 1 6 に示すように、ライト / リードコマンド判定回路 3 3 は、D フリップフロップ 3 0 1、3 0 2、3 0 3 と、インバータ 3 0 4、3 0 5 と、A N D ゲート 3 0 6 と、インバータ 3 0 7 ~ 3 1 0 とからなる。プリチャージコマンド判定回路 3 4 は、ロウのチップセレクト信号 / C S、ロウアドレスストローブ信号 / R A S、ライトイネーブル信号 / W E と、ハイのカラムアドレスストローブ信号 / C A S を入力し、プリチャージコマンド P R E を出力する。バンク系選択回路 3 5 はバンクアドレス信号 B A 0、B A 1、信号 P C L K、テストモード信号 T M D を入力し、バンク選択信号 C I B A \_ A ~ C I B A \_ D、C I B A 1 \_ B、C I B A \_ T を出力する。バンク選択信号 C I B A \_ A ~ C I B A \_ D はバンクアドレス信号 B A 0、B A 1 のハイ / ロウの組み合わせによって決まるバンク A ~ D をそれぞれ選択する信号である。バンク選択信号 C I B A 1 \_ B、C I B A \_ T もバンク選択信号であるが、バンクアドレス信号 B A 1 のハイ、ロウのみで動作する。これは、この先に接続されるロウデコーダ 4 のラッチ回路をバンク A、B 共用として、その数を減らすために、バンクアドレス信号 B A 0 をあえて論理から外している。図 1 7 に示すように、バンク系選択回路 3 5 は、D フリップフロップ 1 0 1、1 0 2 と、A N D ゲート 1 0 3 ~ 1 0 6 と、インバータ 1 0 7 ~ 1 0 9 と、O R ゲート 1 1 0 ~ 1 1 5 とからなる。ロウ系制御回路 3 6 は、信号 R A C T と、バンク選択信号 C I B A \_ A ~ C I B A \_ D、C I B A 1 \_ B、C I B A \_ T を入力し、信号 R R A S B \_ A ~ R R A S B \_ D、M E X A L \_ V、M E X A L \_ G を出力する。信号 R R A S B \_ A ~ R R A S B \_ D は、アクティブコマンド A C T の入力からプリチャージコマンド P R E が入るまでの間ロウとなっている信号である。信号 M E X A L は、アクティブコマンド A C T が入力された際、そのとき入力されたアドレスをロウ系選択信号としてラッチするために使われる信号である。図 1 8 に示すように、ロウ系制御回路 3 6 は、

20

30

40

50

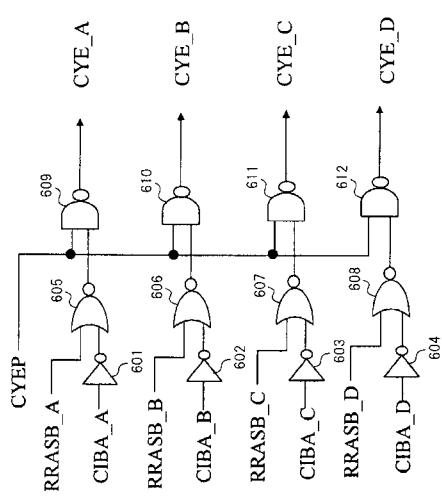

ANDゲート201～206と、Dフリップフロップ207～210と、インバータ211～214からなる。Dフリップフロップ207～210のクロック端子にはANDゲート201～204の出力信号MEXAL\_A～MEXAL\_Dが入力され、またDフリップフロップ207～210はプリチャージコマンドPREによってリセットされる。出力信号RRASB\_A～RRASB\_Dはロウデコーダ4内のデコーダの動作を制御する。信号MEXAL\_V、MEXAL\_Gはロウデコーダ4内のラッチ回路(Dフリップフロップ)のロウアドレス更新動作を制御する。カラム系制御回路37は、バンク選択信号CIBA\_A～CIBA\_Dと信号RRASB\_A～RRASB\_Dと信号CYEPを入力し、信号CYE\_A～CYE\_Dを出力する。信号CYE\_A～CYE\_Dは、リード/ライトコマンドが入力された際、それぞれバンクA～DのYスイッチの選択時間として使われる信号である。図19に示すように、カラム系制御回路37は、インバータ601～604と、NORゲート605～608と、NANDゲート609～612とからなる。

## 【0014】

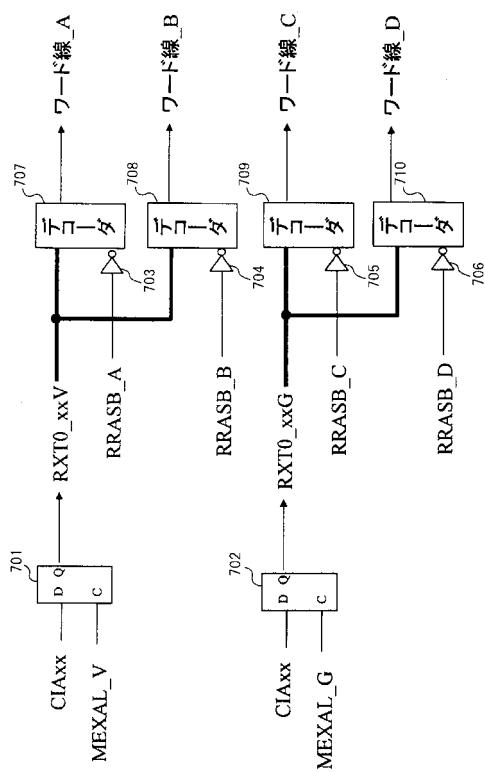

ロウデコーダ4は、アドレスバッファ2の出力であるアドレス信号CIAxx(xx=0～11)を、コマンドデコーダ3のロウ系制御回路36から出力された信号MEXAL\_V、MEXAL\_Gでラッチし、同じくロウ系制御回路36から出力された信号RRASB\_A～RRASB\_Dで制御されるデコーダでワード線A～ワード線Dをデコードする。図20に示すように、ロウデコーダ4は、フリップフロップ701、702と、インバータ703～706と、デコーダ707～710とからなる。

## 【0015】

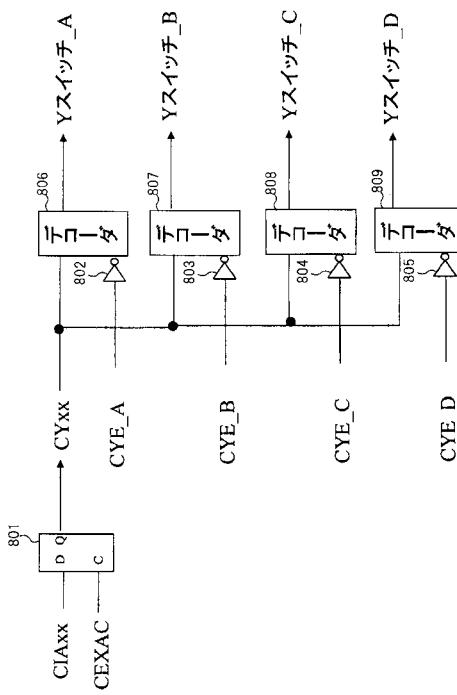

カラムデコーダ5は、アドレスバッファ2の出力であるアドレス信号CIAxx(xx=0～11)を、コマンドデコーダ3のライト/リードコマンド判定回路33から出力された信号CEXACでラッチし、カラム系制御回路37から出力される信号CYE\_A～CYE\_Dでデコードし、それぞれYスイッチ\_A～Yスイッチ\_Dをデコードする。図21に示すように、カラムデコーダ5は、Dフリップフロップ801と、インバータ802～805と、デコーダ806～809とからなる。

## 【0016】

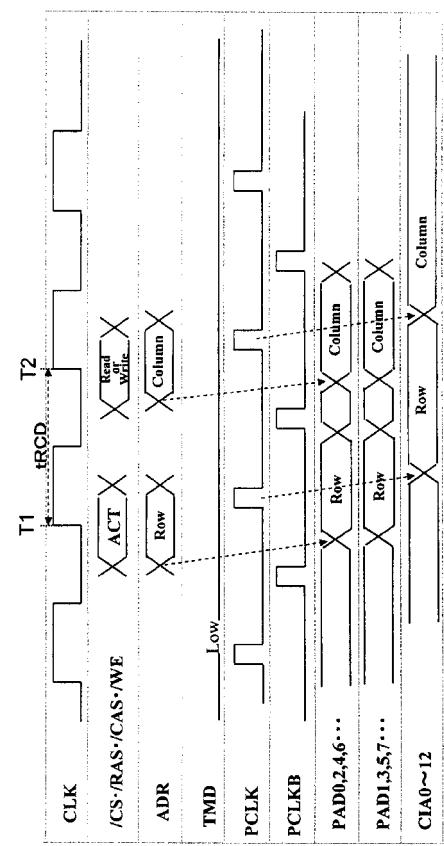

図22は、アドレスを縮退しない場合(通常動作時)のタイミングチャートである。時刻T1に、/CS、/RASがロウ、/CAS、/WEがハイになり、アクティブコマンドACTがアクティブになると、アドレスバッファ2にロウアドレスRowが入力され、信号PCLKによってDフリップフロップ44-0、44-1、…、44-11(図13)にアドレスCIA0～CIA12としてラッチされる。クロックCLKの次の立ち上がりである時刻T2にリードコマンドReadまたはライトコマンドWriteが入力されると、アドレスバッファ2にコラムアドレスColumnが入力され、ラッチパルスPCLKによってDフリップフロップ44-0、44-1、…、44-11(図13)にアドレスCIA0～CIA12としてラッチされる。

## 【0017】

図23は、アドレスを半分に縮退する場合のタイミングチャートである。この場合、テストモード信号TSDはハイとなる。アドレスADRの偶数のロウアドレスRow1がアドレスPAD0、PAD2、PAD4、…として、クロックCLKの立ち上がりに同期して発生するラッチパルスPCLKCによってラッチされ、アドレスCIA0、CIA2、CIA4、…として出力される。次に、アドレスADRの奇数のロウアドレスRow2がアドレスバッファ2の偶数端子から入力され、クロックCLKの立ち下がりに同期して発生するパルスTPCLKBによってDフリップフロップ42-0、42-2、…にアドレスPAD1、PAD3、…としてラッチされ、トランスファーゲート43-0、43-2、…を通過し、ラッチパルスPCLKCによってDフリップフロップ44-1、44-3、…にラッチされる。偶数のコラムアドレスColumn1、奇数のコラムアドレスColumn2も同様にして時刻T2にリードコマンドReadまたはライトコマンドWriteが入力されるまでにアドレスバッファ2に入力され、アドレス信号CIA0～CIA12として出力される。

10

20

30

40

50

## 【0018】

図24は、図11の半導体記憶装置のコマンドデコーダで行われるt R C D チェック時の動作を示すタイミングチャートである。

## 【0019】

まず、タイミングT1においてアクティブコマンドACTが入力された場合を説明する。クロックCLKがハイとなるとクロックジェネレータ1により、信号PCLKにハイのワンショット信号が発生し、そのとき入力されたアクティブコマンドACT( /CSがロウ、/RASがロウ、/CASがハイ、/WEがハイ)によってアクティブコマンド判定回路32の出力信号RACTが信号PCLKのハイの幅に合わせてハイとなる。テストモード信号TMD使用の際、バンク系選択回路35の出力CIBA\_A～CIBA\_DおよびCIBA\_B、CIBA\_Tは全てハイが出力されている。信号RACTによってロウ系制御回路36の内部信号MEXAL\_A～MEXAL\_Dと出力信号MEXAL\_V、MEXAL\_Gもハイとなり、インバータ211～214(図18)の出力RRASB\_A～RRASB\_Dにはロウが出力される。アクティブコマンドACT入力時に入力されたアドレス信号によってアドレスCIA0～CIA12が出力され、信号MEXAL\_V、MEXAL\_Gにて信号RXT0\_xxV、RXT0\_xxGが出力され、信号RRASB\_A～RRASB\_Dのロウ入力にてデコーダ607～610(図20)が動作して、メモリセルアレイ6へアドレスが入力されるワード線が選択される。

10

## 【0020】

次に、t R C D チェックでタイミングT2にライトまたはリードコマンドが入力されたときの動作について説明する。タイミングT1時と同様に、タイミングT2でも信号PCLKにハイのワンショット信号が発生し、そのとき入力されたライト/リードコマンド( /CSがロウ、/RASがハイ、/CASがロウ)によって信号CEXACと信号CYEPは信号PCLKのハイの幅に合わせてハイとなる。先ほどの説明にて信号RRASB\_A～RRASB\_Dはロウ、信号CIBA\_A～CIBA\_Dはハイとなっているのでカラム系制御回路37の出力CYE\_A～CYE\_DはCYEPの幅分だけロウが出力される。アクティブコマンドACT入力時と同様にそのとき入力されたアドレス信号によってアドレスCIA0～CIA12が出力され、信号CEXACにて信号CYxxが出力され、信号CYE\_A～CYE\_Dのロウ入力でデコーダ806～809(図21)が動作して、Yスイッチ\_A～Yスイッチ\_Dが選択される。タイミングT1とT2の間の時間を計ることでこのワード線選択時間とYスイッチの時間の関係を計り、セルデータへの書き込み、読み出しが正常にできる時間を調べることで、これをt R C D の実力として測定することができる。

20

## 【0021】

このように、半導体記憶装置のアドレスは、アドレスを縮退していない場合は、クロックCLKの立ち上がりまたは立ち下がりのエッジに同期して、それぞれ対応するアドレスピンから入力される。一方、アドレスを縮退する場合、例えば、アドレスピンを半分に縮退する場合、クロックCLK立ち上がりまたは立下りの両エッジに同期して、縮退時にアドレスを入力可能なアドレスピン(以上の例では偶数ピン)からそれぞれ異なるアドレスが入力される。半導体記憶装置の試験では、アクティブコマンドACTの入力タイミング( T1 )からリードまたはライトのコマンドの入力タイミング( T2 )までの時間であるt R C D の実力(つまり、T1 - T2間をどこまで短縮可能か)を評価することができる。アドレス縮退を行なっていない場合(通常動作時を含む)、図22に示したように、t R C D はアドレスの取り込み時間に依存しない。これは、アドレスがクロックCLKの立ち上がり、立ち下がりの一方のエッジに同期して入力されるため、ロウアドレス、カラムアドレス共に、充分な取り込み時間をとることが可能であるからである。一方、アドレス縮退を行なった場合、図23に示したように、カラムアドレスColumn1の取り込み時間の影響で、t R C D の実力を正確に測定できない場合が生じる。つまり、通常動作時には、アドレスの取り込み時間に依存しないはずのt R C D が、アドレス縮退テスト時には、アドレスの取り込み時間に依存するものとなってしまい、テスト時においてt R C D の

30

40

50

正確な評価が行なえなくなる。

【0022】

本発明の目的は、アドレスを縮退した試験の際にも、 $t_{RCD}$ の実力を正確に評価することが可能な半導体記憶装置および半導体記憶装置の試験方法を提供することにある。

【課題を解決するための手段】

【0023】

本発明の半導体記憶装置は、テスト動作モード時に、外部から入力されるアクティブコマンドに応じて、外部から入力されるロウアドレス信号の取り込みを行い、ワード線の選択は行なわない第1のロウ系動作を実行する手段と、第1のロウ系動作の実行後に外部から入力されるアクティブコマンドに応じて、ロウアドレス信号の更新は行わずにロウアドレス信号に対応する前記ワード線を選択する第2のロウ系動作を実行する手段とを備える。

10

【0024】

また、本発明の半導体記憶装置の試験方法は、ワード線とビット線とに接続されたメモリセルと、複数のメモリセルを有する複数のバンクとを有し、通常動作モードとテスト動作モードとを設定可能な半導体記憶装置において、アクティブコマンドが入力されてからリードまたはライトコマンドが入力されるまでの時間である $t_{RCD}$ を測定する、半導体記憶装置の試験方法であって、

外部から入力されるアクティブコマンドに応じて、外部から入力されるロウアドレス信号の取り込みを行い、ワード線の選択は行なわない第1のロウ系動作工程と、

20

第1のロウ系制御動作後に外部から入力されるアクティブコマンドに応じて、ロウアドレス信号の更新は行わずにロウアドレス信号に対応する前記ワード線を選択する第2のロウ系動作工程と

を備え、

外部から入力される信号であり、通常動作モード時には所定のバンクを選択するバンクアドレス信号を用いて、第1のロウ系動作と第2のロウ系動作とを切り替えを行い、

バンクアドレス信号が第1の論理レベルの場合、第1のロウ系動作工程が実行され、

バンクアドレス信号が第2の論理レベルの場合、第2のロウ系動作工程が実行される。

【発明の効果】

【0025】

本発明によれば、従来、テストモード時にのみ必要であり、正確な $t_{RCD}$ 測定の妨げとなっていた、アクティブコマンドACT入力後の立ち下がりエッジ入力アドレスのセットアップ、ホールド時間が必要なくなり、その結果、より正確な $t_{RCD}$ 測定を行うことが可能となる効果がある。

30

【発明を実施するための最良の形態】

【0026】

次に、本発明の実施の形態について図面を参照して説明する。

[第1の実施形態]

図1は本発明の第1の実施形態の半導体記憶装置のブロック図である。本実施形態の半導体記憶装置はクロックジェネレータ1とアドレスバッファ2とコマンドデコーダ3とロウデコーダ4とカラムデコーダ5とメモリセルアレイ6を有している。本実施形態の半導体記憶装置は図11の半導体記憶装置とはコマンドデコーダ3の構成が異なっている。

40

【0027】

図2はコマンドデコーダ3のブロック図である。コマンドデコーダ3は、テストコマンド判定回路11と、アクティブコマンド判定回路12と、ライト/リードコマンド判定回路13と、プリチャージコマンド判定回路14と、バンク系選択回路15と、ロウ系制御回路16と、カラム系制御回路17を有する。コマンドデコーダ3は図11のコマンドデコーダ9とはライト/リードコマンド判定回路13とバンク系選択回路15とロウ系制御回路16が異なる。

【0028】

10

20

30

40

50

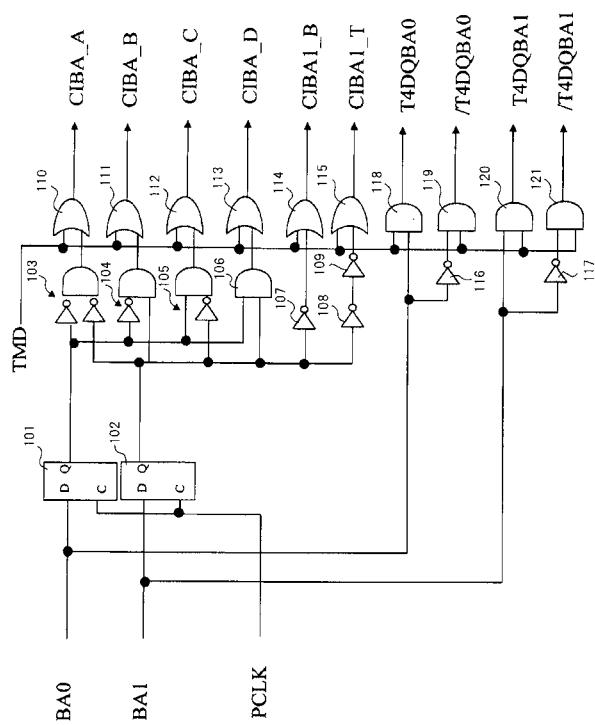

図3はバンク系選択回路15の回路図である。バンク系選択回路15は図17のバンク系選択回路35に対して、インバータ116、117とANDゲート118～121を付加した構成になっている。すなわち、バンク系選択回路13は、テストモード時に、常にハイであるバンク選択信号CIBA\_A～CIBA\_D、CIBA1\_B、CIBA\_Tに加え、バンクアドレス信号BA0、BA1によって動作するテスト信号T4DQBA0、/T4DQBA0、T4DQBA1、/T4DQBA1を出力する。

#### 【0029】

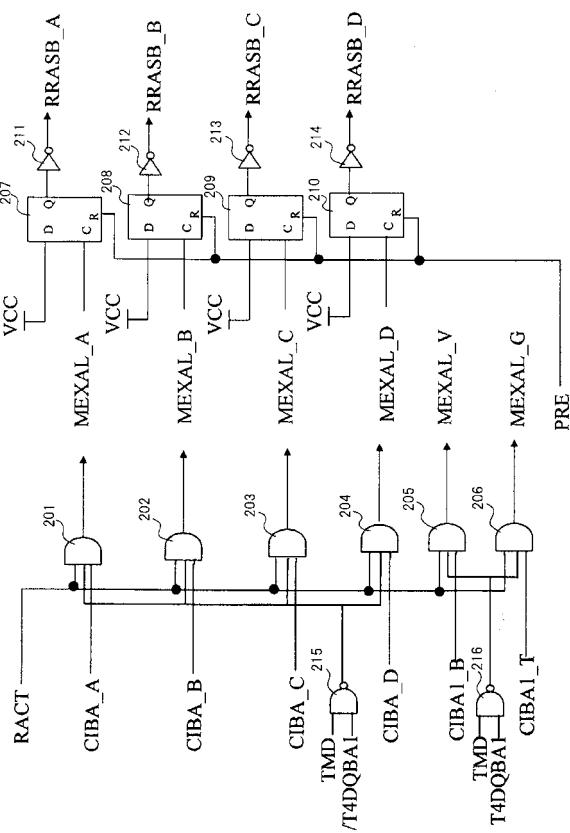

図4はロウ系制御回路16の回路図である。ロウ制御回路16は、図18のロウ制御回路36に対して、テストモード信号TMDとテスト信号/T4DQBA1を入力とし、出力がANDゲート201～204に出力されたNANDゲート215と、テストモード信号TMDとテスト信号T4DQBA1を入力とし、出力がANDゲート205、206に出力されたNANDゲート216が付加されている。このように、NANDゲート215と216を備えることで、信号MEXAL\_A～MEXAL\_Dと信号MEXAL\_V、MEXAL\_Gのアクティブ/インアクティブを相補的に制御することができる。

10

#### 【0030】

バンク系選択回路15とロウ系制御回路16を上述のように構成することで、ロウデコーダ4のデコーダ707～710の動作とロウデコーダ5内のラッチ回路(Dフリップフロップ701、702)のロウアドレス更新動作を、バンクアドレス信号BA1によって制御することが可能となる。特に、プリチャージコマンドPRE入力後の最初のアクティブコマンドACTではロウアドレス入力動作のみを行い、次のアクティブコマンドACTでは、ロウデコーダ4のデコーダ707～710の動作のみを行うように制御することが可能となる。なお、信号RRASB\_A～RRASB\_Dは、カラム系制御回路17(図19)の制御信号の1つとしても用いられる。

20

#### 【0031】

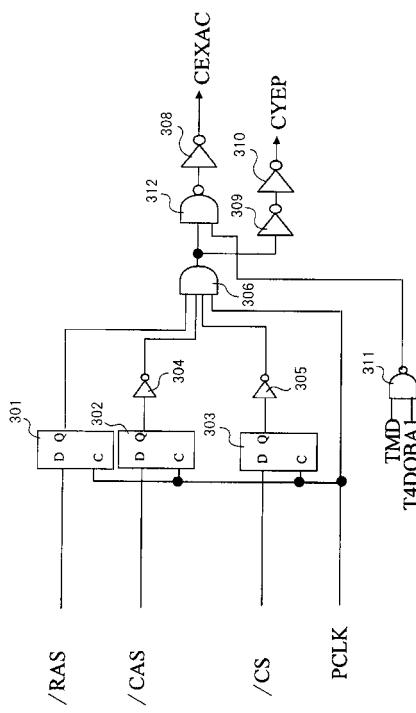

図5はライト/リードコマンド判定回路13の回路図である。ライト/リードコマンド判定回路13は、図16のライト/リードコマンド判定回路33に対して、テストモード信号TMDとテスト信号T4DQBA1を入力とするNANDゲート311を追加し、インバータ307の代わりにANDゲート306の出力とNANDゲート311の出力を入力するNANDゲート312を備えたものである。

30

#### 【0032】

ライト/リードコマンド判定回路13を上述のように構成することで、カラムデコーダ5のデコーダ806～809の動作とカラムデコーダ5内のラッチ回路(Dフリップフロップ801)のカラムアドレス更新動作を、バンクアドレス信号BA1によって制御することが可能となる。特に、プリチャージコマンドPRE入力後の最初のライト/リードコマンドではカラムアドレス入力動作のみを行い、ロウデコーダ4動作後のライト/リードコマンドでは、カラムデコーダ5のデコーダ806～809の動作のみを行うように制御することが可能となる。

#### 【0033】

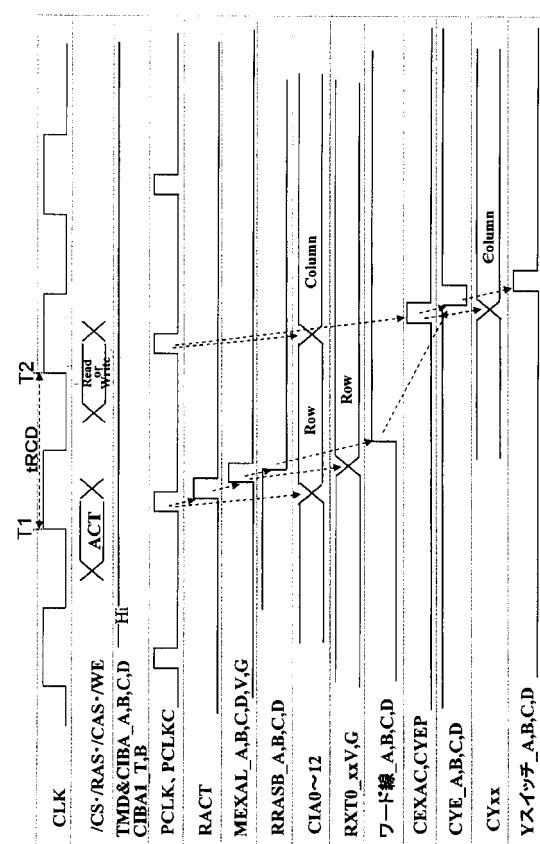

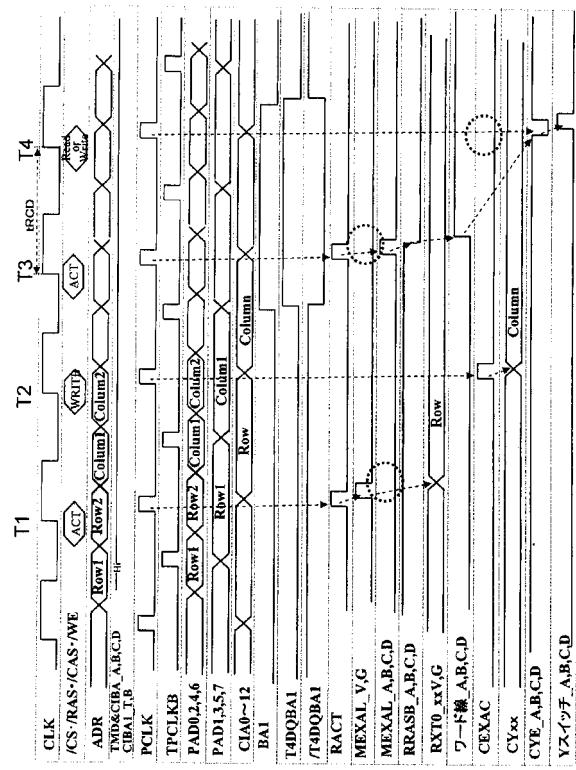

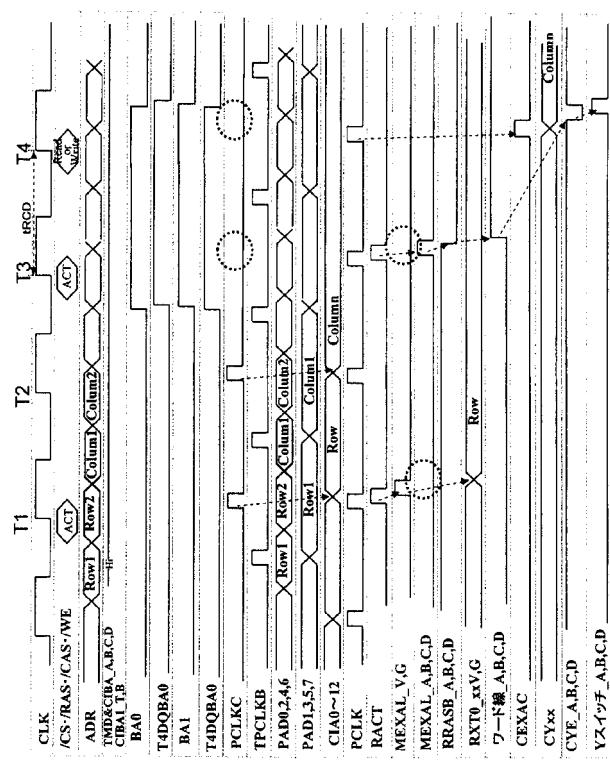

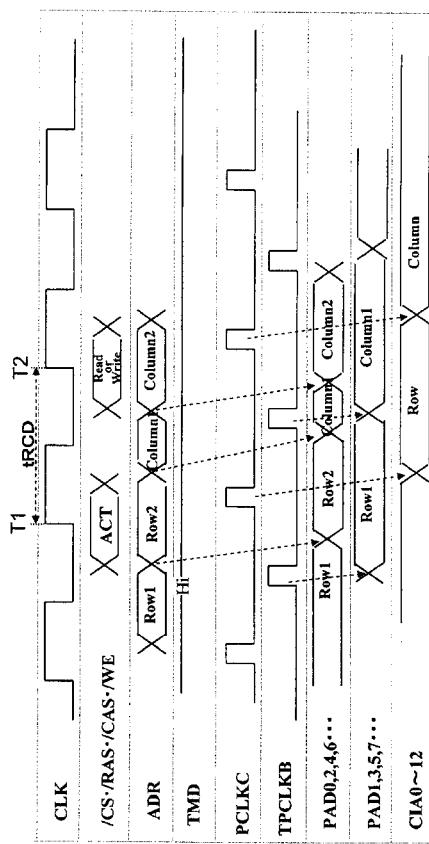

次に、本実施形態の動作を図6のタイミングチャートにより説明する。バンクアドレス信号BA1をロウにしてアクティブコマンドACTおよびライトコマンドWriteを入力したときのタイミングをそれぞれT1、T2とする。

40

#### 【0034】

タイミングT1に、従来と同じくパルス信号PCLKが発生し、アクティブコマンドACT入力を検知し、パルス信号RACTが発生する。しかし、ロウ系制御回路16(図4)において、信号/T4DQBA1がハイであるため、信号MEXAL\_A～MEXAL\_Dはロウのままで、信号MEXAL\_V、MEXAL\_Gのみが発生する。よって信号RRASB\_A～RRASB\_Dはハイのまま、RXT0\_xxV、RXT0\_xxG(図20)のみクロック入力ロウ、ハイそれぞれでラッチした外部アドレス入力に合わせたアドレスCIA\_xxがラッチされるが、信号RRASB\_A～RRASB\_Dがハイのままであるためデコーダ707～710(図20)は動作せず、ワード線\_A～Dは選択さ

50

れない。

【0035】

次に、ライトコマンドWriteが入力されたタイミングT2では、信号T4DQBA1はロウであるので、ライト/リードコマンド判定回路13の出力CEXAC、CYEPはハイを出力し、アクティブコマンドACT入力時と同様にCYxx(図21)にはクロック入力のロウ、ハイそれぞれでラッチした外部アドレス入力に合わせたアドレスCIAxxがラッチされる。しかし、カラム系制御回路17ではRRASB\_A～RRASB\_Dがハイのままであるため、CYE\_A～CYE\_D(図21)はハイのままでなり、デコーダ806～809は動作せず、Yスイッチ\_A～Dは選択されない。

【0036】

以上の動作で、ロウデコーダ4内のラッチ回路RXT0\_xxV、RXT0\_xxGにロウアドレスが保持され、カラムデコーダ5内のタッチ回路CYxxにカラムアドレスが保持される。

【0037】

次に、バンクアドレス信号BA1をハイとしてアクティブコマンドACTおよびライトコマンドWriteを入力する。そのときのタイミングをそれぞれT3、T4とする。このときは信号T4DQBA1、/T4DQBA1の論理レベルは先ほどのタイミングT1、T2のときとは逆となるが、アクティブコマンドACTを入力したときのタイミングT3ではロウ系制御回路16(図4)の出力MEXAL\_V、MEXAL\_Gはロウのままで、逆に信号RRASB\_A～RRASB\_Dはロウが出力される。よってロウデコーダ4は動作することになるが、このときのアドレス入力のラッチ回路(Dフリップフロップ701、702)は動作していないので、先ほどタイミングT1でラッチしたアドレスにてデコードされたワード線が選択される。また、同様にタイミングT4でライト/リードコマンドが入力されたときはライト/リードコマンド判定回路13にて信号CEXACが発生せず、信号CYEPのみ発生する。そのためCYxx(図21)には先ほどのタイミングT2にて入力されたアドレスがラッチされたままで、CYE\_A～CYE\_D(図19)がアクティブになり、CYxxにてデコードされたYスイッチが選択される。従って、バンクアドレス信号BA1をハイとした状態でtRCD測定を行なうことで、アドレスの取り込み時間の影響を受けずに、tRCDの実力を評価することが可能である。

【0038】

このように、第1の実施形態では、ロウデコーダ4またはカラムデコーダ5内のラッチ回路にアドレスを取り込む動作サイクルと、tRCD測定を行なうサイクルとを別サイクルとして動作させることができるとおり、その結果、アドレスの取り込み時間の影響を受けずに、tRCDの実力を正確に評価することができるものである。

【0039】

[第2の実施形態]

図7は本発明の第2の実施形態の半導体記憶装置のブロック図である。本実施形態の半導体記憶装置はクロックジェネレータ7とアドレスバッファ2とコマンドデコーダ8とロウデコーダ4とカラムデコーダ5とメモリセルアレイ6を有している。本実施形態の半導体記憶装置は図11の半導体記憶装置とはクロックジェネレータ7とコマンドデコーダ8のみ異なる。

【0040】

図8はクロックジェネレータ7の回路図である。クロックジェネレータ7は図12の従来のクロックジェネレータ1に、テストモード信号TMDと、図3のバンク系選択回路15の出力信号T4DQBA0、T4DQBA1を入力とするNANDゲート410と、ANDゲート406の出力信号とNANDゲート410の出力信号を入力とするANDゲート411が付加されている。

【0041】

図9はコマンドデコーダ8のブロック図である。コマンドデコーダ8は、テストコマンド判定回路21と、アクティブコマンド判定回路22と、ライト/リードコマンド判定回

10

20

30

40

50

路23と、プリチャージコマンド判定回路24と、バンク系選択回路25と、ロウ系制御回路26と、カラム系制御回路27を有する。バンク系選択回路25およびロウ系制御回路26は第1の実施形態のバンク系選択回路15およびロウ系制御回路16と同じである。

#### 【0042】

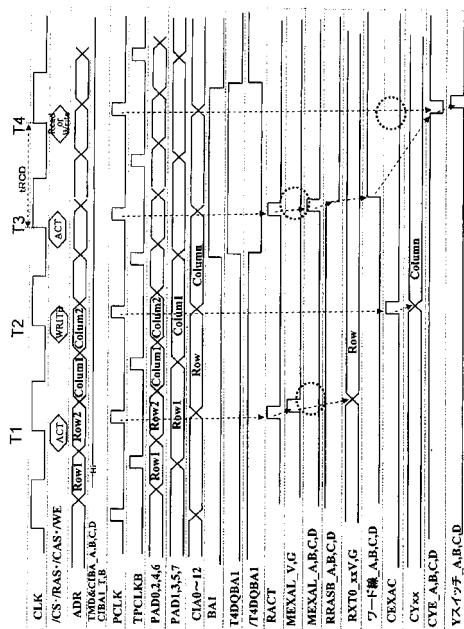

第1の実施形態では、タイミングT2にライトコマンドWriteの入力が必要であったが、本実施形態は、ライトコマンドWriteを入力しなくてもYスイッチアドレスをT2のタイミングでラッチせしようにしたものである。

#### 【0043】

図10は本実施形態の半導体記憶装置の動作を示すタイミングチャートである。タイミングT1、T3における動作は第1の実施形態と変わらないため説明は省略するが、タイミングT2においてバンクアドレス信号BA0とBA1のいずれかをロウにさせているときは信号PCLKCが発生するため、アドレスCIA0～CIA12には外部アドレスがラッチされる。次に、タイミングT3およびT4ではバンクアドレス信号BA0、BA1をハイとし、アクティブコマンドACTおよびライト/リードコマンドを入力する。タイミングT4時は信号PCLKCが発生せず信号PCLKのみが発生し、信号CEXACがアクティブになり、通常のYスイッチ選択動作となるが、カラム選択アドレスは先ほどのタイミングT2でラッチされたアドレスにてYスイッチが選択される。タイミングT4では該ラッチされたラッチアドレスの更新を行わないようにクロックPCLKCを制御するので、タイミングT4でのリード/ライトコマンド時に取り込まれるカラムアドレスのセットアップ時間を十分に取ることができ、T3-T4間のtRCDがカラムアドレスのセットアップ時間に制限されることなくなる。なお、本実施形態で信号PCLKCを止めるためにバンクアドレス信号BA0も使用している理由は、バンクアドレス信号BA1をハイとしたモードレジスタセットコマンド時のアドレス取り込みができなくなってしまうのを防ぐためである。

10

20

30

40

#### 【0044】

このように、第2の実施形態2では、第1の実施形態とは異なり、カラムアドレスをアドレスバッファ2からカラムデコーダ5内のラッチ回路に取り込むタイミング自体はリードまたはライトコマンドのタイミングT4で行なう構成となっている。その代わり、tRCD測定開始前に所望のカラムアドレスをアドレスバッファ2中のラッチ回路にラッチしておき、その後は、tRCD測定が終了するまでアドレスバッファ2のラッチ回路の制御クロック(PCLK)を非活性化する構成となっている。このように構成することで、リードまたはライトコマンドのタイミングでのカラムアドレスの取り込みを、アドレス縮退をしていない場合と同様の状態とすることができる。したがって、tRCDの実力を正確に測定可能となる。

#### 【0045】

第1、第2の実施形態では、動作の切り替え(第1の実施形態における動作サイクルの切り替え、第2の実施形態におけるクロックPCLKのアクティブ/インアクティブの切り替え)を、特にバンクアドレス信号を用いて行なっているが、このバンクアドレス信号は、テストモードエントリー時のMRSのために外部から入力する必要がある信号であるため、縮退することができない。しかし、テストモードにエントリーした後は使用しない信号である。したがって、このように、テストモードエントリー時には必要であり、テスト中には使用しない信号であるバンクアドレス信号を動作の切り替えの制御に用いることで、切り替え用に新たにピン数を増やすことなく、第1、第2の実施形態に記載したような縮退テストを実行可能である。また、このようにテスト中には不要な信号を用いて切り替えを制御することで、該切り替えをクロックCLKに非同期に行なうことが可能となる。

50

#### 【0046】

以上の実施形態では、半導体記憶装置のバンク数を4としたが、バンクの数は2以上任意である。また、アドレスを12ビットとしたが、アドレスのビット数は、これに限定されるものではない。また、カラムアドレスをロウアドレスよりも先にアドレスバッファ2

50

に入力してもよい。

【図面の簡単な説明】

【0047】

【図1】図1は本発明の第1の実施形態の半導体記憶装置のブロック図である。

【図2】図2は図1中のコマンドデコーダのブロック図である。

【図3】図3は図1中のバンク系選択回路の回路図である。

【図4】図4は図1中のロウ系制御回路の回路図である。

【図5】図5は図1中のライト/リードコマンド判定回路の回路図である。

【図6】図6は第1の実施形態の半導体記憶装置の動作を示すタイミングチャートである。

10

【図7】図7は本発明の第2の実施形態の半導体記憶装置のブロック図である。

【図8】図8は図7中のクロックジェネレータの回路図である。

【図9】図9は図7中のコマンドデコーダのブロック図である。

【図10】図10は第2の実施形態の半導体記憶装置の動作を示すタイミングチャートである。

20

【図11】図11は半導体記憶装置の従来例のブロック図である。

【図12】図12は図11中のクロックジェネレータの回路図である。

【図13】図13は図11中のアドレスバッファの回路図である。

【図14】図14は図11中のコマンドデコーダの回路図である。

【図15】図15は図11中のアクティブコマンド判定回路の回路図である。

【図16】図16は図11中のライト/リードコマンド判定回路の回路図である。

【図17】図17は図11中のバンク系選択回路の回路図である。

【図18】図18は図11中のロウ系制御回路の回路図である。

【図19】図19は図11中のカラム系制御回路の回路である。

【図20】図20は図11中のロウデコーダの回路図である。

【図21】図21は図11中のカラムデコーダの回路図である。

【図22】図22はアドレスを縮退しない場合(通常動作時)の、図11の半導体記憶装置の動作を示すタイミングチャートである。

30

【図23】図23はアドレスを縮退する場合の、図11の半導体記憶装置の動作を示すタイミングチャートである。

【図24】図24は、図11の半導体記憶装置のコマンドデコーダで行われるt R C D チェック時の動作を示すタイミングチャートである。

30

【符号の説明】

【0048】

|         |            |

|---------|------------|

| 1、 7    | クロックジェネレータ |

| 2       | アドレスバッファ   |

| 3、 8、 9 | コマンドデコーダ   |

| 4       | ロウデコーダ     |

| 5       | カラムデコーダ    |

| 6       | メモリセルアレイ   |

40

|                                     |                 |

|-------------------------------------|-----------------|

| 1 1、 2 1、 3 1                       | テストコマンド判定回路     |

| 1 2、 2 2、 3 2                       | アクティブコマンド判定回路   |

| 1 3、 2 3、 3 3                       | ライト/リードコマンド判定回路 |

| 1 4、 2 4、 3 4                       | プリチャージコマンド判定回路  |

| 1 5、 2 5、 3 5                       | バンク系選択回路        |

| 1 6、 2 6、 3 6                       | ロウ系制御回路         |

| 1 7、 2 7、 3 7                       | カラム系制御回路        |

| 4 0                                 | インバータ           |

| 4 1 - 0 ~ 4 1 - 1 1                 | バッファ            |

| 4 2 - 0、 4 2 - 2、 . . . 、 4 2 - 1 0 | D フリップフロップ      |

50

|                                       |            |    |

|---------------------------------------|------------|----|

| 4 3 - 0 、 4 3 - 1 、 . . . 、 4 3 - 1 1 | トランスファーゲート |    |

| 4 4 - 0 、 4 4 - 1 、 . . . 、 4 4 - 1 1 | D フリップフロップ |    |

| 4 5 - 0 、 4 5 - 1 、 . . . 、 4 5 - 1 1 | バッファ       |    |

| 1 0 1 、 1 0 2                         | D フリップフロップ |    |

| 1 0 3 ~ 1 0 6 、 1 1 8 ~ 1 2 1         | AND ゲート    |    |

| 1 0 7 ~ 1 0 9 、 1 1 6 、 1 1 7         | インバータ      |    |

| 2 0 1 ~ 2 0 6 、 2 1 7 、 2 1 8         | AND ゲート    |    |

| 2 0 7 ~ 2 1 0                         | D フリップフロップ |    |

| 2 1 1 ~ 2 1 4                         | インバータ      |    |

| 2 1 5 、 2 1 6                         | NAND ゲート   | 10 |

| 3 0 1 ~ 3 0 3                         | D フリップフロップ |    |

| 3 0 4 、 3 0 5 、 3 0 7 ~ 3 1 0         | インバータ      |    |

| 3 0 6                                 | AND ゲート    |    |

| 3 1 1 、 3 1 2                         | NAND ゲート   |    |

| 3 1 0 ~ 3 1 5                         | OR ゲート     |    |

| 4 0 1 ~ 4 0 3 、 4 0 8 、 4 0 9         | インバータ      |    |

| 4 0 4 、 4 0 5                         | 遅延回路       |    |

| 4 0 6 、 4 1 1                         | AND ゲート    |    |

| 4 0 7 、 4 1 0                         | NAND ゲート   |    |

| 5 0 1 ~ 5 0 4                         | D フリップフロップ | 20 |

| 5 0 5 、 5 0 6                         | インバータ      |    |

| 5 0 7                                 | AND ゲート    |    |

| 6 0 1 ~ 6 0 4                         | インバータ      |    |

| 6 0 5 ~ 6 0 8                         | NOT ゲート    |    |

| 6 0 9 ~ 6 1 2                         | NAND ゲート   |    |

| 7 0 1 、 7 0 2                         | D フリップフロップ |    |

| 7 0 3 ~ 7 0 6                         | インバータ      |    |

| 7 0 7 ~ 7 1 0                         | デコーダ       |    |

| 8 0 1                                 | D フリップフロップ |    |

| 8 0 2 ~ 8 0 5                         | インバータ      | 30 |

| 8 0 6 ~ 8 0 9                         | デコーダ       |    |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

【 図 2 1 】

## 【 図 2 2 】

【 図 2 3 】

【 図 2 4 】