#### MINISTERO DELLO SVILUPPO ECONÓMICO DREZIONE GENERALE PER LA TUTELA DELLA PROPRIETA INDUSTRIALE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 101997900592876 |

|--------------------|-----------------|

| Data Deposito      | 29/04/1997      |

| Data Pubblicazione | 29/10/1998      |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 04     | L           |        |             |

## Titolo

DISPOSITIVO PER LA RICERCA DELLA POSIZIONE DI UN BIT ATTIVO A PARTIRE DA UN'ESTREMITA' DI UNA STRINGA DI BIT

Oelio Giustin

**DESCRIZIONE** dell'invenzione industriale a nome

ITALTEL s.p.a., con sede in MILANO.

# Campo di applicazione dell'Invenzione

5

10

15

20

La presente invenzione riguarda un dispositivo per la ricerca della posizione di un bit attivo in una stringa di bit, ed in particolare un dispositivo elettronico che, esaminando una stringa di bit, trova la posizione del primo bit attivo a partire da un'estremità di tale stringa.

È noto che nel campo dell'informatica e delle telecomunicazioni ricorre frequentemente il problema di trovare velocemente il primo o l'ultimo bit attivo in una stringa di bit, dove con il termine bit attivo si intende un bit di valore predefinito, generalmente uguale ad uno. Tale ricerca è stata finora realizzata mediante appositi circuiti elettronici comprendenti una pluralità di porte logiche opportunamente collegate in modo da esaminare in sequenza tutti i bit della stringa e trovare il primo od ultimo bit attivo. Finché il numero di bit della stringa da esaminare non è elevato, in particolare non è maggiore di 8, tali circuiti noti sono in grado di fornire il risultato in breve tempo. Tuttavia, quando il numero di bit della stringa è elevato, tali circuiti elettronici dedicati possono non essere in grado di fornire il risultato in tempo utile, specialmente quando il primo od ultimo bit attivo si trova lontano dal bit rispettivamente più significativo o meno significativo.

#### Rassegna dell'arte nota

Per ovviare a questo problema, sono stati ideati i cosiddetti dispositivi di ricerca "a bisezione", i quali dividono la stringa di bit da esaminare in due metà e verificano la presenza del bit attivo in ciascuna metà. Tali dispositivi dividono successivamente a metà la stringa di bit comprendente un bit attivo più vicina all'estremità di partenza

M 97 A 0 988

finché non resta un solo bit attivo, che è quello ricercato. Tuttavia, questo tipo di dispositivo di ricerca richiede un elevato numero di passaggi, per cui, in caso di stringhe aventi un numero elevato di bit, può anch esso non essere in grado di fornire il risultato in tempo utile.

## 5 Scopi dell'Invenzione

Scopo della presente invenzione è pertanto quello di fornire un dispositivo per la ricerca del bit attivo che sia esente da tali inconvenienti, ovvero un dispositivo che sia in grado di trovare il bit attivo in un tempo breve, indipendentemente dalla sua posizione all'interno della stringa di bit.

O Un altro scopo della presente invenzione è quello di fornire un dispositivo la cui progettazione e fabbricazione siano semplici anche nel caso in cui la stringa di bit da esaminare comprenda un numero assai elevato di bit.

Un ulteriore scopo della presente invenzione è quello di fornire un dispositivo che sia in grado di eseguire la ricerca del bit attivo limitatamente ad una porzione della stringa di bit in ingresso.

#### Sommario dell'Invenzione

15

20

25

Detti scopi vengono conseguiti con un dispositivo le cui caratteristiche principali sono specificate nella prima rivendicazione.

Essendo suddiviso su più livelli di una struttura ad albero, il dispositivo secondo la presente invenzione è in grado di scomporre la ricerca del bit attivo in più ricerche parallele eseguite su piccoli gruppi di bit. Il tempo di calcolo dell'intero dispositivo risulta pertanto ridotto al tempo di calcolo dei moduli di un ramo dell'albero.

Grazie alla sua struttura modulare, il dispositivo secondo la presente invenzione può essere facilmente progettato e fabbricato indipendentemente dal numero di bit contenuti nella stringa da esaminare. Infatti, per realizzare un dispositivo di ricerca per

stringhe contenenti un numero elevato di bit, è sufficiente disporre secondo una struttura ad albero di adeguate dimensioni una pluralità di moduli di ricerca dimensionati per analizzare stringhe contenenti un numero ridotto di bit. Il dispositivo secondo la presente invenzione può inoltre essere facilmente riprogettato e/o modificato per eseguire funzioni supplementari, quale ad esempio la ricerca del bit attivo in una o più porzioni della stringa di bit in ingresso.

Ulteriori vantaggiose caratteristiche della presente invenzione che sono ritenute innovative risulteranno evidenti dalle rivendicazioni dipendenti.

## Breve descrizione delle figure

- 10 Ulteriori vantaggi e caratteristiche del dispositivo secondo la presente invenzione risulteranno evidenti agli esperti del ramo dalla seguente dettagliata descrizione di due sue forme realizzative con riferimento agli annessi disegni in cui:

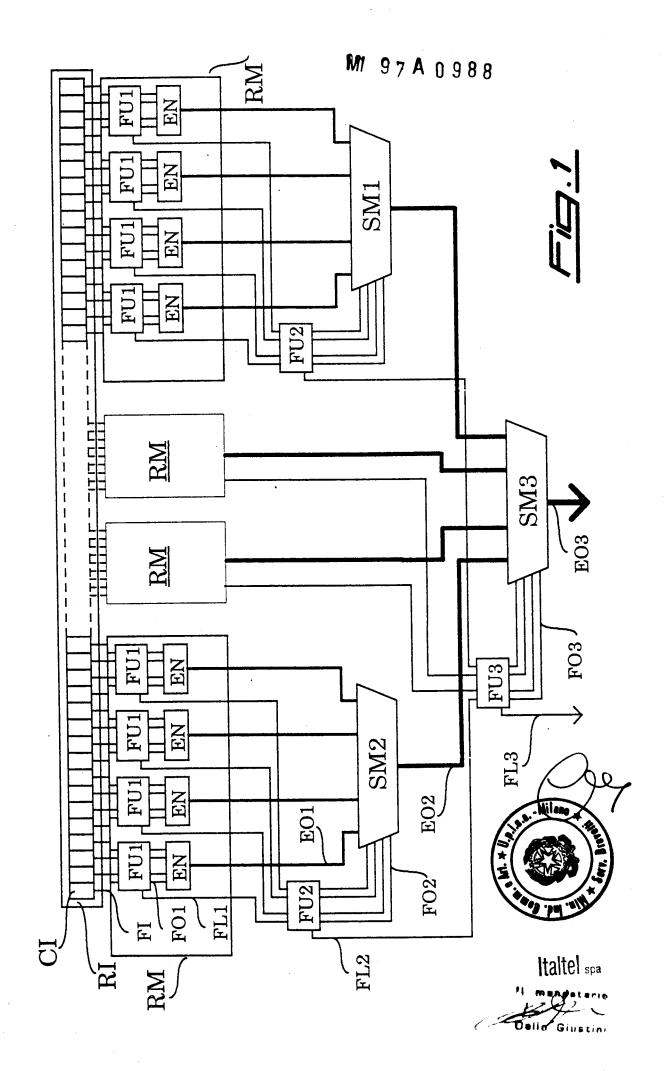

- -la Fig. 1 mostra uno schema a blocchi di una prima forma realizzativa del dispositivo secondo la presente invenzione, la quale trova il primo bit attivo a partire dal bit più significativo della stringa di bit in ingresso;

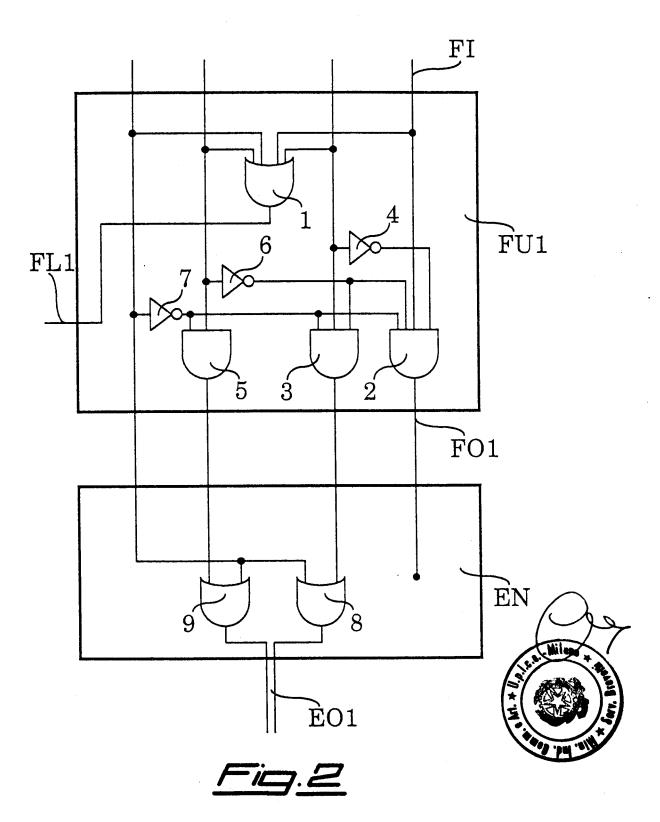

- -la Fig. 2 mostra uno schema del circuito interno di un modulo filtrante e di un codificatore del dispositivo di Fig. 1;

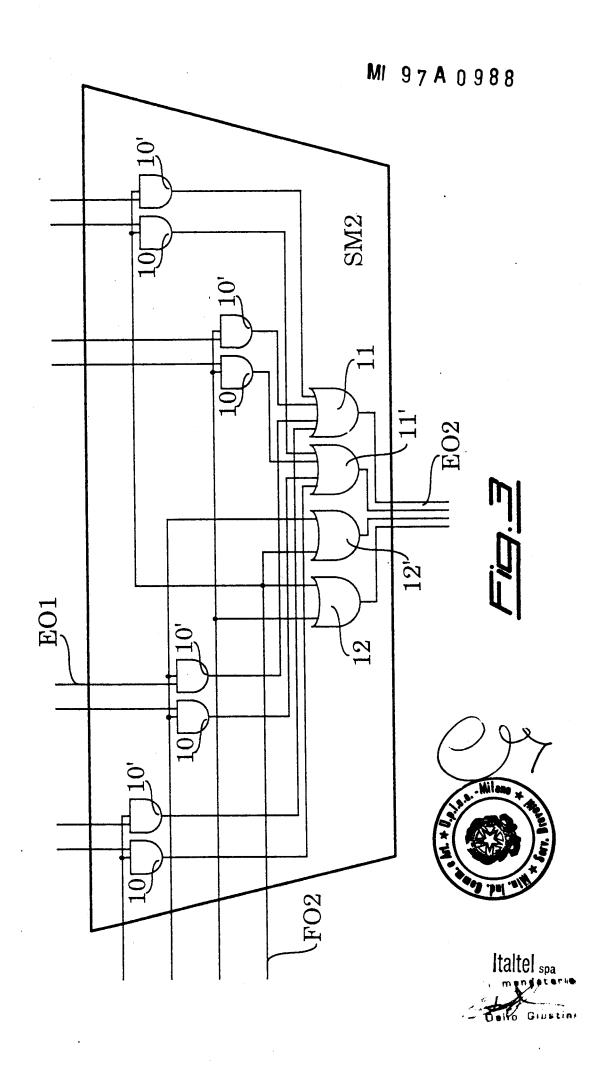

- -la Fig. 3 mostra uno schema del circuito interno di un modulo selettore a 4 ingressi del dispositivo di Fig. 1;

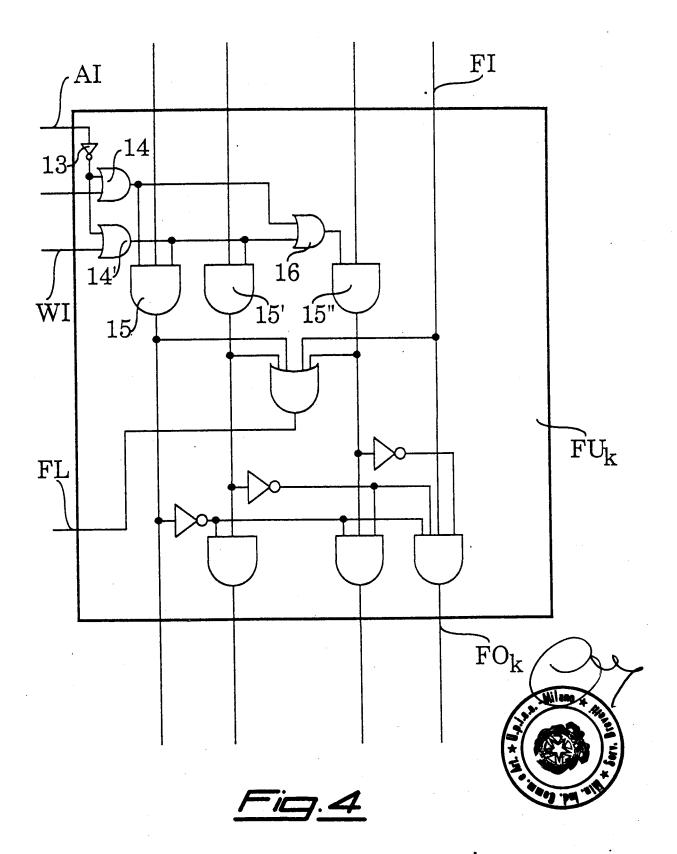

- -la Fig. 4 mostra uno schema del circuito interno di un modulo filtrante di una seconda forma realizzativa del dispositivo secondo la presente invenzione, la quale trova il primo bit attivo a partire da un particolare bit della stringa di bit in ingresso;

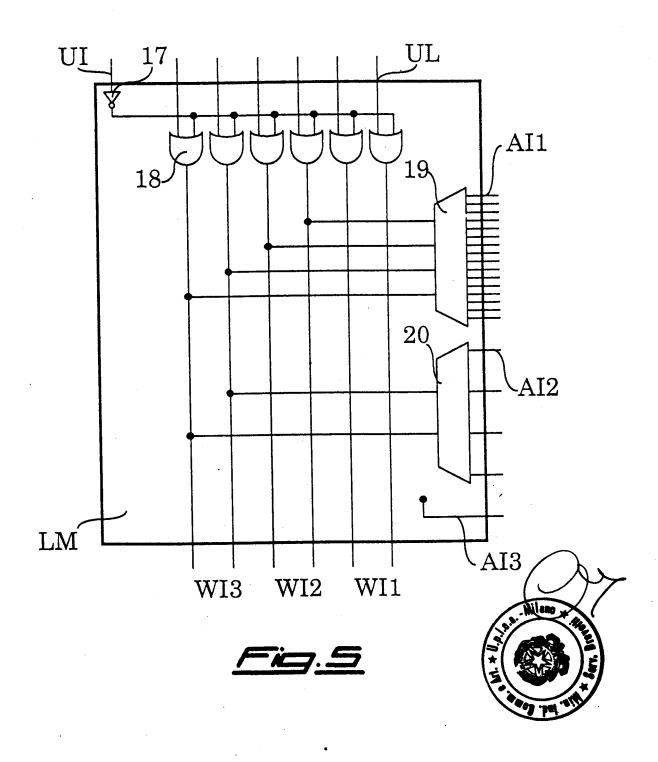

-la Fig. 5 mostra uno schema del circuito interno di un modulo di controllo del modulo filtrante di Fig. 4;

- 25 -la Fig. 6 mostra una tabella esemplificativa del contenuto delle linee della prima

forma realizzativa del dispositivo secondo la presente invenzione; e

-la Fig. 7 mostra una tabella esemplificativa del contenuto delle linee della seconda

forma realizzativa del dispositivo secondo la presente invenzione.

Descrizione dettagliata di una forma preferenziale di realizzazione dell'invenzione

Facendo riferimento alla Fig. 1, si vede che il dispositivo secondo la presente invenzione comprende un registro RI formato da 2<sup>m</sup> celle CI, in ciascuna delle quali viene inserito un bit della stringa da esaminare. Nella presente forma realizzativa tale registro comprende 64 celle, ovvero m è uguale a 6, ma è ovvio che in altre forme realizzative della presente invenzione il numero di celle CI può essere maggiore o minore di 64. In figura sono mostrate per chiarezza solo le prime e le ultime 16 celle CI del registro RI, le quali conterranno rispettivamente i 16 bit più significativi (a sinistrà in figura) e meno significativi (a destra in figura) della stringa da esaminare. I

10

15

comprendente le 64 linee parallele attraverso le quali viene trasmessa la stringa da esaminare. Nel caso in cui la stringa di bit da esaminare non sia formata da un numero di bit uguale ad una potenza intera di 2, si inserisce tale stringa nelle celle Cl corrispondenti ai bit meno significativi. Le restanti celle Cl saranno ovviamente predefinite con bit inattivi, generalmente uguali a zero.

64 ingressi delle celle Cl sono a loro volta collegati ad un bus (non mostrato in figura)

Le linee FI in uscita dalle celle CI sono opportunamente raggruppate in blocchi di 2<sup>n</sup> linee parallele, ciascuno dei quali è collegato in ingresso ad uno di 2<sup>m-n</sup> moduli filtranti FU1. Nella presente forma realizzativa le linee FI collegate a ciascuno dei moduli filtranti FU1 sono 4, ovvero n è uguale a 2, ma è ovvio che in altre forme realizzative della presente invenzione il numero di linee FI in ingresso nei moduli filtranti può essere maggiore o minore di 4, ad esempio uguale ad 8 (n=3). Attraverso le 2<sup>n</sup> linee FI, ciascun modulo filtrante FU1 riceve pertanto una stringa di 2<sup>n</sup> bit che viene filtrata

da tale modulo azzerando tutti i bit in ingresso tranne l'eventuale bit attivo, generalmente uguale a uno, più vicino al bit più significativo. La stringa così filtrata da ciascun modulo FU1 (la quale contiene necessariamente al massimo un uno), viene trasmessa in uscita attraverso 2<sup>n</sup> linee parallele FO1. Dal modulo filtrante FU1 esce anche una linea FL1 attraverso la quale viene trasmesso un segnale binario che è uguale ad uno se la stringa filtrata contiene almeno un bit attivo, oppure è uguale a zero se tale stringa non contiene alcun bit attivo. La seguente tabella mostra la tavola di verità degli ingressi e delle uscite di un modulo FU1 a 4 ingressi (n=2).

Tabella 1: tavola di verità di un modulo filtrante a 4 ingressi

| Ingressi FI | Uscite FO1 | Uscita FL1 |

|-------------|------------|------------|

|             |            | , Y        |

| 0000        | 0000       | 0          |

| 0001        | 0001       | . 1 '      |

| 0010        | 0010 🛴     | 1          |

| 0011        | 0010       | . 1        |

| 0100        | 0100       | 1.         |

| 0101        | 0100       | 1          |

| 0110        | 0100       | 1          |

| 0111        | 0100       | <u>,</u> 1 |

| 1000        | 1000       | 1          |

| 1001        | 1000       | 1          |

| 1010        | 1000       | <u>†</u>   |

| 1011        | 1000       | 1          |

| 1100        | 1000       | 1          |

| 1101        | 1000       | 1          |

|             |            |            |

10

갋

| ,1110° | 1000 | 1   |

|--------|------|-----|

| 1111   | 1000 | 1 . |

Le 2<sup>n</sup> linee FO1 in uscita da ciascun modulo filtrante FU1 vengono collegate agli ingressi di un codificatore EN il quale converte la stringa di 2<sup>n</sup> bit trasmessa dalle linee FO1 in un numero binario di n bit indicante la posizione dell'eventuale bit attivo presente in tale stringa di 2<sup>n</sup> bit. Il risultato del codificatore EN viene quindi trasmesso attraverso un bus EO1 (illustrato con una linea leggermente ingrossata) comprendente n linee parallele. La seguente tabella mostra la tavola di verità degli ingressi e delle uscite di un codificatore EN a 4 ingressi (n=2).

Tabella 2: tavola di verità di un codificatore a 4 ingressi

| Uscita EO1 |

|------------|

| 00         |

| 00         |

| 01         |

| 10         |

| 11         |

|            |

I bus EO1 in uscita da ciascuno dei 2<sup>m-n</sup> codificatori EN sono raggruppati in blocchi di 2<sup>p</sup> bus, ciascun blocco essendo collegato ad un modulo selettore SM2 la cui struttura interna verrà spiegata dettagliatamente in seguito. Anche le linee FL1 uscenti dai moduli filtranti FU1 sono raggruppate in blocchi di 2<sup>p</sup> linee, ciascun blocco essendo collegato in ingresso ad un ulteriore modulo filtrante FU2. Il funzionamento del modulo filtrante FU2 è analogo a quello dei moduli filtranti FU1 ai quali è collegato, per cui

10

anche la stringa di bit in ingresso nel modulo filtrante FU2 viene filtrata azzerando tutti i bit tranne l'eventuale bit attivo più vicino al bit più significativo. Il numero di ingressi del modulo filtrante FU2 può essere eventualmente diverso dal numero di ingressi dei moduli filtranti FU1 ai quali è collegato, ovvero p può essere diverso da n, tuttavia nella presente forma realizzativa anche i moduli filtranti FU2 hanno 4 ingressi come i moduli FU1, ovvero p è uguale a 2.

Le 2º linee di controllo FO2 in uscita da ciascun modulo FU2 sono collegate in ingresso allo stesso modulo selettore SM2 cui erano collegati i 2º bus EO1 di ciascun blocco. Tali linee di controllo servono ad indicare quale dei 2º bus EO1 in ingresso nel modulo selettore SM2 deve essere trasmesso in uscita. Tuttavia, il modulo selettore SM2 differisce da un comune multiplexer per il fatto che la stringa di bit trasmessa da tale modulo, oltre a contenere gli n bit del bus EO1 selezionato dalle linee di controllo FO2, contiene come bit più significativi i p bit indicanti la posizione di tale bus selezionato. Essa viene trasmessa attraverso un bus EO2 (illustrato con una linea ingrossata) comprendente p+n linee parallele. La seguente tabella mostra la tavola di verità degli ingressi e delle uscite di un modulo selettore SM2 di 4 bus EO1 da 2 bit ciascuno (n=2, p=2). I 2 bit trasmessi da tali bus sono stati indicati rispettivamente con le lettere a<sub>1</sub>b<sub>1</sub>, a<sub>2</sub>b<sub>2</sub>, a<sub>3</sub>b<sub>3</sub> e a<sub>4</sub>b<sub>4</sub>.

Tabella 3: tavola di verità di un modulo selettore di 4 bus da 2 bit

| Ingresso FO' | Uscita EO'                      |

|--------------|---------------------------------|

| 0000         | 0000                            |

| 0001         | 00a₁b₁                          |

| 0010         | 01a <sub>2</sub> b <sub>2</sub> |

| 0100         | 10a₃b₃                          |

|              | j                               |

20

10

Delio Giustini

1000 11a₄b₄

Il dispositivo secondo la presente forma realizzativa risulta pertanto suddiviso in 2<sup>m-n-p</sup> moduli principali di ricerca RM, ciascuno dei quali comprende 2<sup>p</sup> moduli filtranti FU1, 2º codificatori EN. La presente forma realizzativa comprende in particolare 4 moduli di ricerca RM, dei quali in Fig. 1 vengono mostrati completamente il primo e l'ultimo. I bus EO2 uscenti dal modulo selettore SM2 sono collegati in ingresso ad un ulteriore modulo selettore SM3, il cui funzionamento è analogo a quello dei 2<sup>m-n-p</sup> moduli selettori SM2 ai quali è collegato. Tuttavia, il modulo selettore SM3 differisce dai moduli selettori SM2 per il fatto che i bus EO2 in ingresso non sono formati da n linee parallele come i bus EO1, bensì sono formati da p+n linee parallele. Il bus EO2 da trasmettere in uscita viene selezionato dalle linee di controllo FO3 uscenti da un ulteriore modulo filtrante FU3 a 2<sup>m-n-p</sup> ingressi, il cui funzionamento è identico a quello dei moduli filtranti FU1 e FU2. Il modulo filtrante FU3 filtra infatti nel modo sopra descritto la stringa di 2<sup>m-n-p</sup> bit che riceve in ingresso attraverso le 2<sup>m-n-p</sup> linee FL2 uscenti dai moduli filtránti FU2, trasmettendo sulle linee di controllo FO3 la risultante stringa di 2<sup>m-n-p</sup> bit filtrata. In base al contenuto di tale stringa, il modulo selettore SM3 seleziona uno dei bus EO2 in ingresso e ne invia il contenuto ad un bus EO3 (illustrato con una linea notevolmente ingrossata), aggiungendovi gli (m-n-p) bit indicanti la posizione del bus EO2 selezionato. La stringa di bit trasmessa attraverso il bus EO3 è formata pertanto da (m-n-p+p+n) bit, ovvero m bit, e corrisponde esattamente al numero binario indicante la posizione del primo bit attivo della stringa di 2<sup>m</sup> bit in esame, a partire dal bit più significativo. Il segnale binario trasmesso dalla linea FL3 in uscita dal modulo filtrante FU3 indica invece l'eventuale presenza di tale bit attivo all'interno della stringa di bit in esame, per cui dalla linea FL3 e dal bus EO3

si ricava il risultato della ricerca per la quale il dispositivo secondo la presente invenzione è stato ideato.

Facendo ancora riferimento alla Fig. 1, si può notare che il dispositivo secondo la presente invenzione possiede una struttura ad albero, le cui foglie sono rappresentate dalle linee in ingresso FI e la cui radice è rappresentata dal bus EO3 e dalla linea FL3. I nodi di tale albero sono distribuiti su un primo livello comprendente una serie di 2<sup>m-n</sup> moduli filtranti FU1 e 2<sup>m-n</sup> codificatori EN, su un secondo livello comprendente una serie di 2<sup>m-n-p</sup> moduli filtranti FU2 e 2<sup>m-n-p</sup> moduli selettori SM2, un terzo livello comprendente una serie di 2<sup>m-n-p-q</sup> moduli filtranti FU3<sup>-</sup>e 2<sup>m-n-p-q</sup> moduli selettori SM3, e così via fino a quando non resta un ultimo livello comprendente un solo modulo filtrante ed un solo modulo selettore, le cui uscite forniranno il risultato della ricerca. In particolare, nella presente forma realizzativa q è uguale a 2, per cui il terzo livello dell'albero è già l'ultimo, comprendendo  $2^{6\cdot 2\cdot 2\cdot 2} = 2^0 = 1$  modulo filtrante e  $2^{6-2-2-2} = 2^0 = 1$  modulo selettore. È ovvio che altre forme realizzative del dispositivo secondo la presente invenzione possono essere strutturate su un numero di livelli maggiore o minore di tre. Tale numero dipende infatti dal numero di bit della stringa da esaminare e dal numero di ingressi dei moduli filtranti compresi nel dispositivo stesso.

10

15

Facendo ora riferimento alla Fig. 2, si vede che i moduli filtranti FU1 a 4 ingressi della presente forma realizzativa dell'invenzione comprendono una porta logica 1 di tipo OR alla quale sono collegate le 4 linee FI e la linea FL1, rispettivamente in ingresso ed in uscita. La linea FI corrispondente al bit meno significativo è direttamente collegata all'ingresso di una porta logica 2 di tipo AND alla cui uscita è collegata la linea FO1 corrispondente al bit meno significativo. La linea FI corrispondente al secondo bit meno significativo è direttamente collegata all'ingresso di un'altra porta

logica 3 di tipo AND la cui uscita è collegata alla linea FO1 corrispondente al secondo bit meno significativo. La linea FI corrispondente al secondo bit meno significativo è collegata anche ad una porta logica 4 di tipo NOT la cui uscita è collegata all'ingresso della porta logica AND 2. La linea FI corrispondente al secondo bit più significativo è direttamente collegata all'ingresso di un'ulteriore porta logica 5 di tipo AND la cui uscita è collegata alla linea FO1 corrispondente al secondo bit più significativo. La linea FI corrispondente al secondo bit più significativo è collegata anche ad una porta logica 6 di tipo NOT la cui uscita è collegata all'ingresso delle porte logiche 2 e 3. Infine, la linea FI corrispondente al bit più significativo è direttamente collegata alla linea FO1 corrispondente al bit più significativo. La linea FI corrispondente al bit più significativo è collegata anche ad una porta logica 7 di tipo NOT la cui uscita è collegata all'ingresso delle porte logiche AND 2, 3 e 5. Grazie a questo schema di porte logiche, il modulo filtrante FU1 esegue le operazioni combinatorie descritte nella Tabella 1. È chiaro che in altre forme realizzative il modulo filtrante FU1 può presentare uno schema circuitale diverso da quello ora descritto, ma equivalente nella sua funzione.

10

15

20

25

Facendo ancora riferimento alla Fig. 2, si vede che i codificatori EN a 4 ingressi della presente forma realizzativa dell'invenzione comprendono una porta logica 8 di tipo OR alla quale sono collegate in ingresso le 2 linee FO1 corrispondenti al bit più significativo ed al secondo bit meno significativo. I codificatori EN comprendono anche un'altra porta logica 9 di tipo OR alla quale sono collegate in ingresso le 2 linee FO1 corrispondenti ai primi due bit più significativi. La linea FO1 corrispondente al bit meno significativo è invece scollegata. Le uscite delle porte logiche 8 e 9 sono collegate alle 2 linee del bus EO1 corrispondenti rispettivamente al bit meno significativo ed a quello più significativo. Grazie a questo schema di porte logiche, il

codificatore EN esegue le operazioni combinatorie descritte nella Tabella 2. È chiaro che in altre forme realizzative della presente invenzione il codificatore EN può presentare uno schema circuitale diverso da quello ora descritto.

Facendo ora riferimento alla Fig. 3, si vede che il modulo selettore SM2 della presente forma realizzativa dell'invenzione comprende in modo noto 4 coppie di porte logiche 10, 10' di tipo AND a ciascuna delle quali sono collegate in ingresso le due linee dei quattro bus EO1. Agli ingressi di ciascuna di tali porte logiche AND è collegata anche una delle 4 linee di controllo FO2, in modo tale che tutti i bit trasmessi dai bus EO1 vengano azzerati tranne quelli trasmessi dal bus EO1 selezionato dalla linea di controllo FO2 che trasmette un segnale binario uguale ad uno. Le uscite delle coppie di porte logiche 10, 10' sono collegate agli ingressi di una coppia di porte logiche 11, 11' di tipo OR. Ad un ulteriore coppia di porte logiche 12, 12' di tipo OR sono opportunamente collegate in ingresso le linee di controllo FO2 corrispondenti rispettivamente ai primi due bit significativi ed al primo e terzo bit più significativo della stringa di bit trasmessa attraverso le linee di controllo FO2. In questo modo, dalla coppia di porte logiche 12, 12' viene trasmesso in uscita un numero binario di 2 bit indicante la posizione del bus EO1 selezionato dalle linee di controllo FO2. Le uscite delle porte logiche 12, 12', 11 ed 11' sono quindi collegate alle 4 linee del bus EO2 uscente dal modulo selettore SM2. Grazie a questo schema di porte logiche, il modulo selettore SM2 esegue le operazioni combinatorie descritte nella Tabella 3. È chiaro che in altre forme realizzative della presente invenzione il modulo selettore SM2 può presentare uno schema circuitale diverso da quello ora descritto. In particolare, il modulo selettore SM3 avrà una struttura interna simile a quella del modulo selettore SM2, dalla quale differisce semplicemente per il fatto di comprendere 4 gruppi di 4 porte logiche di tipo AND in ingresso ed un gruppo di 4 porte logiche di tipo OR in

10

uscita. Tali gruppi di 4 porte logiche AND ed OR sostituiscono rispettivamente le coppie di porte logiche AND 10, 10' ed OR 11, 11'.

Facendo ora riferimento alla Fig. 4, si vede che in un'altra forma realizzativa del dispositivo secondo la presente invenzione i moduli filtranti FU<sub>k</sub> comprendono un circuito combinatorio supplementare posto a monte del circuito sopra descritto ed illustrato in Fig. 2. Tale circuito serve a limitare superiormente e/c inferiormente la ricerca del bit attivo nella stringa di bit da esaminare. Detta limitazione viene eseguita sulla base sia di un numero binario di m bit che corrisponde al limite superiore di ricerca e viene trasmesso attraverso altrettante linee UL, sia di un segnale binario di attivazione UI che è uguale ad uno nel caso si voglia effettivamente attivare la suddetta funzione di limitazione della stringa di bit. I segnali UL ed UI sono generati esternamente al dispositivo e vengono elaborati all'interno del dispositivo da almeno un modulo di controllo LM della limitazione della ricerca, il cui funzionamento verrà descritto in seguito con riferimento alla Fig. 5.

5

10

15

20

25

In particolare, per ogni stadio, le linee Al vengono generate decodificando i bit più significativi della parola UL, tali da selezionare il numero di moduli filtranti appartenenti a detto stadio.

Le linee WI vengono anch'esse generate a partire dalla parola UL Per ogni stadio contengono un numero w di di linee sufficienti alla codifica del numero n di ingressi per ogni modulo filtrante FU<sub>k</sub>. Sono ricavati dalla parola UL escludendo un numero di bit, a partire dal meno significativo, pari a [w\* numero di stadi a monte dello stadio considerato]; dei bit rimanenti le linee WI saranno costituite dai k bit meno significativi. Sempre nell'esempio di parola su cui operare la ricerca pari a 64 linee, il modulo filtrante FU<sub>k</sub> a quattro ingressi con limitatore superiore comprende quindi, oltre a tutte le porte ed i collegamenti dei moduli filtranti della prima forma realizzativa, due

ingressi WI ai quali sono collegate due delle sei linee uscenti dal modulo di controllo LM. In particolare, gli ingressi WI3 del modulo filtrante FU3 posto all'ultimo livello del dispositivo, saranno collegati alle due linee UL corrispondenti ai due bit più significativi del numero binario indicante la posizione del limite superiore di ricerca.

Gli ingressi WI2 dei quattro moduli filtranti FU2 posti a livello intermedio del dispositivo, saranno invece collegati alle due linee UL corrispondenti ai due bit intermedi del numero binario indicante la posizione del limite superiore di ricerca.

Gli ingressi WI1 dei sedici moduli filtranti FU1 posti al primo livello del dispositivo, saranno invece collegati alle due linee UL corrispondenti ai due bit meno significativi del numero binario indicante la posizione del limite superiore di ricerca.

L' ingresso Al3 del modulo filtrante FU3 sempre attivo. Ai segnali Al2 di ciascuno degli FU2 arriva un bit risultato della decodifica dei due bit più significatifi di UL. Ai segnali Al1 di ciascuno degli FU1 arriva un bit risultato della decodifica dei quattro bit più significativi di UL.

Il modulo filtrante FU1 a 4 ingressi con limitatore superiore comprende quindi, oltre a tutte le porte ed i collegamenti dei moduli filtranti della prima forma realizzativa, due linee in ingresso WI provenienti dal modulo LM che indicano la posizione degli eventuali bit da azzerare, nonché una linea in ingresso AI, s'empre proveniente dal modulo LM, che indica l'eventuale attivazione della funzione di limitazione superiore.

O Viene ora descritta in dettaglio la struttura interna dei moduli filtranti FU<sub>k</sub> provvisti del limitatore superiore.

La linea di attivazione Al è collegata in ingresso ad una porta logica 13 di tipo NOT la cui uscita è a sua volta collegata agli ingressi di una coppia di porte logiche 14, 14' di tipo OR. Agli ingressi di queste ultime due porte logiche sono opportunamente collegate anche le linee WI indicanti le posizioni dei bit da azzerare quando l'ingresso

Al è uguale a uno. Per selezionare tali bit, le 3 linee FI in ingresso corrispondenti ai 3 bit più significativi vengono fatte passare attraverso 3 porte logiche 15, 15', 15" di tipo AND, ai cui ingressi sono collegate anche le uscite delle porte OR 14, 14'. In particolare, la porta logica AND 15 corrispondente al bit più significativo riceverà in ingresso la linea FI corrispondente al bit più significativo, nonché le uscite di entrambe le porte OR 14, 14'. La porta logica AND 15' corrispondente al secondo bit più significativo riceverà in ingresso la linea FI corrispondente al secondo bit più significativo, nonché l'uscita della porta OR 14'. Infine, la porta logica AND 15" corrispondente al secondo bit meno significativo riceverà in ingresso la linea Fl corrispondente al secondo bit meno significativo, nonché l'uscita di una porta logica 16 di tipo OR alla quale sono collegate in ingresso le uscite delle porte OR 14, 14'. Grazie a questo schema di porte logiche, il modulo filtrante a 4 ingressi con limitatore superiore esegue le operazioni combinatorie descritte nella seguente Tabella 4. Detta tabella mostra la tavola di verità degli ingressi e delle uscite di un modulo filtrante a 4 ingressi con limitatore superiore. I 4 bit in ingresso nelle linee FI sono stati indicati rispettivamente con le lettere a, b, c e d.

Tabella 4: Tavola di verità di un modulo filtrante con limitatore superiore

| Ingresso Al | Ingressi WI | Uscite FO |

|-------------|-------------|-----------|

| 0           | 00          | abcd      |

| 0           | . 01        | abcd      |

| o           | 10          | abcd      |

| 0           | 11          | abcd      |

| 1           | 00          | 000d      |

| 1           | 01          | , 00cd    |

| 0bcd |

|------|

| abcd |

|      |

È ovvio che in altre forme realizzative della presente invenzione il modulo filtrante con limitatore superiore può presentare uno schema circuitale diverso da quello ora descritto. È altresì ovvio per un tecnico del ramo modificare i collegamenti e/o le porte logiche del modulo filtrante secondo la presente forma realizzativa in modo da eseguire una limitazione inferiore oppure una doppia limitazione, superiore ed inferiore. In quest'ultimo caso il modulo filtrante riceverà in ingresso due coppie di linee che trasmettono i bit del limite superiore e quelli del limite inferiore.

10

20

Facendo ora riferimento alla Fig. 5, si vede che il modulo di controllo LM della limitazione della ricerca riceve in ingresso, attraverso le 6 linee UL, un numero binario di m bit, in particolare 6 bit, indicante la posizione del limite superiore di ricerca nella stringa di 2<sup>m</sup> bit da esaminare mediante il dispositivo secondo la presente invenzione. Il modulo LM riceve anche in ingresso, attraverso la linea UI, un segnale binario che abilita la limitazione della ricerca quando è uguale ad uno. Tale segnale, dopo essere stato negato mediante una porta 17 di tipo NOT, viene trasmesso in ingresso a 6 porte 18 di tipo OR che ricevono in ingresso anche le 6 linee UL. Con questo accorgimento, se la funzione di limitazione è disabilitata, ovvero se il segnale proveniente dalla linea UI è uguale a zero, da tutte le uscite WI1, WI2, e WI3 delle porte OR 18 viene trasmesso un uno. Se invece la funzione di limitazione è abilitata, ovvero se il segnale proveniente dalla linea UI è uguale ad uno, dalle uscite WI1, WI2, e WI3 delle porte OR 18 vengono trasmessi gli stessi bit ricevuti dalle linee UL. In particolare, le due linee WI3 corrispondenti ai due bit più significativi del numero ricevuto dalle linee UL sono collegate al modulo filtrante FU3 posto all'ultimo livello.

Le due linee W12 corrispondenti ai due bit intermedi del numero ricevuto dalle linee UL sono invece collegate in parallelo ai 4 moduli filtranti FU2 posti al livello intermedio. Infine, le due linee W11 corrispondenti ai due bit meno significativi del numero ricevuto dalle linee UL sono collegate in parallelo ai 16 moduli filtranti FU1 posti al primo livello.

Le quattro linee corrispondenti ai quattro bit più significativi del numero ricevuto dalle linee UL sono opportunamente collegate in ingresso ad un decodificatore 19 di tipo noto che trasmette in uscita, su 16 linee Al1, una stringa di 16 bit contenente 15 zeri ed un uno sulla linea Al1 individuata dal numero binario di 4 bit ricevuto da tale decodificatore. Le 16 linee Al sono collegate in ingresso ai 16 moduli filtranti FU1 posti al primo livello. Con questo accorgimento la limitazione della ricerca viene abilitata solo nel modulo filtrante FU1 individuato dal bit uguale ad uno nella stringa in uscita dal decodificatore 19. Analogamente, le due linee corrispondenti ai due bit più significativi del segnale ricevuto dalle linee UL sono collegate in ingresso ad un decodificatore 20 di tipo noto che trasmette in uscita, su 4 linee Al2, una stringa di 4 bit contenente 3 zeri ed un uno sulla particolare linea Al2 individuata dal numero binario di 2 bit ricevuto da tale decodificatore. Le 4 linee Al2 sono collegate in ingresso ai 4 moduli filtranti FU2 posti al livello intermedio. Con questo accorgimento la limitazione della ricerca viene abilitata solo nel modulo filtrante FU2 individuato dal bit uguale ad uno della stringa in uscita dal decodificatore 20. La limitazione della ricerca viene sempre abilitata nel modulo filtrante FU3 poiche' quello e' l' unico FU di quel livello.

10

15

20

25

Il funzionamento delle due forme realizzative del dispositivo secondo la presente invenzione verrà descritto dettagliatamente nei due seguenti esempi, con particolare riferimento alla Fig. 6 ed alla Fig. 7.

#### Esempio 1: Dispositivo senza limitatore superiore

Facendo riferimento alla Fig. 6, si vede che, nel funzionamento della prima forma realizzativa del dispositivo secondo la presente invenzione, sprovvista del limitatore superiore, la stringa di 64 bit da esaminare contenuta nelle 64 celle CI viene suddivisa in 16 stringhe di 4 bit trasmesse dalle linee FI. Si noti che nell'esempio di Fig. 5, il primo bit attivo si trova in trentottesima posizione, ovvero nella posizione 100101 espressa in forma binaria, presupponendo che il bit meno significativo si trovi nella posizione numero 000000, mentre il bit più significativo si trovi nella posizione numero 111111. Le 16 stringhe di 4 bit filtrate dai moduli FU1 vengono trasmesse dalle linee FO1 e codificate dai codificatori EN. In particolare, la stringa di bit del settimo blocco di linee Fl, la quale contiene il bit attivo ricercato, è uguale a 0011, per cui la stringa di bit trasmessa dal settimo blocco di linee FO1 è uguale a 0010, il bit trasmesso dalla settima linea FL1 è uquale a 1 ed il numero binario a 2 bit trasmesso dal settimo bus EO1 è uquale a 01. I 16 numeri binari a 2 bit trasmessi dalle linee EO1 in uscita da tali codificatori EN entrano a gruppi di 4 in 4 moduli selettori SM2. Ciascuno di questi moduli selettori riceve in ingresso anche i 4 gruppi di 4 linee di controllo FO2 uscenti dai 4 moduli filtranti FU2. In particolare, il secondo modulo selettore SM2 seleziona il terzo bus a partire da sinistra, dato che la stringa di bit trasmessa dal secondo gruppo di linee di controllo FO2 è uguale a 0010. L'uscita EO2 del secondo modulo selettore SM2 è guindi uguale a 0101, ovvero 01 (posizione del terzo bus EO1) affiancato a 01 (contenuto del terzo bus EO1). I 4 bus EO2 in uscita dai 4 moduli selettori SM2 giungono infine nel modulo selettore SM3, il quale seleziona un bus EO2 in base al contenuto delle linee di controllo FO3, aggiungendovi la posizione di tale bus EO2. In particolare, poiché il bit trasmesso dalla seconda linea FO3 è uguale ad uno, il selettore SM2 seleziona il secondo bus EO2 aggiungendovi i due bit indicanti la

10

15

20

seconda posizione a partire da sinistra. Il risultato del dispositivo secondo la presente forma realizzativa, trasmesso attraverso il bus EO3, è pertanto 100101, ovvero la posizione del bit attivo ricercato. L'uno trasmesso dalla linea FL3 indica che è stato trovato un bit attivo nella stringa di bit in esame. Il bit trasmesso da tale linea è determinante soprattutto quando il bit attivo si trova nella prima posizione; ovvero nella posizione 000000. Esaminando il contenuto della linea FL3 è possibile distinguere la situazione in cui il bit attivo è in tale posizione dalla situazione in cui non vi sia alcun bit attivo nella stringa di bit in esame. In entrambi i casi, infatti, il risultato trasmesso dal bus EO3 sarebbe uguale a 000000.

## Esempio 2: Dispositivo con limitatore superiore

10

25

Facendo riferimento alla Fig. 7, si vede che, nel funzionamento della seconda forma realizzativa del dispositivo secondo la presente invenzione, questa volta provvista del limitatore superiore, la stringa di 64 bit da esaminare viene trattata in modo analogo all'esempio precedente. Tuttavia, il dispositivo, oltre alla stringa da esaminare, riceve in ingresso attraverso le linee UL anche la posizione del limite superiore di ricerca, che è rappresentato in particolare dalla cinquantaquattresima posizione (110101 in forma binaria), Poiché il bit trasmesso dalla linea UI è uguale ad uno, il dispositivo limiterà la ricerca del bit attivo partendo dal cinquantaquattresimo bit e non più dal bit più significativo. Il modulo LM, che riceve in ingresso le linee UI eo UL, trasmette ai moduli filtranti FU1, FU2 ed FU3 i segnali di controllo della limitazione attraverso le linee WI1, WI2, WI3, AI1, AI2 ed AI3. In particolare, vengono attivate le funzioni di limitazione nel modulo filtrante FU3, nel primo modulo filtrante FU2 a partire da sinistra e nel terzo modulo filtrante FU1 sempre a partire da sinistra. Gli altri moduli filtranti FU1 ed FU2 funzionano nel modo consueto, ovvero senza la limitazione superiore, in quanto ricevono in ingresso dalle linee AI1 ed AI2 un bit uguale a zero.

Mangatario Dello Giustini

Nel presente esempio il terzo modulo filtrante FU1 ed il primo modulo filtrante FU2 a partire da sinistra azzerano i due bit più significativi in ingresso, mentre il modulo filtrante FU3 non azzera alcun bit. Infatti, i bit WI3 sono uguali a 11, mentre i bit WI2 ed i bit WI1 sono uguali a 01. Il risultato della ricerca è pertanto uguale a 110100, dato che il primo bit attivo a partire dalla cinquantaquattresima posizione si trova in cinquantatreesima posizione.

Le due forme realizzative del dispositivo secondo la presente invenzione qui descritte ed illustrate riguardano in particolare un dispositivo che individua nella stringa di bit in ingresso il primo bit attivo a cominciare dal bit più significativo. È ovvio che in altre forme realizzative della presente invenzione è possibile individuare il primo bit attivo a cominciare dal bit meno significativo semplicemente invertendo i collegamenti dei moduli filtranti od collegamenti in ingresso del dispositivo. È inoltre ovvio per un tecnico del ramo modificare i collegamenti e/o le porte logiche del dispositivo secondo la presente invenzione, lasciandone invariata la struttura ad albero, in modo da trovare il primo bit inattivo a cominciare dal bit più significativo e/o da quello meno significativo.

Ulteriori varianti e/o aggiunte possono essere apportate dagli esperti del ramo alle forme realizzative qui descritte ed illustrate restando nell'ambito dell'invenzione stessa. Ad esempio, il dispositivo secondo la presente invenzione comprende un registro RI nel quale viene inserita la stringa di bit da esaminare, ma è ovvio che in altre forme realizzative del dispositivo secondo la presente invenzione tale registro può non essere presente. In tal caso le linee FI saranno collegate direttamente ad altre linee e/o dispositivi esterni, come ad esempio un bus dati, un'interfaccia parallela, ecc.

#### **RIVENDICAZIONI**

- Dispositivo per trovare la posizione di un bit attivo a partire da un'estremita' di una stringa di bit, comprendente:

- una pluralita' di moduli filtranti (FUk) atti a segnalare la presenza di un bit attivo in una stringa di bit e a disattivare tutti i bit di questa stringa tranne l'eventuale bit attivo piu' vicino a detta estremita', e

- una pluralita' di moduli selettori (SMk) atti a selezionare un bus in ingresso in funzione del contenuto di una pluralita' di linee di controllo FOk ed a trasmettere in uscita il contenuto e la posizione di tale bus,

- detti moduli filtranti (FUk) e detti moduli selettori (SMk) essendo disposti su k livelli di una struttura ad albero.

- 2. Dispositivo come alla rivendicazione 1 caratterizzato dal fatto che detti moduli filtranti (FUk) sono atti a:

- analizzare una porzione di detta stringa di bit;

15

- attivare un'uscita (FLk) quando e' presente almeno un bit attivo nella porzione di stringa da esso analizzata;

- rendere disponibile su di una uscita (FOk) una configurazione binaria ottenuta disattivando tutti i bit di detta stringa tranne l'eventuale bit attivo piu' vicino a detta estremita'.

- 3. Dispositivo come alle rivendicazioni 1 e 2, caratterizzato dal fatto di comprendere anche:

- una pluralitàdi moduli filtranti del primo livello (FU1);

- una pluralita' di moduli di codifica (EN), ciascuno dei quali e' collegato alle uscite (FO1) del rispettivo modulo filtrante (FU1), idonei ad associare alla configurazione binaria che corrisponde all'uscita del corrispondente modulo filtrante di primo livello (FO1) una configurazione binaria rappresentativa

della posizione occupata dall'eventuale bit attivo.

- 4. Dispositivo come alla rivendicazione 1 caratterizzato dal fatto che detti moduli selettori (SMk) sono anche atti a:

- ricevere sull'ingresso dati le configurazioni binarie che corrispondono all'uscita dei moduli selettori (SMk-1) del livello inferiore, e

- ricevere sull'ingresso di controllo la configurazione binaria che corrisponde alle uscite (FOk) dei moduli filtranti (FUk)

- fornire in uscita una delle configurazioni binarie dell'ingresso dati assieme alla sua posizione relativamente agli altri ingressi dati.

- 5. Dispositivo secondo le precedenti rivendicazioni caratterizzata dal fatto che ogni livello di tale struttura ad albero comprende un modulo filtrante (FUk) collegato ad una pluralita' di moduli filtranti (FUk 1) del livello inferiore attraverso una pluralita' di linee (FLk 1), ed un selettore (SMk) collegato ad una pluralita' di moduli selettori (SMk 1) del livello inferiore attraverso una pluralita' di bus (EOk 1) ed al modulo filtrante (FUk) di tale livello attraverso una pluralita' di linee di controllo (FOk).

- Dispositivo secondo le precedenti rivendicazioni caratterizzato dal fatto che i moduli filtranti (FUk) sono identici tra loro.

- Dispositivo secondo le precedenti rivendicazioni caratterizzato dal fatto che i

moduli selettori (SMk) sono identici tra loro.

- 8. Dispositivo secondo le precedenti rivendicazioni caratterizzato dal fatto che i moduli di codifica (EN) sono identici tra loro.

- Dispositivo secondo una delle precedenti rivendicazioni caratterizzata dal fatto che l'uitimo livello di tale struttura ad albero comprende un modulo filtrante (FUlast)

collegato ad una pluralita' di moduli filtranti (FUlast 1) del livello inferiore attraverso una pluralita' di linee (FL/ast 1), ed un selettore (SM/ast) collegato ad

una pluralita' di moduli selettori (SM*last - 1*) del livello inferiore attraverso una pluralita' di bus (EO*last - 1*) ed al modulo filtrante (FU*last*) dell'ultimo livello attraverso una pluralita' di linee di controllo (FO*last*), il risultato della ricerca del bit attivo essendo trasmesso dal modulo selettore (SM*last*) e dal modulo filtrante (FU*last*) dell'ultimo livello, detti moduli filtranti dell'ultimo livello (FU*last*) e moduli selettori dell'ultimo livello (SM*last*) differenziantisi dai moduli filtranti e moduli selettori dei livelli inferiori (FU*k* ed SM*k*) ed operanti su un numero ridotto di linee d'ingresso e d'uscita, nel caso in cui il numero di bit della parola su cui opera la ricerca non sia multiplo intero del numero di linee entranti nel modulo filtrante di livello inferiore (FU*k*).

10. Dispositivo secondo una delle precedenti rivendicazioni, caratterizzato dal fatto che la stringa di bit da esaminare viene trasmessa attraverso 2<sup>m</sup> linee Fl raggruppate in blocchi di 2<sup>n</sup> linee, a 2<sup>m-n</sup> moduli filtranti (FU1) del primo livello.

10

15

- 11. Dispositivo secondo una delle precedenti rivendicazioni, caratterizzato dal fatto che ciascuno dei 2<sup>m-n</sup> moduli filtranti (FU1) del primo livello trasmette la stringa di 2<sup>n</sup> bit filtrata ad un codificatore (EN) il cui bus di uscita (EO1) comprende *n* linee.

- 12. Dispositivo secondo la precedente rivendicazione, caratterizzato dal fatto che i  $2^{m-n}$  moduli codificatori (EN) trasmettono la posizione dell'eventuale bit attivo attraverso  $2^{m-n}$  bus (EO1), raggruppati in blocchi di  $2^p$ , a  $2^{m-n-p}$  moduli selettori (SM2) del secondo livello.

- 13. Dispositivo secondo le precedenti rivendicazioni, caratterizzato dal fatto che i  $2^r$  moduli filtranti (FUk) del livello k segnalano l'eventuale presenza di un bit attivo attraverso  $2^r$  linee (FLk) raggruppate in blocchi di  $2^p$  linee a  $2^{r-p}$  moduli filtranti (FUk+1) del livello k+1.

- 25 14. Dispositivo secondo le precedenti rivendicazioni, caratterizzato dal fatto che ciascuno dei moduli selettori (SMk) del livello k seleziona uno dei  $2^p$  bus in

ingresso, ciascuno di q linee, in funzione del contenuto delle  $2^p$  linee di controllo (FOk) uscenti dal corrispondente modulo filtrante (FUk) del livello k e ne trasmette la posizione ed il contenuto attraverso un bus comprendente q+p linee.

- 15. Dispositivo secondo una delle precedenti rivendicazioni, caratterizzato dal fatto di comprendere mezzi per limitare la ricerca del bit attivo ad una porzione della stringa di bit in ingresso.

- 16. Dispositivo come alla rivendicazione precedente caratterizzato dal fatto che i suddetti mezzi per limitare la ricerca del bit attivo operano una mascheratura su un solo modulo filtrante (FUk) per ogni stadio k della struttura ad albero in funzione del contenuto di una pluralita di linee di condizionamento (UL e UI).

- 17. Dispositivo secondo la precedente rivendicazione caratterizzato dal fatto di comprendere almeno un modulo di controllo (LM) della limitazione della ricerca del bit attivo, il quale, in funzione del contenuto delle linee di condizionamento (UL e UI), attiva una pluralita di prime e secone linee di controllo (AI e WI) collegate ai moduli filtranti (FUk) del livello k.

- 18. Dispositivo secondo la precedente rivendicazione caratterizzato dal fatto che le prime lineedi controllo (WI) vengono generate a partire dalla parola presente su dette linee di condizionamento (UL):

- contenendo almeno un numero w di linee sufficienti alla codifica del numero n di ingressi per ogni modulo filtrante (FU) e

- essendo ricavate dalla parola (UL) escludendo un numero di bit, a partire

dal meno significativo, pari a w\*, essendo w\* il numero di stadi a monte

dello stadio considerato; dei bit rimanenti le prime linee di controllo (WI)

essendo costituiti dai k bit meno significativi.

- 25 19. Dispositivo secondo la rivendicazione 17 caratterizzato dal fatto che le seconde linee di controllo (Al) vengono generate decodificando i bit piu' significativi della

.20

suddetta parola (UL), sufficienti a selezionare il numero di moduli filtranti appartenenti a detto stadio.

Italtel spa

Italtel spa

Italtel spa

Oella Sivation

| CI         Protocoorooroorooroorooroorooroorooroorooroo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Linea |      |      |    |      |           |         |         | Contenuto | nuto     |          |         |         |      |      |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|----|------|-----------|---------|---------|-----------|----------|----------|---------|---------|------|------|------|------|

| 0000         0000         0000         0000         0001         0001         0011         0001         0000         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000 <th< td=""><td>CI</td><td></td><td>÷</td><td></td><td>0000</td><td>)00000000</td><td>0000000</td><td>0000000</td><td>0110011</td><td>00111000</td><td>00100000</td><td>0001110</td><td>0001111</td><td>001</td><td></td><td></td><td></td></th<> | CI    |      | ÷    |    | 0000 | )00000000 | 0000000 | 0000000 | 0110011   | 00111000 | 00100000 | 0001110 | 0001111 | 001  |      |      |      |

| 0000         0000         0000         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010         0010 <td< td=""><td>FI</td><td>0000</td><td>ļ.</td><td></td><td></td><td></td><td>0000</td><td>0011</td><td></td><td>0011</td><td></td><td>0100</td><td>0000</td><td>0011</td><td></td><td>0111</td><td>1001</td></td<>                               | FI    | 0000 | ļ.   |    |      |           | 0000    | 0011    |           | 0011     |          | 0100    | 0000    | 0011 |      | 0111 | 1001 |

| 00         00         00         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01         01<                                                                                                                                                                                                                                                                                                                           | F01   | 0000 | 0000 | İ  | 0000 | 0000      | 0000    | 0010    | 0010      | 0010     | 1000     | 0100    | 0000    | 0010 | 1000 | 0100 | 1000 |

| 0         0         0         1         1         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                | E01   | 8    | 8    | 00 | 8    | 8         | 00      | 01      | 01        | 01       | 11       | 10      | 00      | 01   | 11   | 10   | 11   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FL1   | 0    | 0    | 0  | 0    | 0         | 0       | П       | П         | -        | 1        | 1       | 0       | 1    | 1    | • 1  |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F02   |      | 8    | 00 |      |           | 90      | 10      |           |          | 100      | 00      |         |      | 10   | 000  |      |

| . 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E02   |      | 8    | 00 |      |           | 01      | 01      |           |          | 11(      | 01      |         |      | 11   | 01   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FL2   |      |      | C  |      |           | 1       |         |           |          | -        |         |         |      |      |      |      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | F03   |      |      |    |      |           |         |         | 010       | 00       |          |         |         |      |      |      |      |

| FL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E03   |      |      |    |      |           | •       |         | 100       | 101      |          |         |         |      |      |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FL3   |      |      |    |      |           |         |         | 1         |          |          |         |         |      |      |      |      |

Italtel spa

M1 97A 0988

| 1:00         |      |      |      |      |          |         |         | Contenuto                             | nuto     |         |          |         |      |        |      |      |

|--------------|------|------|------|------|----------|---------|---------|---------------------------------------|----------|---------|----------|---------|------|--------|------|------|

|              |      |      |      | 000  | 30101110 | 1111110 | 0010100 | 0000010111011111111111111111111111111 | 1000000  | 1111010 | 11011101 | 1100001 |      |        |      |      |

| <u>ت</u> ا ر | 0000 | 0101 | 1101 | 1111 | 1001     | 0100    | 1000    | 0000                                  | 1000     | 1000    | 1110     | 1011    | 0111 | , 0111 | 0000 | 1001 |

| F1           | 0000 |      | 0001 | 1000 | 1000     | 0100    | 0001    | 0000                                  | 1000     | 0001    | 1000     | 1000    | 0100 | 0100   | 0000 | 1000 |

| FO1          | 00   | 10   | 00   | 11   | 11       | 10      | 8       | 00                                    | 11       | 90      | 11       | 11      | 10   | 10     | 00   | 1.1  |

| FI 1         | 0    | -1   | -    | П    | -        | -       | 1       | 0                                     | 1        |         | 1        | 1       | 1    | 1      | 0    | 1    |

| EO3          |      | 8    | 0010 |      |          | 10      | 1000    |                                       |          | 10      | 1000     |         |      | 10     | 1000 |      |

| FO2          |      | 01   | 0100 |      |          | 11      | 1111    |                                       |          | 11      | 1111     |         |      | 11     | 1110 |      |

| 010          |      |      | -    |      |          |         |         |                                       |          |         |          |         |      |        |      |      |

| 777          |      |      |      |      |          |         |         | 10                                    | 1000     |         |          |         |      |        |      |      |

| 5            |      |      |      |      |          |         |         | 110                                   | 110100   |         |          |         |      |        |      |      |

| E03          |      |      |      |      |          |         |         |                                       |          |         |          |         |      |        |      |      |

| FT.3         |      |      |      |      |          |         |         | •                                     | <b>-</b> |         |          |         |      |        |      |      |

| dr           |      | 1    |      |      | 1        |         | 0       |                                       |          | -       |          |         | 0    |        |      |      |

| In           |      |      |      |      |          |         |         |                                       | 1        |         |          |         |      |        |      |      |

|              |      |      |      |      |          |         |         |                                       |          |         |          |         |      |        |      |      |

Italtel spa