(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6071556号

(P6071556)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

G06F 12/06 (2006.01)

F 1

G 06 F 12/06 515 H

請求項の数 22 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-544896 (P2012-544896)  |

| (86) (22) 出願日 | 平成22年12月17日 (2010.12.17)      |

| (65) 公表番号     | 特表2013-515299 (P2013-515299A) |

| (43) 公表日      | 平成25年5月2日 (2013.5.2)          |

| (86) 國際出願番号   | PCT/US2010/061039             |

| (87) 國際公開番号   | W02011/075649                 |

| (87) 國際公開日    | 平成23年6月23日 (2011.6.23)        |

| 審査請求日         | 平成25年12月16日 (2013.12.16)      |

| 審判番号          | 不服2015-13865 (P2015-13865/J1) |

| 審判請求日         | 平成27年7月23日 (2015.7.23)        |

| (31) 優先権主張番号  | 12/642,257                    |

| (32) 優先日      | 平成21年12月18日 (2009.12.18)      |

| (33) 優先権主張国   | 米国 (US)                       |

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

最終頁に続く

(54) 【発明の名称】省電力メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のメモリチャネルの間で分散させられたタイル化画像情報をあって、静止画像のスキャンラインを表すタイル化画像情報を、再構成されたタイル化画像情報へと再タイルするように動作するメモリ回路を備え、

前記再構成されたタイル化画像情報は、一度に1つのスキャンラインが供給されるよう前に前記複数のメモリチャネルのサブセットのうち1つのメモリチャネルに供給される、回路。

## 【請求項 2】

前記サブセット以外の前記複数のメモリチャネルの少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの少なくとも一方を電力節約モードへと選択的に制御するように動作する電力管理回路を更に備える請求項1の回路。 10

## 【請求項 3】

前記電力管理回路は前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方に対するメモリチャネル自己リフレッシュを有効化することによって前記複数のメモリチャネルの前記少なくとも1つを前記電力節約モードへと制御する請求項2の回路。

## 【請求項 4】

前記電力管理回路は前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方をパワーダウンすることに 20

よって前記複数のメモリチャネルの前記少なくとも1つのメモリチャネルを前記電力節約モードへと制御する請求項2の回路。

**【請求項5】**

前記再構成されたタイル化画像情報は圧縮される請求項1の回路。

**【請求項6】**

静止画像を検出するように動作する静止画像検出回路を更に備え、前記メモリ回路は前記静止画像検出回路が前記静止画像を検出することに応答して前記タイル化画像情報を再タイルするように動作する請求項1の回路。

**【請求項7】**

前記再構成されたタイル化画像情報に基づいてディスプレイを制御するように動作するディスプレイ制御器回路を更に備え、前記メモリ回路は前記再構成されたタイル化画像情報がどのように構成されるのかを表すタイリング情報を前記ディスプレイ制御器回路に供給するように動作する請求項1の回路。 10

**【請求項8】**

画像タイリング装置によって行われる方法であって、

複数のメモリチャネルの間で分散させられるように構成されたタイル化画像情報であつて、静止画像のスキャンラインを表す静止タイル化画像情報を、再構成されたタイル化画像情報へと再タイルすることを備え、

前記再構成されたタイル化画像情報は、一度に1つのスキャンラインが供給されるように前記複数のメモリチャネルのサブセットのうち1つのメモリチャネルに供給される、方法。 20

**【請求項9】**

前記サブセット以外の前記複数のメモリチャネルの少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの少なくとも一方を電力節約モードへと選択的に制御することを更に備える請求項8の方法。

**【請求項10】**

前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方は前記電力節約モードの場合にメモリチャネル自己リフレッシュモードにある請求項9の方法。

**【請求項11】**

前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方は前記電力節約モードの場合にパワーダウンされる請求項9の方法。 30

**【請求項12】**

前記再構成されたタイル化画像情報は圧縮される請求項8の方法。

**【請求項13】**

静止画像を検出することと、前記静止画像を検出することに応答して前記タイル化画像情報を再タイルすることと、を更に備える請求項8の方法。

**【請求項14】**

前記再構成されたタイル化画像情報がどのように構成されるのかを表すタイリング情報をディスプレイ制御器に供給することを更に備える請求項8の方法。 40

**【請求項15】**

複数のメモリチャネルの間で分散させられるように構成されたタイル化画像情報であつて、静止画像のスキャンラインを表すタイル化画像情報を、再構成されたタイル化画像情報へと再タイルするように動作するメモリ回路と、

前記再構成されたタイル化画像情報に基づいて画像をディスプレイするように動作するディスプレイと、を備え、

前記再構成されたタイル化画像情報は、一度に1つのスキャンラインが供給されるように前記複数のメモリチャネルのサブセットのうち1つのメモリチャネルに供給される、デバイス。 50

**【請求項 16】**

前記サブセット以外の前記複数のメモリチャネルの少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方を電力節約モードへと選択的に制御するように動作する電力管理回路を更に備える請求項15のデバイス。

**【請求項 17】**

前記電力管理回路は前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方に対するメモリチャネル自己リフレッシュを有効化することによって前記複数のメモリチャネルの前記少なくとも1つを前記電力節約モードへと制御する請求項16のデバイス。

**【請求項 18】**

前記電力管理回路は前記複数のメモリチャネルの前記少なくとも1つに対応するメモリインターフェース回路およびメモリバンクの前記少なくとも一方をパワーダウンすることによって前記複数のメモリチャネルの前記少なくとも1つを前記電力節約モードへと制御する請求項16のデバイス。

**【請求項 19】**

前記再構成されたタイル化画像情報は圧縮される請求項15のデバイス。

**【請求項 20】**

前記再構成されたタイル化画像情報に基づいて前記ディスプレイを制御するように動作するディスプレイ制御器回路を更に備え、前記メモリ回路は前記再構成されたタイル化画像情報がどのように構成されるのかを表すタイリング情報を前記ディスプレイ制御器回路に供給するように動作する請求項15のデバイス。

10

**【請求項 21】**

前記メモリ回路は、前記複数のメモリチャネルの1つを介してメモリ内のメモリバンクに動作可能に接続されたメモリインターフェース回路を含む請求項1の回路。

**【請求項 22】**

前記再構成されたタイル化画像情報は、前記複数のメモリチャネルの1つを介してメモリ内のメモリバンクに動作可能に接続された1つ以上のメモリインターフェース回路を通じて、分散させられる請求項8の方法。

20

**【発明の詳細な説明】****【技術分野】**

30

**【0001】**

本開示は概してメモリタイリング(memory tiling)に関し、より特定的には効率的な方法でメモリタイリングして電力消費を低減することに関する。

**【背景技術】****【0002】**

コンピュータシステムは、多くの場合、関連するDRAMメモリバンクを各々が制御する多重メモリチャネルを有している。メモリアクセス性能を改善するために、種々のサーフェス(surfaces)（例えばフレームバッファ、テクスチャ等）が多重メモリチャネルの間で分散させられる。多重メモリチャネルの間でサーフェスを分散させることは、しばしばメモリタイリングと称される。画像をレンダリング(rendering)する場合（例えば描画する(drawing)場合）、典型的には、画素を全てのメモリチャネルにわたって均等にスキャンライン(scan line)内に分散させるようにサーフェスが構成される。従って、ディスプレイスキヤンアウトの間、ディスプレイ制御器は、全てのメモリチャネルからスキヤンアウト各ラインへの読み出し要求を作成する必要がある。

40

**【発明の概要】****【発明が解決しようとする課題】****【0003】**

システムがアクティブに使用されていない場合、ディスプレイは同じ画像を何度も繰り返してディスプレイする（一般に静止画面状態又はユーザーアウェイ状態と称される）。静止画面状態にある場合には、ディスプレイデータは、電力消費を最小化するために圧縮さ

50

れ得る。しかし、圧縮を伴ったとしても、全てのチャネルは、ディスプレイデータに対するディスプレイからの要求の合間に短時間だけより低いパワーモードをエンターする必要があり且つエンターすることができるだけである。また、例えばGDDR5等の最新のDRAMデバイスは、低電力モードからの移行に多くの時間を必要とし、チャネルがメモリ要求の合間に低電力モードにエンターすることをほぼ不可能にしている。従って、既知のシステムは大量の電力を消費し得る。

#### 【0004】

上述の欠点を克服するための1つの方法は、より長いウェイクアップ時間を必要とする特定のDRAM(例えばGDDR5)の使用を避けることである。より短いウェイクアップ時間を有するDRAM(例えばDDR2/3、GDDR2/3)を用いる場合、全てのメモリチャネルがオンにされ得るし、そして画像データに値する数ラインがGPUの内部バッファ内にバースト的に入ることができる。一旦データが内部バッファ内に入ると、全てのメモリチャネルは、内部バッファがデータを排出し終えるまで低電力モードにエンターすることができる。これはしばしばディスプレイスタッタモード(display stutter mode)と称される。しかし、最新のDRAM(例えばGDDR5)のより長いウェイクアップ時間に起因して、この解決法は実用的ではない。

#### 【0005】

そこで、メモリタイミングを用いてシステムの電力消費を低減する一方で従来の回路及び方法の上述した不都合を克服するための回路及び方法に対する必要性が存在する。

#### 【図面の簡単な説明】

#### 【0006】

本発明は、以下の図面と共に下記の説明を考慮することでより容易に理解されるはずであり、図面において同様の参照番号は同様の要素を表す。

#### 【0007】

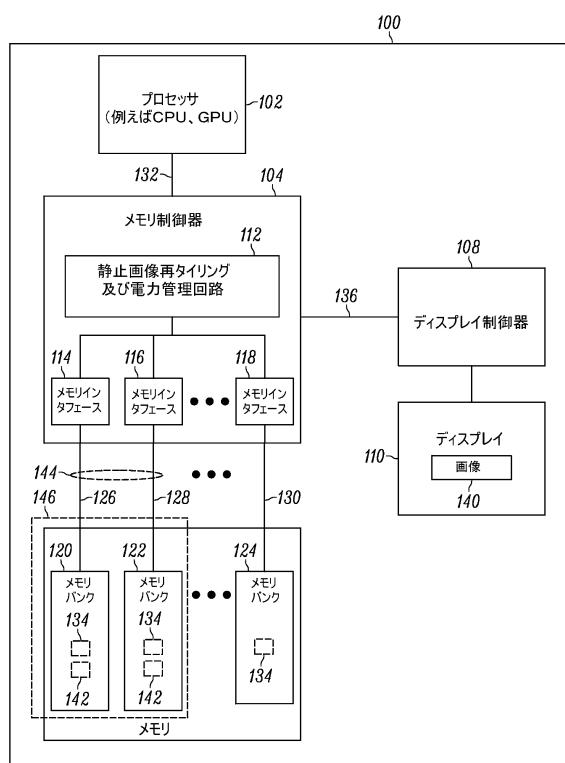

【図1】図1は静止画像再タイミング及び電力管理回路を有するデバイスの例示的な機能ブロック図である。

#### 【0008】

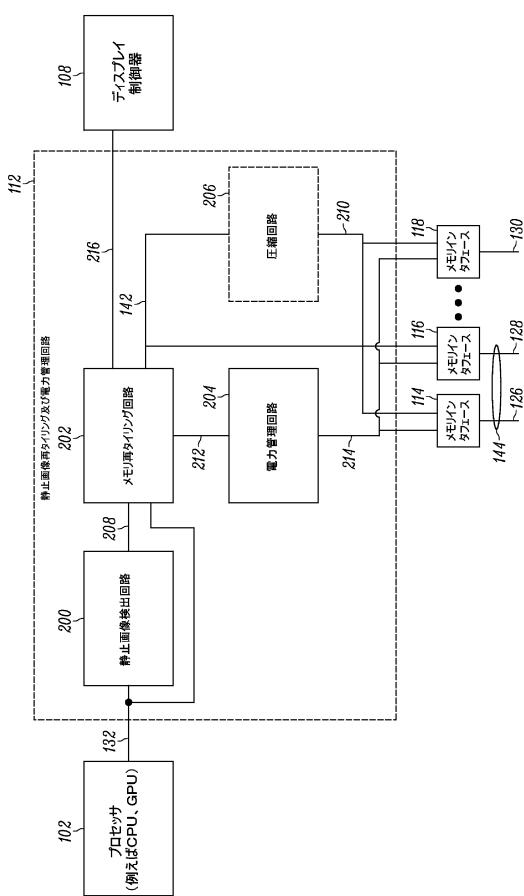

【図2】図2は静止画像再タイミング及び電力管理回路の例示的な機能ブロック図である。

#### 【0009】

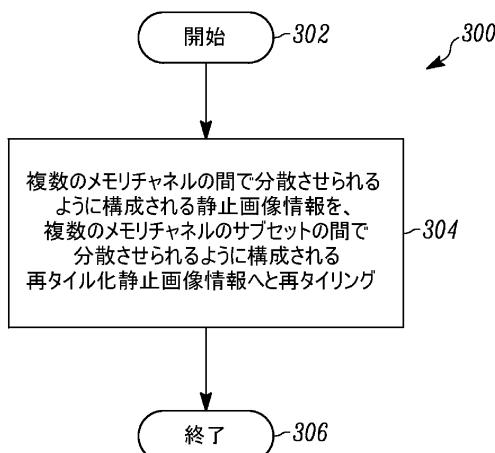

【図3】図3は静止画像再タイミング及び電力管理回路のメモリ再タイミング回路によって行われ得る例示的な動作を示すフローチャートである。

#### 【0010】

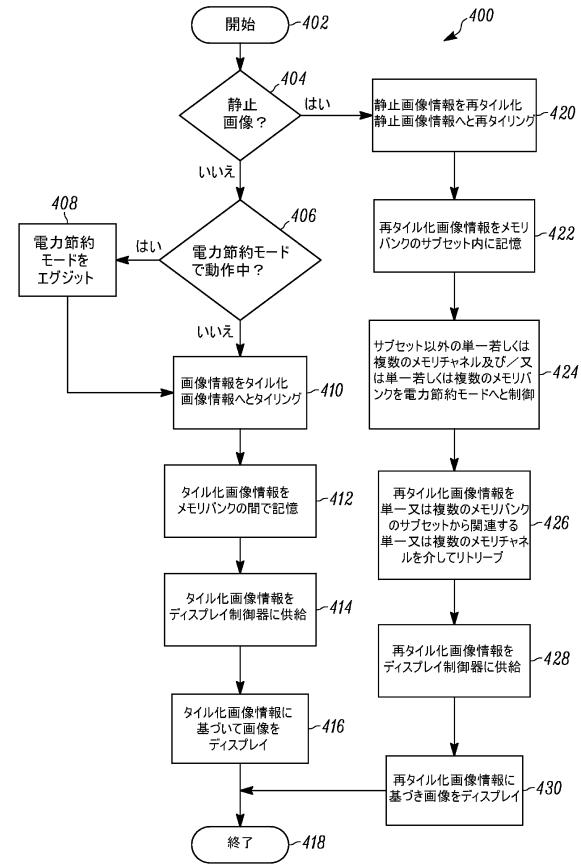

【図4】図4は静止画像再タイミング及び電力管理回路を有するデバイスによって行われ得る例示的な動作を示すフローチャートである。

#### 【発明を実施するための形態】

#### 【0011】

1つの例においては、回路はメモリ回路を含む。メモリ回路は、複数のメモリチャネルの間で分散させられるように構成される画像情報を、複数のメモリチャネルの部分の間で分散させられるように構成される再構成された画像情報へと移動させる。回路はまた、その部分内に含まれない1つ以上のメモリチャネルを電力節約モードへと選択的に制御する電力管理回路を含むこともできる。また、再構成された画像情報は、再タイル化静止画像情報を記憶するために必要なメモリチャネルの部分を少なくするために圧縮され得る。関連する方法も開示される。

#### 【0012】

回路及び方法は、幾つかの利点の中で特に、静止画像のための省電力メモリタイミングを提供し、従来の回路及び方法よりも多くのメモリチャネル及び/又はメモリバンクが電力節約モードにエンターすることを可能にする。また、回路及び方法は、更に多くのメモリチャネル及び/又はメモリバンクが電力節約モードにエンターすることができるよう、再構成された画像情報を圧縮することを提供する。他の利点は当業者によって認識され

10

20

30

40

50

るはずである。

**【0013】**

1つの例においては、回路は静止画像検出回路を含む。静止画像検出回路は静止画像を検出する。メモリ回路は、静止画像検出回路が静止画像を検出することに応答して画像情報を移動させる。

**【0014】**

1つの例においては、回路はディスプレイ制御器回路を含む。ディスプレイ制御器回路は、再構成された画像情報に基づいてディスプレイを制御する。メモリ回路は、再構成された画像情報がどのように構成されるのかを表すタイミング情報をディスプレイ制御器に供給する。

10

**【0015】**

1つの例においては、デバイスは回路及びディスプレイを含む。ディスプレイは、再構成された画像情報に基づいて静止画像をディスプレイする。

**【0016】**

ここで用いられる「回路」の用語は、電子回路、1つ以上のソフトウェア若しくはファームウェアプログラムを実行する1つ以上のプロセッサ（例えば限定はされないがマイクロプロセッサ、DSP、又は中央処理ユニット等の共有された若しくは専用のプロセッサ又はプロセッサのグループ）及びメモリ、組み合わせに係る論理回路、ASIC、並びに／又は説明される機能性を提供する他の適切な要素を含み得る。特に明記しない限り、「パワーダウン」の用語は、「回路」及び／若しくは「デバイス」のソース電力を除去し（又は低下させ）て非動作にすること、並びに／又は「回路」及び／若しくは「デバイス」が通常モードの動作にある場合よりも電力を消費しないモードの動作へと移行することを参照する。また、「パワーアップ」の用語は、「回路」及び／若しくは「デバイス」のソース電力を加え（又は増大させ）て動作状態にすること、並びに／又は「回路」及び／若しくは「デバイス」が通常モードの動作よりも電力を消費しないモードの動作から通常モードの動作へと移行することを参照する。加えて、当業者によって理解されるはずであるように、「回路」の動作、設計、及び組織化は、ハードウェア記述言語、例えばベリログ(Verilog)（商標）、VHDL、又は他の適切なハードウェア記述言語において記述され得る。

20

**【0017】**

30

図1を参照すると、デバイス100、例えば無線電話、携帯型及び／若しくは固定型のコンピュータ、プリンタ、LANインターフェース（無線又は有線）、メディアプレーヤ、ビデオデコーダ及び／若しくはデコーダ、並びに／又は任意の他の適切なデジタルデバイス、の例示的な機能ブロック図が示されている。デバイス100は、少なくとも1つのプロセッサ102（例えばCPU又はGPU）、メモリ制御器104、DRAMメモリ（例えばGDDR5）等のメモリ106、ディスプレイ制御器108、及びディスプレイ110を含む。メモリ制御器104は、プロセッサ102、メモリ106、及びディスプレイ制御器108に動作可能に接続される。ディスプレイ110は、ディスプレイ制御器108に動作可能に接続される。

**【0018】**

40

メモリ制御器104は、静止画像再タイミング及び電力管理回路(static image retiming and power management circuit)112並びに多重メモリインターフェース回路114, 116, 118を含む。この例では3つのメモリインターフェース回路114, 116, 118が図示されているが、メモリ制御器104は必要に応じてそれよりも多い又は少ないメモリインターフェース回路を含むことができる。また幾つかの実施形態においては、メモリ制御器104よりもむしろプロセッサ102が、静止画像再タイミング及び電力管理回路112を含んでいてよい。

**【0019】**

メモリ106は多重メモリバンク120, 122, 124を含む。メモリバンク120, 122, 124は、任意の適切な量の情報、例えば4MB又は8MB、を記憶すること

50

が可能である。図示されるように、メモリインタフェース回路 114, 116, 118 の各々は、それぞれのメモリチャネル 126, 128, 130 を介してメモリバンク 120, 122, 124 に動作可能に結合される。

#### 【0020】

プロセッサ 102 は、描画(drawing)又は他の適切な画像コマンドに基づき画像情報 132 を提供する。画像情報 132 に応答して、メモリ制御器 104 は画像情報 132 をタイル化画像情報(tiled image information) 134 へとタイリングし(tiles)、タイル化画像情報 134 は、メモリチャネル 126, 128, 130 の間で分散させられて構成され、続いてメモリバンク 120, 122, 124 の間で記憶される。1つの実施形態においては、タイル化画像情報 134 は、メモリチャネル 126, 128, 130 及びメモリタイルバンク 120, 122, 124 の間で均等に分散させられる。10

#### 【0021】

メモリ制御器 104 は、タイル化画像情報 134 をディスプレイ制御器 108 にインターフェース 136 を介して供給する。タイル化画像情報 134 に応答して、ディスプレイ制御器 108 は、画像 140 をディスプレイするために、インターフェース 138 を介してディスプレイ 110 を制御する。

#### 【0022】

画像 140 が静止画像であること（例えば画像 140 が変化しないままであること）を画像情報 132 が示す場合、静止画像再タイリング及び電力管理回路 112 は、タイル化画像情報 134 を再タイル化静止画像情報(retiled static image information) 142（例えば再構成された画像情報）へと再タイリングし(retiles)（例えば移動し）、再タイル化静止画像情報 142 は、メモリチャネル 126, 128, 130 のサブセット 144 の間で分散させられるように構成され、続いてメモリバンク 120, 122, 124 の対応するサブセット 146 の間で記憶される。20

#### 【0023】

より具体的には、静止画像再タイリング及び電力管理回路 112 は、再タイル化静止画像情報 142 を（例えば一度に1つのスキャンラインを）、メモリチャネル 126, 128, 130 の1つに、対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなると、静止画像再タイリング及び電力管理回路 112 は、残りの再タイル化静止画像情報 142 を、メモリチャネル 126, 128, 130 の別の1つに、対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。このプロセスは、メモリチャネルのサブセット 144 に対応するメモリバンクのサブセット 146 内に全ての再タイル化静止画像情報 142 が記憶されるまで繰り返す。30

#### 【0024】

この例では、メモリチャネルのサブセット 144 はメモリチャネル 126, 128 を含み、またメモリバンクのサブセット 146 はメモリバンク 120, 122 を含むが、サブセット 144, 146 は、再タイル化静止画像情報 142 を記憶するのにどれくらいの容量が必要であるのかに応じて、より多くの又はより少ないメモリチャネル及びチャネルバンクを含むことができる。40

#### 【0025】

再タイル化静止画像情報 142 の全てがメモリバンクのサブセット 146 内に一旦記憶されると、静止画像再タイリング及び電力管理回路 112 は、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）及び/又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）を選択的に電力節約モードへと制御する。

#### 【0026】

1つの例において、電力節約モードは、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）をパワーダウンすること及び/又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）をパワーダウンすることを含むことができる。この例においては、サブセット 144 以外のメモリチャネルに対応するメモリチャネルイ50

ンタフェース回路（例えばメモリインターフェース回路 118）もまたパワーダウンされてよい。

#### 【0027】

別の例において、電力節約モードは、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）を自己リフレッシュモードへと制御すること及び／又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）を自己リフレッシュモードへと制御することを含むことができる。

#### 【0028】

別の例示的な電力節約モードは、サブセット 146 以外のメモリバンク（例えばメモリバンク 124）及び／又はサブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）のメモリクロック周波数を下げるなどを含むことができる。10

#### 【0029】

更に別の例においては、サブセット 146 以外のメモリバンク（例えばメモリバンク 124）及び／又はサブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）に供給される電圧が下げられてよい。また、必要に応じて前述の例示的な電力節約モードの 1つ以上が組み合わされてよい。

#### 【0030】

ディスプレイ制御器 108 は、再タイル化静止画像情報 142 に基づいてディスプレイ 110 を制御する。より具体的には、メモリ制御器 104 は、再タイル化静止画像情報 142 をメモリバンクのサブセット 146（例えばメモリバンク 120, 122）からメモリチャネルの対応するサブセット 144（例えばメモリチャネル 126, 128）を介してリトリーブし(retrieves)、そして再タイル化静止画像情報 142 をディスプレイ制御器 108 に供給する。再タイル化静止画像情報 142 に応答して、ディスプレイ制御器 108 は、ディスプレイ 110 が画像 140 をディスプレイするようにこれを制御し、この例では画像 140 は静止画像である。また 1 つの実施形態においては、静止画像再タイリング及び電力管理回路 112 は、再タイル化静止画像情報 142 がどのように構成されるのかを表す情報をディスプレイ制御器 108 にインタフェース 136 を介して提供することができる。ディスプレイ制御器 108 は、この情報を再タイル化静止画像情報 142 と共に用いて、ディスプレイ 110 が画像 140 をディスプレイするようにこれを制御することができる。20

#### 【0031】

画像 140 が動画像であること（例えば画像 140 が静止でないこと）を画像情報 132 が示す場合、静止画像再タイリング及び電力管理回路 112 は、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）及び／又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）が電力節約モードをエグジットして通常動作モードに戻るようこれらを選択的に制御する。

#### 【0032】

1 つの例において、電力節約モードをエグジットすることは、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）をパワーアップすること及び／又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）をパワーアップすることを含むことができる。この例においては、サブセット 144 以外のメモリチャネルに対応するメモリチャネルインターフェース回路（例えばメモリインターフェース回路 118）もまたパワーアップされてよい。40

#### 【0033】

別の例において、電力節約モードをエグジットすることは、サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）が自己リフレッシュモードをエグジットするように制御すること及び／又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）が自己リフレッシュモードをエグジットするように制御することを含むことができる。

#### 【0034】

10

20

30

40

50

更に別の例において、電力節約モードをエグジットすることは、サブセット 146 以外のメモリバンク（例えばメモリバンク 124）及び／又はサブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）のメモリクロック周波数を上げることを含むことができる。

#### 【0035】

更に別の例においては、サブセット 146 以外のメモリバンク（例えばメモリバンク 124）及び／又はサブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）に供給される電圧が上げられてよい。また、必要に応じて前述の例示的な電力節約エグジットモードの 1 つ以上が組み合わされてよい。

#### 【0036】

サブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）及び／又はサブセット 146 以外のメモリバンク（例えばメモリバンク 124）が一旦電力節約モードをエグジットして通常動作モードに戻ると、メモリ制御器 104 は画像情報 132 をタイル化画像情報 134 へとタイリングし、タイル化画像情報 134 は、メモリチャネル 126, 128, 130 の間で均等に分散させられて構成され、続いて関連するメモリバンク 120, 122, 124 内に記憶される。

#### 【0037】

メモリ制御器 104 は、インターフェース 136 を介してディスプレイ制御器 108 にタイル化画像情報 134 を供給する。タイル化画像情報 134 に応答して、ディスプレイ制御器 108 は、ディスプレイ 110 が画像 140 をディスプレイするように、インターフェース 138 を介してディスプレイ 110 を制御する。

#### 【0038】

次に図 2 を参照すると、静止画像再タイリング及び電力管理回路 112 の例示的な機能プロック図が示されている。静止画像再タイリング及び電力管理回路 112 は、静止画像検出回路 200、メモリ再タイリング回路 202、及び電力管理回路 204 を含み、そして幾つかの実施形態では圧縮回路 206 を更に含む。静止画像検出回路 200 は、画像情報 132 に基づいて検出された静止画像情報 208 を提供する。例えば静止画像検出回路 200 は、画像 140 が変化しないままであるべきことを画像情報 132 が示している場合に、検出された静止画像情報 208 を提供する。

#### 【0039】

検出された静止画像情報 208 に応答して、メモリ再タイリング回路 202 は、メモリチャネル 126, 128, 130 の間で実質的に均等に分散させられるように構成される静止画像情報 132 を、メモリチャネルのサブセット 144（例えばメモリチャネル 126, 128）の間で分散させられるように構成される再タイル化静止画像情報 142 へと再タイリングする。

#### 【0040】

より具体的には、メモリ再タイリング回路 202 は、再タイル化静止画像情報 142 を（例えば一度に 1 つのスキャンラインを）、メモリチャネル 126, 128, 130 の 1 つに、対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなると、メモリ再タイリング回路 202 は、残りの再タイル化静止画像情報 142 を、メモリチャネル 126, 128, 130 の別の 1 つに、対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。このプロセスは、メモリチャネルのサブセット 144 に対応するメモリバンクのサブセット 146 内に全ての再タイル化静止画像情報 142 が記憶されるまで繰り返す。

#### 【0041】

圧縮回路 206 を含む実施形態においては、メモリ再タイリング回路 202 は、再タイル化静止画像情報 142 を（例えば一度に 1 つのスキャンラインを）圧縮回路 206 に供給する。再タイル化静止画像情報 142 に応答して、圧縮回路 206 は、圧縮された再タイル化静止画像情報 210 を、メモリチャネル 126, 128, 130 の 1 つに、対応す

10

20

30

40

50

るメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなると、圧縮回路 206 は、残りの圧縮された再タイル化静止画像情報 210 を、メモリチャネル 126, 128, 130 の別の 1 つに、対応するメモリバンク 120, 122, 124 がもはや容量を有していなくなるまで供給する。このプロセスは、メモリチャネルのサブセット 144 に対応するメモリバンクのサブセット 146 内に全ての圧縮された再タイル化静止画像情報 210 が記憶されるまで繰り返す。

#### 【0042】

再タイル化静止画像情報 210 は、任意の適切な方法で圧縮され得る。例えば圧縮回路 206 は、圧縮された静止画像情報 210 を提供するために、任意の適切な非可逆又は可逆の圧縮方法論を用いて再タイル化静止画像情報 142 を圧縮することができる。圧縮の結果として、圧縮された静止画像情報 210 を記憶するために必要なメモリチャネル及びメモリバンクが少なくなり、それにより、より多くのメモリチャネル及び / 又はメモリバンクが電力節約モードにエンターすることが可能になる。

#### 【0043】

再タイル化画像情報 142 (又は圧縮された再タイル化画像情報 210) の全てがメモリバンクのサブセット 146 内に一旦記憶されると、電力管理回路 204 は、サブセット 144 以外のメモリチャネル及び / 又はサブセット 146 以外のメモリバンクを電力節約モードへと制御する。例えば 1 つの実施形態においては、メモリ再タイリング回路 202 は、再タイル化画像情報 142 (又は圧縮された再タイル化画像情報 210) の全てがメモリバンクのサブセット 146 内に記憶されたときに、イネーブル電力節約情報 212 を電力管理回路 204 に提供する。イネーブル電力節約情報 212 に応答して、電力管理回路 204 は、電力節約モード制御情報 214 を供給して、サブセット 144 以外のメモリチャネル及び / 又はサブセット 146 以外のメモリバンクを電力節約モードへと制御する。

#### 【0044】

加えて、メモリ再タイリング回路 202 は、再タイリング構成情報 216 をディスプレイ制御器 108 に供給することができる。再タイリング構成情報 216 は、再タイル化静止画像情報 142 (又は圧縮された再タイル化静止画像情報 210) がどのように構成されるのかを表す。従って、ディスプレイ制御器 108 は、次いで再タイリング構成情報 216 を用いて、ディスプレイ 110 が画像 140 をディスプレイするようにこれを制御するのを支援することができる。

#### 【0045】

次に図 3 を参照すると、メモリ再タイリング回路によって行われ得る例示的な動作が一般的に 300 で示されている。プロセスは、画像 140 が変化しないまま (例えば静止画像) であるべきことを画像情報 132 が示している場合に、302 で開始する。304 では、メモリ再タイリング回路 202 は、メモリチャネル 126, 128, 130 の間で分散させられるように構成される静止画像情報 132 を、メモリチャネルのサブセット 144 の間で分散させられるように構成される再タイル化静止画像情報 142 へと再タイリングする。プロセスは 306 で終了する。

#### 【0046】

次に図 4 を参照すると、静止画像再タイリング及び電力管理回路 112 を有するメモリ制御器 104 によって行われ得る例示的な動作が一般的に 400 で示されている。プロセスは、プロセッサ 102 によって画像情報 132 が提供された場合に開始する。404 では、静止画像検出回路 200 は、画像情報 132 が静止画像であるかどうかを検出する。画像情報 132 が静止画像でない (例えば動画像) 場合には、メモリ再タイリング回路 202 は、406 で、メモリチャネルのサブセット 144 及び / 又はメモリバンクのサブセット 146 が電力節約モードで動作しているかどうかを決定する。

#### 【0047】

メモリチャネルのサブセット 144 及び / 又はメモリバンクのサブセット 146 が電力

10

20

30

40

50

節約モードで動作している場合には、電力管理回路 204 は、408 で、メモリチャネルのサブセット 144 及び / 又はメモリバンクのサブセット 146 が電力節約モードをエグジットして通常モードの動作に戻るようにこれらを制御し、そして 410 に進む。一方、メモリチャネルのサブセット 144 及び / 又はメモリバンクのサブセット 146 が電力節約モードで動作していない場合には、プロセスは直接 410 に進む。また幾つかの実施形態においては、電力節約モードのままで 410 に進むことが望ましい場合がある。例えば、画像に対する変化が集中的でなく且つ / 又はレンダリング性能が重要でない場合には、電力節約モードのまま直接 410 に進むことが望ましい。従って幾つかの実施形態においては、408 は随意的であってよい。

## 【0048】

10

410 では、メモリ制御器 104 は、画像情報 132 を、メモリチャネル 126, 128, 130 の全ての間で均等に分散させられるように構成されるタイル化画像情報 134 へとタイミングする。412 では、メモリ制御器 104 は、タイル化画像情報 134 を、メモリチャネル 126, 128, 130 を介してメモリバンク 120, 122, 124 内に記憶させる。

## 【0049】

20

414 では、メモリ制御器 104 は、メモリバンク 120, 122, 124 内に記憶されるタイル化画像情報 134 をリトリープし、そしてタイル化画像情報 134 をディスプレイ制御器 108 に供給する。416 では、ディスプレイ制御器 108 は、タイル化画像情報 134 に基づいてディスプレイ 110 が画像 140 をディスプレイするようにこれを制御する。プロセスは 418 で終了する。

## 【0050】

画像情報 132 が静止画像を表していると静止画像検出回路 200 が 404 で決定すると、メモリ再タイミング回路 202 は、420 で、メモリチャネル 126, 128, 130 の全て（又はメモリバンク 120, 122, 124 の全て）の間で分散させられるように構成される静止画像情報 132 を、メモリチャネルのサブセット 144（又はメモリバンクのサブセット 146）の間で分散させられるように構成される再タイル化画像情報 142 へと再タイミングする。

## 【0051】

30

422 では、メモリ再タイミング回路 202 は、再タイル化画像情報 142 を、メモリチャネルのサブセット 144 を介してメモリバンクのサブセット 146 の間で記憶させる。この例では図示されていないが、圧縮回路 206 は、必要に応じて再タイル化画像情報 142 を圧縮して、次いで圧縮された再タイル化画像情報 210 を記憶させることができる。

## 【0052】

40

424 では、電力管理回路 204 は、メモリチャネルのサブセット 144 以外のメモリチャネル（例えばメモリチャネル 130）及び / 又はメモリバンクのサブセット 146 以外のメモリバンク（例えばメモリバンク 124）を電力節約モードへと制御する。426 では、メモリ制御器 104 は、再タイル化画像情報 142（又は圧縮された再タイル化画像情報 210）をメモリバンクのサブセット 146 からメモリチャネルのサブセット 144 を介してリトリープする。

## 【0053】

428 では、メモリ制御器は、再タイル化画像情報 142 をディスプレイ制御器 108 に供給する。図示はしないが、圧縮された再タイル化画像情報 210 がリトリープされる場合には、メモリ制御器 104 が再タイル化画像情報 142 を供給するのに先立ち、圧縮回路 206 が圧縮された再タイル化画像情報 210 を復元する(uncompresses)。430 では、ディスプレイ制御器 108 は、再タイル化画像情報 142 に基づいてディスプレイ 110 が画像 140 をディスプレイするようにこれを制御する。プロセスは 418 で終了する。

## 【0054】

50

以上説明したように、幾つかの利点の中で特に、回路及び方法は、静止画像のための省電力メモリタイリングを提供し、従来の回路及び方法よりも多くのメモリチャネル及び／又はメモリバンクが電力節約モードにエンターすることを可能にする。また、回路及び方法は、更に多くのメモリチャネル及び／又はメモリバンクが電力節約モードにエンターすることができるよう、再タイル化静止画像情報を圧縮することを提供する。他の利点は当業者によって認識されるはずである。

【 0 0 5 5 】

この開示は特定の例を含むが、開示はそれに限定されないことが理解されるべきである。図面、明細書、及び以下の特許請求の範囲を研究することによって、当業者であれば、本開示の精神及び範囲から逸脱することなしに、多くの修正、変更、変化、置換、及び均等なものに気付くはずである。

10

【 図 1 】

【図2】

【図3】

【図4】

---

フロントページの続き

(73)特許権者 508301087

エーティーアイ・テクノロジーズ・ユーエルシー

A T I T E C H N O L O G I E S U L C

カナダ、オンタリオ エル3ティー 7エックス6、マーカム、コマース バリー ドライブ

イースト 1

One Commerce Valley Drive East, Markham, Ontario, L3T 7X6 Canada

(74)代理人 100108833

弁理士 早川 裕司

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 グレッグ サドウスキー

アメリカ合衆国、02139 マサチューセッツ州、ケンブリッジ、ハーバード ストリート

321、#303

(72)発明者 ウォーレン フリット クルーガー

アメリカ合衆国、94087 カリフォルニア州、サンベイル、ダノック ウェイ 1309

(72)発明者 ジョン ウェイクフィールド ブラザーズ

アメリカ合衆国、94515 カリフォルニア州、カリストガ、マウンテン ホーム ランチ ロード 4225

(72)発明者 スティーブン デイビッド プレザント

アメリカ合衆国、95119 カリフォルニア州、サンノゼ、サン アンセルモ ウェイ 645

6

(72)発明者 デイビッド アイ.ジェイ.グレン

カナダ、オンタリオ エム4エス 2エックス5、トロント、ホイル アベニュー 11

合議体

審判長 石井 茂和

審判官 高木 進

審判官 須田 勝巳

(56)参考文献 特開2004-205577(JP,A)

特開2004-112718(JP,A)

特開2006-301724(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00-12/06

G06F 13/16-13/18