### **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>3</sup>:

H05K 13/00; H01C 1/16

A1

(11) International Publication Number: WO 84/ 01259

(43) International Publication Date: 29 March 1984 (29.03.84)

(21) International Application Number: PCT/SE83/00326

(22) International Filing Date: 14 September 1983 (14.09.83)

(31) Priority Application Number:

8205343-0

(32) Priority Date:

17 September 1982 (17.09.82)

(33) Priority Country:

SE

(71) Applicant (for all designated States except US): TELEF-ONAKTIEBOLAGET L M ERICSSON [SE/SE]; S-126 25 Stockholm (SE).

(72) Inventors; and

- (75) Inventors/Applicants (for US only): OLOFSSON, Lars, Anders [SE/SE]; Stallbacken 4, S-175 43 Järfälla (SE). BJÖRKLUND, Fritz, Lars, Gunnar [SE/SE]; Måndalsvägen 24, S-135 54 Tyresö (SE).

- (74) Agents: GAMSTORP, Bengt et al.; Telefonaktiebolaget L M Ericsson, S-126 25 Stockholm (SE).

(81) Designated States: DE (European patent), FR (European patent), GB (European patent), JP, US.

Published

With international search report.

(54) Title: A METHOD OF PRODUCING ELECTRONIC COMPONENTS

#### (57) Abstract

Method of producing electronic components, e.g. resistors, capacitances, fuses and the like. The components consist of an insulating substrate with electrical connections, connected by layers or wires. In accordance with the invention, the components (5) and their connections are applied to a common substrate (1), which is provided with fractural impressions (6). The components lie in the areas between the impressions. The connections are produced by making holes in the substrate along certain of the fractural impressions (6), and the envelope surface of the holes being coated with conductive material (4), as well as an area about the holes on both sides of the substrate. The components (5) are connected to the connections, subsequent to which the substrate is divided into individual components along the fractural impressions. Certain components require adjustment in manufacture, e.g. by laser beam. This adjustment is carried out before the substrate is divided up.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT   | Austria                               | LI | Liechtenstein            |  |

|------|---------------------------------------|----|--------------------------|--|

| . AU | Australia                             | LK | Sri Lanka                |  |

| BE   | Belgium                               | LU | Luxembourg               |  |

| BR   | Brazil                                | MC | Мопасо                   |  |

| CF   | Central African Republic              | MG | Madagascar               |  |

| CG   | Congo                                 | MR | Mauritania               |  |

| CH   | Switzerland                           | MW | Malawi                   |  |

| CM   | Cameroon                              | NL | Netherlands              |  |

| DE   | Germany, Federal Republic of          | NO | Norway                   |  |

| DK   | Denmark                               | RO | Romania                  |  |

| FI   | Finland                               | SE | Sweden                   |  |

| FR   | France                                | SN | Senegal                  |  |

| GA   | Gabon                                 | SU | Soviet Union             |  |

| GB   | United Kingdom                        | TD | Chad                     |  |

| HU   | Hungary                               | TG | Togo                     |  |

| JP   | Japan                                 | US | United States of America |  |

| KP   | Democratic People's Republic of Korea |    |                          |  |

### A METHOD OF PRODUCING ELECTRONIC COMPONENTS

#### TECHNICAL FIELD

The invention relates to a method of producing electronic components (resistors, capacitances, fuses and the like) which includes an insulating substrate provided with layers or wires and electrical connections for the components.

#### BACKGROUND ART

Microelectronic components have so small dimensions that difficulties occur in their manufacture. This applies to handling individual components in the manufacturing process itself, as well as their after treatment. One example of the former is fuses, of which the dimensions up to now must exceed a given minimum, because a reduction thereof would result in complicated time-consuming handling. An example of the latter is resistances which require adjustment after manufacture.

### DISCLOSURE OF INVENTION

The basic concept of the invention is to manufacture electronic components of the type mentioned in the introduction on a common substrate and to perform all operations before the substrate is divided up to individual components.

#### PREFERRED EMBODIMENT

A preferred embodiment of the invention will now be described in conjunction with the figures where

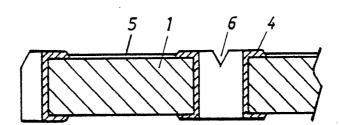

Figure 1 is a portion of the substrate provided with resistors

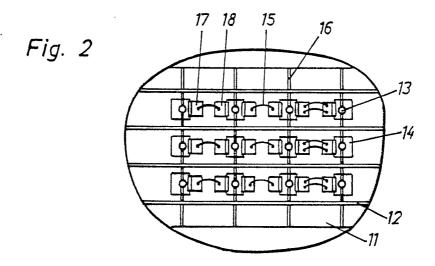

Figure 2 is a portion of the substrate provided with wire fuses

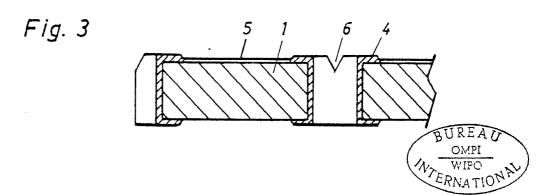

20 Figure 3 is a cross-section to a larger scale of a resistor with connections.

A non-conductive substrate 1, according to figure 1, is provided during the course of production with a first set of parallel fractural impressions 2, e.g. grooves, which define strips with the width of the ready

BUREAU

OMPI

WIPO

WIPO

ERNATIONEL

component. The substrate is then provided with uniformly spaced through holes 3 along the central lines of these strips, so that the holes form columns. The substrate is provided with a second set of parallel fractural impressions 6 passing through the holes 3. The impressions 6 are at 5 right angles to the impressions 2 and define the length of the component. The inside of each hole, together with a minor area round the hole on both sides of the substrate, is coated with a metal paste 4 to form electrical connections for the component. A layer of electrically resistive material 5 is deposited in the form of squares in the areas 10 defined by the fractural impressions, such that all squares will be separated from each other but each has contact with two electrical connections, the squares thus being connected in series in rows. The substrate with its resistors is heated to sinter the metal paste 4. After sintering, the individual resistances of the resistors are 15 measured and the values adjusted e.g. by treatment with a laser beam, sandblasting or the like. The resistors are possibly coated with a protective layer, after which the substrate is broken into strips along the impressions 2, and the strips thus obtained are broken into individual components along the impressions 6 at the holes. In the 20 latter case, the rupture line passes through the centres of the holes. The conductive coating of the holes is thus parted into two halves which constitute electrical connections for the individual components. Figure 2 illustrates a substrate 11, provided with fractural impressions 12,16 and holes 13, in the same way as the embodiment of figure 1. The 25 holes are provided with a conductive coating 14, which is sintered to provide electrical connections. A layer of electrically conductive material is applied, in the form of two mutually separated squares 17 and 18 within a field defined by the fractural impressions, such that these squares are each in electrical contact with a connection. 30 In contradistinction to the method according to figure 1, metal wires 15, constituting fuse elements, are fastened between the squares 17 and 18, e.g. by thermo-compression or supersonic welding. A protective coating, e.g. of plastics, can be applied over the metal wires. In an alternative method of producing fusable fuses, a layer is applied between 35 two connections in the manner apparent from the description applying to figure 1. These layers are electrically conductive in this application, and their thickness, width and length adapted to a given current strength

at which the layer fuses. The layer may be heatinsulated from the substrate with the aid of a glass coating, whereby its ability to withstand current is decreased. The final step in the manufacture of fusable fuses is performed in the same way as with the method according to figure 1, namely in that the individual components are obtained by the common substrate being ruptured along the fractural impressions. Figure 3 illustrates an electrical connection in cross-section. The metal paste is applied by impressing from one or two sides, according to need, subsequent to which the viscous material forms a coating on 10 the inner wall of the hole. As will be seen, the conductive material constituting the coating of the hole, is in electrical contact with the layer 5. The method in accordance with the above signifies the . advance in respect to the prior art residing in that the individual components can be processed in one operation during manufacture, while 15 these are still in one continuous unit, where each unit embraces a number of components in the order of magnitude of 100, for example. Such operations are enabled since each component has a well-defined fixed location in the common substrate. An advantage is obtained if, in accordance with the invention, the electrical connections are made 20 available from both of the substrate. This makes the ready components easy to assemble on a printed board assembly with the aid of so-called surface soldering.

4

### CLAIMS

A method of producing electronic components (resistors, capacitances, fuses and the like) which includes an insulating substrate provided with layers or wires and electrical connections for the components, the components and their connections being applied to a common substrate within individual areas which are defined by fractural impressions, characterized in that the electrical connections are produced by holes being made in the insulating substrate along said fractural impressions, the envelope surface of the holes together with an area round the holes on both sides of the substrate being provided with a conductive coating,

such that the components come into electrical contact with the coating in the hole, subsequent to which the substrate is divided up along the fractural impressions such that the respective halves of the envelope surface constitute connection surface for the contiguous component.

2. Method as claimed in claim 1, characterized in that in manufacture of components, having an electrical value that must be adjusted during manufacture, e.g. by treatment with a laser beam, sandblasting or the like, a measuring device is connected to the components defined by the fractural impressions for measuring their electrical value, and in that the adjustment is carried out before dividing up components along the fractural impressions.

Fig. 1

## INTERNATIONAL SEARCH REPORT

International Application No PCT/SE83/00326

I. CLASSIFICATION OF SUBJECT MATTER (if several classification symbols apply, indicate all) 3 According to International Patent Classification (IPC) or to both National Classification and IPC 3 H 05 K 13/00, H 01C 1/16II. FIELDS SEARCHED Minimum Documentation Searched + Classification Symbols Classification System H 05 K 13/00,04, 3/40,42, H 01 C 1/14,16,22,24 IPC 3 338:195, 203; <u>29:</u> 621 US. Cl Documentation Searched other than Minimum Documentation to the Extent that such Documents are included in the Fields Searched 6 SE, NO, DK, FI classes as above III. DOCUMENTS CONSIDERED TO BE RELEVANT 14 Citation of Document, 16 with indication, where appropriate, of the relevant passages 17 Relevant to Claim No. 18 DE, Al, 2 527 037 (QY PARAMIC AB) 1 Υ 8 January 1976 FR 2 275 862 US 3 983 528 GB 1 481 933 JP 51 013 946 SE 7 506 920 SE 395 326 8007792-8 (TELEFON AB L M ERICSSON) SE, A, 6 May 1982 2 086 139 (KOLLMORGEN TECHNOLOGIES 1 CORPORATION) 6 May 1982 DE 3 008 143 NL 8 101 050 FR 2 482 406 JP 56 162 899 US 4 374 868 SE 8 101 360 fater document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the Special categories of cited documents: 15 "A" document defining the general state of the art which is not considered to be of particular relevance invention earlier document but published on or after the international filling date document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled "O" document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family IV. CERTIFICATION Date of Mailing of this international Search Report \$ Date of the Actual Completion of the International Search 1 1983 -11- 2 9 1983-10-31 Signature of Authorized Officer 10 International Searching Authority 1 Sven-Olof Wirlée Swedish Patent Office

| Category* Citation of Document, is with indication, where appropriate, of the relevant passages II Relevant to Claim No. is  Y IMB Technical Disclosura Bulletin, vol. 23, no. 6, November 1980, p. 2256 W.L. UNDER-KOFLER: "Etchback of Insulation on Wire In A Multiwire Board"  Y AU, B, 59 996/69 (TECHNOGRAPH LIMITED) 4 March 1971  A IBM Technical Disclosura Bulletin, vol. 13, no. 5, October 1970, p. 1105, A. Bross et al: "Modular Resistor Array"  A US, A, 4 228 418 (J.R. PIEDMONT ET AL) 14 October 1980  A GB, A, 1 236 580 (N.G. WORSTER) 23 June 1971 2 DE 1 816 067 FR 1 596 267 US 3 541 491  X US, A, 4 032 881 (D.L.SINGLETON) 28 June 1977 especially figure 5 | III. DOCUMENTS CONSIDERED TO BE RELEVANT (CONTINUED FROM THE SECOND SHEET) |            |                                                                                 |                         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------|-------------------------|--|--|

| no 6, November 1980, p. 2256 W.L. UNDER- KOFLER: "Etchback of Insulation on Wire In A Multiwire Board"  Y AU, B, 59 996/69 (TECHNOGRAPH LIMITED) 4 March 1971  A IBM Technical Disclosura Bulletin, vol 13 no 5, October 1970, p. 1105, A. Bross et al: "Modular Resistor Array"  A US, A, 4 228 418 (J.R. PIEDMONT ET AL) 14 October 1980  A GB, A, 1 236 580 (N.G. WORSTER) 23 June 1971                                                                                                                                                                                                                                                                                             | Category *                                                                 | Citation o | f Document, 18 with indication, where appropriate, of the relevant passages 17  | Relevant to Claim No 18 |  |  |

| A IBM Technical Disclosura Bulletin, vol 13 no 5, October 1970, p. 1105, A. Bross et al: "Modular Resistor Array"  A US, A, 4 228 418 (J.R. PIEDMONT ET AL) 14 October 1980  A GB, A, 1 236 580 (N.G. WORSTER) 23 June 1971                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Y                                                                          | no<br>KO   | 6, November 1980, p. 2256 W.L. UNDER-<br>FLER: " Etchback of Insulation on Wire |                         |  |  |

| no 5, October 1970, p. 1105, A. Bross et al: "Modular Resistor Array"  A US, A, 4 228 418 (J.R. PIEDMONT ET AL) 1 14 October 1980  A GB, A, 1 236 580 (N.G. WORSTER) 1 23 June 1971 & DE 1 816 067 FR 1 596 267 US 3 541 491  X US, A, 4 032 881 (D.L.SINGLETON) 2                                                                                                                                                                                                                                                                                                                                                                                                                     | Y                                                                          | AU, B,     |                                                                                 | 1                       |  |  |

| 14 October 1980  A GB, A, 1 236 580 (N.G. WORSTER) 23 June 1971 & DE 1 816 067 FR 1 596 267 US 3 541 491  X US, A, 4 032 881 (D.L.SINGLETON)  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A                                                                          | no         | 5, October 1970, p. 1105, A. Bross                                              |                         |  |  |

| 23 June 1971<br>& DE 1 816 067<br>FR 1 596 267<br>US 3 541 491<br>X US, A, 4 032 881 (D.L.SINGLETON) 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | А                                                                          | US, A,     |                                                                                 | 1                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | А                                                                          |            | 23 June 1971<br>DE 1 816 067<br>FR 1 596 267                                    | 1                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X                                                                          | US, A,     |                                                                                 | 2                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |            |                                                                                 |                         |  |  |