(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7543960号

(P7543960)

(45)発行日 令和6年9月3日(2024.9.3)

(24)登録日 令和6年8月26日(2024.8.26)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 29/78 (2006.01)  | F I | H 01 L | 29/78 | 6 5 2 N |

| H 01 L | 29/12 (2006.01)  |     | H 01 L | 29/78 | 6 5 2 T |

| H 01 L | 29/06 (2006.01)  |     | H 01 L | 29/78 | 6 5 2 D |

| H 01 L | 21/336 (2006.01) |     | H 01 L | 29/78 | 6 5 3 A |

|        |                  |     | H 01 L | 29/78 | 6 5 2 M |

請求項の数 13 (全25頁) 最終頁に続く

(21)出願番号 特願2021-51536(P2021-51536)

(22)出願日 令和3年3月25日(2021.3.25)

(65)公開番号 特開2022-149402(P2022-149402)

A)

(43)公開日 令和4年10月6日(2022.10.6)

審査請求日 令和5年2月1日(2023.2.1)

(73)特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74)代理人 110000110

弁理士法人 快友国際特許事務所

手賀 直樹

愛知県刈谷市昭和町1丁目1番地 株式

会社デンソー内

(72)発明者 片野 拓真

愛知県刈谷市昭和町1丁目1番地 株式

会社デンソー内

審査官 杉山 芳弘

最終頁に続く

(54)【発明の名称】 半導体装置とその製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体装置(1, 2, 3, 4, 5, 6, 7)であって、

アクティブ領域(10A)と、前記アクティブ領域の周囲を一巡するように配置されている外周領域(10C)と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域(10B)と、に区画されており、第1主面(10a)と第2主面(10b)を有する半導体層(10)と、

トレンチゲート(30)と、を備えており、

前記半導体層は、

前記アクティブ領域と前記中間領域と前記外周領域に配置されている第1導電型のドリフト領域(12)と、

前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域上に設けられている第2導電型のボディ領域(13)と、

前記アクティブ領域と前記中間領域に配置されており、前記ボディ領域上に設けられている第1導電型のソース領域(14)と、

前記アクティブ領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第1コンタクト領域(15)と、

前記中間領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、前記ソース領域と前記ボディ領域の周縁に沿って前記ソース領域と

前記ボディ領域の周囲を一巡しており、第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第2コンタクト領域(16)と、を有しており、

前記トレンチゲートは、前記アクティブ領域に配置されており、前記第1正面から前記ソース領域と前記ボディ領域を超えて伸びており、

前記第1コンタクト領域と前記第2コンタクト領域の第2導電型不純物の深さ方向の濃度分布が一致しており、

前記第2コンタクト領域は、前記アクティブ領域と前記外周領域を結ぶ方向において、前記中間領域の半分以上の範囲を占めており、

前記中間領域に存在する前記ボディ領域は、前記第2コンタクト領域よりも前記アクティブ領域側にのみ配置されている、半導体装置。

10

【請求項2】

前記第1コンタクト領域と前記第2コンタクト領域の底面が前記ボディ領域の底面と同一深さである、請求項1に記載の半導体装置。

【請求項3】

前記半導体層はさらに、

前記外周領域に配置されており、前記アクティブ領域及び前記中間領域の周囲を一巡している第2導電型の複数のガードリング(17)、を有しており、

前記第2コンタクト領域は、前記複数のガードリングのうちの最内周のガードリングに接している、請求項1又は2に記載の半導体装置。

【請求項4】

20

前記半導体層はさらに、

前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられており、前記ドリフト領域よりも第1導電型不純物の濃度が濃い第1導電型の電流拡散領域(102)、を有しており、

前記電流拡散領域は、前記トレンチゲートの側面に接している、請求項1～3のいずれか一項に記載の半導体装置。

【請求項5】

前記第1コンタクト領域は、前記半導体層の前記第1正面に設けられているソース電極(24)と接触する位置に存在するシリサイド層(18)を有しており、

前記第1コンタクト領域の第2導電型不純物の深さ方向の濃度分布は、前記シリサイド層の底面近傍が最大濃度である、請求項1～4のいずれか一項に記載の半導体装置。

30

【請求項6】

前記半導体層はさらに、

前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられている第2導電型の複数のディープ領域(104)、を有しており、

前記複数のディープ領域は、前記半導体層を平面視したときに、第1方向に沿って伸びており、前記第1方向に直交する第2方向に間隔を開けて配置されており、

前記複数のディープ領域の各々は、前記ボディ領域の底面から前記トレンチゲートの底面を超えて伸びておる、

前記複数のディープ領域の各々は、前記中間領域において、前記第2コンタクト領域に接している、請求項1～5のいずれか一項に記載の半導体装置。

40

【請求項7】

前記半導体層を平面視したときに、前記第1方向が前記トレンチゲートの長手方向と平行であり、

前記トレンチゲートの一方の側面が、対応する前記第1コンタクト領域及び前記ディープ領域によって被覆されている、請求項6に記載の半導体装置。

【請求項8】

前記半導体層を平面視したときに、前記第1方向が前記トレンチゲートの長手方向に対して交差している、請求項6に記載の半導体装置。

【請求項9】

50

前記半導体層はさらに、

前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられている第2導電型の複数のディープ領域(104)、を有しており、

前記複数のディープ領域は、複数の上側ディープ領域(104A)と、前記複数の上側ディープ領域の下方に配置されている複数の下側ディープ領域(104B)と、を有しております、

前記複数の上側ディープ領域は、前記半導体層を平面視したときに、第1方向に沿って伸びてあり、前記第1方向に直交する第2方向に間隔を開けて配置されており、

前記複数の上側ディープ領域の各々は、前記ボディ領域の底面から前記トレンチゲートの底面を超えて伸びており、

前記複数の上側ディープ領域の各々は、前記中間領域において、前記第2コンタクト領域に接しており、

前記複数の下側ディープ領域は、前記半導体層を平面視したときに、前記第1方向とは異なる第3方向に沿って伸びてあり、前記第3方向に直交する第4方向に間隔を開けて配置されており、

前記複数の下側ディープ領域の各々は、前記上側ディープ領域に接している、請求項1～5のいずれか一項に記載の半導体装置。

#### 【請求項10】

半導体装置(1, 2, 3, 4, 5, 6, 7)の製造方法であって、

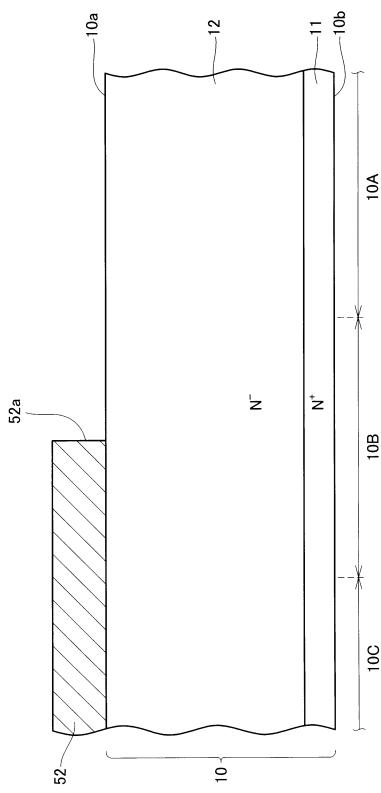

第1主面(10a)と第2主面(10b)を有する第1導電型の半導体層(10)の前記第1主面上に第1マスク(52)を成膜する第1マスク成膜工程であって、前記半導体層は、アクティブ領域(10A)と、前記アクティブ領域の周囲を一巡するように配置されている外周領域(10C)と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域(10B)と、に区画されており、前記第1マスクは、前記アクティブ領域と前記中間領域に対応して開口(52a)が形成されている、第1マスク成膜工程と、

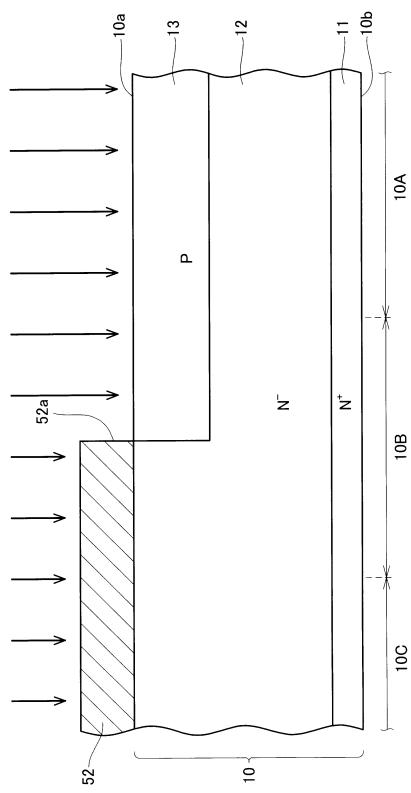

前記半導体層の前記第1主面に向けて前記第1マスク越しに第2導電型不純物をイオン注入し、前記半導体層内にボディ領域(13)を形成するボディ領域形成工程と、

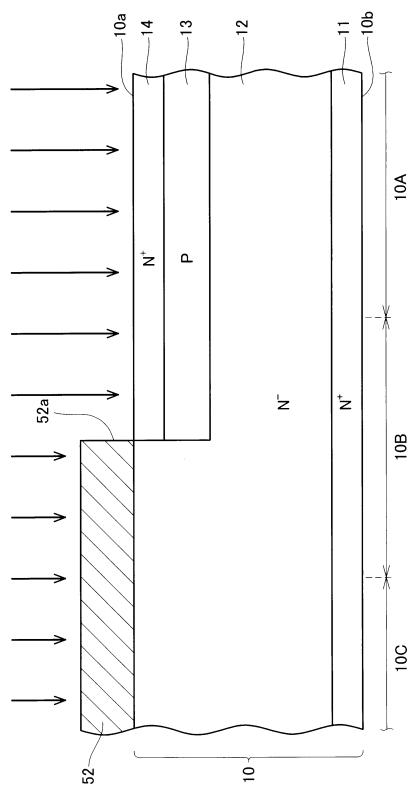

前記半導体層の前記第1主面に向けて前記第1マスク越しに第1導電型不純物をイオン注入し、前記半導体層内の前記ボディ領域よりも浅い範囲にソース領域(14)を形成するソース領域形成工程と、

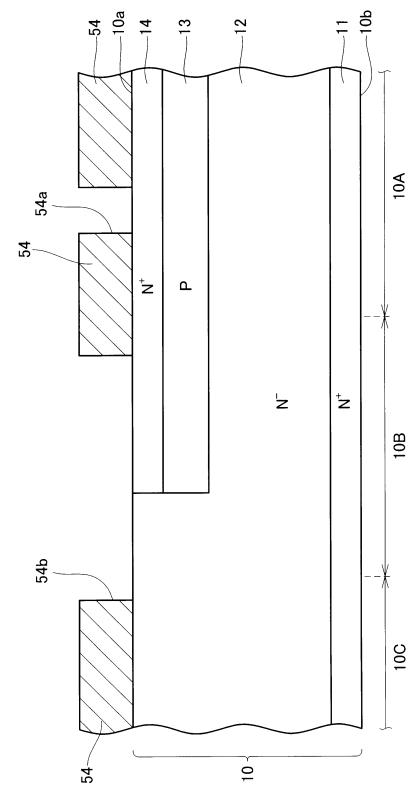

前記半導体層の前記第1主面上に第2マスク(54)を成膜する第2マスク成膜工程であって、前記第2マスクは、前記アクティブ領域の所定位置に内側開口(54a)が形成されるとともに、前記ソース領域の周縁が露出するように前記ソース領域の周縁に沿って前記ソース領域の周囲を一巡する周縁開口(54b)が形成されている、第2マスク成膜工程と、

前記半導体層の前記第1主面に向けて前記第2マスク越しに第2導電型不純物をイオン注入してコンタクト領域(15, 16)を形成する工程であって、前記第2マスクの前記内側開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第1コンタクト領域(15)を形成し、前記第2マスクの前記周縁開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第2コンタクト領域(16)を形成するコンタクト領域形成工程と、

前記アクティブ領域に、前記第1主面から前記ソース領域と前記ボディ領域を超えて伸びるトレンチゲート(30)を形成するトレンチゲート形成工程と、を備えている、半導体装置の製造方法。

#### 【請求項11】

前記コンタクト領域形成工程では、前記第1コンタクト領域と前記第2コンタクト領域の底面が前記ボディ領域の底面と同一深さとなるように形成される、請求項10に記載の

10

20

30

40

50

半導体装置の製造方法。

【請求項 1 2】

前記半導体層の前記外周領域には、前記アクティブ領域及び前記中間領域の周囲を一巡している第 2 導電型の複数のガードリング (17) が配置されており、

前記コンタクト領域形成工程では、前記第 2 コンタクト領域が前記複数のガードリングのうちの最内周のガードリングに接するように形成される、請求項 10 又は 11 に記載の半導体装置。

【請求項 1 3】

前記半導体層の前記第 1 主面に向けて前記第 1 マスク越しに第 1 導電型不純物をイオン注入し、前記半導体層内の前記ボディ領域よりも深い範囲に電流拡散領域 (102) を形成する電流拡散領域形成工程、をさらに備えており、

前記電流拡散領域は、前記トレンチゲートの側面に接している、請求項 10 ~ 12 のいずれか一項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書が開示する技術は、半導体装置とその製造方法に関する。

【0002】

特許文献 1 は、イオン注入技術を利用して、半導体層の所定深さにおいて面的に広がる p 型のボディ領域を形成するとともに、そのボディ領域よりも浅い位置であって半導体層の主面に露出する位置に面的に広がる n 型のソース領域を形成する、半導体装置の製造方法を開示する。この製造方法ではさらに、イオン注入技術を利用して、ソース領域をカウンタードーピングすることにより、p 型のコンタクト領域が形成される。

【先行技術文献】

【特許文献】

【0003】

【文献】特開 2016 - 76553 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

この種の半導体装置では、ゲート構造としてトレンチゲートが採用されることが多い。特許文献 1 に開示される製造方法では、面的に広がるボディ領域及びソース領域を貫通するように、半導体層のアクティブ領域内にトレンチゲートが形成される。通常、アクティブ領域に配置されるトレンチゲートは、面的に広がるボディ領域よりも内側に形成される。このため、アクティブ領域に配置されるトレンチゲートの最外周側の端部よりも外側には、面的に広がるボディ領域及びソース領域が存在することとなる。

【0005】

ボディ領域は、ゲート閾値電圧及びチャネル抵抗を考慮し、比較的薄い不純物濃度で形成されることが多い。このため、トレンチゲートよりも外側のボディ領域では、その面積によっては電位が不安定となる可能性がある。本明細書では、トレンチゲートの最外周側の端部よりも外側に広がるボディ領域の電位を安定化させる技術を提供する。

【課題を解決するための手段】

【0006】

本明細書が開示する半導体装置 (1, 2, 3, 4, 5, 6, 7) は、第 1 主面 (10a) と第 2 主面 (10b) を有する半導体層 (10) と、トレンチゲート (30) と、を備えることができる。前記半導体層は、アクティブ領域 (10A) と、前記アクティブ領域の周囲を一巡するように配置されている外周領域 (10C) と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域 (10B) と、に区画されている。前記半導体層は、前記アクティブ領域と前記中間領域と前記外周領域に配置されている第 1 導電型のドリフト領域 (12) と、前記アクテ

10

20

30

40

50

イブ領域と前記中間領域に配置されており、前記ドリフト領域上に設けられている第2導電型のボディ領域(13)と、前記アクティブ領域と前記中間領域に配置されており、前記ボディ領域上に設けられている第1導電型のソース領域(14)と、前記アクティブ領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第1コンタクト領域(15)と、前記中間領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、前記ソース領域の周縁に沿って前記ソース領域の周囲を一巡しており、第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第2コンタクト領域(16)と、を有することができる。前記トレンチゲートは、前記アクティブ領域に配置されており、前記第1主面から前記ソース領域と前記ボディ領域を超えて伸びている。前記第1コンタクト領域と前記第2コンタクト領域の第2導電型不純物の深さ方向の濃度分布が一致している。

#### 【0007】

上記半導体装置では、トレンチゲートよりも外側の前記中間領域に前記第2コンタクト領域が設けられている。前記第2コンタクト領域は、前記ボディ領域に接している。このため、トレンチゲートよりも外側に設けられている前記ボディ領域の電位が安定化する。さらに、上記半導体装置では、前記第1コンタクト領域と前記第2コンタクト領域の第2導電型不純物の深さ方向の濃度分布が一致しているので、前記第1コンタクト領域と前記第2コンタクト領域は、同時形成されるものである。換言すると、前記第2コンタクト領域を形成するための専用の工程を増加させることなく、前記第1コンタクト領域を形成する工程と同時に前記第2コンタクト領域を形成することができる。このため、上記半導体装置は、低コストで製造可能な構造を有している。このように、上記半導体装置は、低コストで製造可能であるとともに、トレンチゲートよりも外側に設けられている前記ボディ領域の電位が安定化することができる。

#### 【0008】

本明細書が開示する半導体装置(1, 2, 3, 4, 5, 6, 7)の製造方法は、第1マスク成膜工程と、ボディ領域形成工程と、ソース領域形成工程と、第2マスク成膜工程と、コンタクト領域形成工程と、トレンチゲート形成工程と、を備えることができる。前記第1マスク成膜工程では、第1主面(10a)と第2主面(10b)を有する第1導電型の半導体層(10)の前記第1主面上に第1マスク(52)を成膜する。ここで、前記半導体層は、アクティブ領域(10A)と、前記アクティブ領域の周囲を一巡するように配置されている外周領域(10C)と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域(10B)と、に区画されている。前記第1マスクは、前記アクティブ領域と前記中間領域に対応して開口(52a)が形成されている。前記ボディ領域形成工程では、前記半導体層の前記第1主面向て前記第1マスク越しに第2導電型不純物をイオン注入し、前記半導体層内にボディ領域(13)を形成する。前記ソース領域形成工程では、前記半導体層の前記第1主面向て前記第1マスク越しに第1導電型不純物をイオン注入し、前記半導体層内に前記ボディ領域よりも浅い範囲にソース領域(14)を形成する。前記第2マスク成膜工程では、前記半導体層の前記第1主面上に第2マスク(54)を成膜する。ここで、前記第2マスクは、前記アクティブ領域の所定位置に内側開口(54a)が形成されるとともに、前記ソース領域の周縁が露出するように前記ソース領域の周縁に沿って前記ソース領域の周囲を一巡する周縁開口(54b)が形成されている。前記コンタクト領域形成工程では、前記半導体層の前記第1主面向て前記第2マスク越しに第2導電型不純物をイオン注入してコンタクト領域(15, 16)を形成する。前記コンタクト領域形成工程では、前記第2マスクの前記内側開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第1コンタクト領域(15)を形成し、前記第2マスクの前記周縁開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第2コンタクト領域(16)を形

成する。前記トレンチゲート形成工程では、前記アクティブ領域に、前記第1主面から前記ソース領域と前記ボディ領域を超えて伸びるトレンチゲート(30)を形成する。

【0009】

上記製造方法では、共通の前記第1マスクを利用して前記ボディ領域と前記ソース領域を形成することができる。このため、上記製造方法は、低成本で半導体装置を製造することができる。さらに、上記製造方法は、共通の前記第2マスクを利用して前記第1コンタクト領域と前記第2コンタクト領域を形成することができる。前記第2コンタクト領域は、前記中間領域に設けられている前記ボディ領域に接している。このため、前記中間領域に設けられている前記ボディ領域の電位が安定化する。このように、上記製造方法は、前記第2コンタクト領域を形成するための専用の工程を増加させることなく、前記中間領域に設けられている前記ボディ領域の電位を安定化させるための前記第2コンタクト領域を、前記第1コンタクト領域を形成する工程と同時に形成することができる。

10

【図面の簡単な説明】

【0010】

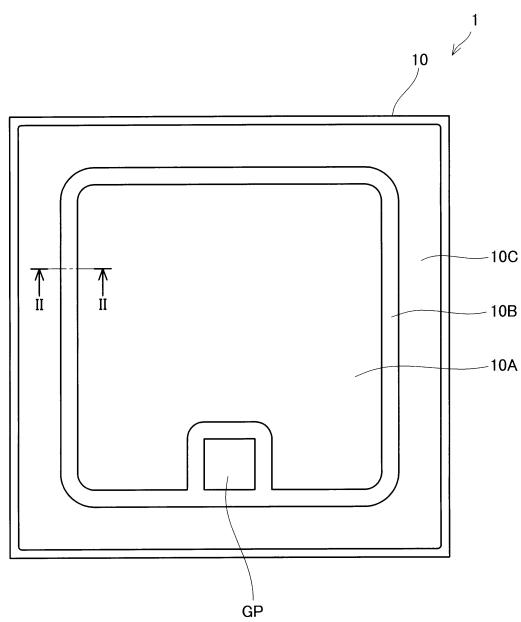

【図1】半導体層を平面視したときに、半導体層に区画されているアクティブ領域、中間領域及び外周領域の位置関係を示す図である。

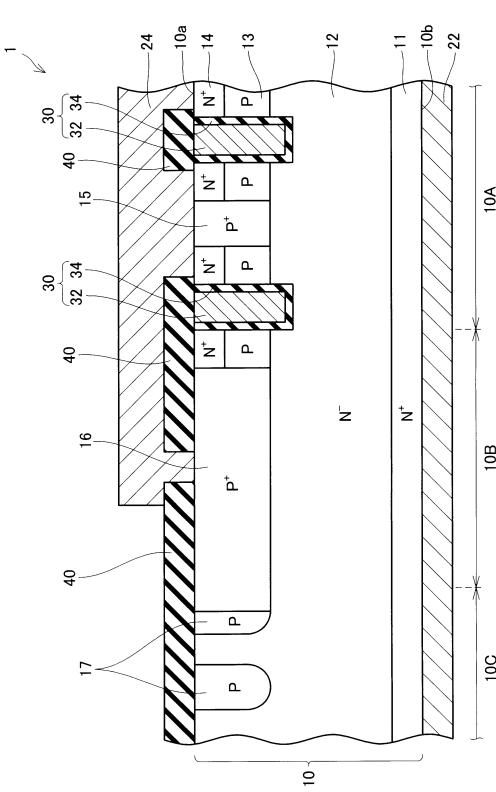

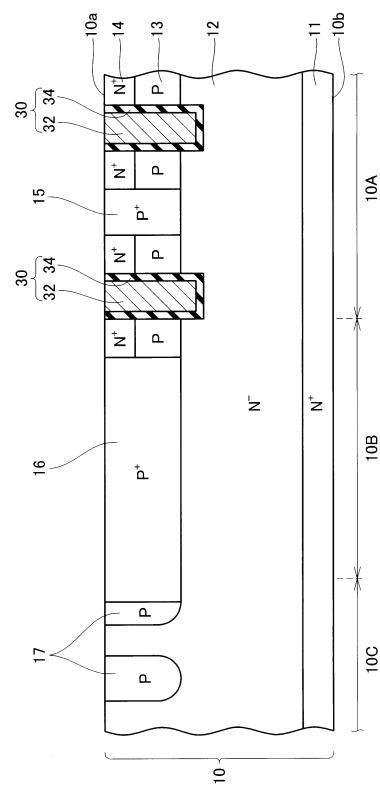

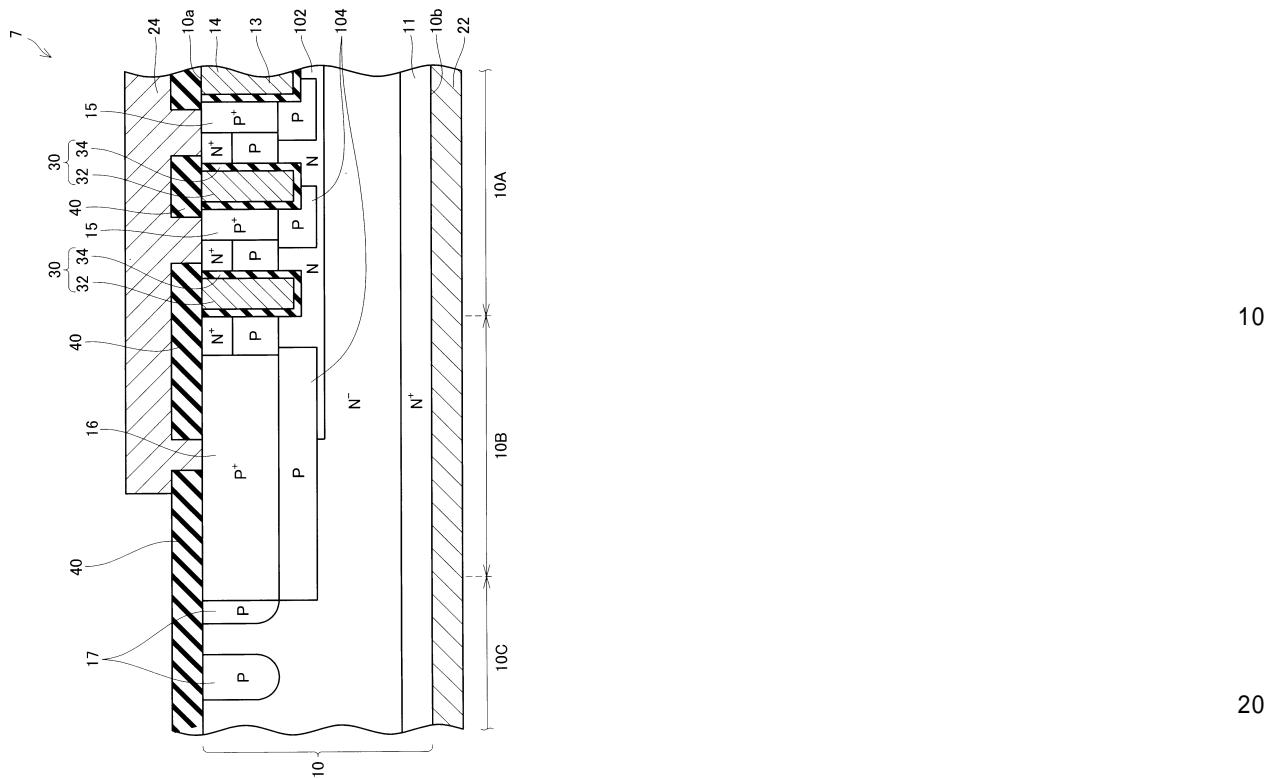

【図2】第1実施形態の半導体装置の要部断面図であり、図1のII-II線に対応した断面図を模式的に示す図である。

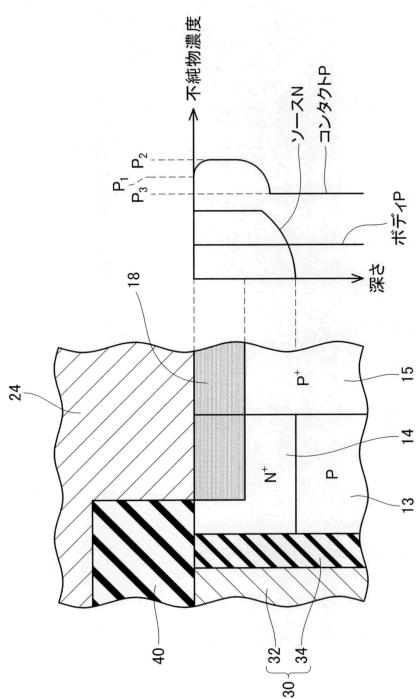

【図3】半導体装置の要部拡大断面図であり、第1コンタクト領域とソース電極の接続箇所の近傍の図である。

20

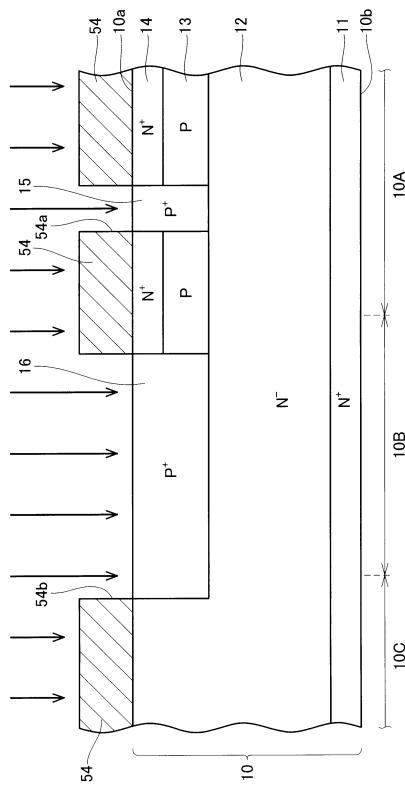

【図4】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図5】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図6】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図7】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図8】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図9】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図10】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図11】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図12】半導体装置を製造する過程の要部断面図を模式的に示す図である。

30

【図13】半導体装置を製造する過程の要部断面図を模式的に示す図である。

【図14】半導体装置を製造する過程の要部断面図を模式的に示す図である。

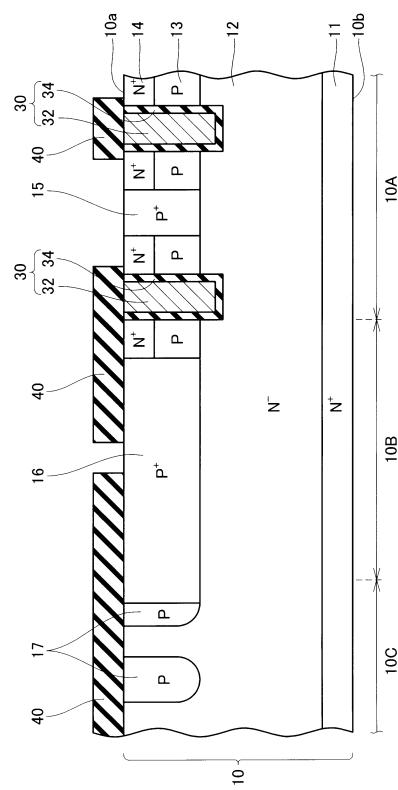

【図15】第2実施形態の半導体装置の要部断面図であり、図1のII-II線に対応した断面図を模式的に示す図である。

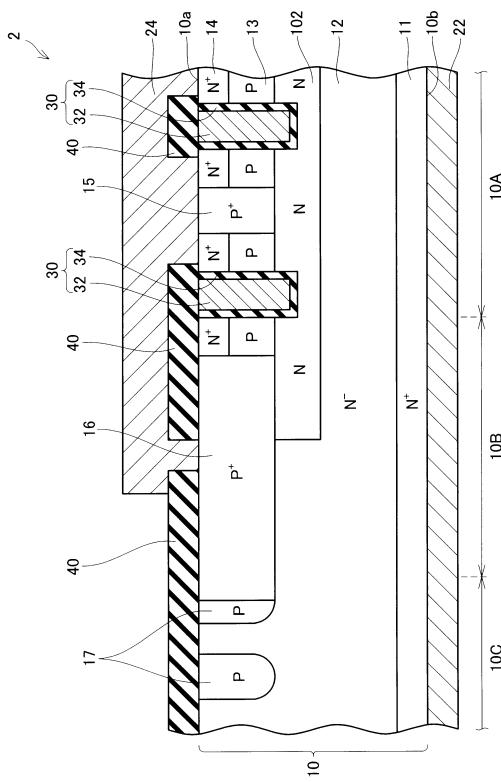

【図16】第3実施形態の半導体装置の要部断面図であり、図1のII-II線に対応した断面図を模式的に示す図である。

【図17】第3実施形態の半導体装置の変形例の要部斜視図である。

【図18】第3実施形態の半導体装置の変形例の要部斜視図である。

【図19】第3実施形態の半導体装置の変形例の要部断面図であり、図18のXIX-XIX線に対応した断面図を模式的に示す図である。

40

【図20】第3実施形態の半導体装置の変形例の要部斜視図である。

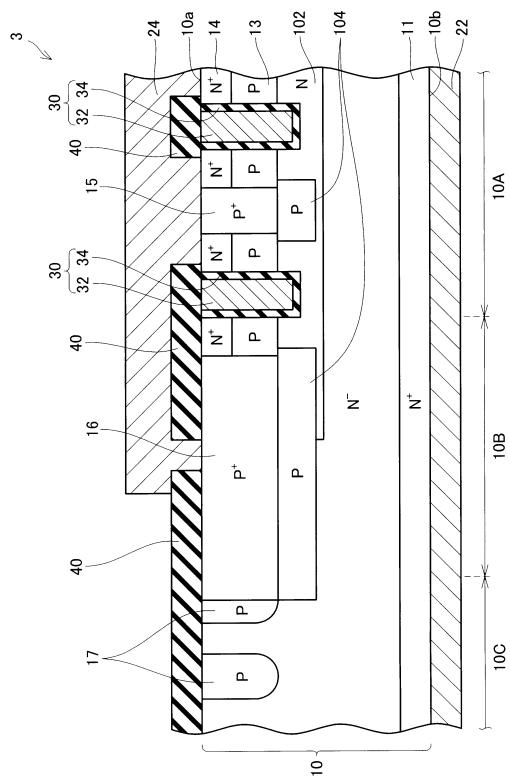

【図21】第4実施形態の半導体装置の要部断面図であり、図1のII-II線に対応した断面図を模式的に示す図である。

【発明を実施するための形態】

【0011】

(第1実施形態)

図1及び図2に示されるように、第1実施形態の半導体装置1は、MOSFETと称される種類のパワーデバイスであり、半導体層10を用いて構成されている。半導体層10の材料は、特に限定されるものではないが、例えば炭化珪素(SiC)であってもよい。

【0012】

図1に示されるように、半導体層10は、半導体層10を上側から見たときに(以下、

50

「平面視したときに」という)、アクティブ領域 10 A と中間領域 10 B と外周領域 10 C に区画されている。アクティブ領域 10 A は、半導体層 10 の中央側に区画された領域であり、後述するように、スイッチング構造が形成された領域である。中間領域 10 B は、アクティブ領域 10 A と外周領域 10 C の間に区画された領域であり、アクティブ領域 10 A の周囲を一巡している。外周領域 10 C は、アクティブ領域 10 A 及び中間領域 10 B の周囲に区画された領域であり、アクティブ領域 10 A 及び中間領域 10 B の周囲を一巡している。外周領域 10 C には、後述するように、外周耐圧構造が形成されている。なお、図 1 の「G P」の領域は、ゲートパットが配設される領域を示している。

#### 【0013】

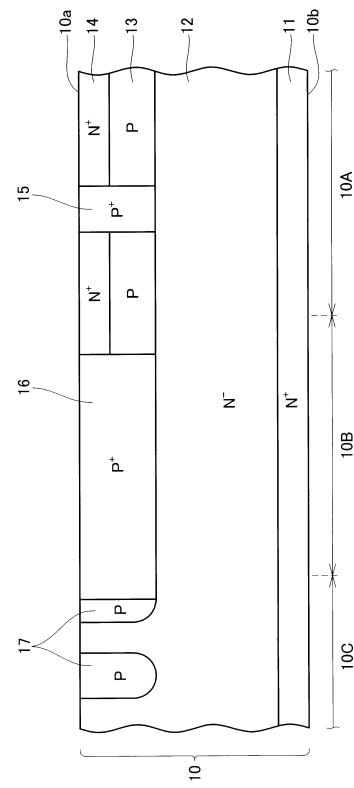

図 2 に示されるように、半導体装置 1 は、半導体層 10 と、ドレイン電極 22 と、ソース電極 24 と、複数のトレンチゲート 30 と、を備えている。半導体層 10 は、ドレイン領域 11 と、ドリフト領域 12 と、ボディ領域 13 と、ソース領域 14 と、第 1 コンタクト領域 15 と、第 2 コンタクト領域 16 と、複数のガードリング 17 と、を有している。図 2 に示されるように、アクティブ領域 10 A は、複数のトレンチゲート 30 が設けられている領域である。中間領域 10 B は、アクティブ領域 10 A に設けられているトレンチゲート 30 の最外周側の端部から外周領域 10 C のガードリング 17 までの領域である。外周領域 10 C は、最内周のガードリング 17 よりも外側の領域である。

#### 【0014】

ドレイン電極 22 は、半導体層 10 の下面 10 b を被覆するように設けられている。ドレイン電極 22 は、アクティブ領域 10 A と中間領域 10 B と外周領域 10 C に亘って配設されており、半導体層 10 の下面 10 b の全体に接している。

#### 【0015】

ソース電極 24 は、半導体層 10 の上面 10 a を被覆するように設けられている。ソース電極 24 は、アクティブ領域 10 A の全範囲と中間領域 10 B の一部に亘って配設されており、半導体層 10 の上面 10 a に形成されている層間絶縁膜 40 の開口から露出する半導体層 10 の上面 10 a に接している。

#### 【0016】

ドレイン領域 11 は、高濃度の n 型不純物を含有する N 型層である。ドレイン領域 11 は、アクティブ領域 10 A と中間領域 10 B と外周領域 10 C に亘って配置されており、半導体層 10 の下面 10 b に露出する位置に設けられている。ドレイン領域 11 は、ドレイン電極 22 にオーミック接觸している。ドレイン領域 11 は、後述するように、ドリフト領域 12 をエピタキシャル成長するための下地基板でもある。

#### 【0017】

ドリフト領域 12 は、ドレイン領域 11 よりも n 型不純物濃度が低い N 型層である。ドリフト領域 12 は、アクティブ領域 10 A と中間領域 10 B と外周領域 10 C に亘って配置されている。ドリフト領域 12 は、複数のトレンチゲート 30 の各々の側面及び底面に接している。

#### 【0018】

ボディ領域 13 は、低濃度の p 型不純物を含有する P 型層である。ボディ領域 13 は、アクティブ領域 10 A の全範囲と中間領域 10 B の一部の範囲に亘って配置されており、ドリフト領域 12 上に設けられている。ボディ領域 13 は、半導体層 10 の上面 10 a から所定深さにおいて面的に広がって形成されており、トレンチゲート 30 の側面のうちの下側部分に接している。ボディ領域 13 は、ドリフト領域 12 とソース領域 14 を隔てるよう配置されている。

#### 【0019】

ソース領域 14 は、高濃度の n 型不純物を含有する N 型層である。ソース領域 14 は、アクティブ領域 10 A の全範囲と中間領域 10 B の一部の範囲に亘って配置されており、ボディ領域 13 上に設けられている。ソース領域 14 は、半導体層 10 の上面 10 a に露出する位置において面的に広がって形成されており、トレンチゲート 30 の側面のうちの上側部分に接している。ソース領域 14 は、半導体層 10 の上面 10 a に形成されている

10

20

30

40

50

層間絶縁膜 4 0 の開口から露出しており、ソース電極 2 4 にオーミック接触している。

【 0 0 2 0 】

第 1 コンタクト領域 1 5 は、ボディ領域 1 3 よりも p 型不純物を高濃度に含有する P 型層である。第 1 コンタクト領域 1 5 は、アクティブ領域 1 0 A に配置されており、半導体層 1 0 を平面視したときに、トレンチゲート 3 0 の長手方向と平行に伸びている。第 1 コンタクト領域 1 5 は、半導体層 1 0 を平面視したときに、トレンチゲート 3 0 の長手方向の一方の端部から他方の端部まで伸びている。第 1 コンタクト領域 1 5 は、半導体層 1 0 の上面 1 0 a からソース領域 1 4 を超えてボディ領域 1 3 に達するように形成されており、ボディ領域 1 3 に接している。この例では、第 1 コンタクト領域 1 5 の底面は、ボディ領域 1 3 の底面と略同一深さである。この例に代えて、第 1 コンタクト領域 1 5 の底面は、ボディ領域 1 3 の底面よりも浅い位置にあってもよい。第 1 コンタクト領域 1 5 は、半導体層 1 0 の上面 1 0 a に形成されている層間絶縁膜 4 0 の開口から露出しており、ソース電極 2 4 にオーミック接触している。これにより、アクティブ領域 1 0 A のボディ領域 1 3 は、第 1 コンタクト領域 1 5 を介してソース電極 2 4 の電位に固定されている。

10

【 0 0 2 1 】

図 3 に、第 1 コンタクト領域 1 5 がソース電極 2 4 に接する部分の要部拡大図を示す。また、図 3 には、ボディ領域 1 3 とソース領域 1 4 と第 1 コンタクト領域 1 5 の各々の不純物の深さ方向の濃度プロファイルも合わせて示されている。図中の「ボディ P 」がボディ領域 1 3 に含まれる p 型不純物の深さ方向の濃度プロファイルであり、図中の「ソース N 」がソース領域 1 4 に含まれる n 型不純物の深さ方向の濃度プロファイルであり、図中の「コンタクト P 」が第 1 コンタクト領域 1 5 に含まれる p 型不純物の深さ方向の濃度プロファイルである。

20

【 0 0 2 2 】

図 3 に示されるように、ソース領域 1 4 及び第 1 コンタクト領域 1 5 の各々のうちのソース電極 2 4 に接する部分には、シリサイド層 1 8 が形成されている。一例ではあるが、シリサイド層 1 8 の厚みは  $50 \sim 200 \text{ nm}$  である。第 1 コンタクト領域 1 5 は、シリサイド層 1 8 が形成される深さ範囲、特にシリサイド層 1 8 の底面に対応する深さにおいて p 型不純物の濃度が濃くなるように調整されている。ここで、第 1 コンタクト領域 1 5 とソース電極 2 4 の接合面における第 1 コンタクト領域 1 5 の p 型不純物の濃度が  $P_1$  であり、第 1 コンタクト領域 1 5 の深さ方向における p 型不純物の最大濃度が  $P_2$  であり、ボディ領域 1 3 とソース領域 1 4 の接合面に対応する深さにおける第 1 コンタクト領域 1 5 の p 型不純物の濃度が  $P_3$  である。特に限定されるものではないが、例えば、 $P_1$  が  $1 \times 10^{17} \sim 1 \times 10^{20} \text{ cm}^{-3}$  であり、 $P_2$  が  $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$  であり、 $P_3$  が  $1 \times 10^{17} \sim 1 \times 10^{20} \text{ cm}^{-3}$  であってもよい。 $P_3$  はソース領域 1 4 の不純物濃度よりも濃く調整されている。

30

【 0 0 2 3 】

第 1 コンタクト領域 1 5 に含まれる p 型不純物の深さ方向の濃度プロファイルは、 $P_1 < P_2$ 、且つ、 $P_3 < P_2$  を満たす。換言すると、第 1 コンタクト領域 1 5 は、半導体層 1 0 の内部に p 型不純物の最大濃度が位置するとともに、シリサイド層 1 8 の底面近傍が最大濃度となるような濃度プロファイルを有している。このような濃度プロファイルを有していると、第 1 コンタクト領域 1 5 とソース電極 2 4 のコンタクト抵抗を低くしながら、第 1 コンタクト領域 1 5 をイオン注入工程で形成するときの p 型不純物のドーズ量を減らすことができる。

40

【 0 0 2 4 】

図 2 に戻る。第 2 コンタクト領域 1 6 は、中間領域 1 0 B に配置されており、ボディ領域 1 3 よりも p 型不純物を高濃度に含有する P 型層である。第 2 コンタクト領域 1 6 は、半導体層 1 0 の上面 1 0 a からソース領域 1 4 を超えてボディ領域 1 3 に達するように形成されており、ボディ領域 1 3 に接している。この例では、第 2 コンタクト領域 1 6 の底面は、ボディ領域 1 3 の底面と略同一深さである。この例に代えて、第 2 コンタクト領域 1 6 の底面は、ボディ領域 1 3 の底面よりも浅い位置にあってもよい。第 2 コンタクト領

50

域 1 6 は、ボディ領域 1 3 及びソース領域 1 4 の周縁を被覆するように配置されており、ボディ領域 1 3 及びソース領域 1 4 の周縁に沿ってボディ領域 1 3 及びソース領域 1 4 を一巡している。第 2 コンタクト領域 1 6 は、内周側の端部がボディ領域 1 3 及びソース領域 1 4 に接しており、外周側の端部が複数のガードリング 1 7 のうちの最内周のガードリング 1 7 に接している。第 2 コンタクト領域 1 6 は、半導体層 1 0 の上面 1 0 a に形成されている層間絶縁膜 4 0 の開口から露出しており、ソース電極 2 4 にオーミック接触している。これにより、中間領域 1 0 B のボディ領域 1 3 は、第 2 コンタクト領域 1 6 を介してソース電極 2 4 の電位に固定されている。

#### 【 0 0 2 5 】

後述するように、第 1 コンタクト領域 1 5 と第 2 コンタクト領域 1 6 は、同一のイオン注入工程によって形成されている。このため、第 1 コンタクト領域 1 5 と第 2 コンタクト領域 1 6 の p 型不純物の深さ方向の濃度分布が一致している。第 2 コンタクト領域 1 6 についても、第 1 コンタクト領域 1 5 と同様に、ソース電極 2 4 に接する部分にシリサイド層が形成されている。上記したように、第 2 コンタクト領域 1 6 についても、第 1 コンタクト領域 1 5 と同様に、第 2 コンタクト領域 1 6 とソース電極 2 4 のコンタクト抵抗を低くしながら、第 2 コンタクト領域 1 6 をイオン注入工程で形成するときの p 型不純物のドーズ量を減らすことができる。

#### 【 0 0 2 6 】

ガードリング 1 7 は、外周領域 1 0 C に配置されており、p 型不純物を含む P 型層である。ガードリング 1 7 は、半導体層 1 0 の上面 1 0 a から所定深さに達するように形成されており、外周領域 1 0 C に沿ってアクティブ領域 1 0 A 及び中間領域 1 0 B の周囲を一巡している。ガードリング 1 7 は、外周耐圧構造の一例であり、半導体装置 1 がオフしたときに空乏層を外側へと伸ばし、電界集中を緩和する役割を担っている。ガードリング 1 7 に代えて、外周耐圧構造として例えばリサーフ層が設けられていてもよい。

#### 【 0 0 2 7 】

複数のトレンチゲート 3 0 は、アクティブ領域 1 0 A に配置されており、半導体層 1 0 の上面 1 0 a からソース領域 1 4 及びボディ領域 1 3 を超えてドリフト領域 1 2 に達するように形成されている。半導体層 1 0 を平面視したとき、複数のトレンチゲート 3 0 の各々は、アクティブ領域 1 0 A 内を一方向に沿って伸びており、アクティブ領域 1 0 A の一方端から他方端まで伸びている。このように、半導体層 1 0 を平面視したとき、複数のトレンチゲート 3 0 は、ストライプ状に配置されている。なお、ストライプ状の配置は一例であり、複数のトレンチゲート 3 0 は他のレイアウトで配置されてもよい。複数のトレンチゲート 3 0 の各々は、ゲート電極 3 2 とゲート絶縁膜 3 4 を有している。ゲート電極 3 2 は、ゲート絶縁膜 3 4 によってドリフト領域 1 2 とボディ領域 1 3 とソース領域 1 4 から絶縁されており、層間絶縁膜 4 0 によってソース電極 2 4 から絶縁されている。ゲート電極 3 2 は、ゲートパッド GP (図 1 参照) に電気的に接続されている。ゲート電極 3 2 は、特に限定されるものではないが、例えば酸化シリコン (SiO<sub>2</sub>) であってもよい。ゲート絶縁膜 3 4 は、特に限定されるものではないが、例えば多結晶シリコンであってもよい。

#### 【 0 0 2 8 】

このように、アクティブ領域 1 0 A には、ドレイン電極 2 2 、ドレイン領域 1 1 、ドリフト領域 1 2 、ボディ領域 1 3 、ソース領域 1 4 、第 1 コンタクト領域 1 5 、ソース電極 2 4 及びトレンチゲート 3 0 等によってスイッチング構造が形成されている。

#### 【 0 0 2 9 】

次に、半導体装置 1 の動作について説明する。ドレイン電極 2 2 がソース電極 2 4 よりも高電位となるような電圧がドレイン・ソース間に印加されている状態で、ゲート電極 3 2 にゲート閾値電圧以上の電圧が印加されると、ゲート絶縁膜 3 4 に隣接する範囲のボディ領域 1 3 にチャネルが形成される。ソース領域 1 4 から供給される電子は、このチャネルを介してドリフト領域 1 2 に流入することができる。これにより、ドレイン電極 2 2 とソース電極 2 4 の間が導通し、半導体装置 1 がオンとなる。一方、ゲート電極 3 2 にゲー

10

20

30

40

50

ト閾値電圧未満の電圧が印加されると、チャネルが消失し、半導体装置 1 がオフとなる。このように、半導体装置 1 は、ゲート電極 3 2 に印加する電圧に応じてドレイン電極 2 2 とソース電極 2 4 の間を流れる電流を制御するスイッチング素子として動作することができる。

#### 【 0 0 3 0 】

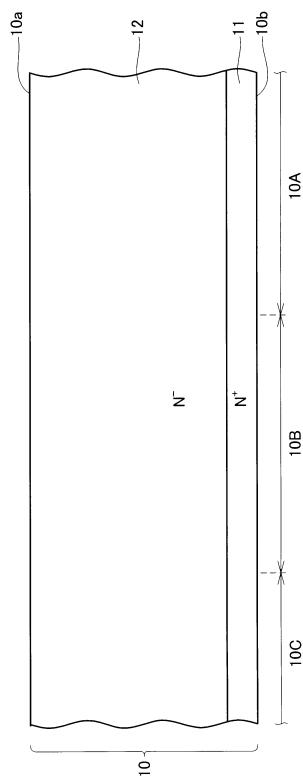

次に、半導体装置 1 の製造方法について説明する。まず、図 4 に示されるように、ドレイン領域 1 1 として機能する SiC 基板を準備する。この SiC 基板は、特に限定されるものではないが、例えば n 型不純物の濃度が  $1 \times 10^{18} \sim 1 \times 10^{19} \text{ cm}^{-3}$  であり、厚みが  $350 \sim 500 \mu\text{m}$  であってもよい。次に、エピタキシャル成長技術を利用して、ドレイン領域 1 1 の上面からドリフト領域 1 2 を結晶成長させる。ドリフト領域 1 2 は、特に限定されるものではないが、例えば n 型不純物の濃度が  $1 \times 10^{15} \sim 1 \times 10^{17} \text{ cm}^{-3}$  であり、厚みが  $5 \sim 100 \mu\text{m}$  であってもよい。これにより、ドレイン領域 1 1 とドリフト領域 1 2 が積層した半導体層 1 0 が準備される。

#### 【 0 0 3 1 】

次に、図 5 に示されるように、CVD 技術及びフォトリソグラフィー技術を利用して、半導体層 1 0 の上面 1 0 a にマスク 5 2 を成膜する（第 1 マスク成膜工程の一例）。マスク 5 2 には、アクティブ領域 1 0 A の全範囲と中間領域 1 0 B の一部の範囲に対応した開口 5 2 a が形成されている。なお、後述するように、マスク 5 2 には、外周領域 1 0 C に形成される複数のガードリング 1 7 に対応した開口が形成されていてもよい。

#### 【 0 0 3 2 】

次に、図 6 に示されるように、イオン注入技術を利用して、マスク 5 2 の開口 5 2 a から露出する半導体層 1 0 の上面 1 0 a に向けてアルミニウムを多段でイオン注入し、ボディ領域 1 3 を形成する（ボディ領域形成工程の一例）。ボディ領域 1 3 は、半導体層 1 0 のアクティブ領域 1 0 A の全範囲及び中間領域 1 0 B の一部の範囲において面的に広がるように形成される。このイオン注入工程は、特に限定されるものではないが、例えばドーズ量が  $1 \times 10^{11} \sim 1 \times 10^{14} \text{ cm}^{-2}$  であり、注入エネルギーが  $10 \sim 1500 \text{ eV}$  であってもよい。ボディ領域 1 3 は、特に限定されるものではないが、例えば p 型不純物のピーカ濃度が  $1 \times 10^{17} \sim 1 \times 10^{18} \text{ cm}^{-3}$  であり、底面の深さが  $0.5 \sim 1.5 \mu\text{m}$  であってもよい。

#### 【 0 0 3 3 】

次に、図 7 に示されるように、イオン注入技術を利用して、マスク 5 2 の開口 5 2 a から露出する半導体層 1 0 の上面 1 0 a に向けて窒素を多段でイオン注入し、ソース領域 1 4 を形成する（ソース領域形成工程の一例）。ソース領域 1 4 は、半導体層 1 0 のアクティブ領域 1 0 A の全範囲及び中間領域 1 0 B の一部の範囲において面的に広がるように形成され、ボディ領域 1 3 に積層するようにボディ領域 1 3 よりも浅い範囲に形成される。また、ソース領域 1 4 は、半導体層 1 0 の上面に露出する位置に形成される。なお、ソース領域 1 4 は、ボディ領域 1 3 よりも先に形成されてもよい。このイオン注入工程は、特に限定されるものではないが、例えばドーズ量が  $1 \times 10^{13} \sim 1 \times 10^{16} \text{ cm}^{-2}$  であり、注入エネルギーが  $10 \sim 500 \text{ eV}$  であってもよい。ソース領域 1 4 は、特に限定されるものではないが、例えば n 型不純物のピーカ濃度が  $1 \times 10^{18} \sim 1 \times 10^{20} \text{ cm}^{-3}$  であり、底面の深さが  $0.1 \sim 0.8 \mu\text{m}$  であってもよい。ボディ領域 1 3 及びソース領域 1 4 を形成した後に、マスク 5 2 は除去される。

#### 【 0 0 3 4 】

次に、図 8 に示されるように、CVD 技術及びフォトリソグラフィー技術を利用して、半導体層 1 0 の上面 1 0 a にマスク 5 4 を成膜する（第 2 マスク成膜工程の一例）。マスク 5 4 には、アクティブ領域 1 0 A の一部の範囲に対応した内側開口 5 4 a 及び中間領域 1 0 B の一部の範囲に対応した周縁開口 5 4 b が形成されている。マスク 5 4 の周縁開口 5 4 b は、ソース領域 1 4 の周縁が露出するようにソース領域 1 4 の周縁に沿ってソース領域 1 4 の周囲を一巡して形成されている。

#### 【 0 0 3 5 】

10

20

30

40

50

次に、図9に示されるように、イオン注入技術を利用して、マスク54の内側開口54a及び周縁開口54bから露出する半導体層10の上面10aに向けてアルミニウムを多段でイオン注入し、第1コンタクト領域15及び第2コンタクト領域16を形成する（コンタクト領域形成工程の一例）。このイオン注入工程は、特に限定されるものではないが、例えばドーズ量が $1 \times 10^{13} \sim 1 \times 10^{16} \text{ cm}^{-2}$ であり、注入エネルギーが10～1500eVであってもよい。第1コンタクト領域15及び第2コンタクト領域16は、特に限定されるものではないが、例えばp型不純物のピーク濃度が $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$ であり、底面の深さが0.5～1.5μmであってもよい。第1コンタクト領域15及び第2コンタクト領域16を形成した後に、マスク54は除去される。

#### 【0036】

第1コンタクト領域15及び第2コンタクト領域16は、ソース領域14を超えてボディ領域13に達するように形成される。これにより、第1コンタクト領域15は、アクティブ領域10Aにおいてボディ領域13に電気的に接続される。第2コンタクト領域16は、中間領域10Bにおいてボディ領域13に電気的に接続される。さらに、第1コンタクト領域15及び第2コンタクト領域16は、その底面がボディ領域13の底面と略同一深さとなるように形成される。例えば、第1コンタクト領域15及び第2コンタクト領域16の底面がボディ領域13の底面よりも浅くなるように第1コンタクト領域15及び第2コンタクト領域16が形成されると、中間領域10Bにおいては、ボディ領域13の終端部に対応した角部がドリフト領域12に露出する。このため、この角部の電界集中が懸念される。一方、第1コンタクト領域15及び第2コンタクト領域16の底面がボディ領域13の底面と一致するように第1コンタクト領域15及び第2コンタクト領域16が形成されると、ボディ領域13の周縁部に対応した角部がドリフト領域12に露出することができない。このため、この角部における電界集中が緩和される。

#### 【0037】

次に、図10に示されるように、イオン注入技術を利用して、外周領域10Cにガードリング17を形成する。具体的には、ガードリング17の形成位置に対応した開口が形成されているマスクを半導体層10の上面10aに成膜した後に、そのマスクの開口越しにアルミニウムをイオン注入することにより、ガードリング17を形成することができる。なお、複数のガードリング17は、ボディ領域13と同時に形成されてもよい。この場合、ボディ領域13を形成するためのマスク52に複数のガードリング17に対応した開口を形成して置くことで、複数のガードリング17をボディ領域13と同時に形成することができる。

#### 【0038】

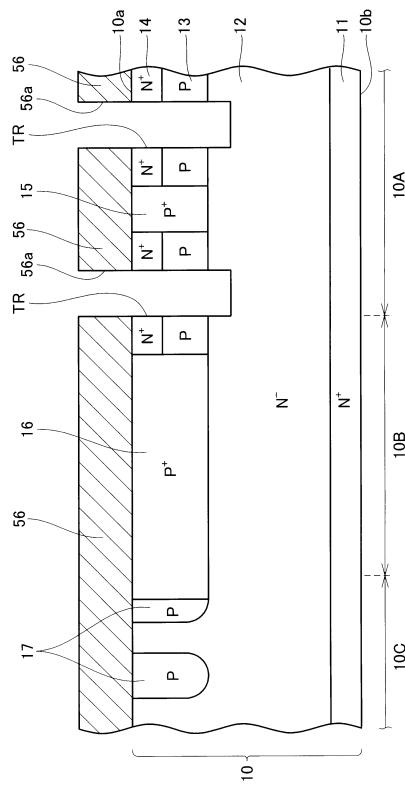

次に、図11に示されるように、CVD技術及びフォトリソグラフィー技術を利用して、半導体層10の上面10aにマスク56を成膜する。マスク56には、アクティブ領域10Aの一部の範囲に対応した複数の開口56aが形成されている。次に、ドライエッチング技術を利用して、マスク56の開口56aから露出する半導体層10の表層部にトレチTRを形成する。トレチTRは、半導体層10の上面10aからソース領域14及びボディ領域13を貫通してドリフト領域12に達するように形成される。トレチTRは、特に限定されるものではないが、例えば深さが0.5～2μmであり、短手方向の幅が0.3～1μmであってもよい。トレチTRを形成した後に、マスク56は除去される。マスク56を除去した後に、半導体層10の表面及びトレチTRの内面を被覆するように保護膜を成膜し、活性化アニール処理を実施する。その後、保護膜は除去される。

#### 【0039】

次に、図12に示されるように、CVD技術を利用して、半導体層10の上面10a及びトレチTRの内面を被覆するようにゲート絶縁膜34を成膜する。次に、CVD技術を利用して、トレチTRが充填されるように、ゲート電極32を成膜する。

#### 【0040】

次に、図13に示されるように、半導体層10の上面10aに成膜されたゲート絶縁膜34及びゲート電極32を除去する。なお、半導体層10の上面10aに成膜されたゲー

10

20

30

40

50

ト電極 32 の一部は、この断面では図示されないが、ゲート配線として用いるために残存させてもよい。

#### 【0041】

次に、図 14 に示されるように、CVD 技術及びフォトリソグラフィー技術を利用して、半導体層 10 の上面 10a に層間絶縁膜 40 を成膜する。層間絶縁膜 40 には、アクティブ領域 10A のソース領域 14 及び第 1 コンタクト領域 15 が露出する開口及び中間領域 10B の第 2 コンタクト領域 16 が露出する開口が形成されている。次に、層間絶縁膜 40 の開口から露出する半導体層 10 の上面 10a に、シリサイド層を形成するための金属膜を成膜する。金属膜は、特に限定されるものではないが、例えばニッケル (Ni) とコバルト (Co) とチタン (Ti) が積層した金属膜であってもよい。金属膜を成膜した後に、アニール処理を実施してシリサイド層を形成する。アニール処理を実施後、未反応金属は除去される。次に、ドレイン電極 22、ソース電極 24 及びゲートパッド GP (図 1 参照) の各々を成膜し、半導体装置 1 が完成する。

#### 【0042】

この製造方法では、ボディ領域 13 とソース領域 14 が共通のマスク 52 を利用して形成される。このため、この製造方法は、マスク成膜工程を削減することができる、低成本で半導体装置 1 を製造することができる。

#### 【0043】

一方、共通のマスク 52 を利用してボディ領域 13 とソース領域 14 が形成されると、トレンチゲート 30 よりも外側に、即ち、中間領域 10B にボディ領域 13 及びソース領域 14 が面的に広がるように形成される。ボディ領域 13 は、ゲート閾値電圧及びチャネル抵抗を考慮し、比較的薄い不純物濃度で形成されている。このため、中間領域 10B に面的に広がるボディ領域 13 が存在していると、その面積によっては電位が不安定となる可能性がある。特に、炭化珪素を材料とする半導体層 10 では、p 型領域の抵抗が高くなる。このため、中間領域 10B に面的に広がるボディ領域 13 では、電位が不安定となり易い。

#### 【0044】

この製造方法は、中間領域 10B に第 2 コンタクト領域 16 が設けられているので、中間領域 10B に配置されているボディ領域 13 の電位が安定化する。特に、第 2 コンタクト領域 16 は、その底面がボディ領域 13 の底面と略同一深さとなるように形成されるので、ボディ領域 13 が第 2 コンタクト領域 16 とオーバーラップすることとなる。このため、中間領域 10B のボディ領域 13 は、高濃度な第 2 コンタクト領域 16 にオーバーラップされるので、その不純物濃度が実質的に濃くなり、その部分の電位が安定する。

#### 【0045】

また、第 2 コンタクト領域 16 は、内周側の端部がボディ領域 13 及びソース領域 14 に接しており、外周側の端部が複数のガードリング 17 のうちの最内周のガードリング 17 に接しており、中間領域 10B の広い範囲に亘って設けられている。例えば、第 2 コンタクト領域 16 は、周方向 (アクティブ領域 10A と外周領域 10C を結ぶ方向) において、半分以上の範囲を占めている。これにより、中間領域 10B に存在するボディ領域 13 及びソース領域 14 の面積が小さくなる。ボディ領域 13 の面積が小さくなることで、ボディ領域 13 の電位が安定化する。また、中間領域 10B に存在するソース領域 14 は、電位がフローティングになっており、電位が不安定である。しかしながら、ソース領域 14 の面積が小さいことから、このような不安定な電位のソース領域 14 による耐量低下等の問題も抑制されている。

#### 【0046】

さらに、第 2 コンタクト領域 16 は、マスク 54 を利用して第 1 コンタクト領域 15 と同時に形成することができる。この製造方法は、第 2 コンタクト領域 16 を形成するための専用の工程を増加させることなく、第 1 コンタクト領域 15 を形成する工程と一緒に第 2 コンタクト領域 16 を形成することができる。

#### 【0047】

10

20

30

40

50

## (第2実施形態)

図15に、第2実施形態の半導体装置2を示す。なお、第1実施形態の半導体装置1と共に通する構成要素については同一の符号を付し、その説明を省略する。半導体装置2は、半導体層10が電流拡散領域102を有していることを特徴としている。

## 【0048】

電流拡散領域102は、ドリフト領域12よりもn型不純物を高濃度に含有するN型層である。電流拡散領域102は、アクティブ領域10Aの全範囲と中間領域10Bの一部の範囲に亘って配置されており、ドリフト領域12とボディ領域13の間に設けられており、ドリフト領域12とボディ領域13の双方に接している。電流拡散領域102は、ドリフト領域12とボディ領域13の間ににおいて面的に広がって形成されており、トレンチゲート30の底面及び側面のうちの下側部分に接している。電流拡散領域102は、図5～7で説明したイオン注入工程において、共通のマスク52を利用して形成することができる。このため、電流拡散領域102は、専用のマスクを成膜するための工程を追加することなく形成することができる。

## 【0049】

このような電流拡散領域102が設けられていると、ドリフト領域12内を電流が拡散して流れることができる。このため、半導体装置2は、低オン抵抗な特性を有することができる。

## 【0050】

## (第3実施形態)

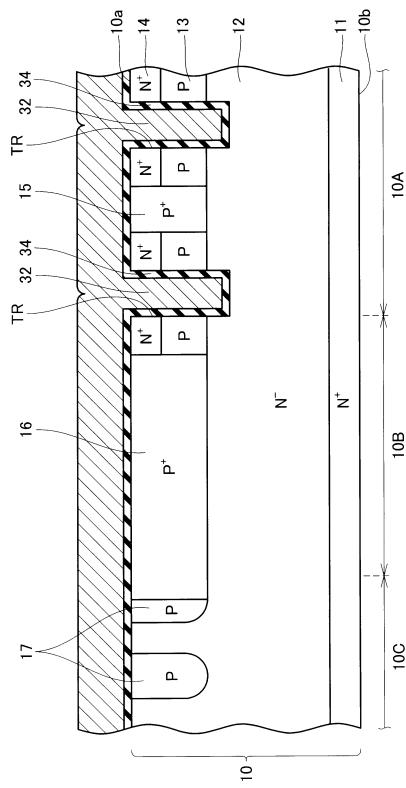

図16に、第3実施形態の半導体装置3を示す。なお、第2実施形態の半導体装置2と共に通する構成要素については同一の符号を付し、その説明を省略する。半導体装置3は、半導体層10が複数のディープ領域104を有していることを特徴としている。

## 【0051】

ディープ領域104は、p型不純物を含有するP型層である。ディープ領域104は、アクティブ領域10Aと中間領域10Bの各々に配置されており、ボディ領域13の下面からトレンチゲート30の底面よりも深い位置まで伸びている。ディープ領域104の底面は、電流拡散領域102の底面より浅くてもよく、電流拡散領域102の底面より深くてもよい。アクティブ領域10Aに設けられているディープ領域104は、第1コンタクト領域15の下方に配置されており、第1コンタクト領域15の底面に接しており、半導体層10を平面視したときに、第1コンタクト領域15に沿って、即ち、トレンチゲート30の長手方向と平行に伸びている。

## 【0052】

図16では、アクティブ領域10Aに設けられているディープ領域104が1つのみ図示されているが、実際には、アクティブ領域10Aに複数のディープ領域104が設けられている。このため、アクティブ領域10Aに設けられている複数のディープ領域104は、半導体層10を平面視したときに、トレンチゲート30の長手方向に沿って伸びており、トレンチゲート30の長手方向に直交する方向に間隔を開けて配置されている。隣り合うディープ領域104の間には、電流拡散領域102が設けられている。中間領域10Bに設けられているディープ領域104は、第2コンタクト領域16の下方に配置されており、第2コンタクト領域16の底面に接しており、半導体層10を平面視したときに、第2コンタクト領域16に沿って、即ち、ボディ領域13及びソース領域14の周縁に沿って一巡している。ディープ領域104は、例えばイオン注入技術を利用して形成することができる。この場合、ディープ領域104を形成するときにガードリング17を同時に形成してもよい。具体的には、ディープ領域104とガードリング17の形成位置に対応して開口が形成されているマスクを半導体層10の上面に成膜した後に、イオン注入技術を利用して、そのマスクの開口越しにp型不純物をイオン注入することにより、ディープ領域104とガードリング17を同時に形成することができる。このように形成されるガードリング17は、ディープ領域104と同一の深さに、即ち、半導体層10の内部に配置される。ガードリング17とディープ領域104を同時形成すると、ガードリング17

10

20

30

40

50

とディープ領域 104 を形成するために必要なマスクと工程を共通化することができるの

で、低コストで半導体装置 3 を製造することができる。

【 0 0 5 3 】

このようなディープ領域 104 が設けられると、トレンチゲート 30 のゲート絶縁

膜 34 に加わる電界集中が緩和される。このため、半導体装置 3 は、高耐圧な特性を有す

ることができる。

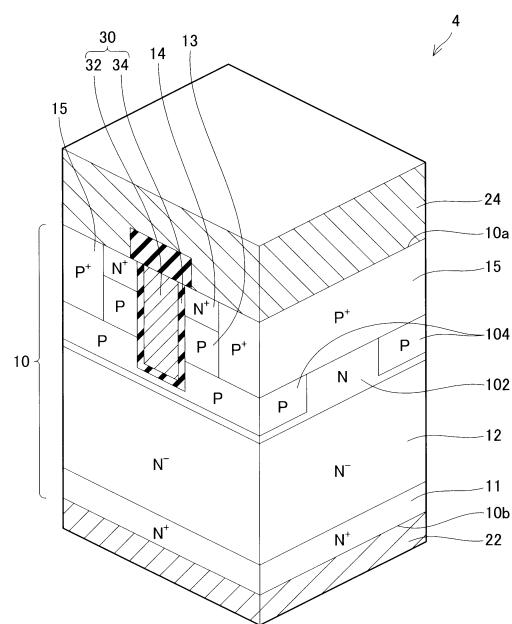

【 0 0 5 4 】

半導体装置 3 では、アクティブ領域 10A に設けられている複数のディープ領域 104

が、半導体層 10 を平面視したときに、トレンチゲート 30 の長手方向と平行に伸びてい

た。この例に代えて、図 17 に示す半導体装置 4 のように、アクティブ領域 10A に設け

られている複数のディープ領域 104 は、トレンチゲート 30 に交差して伸びていてもよ

い。

10

【 0 0 5 5 】

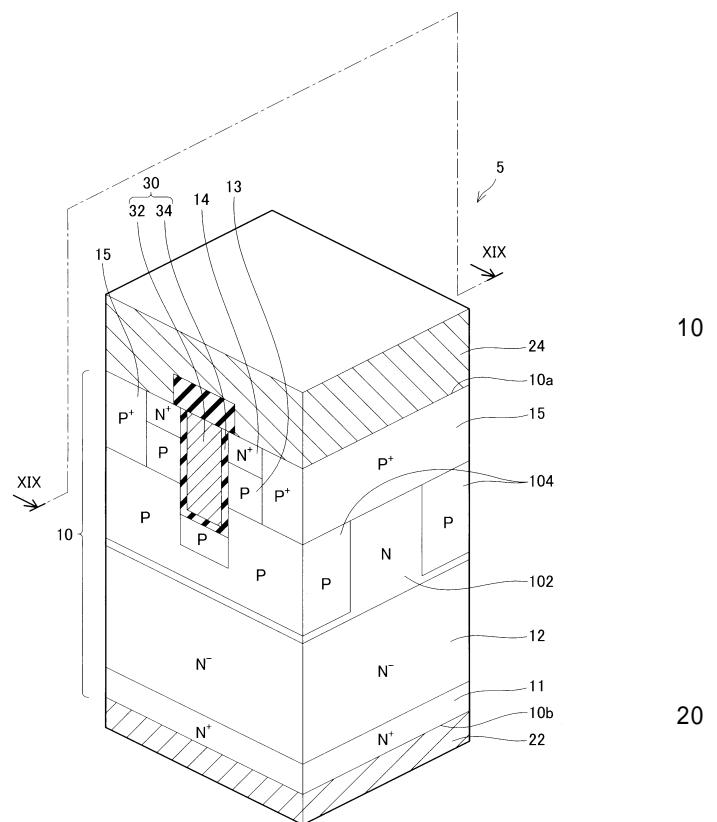

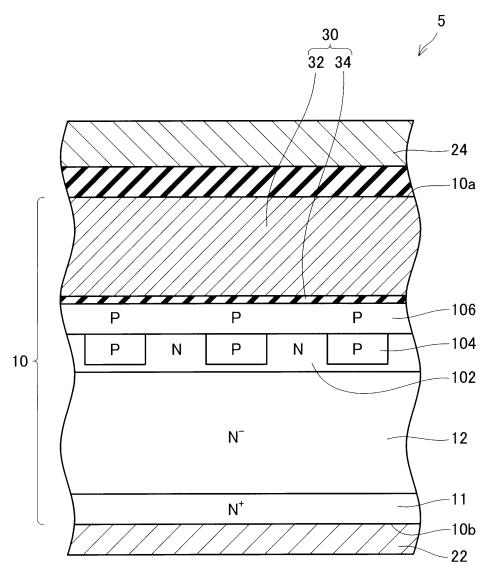

また、図 18 及び図 19 に示す半導体装置 5 のように、半導体層 10 がさらに、トレン

チゲート 30 の底面に接する電界緩和領域 106 を有していてもよい。電界緩和領域 10

6 は、p 型不純物を含有する P 型層である。電界緩和領域 106 は、トレンチゲート 30

の長手方向に沿って設けられており、半導体層 10 を平面視したときに、トレンチゲート

30 の一方端から他方端まで伸びている。電界緩和領域 106 は、トレンチ 14 の底面を

被覆するゲート絶縁膜 34 に接している。電界緩和領域 106 は、ディープ領域 104 よ

りも浅く形成されている。この例に代えて、電界緩和領域 106 は、ディープ領域 104

よりも深く形成されていてもよい。電界緩和領域 106 は、ディープ領域 104 を介して

ボディ領域 15 に電気的に接続されている。

20

【 0 0 5 6 】

このような電界緩和領域 106 が設けられると、トレンチゲート 30 のゲート絶縁

膜 34 に加わる電界集中が緩和される。このため、半導体装置 5 は、高耐圧な特性を有す

ることができる。また、このような電界緩和領域 106 が設けられると、トレンチゲ

ート 30 と電流拡散領域 102 が接する面積が減少するので、帰還容量（ゲート - ドレイ

ン間容量）が減少する。

【 0 0 5 7 】

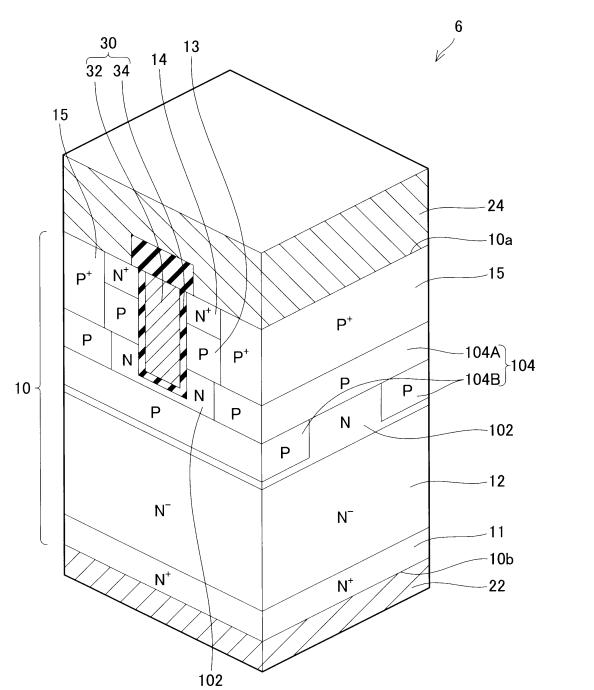

また、図 20 に示す半導体装置 6 のように、アクティブ領域 10A に設けられている複

数のディープ領域 104 は、トレンチゲート 30 の長手方向と平行に伸びている複数の上

側ディープ領域 104A と、複数の上側ディープ領域 104A の下方に配置されていると

ともにトレンチゲート 30 に交差して伸びている複数の下側ディープ領域 104B と、を

有していてもよい。複数の上側ディープ領域 104A の各々は、ボディ領域 13 の底面か

らトレンチゲート 30 の底面を超えて伸びている。複数の上側ディープ領域 104A の各

々は、第 1 コンタクト領域 15 の下方に配置されており、第 1 コンタクト領域 15 の底面

に接している。隣り合う上側ディープ領域 104A の間には、電流拡散領域 102 が設け

られている。複数の下側ディープ領域 104B の各々は、複数の上側ディープ領域 104

A の各々の底面に接している。隣り合う下側ディープ領域 104B の間には、電流拡散領域

102 が設けられている。複数の下側ディープ領域 104B の各々の底面は、電流拡散

領域 102 の底面より浅くてもよく、電流拡散領域 102 の底面より深くてもよい。なお

、図示を省略するが、半導体装置 6 では、中間領域 10B の第 2 コンタクト領域 16 の下

方に上側ディープ領域 104A と下側ディープ領域 104B の双方が設けられている。

30

【 0 0 5 8 】

このようなディープ領域 104 が設けられると、トレンチゲート 30 のゲート絶縁

膜 34 に加わる電界集中がさらに緩和される。このため、半導体装置 6 は、さらに高耐圧

な特性を有することができる。

40

【 0 0 5 9 】

( 第 4 実施形態 )

図 21 に、第 4 実施形態の半導体装置 7 を示す。なお、第 3 実施形態の半導体装置 3 と

50

共通する構成要素については同一の符号を付し、その説明を省略する。半導体装置 7 は、第 1 コンタクト領域 15 とディープ領域 104 がトレンチゲート 30 の一方の側面を被覆するように設けられていることを特徴としている。

#### 【 0 0 6 0 】

第 1 コンタクト領域 15 は、トレンチゲート 30 の側面のうちの上側部分に接している。ディープ領域 104 は、トレンチゲート 30 の側面のうちの下側部分と底面の一部に接している。このように、トレンチゲート 30 と接するように第 1 コンタクト領域 15 及びディープ領域 104 が設けられているので、ゲート絶縁膜 34 に加わる電界集中が良好に緩和される。一方、半導体装置 7 では、トレンチゲート 30 の一方の側面がチャネルとして機能しない。しかしながら、トレンチゲート 30 の一方の側面が第 1 コンタクト領域 15 及びディープ領域 104 とオーバーラップするように配置されることで、トレンチゲート 30 のピッチを狭くすることができ、チャネル面積が確保される。したがって、半導体装置 6 は、オン抵抗の低下を抑えながら、ゲート絶縁膜 34 に加わる電界集中を良好に緩和することができる。

#### 【 0 0 6 1 】

以下、本明細書で開示される技術の特徴を整理する。なお、以下に記載する技術要素は、それぞれ独立した技術要素であって、単独あるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。

#### 【 0 0 6 2 】

本明細書が開示する半導体装置の一例は、第 1 主面と第 2 主面を有する半導体層と、トレンチゲートと、を備えることができる。前記半導体層は、アクティブ領域と、前記アクティブ領域の周囲を一巡するように配置されている外周領域と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域と、に区画されている。前記アクティブ領域は、前記トレンチゲートが配置されており、電流のオンとオフを制御するためのスイッチング構造が形成されている領域である。前記外周領域は、前記半導体装置がオフしたときに、前記アクティブ領域から外周に向けて空乏層を伸展させるための外周耐圧構造が形成されている領域である。前記外周耐圧構造は、特に限定されるものではないが、例えばガードドーリングであってもよい。前記中間領域は、前記アクティブ領域に配置されている前記トレンチゲートの最外周側の端部から前記外周領域に配置されている前記外周耐圧構造の最内周側の端部まで間の領域である。前記半導体層は、第 1 導電型のドリフト領域と、第 2 導電型のボディ領域と、第 1 導電型のソース領域と、第 2 導電型の第 1 コンタクト領域と、第 2 導電型の第 2 コンタクト領域と、を有することができる。前記ドリフト領域は、前記アクティブ領域と前記中間領域と前記外周領域に配置されている。前記ボディ領域は、前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域上に設けられている。典型的には、前記ボディ領域は、前記アクティブ領域の全範囲と前記中間領域の一部の範囲に配置されている。前記ボディ領域は、前記ドリフト領域に接するように前記ドリフト領域上に設けられていてもよいし、他の領域を介して前記ドリフト領域上に設けられていてもよい。前記ソース領域は、前記アクティブ領域と前記中間領域に配置されており、前記ボディ領域上に設けられている。典型的には、前記ソース領域は、前記アクティブ領域の全範囲と前記中間領域の一部の範囲に配置されている。前記ソース領域は、前記ボディ領域に接するように前記ボディ領域上に設けられていてもよいし、他の領域を介して前記ボディ領域上に設けられていてもよい。前記第 1 コンタクト領域は、前記アクティブ領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、第 2 導電型不純物の濃度が前記ボディ領域よりも濃い。前記第 2 コンタクト領域は、前記中間領域に配置されており、前記ソース領域を超えて前記ボディ領域に達するように設けられており、前記ソース領域の周縁に沿って前記ソース領域の周囲を一巡しており、第 2 導電型不純物の濃度が前記ボディ領域よりも濃い。前記トレンチゲートは、前記アクティブ領域に配置されており、前記第 1 主面から前記ソース領域と前記ボディ領域を超えて伸びている。前記第 1 コンタクト領域と前記第 2 コンタクト領域の第 2 導電型不純物の深さ方向の濃度分布が一致して

10

20

30

40

50

いる。

【 0 0 6 3 】

上記半導体装置では、前記第1コンタクト領域と前記第2コンタクト領域の底面が前記ボディ領域の底面と略同一深さであってもよい。この半導体装置では、前記第2コンタクト領域と前記ボディ領域の底面が略同一面となるので、両者の底面の間に角部が形成されない。このため、前記中間領域に前記第2コンタクト領域を形成しても、電界集中箇所が形成されない。

【 0 0 6 4 】

上記半導体装置では、前記半導体層がさらに、第2導電型の複数のガードリングを有していてもよい。前記複数のガードリングは、前記外周領域に配置されており、前記アクティブ領域及び前記中間領域の周囲を一巡している。前記第2コンタクト領域は、前記複数のガードリングのうちの最内周のガードリングに接している。

10

【 0 0 6 5 】

上記半導体装置では、前記半導体層がさらに第1導電型の電流拡散領域を有していてもよい。前記電流拡散領域は、前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられており、前記ドリフト領域よりも第1導電型不純物の濃度が濃い。前記電流拡散領域は、前記トレンチゲートの側面に接している。典型的には、前記電流拡散領域は、前記アクティブ領域の全範囲と前記中間領域の一部の範囲に配置されている。このような前記電流拡散領域が設けられると、上記半導体装置は低オン抵抗な特性を有することができる。

20

【 0 0 6 6 】

上記半導体装置では、前記第1コンタクト領域が、前記半導体層の前記第1主面上に設けられているソース電極と接触する位置に存在するシリサイド層を有していてもよい。この場合、前記第1コンタクト領域の第2導電型不純物の深さ方向の濃度分布は、前記シリサイド層の底面近傍が最大濃度である。この半導体装置では、前記第1コンタクト領域と前記ソース電極の接触抵抗を低下させながら、前記第1コンタクト領域を形成するための第2導電型不純物のドーズ量を小さくすることができる。

【 0 0 6 7 】

上記半導体装置では、前記半導体層がさらに、第2導電型の複数のディープ領域を有していてもよい。前記複数のディープ領域は、前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられている。前記複数のディープ領域は、前記半導体層を平面視したときに、第1方向に沿って伸びており、前記第1方向に直交する第2方向に間隔を開けて配置されている。前記複数のディープ領域の各々は、前記ボディ領域の底面から前記トレンチゲートの底面を超えて伸びている。前記複数のディープ領域の各々は、前記中間領域において、前記第2コンタクト領域に接している。隣り合う前記ディープ領域の間の領域には、例えば前記ドリフト領域及び/又は前記電流拡散領域が配置されていてもよい。このような前記複数のディープ領域が設けられていると、前記半導体装置は高耐圧な特性を有することができる。

30

【 0 0 6 8 】

前記複数のディープ領域を有する上記半導体装置では、前記半導体層を平面視したときに、前記第1方向が前記トレンチゲートの長手方向と平行であってもよい。この場合、前記トレンチゲートの一方の側面が、対応する前記第1コンタクト領域及び前記ディープ領域によって被覆されていてもよい。この半導体装置は、低オン抵抗な特性と高耐圧な特性を両立した特性を有することができる。

40

【 0 0 6 9 】

前記複数のディープ領域を有する上記半導体装置では、前記半導体層を平面視したときに、前記第1方向が前記トレンチゲートの長手方向に対して交差していてもよい。典型的には、前記第1方向が前記トレンチゲートの長手方向に対して直交していてもよい。

【 0 0 7 0 】

上記半導体装置では、前記半導体層がさらに、第2導電型の複数のディープ領域、を有

50

していてもよい。前記複数のディープ領域は、前記アクティブ領域と前記中間領域に配置されており、前記ドリフト領域と前記ボディ領域の間に設けられている。前記複数のディープ領域は、複数の上側ディープ領域と、前記複数の上側ディープ領域の下方に配置されている複数の下側ディープ領域と、を有していてもよい。前記複数の上側ディープ領域は、前記半導体層を平面視したときに、第1方向に沿って伸びてあり、前記第1方向に直交する第2方向に間隔を開けて配置されている。前記複数の上側ディープ領域の各々は、前記ボディ領域の底面から前記トレンチゲートの底面を超えて伸びている。前記複数の上側ディープ領域の各々は、前記中間領域において、前記第2コンタクト領域に接している。前記複数の下側ディープ領域は、前記半導体層を平面視したときに、前記第1方向とは異なる第3方向に沿って伸びてあり、前記第3方向に直交する第4方向に間隔を開けて配置されている。前記複数の下側ディープ領域の各々は、前記上側ディープ領域に接している。隣り合う前記上側ディープ領域の間の領域には、例えば前記ドリフト領域及び／又は前記電流拡散領域が配置されていてもよい。同様に、隣り合う前記下側ディープ領域の間の領域には、例えば前記ドリフト領域及び／又は前記電流拡散領域が配置されていてもよい。このような前記上側ディープ領域と前記下側ディープ領域が設けられると、前記半導体装置は高耐圧な特性を有することができる。

#### 【0071】

本明細書が開示する半導体装置の製造方法の一例は、第1マスク成膜工程と、ボディ領域形成工程と、ソース領域形成工程と、第2マスク成膜工程と、コンタクト領域形成工程と、トレンチゲート形成工程と、を備えることができる。前記第1マスク成膜工程では、第1主面と第2主面を有する第1導電型の半導体層の前記第1主面上に第1マスクを成膜する。前記半導体層は、アクティブ領域と、前記アクティブ領域の周囲を一巡するように配置されている外周領域と、前記アクティブ領域と前記外周領域の間であって前記アクティブ領域の周囲を一巡するように配置されている中間領域と、に区画されている。前記第1マスクは、前記アクティブ領域と前記中間領域に対応して開口が形成されている。典型的には、前記第1マスクは、前記アクティブ領域の全範囲と前記中間領域の一部の範囲に対応して開口が形成されている。前記ボディ領域形成工程では、前記半導体層の前記第1主面に向けて前記第1マスク越しに第2導電型不純物をイオン注入し、前記半導体層内にボディ領域を形成する。前記ソース領域形成工程では、前記半導体層の前記第1主面に向けて前記第1マスク越しに第1導電型不純物をイオン注入し、前記半導体層内の前記ボディ領域よりも浅い範囲にソース領域を形成する。前記ボディ領域形成工程と前記ソース領域形成工程は、その実施順序が特に限定されるものではない。前記第2マスク成膜工程では、前記半導体層の前記第1主面上に第2マスクを成膜する。前記第2マスクは、前記アクティブ領域の所定位置に内側開口が形成されるとともに、前記ソース領域の周縁が露出するように前記ソース領域の周縁に沿って前記ソース領域の周囲を一巡する周縁開口が形成されている。前記コンタクト領域形成工程では、前記半導体層の前記第1主面に向けて前記第2マスク越しに第2導電型不純物をイオン注入してコンタクト領域を形成する。前記コンタクト領域形成工程では、前記第2マスクの前記内側開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第1コンタクト領域を形成し、前記第2マスクの前記周縁開口に対応した前記半導体層内に前記ソース領域を超えて前記ボディ領域に達するとともに第2導電型不純物の濃度が前記ボディ領域よりも濃い第2導電型の第2コンタクト領域を形成する。前記トレンチゲート形成工程では、前記アクティブ領域に、前記第1主面から前記ソース領域と前記ボディ領域を超えて伸びるトレンチゲートを形成する。

#### 【0072】

上記製造方法の前記コンタクト領域形成工程では、前記第1コンタクト領域と前記第2コンタクト領域の底面が前記ボディ領域の底面と略同一深さとなるように形成されてもよい。

#### 【0073】

10

20

30

40

50

前記半導体層の前記外周領域には、前記アクティブ領域及び前記中間領域の周囲を一巡している第2導電型の複数のガードリングが配置されていてもよい。上記製造方法の前記コンタクト領域形成工程では、前記第2コンタクト領域が前記複数のガードリングのうちの最内周のガードリングに接するように形成されてもよい。なお、前記複数のガードリングは、前記ボディ領域を形成するときに、前記外周領域に同時に形成されてもよい。

#### 【0074】

上記製造方法はさらに、電流拡散領域形成工程を備えていてもよい。前記電流拡散工程では、前記半導体層の前記第1主面に向けて前記第1マスク越しに第1導電型不純物をイオン注入し、前記半導体層内の前記ボディ領域よりも深い範囲に電流拡散領域を形成する。前記電流拡散領域は、前記トレンチゲートの側面に接している。

10

#### 【0075】

以上、実施形態について詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。本明細書または図面に説明した技術要素は、単独あるいは各種の組み合わせによって技術有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの1つの目的を達成すること自体で技術有用性を持つものである。

#### 【符号の説明】

#### 【0076】

20

10：半導体層、10A：アクティブ領域、10B：中間領域、10C：外周領域、

11：ドレイン領域、12：ドリフト領域、13：ボディ領域、14：ソース領域、

15：第1コンタクト領域、16：第2コンタクト領域、17：ガードリング、22

：ドレイン電極、24：ソース電極、30：トレンチゲート、32：ゲート電極、

34：ゲート絶縁膜、40：層間絶縁膜

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図5】

【図6】

10

20

30

40

【図7】

【図8】

50

【 9 】

【図10】

### 【図 1 1】

【 図 1 2 】

10

20

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

### 【図21】

30

40

50

## フロントページの続き

## (51)国際特許分類

| F I    |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 P |

| H 01 L | 29/06 | 3 0 1 G |

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/78 | 6 5 8 A |

| H 01 L | 29/78 | 6 5 2 J |

| H 01 L | 29/78 | 6 5 2 H |

## (56)参考文献

特開2019-102737 (JP, A)

特開2009-141185 (JP, A)

国際公開第2014/068813 (WO, A1)

特表2020-512682 (JP, A)

特開2011-253837 (JP, A)

特開2020-141130 (JP, A)

特開2011-124464 (JP, A)

米国特許出願公開第2015/0187877 (US, A1)

国際公開第2020/235629 (WO, A1)

## (58)調査した分野

(Int.Cl. , DB名)

H 01 L 29 / 78

H 01 L 29 / 12

H 01 L 29 / 06

H 01 L 21 / 336