(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6130170号

(P6130170)

(45) 発行日 平成29年5月17日(2017.5.17)

(24) 登録日 平成29年4月21日(2017.4.21)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 29/786  | (2006.01) | HO1L | 29/78 | 619A |

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 626C |

| HO1L 21/28   | (2006.01) | HO1L | 29/78 | 617T |

| HO1L 29/417  | (2006.01) | HO1L | 29/78 | 617V |

| HO1L 21/8242 | (2006.01) | HO1L | 29/78 | 618B |

請求項の数 8 (全 101 頁) 最終頁に続く

(21) 出願番号 特願2013-42905 (P2013-42905)

(22) 出願日 平成25年3月5日 (2013.3.5)

(65) 公開番号 特開2013-214732 (P2013-214732A)

(43) 公開日 平成25年10月17日 (2013.10.17)

審査請求日 平成28年2月16日 (2016.2.16)

(31) 優先権主張番号 特願2012-51261 (P2012-51261)

(32) 優先日 平成24年3月8日 (2012.3.8)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2012-51263 (P2012-51263)

(32) 優先日 平成24年3月8日 (2012.3.8)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 田中 哲弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 高橋 絵里香

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

審査官 竹口 泰裕

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

ゲート電極と、前記ゲート電極上のゲート絶縁膜と、前記ゲート絶縁膜上にあり、前記ゲート電極と重畳する半導体膜と、前記半導体膜上の絶縁膜と、を有し、前記絶縁膜は、結晶性絶縁膜と、前記結晶性絶縁膜上の酸化アルミニウム膜とを有し、前記酸化アルミニウム膜は結晶性を有し、

前記結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含むことを特徴とする半導体装置。 10

【請求項 2】

絶縁膜と、前記絶縁膜上のゲート電極と、前記ゲート電極上のゲート絶縁膜と、前記ゲート絶縁膜上にあり、前記ゲート電極と重畳する半導体膜と、を有し、前記絶縁膜は、結晶性絶縁膜と、前記結晶性絶縁膜上の酸化アルミニウム膜とを有し、前記酸化アルミニウム膜は結晶性を有し、

前記結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含むことを特徴とする半導体装置。

【請求項 3】

絶縁膜と、

前記絶縁膜上の半導体膜と、

前記半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上にあり、前記半導体膜と重畳するゲート電極と、を有し、

前記絶縁膜は、結晶性絶縁膜と、前記結晶性絶縁膜上の酸化アルミニウム膜とを有し、

前記酸化アルミニウム膜は結晶性を有し、

前記結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含むことを特徴とする半導体装置。

【請求項4】

半導体膜と、

10

前記半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上にあり、前記半導体膜と重畳するゲート電極と、

前記ゲート電極上の絶縁膜と、を有し、

前記絶縁膜は、結晶性絶縁膜と、前記結晶性絶縁膜上の酸化アルミニウム膜とを有し、

前記酸化アルミニウム膜は結晶性を有し、

前記結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含むことを特徴とする半導体装置。

【請求項5】

半導体膜と、

20

前記半導体膜と重畳するゲート電極と、

前記半導体膜および前記ゲート電極の間に位置するゲート絶縁膜と、を有し、

前記ゲート絶縁膜は、結晶性絶縁膜と、前記結晶性絶縁膜上の酸化アルミニウム膜とを有し、

前記酸化アルミニウム膜は結晶性を有し、

前記結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含むことを特徴とする半導体装置。

【請求項6】

請求項1乃至請求項5のいずれか一において、

前記酸化アルミニウム膜の密度が $3.2\text{ g/cm}^3$ 以上 $4.1\text{ g/cm}^3$ 以下であることを特徴とする半導体装置。

30

【請求項7】

請求項1乃至請求項6のいずれか一において、

前記半導体膜は、酸化物半導体膜であることを特徴とする半導体装置。

【請求項8】

請求項7において、

前記酸化物半導体膜は、Inを含むことを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその作製方法に関する。

40

【0002】

また、本発明は、物、方法、製造方法、プロセス、マシーン、マニュファクチャ、または、組成物（コンポジション オブ マター）に関する。特に、本発明は、例えば、半導体装置、記憶装置、表示装置、液晶表示装置、発光装置、それらの駆動方法、またはそれらを生産する方法に関する。または、本発明は、例えば、当該記憶装置、当該表示装置、または当該発光装置を有する電子機器に関する。

【0003】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能し得る装置全般をいい、電気光学装置、半導体回路および電子機器などは全て半導体装置である。

【背景技術】

50

## 【0004】

絶縁表面を有する基板上に形成された半導体膜を用いて、トランジスタを構成する技術が注目されている。該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体膜としてシリコン膜が知られている。

## 【0005】

トランジスタの半導体膜に用いられるシリコン膜は、用途によって非晶質と多結晶とが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積の成膜技術が確立されている非晶質シリコン膜を用いると好適である。一方、駆動回路を一体形成した高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコン膜を用いると好適である。多結晶シリコン膜は、非晶質シリコン膜に対し高温での熱処理、またはレーザービーム処理を行うことで形成する方法が知られる。

10

## 【0006】

さらに、近年では酸化物半導体膜が注目されている。例えば、キャリア密度が  $10^{18} / \text{cm}^3$  未満であるインジウム、ガリウムおよび亜鉛を含む非晶質酸化物半導体膜を用いたトランジスタが開示されている（特許文献1参照。）。

## 【0007】

酸化物半導体膜は、スパッタリング法を用いて成膜できるため、大型の表示装置を構成するトランジスタに適用することができる。また、酸化物半導体膜を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路を一体形成した高機能の表示装置を実現できる。また、非晶質シリコン膜を用いたトランジスタの生産設備の一部を改良して利用することができるため、設備投資を抑えられるメリットもある。

20

## 【0008】

トランジスタの設けられる基板としてガラスを用いる場合、ガラスに起因する不純物の拡散により、トランジスタの電気特性の劣化が起こることがある。当該劣化を抑制するためには、基板とトランジスタとの間にバリア性を有する膜が設けられる。

## 【先行技術文献】

## 【特許文献】

## 【0009】

## 【特許文献1】特開2006-165528号公報

30

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0010】

安定した電気特性を有し、信頼性の高い半導体装置を提供することを課題の一とする。また、安定した電気特性を有する半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置を提供することを課題の一とする。また、動作速度の速い半導体装置を提供することを課題の一とする。また、消費電力の小さい半導体装置を提供することを課題の一とする。また、歩留まり高く半導体装置を提供することを課題の一とする。

## 【課題を解決するための手段】

## 【0011】

本発明の一態様に係る半導体装置は、絶縁表面上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上にあり、ゲート電極と重畳して設けられた半導体膜と、半導体膜上に設けられた保護膜と、を有し、保護膜は、結晶性絶縁膜、および結晶性絶縁膜上の酸化アルミニウム膜を有する。

40

## 【0012】

または、本発明の一態様に係る半導体装置は、下地膜と、下地膜上に設けられた半導体膜と、半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上にあり、前記半導体膜と重畳して設けられたゲート電極と、を有し、下地膜は、結晶性絶縁膜、および結晶性絶縁膜上の酸化アルミニウム膜を有する。

## 【0013】

50

または、本発明の一態様に係る半導体装置は、下地膜と、下地膜上に設けられた半導体膜と、半導体膜上的一部分に設けられたゲート絶縁膜と、ゲート絶縁膜上にあり、前記半導体膜と重畳して設けられたゲート電極と、半導体膜および前記ゲート電極上に設けられた保護膜と、を有し、保護膜は、結晶性絶縁膜、および結晶性絶縁膜上の酸化アルミニウム膜を有する。

## 【0014】

または、本発明の一態様に係る半導体装置は、半導体膜と、半導体膜と重畳するゲート電極と、半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、を有し、ゲート絶縁膜は、結晶性絶縁膜、および結晶性絶縁膜上の酸化アルミニウム膜を有する。

## 【0015】

また、結晶性絶縁膜は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含む。

## 【0016】

また、酸化アルミニウム膜は結晶性を有する。

## 【0017】

また、酸化アルミニウム膜の密度が3.2g/cm<sup>3</sup>以上4.1g/cm<sup>3</sup>以下である。

## 【0018】

結晶性絶縁膜上に酸化アルミニウム膜を設けることで、結晶性を有し、密度が3.2g/cm<sup>3</sup>以上4.1g/cm<sup>3</sup>以下である酸化アルミニウム膜を得ることができる。当該酸化アルミニウム膜は、不純物に対するバリア性が高い。そのため、不純物に起因したトランジスタの電気特性の変動を抑制することができる。

## 【0019】

また、密度が3.2g/cm<sup>3</sup>以上4.1g/cm<sup>3</sup>以下である酸化アルミニウム膜は、薬液やプラズマなどに対する耐性が高く、意図しないエッティングなどが起こりにくい。そのため、酸化アルミニウム膜の意図しないエッティングによる形状不良の発生を抑制できる。トランジスタを構成する各層の形状不良は、発生箇所において、エッティング残渣物が生じる、またさらなる形状不良の原因ともなる。従って、安定した電気特性のトランジスタを提供するためには、形状不良の発生を抑制することが重要となる。また、当該酸化アルミニウム膜は、不純物に対するバリア性が高い。また、欠陥が少ないため、当該酸化アルミニウム膜をゲート絶縁膜に用いることで、ゲート絶縁膜の欠陥に起因したトランジスタの電気特性の劣化を抑制することができる。

## 【発明の効果】

## 【0020】

結晶性絶縁膜上に酸化アルミニウム膜を設けることで、結晶性を有し、密度が3.2g/cm<sup>3</sup>以上4.1g/cm<sup>3</sup>以下である酸化アルミニウム膜を得ることができる。そのため、安定した電気特性を有し、信頼性の高い半導体装置を提供することができる。また、安定した電気特性を有する半導体装置を提供することができる。また、信頼性の高い半導体装置を提供することできる。また、動作速度の速い半導体装置を提供することできる。また、消費電力の小さい半導体装置を提供することができる。また、歩留まり高く半導体装置を提供することできる。

## 【図面の簡単な説明】

## 【0021】

【図1】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図2】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図3】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図4】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図5】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図6】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

【図7】図1に示すトランジスタの作製方法の一例を示す断面図。

【図8】図1に示すトランジスタの作製方法の一例を示す断面図。

10

20

30

40

50

- 【図 9】図 2 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 10】図 2 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 11】図 3 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 12】図 3 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 13】図 4 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 14】図 4 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 15】図 5 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 16】図 5 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 17】図 6 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 18】図 6 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 19】図 6 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 20】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

- 【図 21】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

- 【図 22】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

- 【図 23】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

- 【図 24】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

- 【図 25】本発明の一態様に係るトランジスタの一例を示す上面図および断面図。

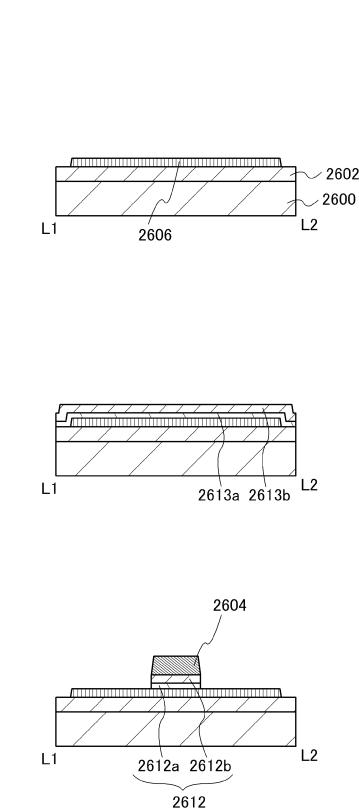

- 【図 26】図 20 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 27】図 20 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 28】図 21 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 29】図 21 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 30】図 22 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 31】図 22 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 32】図 23 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 33】図 23 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 34】図 24 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 35】図 24 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 36】図 25 に示すトランジスタの作製方法の一例を示す断面図。

- 【図 37】図 25 に示すトランジスタの作製方法の一例を示す断面図。

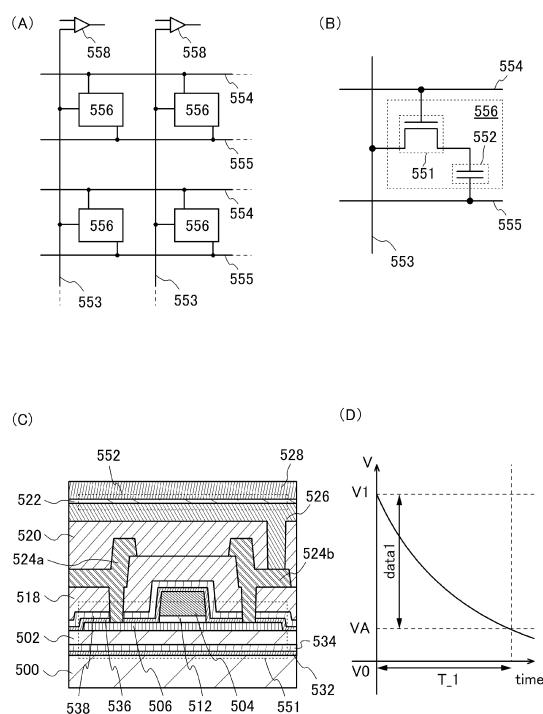

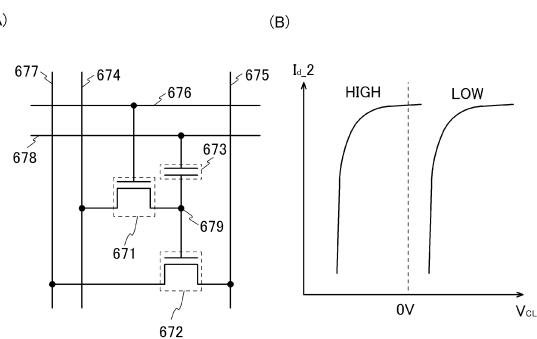

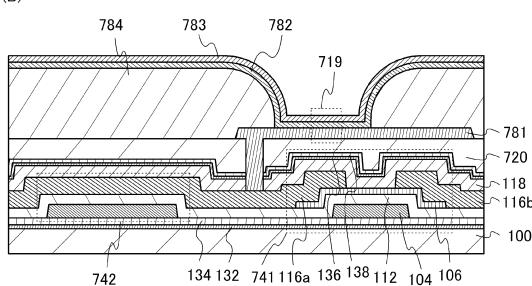

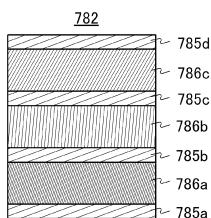

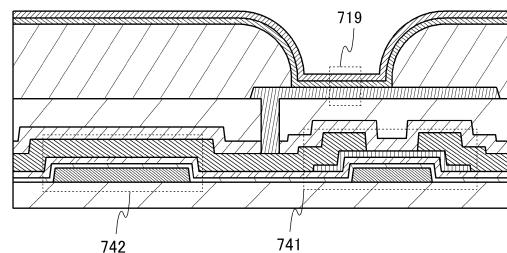

- 【図 38】本発明の一態様に係る半導体装置の回路図、断面図および電気特性を示す図。

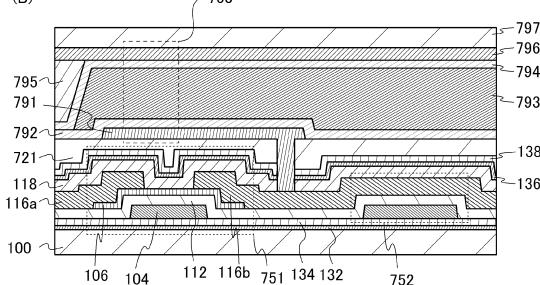

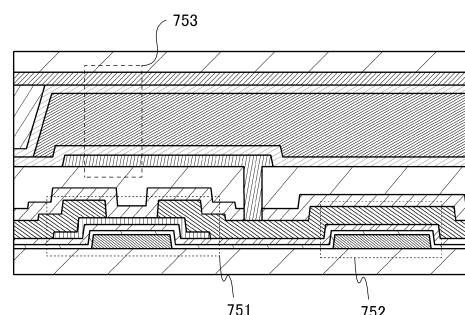

- 【図 39】本発明の一態様に係る半導体装置の断面図。

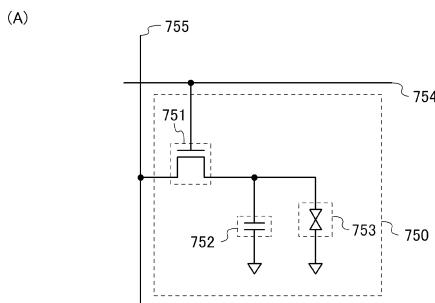

- 【図 40】本発明の一態様に係る半導体装置の回路図、電気特性を示す図および断面図。

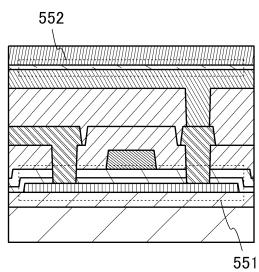

- 【図 41】本発明の一態様に係る半導体装置の断面図。

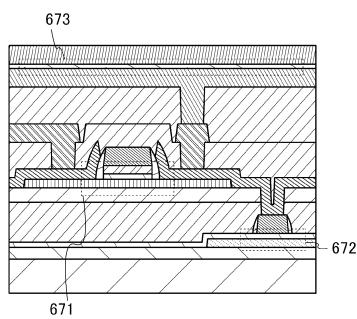

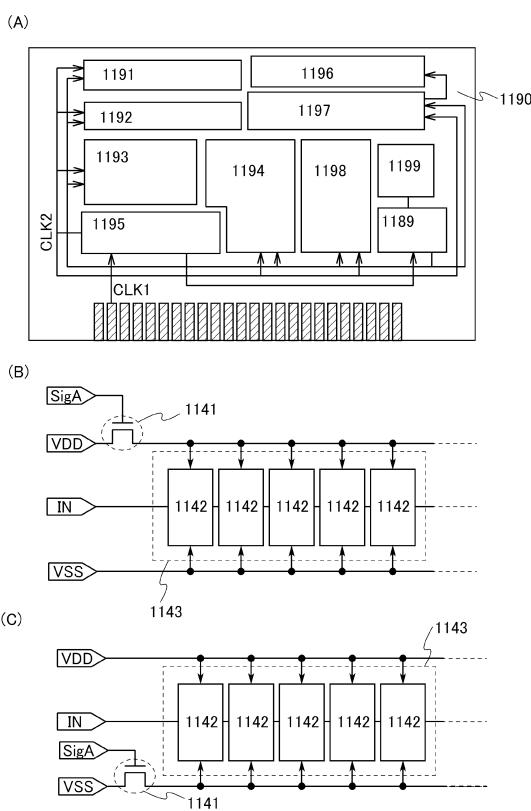

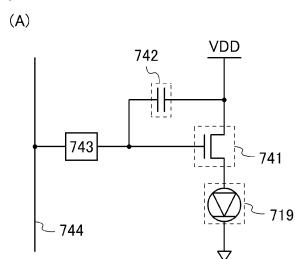

- 【図 42】本発明の一態様に係る C P U の構成を示すブロック図。

- 【図 43】本発明の一態様に係る E L 素子を用いた表示装置の画素の一部の断面図、発光層の断面図および回路図。

- 【図 44】本発明の一態様に係る E L 素子を用いた表示装置の画素の一部の断面図。

- 【図 45】本発明の一態様に係る液晶素子を用いた表示装置の画素の回路図および断面図。

- 【図 46】本発明の一態様に係る液晶素子を用いた表示装置の画素の断面図。

- 【図 47】本発明の一態様に係る電子機器を説明する図。

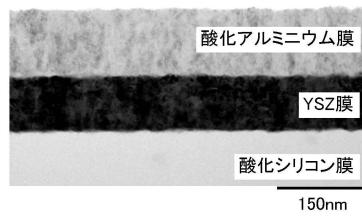

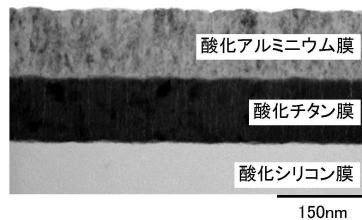

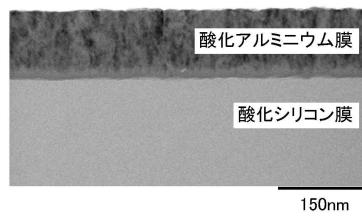

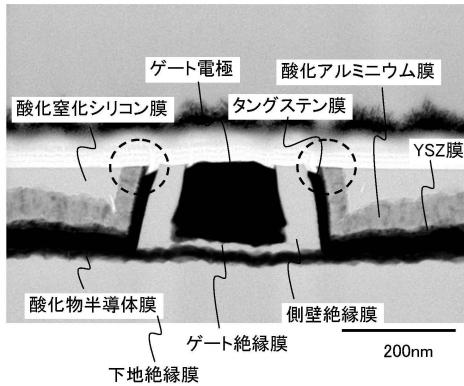

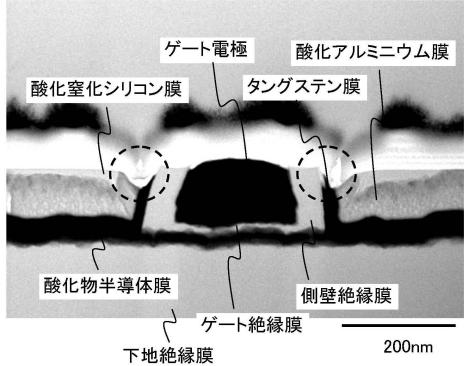

- 【図 48】各試料の走査透過電子顕微鏡による断面 T E 像。

- 【図 49】各試料の走査透過電子顕微鏡による断面 T E 像。

- 【発明を実施するための形態】

- 【0022】

- 本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じく

し、特に符号を付さない場合がある。

【0023】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、または／および、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、または置き換えなどを行うことが出来る。

【0024】

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、または明細書に記載される文章を用いて述べる内容のことである。

【0025】

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、または／および、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることが出来る。

【0026】

なお、図において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0027】

なお、図は、理想的な例を模式的に示したものであり、図に示す形状または値などに限定されない。例えば、製造技術による形状のばらつき、誤差による形状のばらつき、ノイズによる信号、電圧、若しくは電流のばらつき、または、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

【0028】

また、電圧は、ある電位と、基準の電位（例えば接地電位（GND）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。

【0029】

本明細書においては、「電気的に接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在しているだけの場合もある。

【0030】

なお、専門用語は、特定の実施の形態、または実施例などを述べる目的で用いられる場合が多い。ただし、本発明の一態様は、専門用語によって、限定して解釈されるものではない。

【0031】

なお、定義されていない文言（専門用語または学術用語などの科学技術文言を含む）は、通常の当業者が理解する一般的な意味と同等の意味として用いることが可能である。辞書等により定義されている文言は、関連技術の背景と矛盾がないような意味に解釈されることが好ましい。

【0032】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0033】

なお、明細書の中の図面や文章において規定されていない内容について、その内容を除くことを規定した発明を構成することが出来る。または、ある値について、上限値と下限値などで示される数値範囲が記載されている場合、その範囲を任意に狭めることで、または、その範囲の中の一点を除くことで、その範囲を一部除いて発明を規定することができる。これらにより、例えば、従来技術が本発明の技術的範囲内に入らないことを規定することができる。

【0034】

10

20

30

40

50

具体例としては、ある回路において、第1乃至第5のトランジスタを用いている回路図が記載されているとする。その場合、その回路が、第6のトランジスタを有していないことを発明として規定することが可能である。または、その回路が、容量素子を有していないことを規定することが可能である。さらに、その回路が、ある特定の接続構造を有している第6のトランジスタを有していない、と規定して発明を構成することができる。または、その回路が、ある特定の接続構造を有している容量素子を有していない、と規定して発明を構成することができる。例えば、ゲートが第3のトランジスタのゲートと接続されている第6のトランジスタを有していない、と発明を規定することが可能である。または、例えば、第1の電極が第3のトランジスタのゲートと接続されている容量素子を有していない、と発明を規定することが可能である。

10

#### 【0035】

別の具体例としては、ある値について、例えば、「ある電圧が、3V以上10V以下であることが好適である」と記載されているとする。その場合、例えば、ある電圧が、-2V以上1V以下である場合を除く、と発明を規定することが可能である。または、例えば、ある電圧が、13V以上である場合を除く、と発明を規定することが可能である。なお、例えば、その電圧が、5V以上8V以下であると発明を規定することも可能である。なお、例えば、その電圧が、概略9Vであると発明を規定することも可能である。なお、例えば、その電圧が、3V以上10V以下であるが、9Vである場合を除くと発明を規定することも可能である。

20

#### 【0036】

別の具体例としては、ある値について、例えば、「ある電圧が、10Vであることが好適である」と記載されているとする。その場合、例えば、ある電圧が、-2V以上1V以下である場合を除く、と発明を規定することが可能である。または、例えば、ある電圧が、13V以上である場合を除く、と発明を規定することが可能である。

#### 【0037】

別の具体例としては、ある物質の性質について、例えば、「ある膜は、絶縁膜である」と記載されているとする。その場合、例えば、その絶縁膜が、有機絶縁膜である場合を除く、と発明を規定することが可能である。または、例えば、その絶縁膜が、無機絶縁膜である場合を除く、と発明を規定することが可能である。

30

#### 【0038】

別の具体例としては、ある積層構造について、例えば、「AとBとの間に、ある膜が設けられている」と記載されているとする。その場合、例えば、その膜が、4層以上の積層膜である場合を除く、と発明を規定することが可能である。または、例えば、Aとその膜との間に、導電膜が設けられている場合を除く、と発明を規定することが可能である。

#### 【0039】

なお、本明細書等において記載されている発明は、さまざまな人が実施することが出来る。しかしながら、その実施は、複数の人にまたがって実施される場合がある。例えば、送受信システムの場合において、A社が送信機を製造および販売し、B社が受信機を製造および販売する場合がある。別の例としては、TFTおよび発光素子を有する発光装置の場合において、TFTが形成された半導体装置は、A社が製造および販売する。そして、B社がその半導体装置を購入して、その半導体装置に発光素子を成膜して、発光装置として完成させる、という場合がある。

40

#### 【0040】

このような場合、A社またはB社のいずれに対しても、特許侵害を主張できるような発明の一態様を、構成することが出来る。従って、A社またはB社に対して、特許侵害を主張できるような発明の一態様は、明確であり、本明細書等に記載されていると判断する事が出来る。例えば、送受信システムの場合において、送信機のみで発明の一態様を構成することができ、受信機のみで発明の一態様を構成することができ、それらの発明の一態様は、明確であり、本明細書等に記載されていると判断する事が出来る。別の例としては、TFTおよび発光素子を有する発光装置の場合において、TFTが形成された半導体装置

50

のみで発明の一態様を構成することができ、TFTおよび発光素子を有する発光装置のみで発明の一態様を構成することができ、それらの発明の一態様は、明確であり、本明細書等に記載されていると判断することが出来る。

【0041】

(実施の形態1)

本実施の形態では、本発明の一態様に係るトランジスタについて説明する。

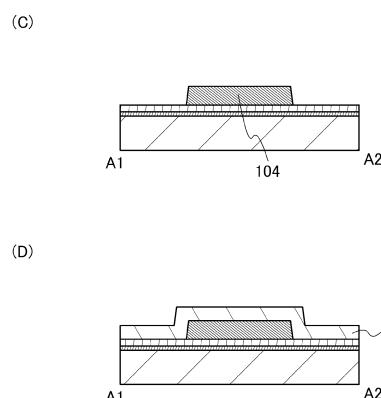

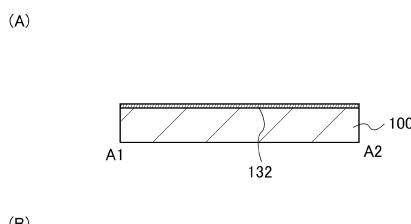

【0042】

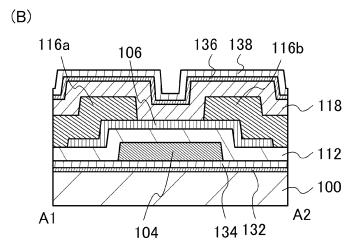

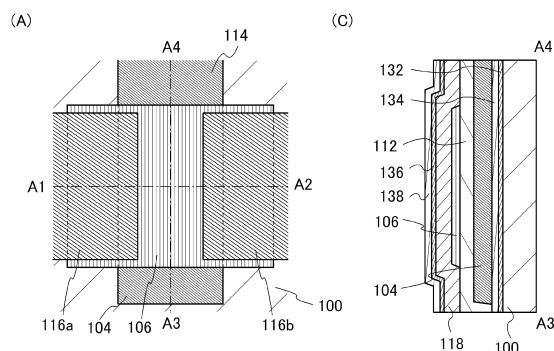

図1(A)は本発明の一態様に係るトランジスタの上面図である。図1(A)に示す一点鎖線A1-A2に対応する断面図を図1(B)に示す。また、図1(A)に示す一点鎖線A3-A4に対応する断面図を図1(C)に示す。なお、簡単のため、図1(A)においては、ゲート絶縁膜112などを省略して示す。

10

【0043】

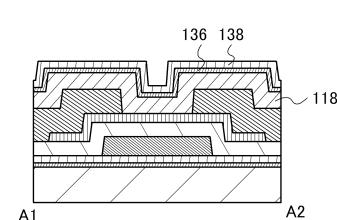

図1(B)は、基板100上に設けられた結晶性絶縁膜132と、結晶性絶縁膜132上に設けられた酸化アルミニウム膜134と、酸化アルミニウム膜134上に設けられたゲート電極104と、ゲート電極104上に設けられたゲート絶縁膜112と、ゲート絶縁膜112上にあり、ゲート電極104と重畳して設けられた半導体膜106と、半導体膜106上に設けられたソース電極116aおよびドレイン電極116bと、半導体膜106、ソース電極116aおよびドレイン電極116b上に設けられた結晶性絶縁膜136と、結晶性絶縁膜136上に設けられた酸化アルミニウム膜138と、を有するトランジスタの断面図である。

20

【0044】

ここで、結晶性絶縁膜132および結晶性絶縁膜136は、Mg、Ti、V、Cr、Y、ZrおよびTaのいずれか一種以上を含む。具体的には、酸化マグネシウム、酸化チタン、酸化バナジウム、酸化クロム、酸化イットリウム、酸化ジルコニウムおよび酸化タンタルのいずれかを一種以上含むと好ましい。例えば、酸化ジルコニウムおよび酸化イットリウムを含む絶縁膜を用いることができる。

【0045】

結晶性絶縁膜132および結晶性絶縁膜136は、結晶性を有する絶縁膜である。具体的にはX線回折(XRD:X-Ray Diffraction)、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

30

【0046】

酸化アルミニウム膜134および酸化アルミニウム膜138は、結晶性を有する。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる。

【0047】

酸化アルミニウム膜134は、結晶性絶縁膜132との界面近傍においても結晶性を有する。また、酸化アルミニウム膜138は、結晶性絶縁膜136との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。非晶質酸化アルミニウム膜は、結晶性を有する酸化アルミニウム膜と比べて低密度の酸化アルミニウム膜である。

40

【0048】

酸化アルミニウム膜134および酸化アルミニウム膜138は、高密度の酸化アルミニウム膜である。具体的には、X線反射率(XRR:X-Ray Reflectivity)またはラザフォード後方散乱分光法(RBS:Rutherford Backscattering Spectrometry)によって密度が $3.2\text{ g/cm}^3$ 以上 $4.1\text{ g/cm}^3$ 以下の酸化アルミニウム膜である。酸化アルミニウム膜134および酸化アルミニウム膜138は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0049】

なお、酸化アルミニウム膜134は、結晶性絶縁膜132の近傍に低密度層を有さない。

50

また、酸化アルミニウム膜 138 は、結晶性絶縁膜 136 の近傍に低密度層を有さない。具体的には、XRR によって密度が  $3.2 \text{ g/cm}^3$  未満の層を有さない。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッティングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

#### 【0050】

半導体膜 106 は、シリコン膜、ゲルマニウム膜、シリコングルマニウム膜、ヒ化ガリウム膜、炭化シリコン膜または窒化ガリウム膜を用いればよい。なお、半導体膜 106 として、有機半導体膜を用いてもよい。また、半導体膜 106 として、酸化物半導体膜を用いてもよい。

10

#### 【0051】

なお、酸化物半導体膜として、In - M - Zn 酸化物膜を用いればよい。ここで、金属元素 M は酸素との結合エネルギーが In および Zn よりも高い元素である。または、In - M - Zn 酸化物膜から酸素が脱離することを抑制する機能を有する元素である。金属元素 M の作用によって、酸化物半導体膜中の酸素欠損の生成が抑制される。なお、酸化物半導体膜の酸素欠損はキャリアを生成することがある。そのため、金属元素 M の作用によって、酸化物半導体膜中のキャリア密度が増大し、オフ電流が増大することを抑制できる。また、酸素欠損に起因するトランジスタの電気特性の変動を低減することができ、信頼性の高いトランジスタを得ることができる。

20

#### 【0052】

金属元素 M は、具体的には Al、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Ga、Y、Zr、Nb、Mo、Sn、La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Hf、Ta または W とすればよく、好ましくは Al、Ti、Ga、Y、Zr、Ce または Hf とする。金属元素 M は、前述の元素から一種または二種以上選択すればよい。また、金属元素 M の代わりに Si または Ge を用いても構わない。

#### 【0053】

また、酸化物半導体膜は、水素濃度を、 $2 \times 10^{20} \text{ atoms/cm}^3$  以下、好ましくは  $5 \times 10^{19} \text{ atoms/cm}^3$  以下、さらに好ましくは  $1 \times 10^{19} \text{ atoms/cm}^3$  以下とする。これは、酸化物半導体膜に含まれる水素が、意図しないキャリアを生成することがあるためである。生成されたキャリアは、トランジスタのオフ電流を増大させ、かつトランジスタの電気特性を変動させる要因となる。従って、酸化物半導体膜の水素濃度を上述の範囲とすることで、トランジスタのオフ電流の増大を抑制し、かつトランジスタの電気特性の変動を抑制することができる。

30

#### 【0054】

酸化物半導体膜は、例えば非単結晶を有してもよい。非単結晶は、例えば、CAAC ( C Axis Aligned Crystal )、多結晶、微結晶、非晶質を有する。非晶質は、微結晶、CAAC よりも欠陥準位密度が高い。また、微結晶は、CAAC よりも欠陥準位密度が高い。なお、CAAC を有する酸化物半導体を、CAAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor ) と呼ぶ。

40

#### 【0055】

酸化物半導体膜は、例えば CAAC - OS を有してもよい。CAAC - OS は、例えば、c 軸配向し、a 軸または / および b 軸はマクロに揃っていない。

#### 【0056】

酸化物半導体膜は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。微結晶酸化物半導体膜は、例えば、1 nm 以上 10 nm 未満のサイズの微結晶 ( ナノ結晶ともいう。 ) を膜中に含む酸化物半導体を有している。

50

## 【0057】

酸化物半導体膜は、例えば非晶質を有してもよい。なお、非晶質を有する酸化物半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質酸化物半導体膜は、例えば、完全な非晶質であり、結晶部を有さない。

## 【0058】

なお、酸化物半導体膜が、CAAC-OS、微結晶酸化物半導体、非晶質酸化物半導体の混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、を有する。また、混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、の積層構造を有してもよい。10

## 【0059】

なお、酸化物半導体膜は、例えば、単結晶を有してもよい。

## 【0060】

酸化物半導体膜は、複数の結晶部を有し、当該結晶部のc軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っていることが好ましい。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。そのような酸化物半導体膜の一例としては、CAAC-OS膜がある。

## 【0061】

CAAC-OS膜に含まれる結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる結晶部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には明確な粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。20

## 【0062】

CAAC-OS膜に含まれる結晶部は、例えば、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつa b面に垂直な方向から見て金属原子が三角形状または六角形状に配列し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80°以上100°以下、好ましくは85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-10°以上10°以下、好ましくは-5°以上5°以下の範囲も含まれることとする。30

## 【0063】

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部の結晶性が低下することもある。40

## 【0064】

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃うため、CAAC-OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。また、結晶部は、成膜したとき、または成膜後に加熱処理などの結晶化処理を行ったときに形成される。従って、結晶部のc軸は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃う。

## 【0065】

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。50

## 【0066】

酸化物半導体膜は、シリコン膜と比べて1~2 eV程度バンドギャップが大きい。そのため、酸化物半導体膜を用いたトランジスタは、衝突イオン化が起こりにくく、アバランシェブレークダウンが起こりにくい。即ち、当該トランジスタは、ホットキャリア劣化が起こりにくいといえる。

## 【0067】

また、以上のように半導体膜106として酸化物半導体膜を用いた場合、酸化物半導体膜はキャリアの生成が少ないため、半導体膜106の厚さが厚い場合（例えば、15 nm以上100 nm未満）でも、ゲート電極104の電界によってチャネル領域を完全空乏化させることができる。従って、酸化物半導体膜を用いたトランジスタは、パンチスルーフ現象によるオフ電流の増大およびしきい値電圧の変動が起こらない。例えば、チャネル長が3 μmのとき、チャネル幅1 μmあたりのオフ電流を、室温において $10^{-21}$  A未満、または $10^{-24}$  A未満とすることができます。

10

## 【0068】

キャリア生成源の一つである、酸化物半導体膜中の酸素欠損は、電子スピン共鳴（ESR：Electron Spin Resonance）によって評価できる。即ち、酸素欠損の少ない酸化物半導体膜は、ESRによって、酸素欠損に起因する信号を有さない酸化物半導体膜と言い換えることができる。具体的には、酸素欠損に起因するスピン密度が、 $5 \times 10^{16}$  spins/cm<sup>3</sup>未満の酸化物半導体膜である。なお、酸化物半導体膜が酸素欠損を有すると、ESRにてg値が1.93近傍に対称性を有する信号が現れる。

20

## 【0069】

ここで、基板100に大きな制限はないが、少なくとも、後の熱処理に耐え得る程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI（Silicon On Insulator）基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

## 【0070】

また、基板100として、第5世代（1000 mm × 1200 mmまたは1300 mm × 1500 mm）、第6世代（1500 mm × 1800 mm）、第7世代（1870 mm × 2200 mm）、第8世代（2200 mm × 2500 mm）、第9世代（2400 mm × 2800 mm）、第10世代（2880 mm × 3130 mm）などの大型ガラス基板を用いる場合、半導体装置の作製工程における加熱処理などで生じる基板100の縮みによって、微細な加工が困難になる場合ある。そのため、前述したような大型ガラス基板を基板100として用いる場合、加熱処理による縮みの小さいものを用いることが好ましい。例えば、基板100として、400、好ましくは450、さらに好ましくは500の温度で1時間加熱処理を行った後の縮み量が10 ppm以下、好ましくは5 ppm以下、さらに好ましくは3 ppm以下である大型ガラス基板を用いればよい。

30

## 【0071】

また、基板100として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。

40

## 【0072】

ゲート電極104は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびWを一種以上含む、単体、窒化物、酸化物または合金を、単層で、または積層で用いればよい。

## 【0073】

ソース電極116aおよびドレイン電極116bは、Al、Ti、Cr、Co、Ni、C

50

u、Y、Zr、Mo、Ag、TaおよびWを一種以上含む、単体、窒化物、酸化物または合金を、単層で、または積層で用いればよい。なお、ソース電極116aとドレイン電極116bの導電膜は同一であってもよいし、異なっていてもよい。

【0074】

保護絶縁膜118は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルから一種以上を含む絶縁膜を、単層で、または積層で用いればよい。

【0075】

酸化窒化シリコンは、その組成において、窒素よりも酸素の含有量が多いものを示し、また、窒化酸化シリコンは、その組成において、酸素よりも窒素の含有量が多いものを示す。

10

【0076】

保護絶縁膜118は、過剰酸素を含む絶縁膜であると好ましい。

【0077】

保護絶縁膜118が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

【0078】

過剰酸素を含む絶縁膜とは、TDS (Thermal Desorption Spectroscopy : 昇温脱離ガス分光法) 分析にて放出される酸素が酸素原子に換算して  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以上、 $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以上または  $1 \times 10^{20}$  atoms / cm<sup>3</sup> 以上である絶縁膜をいう。

20

【0079】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

【0080】

TDS分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そしてこの積分値と標準試料との比較により、気体の全放出量を計算することができる。

【0081】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量 ( $N_{O_2}$ ) は、数式(1)で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH<sub>3</sub>OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

30

【0082】

【数1】

$$N_{O_2} = \frac{N_{H_2}}{S_{H_2}} \times S_{O_2} \times \alpha \quad (1)$$

40

【0083】

$N_{H_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$ は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$ とする。 $S_{O_2}$ は、絶縁膜をTDS分析したときのイオン強度の積分値である。は、TDS分析におけるイオン強度に影響する係数である。数式(1)の詳細に関しては、特開平6-275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として  $1 \times 10^{16}$  atoms / cm<sup>2</sup> の水素原子を含むシリコンウェハを用いて測定した。

50

## 【0084】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

## 【0085】

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

## 【0086】

または、過剰酸素を含む絶縁膜は、過酸化ラジカルを含む絶縁膜であってもよい。具体的には、過酸化ラジカルに起因するスピン密度が、 $5 \times 10^{17} \text{ spins/cm}^3$  以上の絶縁膜である。なお、過酸化ラジカルを含む絶縁膜は、ESRにて、g値が2.01近傍に非対称の信号を有する絶縁膜である。

## 【0087】

または、過剰酸素を含む絶縁膜は、酸素が過剰な酸化シリコン( $SiO_x (X > 2)$ )であってもよい。酸素が過剰な酸化シリコン( $SiO_x (X > 2)$ )は、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、RBSにより測定した値である。

## 【0088】

ゲート絶縁膜112は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルから一種以上を含む絶縁膜を、単層で、または積層で用いればよい。

## 【0089】

ゲート絶縁膜112は、過剰酸素を含む絶縁膜であると好ましい。

## 【0090】

ゲート絶縁膜112が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0091】

図1に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜134および酸化アルミニウム膜138に囲まれた構造を有する。従って、トランジスタの外部からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

## 【0092】

従って、図1に示すトランジスタは、安定した電気特性を有する。

## 【0093】

なお、図1では、結晶性絶縁膜132および酸化アルミニウム膜134、ならびに結晶性絶縁膜136および酸化アルミニウム膜138の全てを有する構造を示したが、これに限定されない。例えば、結晶性絶縁膜132および酸化アルミニウム膜134が設けられなくても構わない。または、結晶性絶縁膜136および酸化アルミニウム膜138が設けられなくても構わない。

## 【0094】

次に、図1とは異なる構造のトランジスタについて、図2を用いて説明する。

## 【0095】

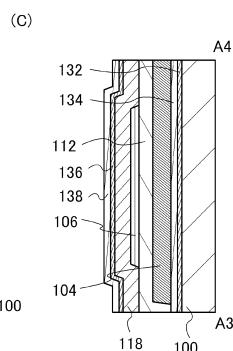

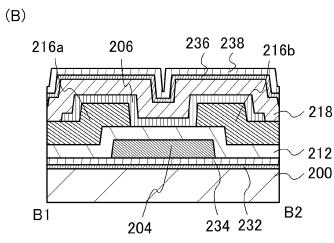

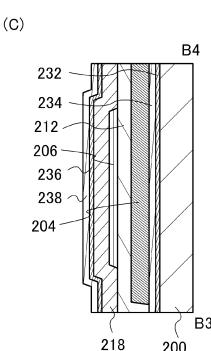

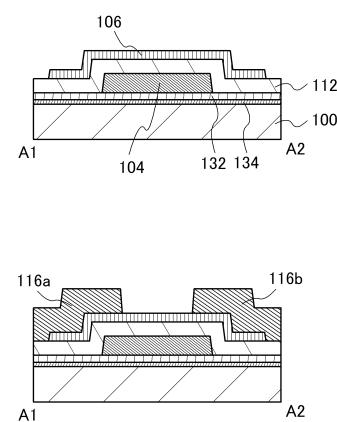

図2(A)は本発明の一態様に係るトランジスタの上面図である。図2(A)に示す一点鎖線B1-B2に対応する断面図を図2(B)に示す。また、図2(A)に示す一点鎖線B3-B4に対応する断面図を図2(C)に示す。なお、簡単のため、図2(A)においては、ゲート絶縁膜212などを省略して示す。

## 【0096】

図2(B)は、基板200上に設けられた結晶性絶縁膜232と、結晶性絶縁膜232上

10

20

30

40

50

に設けられた酸化アルミニウム膜 234 と、酸化アルミニウム膜 234 上に設けられたゲート電極 204 と、ゲート電極 204 上に設けられたゲート絶縁膜 212 と、ゲート絶縁膜 212 上に設けられたソース電極 216a およびドレイン電極 216b と、ゲート絶縁膜 212、ソース電極 216a およびドレイン電極 216b 上にあり、ゲート電極 204 と重畠して設けられた半導体膜 206 と、半導体膜 206、ソース電極 216a およびドレイン電極 216b 上に設けられた結晶性絶縁膜 236 と、結晶性絶縁膜 236 上に設けられた酸化アルミニウム膜 238 と、を有するトランジスタの断面図である。

【0097】

ここで、結晶性絶縁膜 232 および結晶性絶縁膜 236 は、結晶性絶縁膜 132 および結晶性絶縁膜 136 として示した絶縁膜から選択して用いればよい。

10

【0098】

結晶性絶縁膜 232 および結晶性絶縁膜 236 は、結晶性を有する絶縁膜である。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【0099】

酸化アルミニウム膜 234 および酸化アルミニウム膜 238 は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

【0100】

酸化アルミニウム膜 234 は、結晶性絶縁膜 232 との界面近傍においても結晶性を有する。また、酸化アルミニウム膜 238 は、結晶性絶縁膜 236 との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。

20

【0101】

酸化アルミニウム膜 234 および酸化アルミニウム膜 238 は、高密度の酸化アルミニウム膜である。具体的には、XRR または RBS によって密度が  $3.2 \text{ g/cm}^3$  以上  $4.1 \text{ g/cm}^3$  以下の酸化アルミニウム膜である。酸化アルミニウム膜 234 および酸化アルミニウム膜 238 は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0102】

なお、酸化アルミニウム膜 234 は、結晶性絶縁膜 232 の近傍に低密度層を有さない。また、酸化アルミニウム膜 238 は、結晶性絶縁膜 236 の近傍に低密度層を有さない。具体的には、XRR によって密度が  $3.2 \text{ g/cm}^3$  未満の層を有さない。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

30

【0103】

半導体膜 206 は、半導体膜 106 の記載を参照する。

【0104】

基板 200 は、基板 100 の記載を参照する。

40

【0105】

ゲート電極 204 は、ゲート電極 104 の記載を参照する。

【0106】

ソース電極 216a およびドレイン電極 216b は、ソース電極 116a およびドレイン電極 116b の記載を参照する。

【0107】

保護絶縁膜 218 は、保護絶縁膜 118 の記載を参照する。

【0108】

保護絶縁膜 218 は、過剰酸素を含む絶縁膜であると好ましい。

【0109】

50

保護絶縁膜 218 が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0110】

ゲート絶縁膜 212 は、ゲート絶縁膜 112 の記載を参照する。

## 【0111】

ゲート絶縁膜 212 は、過剰酸素を含む絶縁膜であると好ましい。

## 【0112】

ゲート絶縁膜 212 が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0113】

図2に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜 234 および酸化アルミニウム膜 238 に囲まれた構造を有する。従って、トランジスタの外部からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

10

## 【0114】

従って、図2に示すトランジスタは、安定した電気特性を有する。

## 【0115】

なお、図2では、結晶性絶縁膜 232 および酸化アルミニウム膜 234、ならびに結晶性絶縁膜 236 および酸化アルミニウム膜 238 の全てを有する構造を示したが、これに限定されない。例えば、結晶性絶縁膜 232 および酸化アルミニウム膜 234 が設けられなくても構わない。または、結晶性絶縁膜 236 および酸化アルミニウム膜 238 が設けられなくても構わない。

20

## 【0116】

次に、図1および図2とは異なる構造のトランジスタについて、図3を用いて説明する。

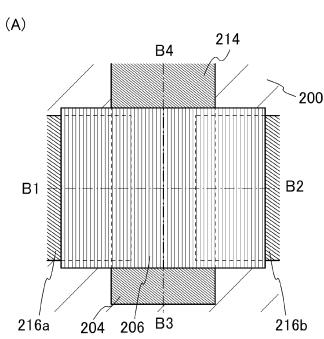

## 【0117】

図3(A)は本発明の一態様に係るトランジスタの上面図である。図3(A)に示す一点鎖線 C1-C2 に対応する断面図を図3(B)に示す。また、図3(A)に示す一点鎖線 C3-C4 に対応する断面図を図3(C)に示す。なお、簡単のため、図3(A)においては、ゲート絶縁膜 312などを省略して示す。

30

## 【0118】

図3(B)は、基板 300 上に設けられた結晶性絶縁膜 332 と、結晶性絶縁膜 332 上に設けられた酸化アルミニウム膜 334 と、酸化アルミニウム膜 334 上に設けられた下地絶縁膜 302 と、下地絶縁膜 302 上に設けられた半導体膜 306 と、半導体膜 306 上に設けられたソース電極 316a およびドレイン電極 316b と、半導体膜 306、ソース電極 316a およびドレイン電極 316b 上に設けられたゲート絶縁膜 312 と、ゲート絶縁膜 312 上にあり、半導体膜 306 と重畠して設けられたゲート電極 304 と、ゲート電極 304 上に設けられた結晶性絶縁膜 336 と、結晶性絶縁膜 336 上に設けられた酸化アルミニウム膜 338 と、を有するトランジスタの断面図である。

## 【0119】

ここで、結晶性絶縁膜 332 および結晶性絶縁膜 336 は、結晶性絶縁膜 132 および結晶性絶縁膜 136 として示した絶縁膜から選択して用いればよい。

40

## 【0120】

結晶性絶縁膜 332 および結晶性絶縁膜 336 は、結晶性を有する絶縁膜である。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

## 【0121】

酸化アルミニウム膜 334 および酸化アルミニウム膜 338 は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

## 【0122】

酸化アルミニウム膜 334 は、結晶性絶縁膜 332 との界面近傍においても結晶性を有する。また、酸化アルミニウム膜 338 は、結晶性絶縁膜 336 との界面近傍においても結

50

晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。

【0123】

酸化アルミニウム膜334および酸化アルミニウム膜338は、高密度の酸化アルミニウム膜である。具体的には、XRRまたはRBSによって密度が3.2 g/cm<sup>3</sup>以上4.1 g/cm<sup>3</sup>以下の酸化アルミニウム膜である。酸化アルミニウム膜334および酸化アルミニウム膜338は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0124】

なお、酸化アルミニウム膜334は、結晶性絶縁膜332の近傍に低密度層を有さない。また、酸化アルミニウム膜338は、結晶性絶縁膜336の近傍に低密度層を有さない。具体的には、XRRによって密度が3.2 g/cm<sup>3</sup>未満の層を有さない。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッティングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

【0125】

半導体膜306は、半導体膜106の記載を参照する。

【0126】

基板300は、基板100の記載を参照する。

【0127】

下地絶縁膜302は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルから一種以上を含む絶縁膜を、単層で、または積層で用いればよい。

【0128】

下地絶縁膜302は、過剰酸素を含む絶縁膜であると好ましい。

【0129】

下地絶縁膜302が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

【0130】

ゲート絶縁膜312は、ゲート絶縁膜112の記載を参照する。

【0131】

ゲート絶縁膜312は、過剰酸素を含む絶縁膜であると好ましい。

【0132】

ゲート絶縁膜312が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

【0133】

ソース電極316aおよびドレイン電極316bは、ソース電極116aおよびドレイン電極116bの記載を参照する。

【0134】

ゲート電極304は、ゲート電極104の記載を参照する。

【0135】

図3に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜334および酸化アルミニウム膜338に囲まれた構造を有する。従って、トランジスタの外部からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

【0136】

従って、図3に示すトランジスタは、安定した電気特性を有する。

10

20

30

40

50

## 【0137】

なお、図3では、結晶性絶縁膜332および酸化アルミニウム膜334、ならびに結晶性絶縁膜336および酸化アルミニウム膜338の全てを有する構造を示したが、これに限定されない。例えば、結晶性絶縁膜332および酸化アルミニウム膜334が設けられなくて構わない。または、結晶性絶縁膜336および酸化アルミニウム膜338が設けられなくて構わない。

## 【0138】

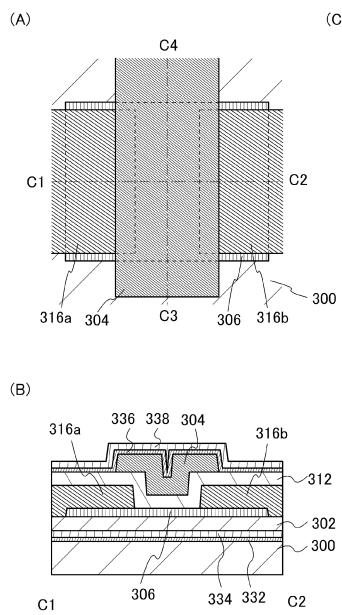

次に、図1乃至図3とは異なる構造のトランジスタについて、図4を用いて説明する。

## 【0139】

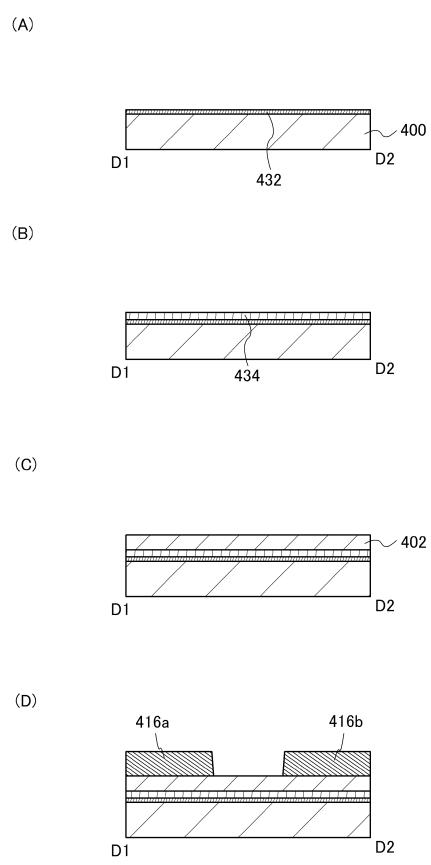

図4(A)は本発明の一態様に係るトランジスタの上面図である。図4(A)に示す一点鎖線D1-D2に対応する断面図を図4(B)に示す。また、図4(A)に示す一点鎖線D3-D4に対応する断面図を図4(C)に示す。なお、簡単のため、図4(A)においては、ゲート絶縁膜412などを省略して示す。

10

## 【0140】

図4(B)は、基板400上に設けられた結晶性絶縁膜432と、結晶性絶縁膜432上に設けられた酸化アルミニウム膜434と、酸化アルミニウム膜434上に設けられた下地絶縁膜402と、下地絶縁膜402上に設けられたソース電極416aおよびドレイン電極416bと、下地絶縁膜402、ソース電極416aおよびドレイン電極416b上に設けられた半導体膜406と、半導体膜406上に設けられたゲート絶縁膜412と、ゲート絶縁膜412上にあり、半導体膜406と重畠して設けられたゲート電極404と、ゲート電極404上に設けられた結晶性絶縁膜436と、結晶性絶縁膜436上に設けられた酸化アルミニウム膜438と、を有するトランジスタの断面図である。なお、ゲート絶縁膜412は、結晶性絶縁膜412a、および結晶性絶縁膜412a上に設けられた酸化アルミニウム膜412bを有する。

20

## 【0141】

ここで、結晶性絶縁膜432および結晶性絶縁膜436は、結晶性絶縁膜132および結晶性絶縁膜136として示した絶縁膜から選択して用いればよい。

## 【0142】

結晶性絶縁膜432および結晶性絶縁膜436は、結晶性を有する絶縁膜である。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

30

## 【0143】

酸化アルミニウム膜434および酸化アルミニウム膜438は、結晶性を有する。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる。

## 【0144】

酸化アルミニウム膜434は、結晶性絶縁膜432との界面近傍においても結晶性を有する。また、酸化アルミニウム膜438は、結晶性絶縁膜436との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。

## 【0145】

酸化アルミニウム膜434および酸化アルミニウム膜438は、高密度の酸化アルミニウム膜である。具体的には、XRRまたはRBSによって密度が $3.2\text{ g/cm}^3$ 以上 $4.1\text{ g/cm}^3$ 以下の酸化アルミニウム膜である。酸化アルミニウム膜434および酸化アルミニウム膜438は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

40

## 【0146】

なお、酸化アルミニウム膜434は、結晶性絶縁膜432の近傍に低密度層を有さない。また、酸化アルミニウム膜438は、結晶性絶縁膜436の近傍に低密度層を有さない。具体的には、XRRによって密度が $3.2\text{ g/cm}^3$ 未満の層を有さない。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対

50

する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッティングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

## 【0147】

半導体膜406は、半導体膜106の記載を参照する。

## 【0148】

基板400は、基板100の記載を参照する。

## 【0149】

下地絶縁膜402は、下地絶縁膜302の記載を参照する。

## 【0150】

下地絶縁膜402は、過剰酸素を含む絶縁膜であると好ましい。

10

## 【0151】

下地絶縁膜402が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0152】

ゲート絶縁膜412は、ゲート絶縁膜112の記載を参照する。

## 【0153】

ゲート絶縁膜412は、過剰酸素を含む絶縁膜であると好ましい。

## 【0154】

ゲート絶縁膜412が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

20

## 【0155】

ソース電極416aおよびドレイン電極416bは、ソース電極116aおよびドレイン電極116bの記載を参照する。

## 【0156】

ゲート電極404は、ゲート電極104の記載を参照する。

## 【0157】

図4に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜434および酸化アルミニウム膜438に囲まれた構造を有する。従って、トランジスタの外部からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

30

## 【0158】

従って、図4に示すトランジスタは、安定した電気特性を有する。

## 【0159】

なお、図4では、結晶性絶縁膜432および酸化アルミニウム膜434、ならびに結晶性絶縁膜436および酸化アルミニウム膜438の全てを有する構造を示したが、これに限定されない。例えば、結晶性絶縁膜432および酸化アルミニウム膜434が設けられなくて構わない。または、結晶性絶縁膜436および酸化アルミニウム膜438が設けられなくて構わない。

40

## 【0160】

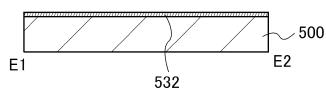

次に、図1乃至図4とは異なる構造のトランジスタについて、図5を用いて説明する。

## 【0161】

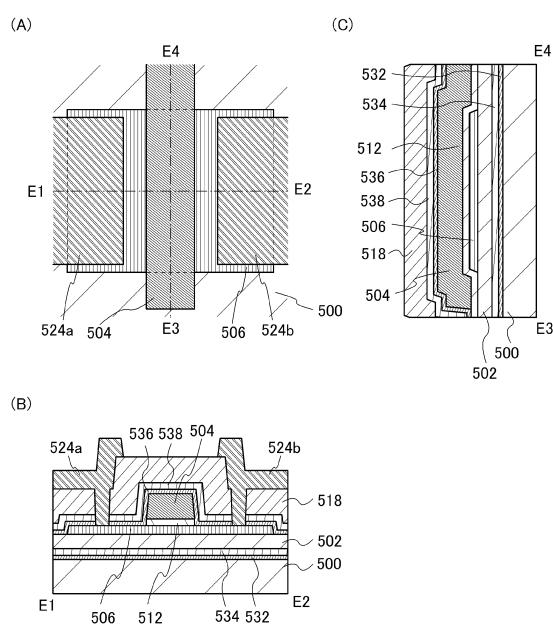

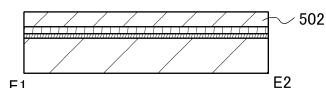

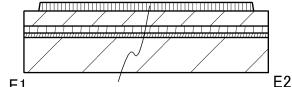

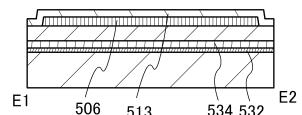

図5(A)は本発明の一態様に係るトランジスタの上面図である。図5(A)に示す一点鎖線E1-E2に対応する断面図を図5(B)に示す。また、図5(A)に示す一点鎖線E3-E4に対応する断面図を図5(C)に示す。なお、簡単のため、図5(A)においては、ゲート絶縁膜512などを省略して示す。

## 【0162】

図5(B)は、基板500上に設けられた結晶性絶縁膜532と、結晶性絶縁膜532上に設けられた酸化アルミニウム膜534と、酸化アルミニウム膜534上に設けられた下地絶縁膜502と、下地絶縁膜502上に設けられた半導体膜506と、半導体膜506

50

上に設けられたゲート絶縁膜 512 と、ゲート絶縁膜 512 上にあり、半導体膜 506 と重畠して設けられたゲート電極 504 と、半導体膜 506 およびゲート電極 504 上に設けられた結晶性絶縁膜 536 と、結晶性絶縁膜 536 上に設けられた酸化アルミニウム膜 538 と、を有するトランジスタの断面図である。

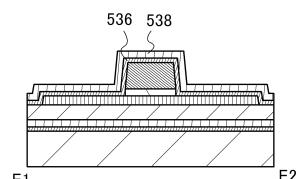

【0163】

図 5 (B) に示す断面図では、酸化アルミニウム膜 538 上に保護絶縁膜 518 が設けられる。なお、結晶性絶縁膜 536、酸化アルミニウム膜 538 および保護絶縁膜 518 は、半導体膜 506 に達する開口部を有し、当該開口部を介して、保護絶縁膜 518 上に設けられた配線 524a および配線 524b は半導体膜 506 と接する。

【0164】

なお、図 5 (B) では、ゲート絶縁膜 512 がゲート電極 504 と重畠する領域のみに設けられているが、これに限定されない。例えば、ゲート絶縁膜 512 が半導体膜 506 を覆うように設けられていてもよい。また、ゲート電極 504 の側壁に接して側壁絶縁膜を有しても構わない。

【0165】

また、側壁絶縁膜を設ける場合、半導体膜 506 の側壁絶縁膜と重畠する領域は、ゲート電極 504 と重畠する領域よりも低抵抗であると好ましい。例えば、半導体膜 506 のゲート電極 504 と重畠しない領域は、半導体膜 506 を低抵抗化する不純物を有する領域であってもよい。また、欠陥によって低抵抗化された領域であってもよい。半導体膜 506 の側壁絶縁膜と重畠する領域が、ゲート電極 504 と重畠する領域よりも低抵抗であることにより、当該領域は LDD (Lightly Doped Drain) 領域として機能する。トランジスタが、LDD 領域を有することによって、DIBL (Drain Induced Barrier Lowering) およびホットキャリア劣化を抑制することができる。ただし、半導体膜 506 の側壁絶縁膜と重畠する領域をオフセット領域としても構わない。トランジスタが、オフセット領域を有することでも、DIBL およびホットキャリア劣化を抑制することができる。

【0166】

ここで、結晶性絶縁膜 532 および結晶性絶縁膜 536 は、結晶性絶縁膜 132 および結晶性絶縁膜 136 として示した絶縁膜から選択して用いればよい。

【0167】

結晶性絶縁膜 532 および結晶性絶縁膜 536 は、結晶性を有する絶縁膜である。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【0168】

酸化アルミニウム膜 534 および酸化アルミニウム膜 538 は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

【0169】

酸化アルミニウム膜 534 は、結晶性絶縁膜 532 との界面近傍においても結晶性を有する。また、酸化アルミニウム膜 538 は、結晶性絶縁膜 536 との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。

【0170】

酸化アルミニウム膜 534 および酸化アルミニウム膜 538 は、高密度の酸化アルミニウム膜である。具体的には、XRR または RBS によって密度が  $3.2 \text{ g/cm}^3$  以上  $4.1 \text{ g/cm}^3$  以下の酸化アルミニウム膜である。酸化アルミニウム膜 534 および酸化アルミニウム膜 538 は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0171】

なお、酸化アルミニウム膜 534 は、結晶性絶縁膜 532 の近傍に低密度層を有さない。また、酸化アルミニウム膜 538 は、結晶性絶縁膜 536 の近傍に低密度層を有さない。具体的には、XRR によって密度が  $3.2 \text{ g/cm}^3$  未満の層を有さない。対して、下地

10

20

30

40

50

として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

## 【0172】

半導体膜506は、半導体膜106の記載を参照する。

## 【0173】

半導体膜506のゲート電極504と重畳しない領域は、ゲート電極504と重畳する領域よりも低抵抗であると好ましい。例えば、半導体膜506のゲート電極504と重畳しない領域は、半導体膜506を低抵抗化する不純物を有する領域であってもよい。また、欠陥によって低抵抗化された領域であってもよい。半導体膜506のゲート電極504と重畳しない領域がゲート電極504と重畳する領域よりも低抵抗であることにより、トランジスタのソース領域およびドレイン領域として機能することができる。

10

## 【0174】

基板500は、基板100の記載を参照する。

## 【0175】

下地絶縁膜502は、下地絶縁膜302の記載を参照する。

## 【0176】

下地絶縁膜502は、過剰酸素を含む絶縁膜であると好ましい。

20

## 【0177】

下地絶縁膜502が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0178】

ゲート絶縁膜512は、ゲート絶縁膜112の記載を参照する。

## 【0179】

ゲート絶縁膜512は、過剰酸素を含む絶縁膜であると好ましい。

## 【0180】

ゲート絶縁膜512が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

30

## 【0181】

ゲート電極504は、ゲート電極104の記載を参照する。

## 【0182】

保護絶縁膜518は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルから一種以上を含む絶縁膜を、単層で、または積層で用いればよい。

## 【0183】

配線524aおよび配線524bは、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびWを一種以上含む、単体、窒化物、酸化物または合金を、単層で、または積層で用いればよい。なお、配線524aおよび配線524bは同一であってもよいし、異なっていてもよい。

40

## 【0184】

図5に示すトランジスタは、ゲート電極504と他の配線および電極との重畳する領域が小さいため、寄生容量が発生しにくく、トランジスタのスイッチング特性を高めることができる。また、トランジスタのチャネル長がゲート電極504の幅で決定されるため、チャネル長の小さい、微細なトランジスタを作製しやすい構造である。

## 【0185】

また、図5に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜534および酸化アルミニウム膜538に囲まれた構造を有する。従って、トランジスタの外部

50

からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

【0186】

従って、図5に示すトランジスタは、安定した電気特性を有する。

【0187】

なお、図5では、結晶性絶縁膜532および酸化アルミニウム膜534、ならびに結晶性絶縁膜536および酸化アルミニウム膜538の全てを有する構造を示したが、これに限定されない。例えば、結晶性絶縁膜532および酸化アルミニウム膜534が設けられなくて構わない。または、結晶性絶縁膜536および酸化アルミニウム膜538が設けられなくて構わない。

10

【0188】

次に、図1乃至図5とは異なる構造のトランジスタについて、図6を用いて説明する。

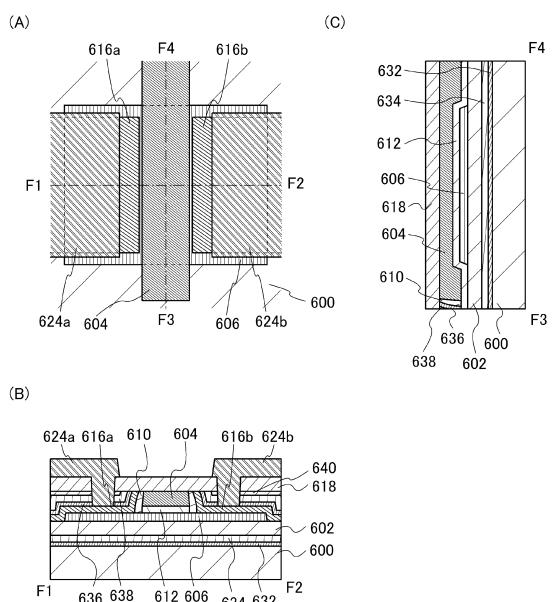

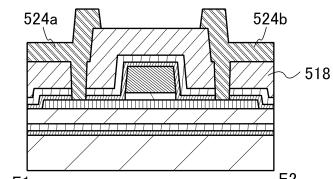

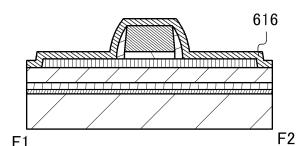

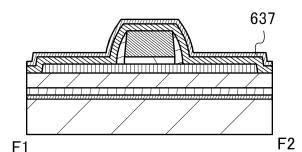

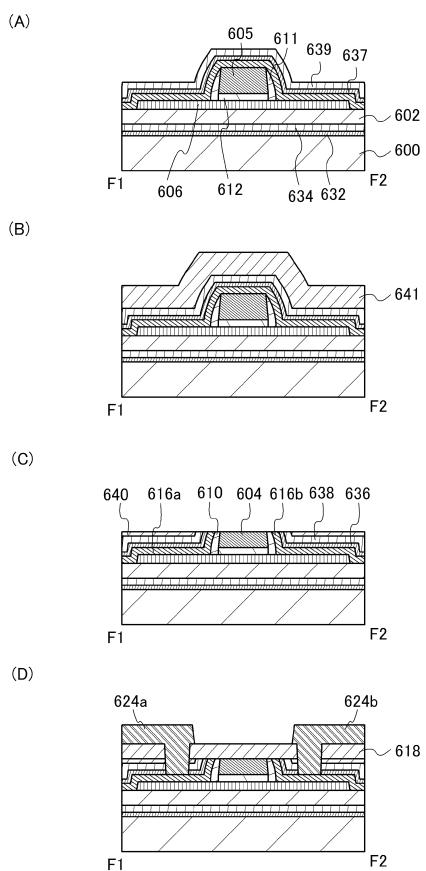

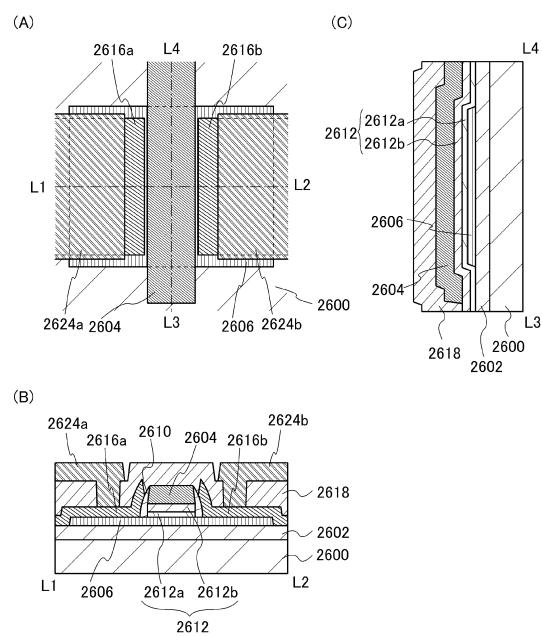

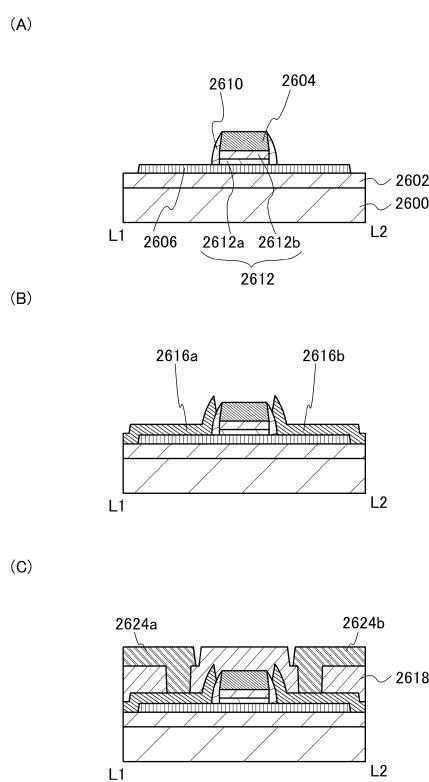

【0189】

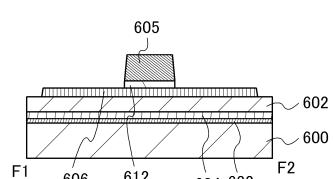

図6(A)は本発明の一態様に係るトランジスタの上面図である。図6(A)に示す一点鎖線F1-F2に対応する断面図を図6(B)に示す。また、図6(A)に示す一点鎖線F3-F4に対応する断面図を図6(C)に示す。なお、簡単のため、図6(A)においては、ゲート絶縁膜612などを省略して示す。

【0190】

図6(B)は、基板600上に設けられた結晶性絶縁膜632と、結晶性絶縁膜632上に設けられた酸化アルミニウム膜634と、酸化アルミニウム膜634上に設けられた下地絶縁膜602と、下地絶縁膜602上に設けられた半導体膜606と、半導体膜606上に設けられたゲート絶縁膜612と、ゲート絶縁膜612上に設けられたゲート電極604と、ゲート電極604の側面と接して設けられた側壁絶縁膜610と、半導体膜606および側壁絶縁膜610上に設けられたソース電極616aおよびドレイン電極616bと、半導体膜606、ソース電極616aおよびドレイン電極616b上に設けられた結晶性絶縁膜636と、結晶性絶縁膜636上に設けられた酸化アルミニウム膜638と、酸化アルミニウム膜638上に設けられた絶縁膜640と、を有するトランジスタの断面図である。

20

【0191】

図6(B)に示す断面図では、ゲート電極604、側壁絶縁膜610、ソース電極616aおよびドレイン電極616b、結晶性絶縁膜636、酸化アルミニウム膜638、絶縁膜640上に保護絶縁膜618が設けられる。なお、結晶性絶縁膜636、酸化アルミニウム膜638、絶縁膜640および保護絶縁膜618は、ソース電極616aおよびドレイン電極616bに達する開口部をそれぞれ有し、当該開口部を介して、保護絶縁膜618上に設けられた配線624aおよび配線624bは、ソース電極616aおよびドレイン電極616bとそれぞれ接する。

30

【0192】

なお、図6(B)では、側壁絶縁膜610の一部が、ゲート絶縁膜612の側面に設けられているが、これに限定されない。例えば、ゲート絶縁膜612上に側壁絶縁膜610が設けられていてもよい。

40

【0193】

なお、図6(B)では、ゲート電極604、側壁絶縁膜610、ソース電極616a、ドレイン電極616b、結晶性絶縁膜636、酸化アルミニウム膜638および絶縁膜640の形成する表面の高さが揃っている。

【0194】

ここで、結晶性絶縁膜632および結晶性絶縁膜636は、結晶性絶縁膜132および結晶性絶縁膜136として示した絶縁膜から選択して用いればよい。

【0195】

結晶性絶縁膜632および結晶性絶縁膜636は、結晶性を有する絶縁膜である。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

50

## 【0196】

酸化アルミニウム膜634および酸化アルミニウム膜638は、結晶性を有する。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる。

## 【0197】

酸化アルミニウム膜634は、結晶性絶縁膜632との界面近傍においても結晶性を有する。また、酸化アルミニウム膜638は、結晶性絶縁膜636との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。

## 【0198】

酸化アルミニウム膜634および酸化アルミニウム膜638は、高密度の酸化アルミニウム膜である。具体的には、XRRまたはRBSによって密度が $3.2 \text{ g/cm}^3$ 以上 $4.1 \text{ g/cm}^3$ 以下の酸化アルミニウム膜である。酸化アルミニウム膜634および酸化アルミニウム膜638は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。10

## 【0199】

なお、酸化アルミニウム膜634は、結晶性絶縁膜632の近傍に低密度層を有さない。また、酸化アルミニウム膜638は、結晶性絶縁膜636の近傍に低密度層を有さない。具体的には、XRRによって密度が $3.2 \text{ g/cm}^3$ 未満の層を有さない。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッティングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。20

## 【0200】

半導体膜606は、半導体膜106の記載を参照する。

## 【0201】

半導体膜606のゲート電極604と重畠しない領域は、ゲート電極604と重畠する領域よりも低抵抗であると好ましい。例えば、半導体膜606のゲート電極604と重畠しない領域は、半導体膜606を低抵抗化する不純物を有する領域であってもよい。また、欠陥によって低抵抗化された領域であってもよい。半導体膜606のゲート電極604と重畠しない領域がゲート電極604と重畠する領域よりも低抵抗であることにより、トランジスタのソース領域およびドレイン領域として機能することができる。ただし、図6(B)に示すトランジスタはソース電極616aおよびドレイン電極616bを有するため、ソース領域およびドレイン領域を特に設けなくても構わない。30

## 【0202】

また、半導体膜606の側壁絶縁膜610と重畠する領域は、ソース電極616aおよびドレイン電極616bと重畠する領域よりも高抵抗、かつゲート電極604と重畠する領域よりも低抵抗であると好ましい。例えば、半導体膜606のゲート電極604と重畠しない領域は、半導体膜606を低抵抗化する不純物を有する領域であってもよい。また、欠陥によって低抵抗化された領域であってもよい。半導体膜606の側壁絶縁膜610と重畠する領域が、ソース電極616aおよびドレイン電極616bよりも高抵抗、かつゲート電極604と重畠する領域よりも低抵抗であることにより、当該領域はLDD領域として機能する。トランジスタが、LDD領域を有することによって、DIBLおよびホットキャリア劣化を抑制することができる。ただし、半導体膜606の側壁絶縁膜610と重畠する領域をオフセット領域としても構わない。トランジスタが、オフセット領域を有することでも、DIBLおよびホットキャリア劣化を抑制することができる。40

## 【0203】

基板600は、基板100の記載を参照する。

## 【0204】

下地絶縁膜602は、下地絶縁膜302の記載を参照する。50

## 【0205】

下地絶縁膜602は、過剰酸素を含む絶縁膜であると好ましい。

## 【0206】

下地絶縁膜602が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0207】

ゲート絶縁膜612は、ゲート絶縁膜112の記載を参照する。

## 【0208】

ゲート絶縁膜612は、過剰酸素を含む絶縁膜であると好ましい。

## 【0209】

ゲート絶縁膜612が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

10

## 【0210】

ゲート電極604は、ゲート電極104の記載を参照する。

## 【0211】

側壁絶縁膜610は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルから一種以上を含む絶縁膜を、単層で、または積層で用いればよい。

20

## 【0212】

なお、側壁絶縁膜610として、結晶性絶縁膜、および結晶性絶縁膜上の酸化アルミニウム膜を用いると好ましい。このようにすることで、側壁絶縁膜610の形状不良が起こりにくくできる。

## 【0213】

ソース電極616aおよびドレイン電極616bは、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびWを一種以上含む、単体、窒化物、酸化物または合金を、単層で、または積層で用いればよい。なお、ソース電極616aおよびドレイン電極616bは同一であってもよいし、異なっていてもよい。

## 【0214】

保護絶縁膜618は、保護絶縁膜518の記載を参照する。

30

## 【0215】

配線624aおよび配線624bは、配線524aおよび配線524bの記載を参照する。

## 【0216】

図6に示すトランジスタは、ゲート電極604と他の配線および電極との重畳する領域が小さいため、寄生容量が発生しにくく、トランジスタのスイッチング特性を高めることができる。また、ソース電極616aおよびドレイン電極616bが設けられることにより、図5に示したトランジスタよりも寄生抵抗が小さくでき、オン電流を増大させることができる。また、トランジスタのチャネル長がゲート電極604の幅で決定されるため、チャネル長の小さい、微細なトランジスタを作製しやすい構造である。

40

## 【0217】

また、図6に示すトランジスタは、結晶性を有し、密度の高い酸化アルミニウム膜634および酸化アルミニウム膜638に囲まれた構造を有する。従って、トランジスタの外部からの不純物に対して高いバリア性を有する。また、当該酸化アルミニウム膜は、酸素不透過であるため、トランジスタ内部に含まれる過剰酸素の外方拡散を抑制できる。

## 【0218】

従って、図6に示すトランジスタは、安定した電気特性を有する。

## 【0219】

なお、図6では、結晶性絶縁膜632および酸化アルミニウム膜634、ならびに結晶性絶縁膜636および酸化アルミニウム膜638の全てを有する構造を示したが、これに限

50

定されない。例えば、結晶性絶縁膜 632 および酸化アルミニウム膜 634 が設けられなくて構わない。または、結晶性絶縁膜 636 および酸化アルミニウム膜 638 が設けられなくても構わない。

【0220】

本実施の形態より、ゲート絶縁膜が不純物に対して高いバリア性を有し、かつ含まれる欠陥が少ないため、安定した電気特性を有し、信頼性が高いトランジスタを提供することができる。

【0221】

本実施の形態は、基本原理の一例について述べたものである。したがって、本実施の形態の一部または全部について、他の実施の形態の一部または全部と、自由に組み合わせることや、適用することや、置き換えて実施することができる。

10

【0222】

(実施の形態 2)

本実施の形態では、実施の形態 1 で示したトランジスタの作製方法について説明する。

【0223】

まずは、図 1 に示すトランジスタの作製方法について、図 7 および図 8 を用いて説明する。なお、簡単のため、図 7 および図 8 には、図 1 (B) に対応する断面図のみ示す。

【0224】

まず、基板 100 を準備する。基板 100 は、基板 100 として示した基板から選択して用いればよい。

20

【0225】

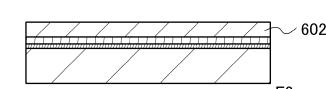

次に、結晶性絶縁膜 132 を成膜する (図 7 (A) 参照。)。結晶性絶縁膜 132 は、結晶性絶縁膜 132 として示した絶縁膜から選択し、スパッタリング法、化学気相成長 (CVD: Chemical Vapor Deposition) 法、分子線エピタキシー (MBE: Molecular Beam Epitaxy) 法、原子層堆積 (ALD: Atomic Layer Deposition) 法またはパルスレーザ堆積 (PLD: Pulsed Laser Deposition) 法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜 132 を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

30

【0226】

CVD 法として、マイクロ波 CVD 法を適用すると、成膜面へのプラズマダメージを小さくすることができる。また、高密度プラズマを用いるため、比較的低温 (325 度) でも緻密で欠陥の少ない膜を成膜することができる。なお、マイクロ波 CVD 法は、高密度プラズマ CVD 法とも呼ばれる。

【0227】

なお、結晶性絶縁膜 132 を成膜した後、第 1 の加熱処理を行ってもよい。第 1 の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下で行えばよい。第 1 の加熱処理の雰囲気は、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上、1% 以上もしくは 10% 以上含む雰囲気、または減圧状態で行う。または、第 1 の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上、1% 以上または 10% 以上含む雰囲気で加熱処理を行ってもよい。第 1 の加熱処理によって、結晶性絶縁膜 132 の結晶性を高め、かつ水素や水などの不純物を除去することができる。

40

【0228】

次に、酸化アルミニウム膜 134 を成膜する (図 7 (B) 参照。)。酸化アルミニウム膜 134 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0229】

結晶性絶縁膜 132 上に酸化アルミニウム膜 134 を成膜することで、高密度で結晶性を

50

有する酸化アルミニウム膜 134 を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜 134 は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

【0230】

なお、スパッタリング法を用いると、結晶性絶縁膜 132 上に高密度で結晶性を有する酸化アルミニウム膜 134 が成膜されやすいため、好ましい。また、酸化アルミニウム膜 134 を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【0231】

次に、ゲート電極 104 となる導電膜を成膜する。ゲート電極 104 となる導電膜は、ゲート電極 104 として示した導電膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0232】

次に、ゲート電極 104 となる導電膜を加工し、ゲート電極 104 を形成する（図 7 (C) 参照。）。

【0233】

次に、ゲート絶縁膜 112 を成膜する（図 7 (D) 参照。）。ゲート絶縁膜 112 は、ゲート絶縁膜 112 として示した絶縁膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0234】

次に、半導体膜 106 となる半導体膜を成膜する。半導体膜 106 となる半導体膜は、半導体膜 106 として示した半導体膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。半導体膜 106 となる半導体膜は、酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0235】

なお、酸化物半導体膜の成膜後に第 2 の加熱処理を行ってもよい。第 2 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えればよい。第 2 の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

【0236】

次に、半導体膜 106 となる半導体膜を加工し、島状に加工された半導体膜 106 を形成する（図 8 (A) 参照。）。

【0237】

なお、半導体膜 106 が酸化物半導体膜であるとき、半導体膜 106 の形成後に第 3 の加熱処理を行ってもよい。第 3 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えればよい。第 3 の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。なお、酸化物半導体膜が CAAAC-O<sub>5</sub> 膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

【0238】

次に、ソース電極 116a およびドレイン電極 116b となる導電膜を成膜する。ソース電極 116a およびドレイン電極 116b となる導電膜は、ソース電極 116a およびドレイン電極 116b として示した導電膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0239】

次に、ソース電極 116a およびドレイン電極 116b となる導電膜を加工し、ソース電極 116a およびドレイン電極 116b を形成する（図 8 (B) 参照。）。

10

20

30

40

50

## 【0240】

次に、保護絶縁膜118を成膜する。保護絶縁膜118は、保護絶縁膜118として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0241】

保護絶縁膜118は、例えば、石英（好ましくは合成石英）をターゲットに用い、基板加熱温度30以上450以下（好ましくは70以上200以下）、基板とターゲットの間の距離（T-S間距離）を20mm以上400mm以下（好ましくは40mm以上200mm以下）、圧力を0.1Pa以上4Pa以下（好ましくは0.2Pa以上1.2Pa以下）、高周波電源を0.5kW以上12kW以下（好ましくは1kW以上5kW以下）、成膜ガス中のO<sub>2</sub>/(O<sub>2</sub>+Ar)割合を20%超過100%以下（好ましくは50%以上100%以下）として、RFスパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英（好ましくは合成石英）ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、保護絶縁膜118を過剰酸素を含む絶縁膜とすることができます。

10

## 【0242】

次に、結晶性絶縁膜136を成膜する。結晶性絶縁膜136は、結晶性絶縁膜136として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

20

## 【0243】

次に、第4の加熱処理を行ってもよい。第4の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第4の加熱処理によって、結晶性絶縁膜136の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜106が酸化物半導体膜であり、かつ保護絶縁膜118が過剰酸素を含む絶縁膜であるとき、半導体膜106の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。

## 【0244】

次に、酸化アルミニウム膜138を成膜する（図8（C）参照。）。酸化アルミニウム膜138は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

30

## 【0245】

次に、第5の加熱処理を行ってもよい。第5の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第5の加熱処理によって、半導体膜106が酸化物半導体膜であり、かつ保護絶縁膜118が過剰酸素を含む絶縁膜であるとき、半導体膜106の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。なお、第4の加熱処理に代えて、第5の加熱処理を行っても構わない。このとき、酸化アルミニウム膜138を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

## 【0246】

以上のようにして図1に示したトランジスタを作製することができる。

40

## 【0247】

半導体膜106が酸化物半導体膜であるとき、第1乃至第5の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜134および酸化アルミニウム膜138がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第1乃至第5の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし、第1乃至第5の加熱処理を全て行うことには限られない。

## 【0248】

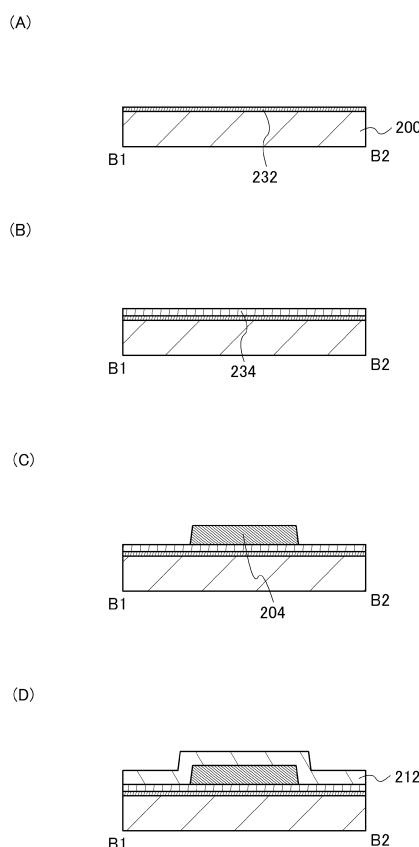

次に、図2に示したトランジスタの作製方法について、図9および図10を用いて説明する。なお、簡単のため、図9および図10には、図2（B）に対応する断面図のみ示す。

## 【0249】

50

まず、基板 200 を準備する。基板 200 は、基板 200 として示した基板から選択して用いればよい。

【 0 2 5 0 】

次に、結晶性絶縁膜 232 を成膜する（図 9（A）参照。）。結晶性絶縁膜 232 は、結晶性絶縁膜 232 として示した絶縁膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜 232 を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【 0 2 5 1 】

なお、結晶性絶縁膜 232 を成膜した後、第 6 の加熱処理を行ってもよい。第 6 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えばよい。第 6 の加熱処理によって、結晶性絶縁膜 232 の結晶性を高め、かつ水素や水などの不純物を除去することができる。

【 0 2 5 2 】

次に、酸化アルミニウム膜 234 を成膜する（図 9（B）参照。）。酸化アルミニウム膜 234 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 2 5 3 】

結晶性絶縁膜 232 上に酸化アルミニウム膜 234 を成膜することで、高密度で結晶性を有する酸化アルミニウム膜 234 を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜 234 は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

【 0 2 5 4 】

なお、スパッタリング法を用いると、結晶性絶縁膜 232 上に高密度で結晶性を有する酸化アルミニウム膜 234 が成膜されやすいため、好ましい。また、酸化アルミニウム膜 234 を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【 0 2 5 5 】

次に、ゲート電極 204 となる導電膜を成膜する。ゲート電極 204 となる導電膜は、ゲート電極 204 として示した導電膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 2 5 6 】

次に、ゲート電極 204 となる導電膜を加工し、ゲート電極 204 を形成する（図 9（C）参照。）。

【 0 2 5 7 】

次に、ゲート絶縁膜 212 を成膜する（図 9（D）参照。）。ゲート絶縁膜 212 は、ゲート絶縁膜 212 として示した絶縁膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 2 5 8 】

次に、ソース電極 216a およびドレイン電極 216b となる導電膜を成膜する。ソース電極 216a およびドレイン電極 216b となる導電膜は、ソース電極 216a およびドレイン電極 216b として示した導電膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【 0 2 5 9 】

次に、ソース電極 216a およびドレイン電極 216b となる導電膜を加工し、ソース電極 216a およびドレイン電極 216b を形成する（図 10（A）参照。）。

【 0 2 6 0 】

次に、半導体膜 206 となる半導体膜を成膜する。半導体膜 206 となる半導体膜は、半導体膜 206 として示した半導体膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。半導体膜 206 となる半導体膜は、

10

20

30

40

50

酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0261】

なお、酸化物半導体膜の成膜後に第7の加熱処理を行ってもよい。第7の加熱処理は、第1の加熱処理で示した条件を用いて行えればよい。第7の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

【0262】

次に、半導体膜206となる半導体膜を加工し、島状に加工された半導体膜206を形成する(図10(B)参照。)。

【0263】

なお、半導体膜206が酸化物半導体膜であるとき、半導体膜206の形成後に第8の加熱処理を行ってもよい。第8の加熱処理は、第1の加熱処理で示した条件を用いて行えればよい。第8の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。また、ゲート絶縁膜212と半導体膜206との界面に存在する水素や水などの不純物も除去できる。なお、酸化物半導体膜がCAC-O<sub>5</sub>膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

【0264】

次に、保護絶縁膜218を成膜する。保護絶縁膜218は、保護絶縁膜218として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0265】

保護絶縁膜218は、例えば、石英(好ましくは合成石英)をターゲットに用い、基板加熱温度30以上450以下(好ましくは70以上200以下)、基板とターゲットの間の距離(T-S間距離)を20mm以上400mm以下(好ましくは40mm以上200mm以下)、圧力を0.1Pa以上4Pa以下(好ましくは0.2Pa以上1.2Pa以下)、高周波電源を0.5kW以上12kW以下(好ましくは1kW以上5kW以下)、成膜ガス中のO<sub>2</sub>/(O<sub>2</sub>+Ar)割合を20%超過100%以下(好ましくは50%以上100%以下)として、RFスパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英(好ましくは合成石英)ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、保護絶縁膜218を過剰酸素を含む絶縁膜とすることができます。

【0266】

次に、結晶性絶縁膜236を成膜する。結晶性絶縁膜236は、結晶性絶縁膜236として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0267】

次に、第9の加熱処理を行ってもよい。第9の加熱処理は第1の加熱処理と同様の条件から選択して行えればよい。第9の加熱処理によって、結晶性絶縁膜236の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜206が酸化物半導体膜であり、かつ保護絶縁膜218が過剰酸素を含む絶縁膜であるとき、半導体膜206の欠陥(酸化物半導体膜の酸素欠損)を低減することができる。

【0268】

次に、酸化アルミニウム膜238を成膜する(図10(C)参照。)。酸化アルミニウム膜238は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて

10

20

30

40

50

成膜すればよい。

【0269】

次に、第10の加熱処理を行ってもよい。第10の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第10の加熱処理によって、半導体膜206が酸化物半導体膜であり、かつ保護絶縁膜218が過剰酸素を含む絶縁膜であるとき、半導体膜206の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。なお、第9の加熱処理に代えて、第10の加熱処理を行っても構わない。このとき、酸化アルミニウム膜238を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

【0270】

以上のようにして図2に示したトランジスタを作製することができる。

【0271】

半導体膜206が酸化物半導体膜であるとき、第6乃至第10の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜234および酸化アルミニウム膜238がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第6乃至第10の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし、第6乃至第10の加熱処理を全て行うことには限られない。

【0272】

次に、図3に示したトランジスタの作製方法について、図11および図12を用いて説明する。なお、簡単のため、図11および図12には、図3（B）に対応する断面図のみ示す。

【0273】

まず、基板300を準備する。基板300は、基板300として示した基板から選択して用いればよい。

【0274】

次に、結晶性絶縁膜332を成膜する（図11（A）参照。）。結晶性絶縁膜332は、結晶性絶縁膜332として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜332を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【0275】

なお、結晶性絶縁膜332を成膜した後、第11の加熱処理を行ってもよい。第11の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第11の加熱処理によって、結晶性絶縁膜332の結晶性を高め、かつ水素や水などの不純物を除去することができる。

【0276】

次に、酸化アルミニウム膜334を成膜する（図11（B）参照。）。酸化アルミニウム膜334は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0277】

結晶性絶縁膜332上に酸化アルミニウム膜334を成膜することで、高密度で結晶性を有する酸化アルミニウム膜334を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜334は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

【0278】

なお、スパッタリング法を用いると、結晶性絶縁膜332上に高密度で結晶性を有する酸化アルミニウム膜334が成膜されやすいため、好ましい。また、酸化アルミニウム膜334を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する

10

20

30

40

50

絶縁膜が成膜されやすいため、好ましい。

【0279】

次に、下地絶縁膜302を成膜する（図11（C）参照。）。下地絶縁膜302は、下地絶縁膜302として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0280】

下地絶縁膜302は、例えば、石英（好ましくは合成石英）をターゲットに用い、基板加熱温度30以上450以下（好ましくは70以上200以下）、基板とターゲットの間の距離（T-S間距離）を20mm以上400mm以下（好ましくは40mm以上200mm以下）、圧力を0.1Pa以上4Pa以下（好ましくは0.2Pa以上1.2Pa以下）、高周波電源を0.5kW以上12kW以下（好ましくは1kW以上5kW以下）、成膜ガス中のO<sub>2</sub> / (O<sub>2</sub> + Ar)割合を20%超過100%以下（好ましくは50%以上100%以下）として、RFスパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英（好ましくは合成石英）ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、下地絶縁膜302を過剰酸素を含む絶縁膜とすることができる。

【0281】

次に、半導体膜306となる半導体膜を成膜する。半導体膜306となる半導体膜は、半導体膜306として示した半導体膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。半導体膜306となる半導体膜は、酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0282】

なお、酸化物半導体膜の成膜後に第12の加熱処理を行ってもよい。第12の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第12の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

【0283】

次に、半導体膜306となる半導体膜を加工し、島状に加工された半導体膜306を形成する（図11（D）参照。）。

【0284】

なお、半導体膜306が酸化物半導体膜であるとき、半導体膜306の形成後に第13の加熱処理を行ってもよい。第13の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第13の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。また、下地絶縁膜302と半導体膜306との界面に存在する水素や水などの不純物も除去できる。なお、酸化物半導体膜がCAC-O<sub>5</sub>膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

【0285】

次に、ソース電極316aおよびドレイン電極316bとなる導電膜を成膜する。ソース電極316aおよびドレイン電極316bとなる導電膜は、ソース電極316aおよびドレイン電極316bとして示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0286】

次に、ソース電極316aおよびドレイン電極316bとなる導電膜を加工し、ソース電極316aおよびドレイン電極316bを形成する（図12（A）参照。）。

10

20

30

40

50

## 【0287】

次に、ゲート絶縁膜312を成膜する(図12(B)参照。)。ゲート絶縁膜312は、ゲート絶縁膜312として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0288】

次に、ゲート電極304となる導電膜を成膜する。ゲート電極304となる導電膜は、ゲート電極304として示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0289】

次に、ゲート電極304となる導電膜を加工し、ゲート電極304を形成する(図12(C)参照。)。

## 【0290】

次に、結晶性絶縁膜336を成膜する。結晶性絶縁膜336は、結晶性絶縁膜336として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0291】

次に、第14の加熱処理を行ってもよい。第14の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第14の加熱処理によって、結晶性絶縁膜336の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜306が酸化物半導体膜であり、かつ下地絶縁膜302が過剰酸素を含む絶縁膜であるとき、半導体膜306の欠陥(酸化物半導体膜の酸素欠損)を低減することができる。

20

## 【0292】

次に、酸化アルミニウム膜338を成膜する(図12(D)参照。)。酸化アルミニウム膜338は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0293】

次に、第15の加熱処理を行ってもよい。第15の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第15の加熱処理によって、半導体膜306が酸化物半導体膜であり、かつ下地絶縁膜302が過剰酸素を含む絶縁膜であるとき、半導体膜306の欠陥(酸化物半導体膜の酸素欠損)を低減することができる。なお、第14の加熱処理に代えて、第15の加熱処理を行っても構わない。このとき、酸化アルミニウム膜338を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

30

## 【0294】

以上のようにして図3に示したトランジスタを作製することができる。

## 【0295】

半導体膜306が酸化物半導体膜であるとき、第11乃至第15の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜334および酸化アルミニウム膜338がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第11乃至第15の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし第11乃至第15の加熱処理を全て行うことには限られない。

40

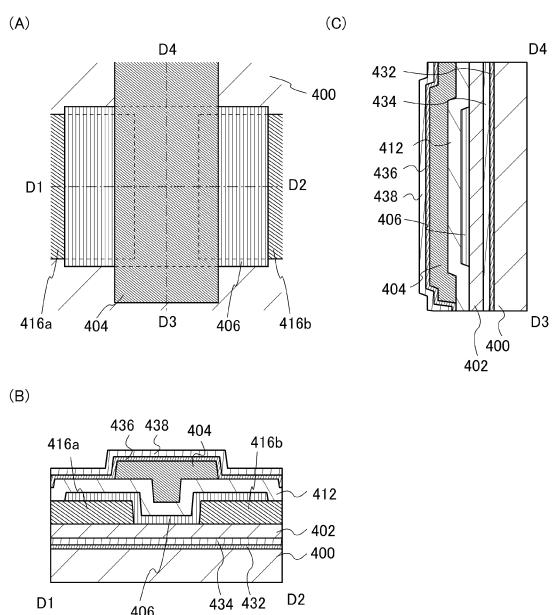

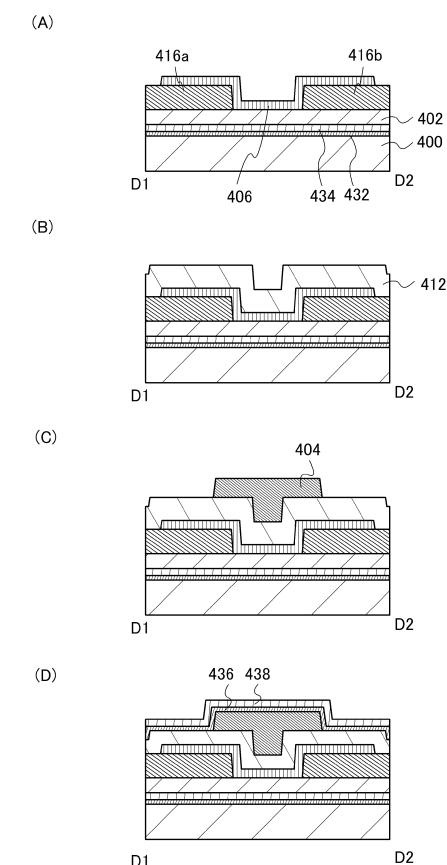

## 【0296】

次に、図4に示したトランジスタの作製方法について、図13および図14を用いて説明する。なお、簡単のため、図13および図14には、図4(B)に対応する断面図のみ示す。

## 【0297】

まず、基板400を準備する。基板400は、基板400として示した基板から選択して用いればよい。

## 【0298】

50

次に、結晶性絶縁膜432を成膜する(図13(A)参照。)。結晶性絶縁膜432は、結晶性絶縁膜432として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜432を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

#### 【0299】

なお、結晶性絶縁膜432を成膜した後、第16の加熱処理を行ってもよい。第16の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第16の加熱処理によって、結晶性絶縁膜432の結晶性を高め、かつ水素や水などの不純物を除去することができる。

10

#### 【0300】

次に、酸化アルミニウム膜434を成膜する(図13(B)参照。)。酸化アルミニウム膜434は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

#### 【0301】

結晶性絶縁膜432上に酸化アルミニウム膜434を成膜することで、高密度で結晶性を有する酸化アルミニウム膜434を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜434は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

20

#### 【0302】

なお、スパッタリング法を用いると、結晶性絶縁膜432上に高密度で結晶性を有する酸化アルミニウム膜434が成膜されやすいため、好ましい。また、酸化アルミニウム膜434を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

#### 【0303】

次に、下地絶縁膜402を成膜する(図13(C)参照。)。下地絶縁膜402は、下地絶縁膜402として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

#### 【0304】

下地絶縁膜402は、例えば、石英(好ましくは合成石英)をターゲットに用い、基板加熱温度30以上450以下(好ましくは70以上200以下)、基板とターゲットの間の距離(T-S間距離)を20mm以上400mm以下(好ましくは40mm以上200mm以下)、圧力を0.1Pa以上4Pa以下(好ましくは0.2Pa以上1.2Pa以下)、高周波電源を0.5kW以上12kW以下(好ましくは1kW以上5kW以下)、成膜ガス中のO<sub>2</sub>/(O<sub>2</sub>+Ar)割合を20%超過100%以下(好ましくは50%以上100%以下)として、RFスパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英(好ましくは合成石英)ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、下地絶縁膜402を過剰酸素を含む絶縁膜とすることができます。

30

#### 【0305】

次に、ソース電極416aおよびドレイン電極416bとなる導電膜を成膜する。ソース電極416aおよびドレイン電極416bとなる導電膜は、ソース電極416aおよびドレイン電極416bとして示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

40

#### 【0306】

次に、ソース電極416aおよびドレイン電極416bとなる導電膜を加工し、ソース電極416aおよびドレイン電極416bを形成する(図13(D)参照。)。

#### 【0307】

50

次に、半導体膜406となる半導体膜を成膜する。半導体膜406となる半導体膜は、半導体膜406として示した半導体膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。半導体膜406となる半導体膜は、酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0308】

なお、酸化物半導体膜の成膜後に第17の加熱処理を行ってもよい。第17の加熱処理は、第1の加熱処理で示した条件を用いて行えればよい。第17の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

10

【0309】

次に、半導体膜406となる半導体膜を加工し、島状に加工された半導体膜406を形成する(図14(A)参照。)。

【0310】

なお、半導体膜406が酸化物半導体膜であるとき、半導体膜406の形成後に第18の加熱処理を行ってもよい。第18の加熱処理は、第1の加熱処理で示した条件を用いて行えればよい。第18の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。また、下地絶縁膜402と半導体膜406との界面に存在する水素や水などの不純物も除去できる。なお、酸化物半導体膜がCAC-OS膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

20

【0311】

次に、ゲート絶縁膜412を成膜する(図14(B)参照。)。ゲート絶縁膜412は、ゲート絶縁膜412として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0312】

次に、ゲート電極404となる導電膜を成膜する。ゲート電極404となる導電膜は、ゲート電極404として示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

30

【0313】

次に、ゲート電極404となる導電膜を加工し、ゲート電極404を形成する(図14(C)参照。)。

【0314】

次に、結晶性絶縁膜436を成膜する。結晶性絶縁膜436は、結晶性絶縁膜436として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

40

【0315】

次に、第19の加熱処理を行ってもよい。第19の加熱処理は第1の加熱処理と同様の条件から選択して行えればよい。第19の加熱処理によって、結晶性絶縁膜436の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜406が酸化物半導体膜であり、かつ下地絶縁膜402が過剰酸素を含む絶縁膜であるとき、半導体膜406の欠陥(酸化物半導体膜の酸素欠損)を低減することができる。

【0316】

次に、酸化アルミニウム膜438を成膜する(図14(D)参照。)。酸化アルミニウム膜438は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0317】

50

次に、第20の加熱処理を行ってもよい。第20の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第20の加熱処理によって、半導体膜406が酸化物半導体膜であり、かつ下地絶縁膜402が過剰酸素を含む絶縁膜であるとき、半導体膜406の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。なお、第19の加熱処理に代えて、第20の加熱処理を行っても構わない。このとき、酸化アルミニウム膜438を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

### 【0318】

以上のようにして図4に示したトランジスタを作製することができる。

### 【0319】

半導体膜406が酸化物半導体膜であるとき、第16乃至第20の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜434および酸化アルミニウム膜438がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第16乃至第20の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし、第16乃至第20の加熱処理を全て行うことには限られない。

### 【0320】

次に、図5に示したトランジスタの作製方法について、図15および図16を用いて説明する。なお、簡単のため、図15および図16には、図5（B）に対応する断面図のみ示す。

### 【0321】

まず、基板500を準備する。基板500は、基板500として示した基板から選択して用いればよい。

### 【0322】

次に、結晶性絶縁膜532を成膜する（図15（A）参照。）。結晶性絶縁膜532は、結晶性絶縁膜532として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜532を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

### 【0323】

なお、結晶性絶縁膜532を成膜した後、第21の加熱処理を行ってもよい。第21の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第21の加熱処理によって、結晶性絶縁膜532の結晶性を高め、かつ水素や水などの不純物を除去することができる。

### 【0324】

次に、酸化アルミニウム膜534を成膜する（図15（B）参照。）。酸化アルミニウム膜534は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

### 【0325】

結晶性絶縁膜532上に酸化アルミニウム膜534を成膜することで、高密度で結晶性を有する酸化アルミニウム膜534を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜534は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

### 【0326】

なお、スパッタリング法を用いると、結晶性絶縁膜532上に高密度で結晶性を有する酸化アルミニウム膜534が成膜されやすいため、好ましい。また、酸化アルミニウム膜534を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

### 【0327】

10

20

30

40

50

次に、下地絶縁膜 502 を成膜する（図 15（C）参照。）。下地絶縁膜 502 は、下地絶縁膜 502 として示した絶縁膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0328】

下地絶縁膜 502 は、例えば、石英（好ましくは合成石英）をターゲットに用い、基板加熱温度 30 以上 450 以下（好ましくは 70 以上 200 以下）、基板とターゲットの間の距離（T-S 間距離）を 20mm 以上 400mm 以下（好ましくは 40mm 以上 200mm 以下）、圧力を 0.1Pa 以上 4Pa 以下（好ましくは 0.2Pa 以上 1.2Pa 以下）、高周波電源を 0.5kW 以上 1.2kW 以下（好ましくは 1kW 以上 5kW 以下）、成膜ガス中の  $O_2 / (O_2 + Ar)$  割合を 20% 超過 100% 以下（好ましくは 50% 以上 100% 以下）として、RF スパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英（好ましくは合成石英）ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、下地絶縁膜 502 を過剰酸素を含む絶縁膜とすることができます。

【0329】

次に、半導体膜 506 となる半導体膜を成膜する。半導体膜 506 となる半導体膜は、半導体膜 506 として示した半導体膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。半導体膜 506 となる半導体膜は、酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0330】

なお、酸化物半導体膜の成膜後に第 22 の加熱処理を行ってもよい。第 22 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えばよい。第 22 の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

【0331】

次に、半導体膜 506 となる半導体膜を加工し、島状に加工された半導体膜 506 を形成する（図 16（A）参照。）。

【0332】

なお、半導体膜 506 が酸化物半導体膜であるとき、半導体膜 506 の形成後に第 23 の加熱処理を行ってもよい。第 23 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えばよい。第 23 の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。また、下地絶縁膜 502 と半導体膜 506 との界面に存在する水素や水などの不純物も除去できる。なお、酸化物半導体膜が CAC-OS 膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

【0333】

次に、ゲート絶縁膜 512 となる絶縁膜 513 を成膜する（図 16（A）参照。）。絶縁膜 513 は、ゲート絶縁膜 512 として示した絶縁膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0334】

次に、ゲート電極 504 となる導電膜を成膜する。ゲート電極 504 となる導電膜は、ゲート電極 504 として示した導電膜から選択し、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法を用いて成膜すればよい。

【0335】

次に、ゲート電極 504 となる導電膜を加工し、ゲート電極 504 を形成する。

10

20

30

40

50

## 【0336】

次に、ゲート電極504の加工で用いたレジストマスクまたはゲート電極504をマスクとして、絶縁膜513を加工し、ゲート絶縁膜512を形成する（図16（B）参照。）。

## 【0337】

次に、ゲート電極504をマスクとし、半導体膜506に不純物を添加してもよい。不純物としては、半導体膜506が低抵抗化する不純物から選択して添加すればよい。なお、半導体膜506が酸化物半導体膜である場合、不純物として、ヘリウム、ホウ素、窒素、フッ素、ネオン、アルミニウム、リン、アルゴン、ヒ素、クリプトン、インジウム、スズ、アンチモンおよびキセノンから選ばれた一種以上を添加すればよい。なお、不純物を添加するためには、イオン注入法、イオンドーピング法で行えばよい。好ましくはイオン注入法を用いればよい。このとき、加速電圧を5kV以上100kV以下とする。また、不純物の添加量は $1 \times 10^{14}$  ions/cm<sup>2</sup>以上 $1 \times 10^{16}$  ions/cm<sup>2</sup>以下とする。

10

## 【0338】

次に、第24の加熱処理を行ってもよい。第24の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第24の加熱処理によって、半導体膜506の不純物の添加された領域を低抵抗領域とすることができる。また、半導体膜506が酸化物半導体膜であり、かつ下地絶縁膜502が過剰酸素を含む絶縁膜であるとき、半導体膜506の欠陥（酸化物半導体膜の酸素欠損）を低減することもできる。

20

## 【0339】

次に、結晶性絶縁膜536を成膜する。結晶性絶縁膜536は、結晶性絶縁膜536として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0340】

次に、第25の加熱処理を行ってもよい。第25の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第25の加熱処理によって、結晶性絶縁膜536の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜506が酸化物半導体膜であり、かつ下地絶縁膜502が過剰酸素を含む絶縁膜であるとき、半導体膜506の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。

30

## 【0341】

次に、酸化アルミニウム膜538を成膜する（図16（C）参照。）。酸化アルミニウム膜538は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0342】

次に、第26の加熱処理を行ってもよい。第26の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第26の加熱処理によって、半導体膜506が酸化物半導体膜であり、かつ下地絶縁膜502が過剰酸素を含む絶縁膜であるとき、半導体膜506の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。なお、第25の加熱処理に代えて、第26の加熱処理を行っても構わない。このとき、酸化アルミニウム膜538を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

40

## 【0343】

次に、保護絶縁膜518を成膜する。保護絶縁膜518は、保護絶縁膜518として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0344】

次に、結晶性絶縁膜536、酸化アルミニウム膜538および保護絶縁膜518を加工し、半導体膜506を露出する開口部を形成する。

## 【0345】

50

次に、配線 524a および配線 524b となる導電膜を成膜する。配線 524a および配線 524b となる導電膜は、配線 524a および配線 524b として示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0346】

次に、配線 524a および配線 524b となる導電膜を加工し、配線 524a および配線 524b を形成する（図16（D）参照。）。

【0347】

以上のようにして図5に示したトランジスタを作製することができる。

【0348】

半導体膜506が酸化物半導体膜であるとき、第21乃至第26の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜534および酸化アルミニウム膜538がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第21乃至第26の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし、第21乃至第26の加熱処理を全て行うことには限られない。

【0349】

次に、図6に示したトランジスタの作製方法について、図17乃至図19を用いて説明する。なお、簡単のため、図17乃至図19には、図6（B）に対応する断面図のみ示す。

【0350】

まず、基板600を準備する。基板600は、基板600として示した基板から選択して用いればよい。

【0351】

次に、結晶性絶縁膜632を成膜する（図17（A）参照。）。結晶性絶縁膜632は、結晶性絶縁膜632として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。なお、スパッタリング法を用いると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。また、結晶性絶縁膜632を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【0352】

なお、結晶性絶縁膜632を成膜した後、第27の加熱処理を行ってもよい。第27の加熱処理は、第1の加熱処理で示した条件を用いて行えばよい。第27の加熱処理によって、結晶性絶縁膜632の結晶性を高め、かつ水素や水などの不純物を除去することができる。

【0353】

次に、酸化アルミニウム膜634を成膜する（図17（B）参照。）。酸化アルミニウム膜634は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0354】

結晶性絶縁膜632上に酸化アルミニウム膜634を成膜することで、高密度で結晶性を有する酸化アルミニウム膜634を成膜することができる。高密度で結晶性を有する酸化アルミニウム膜634は、水素、水、酸素および金属元素が透過しにくい。従って、トランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。

【0355】

なお、スパッタリング法を用いると、結晶性絶縁膜632上に高密度で結晶性を有する酸化アルミニウム膜634が成膜されやすいため、好ましい。また、酸化アルミニウム膜634を100以上450以下に基板加熱しつつ成膜すると、高密度で結晶性を有する絶縁膜が成膜されやすいため、好ましい。

【0356】

次に、下地絶縁膜602を成膜する（図17（C）参照。）。下地絶縁膜602は、下地

10

20

30

40

50

絶縁膜 602 として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0357】

下地絶縁膜 602 は、例えば、石英（好ましくは合成石英）をターゲットに用い、基板加熱温度 30 以上 450 以下（好ましくは 70 以上 200 以下）、基板とターゲットの間の距離（T-S 間距離）を 20mm 以上 400mm 以下（好ましくは 40mm 以上 200mm 以下）、圧力を 0.1Pa 以上 4Pa 以下（好ましくは 0.2Pa 以上 1.2Pa 以下）、高周波電源を 0.5kW 以上 12kW 以下（好ましくは 1kW 以上 5kW 以下）、成膜ガス中の O<sub>2</sub> / (O<sub>2</sub> + Ar) 割合を 20% 超過 100% 以下（好ましくは 50% 以上 100% 以下）として、RFスパッタリング法により酸化シリコン膜を成膜すると好ましい。なお、石英（好ましくは合成石英）ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素ガスまたは、酸素及びアルゴンの混合ガスを用いて行う。このような方法を用いることで、下地絶縁膜 602 を過剰酸素を含む絶縁膜とすることができます。

【0358】

次に、半導体膜 606 となる半導体膜を成膜する。半導体膜 606 となる半導体膜は、半導体膜 606 として示した半導体膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。半導体膜 606 となる半導体膜は、酸化物半導体膜を用い、スパッタリング法で成膜すると好ましい。なお、スパッタリング法を用いると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。また、酸化物半導体膜を 100 以上 450 以下に基板加熱しつつ成膜すると、高密度で結晶性を有する酸化物半導体膜が成膜されやすいため、好ましい。

【0359】

なお、酸化物半導体膜の成膜後に第 28 の加熱処理を行ってもよい。第 28 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えればよい。第 28 の加熱処理によって、酸化物半導体膜の結晶性を高め、さらに酸化物半導体膜から水素や水などの不純物を除去することができる。

【0360】

次に、半導体膜 606 となる半導体膜を加工し、島状に加工された半導体膜 606 を形成する（図 17 (D) 参照。）。

【0361】

なお、半導体膜 606 が酸化物半導体膜であるとき、半導体膜 606 の形成後に第 29 の加熱処理を行ってもよい。第 29 の加熱処理は、第 1 の加熱処理で示した条件を用いて行えればよい。第 29 の加熱処理は、酸化物半導体膜の側面が露出した状態で行うため、酸化物半導体膜の側面から水素や水などの不純物が除去されやすく、効果的に不純物を除去することができる。また、下地絶縁膜 602 と半導体膜 606 との界面に存在する水素や水などの不純物も除去できる。なお、酸化物半導体膜が CAC-OS 膜であるとき、結晶の層に沿って不純物が拡散しやすいため、さらに側面から水素や水などの不純物が除去されやすい。

【0362】

次に、ゲート絶縁膜 612 となる絶縁膜を成膜する。ゲート絶縁膜 612 となる絶縁膜は、ゲート絶縁膜 612 として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0363】

次に、ゲート電極 604 となる導電膜を成膜する。ゲート電極 604 となる導電膜は、ゲート電極 604 として示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0364】

次に、ゲート電極 604 となる導電膜を加工し、ゲート電極 604 となる導電膜 605 を形成する。

10

20

30

40

50

## 【0365】

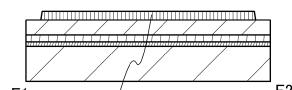

次に、導電膜605の加工で用いたレジストマスクまたは導電膜605をマスクとして、ゲート絶縁膜612となる絶縁膜を加工し、ゲート絶縁膜612を形成する(図18(A)参照。)。

## 【0366】

次に、導電膜605をマスクとし、半導体膜606に不純物を添加してもよい(第1の不純物添加ともいう。)。不純物としては、半導体膜606が低抵抗化する不純物から選択して添加すればよい。なお、半導体膜606が酸化物半導体膜である場合、不純物として、ヘリウム、ホウ素、窒素、フッ素、ネオン、アルミニウム、リン、アルゴン、ヒ素、クリプトン、インジウム、スズ、アンチモンおよびキセノンから選ばれた一種以上を添加すればよい。なお、不純物を添加するためには、イオン注入法、イオンドーピング法で行えればよい。好ましくはイオン注入法を用いればよい。このとき、加速電圧を5kV以上100kV以下とする。また、不純物の添加量は $1 \times 10^{14}$  ions/cm<sup>2</sup>以上 $1 \times 10^{16}$  ions/cm<sup>2</sup>以下とする。

10

## 【0367】

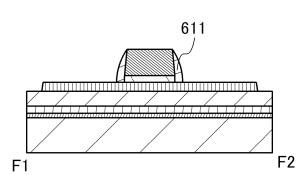

次に、側壁絶縁膜611となる絶縁膜を成膜する。側壁絶縁膜611となる絶縁膜は、側壁絶縁膜610として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。次に、側壁絶縁膜611となる絶縁膜に対し異方性の高いエッチング処理を行うことにより、ゲート絶縁膜612および導電膜605の側面に接する側壁絶縁膜611を形成することができる(図18(B)参照。)。

20

## 【0368】

次に、導電膜605および側壁絶縁膜611をマスクとし、半導体膜606に不純物を添加してもよい(第2の不純物添加ともいう。)。第2の不純物添加は、第1の不純物添加の条件を参考すればよい。第1の不純物添加および第2の不純物添加を行うことで、半導体膜606に二種類の低抵抗領域を設けることができる。そのため、ドレイン電極端での電界集中が緩和されやすく、ホットキャリア劣化の抑制効果が高い。また、ソース電極端においてドレイン電極端からの電界の影響が小さくなり、DIBLを抑制することができる。なお、第1の不純物添加および第2の不純物添加は、いずれか一方のみを行うこととしてもよい。

30

## 【0369】

次に、第30の加熱処理を行ってもよい。第30の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第30の加熱処理によって、半導体膜606の不純物の添加された領域を低抵抗領域とすることができます。また、半導体膜606が酸化物半導体膜であり、かつ下地絶縁膜602が過剰酸素を含む絶縁膜であるとき、半導体膜606の欠陥(酸化物半導体膜の酸素欠損)を低減することもできる。

## 【0370】

次に、ソース電極616aおよびドレイン電極616bとなる導電膜を成膜する。ソース電極616aおよびドレイン電極616bとなる導電膜は、ソース電極616aおよびドレイン電極616bとして示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

40

## 【0371】

次に、ソース電極616aおよびドレイン電極616bとなる導電膜を加工し、導電膜616を形成する(図18(C)参照。)。

## 【0372】

次に、結晶性絶縁膜637を成膜する(図18(D)参照。)。結晶性絶縁膜637は、結晶性絶縁膜637として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

## 【0373】

次に、第31の加熱処理を行ってもよい。第31の加熱処理は第1の加熱処理と同様の条

50

件から選択して行えばよい。第31の加熱処理によって、結晶性絶縁膜637の結晶性を高め、かつ水素や水などの不純物を除去することができる。また、半導体膜606が酸化物半導体膜であり、かつ下地絶縁膜602が過剰酸素を含む絶縁膜であるとき、半導体膜606の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。

【0374】

次に、酸化アルミニウム膜639を成膜する（図19（A）参照。）。酸化アルミニウム膜639は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0375】

次に、第32の加熱処理を行ってもよい。第32の加熱処理は第1の加熱処理と同様の条件から選択して行えばよい。第32の加熱処理によって、半導体膜606が酸化物半導体膜であり、かつ下地絶縁膜602が過剰酸素を含む絶縁膜であるとき、半導体膜606の欠陥（酸化物半導体膜の酸素欠損）を低減することができる。なお、第31の加熱処理に代えて、第32の加熱処理を行っても構わない。このとき、酸化アルミニウム膜639を有することにより、過剰酸素の外方拡散が抑制され、効果的に酸素欠損を低減することができる。

10

【0376】

次に、絶縁膜640となる絶縁膜641を成膜する（図19（B）参照。）。絶縁膜641は、絶縁膜640として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

20

【0377】

次に、絶縁膜641、酸化アルミニウム膜639、結晶性絶縁膜637、導電膜616、側壁絶縁膜611および導電膜605に対し、各層の表面の高さが揃うよう加工する。当該加工は、ドライエッチング処理、または化学機械研磨（CMP：Chemical Mechanical Polishing）処理によって行えばよい。当該加工によって、導電膜605がゲート電極604となり、側壁絶縁膜611が側壁絶縁膜610となり、導電膜616がソース電極616aおよびドレイン電極616bとなり、結晶性絶縁膜637が結晶性絶縁膜636となり、酸化アルミニウム膜639が酸化アルミニウム膜638となり、絶縁膜641が絶縁膜640となる（図19（C）参照。）。

30

【0378】

このようにして、ソース電極616aおよびドレイン電極616bを形成することで、ゲート電極604とソース電極616aおよびドレイン電極616bとの距離を側壁絶縁膜610の厚さと同様にすることができる。従って、ゲート電極604とソース電極616aおよびドレイン電極616bとの距離の長さを最小加工寸法よりも小さくできるため、図6に示すトランジスタの構成は微細なトランジスタを作製する際に好適な構造である。

【0379】

このような構造としたときに、酸化アルミニウム膜638の耐薬品性が高いため、形状不良の発生が抑制できる。従って、酸化アルミニウム膜638の形状不良箇所において、エッチング残渣物が生じることや、さらなる形状不良の原因ともなることが抑制できる。従って、安定した電気特性のトランジスタとすることができます。

40

【0380】

次に、保護絶縁膜618を成膜する。保護絶縁膜618は、保護絶縁膜618として示した絶縁膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0381】

次に、結晶性絶縁膜636、酸化アルミニウム膜638、絶縁膜640および保護絶縁膜618を加工し、ソース電極616aおよびドレイン電極616bを露出する開口部を形成する。

【0382】

次に、配線624aおよび配線624bとなる導電膜を成膜する。配線624aおよび配

50

線 6 2 4 b となる導電膜は、配線 6 2 4 a および配線 6 2 4 b として示した導電膜から選択し、スパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜すればよい。

【0383】

次に、配線 6 2 4 a および配線 6 2 4 b となる導電膜を加工し、配線 6 2 4 a および配線 6 2 4 b を形成する（図18（C）参照。）。

【0384】

以上のようにして図6に示したトランジスタを作製することができる。

【0385】

半導体膜 6 0 6 が酸化物半導体膜であるとき、第27乃至第32の加熱処理を行うことで、安定した電気特性を有し、信頼性の高いトランジスタを提供することができる。また、酸化アルミニウム膜 6 3 4 および酸化アルミニウム膜 6 3 8 がトランジスタの電気特性を劣化させる不純物に対するバリア膜としての機能を有する。従って、第27乃至第32の加熱処理によって、当該不純物の拡散が生じた場合でも、電気特性の劣化を引き起こさないことができる。ただし、第27乃至第32の加熱処理を全て行うことには限られない。

10

【0386】

本実施の形態より、不純物に対して高いバリア性を有する酸化アルミニウム膜を形成できるため、安定した電気特性を有し、信頼性が高いトランジスタを提供することができる。

【0387】

本実施の形態は、他の実施の形態の一部または全部について、変更、追加、修正、削除、応用、上位概念化、又は、下位概念化したものに相当する。したがって、本実施の形態の一部または全部について、他の実施の形態の一部または全部と自由に組み合わせることや、適用することや、置き換えて実施することができる。

20

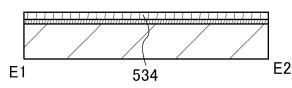

【0388】

（実施の形態3）

本実施の形態では、本発明の一態様に係るトランジスタについて説明する。

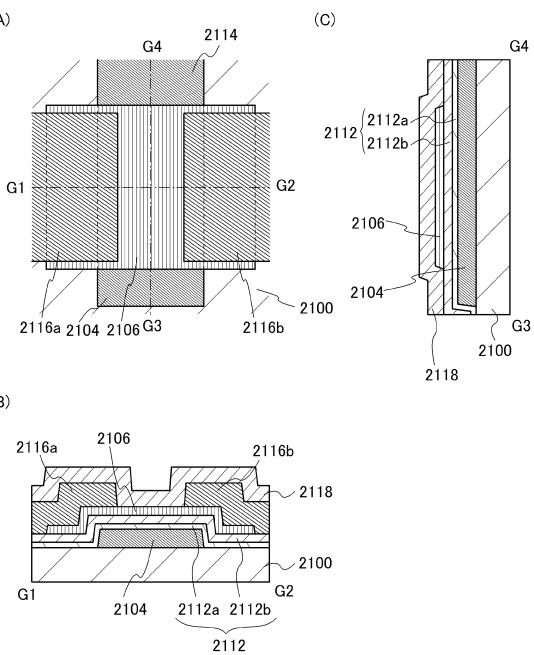

【0389】

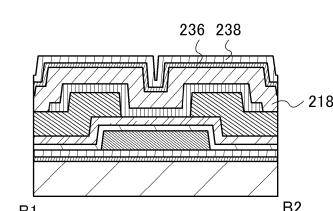

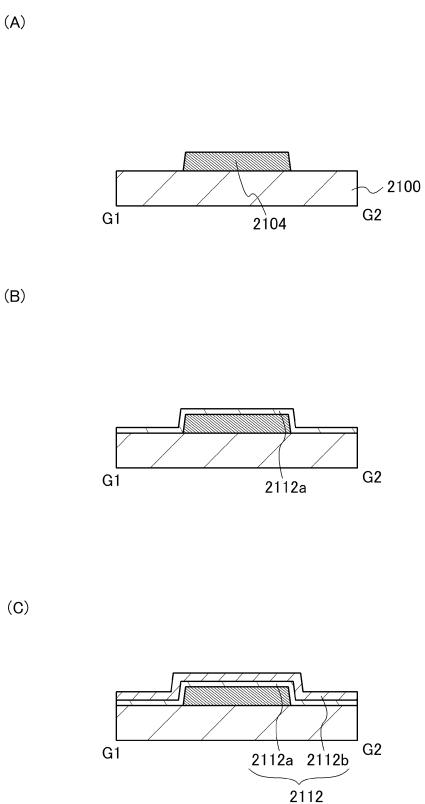

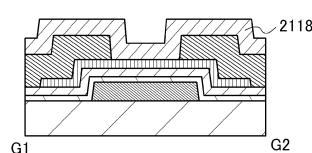

図20（A）は本発明の一態様に係るトランジスタの上面図である。図20（A）に示す一点鎖線 G 1 - G 2 に対応する断面図を図20（B）に示す。また、図20（A）に示す一点鎖線 G 3 - G 4 に対応する断面図を図20（C）に示す。なお、簡単のため、図20（A）においては、ゲート絶縁膜 2 1 1 2などを省略して示す。

30

【0390】

図20（B）は、基板 2 1 0 0 上に設けられたゲート電極 2 1 0 4 と、ゲート電極 2 1 0 4 上に設けられたゲート絶縁膜 2 1 1 2 と、ゲート絶縁膜 2 1 1 2 上にあり、ゲート電極 2 1 0 4 と重畳して設けられた半導体膜 2 1 0 6 と、半導体膜 2 1 0 6 上に設けられたソース電極 2 1 1 6 a およびドレイン電極 2 1 1 6 b と、半導体膜 2 1 0 6 、ソース電極 2 1 1 6 a およびドレイン電極 2 1 1 6 b 上に設けられた保護絶縁膜 2 1 1 8 と、を有するトランジスタの断面図である。なお、ゲート絶縁膜 2 1 1 2 は、結晶性絶縁膜 2 1 1 2 a 、および結晶性絶縁膜 2 1 1 2 a 上に設けられた酸化アルミニウム膜 2 1 1 2 b を有する。

40

【0391】

ここで、結晶性絶縁膜 2 1 1 2 a は、Mg、Ti、V、Cr、Y、Zr およびTaのいずれか一種以上を含む。具体的には、酸化マグネシウム、酸化チタン、酸化バナジウム、酸化クロム、酸化イットリウム、酸化ジルコニウムおよび酸化タンタルのいずれかを一種以上含むと好ましい。例えば、酸化ジルコニウムおよび酸化イットリウムを含む絶縁膜を用いることができる。

【0392】

結晶性絶縁膜 2 1 1 2 a は、結晶性を有する絶縁膜である。具体的にはXRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【0393】

50

酸化アルミニウム膜 2112b は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

【0394】

酸化アルミニウム膜 2112b は、結晶性絶縁膜 2112a との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。非晶質酸化アルミニウム膜は欠陥が多いため、ゲート絶縁膜として用いると、トランジスタの電気特性の劣化が生じる場合がある。酸化アルミニウム膜 2112b は、欠陥が少ないため、ゲート絶縁膜 2112 の欠陥に起因したトランジスタの電気特性の劣化を抑制することができる。

【0395】

酸化アルミニウム膜 2112b は、高密度の酸化アルミニウム膜である。具体的には、XRR またはラザフォード RBS によって密度が  $3.2 \text{ g/cm}^3$  以上  $4.1 \text{ g/cm}^3$  以下の酸化アルミニウム膜である。酸化アルミニウム膜 2112b は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0396】

なお、酸化アルミニウム膜 2112b は、結晶性絶縁膜 2112a の近傍に低密度層を有さない。具体的には、XRR によって密度が  $3.2 \text{ g/cm}^3$  未満の層を有さない。従って、酸化アルミニウム膜 2112b は欠陥が少ないため、良好なゲート絶縁膜 2112 を構成する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜はリーク電流が大きいため、ゲート絶縁膜として用いると、トランジスタのオフ電流を増大させる場合がある。また、低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

【0397】

また、酸化アルミニウム膜 2112b は、比誘電率が 7 以上 10 以下となる。従って、要求される等価酸化膜厚に対し 2 倍程度の物理膜厚とすることができます。そのため、ゲートリーク電流を低減することができる場合がある。

【0398】

半導体膜 2106 は、シリコン膜、ゲルマニウム膜、シリコンゲルマニウム膜、ヒ化ガリウム膜、炭化シリコン膜または窒化ガリウム膜を用いればよい。なお、半導体膜 2106 として、有機半導体膜を用いてもよい。また、半導体膜 2106 として、酸化物半導体膜を用いてもよい。

【0399】

なお、半導体膜 2106 に用いる酸化物半導体膜としては、先の実施の形態の記載を参照する。

【0400】

基板 2100 は、基板 100 の記載を参照する。

【0401】

ゲート電極 2104 は、ゲート電極 104 の記載を参照する。

【0402】

ソース電極 2116a およびドレイン電極 2116b は、ソース電極 116a およびドレイン電極 116b の記載を参照する。

【0403】

保護絶縁膜 2118 は、保護絶縁膜 118 の記載を参照する。

【0404】

次に、図 20 とは異なる構造のトランジスタについて、図 21 を用いて説明する。

【0405】

図 21(A) は本発明の一態様に係るトランジスタの上面図である。図 21(A) に示す

10

20

30

40

50

一点鎖線 H 1 - H 2 に対応する断面図を図 2 1 ( B ) に示す。また、図 2 1 ( A ) に示す一点鎖線 H 3 - H 4 に対応する断面図を図 2 1 ( C ) に示す。なお、簡単のため、図 2 1 ( A ) においては、ゲート絶縁膜 2 2 1 2 などを省略して示す。

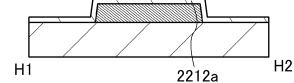

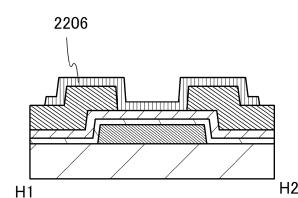

【 0 4 0 6 】

図 2 1 ( B ) は、基板 2 2 0 0 上に設けられたゲート電極 2 2 0 4 と、ゲート電極 2 2 0 4 上に設けられたゲート絶縁膜 2 2 1 2 と、ゲート絶縁膜 2 2 1 2 上に設けられたソース電極 2 2 1 6 a およびドレイン電極 2 2 1 6 b と、ゲート絶縁膜 2 2 1 2 、ソース電極 2 2 1 6 a およびドレイン電極 2 2 1 6 b 上にあり、ゲート電極 2 2 0 4 と重畳して設けられた半導体膜 2 2 0 6 と、半導体膜 2 2 0 6 、ソース電極 2 2 1 6 a およびドレイン電極 2 2 1 6 b 上に設けられた保護絶縁膜 2 2 1 8 と、を有するトランジスタの断面図である。なお、ゲート絶縁膜 2 2 1 2 は、結晶性絶縁膜 2 2 1 2 a 、および結晶性絶縁膜 2 2 1 2 a 上に設けられた酸化アルミニウム膜 2 2 1 2 b を有する。

【 0 4 0 7 】

ここで、結晶性絶縁膜 2 2 1 2 a は、結晶性絶縁膜 2 1 1 2 a の記載を参照する。

【 0 4 0 8 】

結晶性絶縁膜 2 2 1 2 a は、結晶性を有する絶縁膜である。具体的には X R D 、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【 0 4 0 9 】

酸化アルミニウム膜 2 2 1 2 b は、結晶性を有する。具体的には X R D 、電子線回折または中性子回折によって結晶性が確認できる。

【 0 4 1 0 】

酸化アルミニウム膜 2 2 1 2 b は、結晶性絶縁膜 2 2 1 2 a との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。非晶質酸化アルミニウム膜は欠陥が多いため、ゲート絶縁膜として用いると、トランジスタの電気特性の劣化が生じる場合がある。酸化アルミニウム膜 2 2 1 2 b は、欠陥が少ないため、ゲート絶縁膜 2 2 1 2 の欠陥に起因したトランジスタの電気特性の劣化を抑制することができる。

【 0 4 1 1 】

酸化アルミニウム膜 2 2 1 2 b は、高密度の酸化アルミニウム膜である。具体的には、X R R または R B S によって密度が 3 . 2 g / c m<sup>3</sup> 以上 4 . 1 g / c m<sup>3</sup> 以下の酸化アルミニウム膜である。酸化アルミニウム膜 2 2 1 2 b は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【 0 4 1 2 】

なお、酸化アルミニウム膜 2 2 1 2 b は、結晶性絶縁膜 2 2 1 2 a の近傍に低密度層を有さない。具体的には、X R R によって密度が 3 . 2 g / c m<sup>3</sup> 未満の層を有さない。従って、酸化アルミニウム膜 2 2 1 2 b は欠陥が少ないため、良好なゲート絶縁膜 2 2 1 2 を構成する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜はリーク電流が大きいため、ゲート絶縁膜として用いると、トランジスタのオフ電流を増大させる場合がある。また、低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

【 0 4 1 3 】

また、酸化アルミニウム膜 2 2 1 2 b は、比誘電率が 7 以上 10 以下となる。従って、要求される等価酸化膜厚に対し 2 倍程度の物理膜厚とすることができます。そのため、ゲートリーク電流を低減することができる場合がある。

【 0 4 1 4 】

半導体膜 2 2 0 6 は、半導体膜 1 0 6 の記載を参照する。

【 0 4 1 5 】

10

20

30

40

50

基板 2200 は、基板 100 の記載を参照する。

【0416】

ゲート電極 2204 は、ゲート電極 104 の記載を参照する。

【0417】

ソース電極 2216a およびドレイン電極 2216b は、ソース電極 116a およびドレイン電極 116b の記載を参照する。

【0418】

保護絶縁膜 2218 は、保護絶縁膜 118 の記載を参照する。

【0419】

保護絶縁膜 2218 は、過剰酸素を含む絶縁膜であると好ましい。

10

【0420】

保護絶縁膜 2218 が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

【0421】

次に、図 20 および図 21 とは異なる構造のトランジスタについて、図 22 を用いて説明する。

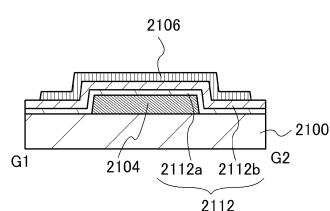

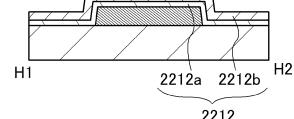

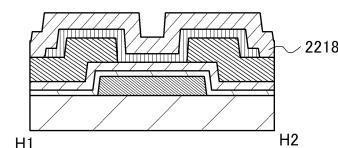

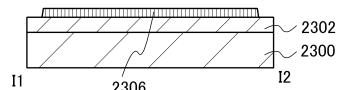

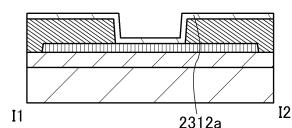

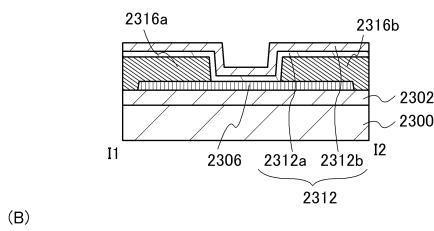

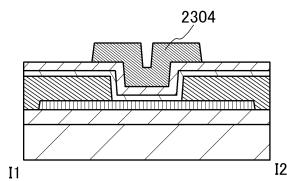

【0422】

図 22 (A) は本発明の一態様に係るトランジスタの上面図である。図 22 (A) に示す一点鎖線 I1 - I2 に対応する断面図を図 22 (B) に示す。また、図 22 (A) に示す一点鎖線 I3 - I4 に対応する断面図を図 22 (C) に示す。なお、簡単のため、図 22 (A) においては、ゲート絶縁膜 2312などを省略して示す。

20

【0423】

図 22 (B) は、基板 2300 上に設けられた下地絶縁膜 2302 と、下地絶縁膜 2302 上に設けられた半導体膜 2306 と、半導体膜 2306 上に設けられたソース電極 2316a およびドレイン電極 2316b と、半導体膜 2306、ソース電極 2316a およびドレイン電極 2316b 上に設けられたゲート絶縁膜 2312 と、ゲート絶縁膜 2312 上にあり、半導体膜 2306 と重畠して設けられたゲート電極 2304 と、を有するトランジスタの断面図である。なお、ゲート絶縁膜 2312 は、結晶性絶縁膜 2312a、および結晶性絶縁膜 2312a 上に設けられた酸化アルミニウム膜 2312b を有する。

【0424】

30

ここで、結晶性絶縁膜 2312a は、結晶性絶縁膜 2112a の記載を参照する。

【0425】

結晶性絶縁膜 2312a は、結晶性を有する絶縁膜である。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【0426】

酸化アルミニウム膜 2312b は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

【0427】

酸化アルミニウム膜 2312b は、結晶性絶縁膜 2312a との界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。非晶質酸化アルミニウム膜は欠陥が多いため、ゲート絶縁膜として用いると、トランジスタの電気特性の劣化が生じる場合がある。酸化アルミニウム膜 2312b は、欠陥が少ないため、ゲート絶縁膜 2312 の欠陥に起因したトランジスタの電気特性の劣化を抑制することができる。

40

【0428】

酸化アルミニウム膜 2312b は、高密度の酸化アルミニウム膜である。具体的には、XRD または RBS によって密度が  $3.2 \text{ g/cm}^3$  以上  $4.1 \text{ g/cm}^3$  以下の酸化アルミニウム膜である。酸化アルミニウム膜 2312b は、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

【0429】

50

なお、酸化アルミニウム膜 2312b は、結晶性絶縁膜 2312a の近傍に低密度層を有さない。具体的には、XRR によって密度が  $3.2 \text{ g/cm}^3$  未満の層を有さない。従って、酸化アルミニウム膜 2312b は欠陥が少ないため、良好なゲート絶縁膜 2312 を構成する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜はリーク電流が大きいため、ゲート絶縁膜として用いると、トランジスタのオフ電流を増大させる場合がある。また、低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

10

【0430】

また、酸化アルミニウム膜 2312b は、比誘電率が 7 以上 10 以下となる。従って、要求される等価酸化膜厚に対し 2 倍程度の物理膜厚とすることができます。そのため、ゲートリーク電流を低減することができる場合がある。

【0431】

半導体膜 2306 は、半導体膜 106 の記載を参照する。

【0432】

基板 2300 は、基板 100 の記載を参照する。

【0433】

下地絶縁膜 2302 は、下地絶縁膜 302 の記載を参照する。

20

【0434】

ソース電極 2316a およびドレイン電極 2316b は、ソース電極 2116a およびドレイン電極 2116b の記載を参照する。

【0435】

ゲート電極 2304 は、ゲート電極 2104 の記載を参照する。

【0436】

次に、図 20 乃至図 22 とは異なる構造のトランジスタについて、図 23 を用いて説明する。

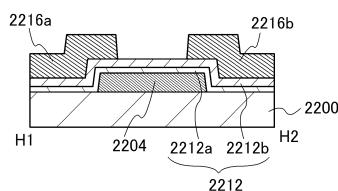

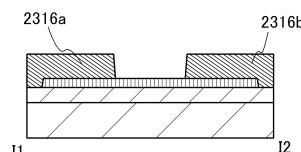

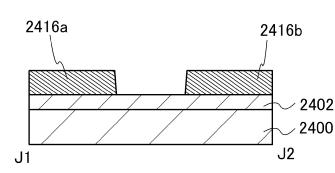

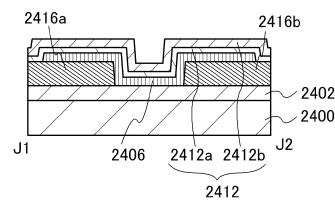

【0437】

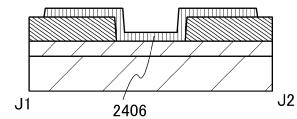

図 23 (A) は本発明の一態様に係るトランジスタの上面図である。図 23 (A) に示す一点鎖線 J1 - J2 に対応する断面図を図 23 (B) に示す。また、図 23 (A) に示す一点鎖線 J3 - J4 に対応する断面図を図 23 (C) に示す。なお、簡単のため、図 23 (A) においては、ゲート絶縁膜 2412などを省略して示す。

30

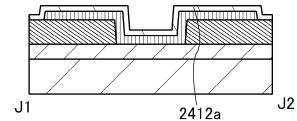

【0438】

図 23 (B) は、基板 2400 上に設けられた下地絶縁膜 2402 と、下地絶縁膜 2402 上に設けられたソース電極 2416a およびドレイン電極 2416b と、下地絶縁膜 2402、ソース電極 2416a およびドレイン電極 2416b 上に設けられた半導体膜 2406 と、半導体膜 2406 上に設けられたゲート絶縁膜 2412 と、ゲート絶縁膜 2412 上にあり、半導体膜 2406 と重畠して設けられたゲート電極 2404 と、を有するトランジスタの断面図である。なお、ゲート絶縁膜 2412 は、結晶性絶縁膜 2412a および結晶性絶縁膜 2412b 上に設けられた酸化アルミニウム膜 2412b を有する。

40

【0439】

ここで、結晶性絶縁膜 2412a は、結晶性絶縁膜 2112a の記載を参照する。

【0440】

結晶性絶縁膜 2412a は、結晶性を有する絶縁膜である。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる絶縁膜である。

【0441】

酸化アルミニウム膜 2412b は、結晶性を有する。具体的には XRD、電子線回折または中性子回折によって結晶性が確認できる。

50

## 【0442】

酸化アルミニウム膜2412bは、結晶性絶縁膜2412aとの界面近傍においても結晶性を有する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に非晶質酸化アルミニウム膜が形成される。非晶質酸化アルミニウム膜は欠陥が多いため、ゲート絶縁膜として用いると、トランジスタの電気特性の劣化が生じる場合がある。酸化アルミニウム膜2412bは、欠陥が少ないため、ゲート絶縁膜2412の欠陥に起因したトランジスタの電気特性の劣化を抑制することができる。

## 【0443】

酸化アルミニウム膜2412bは、高密度の酸化アルミニウム膜である。具体的には、XRRまたはRBSによって密度が3.2g/cm<sup>3</sup>以上4.1g/cm<sup>3</sup>以下の酸化アルミニウム膜である。酸化アルミニウム膜2412bは、不純物に対するバリア性が高いため、不純物に起因したトランジスタの電気特性の劣化を抑制できる。

10

## 【0444】

なお、酸化アルミニウム膜2412bは、結晶性絶縁膜2412aの近傍に低密度層を有さない。具体的には、XRRによって密度が3.2g/cm<sup>3</sup>未満の層を有さない。従って、酸化アルミニウム膜2412bは欠陥が少ないため、良好なゲート絶縁膜2412を構成する。対して、下地として、金属膜または非晶質絶縁膜上に酸化アルミニウム膜を形成した場合、下地の近傍に低密度の酸化アルミニウム膜が形成される。低密度の酸化アルミニウム膜はリーク電流が大きいため、ゲート絶縁膜として用いると、トランジスタのオフ電流を増大させる場合がある。また、低密度の酸化アルミニウム膜は、薬液に対する耐性が低く、トランジスタの作製時における薬液処理において、意図せずエッチングされてしまうことがある。その結果、形状不良が生じ、トランジスタの動作に不具合が現れることがある。

20

## 【0445】

また、酸化アルミニウム膜2412bは、比誘電率が7以上10以下となる。従って、要求される等価酸化膜厚に対し2倍程度の物理膜厚とすることができます。そのため、ゲートリーク電流を低減することができる場合がある。

## 【0446】

半導体膜2406は、半導体膜106の記載を参照する。

30

## 【0447】

基板2400は、基板100の記載を参照する。

## 【0448】

下地絶縁膜2402は、下地絶縁膜302の記載を参照する。

## 【0449】

下地絶縁膜2402は、過剰酸素を含む絶縁膜であると好ましい。

## 【0450】

下地絶縁膜2402が過剰酸素を含む絶縁膜である場合、酸化物半導体膜の酸素欠損を低減することができる。

## 【0451】

ソース電極2416aおよびドレイン電極2416bは、ソース電極116aおよびドレイン電極116bの記載を参照する。

40

## 【0452】

ゲート電極2404は、ゲート電極104の記載を参照する。

## 【0453】

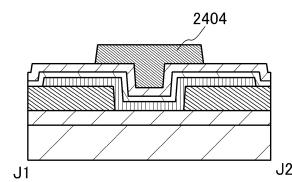

次に、図20乃至図23とは異なる構造のトランジスタについて、図24を用いて説明する。

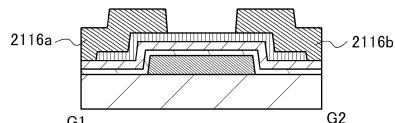

## 【0454】

図24(A)は本発明の一態様に係るトランジスタの上面図である。図24(A)に示す一点鎖線K1-K2に対応する断面図を図24(B)に示す。また、図24(A)に示す一点鎖線K3-K4に対応する断面図を図24(C)に示す。なお、簡単のため、図24

50

(A)においては、ゲート絶縁膜2512などを省略して示す。

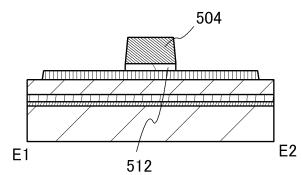

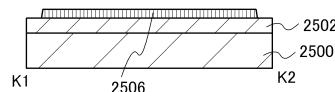

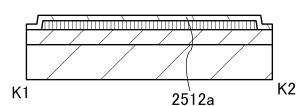

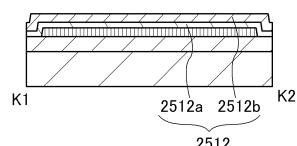

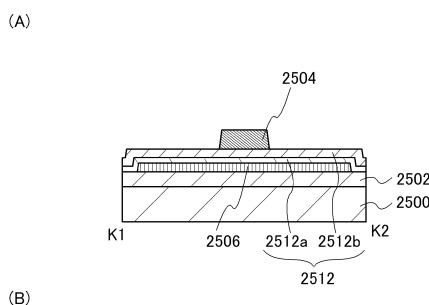

【0455】

図24(B)は、基板2500上に設けられた下地絶縁膜2502と、下地絶縁膜2502上に設けられた半導体膜2506と、半導体膜2506上に設けられたゲート絶縁膜2512と、ゲート絶縁膜2512上にあり、半導体膜2506と重畳して設けられたゲート電極2504と、を有するトランジスタの断面図である。なお、ゲート絶縁膜2512は、結晶性絶縁膜2512a、および結晶性絶縁膜2512a上に設けられた酸化アルミニウム膜2512bを有する。

【0456】