(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년07월09일

(11) 등록번호 10-1164349

(24) 등록일자 2012년07월03일

- (51) 국제특허분류(Int. C1.)

*H01L 33/16* (2010.01)

- (21) 출원번호 10-2010-7013933

- (22) 출원일자(국제) 2009년08월03일

심사청구일자 2010년07월15일

- (85) 번역문제출일자 2010년06월23일

- (65) 공개번호 10-2010-0087042

- (43) 공개일자 2010년08월02일

- (86) 국제출원번호 PCT/JP2009/063744

- (87) 국제공개번호 WO 2010/016459

국제공개일자 2010년02월11일

- (30) 우선권주장

JP-P-2008-201039 2008년08월04일 일본(JP)

(뒷면에 계속)

- (56) 선행기술조사문현

JP2003347585 A\*

JP2003218389 A\*

JP2006156958 A\*

\*는 심사관에 의하여 인용된 문현

- (73) 특허권자

**스미토모덴키고교가부시키가이샤**

일본 오사카후 오사카시 주오구 기타하마 4쵸메

5반33고

- (72) 발명자

**엔야 요헤이**

일본 효고켄 이타미시 고야키타 1-1-1 스미토모

덴키고교가부시키가이샤 이타미 세이사쿠쇼 나이

**요시즈미 유스케**

일본 효고켄 이타미시 고야키타 1-1-1 스미토모

덴키고교가부시키가이샤 이타미 세이사쿠쇼 나이

(뒷면에 계속)

- (74) 대리인

**신정건, 김태홍**

전체 청구항 수 : 총 26 항

심사관 : 김한수

(54) 발명의 명칭 GaN계 반도체 광소자, GaN계 반도체 광소자를 제작하는 방법, 에피택셜 웨이퍼 및 GaN계 반도체막을 성장시키는 방법

### (57) 요 약

GaN계 반도체 광소자(11a)에서는, 기판(13)의 주면(13a)은, 제1 GaN계 반도체의 c축을 따라 연장되는 기준축(Cx)에 직교하는 면으로부터 상기 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있다. GaN계 반도체 에피택셜 영역(15)은, 주면(13a) 위에 마련되어 있다. GaN계 반도체 에피택셜 영역(15) 위에는, 활성층(17)이 마련되어 있다. 활성층(17)은, 하나 이상의 반도체 에피택셜층(19)을 포함한다. 반도체 에피택셜층(19)은, InGaN으로 이루어진다. 반도체 에피택셜층(19)의 막 두께 방향은, 기준축(Cx)에 대하여 경사져 있다. 이 기준축(Cx)은, 제1 GaN계 반도체의 [0001]축의 방향을 향하고 있다. 이것에 의해, 활성층에서의 In 편석에 따른 발광 특성의 저하가 억제된 GaN계 반도체 발광 소자를 제공한다.

대 표 도

(72) 발명자

우에노 마사키

일본 효고켄 이타미시 고야키타 1-1-1 스미토모덴

키고교가부시키가이샤 이타미 세이사쿠쇼 나이

아키타 가츠시

일본 효고켄 이타미시 고야키타 1-1-1 스미토모덴

키고교가부시키가이샤 이타미 세이사쿠쇼 나이

교노 다파시

일본 효고켄 이타미시 고야키타 1-1-1 스미토모덴

키고교가부시키가이샤 이타미 세이사쿠쇼 나이

스미토모 다카미치

일본 효고켄 이타미시 고야키타 1-1-1 스미토모덴

키고교가부시키가이샤 이타미 세이사쿠쇼 나이

나카무라 다카오

일본 효고켄 이타미시 고야키타 1-1-1 스미토모덴

키고교가부시키가이샤 이타미 세이사쿠쇼 나이

### (30) 우선권주장

JP-P-2009-094335 2009년04월08일 일본(JP)

JP-P-2009-155208 2009년06월30일 일본(JP)

## 특허청구의 범위

### 청구항 1

GaN계 반도체 광소자로서,

제1 GaN계 반도체로 이루어지고, 이 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 이 제1 GaN계 반도체의 m축 방향으로 70도 이상 80도 미만의 범위의 경사각으로 경사진 주면(正面)을 갖는 기판과,

상기 주면 위에 마련된 GaN계 반도체 에피택셜 영역과,

상기 GaN계 반도체 에피택셜 영역 위에 마련되며, 활성층을 위한 반도체 에피택셀층을 포함하고,

상기 반도체 에피택셀층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 인듐을 함유하고, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있으며,

상기 기준축의 방향은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 한 방향인 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 2

삭제

### 청구항 3

제1항에 있어서, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의 m축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 4

제1항에 있어서, 상기 제1 GaN계 반도체의 a축 방향의 오프각은 유한의 값이고, -3도 이상 +3도 이하의 범위에 있는 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 5

제1항에 있어서, 상기 활성층 위에 마련된 제2 도전형 GaN계 반도체층을 포함하고,

상기 GaN계 반도체 에피택셀 영역은, 제1 도전형 GaN계 반도체층을 포함하며,

상기 활성층은, 미리 정해진 축 방향으로 교대로 배치된 우물층 및 장벽층을 포함하고,

상기 우물층은 상기 반도체 에피택셀층으로 이루어지며, 상기 장벽층은 GaN계 반도체로 이루어지고,

상기 제1 도전형 GaN계 반도체층, 상기 활성층 및 상기 제2 도전형 GaN계 반도체층은, 미리 정해진 축의 방향으로 배열되며, 상기 기준축의 방향은 상기 미리 정해진 축의 방향과 상이한 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 6

제1항에 있어서, 상기 활성층은 370 nm 이상 650 nm 이하의 파장 범위의 광을 생성하도록 마련되어 있는 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 7

제1항에 있어서, 상기 활성층은 480 nm 이상 600 nm 이하의 파장 범위의 광을 생성하도록 마련되어 있는 것을 특징으로 하는 GaN계 반도체 광소자.

### 청구항 8

제1항에 있어서, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의 (20-21)면 및 (20-2-1)면 중 어느 하나로부터 -3도 이상 +3도 이하 범위의 각도로 경사진 반도체면인 것을 특징으로 하는 GaN계 반도체 광소자.

**청구항 9**

제1항에 있어서, 상기 기준축은 상기 [0001]축 방향을 향하는 것을 특징으로 하는 GaN계 반도체 광소자.

**청구항 10**

제1항에 있어서, 상기 기준축은 상기 [000-1]축 방향을 향하는 것을 특징으로 하는 GaN계 반도체 광소자.

**청구항 11**

제1항에 있어서, 상기 기판은 GaN으로 이루어지는 것을 특징으로 하는 GaN계 반도체 광소자.

**청구항 12**

제1항에 있어서, 상기 기판의 상기 주면의 표면 모폴로지는 복수의 마이크로 스텝을 갖고 있고, 이 마이크로 스텝의 주요 구성면은, 적어도 Ⅲ면 및 (10-11)면을 포함하는 것을 특징으로 하는 GaN계 반도체 광소자.

**청구항 13**

GaN계 반도체 광소자를 제작하는 방법으로서,

제1 GaN계 반도체로 이루어지는 웨이퍼를 열처리하는 공정과,

상기 웨이퍼의 주면 위에, GaN계 반도체 에피택셜 영역을 성장시키는 공정과,

상기 GaN계 반도체 에피택셜 영역의 주면 위에, 활성층을 위한 반도체 에피택셜층을 형성하는 공정을 포함하고,

상기 웨이퍼는, 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 제1 GaN계 반도체의 Ⅲ축 방향으로 70도 이상 80도 미만 범위의 경사각으로 경사진 주면을 갖고 있으며,

상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지고, 상기 제2 GaN계 반도체는 구성 원소로서 인듐을 함유하며,

상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있고,

상기 기준축은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향을 향하고 있는 것을 특징으로 하는 방법.

**청구항 14**

삭제

**청구항 15**

제13항에 있어서, 상기 웨이퍼의 상기 주면은, 상기 제1 GaN계 반도체의 Ⅲ축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것을 특징으로 하는 방법.

**청구항 16**

제13항에 있어서, 상기 활성층은, 미리 정해진 축 방향으로 교대로 배치된 우물층 및 장벽층을 포함하는 양자우물 구조를 갖고 있고,

상기 반도체 에피택셜층은 상기 우물층이며,

상기 장벽층은 GaN계 반도체로 이루어지고,

이 방법은,

상기 반도체 에피택셜층 위에 상기 장벽층을 형성하는 공정과,

상기 활성층 위에, 제2 도전형 GaN계 반도체층을 성장시키는 공정을 포함하며,

상기 GaN계 반도체 에피택셜 영역은, 제1 도전형 GaN계 반도체층을 포함하고,

상기 제1 도전형 GaN계 반도체층, 상기 활성층 및 상기 제2 도전형 GaN계 반도체층은, 미리 정해진 축의 방향

으로 배열되며, 상기 기준축의 방향은 상기 미리 정해진 축의 방향과 상이한 것을 특징으로 하는 방법.

### 청구항 17

제13항에 있어서, 상기 제1 GaN계 반도체의 a축 방향의 오프각은 유한의 값이고, -3도 이상 +3도 이하의 범위에 있는 것을 특징으로 하는 방법.

### 청구항 18

제13항에 있어서, 상기 웨이퍼의 상기 주면에서의 상기 경사각은, 상기 제1 GaN계 반도체의 (20-21)면 및 (20-2-1)면 중 어느 하나의 결정면으로부터 -3도 이상 +3도 이하의 범위로 분포되어 있는 것을 특징으로 하는 방법.

### 청구항 19

제13항에 있어서, 상기 웨이퍼는  $In_sAl_tGa_{1-s-t}N$  ( $0 \leq s \leq 1$ ,  $0 \leq t \leq 1$ ,  $0 \leq s+t < 1$ )으로 이루어지는 것을 특징으로 하는 방법.

### 청구항 20

제13항에 있어서, 상기 웨이퍼는 GaN으로 이루어지는 것을 특징으로 하는 방법.

### 청구항 21

제13항에 있어서, 상기 웨이퍼의 상기 주면의 표면 모폴로지는 복수의 마이크로 스텝을 갖고 있고, 이 마이크로 스텝의 주요 구성면은, 적어도 m면 및 (10-11)면을 포함하는 것을 특징으로 하는 방법.

### 청구항 22

GaN계 반도체 광소자를 위한 에피택셜 웨이퍼로서,

제1 GaN계 반도체로 이루어지고, 이 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 이 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사진 주면을 갖는 기판과,

상기 주면 위에 마련된 GaN계 반도체 에피택셜 영역과,

상기 GaN계 반도체 에피택셜 영역 위에 마련되며, 활성층을 위한 반도체 에피택셜층을 포함하고,

상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 인듐을 함유하고, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있으며,

상기 기준축의 방향은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향인 것을 특징으로 하는 에피택셜 웨이퍼.

### 청구항 23

제22항에 있어서, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의 m축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것을 특징으로 하는 에피택셜 웨이퍼.

### 청구항 24

GaN계 반도체막을 성장시키는 방법으로서,

주요 구성면으로서 적어도 m면 및 (10-11)면을 포함하는 복수의 마이크로 스텝을 갖는 표면이 있는 GaN계 반도체 영역을 형성하는 공정과,

상기 GaN계 반도체 영역의 상기 표면 위에, 구성 원소로서 In을 포함하는 GaN계 반도체막을 성장시키는 공정을 포함하고,

상기 GaN계 반도체 영역의 상기 표면은, 이 GaN계 반도체 영역의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 이 GaN계 반도체 영역의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있는 것을 특징으로 하는 방법.

**청구항 25**

제24항에 있어서, 상기 GaN계 반도체 영역의 상기 표면은, 이 GaN계 반도체 영역의  $\bar{m}$ 축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것을 특징으로 하는 방법.

**청구항 26**

GaN계 반도체 광소자를 제작하는 방법으로서,

제1 GaN계 반도체로 이루어지는 웨이퍼를 열처리하는 공정과,

상기 웨이퍼의 주면 위에, 제1 도전형 GaN계 반도체층을 포함하는 GaN계 반도체 에피택셜 영역을 성장시키는 공정과,

상기 GaN계 반도체 에피택셜 영역의 주면 위에, 활성층을 위한 반도체 에피택셜층을 성장시키는 공정과,

상기 활성층 위에 제2 도전형 GaN계 반도체층을 형성하고, 에피택셜 웨이퍼를 제작하는 공정과,

상기 에피택셜 웨이퍼를 형성한 후에, 상기 GaN계 반도체 광소자를 위한 애노드 전극 및 캐소드 전극을 형성하여 기판 생산물을 제작하는 공정과,

상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향에 맞춰, 상기 기판 생산물의 주면의 표면에 스크라이브를 실시하는 공정과,

상기 기판 생산물에 스크라이브를 실시한 후에, 상기 기판 생산물을 벽개하여 벽개면을 형성하는 공정을 포함하고,

상기 기판 생산물은, GaN계 반도체 에피택셜 영역, 반도체 에피택셜층 및 제2 도전형 GaN계 반도체층을 포함하는 반도체 적층을 포함하며,

상기 반도체 적층은, 상기 기판 생산물의 상기 주면과 상기 웨이퍼의 상기 주면 사이에 있고,

상기 벽개면은 a면을 포함하며,

상기 웨이퍼는, 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향으로 63도 이상 80도 미만 범위의 경사각으로 경사진 주면을 갖고 있고,

상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 구성 원소로서 인듐을 함유하고,

상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있으며,

상기 기준축은, 상기 제1 GaN계 반도체의 [000-1]축의 방향을 향하고 있는 것을 특징으로 하는 방법.

**청구항 27**

제26항에 있어서, 상기 웨이퍼의 상기 주면은, 상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것을 특징으로 하는 방법.

**청구항 28**

GaN계 반도체 광소자를 제작하는 방법으로서,

제1 GaN계 반도체로 이루어지는 웨이퍼를 열처리하는 공정과,

상기 웨이퍼의 주면 위에, 제1 도전형 GaN계 반도체층을 포함하는 GaN계 반도체 에피택셜 영역을 성장시키는 공정과,

상기 GaN계 반도체 에피택셜 영역의 주면 위에, 활성층을 위한 반도체 에피택셜층을 성장시키는 공정과,

상기 활성층 위에 제2 도전형 GaN계 반도체층을 형성하여, 에피택셜 웨이퍼를 제작하는 공정과,

상기 에피택셜 웨이퍼를 형성한 후에, 상기 GaN계 반도체 광소자를 위한 애노드 전극 및 캐소드 전극을 형성하여 기판 생산물을 제작하는 공정과,

상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향에 맞춰, 상기 기판 생산물의 주면의 반대측 이면에 스크라이브를 실시하는

공정과,

상기 기판 생산물에 스크라이브를 실시한 후에, 상기 기판 생산물을 벽개하여 벽개면을 형성하는 공정을 포함하고,

상기 기판 생산물은, GaN계 반도체 에피택셜 영역, 반도체 에피택셜층 및 제2 도전형 GaN계 반도체층을 포함하는 반도체 적층을 포함하며,

상기 반도체 적층은, 상기 기판 생산물의 상기 주면과 상기 웨이퍼의 상기 주면 사이에 있고,

상기 벽개면은 a면을 포함하며,

상기 웨이퍼의 주면은 (20-21)면을 갖고 있고,

상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 구성 원소로서 인듐을 함유하고,

상기 제2 GaN계 반도체의 c축은 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 대하여 경사져 있으며,

상기 기준축은, 상기 제1 GaN계 반도체의 [0001]축의 방향을 향하고 있는 것을 특징으로 하는 방법.

## 명세서

### 기술분야

[0001]

본 발명은, GaN계 반도체 광소자, GaN계 반도체 광소자를 제작하는 방법, 에피택셜 웨이퍼 및 GaN계 반도체막을 성장시키는 방법에 관한 것이다.

### 배경기술

[0002]

특허문현 1에는, 발광 다이오드가 기재되어 있다. 이 발광 다이오드에서는, 기판 표면의 오프각이 30도 ~ 50도, 80도 ~ 100도, 그리고 120도 ~ 150도의 범위 내에 있다. 이들 각도 범위에서는, 발광층에서의 피에조 전계와 자발 분극에 의한 내부 전계의 합이, 제로에 가까운 작은 값이다. 또한 비특허문현 1~3에는, GaN 계 반도체의 발광 다이오드가 기재되어 있다. 비특허문현 1의 발광 다이오드는, 오프각 58도의 GaN 기판 위에 제작되어 있다. 비특허문현 2의 발광 다이오드는, 오프각 62도의 GaN 기판 위에 제작되어 있다. 비특허문현 3의 발광 다이오드는 m면 GaN 기판 위에 제작되어 있다. 비특허문현 4 및 5에는, 피에조 전계의 계산에 대해서 기재되어 있다.

### 선행기술문현

#### 특허문현

[0003]

(특허문현 0001) 특허문현 1: USP6849472호

#### 비특허문현

[0004]

- (비)특허문현 0001) 비특허문현 1: Japanese Journal of Applied Physics vol.45 No.26(2006) pp. L659

- (비)특허문현 0002) 비특허문현 2: Japanese Journal of Applied Physics vol.46 No.7(2007) pp. L129

- (비)특허문현 0003) 비특허문현 3: Japanese Journal of Applied Physics vol.46 No.40(2007) pp. L960

- (비)특허문현 0004) 비특허문현 4: Japanese Journal of Applied Physics vol.39(2000) pp.413

- (비)특허문현 0005) 비특허문현 5: Japanese Journal of Applied Physics vol.91 No.12(2002) pp.9904

### 발명의 내용

## 해결하려는 과제

[0005]

입수 가능한 GaN계 반도체 광소자는 c면 GaN 기판 위에 제작되어 있다. 최근, GaN계 반도체 광소자는 비특허 문현 3에 나타내는 바와 같이, GaN의 c면과는 다른 비극성면(a면, m면) 위에 제작되어 있다. 비극성면에서는, 극성면과 다르고 피에조 전계의 영향이 작다. 또한 GaN계 반도체 광소자의 제작에서는, 극성면 및 비극성면과 다르고 GaN의 c면으로부터 경사진 반극성면도 주목받고 있다. 비특허문현 1 및 비특허문현 2의 발광 다이오드는 특정 오프각의 GaN 기판 위에 제작되어 있다.

[0006]

특허문현 1에서는, GaN의 결정면에 의존한 피에조 전계뿐만 아니라, GaN의 자발 분극에도 착안하고 있다. 발광층에서의 피에조 전계와 자발 분극에 의한 내부전계의 합이 제로에 가까운 작은 값이 되도록 기판 표면의 패싯 방향을 선택하고 있다. 특허문현 1은 발광층의 내부 전계에 따른 과제를 해결하고 있다.

[0007]

한편, GaN계 반도체 광소자의 발광은, 넓은 파장 범위에서 변경될 수 있다. 발광층에는, 인듐을 함유하는 GaN 계 반도체층을 이용할 수 있다. 발광 파장의 변경은, 발광층에서의 인듐 조성을 조정하는 것에 의해 행해진다. 이 GaN계 반도체층의 하나로서, 예컨대 InGaN을 들 수 있다. InGaN은 강한 비호화성을 나타내고, 이 때문에 InGaN 성장에서는 자발적으로 In 조성의 변동이 생겨, In의 편석이 발생한다. In의 편석은 InGaN뿐만 아니라, 그 외의 인듐 함유의 GaN계 반도체에서도 관측된다. 또한 In의 편석은, 발광 파장의 변경을 위해 In 조성을 증가시킬 때, 현저하게 된다.

[0008]

발광층에서의 In의 편석은, 반도체 레이저에 있어서는 임계값 전류를 증가시킨다. 또한, 발광층에서의 In의 편석은, 발광 다이오드에 있어서는 면발광의 불균일의 원인이 된다. 그러므로 어떤 발광 소자에서도 In 편석을 저감하는 것이 바람직하다.

[0009]

본 발명은, 이러한 사정을 감안하여 이루어진 것으로, In 편석에 따른 발광 특성의 저하가 억제된 GaN계 반도체 발광 소자 및 에피택셜 웨이퍼를 제공하는 것을 목적으로 하고, 또한 이 GaN계 반도체 발광 소자를 제작하는 방법을 제공하는 것을 목적으로 한다. 또한, 본 발명은 낮은 In 편석을 나타내는 GaN계 반도체 영역을 성장시키는 방법을 제공하는 것을 목적으로 한다.

## 과제의 해결 수단

[0010]

본 발명의 일 측면에 따른 GaN계 반도체 광소자는, (a) 제1 GaN계 반도체로 이루어지고, 이 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 이 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사진 주면(主面)을 갖는 기판과, (b) 상기 주면 위에 마련된 GaN계 반도체 에피택셜 영역과, (c) 상기 GaN계 반도체 에피택셜 영역 위에 마련되며, 활성층을 위한 반도체 에피택셜층을 포함한다. 상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지고, 상기 제2 GaN계 반도체는 인듐을 함유하며, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있고, 상기 기준축의 방향은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 한 방향이다.

[0011]

상기 GaN계 반도체 광소자에 의하면, 상기한 경사각의 기판에서는, 그 주면은 폭이 좁은 복수의 테라스로 이루어진다. 또한, 기판 위에는 GaN계 반도체 에피택셜 영역이 마련되어 있기 때문에, GaN계 반도체 에피택셜 영역은, 기판의 결정축을 이어 받는다. 이로 인해, GaN계 반도체 에피택셜 영역의 주면도, 그 c축을 따라 연장되는 기준축에 직교하는 면으로부터 m축 방향으로 63도 이상 80도 미만 범위의 각도로 경사져 있다. 따라서, GaN계 반도체 에피택셜 영역의 주면도 폭이 좁은 복수의 테라스를 갖는다. 이 테라스 배열은 마이크로 스텝을 구성한다. 상기한 각도 범위의 테라스 폭이 좁기 때문에, 복수의 테라스에 걸쳐 In 조성의 불균일은 잘 발생하지 않는다. 그러므로 In 편석에 따른 발광 특성의 저하가 억제된다. 또한, 테라스 구조가 c축으로부터의 경사각에 의해 규정되기 때문에, 이 경사각이 제1 GaN계 반도체의 (0001)면을 기준으로 규정되는 기판과, 이 경사각이 제1 GaN계 반도체의 (000-1)면을 기준으로 규정되는 기판 중 어떤 것에서도, 발광 특성의 저하는 억제된다. 즉 기준축이 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향을 향하고 있더라도, 발광 특성의 저하가 억제된다.

[0012]

본 발명에 따른 GaN계 반도체 광소자에서, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의 m축 방향으로 상기 기준축에 직교하는 면으로부터 70도 이상의 각도로 경사져 있는 것이 바람직하다. 이 GaN계 반도체 광소자에서, 상기 각도 범위의 기판 주면은, 폭이 좁은 복수의 테라스를 더 갖는다.

[0013]

본 발명에 따른 GaN계 반도체 광소자에서는, 상기 제1 GaN계 반도체의 a축 방향의 오프각은 유한의 값이고, 또한 -3도 이상 +3도 이하의 범위에 있을 수 있다. 이 GaN계 반도체 광소자에 의하면, a축 방향의 오프각은,

에피택셜 영역의 표면 모폴로지를 양호하게 한다. 또한 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것이 바람직하다. 이 GaN계 반도체 광소자에 의하면, 스텝단(端) 성장과 테라스 위 성장의 밸런스가 양호하다.

[0014] 본 발명에 따른 GaN계 반도체 광소자는, 상기 활성층 위에 설치된 제2 도전형 GaN계 반도체층을 포함할 수 있다. 상기 GaN계 반도체 에피택셜 영역은, 제1 도전형 GaN계 반도체층을 포함하고, 상기 활성층은 미리 정해진 축 방향으로 교대로 배치된 우물층 및 장벽층을 포함하며, 상기 우물층은 상기 반도체 에피택셀층으로 이루어지고, 상기 장벽층은 GaN계 반도체로 이루어지며, 상기 제1 도전형 GaN계 반도체층, 상기 활성층 및 상기 제2 도전형 GaN계 반도체층은, 미리 정해진 축 방향으로 배열되고, 상기 기준축의 방향은 상기 미리 정해진 축 방향과 상이하다.

[0015] 이 GaN계 반도체 광소자에 의하면, 단층막으로 이루어지는 반도체 에피택셀층뿐만 아니라, 양자 우물 구조의 활성층에서 작은 In 편석이 달성된다.

[0016] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 활성층은 370 nm 이상의 발광 파장을 생성하도록 마련되는 것이 좋다. 이 GaN계 반도체 광소자에 의하면, 370 nm 이상의 발광 파장을 발생하는 활성층을 달성하는 인듐 조성의 범위에서, In 편석을 작게 할 수 있다. 또한, 상기 활성층은 650 nm 이하의 발광 파장을 생성하도록 설치되는 것이 바람직하다. 이 GaN계 반도체 광소자에 의하면, 650 nm 이상의 발광 파장을 발생하는 활성층에서는, 반도체 에피택셀층의 인듐 조성이 크기 때문에, 원하는 결정 품질의 반도체 에피택셀층이 잘 얻어지 않는다.

[0017] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 활성층은 480 nm 이상의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 또한, 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 활성층은 600 nm 이하의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 이 GaN계 반도체 광소자에 의하면, 63도 이상 80도 미만의 범위의 경사각은, 480 nm 이상 600 nm 이하의 발광 파장의 범위에서 유효하다.

[0018] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기판의 상기 주면은, 상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향으로 (20-21)면 및 (20-2-1)면 중 어느 하나로부터 -3도 이상 +3도 이하의 범위의 각도로 경사진 반도체면일 수 있다.

[0019] 이 GaN계 반도체 광소자에 의하면, (20-21)면 및 (20-2-1)면은 기준축에 직교하는 면으로부터 약 75도로 경사져 있다. 이 각도 근방에서 양호한 발광 특성을 나타내고 있다.

[0020] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기준축은 상기 [0001]축의 방향을 향하고 있다. 또는, 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기준축은 상기 [000-1]축의 방향을 향하고 있다.

[0021] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기판은  $In_xAl_xGa_{1-S-T}N(0 \leq S \leq 1, 0 \leq T \leq 1, 0 \leq S+T < 1)$ 으로 이루어질 수 있다. 또한, 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기판은 GaN으로 이루어지는 것이 좋다. 이 GaN계 반도체 광소자에 의하면, GaN은 이원 화합물인 GaN계 반도체이기 때문에, 양호한 결정 품질과 안정된 기판 주면이 제공된다.

[0022] 본 발명에 따른 GaN계 반도체 광소자에서는, 상기 기판의 상기 주면의 표면 모폴로지는 복수의 마이크로 스텝을 갖는다. 이 마이크로 스텝의 주요 구성면은, 적어도  $\bar{m}$ 면 및 (10-11)면을 포함한다. 이 GaN계 반도체 광소자에서는, 상기한 구성면 및 스텝단에서는, In의 혼입이 양호하다.

[0023] 본 발명의 다른 측면은, GaN계 반도체 광소자를 제작하는 방법이다. 이 방법은 (a) 제1 GaN계 반도체로 이루어지는 웨이퍼를 성장로에서 열처리하는 공정과, (b) 상기 주면 위에, GaN계 반도체 에피택셀 영역을 성장시키는 공정과, (c) 상기 GaN계 반도체 에피택셀 영역의 주면 위에, 활성층을 위한 반도체 에피택셀층을 형성하는 공정을 포함한다. 상기 웨이퍼는, 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 제1 GaN계 반도체의  $\bar{m}$ 축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사진 주면을 갖는다. 상기 반도체 에피택셀층은 인듐을 함유하는 제2 GaN계 반도체로 이루어지고, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있으며, 상기 기준축의 방향은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향이다.

[0024] 이 방법에 의하면, 상기한 경사각의 웨이퍼에서, 그 주면은, 폭이 좁은 복수의 테라스로 이루어진다. 또한, 웨이퍼 위에는 GaN계 반도체 에피택셀 영역이 마련되어 있기 때문에, GaN계 반도체 에피택셀 영역의

결정축은, 웨이퍼의 결정축을 이어 받는다. 이로 인해, GaN계 반도체 에피택셜 영역의 주면도, 그 c축을 따라 연장되는 기준축으로부터 m축 방향으로 63도 이상 80도 미만의 범위의 각도로 경사져 있다. 따라서, GaN계 반도체 에피택셜 영역의 주면도 폭이 좁은 복수의 테라스를 갖는다. 이들 테라스의 배열에 의해, 마이크로 스텝이 구성된다. 상기한 각도 범위의 테라스의 폭은 좁다. 좁은 테라스 폭을 위해, 각 테라스에 부착된 In 원자와 마이그레이션에 의한 이동이 방해된다. 그러므로 복수의 테라스에 걸쳐 In 조성의 불균일이 생기지 않는다. 따라서, In 편석에 따른 발광 특성의 저하가 억제된다. 또한, 테라스 구조가 c축으로부터의 경사각에 의해 규정되기 때문에, 제1 GaN계 반도체의 (0001)면을 기준으로 규정되는 웨이퍼 및 제1 GaN계 반도체의 (000-1)면을 기준으로 규정되는 웨이퍼의 모두에서는, 발광 특성의 저하가 억제된다. 즉, 기준축의 방향이 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향일 때, 발광 특성의 저하가 억제된다.

[0025] 본 발명에 따른 방법에서, 상기 웨이퍼의 상기 주면은, 상기 제1 GaN계 반도체의 m축 방향으로 상기 기준축에 직교하는 면으로부터 70도 이상의 범위의 각도로 경사져 있는 것이 좋다. 이 방법에서, 상기 각도 범위의 웨이퍼 주면은, 폭이 좁은 복수의 테라스를 더 갖는다. 또한 본 발명에 따른 방법에서, 상기 웨이퍼의 상기 주면은, 상기 제1 GaN계 반도체의 m축 방향으로 상기 기준축에 직교하는 면으로부터 71도 이상 79도 이하의 각도로 경사져 있는 것이 좋다. 이 GaN계 반도체 광소자에 의하면, 스텝단 성장과 테라스 위 성장의 밸런스가 양호하다.

[0026] 본 발명에 따른 방법에서, 상기 활성층은, 미리 정해진 축 방향에 교대로 배치된 우물층 및 장벽층을 포함하는 양자 우물 구조를 갖고 있고, 상기 반도체 에피택셜층은 상기 우물층이며, 상기 장벽층은 GaN계 반도체로 이루어지는 것이 좋다. 이 방법은, 상기 반도체 에피택셜층 위에 상기 장벽층을 형성하는 공정과, 상기 활성층 위에, 제2 도전형 GaN계 반도체층을 성장시키는 공정을 포함할 수 있다. 상기 GaN계 반도체 에피택셜 영역은, 제1 도전형 GaN계 반도체층을 포함하고, 상기 제1 도전형 GaN계 반도체층, 상기 활성층 및 상기 제2 도전형 GaN계 반도체층은, 미리 정해진 축 방향으로 배열되며, 상기 기준축의 방향은 상기 미리 정해진 축 방향과 상이하다.

[0027] 이 방법에서는, 단층막으로 이루어지는 반도체 에피택셜층의 성장뿐만 아니라, 양자 우물 구조의 활성층의 성장에서도, 작은 In 편석이 달성되고 있다.

[0028] 본 발명에 따른 방법에서는, 상기 제1 GaN계 반도체의 a축 방향의 오프각은 유한의 값이고, 또한 -3도 이상 +3도 이하의 범위에 있는 것이 좋다. 이 방법에 의하면, a축 방향으로부터의 오프각에 의해, 양호한 표면 모폴로지의 에피택셜 영역을 성장시킬 수 있다.

[0029] 본 발명에 따른 방법에서는, 상기 웨이퍼의 상기 주면에서의 상기 경사각은, 상기 제1 GaN계 반도체의 (20-21)면 및 (20-2-1)면 중 어느 하나의 결정면으로부터 -3도 이상 +3도 이하의 범위에 분포되어 있다.

[0030] 이 방법에 의하면, (20-21)면 및 (20-2-1)면은, 기준축으로부터 75.09도로 경사져 있다. 이 각도 근방에서 양호한 발광 특성을 나타내고 있다.

[0031] 본 발명에 따른 방법에서는, 상기 웨이퍼는  $In_{S}Al_{T}Ga_{1-S-T}N$  ( $0 \leq S \leq 1$ ,  $0 \leq T \leq 1$ ,  $0 \leq S+T < 1$ )으로 이루어질 수 있다. 또한, 본 발명에 따른 방법에서는, 상기 웨이퍼는 GaN으로 이루어지는 것이 좋다. 이 방법에 의하면, GaN은 이원 화합물인 GaN계 반도체이기 때문에, 양호한 결정 품질과 안정된 기판 주면이 제공된다.

[0032] 본 발명에 따른 방법에서는, 상기 웨이퍼의 상기 주면의 표면 모폴로지는 복수의 마이크로 스텝을 갖는다. 이 마이크로 스텝의 주요 구성면은, 적어도 m면 및 (10-11)면을 포함한다. 이 방법에서는, 상기한 구성면 및 스텝단에서는, In의 함유가 양호하다. 이 때문에 In의 편석이 저감된다.

[0033] 본 발명의 다른 측면은, GaN계 반도체 광소자를 제작하는 방법이다. 이 방법은, (a) 제1 GaN계 반도체로 이루어지는 웨이퍼를 열처리하는 공정과, (b) 상기 웨이퍼의 주면 위에, 제1 도전형 GaN계 반도체층을 포함하는 GaN계 반도체 에피택셜 영역을 성장시키는 공정과, (c) 상기 GaN계 반도체 에피택셜 영역의 주면 위에, 활성층을 위한 반도체 에피택셜층을 성장시키는 공정과, (d) 상기 활성층 위에 제2 도전형 GaN계 반도체층을 형성하고, 에피택셜 웨이퍼를 제작하는 공정과, (e) 상기 에피택셜 웨이퍼를 형성한 후에, 상기 GaN계 반도체 광소자를 위한 애노드 전극 및 캐소드 전극을 형성하여 기판 생산물을 제작하는 공정과, (f) 상기 제1 GaN계 반도체의 m축 방향에 맞춰, 상기 기판 생산물의 주면의 표면에 스크라이브를 실시하는 공정과, (g) 상기 기판 생산물에 스크라이브를 실시한 후에, 상기 기판 생산물의 벽개를 실시하여 벽개면을 형성하는 공정을 포함한다. 상기 기판 생산물은, GaN계 반도체 에피택셜 영역, 반도체 에피택셜층 및 제2 도전형 GaN계 반도체층을 포함하는 반도체 적층을 포함하고, 상기 반도체 적층은, 상기 기판 생산물의 상기 주면과 상기 웨이퍼의 상기

주면 사이에 있다. 상기 벽개면은 a면을 포함한다. 상기 웨이퍼는 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사진 주면을 갖고 있고, 상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 구성 원소로서 인듐을 함유하고, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있으며, 상기 기준축은, 상기 제1 GaN계 반도체의 [000-1]축 방향을 향하고 있다.

[0034] 이 방법에 의하면, 기준축의 방향이 제1 GaN계 반도체의 [000-1]축의 방향일 때, 이미 설명한 바와 같이, 발광 특성의 저하가 억제된다. 스크라이브는 기판 생산물의 표면에 대하여 행해진다. 이 스크라이브법을 이용하면, 벽개 수율이 양호하다.

[0035] 본 발명의 다른 측면은, GaN계 반도체 광소자를 제작하는 방법이다. 이 방법은 (a) 제1 GaN계 반도체로 이루어지는 웨이퍼를 열처리하는 공정과, (b) 상기 웨이퍼의 주면 위에, 제1 도전형 GaN계 반도체층을 포함하는 GaN계 반도체 에피택셜 영역을 성장시키는 공정과, (c) 상기 GaN계 반도체 에피택셜 영역의 주면 위에, 활성층을 위한 반도체 에피택셜층을 성장시키는 공정과, (d) 상기 활성층 위에 제2 도전형 GaN계 반도체층을 형성하고, 에피택셜 웨이퍼를 제작하는 공정과, (e) 상기 에피택셜 웨이퍼를 형성한 후에, 상기 GaN계 반도체 광소자를 위한 애노드 전극 및 캐소드 전극을 형성하여 기판 생산물을 제작하는 공정과, (f) 상기 제1 GaN계 반도체의 m축 방향에 맞춰, 상기 기판 생산물의 주면의 반대측 이면에 스크라이브를 실시하는 공정과, (g) 상기 기판 생산물에 스크라이브를 실시한 후에, 상기 기판 생산물의 벽개를 실시하여 벽개면을 형성하는 공정을 포함한다. 상기 기판 생산물은, GaN계 반도체 에피택셜 영역, 반도체 에피택셜층 및 제2 도전형 GaN계 반도체층을 포함하는 반도체 적층을 포함하고, 상기 반도체 적층은, 상기 기판 생산물의 상기 주면과 상기 웨이퍼의 상기 주면 사이에 있고, 상기 벽개면은 a면을 포함하며, 상기 웨이퍼의 주면은 (20-21)면을 갖고 있고, 상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지며, 상기 제2 GaN계 반도체는 구성 원소로서 인듐을 함유하고, 상기 제2 GaN계 반도체의 c축은 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 대하여 경사져 있고, 상기 기준축은, 상기 제1 GaN계 반도체의 [0001]축 방향을 향하고 있다.

[0036] GaN 웨이퍼의 (20-21)면 주면 위에 GaN계 반도체 에피택셜 영역을 성장시켜 에피택셜 웨이퍼를 제작한 후에, 이 에피택셜 웨이퍼로 기판 생산물을 제작한다. (20-21)면의 GaN 웨이퍼를 이용하여 제작된 기판 생산물에서는, 기판 생산물의 이면(웨이퍼의 이면)에 스크라이브를 실시하는 것이 바람직하다. 이것은 (20-2-1)면에 스크라이브를 실시하는 것이다. GaN의 (20-2-1)면은 Ga면이고, GaN의 (20-21)면은 N면이다. (20-2-1)면은 (20-21)면보다 딱딱하다. 웨이퍼 이면의 (20-2-1)면에 대한 스크라이브에 의해, 벽개 수율을 향상시킬 수 있다.

[0037] 본 발명에 따른 또 다른 측면은, GaN계 반도체 광소자를 위한 에피택셜 웨이퍼이다. 이 에피택셜 웨이퍼는, (a) 제1 GaN계 반도체로 이루어지고, 이 제1 GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 이 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만 범위의 경사각으로 경사진 주면을 갖는 기판과, (b) 상기 주면 위에 마련된 GaN계 반도체 에피택셜 영역과, (c) 상기 GaN계 반도체 에피택셜 영역 위에 마련되며, 활성층을 위한 반도체 에피택셜층을 포함하며, 상기 반도체 에피택셜층은 제2 GaN계 반도체로 이루어지고, 상기 제2 GaN계 반도체는 인듐을 함유하며, 상기 제2 GaN계 반도체의 c축은 상기 기준축에 대하여 경사져 있고, 상기 기준축의 방향은, 상기 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향이다.

[0038] 이 에피택셜 웨이퍼에 의하면, 상기한 경사각의 기판에서는, 그 주면은 폭이 좁은 복수의 테라스로 이루어진다. 또한, 기판 위에는 GaN계 반도체 에피택셜 영역이 마련되어 있기 때문에, GaN계 반도체 에피택셜 영역은, 기판의 결정축을 이어 받는다. 이로 인해, GaN계 반도체 에피택셜 영역의 주면도, 그 c축을 따라 연장되는 기준축에 직교하는 면으로부터 m축 방향으로 63도 이상 80도 미만의 범위의 각도로 경사져 있다. 따라서, GaN계 반도체 에피택셜 영역의 주면도 폭이 좁은 복수의 테라스를 갖는다. 이 테라스 배열은 마이크로 스텝을 구성한다. 상기한 각도 범위의 테라스 폭이 좁기 때문에, 복수의 테라스에 걸쳐 In 조성의 불균일은 발생하지 않는다. 그러므로 이 에피택셜 웨이퍼에 있어서, In 편석에 따른 발광 특성의 저하가 억제된다. 또한, 테라스 구조가 c축으로부터의 경사각에 의해 규정되기 때문에, 이 경사각이 제1 GaN계 반도체의 (0001)면을 기준으로 규정되는 기판과, 이 경사각이 제1 GaN계 반도체의 (000-1)면을 기준으로 규정되는 기판 모두에서, 발광 특성의 저하를 억제할 수 있다. 즉, 기준축이 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향을 향하고 있어도, 발광 특성의 저하가 억제된다.

[0039] 본 발명에 따른 또 다른 측면은, GaN계 반도체막을 성장시키는 방법이다. 이 방법은, 주요 구성면으로서 적어도 m면 및 (10-11)면을 포함하는 복수의 마이크로 스텝을 갖는 표면이 있는 GaN계 반도체 영역을 준비하는 공정과, 상기 GaN계 반도체 영역의 상기 표면 위에, 구성 원소로서 In을 포함하는 GaN계 반도체막을 성장시키는

공정을 포함한다. 상기 GaN계 반도체 영역의 상기 표면은, 상기 GaN계 반도체 영역의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 GaN계 반도체 영역의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있다.

[0040] 본 발명의 상기한 목적 및 다른 목적, 특징 및 이점은, 첨부 도면을 참조하여 기술하는 본 발명의 적합한 실시형태에 대한 이하의 상세한 설명으로부터, 보다 용이하게 명백해진다.

### 발명의 효과

[0041] 이상 설명한 바와 같이, 본 발명의 일측면에 의하면, 활성층에서의 In 편석에 따른 발광 특성의 저하가 억제된 GaN계 반도체 발광 소자 및 에피택셜 웨이퍼가 제공된다. 또한, 본 발명의 다른 측면에 의하면, 이 GaN계 반도체 발광 소자를 제작하는 방법이 제공된다. 본 발명의 또 다른 측면에 의하면, 낮은 In 편석을 나타내는 GaN계 반도체 영역을 성장시키는 방법이 제공된다.

### 도면의 간단한 설명

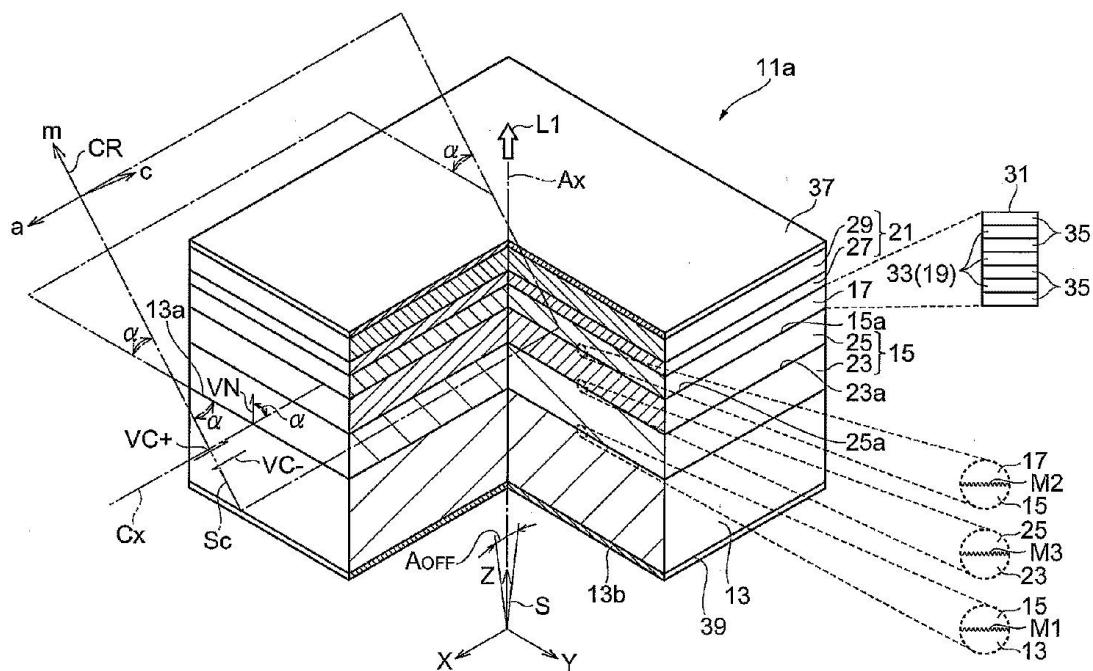

[0042] 도 1은 본 실시형태에 따른 GaN계 반도체 광소자의 구조를 개략적으로 도시하는 도면이다.

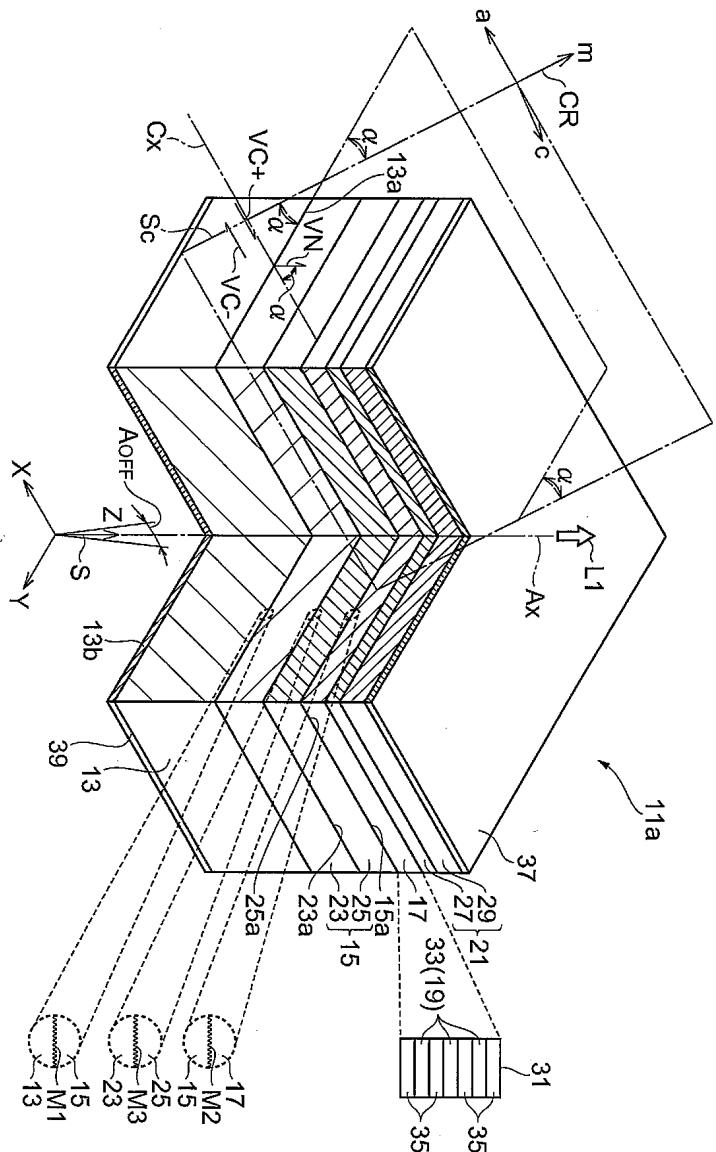

도 2는 본 실시형태에 따른 GaN계 반도체 광소자의 구조를 개략적으로 도시하는 도면이다.

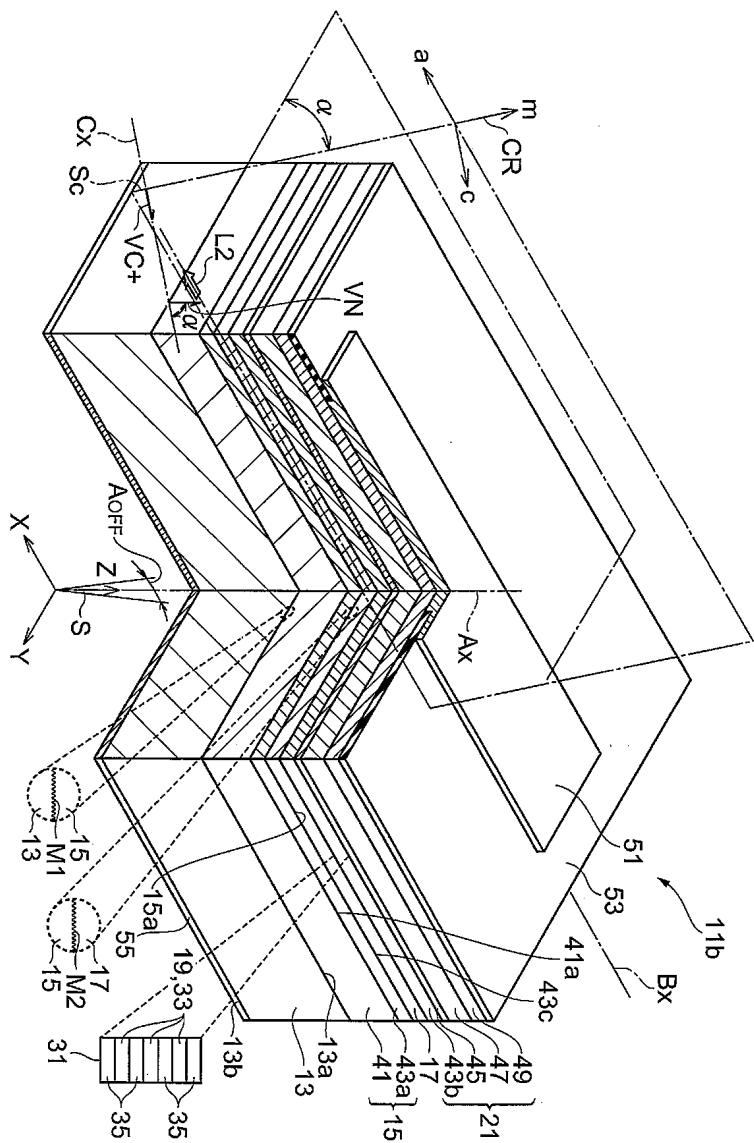

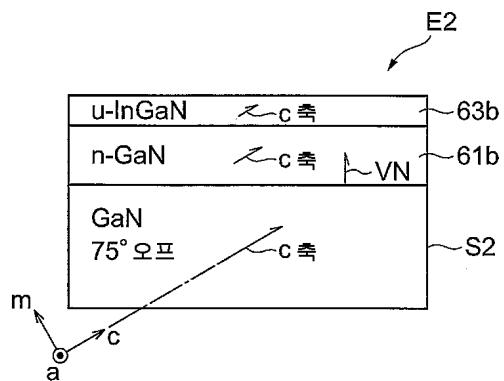

도 3은 실시예 1에 따른 에피택셜 웨이퍼(E1, E2)를 도시하는 도면이다.

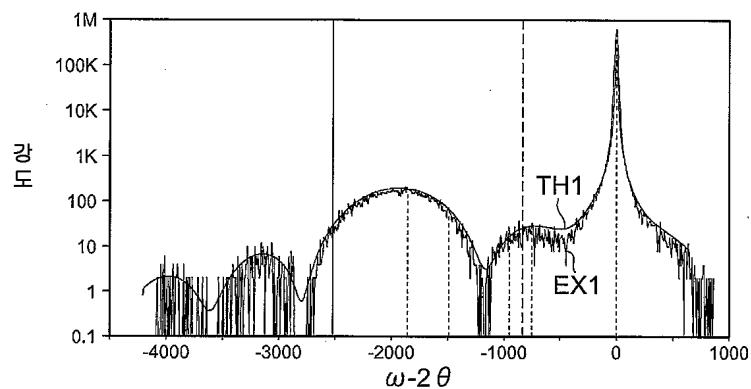

도 4는 X선 회절 결과 및 이론 계산의 결과를 도시하는 도면이다.

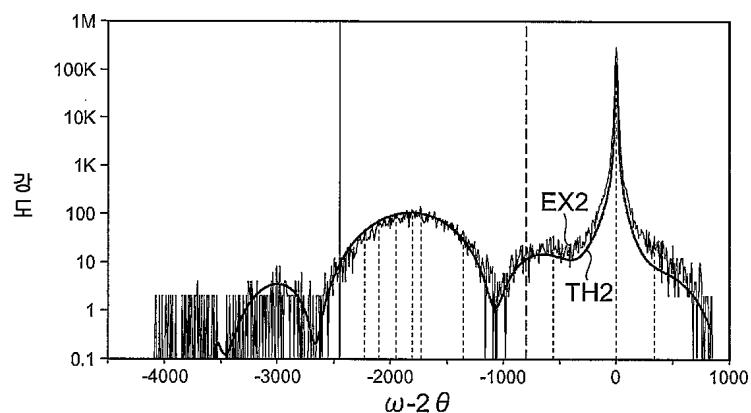

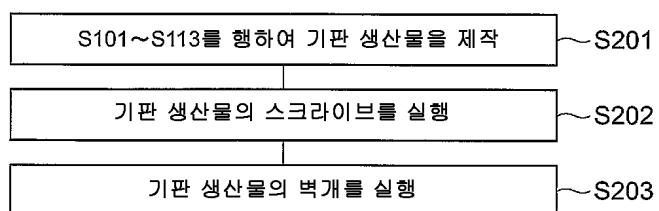

도 5는 본 실시형태에 따른 GaN계 반도체 광소자를 제작하는 방법의 주요 공정을 나타내는 도면이다.

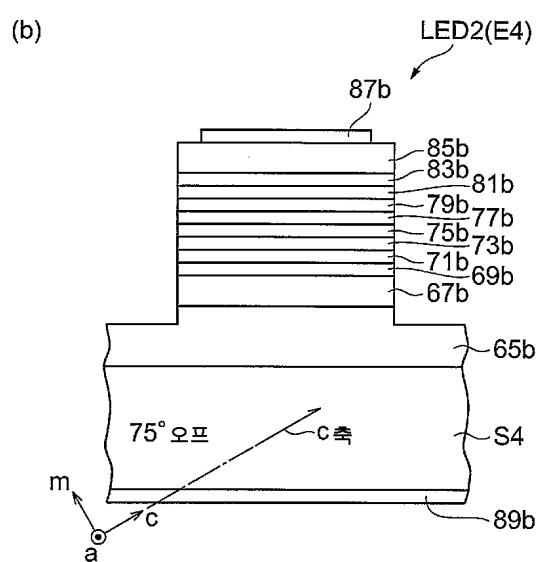

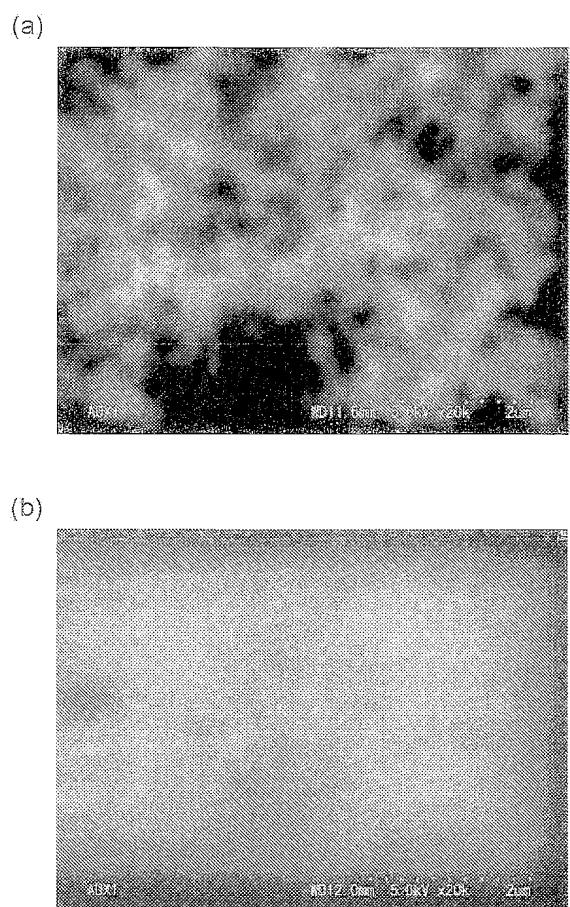

도 6은 실시예 2에 따른 발광 다이오드 구조(LED1, LED2)를 도시하는 도면이다.

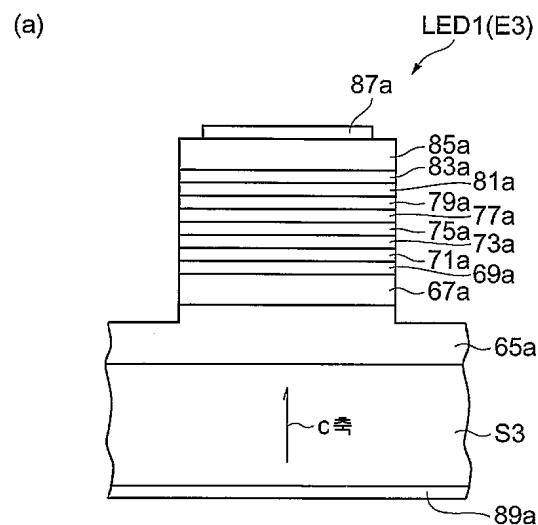

도 7은 발광 다이오드 구조(LED1, LED2)의 일렉트로 루미네센스 스펙트럼을 도시하는 도면이다.

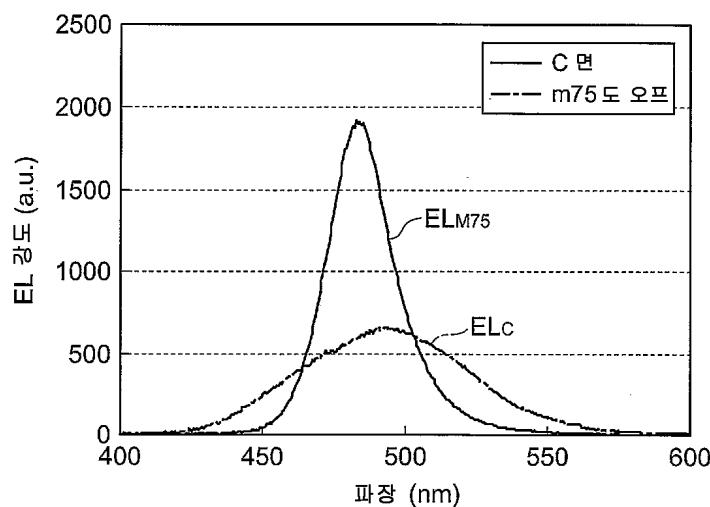

도 8은 에피택셜 웨이퍼(E3, E4)에서의 캐소드 루미네센스(CL) 위를 도시하는 도면이다.

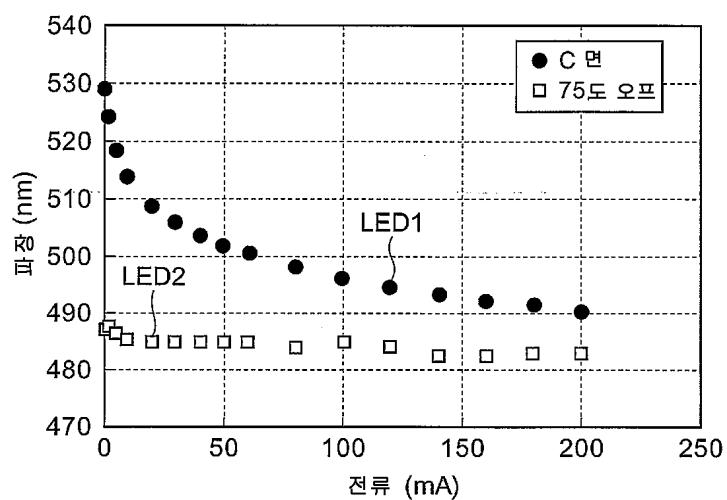

도 9는 발광 다이오드 구조(LED1, LED2)에서 발광 파장과 전류 주입량의 관계의 측정을 도시하는 도면이다.

도 10은 피에조 전계에 관한 계산 결과를 도시하는 도면이다.

도 11은 상이한 In 조성을 갖는 우물층의 발광 다이오드 구조의 일렉트로 루미네센스를 도시하는 도면이다.

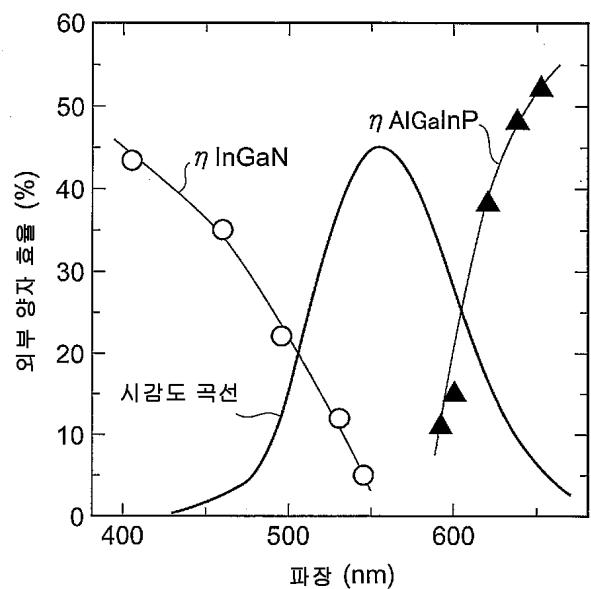

도 12는 InGaN 우물층의 발광 다이오드 및 AlGaInP 우물층의 외부 양자 효율 및 인간의 시감도 곡선을 도시하는 도면이다.

도 13은 실시예 4에 따른 레이저 다이오드 구조(LD1)를 도시하는 도면이다.

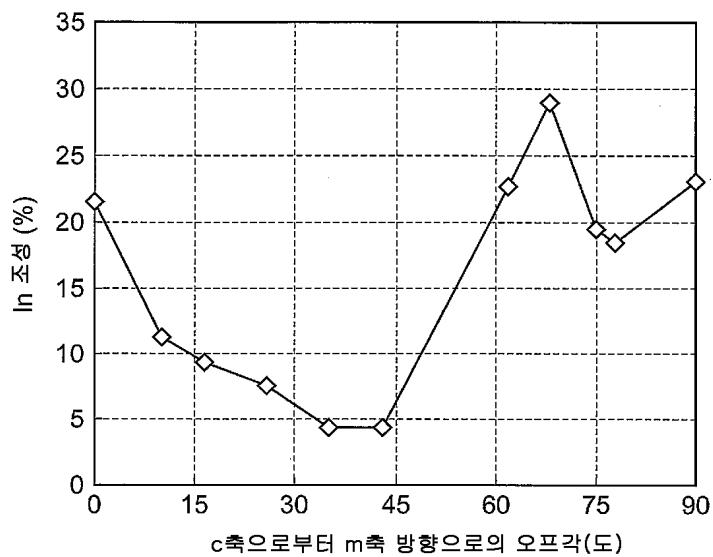

도 14는 c축으로부터 m축 방향으로 취한 여러 경사각(오프각)을 갖는 GaN 주면 위에 퇴적된 InGaN의 In 조성과 오프각의 관계를 도시하는 도면이다.

도 15는 c면 및 오프각  $\beta$ 를 갖는 GaN계 반도체면 위에 In 함유의 GaN계 반도체가 퇴적되는 것을 모식적으로 도시하는 도면이다.

도 16은 실시예 6에서의 반도체 레이저를 개략적으로 도시하는 도면이다.

도 17은 실시예 7에서의 반도체 레이저를 개략적으로 도시하는 도면이다.

도 18은 실시예 8에서의 반도체 레이저를 개략적으로 도시하는 도면이다.

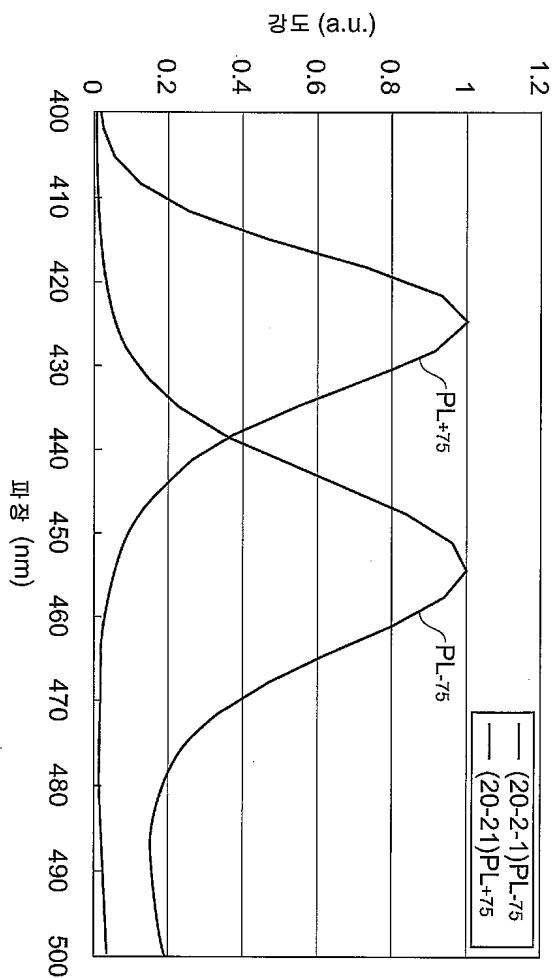

도 19는 m면 +75도 오프 GaN 기판 위의 양자 우물 구조의 포토 루미네센스(PL) 스펙트럼( $PL_{+75}$ ), 및 m면 -75도 오프 GaN 기판 위의 양자 우물 구조의 PL 스펙트럼( $PL_{-75}$ )를 도시하는 도면이다.

도 20은 (000-1)면으로부터 예각의 각도로 경사진 반극성 기판을 이용하여 반도체 발광 소자를 제작하는 방법에서의 주요 흐름을 나타내는 도면이다.

도 21은 (000-1)면으로부터 예각의 각도로 경사진 반극성 기판을 이용한 반도체 발광 소자를 위한 벽개에서의 주요 공정을 도시하는 도면이다.

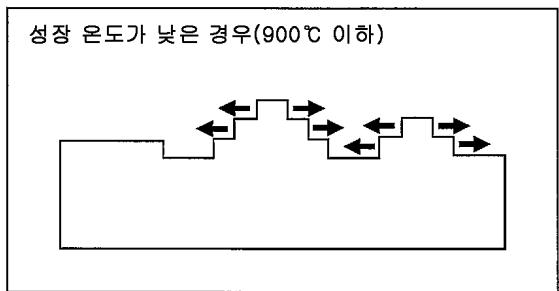

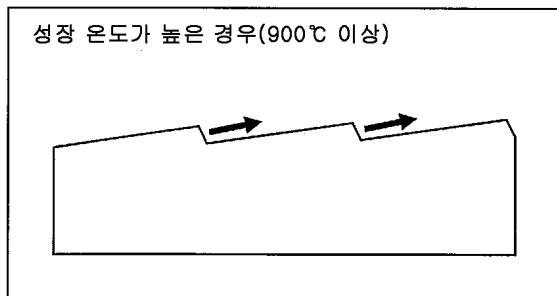

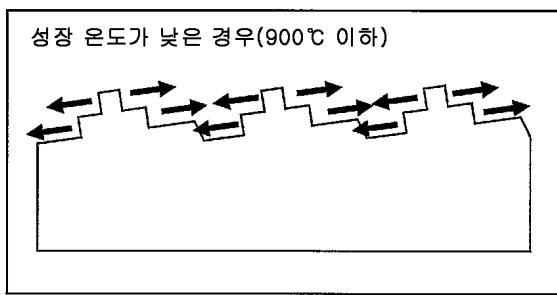

도 22는 성장 온도가 높을 때의 성장 모드 및 성장 온도가 낮을 때의 성장 모드를 모식적으로 도시하는 도면

이다.

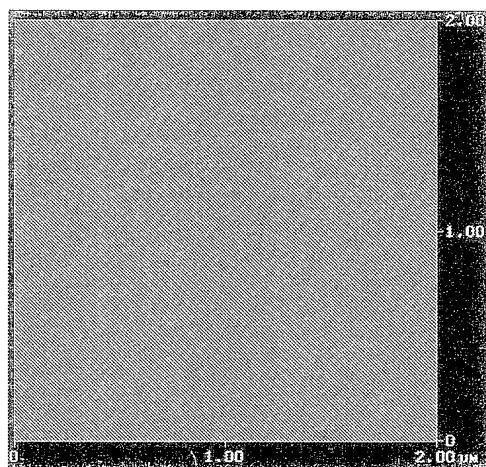

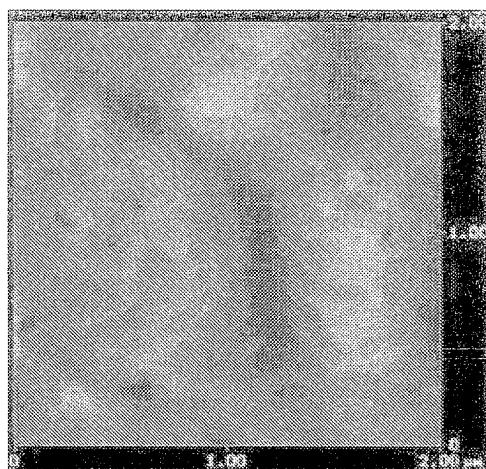

도 23은 스텝 플로 성장 및 테라스 성장에 의해 성장된 GaN의 성장 표면의 AFM상(像)을 도시하는 도면이다.

도 24는 비안정면에서의 GaN 및 InGaN의 고온 성장에서의 스텝 플로 성장의 성장 기구와, 비안정면에서의 GaN 및 InGaN의 저온 성장에서의 테라스 위 성장 및 스텝단 성장의 성장 기구를 모식적으로 도시하는 도면이다.

도 25는 c면으로부터 m축 방향으로 여러 경사 각도로 경사진 GaN 기판 위에, 섭씨 760도에서 모두 같은 조건으로 InGaN을 성장시키는 실험 결과를 도시하는 도면이다.

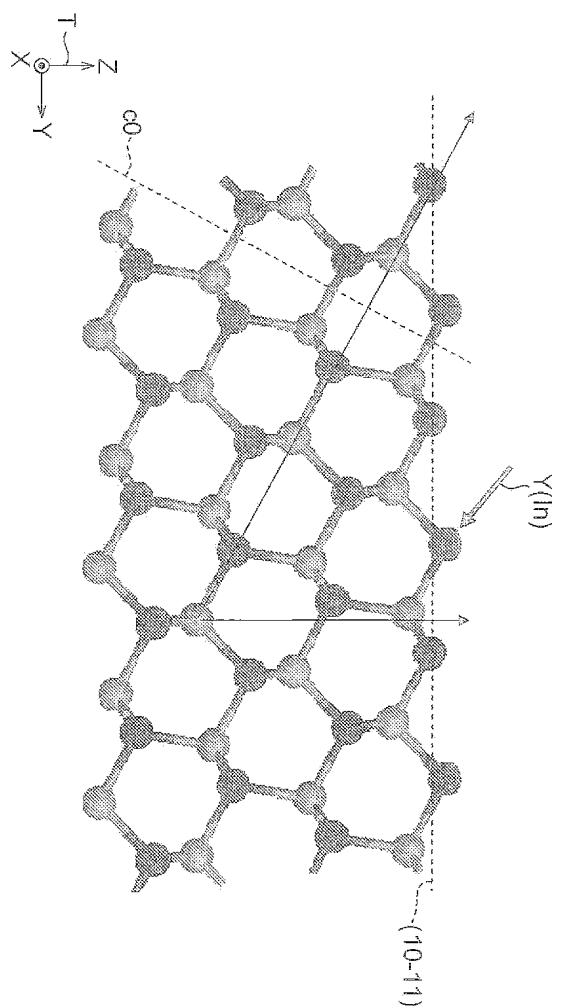

도 26은 예로서 {10-11}면의 표면 원자 배열을 도시하는 도면이다.

도 27은 예로서 m축 방향으로 45도 정도 기울인 면의 성장 표면의 원자 배열을 도시하였다.

도 28은 {10-11}면과 m면으로부터 형성되는 마이크로 스텝으로 이루어지는 성장 표면을 도시하는 도면이다.

도 29는, 예로서 c면을 m축 방향으로 오프각 75도로 기울인 면의 표면 원자 배열을 도시하는 도면이다.

도 30은 In 혼입과 오프각 사이의 관계를 도시한 도면이다.

도 31은 In 혼입, In 편석, 및 피에조 전계에 대해서, 각각의 면 및 각도 범위의 특징을 나타내는 도면이다.

도 32는 In 혼입, In 편석, 및 피에조 전계에 대해서, 상세한 각각의 면 및 각도 범위의 특징을 나타내는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0043]

본 발명의 지견은, 예시로서 나타낸 첨부 도면을 참조하고 이하의 상세한 기술을 고려함으로써 용이하게 이해할 수 있다. 이어서, 첨부 도면을 참조하면서, 본 발명의 GaN계 반도체 광소자, GaN계 반도체 광소자를 제작하는 방법, 에피택셜 웨이퍼 및 GaN계 반도체 영역을 성장시키는 방법에 따른 실시형태를 설명한다. 가능한 경우에는, 동일한 부분에는 동일한 부호를 붙인다. 또한 본 기술에서는, 육방정계 결정의 결정축을 나타내는 a1축, a2축, a3축, c축에서, 각 결정축의 플러스 방향과 역방향을 나타내는 표기에 관해서, 예컨대 [000-1]축은 [0001]축의 역방향이고, 역방향을 나타내기 위해 숫자(예컨대 「1」) 앞에 부호 「-」를 붙여 이용한다.

[0044]

도 1은 본 실시형태에 따른 GaN계 반도체 광소자의 구조를 개략적으로 도시하는 도면이다. GaN계 반도체 광소자(11a)로서는, 예컨대 발광 다이오드 등이 있다.

[0045]

GaN계 반도체 광소자(11a)는, 기판(13)과, GaN계 반도체 에피택셜 영역(15)과, 활성층(17)을 구비한다. 기판(13)은, 제1 GaN계 반도체로 이루어지고, 예컨대 GaN, InGaN, AlGaN 등으로 이루어질 수 있다. GaN은, 이원화합물인 GaN계 반도체이기 때문에, 양호한 결정 품질과 안정된 기판 주면을 제공할 수 있다. 또한, 제1 GaN 계 반도체는, 예컨대 AlN 등으로 이루어질 수 있다. 기판(13)의 c면은, 도 1에 도시된 평면(Sc)을 따라 연장되어 있다. 평면(Sc) 위에서는, 육방정계 GaN계 반도체의 결정축을 도시하기 위한 좌표계(CR)(c축, a축, m축)가 표시되어 있다. 기판(13)의 주면(13a)은, 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축(Cx)에 직교하는 면으로부터 상기 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있다. 경사각  $\alpha$ 는, 기판(13)의 주면(13a)의 법선 벡터(VN)와 기준축(Cx)이 이루는 각도에 의해 규정되고, 이 각도  $\alpha$ 는, 본 실시예에서는, 벡터 VC+와 벡터 VN이 이루는 각과 같다. GaN계 반도체 에피택셜 영역(15)은, 주면(13a) 위에 마련되어 있다. GaN계 반도체 에피택셜 영역(15)은 하나 또는 복수의 반도체층을 포함할 수 있다. GaN계 반도체 에피택셜 영역(15) 위에는, 활성층(17)이 마련되어 있다. 활성층(17)은, 하나 이상의 반도체 에피택셜층(19)을 포함한다. 반도체 에피택셜층(19)은, GaN계 반도체 에피택셜 영역(15) 위에 마련되어 있다. 반도체 에피택셜층(19)은, 인듐을 함유하는 제2 GaN계 반도체로 이루어지고, 예컨대 InGaN, InAlGaN 등으로 이루어진다. 반도체 에피택셜층(19)의 막 두께 방향은, 기준축(Cx)에 대하여 경사져 있다. 이 기준축(Cx)은, 제1 GaN계 반도체의 [0001]축 방향, 또는 [000-1]축 방향을 향할 수 있다. 본 실시예에서는, 기준축(Cx)은 벡터 VC+로 나타내는 방향을 향하고 있고, 이 결과, 벡터 VC-는 [000-1]축 방향을 향하고 있다.

[0046]

이 GaN계 반도체 광소자(11a)에 의하면, 상기한 경사각의 기판(13)에서, 그 주면(13a)은, 도 1에 도시되는 폭이 좁은 복수의 테라스를 포함하는 표면 모폴로지(M1)로 이루어진다. 또한, 기판(13) 위에는 GaN계 반도체 에피택셜 영역(15)이 마련되어 있기 때문에, GaN계 반도체 에피택셜 영역(15)의 결정축은, 기판(13)의 결정축을 이어 받는다. 이로 인해, GaN계 반도체 에피택셜 영역(15)의 주면(15a)도, 기준축(Cx)에 직교하는 면으로부터 m축 방향으로 63도 이상 80도 미만의 범위의 각도로 경사져 있고, GaN계 반도체 에피택셜 영역(15)의 주면(15a)도, 폭이 좁은 복수의 테라스를 포함하는 표면 모폴로지(M2)를 갖는다. 이들 테라스의 배열은 마이크로

스텝을 구성한다. 상기한 각도 범위의 테라스의 폭이 좁기 때문에, 복수의 테라스에 걸쳐 In 조성의 불균일은 발생하지 않는다. 그러므로 In 편석에 따른 발광 특성의 저하가 억제된다.

[0047] 또한, 테라스 구조가 c축으로부터의 경사각에 관계하고 있기 때문에, 이 경사각이 제1 GaN계 반도체의 (000-1)면을 기준으로 규정되는 기판과, 이 경사각이 제1 GaN계 반도체의 (000-1)면을 기준으로 규정되는 기판 모두에서, 발광 특성의 저하가 억제된다. 즉, 기준축(Cx)은 제1 GaN계 반도체의 [0001]축 및 [000-1]축 중 어느 하나의 방향을 향하고 있어도, 발광 특성의 저하가 억제된다.

[0048] GaN계 반도체 광소자(11a)에서는, 기판(13)의 주면(13a)은, 상기 제1 GaN계 반도체의 m축 방향으로 기준축에 직교하는 면으로부터 70도 이상 80도 미만의 범위의 각도로 경사져 있는 것이 좋다. 이 각도 범위의 기판 주면(13a)은, 폭이 좁은 복수의 테라스를 더 갖는다.

[0049] GaN계 반도체 광소자(11a)에 의하면, 활성층(17)에서의 In 편석에 따른 발광 특성의 저하가 억제된다.

[0050] 도 1을 참조하면, 좌표계(S)가 도시되어 있다. 기판(13)의 주면(13a)은 Z축 방향을 향하고 있고, 또한 X 방향 및 Y 방향으로 연장되어 있다. X축은 a축 방향을 향하고 있다.

[0051] GaN계 반도체 에피택셜 영역(15)은, 하나 또는 복수의 제1 도전형 GaN계 반도체층을 포함할 수 있다. 본 실시 예에서는, GaN계 반도체 에피택셜 영역(15)은, Z 방향으로 배열된 n형 GaN 반도체층(23) 및 n형 InGaN 반도체 층(25)을 포함하고 있다. n형 GaN 반도체층(23) 및 n형 InGaN 반도체층(25)이, 기판(13)의 주면(13a)에 에피택셜 성장되기 때문에, n형 GaN 반도체층(23)의 주면(23a) 및 n형 InGaN 반도체층(25)의 주면(25a)[본 실시예에서는, 표면(15a)과 등가]도, 각각, 테라스 구조를 갖는 모폴로지(M3, M2)를 갖는다.

[0052] 모폴로지(M1, M2, M3)는 c축 경사의 방향으로 배열된 복수의 마이크로 스텝을 갖고 있고, 이를 마이크로 스텝은, 경사 방향에 교차하는 방향으로 연장되어 있다. 마이크로 스텝의 주요 구성면은, 적어도 m면 및 (10-11)면을 포함한다. 상기한 구성면 및 스텝단에서는, In의 혼입이 양호하다.

[0053] GaN계 반도체 광소자(11a)는, 활성층(17) 위에 마련된 GaN계 반도체 영역(21)을 구비할 수 있다. GaN계 반도체 영역(21)은, 하나 또는 복수의 제2 도전형 GaN계 반도체층을 포함할 수 있다. GaN계 반도체 영역(21)은, Z 방향으로 배열된 전자 블록층(27) 및 컨택트층(29)을 포함한다. 전자 블록층(27)은, 예컨대 AlGaN으로 이루어질 수 있고, 또한 컨택트층(29)은, 예컨대 p형 GaN 또는 p형 AlGaN으로 이루어질 수 있다.

[0054] GaN계 반도체 광소자(11a)에서는, 활성층(17)은 370 nm 이상의 발광 파장을 생성하도록 마련되는 것이 좋다. 370 nm 이상의 파장의 광을 발생하는 활성층을 달성하는 인듐 조성의 범위에서, In 편석을 작게 할 수 있다. 또한, 활성층(17)은 650 nm 이하의 발광 파장을 생성하도록 마련되는 것이 좋다. 650 nm 이상의 발광 파장을 발생하는 활성층에서는, 반도체 에피택셜층의 인듐 조성이 크기 때문에, 원하는 결정 품질의 반도체 에피택셜층이 잘 얻어지지 않는다.

[0055] 활성층(17)은, 양자 우물 구조(31)를 가질 수 있고, 이 양자 우물 구조(31)는, 미리 정해진 축(Ax) 방향으로 교대로 배치된 우물층(33) 및 장벽층(35)을 포함한다. 본 실시예에서는, 우물층(33)은 반도체 에피택셜층(1-9)으로 이루어지고, 우물층(33)은 예컨대 InGaN, InAlGaN 등으로 이루어진다. 또한, 장벽층(35)은 GaN계 반도체로 이루어지고, GaN계 반도체는, 예컨대 GaN, InGaN, AlGaN 등으로 이루어질 수 있다. n형 GaN계 반도체층(23, 25), 활성층(17) 및 GaN계 반도체층(27, 29)은 미리 정해진 축(Ax) 방향으로 배열된다. 기준축(Cx)의 방향은 미리 정해진 축(Ax)의 방향과 상이하다.

[0056] 이 GaN계 반도체 광소자(11a)에 의하면, 단층막으로 이루어지는 반도체 에피택셜층뿐만 아니라, 양자 우물 구조(31)에서 작은 In 편석이 달성되고 있다.

[0057] GaN계 반도체 광소자(11a)는, 컨택트층(29) 위에 설치된 제1 전극(37)(예컨대 애노드)을 포함할 수 있고, 제1 전극(37)은, 컨택트층(29)을 덮는 투명 전극을 포함할 수 있다. 투명 전극으로서는, 예컨대 Ni/Au을 이용할 수 있다. GaN계 반도체 광소자(11a)는, 기판(13)의 이면(13b) 위에 설치된 제2 전극(39)(예컨대 캐소드)을 포함할 수 있고, 제2 전극(39)은 예컨대 Ti/Al으로 이루어진다.

[0058] 활성층(17)은, 전극(37, 39)의 양단에 인가된 외부 전압에 응답하여 광(L1)을 생성하고, 본 실시예에서는 GaN 계 반도체 광소자(11a)는 면발광 소자를 포함한다. 이 활성층(17)에서는, 괴이조 전계가 작다.

[0059] 기판(13)에서의 a축 방향의 오프각( $A_{OFF}$ )은 유한의 값인 것이 좋다. a축 방향의 오프각( $A_{OFF}$ )은, 에피택셜 영역의 표면 모폴로지를 양호하게 한다. 이 오프각( $A_{OFF}$ )은 XZ면 내에서의 각도이다. 오프각( $A_{OFF}$ )의 범위는, 예컨

대 -3도 이상 +3도 이하의 범위에 있을 수 있고, 구체적으로는 오프각( $A_{OFF}$ )의 범위는, 예컨대 -3도 이상 -0.1도 이하 및 +0.1도 이상 +3도 이하의 범위에 있는 것이 바람직하다. 오프각( $A_{OFF}$ )의 범위가 예컨대 -0.4도 이상 -0.1도 이하 및 +0.1도 이상 +0.4도 이하의 범위에 있을 때, 표면 모폴로지가 더 양호하게 된다.

[0060] GaN계 반도체 광소자(11a)에서는, 활성층(17)은 480 nm 이상의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 또한, 활성층(17)은 600 nm 이하의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 63도 이상 80도 미만의 범위의 경사각은, 480 nm 이상 600 nm 이하의 발광 파장의 범위에서 유효하다. 이 파장 범위에 있는 장파장에서는, 큰 In 조성이 우물층에 필요하고, 큰 In 편석을 나타내는 면, 예컨대 c면이나 m면 및 (10-11)면 등에서는 발광 강도가 크게 저하된다. 한편, 본 실시형태의 각도 범위에서는, In 편석이 작기 때문에, 480 nm 이상의 장파장 영역에서도 발광 강도의 저하가 작다.

[0061] 도 2는, 본 실시형태에 따른 GaN계 반도체 광소자의 구조를 개략적으로 도시하는 도면이다. GaN계 반도체 광소자(11b)로서는, 예컨대 반도체 레이저 등이 있다. GaN계 반도체 광소자(11b)는, GaN계 반도체 광소자(11a)와 마찬가지로, 기판(13)과, GaN계 반도체 에피택셜 영역(15)과, 활성층(17)을 구비한다. 기판(13)의 c면은, 도 2에 도시된 평면(Sc)을 따라 연장되어 있다. 평면(Sc) 위에는, 좌표계(CR)(c축, a축, m축)가 도시되어 있다. 기판(13)의 주면(13a)은 상기 제1 GaN계 반도체의 c축을 따라 연장되는 기준축(Cx)에 직교하는 면으로부터 상기 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있다. 경사각  $\alpha$ 는, 기판(13) 주면(13a)의 법선 벡터(VN)과 기준축(Cx)이 이루는 각도에 의해 규정되고, 이 각도는, 본 실시 예에서는, 벡터 VC+와 법선 벡터 VN이 이루는 각과 같다. GaN계 반도체 에피택셜 영역(15)은, 주면(13a) 위에 마련되어 있다. 활성층(17)은, 적어도 하나의 반도체 에피택셜층(19)을 포함한다. 반도체 에피택셜층(19)은, GaN계 반도체 에피택셜 영역(15) 위에 마련된다. 반도체 에피택셜층(19)은 제2 GaN계 반도체로 이루어지고, 제2 GaN계 반도체는 구성 원소로서 인듐을 함유한다. 반도체 에피택셜층(19)의 막 두께 방향은, 기준축(Cx)에 대하여 경사져 있다. 이 기준축(Cx)은, 제1 GaN계 반도체의 [0001]축 방향, 또는 [000-1]축 방향을 향할 수 있다. 본 실시예에서는, 기준축(Cx)은 벡터 VC+로 나타내는 방향을 향하고 있고, 따라서 벡터 VC-는, [000-1]축의 방향을 향하고 있다. 또한, 도 2에도, 오프각( $A_{OFF}$ )이 도시되어 있고, 이 오프각( $A_{OFF}$ )은 XZ면 내에서의 각도이다.

[0062] 이 GaN계 반도체 광소자(11b)에 의하면, 기판(13)에서는, 그 주면(13a)은, 도 2에 도시되는 폭이 좁은 복수의 테라스를 포함하는 표면 모폴로지(M1)로 이루어진다. 또한, 기판(13) 위에는 GaN계 반도체 에피택셜 영역(15)이 마련되어 있다. GaN계 반도체 에피택셜 영역(15)의 결정축은, 기판(13)의 결정축을 이어 받는다. 이로 인해, GaN계 반도체 에피택셜 영역(15)의 주면(15a)도, 기준축(Cx)에 직교하는 면으로부터 m축 방향으로 63도 이상 80도 미만의 범위의 각도로 경사져 있다. 따라서, GaN계 반도체 에피택셜 영역(15)의 주면(15a)도, 폭이 좁은 복수의 테라스를 포함하는 표면 모폴로지(M2)를 갖는다. 이들 테라스의 배열은 마이크로 스텝을 구성한다. 상기한 각도 범위의 테라스의 폭이 좁기 때문에, 복수의 테라스에 걸쳐 In 조성의 불균일이 생기지 않는다. 그러므로 In 편석에 따른 발광 특성의 저하가 억제된다.

[0063] GaN계 반도체 광소자(11b)의 일 실시예에서, GaN계 반도체 에피택셜 영역(15)은, Ax축 방향(Z 방향)으로 배열된 n형 클래드층(41) 및 광 가이드층(43a)을 포함하고 있다. n형 클래드층(41)은, 예컨대 AlGaN 또는 GaN으로 이루어질 수 있고, 또한 광 가이드층(43a)은, 예컨대 언도핑 InGaN으로 이루어질 수 있다. n형 클래드층(41) 및 광 가이드층(43a)이, 기판(13)의 주면(13a)에 에피택셜 성장되기 때문에, n형 클래드층(41)의 주면(41a) 및 광 가이드층(43a)의 주면(43c)[본 실시예에서는, 표면(15a)과 등가]도, 각각, 테라스 구조를 갖는 표면 모폴로지를 갖는다. 상기한 표면 모폴로지는, c축의 경사 방향으로 배열된 복수의 마이크로 스텝을 갖고 있고, 이들 마이크로 스텝은, 경사 방향에 교차하는 방향으로 연장되어 있다. 마이크로 스텝의 주요 구성면은, 적어도 m면, (20-21)면 및 (10-11)면 등을 포함한다. 상기한 구성면 및 스텝단에서는, In의 혼입이 양호하다.

[0064] GaN계 반도체 광소자(11b)에서, GaN계 반도체 영역(21)은, Z 방향으로 배열된 광 가이드층(43b), 전자 블록층(45), 클래드층(47) 및 컨택트층(49)을 포함한다. 광 가이드층(43b)은, 예컨대 언도핑 InGaN으로 이루어질 수 있다. 전자 블록층(45)은, 예컨대 AlGaN으로 이루어질 수 있고, 클래드층(47)은, 예컨대 p형 AlGaN 또는 p형 GaN으로 이루어질 수 있으며, 또한 컨택트층(49)은, 예컨대 p형 GaN 또는 p형 AlGaN으로 이루어질 수 있다.

[0065] GaN계 반도체 광소자(11b)는, 컨택트층(49) 위에 설치된 제1 전극(51)(예컨대 애노드)을 포함할 수 있고, 제1 전극(51)은, 컨택트층(49)을 덮는 절연막(53)의 스트라이프장을 통해 컨택트층(49)에 접속된다. 제1 전극(51)으로서는, 예컨대 Ni/Au을 이용한다. GaN계 반도체 광소자(11b)는, 기판(13)의 이면(13b) 위에 설치된 제2 전극(55)(예컨대 캐소드)을 포함할 수 있고, 제2 전극(55)은 예컨대 Ti/AI으로 이루어진다.

- [0066] 활성층(17)은, 전극(51, 55)의 양단부에 인가된 외부 전압에 응답하여 광(L2)을 생성하고, 본 실시예에서 GaN 계 반도체 광소자(11b)는 단부면 발광 소자를 포함한다. 이 활성층(17)에서, 피에조 전계의 Z 성분[미리 정해진 축(Ax)의 방향에 관한 성분]은, p형 GaN계 반도체층(43a, 45, 47, 49)으로부터 n형 GaN계 반도체층(41, 43a)을 향하는 방향과 역방향이다. 상기 GaN계 반도체 광소자(11b)에 의하면, 피에조 전계의 Z 성분이, 전극(51, 55)의 양단에 인가된 외부 전압에 의한 전계의 방향과 역방향이기 때문에, 발광 파장의 시프트가 저감된다.

- [0067] GaN계 반도체 광소자(11a, 11b)에서는, 기판(13)에서의 a축 방향의 오프각( $A_{OFF}$ )은 유한의 값인 것이 좋다. a축 방향의 오프각( $A_{OFF}$ )은, 에피택셜 영역의 표면 모폴로지를 양호하게 한다. 오프각( $A_{OFF}$ )의 범위는, 예컨대 -3도 이상 +3도 이하의 범위에 있을 수 있고, 구체적으로는 오프각( $A_{OFF}$ )의 범위는, 예컨대 -3도 이상 -0.1도 이하 및 +0.1도 이상 +3도 이하의 범위에 있는 것이 좋다. 오프각( $A_{OFF}$ )의 범위가 예컨대 -0.4도 이상 -0.1도 이하 및 +0.1도 이상 +0.4도 이하의 범위에 있을 때, 표면 모폴로지가 더 양호하게 된다.

- [0068] GaN계 반도체 광소자(11a, 11b)에서, 활성층(17)은 480 nm 이상의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 또한, 활성층(17)은 600 nm 이하의 발광 파장을 생성하도록 마련되어 있는 것이 좋다. 63도 이상 80도 미만의 범위의 경사각은, 480 nm 이상 600 nm 이하의 발광 파장의 범위에서 유효하다. 이 정도의 파장이 되면, 우물층의 In 조성이 상당히 커지고, c면이나 m면 및 (10-11)면 등의 In 편석이 큰 면에서는, 발광 강도가 크게 저하된다. 한편, 이 각도 범위에서는, In 편석이 작기 때문에, 480 nm 이상의 장파장 영역에서도 발광 강도의 저하가 작다. 또한, 우물층 두께의 범위는, 예컨대 0.5 nm ~ 10 nm일 수 있다.  $In_xGa_{1-x}N$  우물층의 In 조성 X의 범위는, 예컨대 0.01 ~ 0.50일 수 있다.

- [0069] (실시예 1)

- [0070] GaN 웨이퍼(S1) 및 GaN 웨이퍼(S2)를 준비하였다. GaN 웨이퍼(S1)의 주면은 육방정계 GaN에서의 c면으로 이루어진다. GaN 웨이퍼(S2)의 주면은, 육방정계 GaN에서의 m축 방향에 c면으로부터 75도의 각도로 경사져 있고, 이 경사면은 (20-21)면으로서 표시된다. 이들 주면은 모두 경면 연마되어 있다. 웨이퍼(S2)의 주면에서는, -3도 이상 +3도 이하의 범위의 각도에서 (20-21)면으로부터 오프각이 분포되어 있다.

- [0071] GaN 웨이퍼(S1) 및 GaN 웨이퍼(S2) 위에, 유기 금속 기상 성장법에 의해, Si 도핑 n형 GaN층 및 언도핑 InGaN층을 에피택셜 성장시켜, 도 3에 도시되는 에피택셜 웨이퍼(E1, E2)를 제작하였다. 에피택셜 성장을 위한 원료로서, 트리메틸갈륨(TMG), 트리메틸인듐(TMI), 암모니아( $NH_3$ ), 실란( $SiH_4$ )을 이용하였다.

- [0072] 성장로 안에 웨이퍼(S1, S2)를 설치하였다. 이들 웨이퍼 위에 이하의 조건으로 에피택셜 성장을 하였다. 섭씨 1050도의 온도 및 27 kPa의 로내 압력에서,  $NH_3$ 와  $H_2$ 를 흘리면서 10분간 열처리하였다. 이 열처리 온도로서, 예컨대 섭씨 850도 이상 1150도 이하의 온도를 이용할 수 있다. 또한, 열처리의 분위기로서,  $NH_3$ 와  $H_2$  등의 조합을 이용할 수 있다. 이 열처리에 의한 표면 개질에 의해, 웨이퍼 S2의 표면에, 오프각에 의해 규정되는 테라스 구조가 형성된다.

- [0073] 이 열처리 후에, TMG,  $NH_3$ ,  $SiH_4$ 를 성장로에 공급하여, 섭씨 1000도에서 Si 도핑한 GaN층(61a, 61b)을 성장시켰다. GaN층(61a, 61b)의 두께는, 예컨대 2 마이크로미터이다. 계속해서, TMG, TMI,  $NH_3$ 를 성장로에 공급하여, 섭씨 750도의 기판 온도에서 언도핑 InGaN층(63a, 63b)을 성장시켰다. InGaN층(63a, 63b)의 두께는 20 nm 이다. 또한, 몰비는 V/III=7322이고, 성장로 압력은 100 kPa이다. 성막 후에, 성장로의 온도를 실온까지 내려, 에피택셜 웨이퍼(E1, E2)를 제작하였다.

- [0074] 에피택셜 웨이퍼(E1, E2)의 X선 회절 측정을 하였다. 스캔은  $\omega$ -2 $\Theta$  법을 이용하여 행해졌다. X선의 회절각이 결정의 격자 상수를 반영하기 때문에, 예컨대 InGaN 3원 혼정의 각 원소의 물분률을 측정할 수 있다.

- [0075] 또한, 에피택셜 웨이퍼(E1, E2)에서는, 웨이퍼 주면의 오프각이 서로 상이하기 때문에, X선 회절 측정을 할 때에, 각각의 웨이퍼 주면의 오프각에 맞춘 위치에, X선 입사 장치, 시료대, X선 검출 장치를 배치하였다.

- [0076] 구체적으로는, 에피택셜 웨이퍼 E1에서는 [0001] 방향으로 축을 세웠다. 회절 결과를 이론 계산과 피팅하여, InGaN층의 In 조성을 결정한다. 이 면방위에서는, 웨이퍼 주면의 법선 방향 [0001]과 측정의 축을 세우는 방향 [0001]이 일치하기 때문에, 이론 계산으로부터 얻어진 값을 그대로 실제 조성으로서 사용할 수 있다.

- [0077] 에피택셜 웨이퍼 E2에서는 [10-10] 방향으로 축을 세운다. 이와 같이 축을 세움으로써, 웨이퍼의 주면 (20-

21)면에 대하여 15도만큼 경사져 X선이 입사하기 때문에, X선 회절로부터의 값은, In 조성을 너무 작게 예측하고 있다. 이 때문에, 실험 결과를 이론 계산과 피팅할 때에, [10-10] 방향으로부터의 기울기에 따라 측정값을 보정해야 한다. 이 보정에 의해, InGaN중의 In 조성이 결정된다.

[0078] 도 4는 X선 회절 결과 및 이론 계산의 결과를 도시하는 도면이다. 도 4의 (a)를 참조하면, 에피택셜 웨이퍼 E1의 실험 결과 EX1 및 이론 계산 결과 TH1이 도시되어 있다. 도 4의 (b)를 참조하면, 에피택셜 웨이퍼 E2의 실험 결과 EX2 및 이론 계산 결과 TH2가 도시되어 있다. 에피택셜 웨이퍼 E1의 In 조성은 20.5 퍼센트이고, 한편 에피택셜 웨이퍼 E2의 In 조성은 19.6 퍼센트이다. 이 실험 결과는 GaN(20-21)면이 GaN의 c면에 비하여 동등하게 In이 흔입되는 것을 나타내고 있다. 이것은, 예컨대 발광 다이오드나, 반도체 레이저 다이오드 등의 광 디바이스의 제작에서, 높은 In 조성을 필요로 하는 장파장의 발광 소자에 유리하다. 또한, 동일한 In 조성다면, InGaN의 성장 온도를 높이는 것이 가능하고, 발광층의 결정성을 향상시킬 수 있다.

[0079] (실시예 2)

[0080] 도 5에 나타내는 공정에 따라서, 유기 금속 기상 성장법에 의해, 도 6에 도시되는 발광 다이오드 구조(LED1, LED2)의 에피택셜 웨이퍼를 GaN 웨이퍼(S3) 및 GaN 웨이퍼(S4) 위에 제작하였다. 에피택셜 성장을 위한 원료로서, 트리메틸갈륨(TMG), 트리메틸인듐(TMI), 트리메틸알루미늄(TMA), 암모니아(NH<sub>3</sub>), 실란(SiH<sub>4</sub>), 비스시클로펜타디에닐마그네슘(Cp<sub>2</sub>Mg)을 이용하였다.

[0081] GaN 웨이퍼 S3 및 S4를 준비하였다. GaN 웨이퍼 S3의 주면은 육방정계 GaN에서의 c면으로 이루어진다. 공정 S101에서는, 63도 내지 80도 미만의 경사각 범위 내의 경사각에 해당하는 GaN 웨이퍼 S4를 준비하였다. 본 실시예에서, GaN 웨이퍼 S4는, 육방정계 GaN에서의 m축 방향으로 c면으로부터 75도의 각도로 경사진 주면을 갖고, 이 경사면은 (20-21)면으로서 표시된다. 이들 주면은 모두 경면 연마되어 있다.

[0082] 웨이퍼 S3, S4 위에 이하의 조건으로 에피택셜 성장을 하였다. 우선, 공정 S102에서는, 웨이퍼 S3, S4를 성장로 안에 제공하였다. 공정 S103에서는, 섭씨 1050도의 온도 및 27 kPa의 로 내 압력에서, NH<sub>3</sub>과 H<sub>2</sub>를 흘리면서 10분간 열처리하였다. 이 열처리에 의한 표면 개질에 의해, 웨이퍼 S4의 표면에, 오프각에 의해 규정되는 테라스 구조를 형성하였다. 이 열처리 후에, 공정 S104에서는, GaN계 반도체 영역이 성장된다. 예컨대 섭씨 1000도에서, TMG, NH<sub>3</sub>, SiH<sub>4</sub>를 성장로에 공급하여, Si 도핑 GaN층(65b)을 성장시켰다. GaN층(65b)의 두께는 예컨대 2 마이크로미터이다. 이어서, 섭씨 850도의 기판 온도로, TMG, TMI, NH<sub>3</sub>, SiH<sub>4</sub>를 성장로에 공급하여, Si 도핑 InGaN층(67b)을 성장시켰다. InGaN층(67b)의 두께는 100 nm 이다. InGaN층(67b)의 In 조성은 예컨대 0.02이다.

[0083] 공정 S105에서는 활성층을 성장시킨다. 공정 S106에서는, 섭씨 870도의 기판 온도로, TMG, NH<sub>3</sub>을 성장로에 공급하여, 이 성장 온도 T1에서 언도핑 GaN 장벽층(69b)을 성장시켰다. GaN층(69b)의 두께는 15 nm이다. 공정 S107에서는, 성장 후에, 성장을 중단하여, 섭씨 870도로부터 섭씨 760도로 기판 온도를 변경한다. 변경 후에, 공정 S108에서는, 이 성장 온도 T2에서, TMG, TMI, NH<sub>3</sub>을 성장로에 공급하여, 언도핑 InGaN 우물층(71b)을 성장시켰다. InGaN 우물층(71b)의 두께는 3 nm이다. InGaN층(71b)의 In 조성은 예컨대 0.25이다. 우물층(71b)에서는, 발광 파장에 따라서 In 유량을 변경하고 있다. InGaN 우물층(71b)의 성장 후에, TMI의 공급을 정지하였다. 공정 S109에서는, TMG, NH<sub>3</sub>을 성장로에 공급하면서, 섭씨 760도로부터 섭씨 870도로 기판 온도를 변경하였다. 이 변경 중에도, 언도핑 GaN 장벽층(73b)의 일부가 성장되고 있다. 변경 후에, 공정 S110에서 언도핑 GaN 장벽층(73b)의 나머지를 성장시켰다. GaN 장벽층(73b)의 두께는 15 nm이다. 공정 S111에서는, 장벽층의 성장, 온도 변경, 우물층의 성장을 반복하여, InGaN 우물층(75b, 79b), GaN 장벽층(77b, 81b)을 형성하였다.

[0084] 공정 S112에서는, GaN계 반도체 영역이 성장된다. 예컨대, GaN 장벽층(81b)의 성장 후에, TMG의 공급을 정지하여, 기판 온도를 섭씨 1000도로 상승시켰다. 이 온도에서, TMG, TMA, NH<sub>3</sub>, Cp<sub>2</sub>Mg를 성장로에 공급하여, p형 Al<sub>0.18</sub>Ga<sub>0.82</sub>N 전자 블록층(83b)을 성장시켰다. 전자 블록층(83b)은 예컨대 20 nm였다. 이 후에, TMA의 공급을 정지하여, p형 GaN 컨택트층(85b)을 성장시켰다. p형 GaN 컨택트층(85b)은 예컨대 50 nm였다. 성막 후에, 성장로의 온도를 실온까지 내려, 에피택셜 웨이퍼(E4)를 제작하였다. 본 실시예에서의 p형 영역의 성장 온도는, c면 위에서의 p형 영역의 성장에 최적인 성장 온도에 비해 100도 정도 낮다. 발명자들의 실험에 의해, 이하의 것이 확인되었다. 본 오프각 범위 내의 기판 위에 성막된 활성층은 p층 성장시의 승온에 민감하여 열화되기 쉽고, c면에서의 p형 영역의 성장에 최적인 온도에서는, 특히 장파장의 활성층을 성장시켰을 때에 거시적인 암(暗) 영역이 넓어진다. 여기서, 암 영역은 형광 현미경상(像)에서의 비발광 영역을 의미한다. p층 성장 온도

도를 내림으로써, p층 성장시의 승온에 의한 암 영역의 확대를 막을 수 있었다.

[0085] 이어서, 웨이퍼 S3에 대해서도 동일한 성막 조건을 이용하여, Si 도핑 GaN층(두께: 2 마이크로미터)(65a), Si 도핑 InGaN층(두께: 100 nm)(67a), p형 AlGaN 전자 블록층(두께: 20 nm)(83a) 및 p형 GaN 컨택트층(두께: 50 nm)(85a)을 성장시켰다. 활성층은 InGaN 우물층(두께: 3 nm)(71a, 75a, 79a), GaN 장벽층(두께: 15 nm)(69a, 73a, 77a, 81a)을 포함한다. 컨택트층의 성장 후에, 성장로의 온도를 실온까지 내려, 에피택셜 웨이퍼(E3)를 제작하였다.

[0086] 공정 S113에서는 에피택셜 웨이퍼(E3, E4) 위에 전극을 형성하였다. 우선, 예칭(예컨대 RIE)에 의해, 메사 형상을 형성하였다. 메사 형상의 사이즈는 예컨대 한 변이 400  $\mu\text{m}$ 인 사각형이다. 이어서, p형 GaN 컨택트층(85a, 85b) 위에 p 투명 전극(Ni/Au)(87a, 87b)을 형성하였다. 이 후에, p 패드 전극(Ti/Au)을 형성하였다. n 전극(Ti/A1)(89a, 89b)을 웨이퍼(S3, S4)의 이면에 형성하였다. 전극 어닐링(예컨대 섭씨 550도로 1분)의 순서로 하였다. 이 공정에 의해, 발광 다이오드 구조(LED1, LED2)를 얻을 수 있었다.

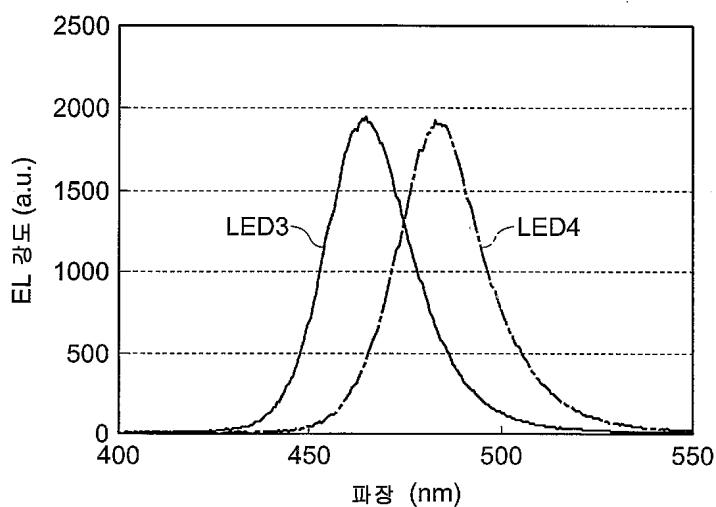

[0087] 발광 다이오드 구조(LED1, LED2)에 전류를 인가하여, 일렉트로 루미네센스 스펙트럼을 측정하였다. 전극 사이즈는 한 변 500 마이크로미터의 사각형이고, 인가 전류는 120 mA이다. 도 7은 발광 다이오드 구조(LED1, LED2)의 일렉트로 루미네센스 스펙트럼을 도시하는 도면이다. 스펙트럼( $\text{EL}_c$ ,  $\text{EL}_{M75}$ )이 도시되어 있다. 이들 스펙트럼의 피크 파장은 같은 정도이고, 스펙트럼  $\text{EL}_{M75}$ 의 피크 강도가 스펙트럼  $\text{EL}_c$ 의 피크 강도의 2배 이상이다. 또한 스펙트럼  $\text{EL}_{M75}$ 의 반치전폭이 스펙트럼  $\text{EL}_c$ 의 반치전폭의 절반 이하이다. 발광 다이오드 구조 LED2의 광 출력이 높고, 또한 반치전폭이 작다. 이들은, 우수한 색 순도를 나타내고, 또한 다른 색의 발광과 혼합했을 때의 연색성(演色性)을 높일 수 있다. LED 모드에서의 발광의 반치전폭이 작고, 이것은 레이저 다이오드의 임계값을 낮추는 데에 매우 유효하다.

[0088] 도 8은, 에피택셜 웨이퍼(E3, E4)에서의 캐소드 루미네센스(CL)상을 도시하는 도면이다. 도 8의 (a)를 참조하면, 에피택셜 웨이퍼(E3)의 캐소드 루미네센스상이 표시되어 있다. 도 8의 (a)의 발광상에는 열룩이 있고, 발광에 기여하지 않는 암 영역이 넓은 것을 알 수 있다. 이 발광의 불균일은 에피택셜 웨이퍼 E3의 활성층에서의 In 편석에 기인하는 것으로 생각된다. c면 기판을 이용하는 에피택셜 웨이퍼에서는, 발광 파장이 장파가됨에 따라서, 발광 불균일의 정도가 현저해진다. 이로 인해 c면 기판을 이용하는 발광 소자에서는, 발광이 장파장이 될수록 광 출력이 저하되고, 또한 발광스펙트럼의 반치전폭이 커진다.

[0089] 도 8의 (b)를 참조하면, 에피택셜 웨이퍼(E4)의 캐소드 루미네센스상이 도시되어 있다. 도 8의 (b)의 발광상은, 도 8의 (a)의 발광상에 비해 발광의 균일성이 우수하다. 그러므로 에피택셜 웨이퍼 E4에서는, InGaN층의 In 편석이 작은 것으로 생각된다. 이 때문에, 발광 소자의 발광 강도가 크고, 발광 반치폭도 작아진다. 또한, 웨이퍼 S4 위에 제작된 발광 소자에서는, 장파장의 발광에서의 광 출력의 저하가 작고, 또한 장파장의 발광 스펙트럼에서의 반치폭의 증대도 작다.

[0090] 도 9는, 발광 다이오드 구조(LED1, LED2)에 있어서 발광 파장과 전류 주입량의 관계의 측정을 도시하는 도면이다. 도 9를 참조하면, 발광 다이오드 구조 LED1에서는, 전류 주입량을 늘림에 따라 발광 파장이 점차 단파장으로 시프트된다. 이에 대하여, 발광 다이오드 구조 LED2에서는, 적은 전류 주입량일 때 발광 파장이 약간 단파장으로 시프트된 후에는, 발광 파장은, 전류량의 증가에 대하여 거의 변화하지 않는다. 이것은, 발광 다이오드에의 인가 전류량을 바꿔 발광 다이오드의 발광 강도를 변경할 때에, 발광 파장의 변동이 거의 없다는 것을 나타내는 것이다. 즉, 발광 다이오드 구조 LED2에서는, LED 모드에서의 발광 피크 파장의 전류 의존성이 저감된다.

[0091] 광 여기에 의한 발광 측정에서는, 발광 다이오드 구조 LED1(c면)의 발광 파장은 535 nm이고, 발광 다이오드 구조(75도 오프) LED2의 발광 파장은 500 nm였다. 광 여기되어 있는 발광 다이오드 구조의 내부 상태는, 매우 적은 전류가 주입되어 있는 발광 다이오드 구조의 내부 상태에 상당한다.

[0092] 전류 주입에 대한 발광 파장의 의존성과 광 여기에 의한 발광 측정 결과는 이하의 사항을 의미한다. 발광 다이오드 구조 LED2에서는, 인가 전압을 서서히 크게 했을 때, 매우 작은 발광(실용적인 면에서는 「발광 전」)에서 발광 파장의 시프트가 실질적으로 완료되어 있고, 충분한 강도의 발광이 생긴 후에는 발광 파장이 거의 시프트되지 않는다.

[0093] c면 위의 활성층에서의 피에조 전계는, GaN계 반도체의 m축 방향으로 c면으로부터 63도 이상 80도 미만의 범위의 경사각으로 경사진 GaN계 반도체면 위에 마련된 활성층에서의 피에조 전계에 비해 크다. 도 9에 도시되는 특성으로부터, 발광 다이오드 구조 LED2에서의 피에조 전계의 방향은, 발광 다이오드 구조 LED1에서의 피

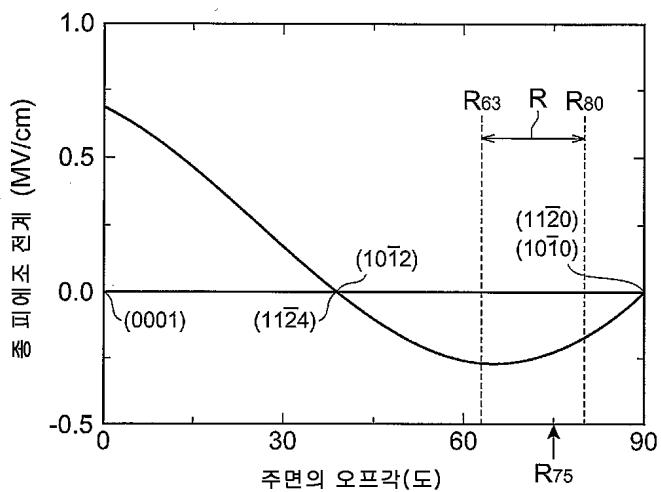

예조 전계의 방향과 반대이다. 또한, 전류 주입시의 전계 방향은, 발광 다이오드 구조 LED2에서의 피에조 전계의 방향과 반대이다. 도 10은 비특허문헌 4 및 5에 언급한 계산 결과를 도시하는 도면이다. 도 10의 (a) 및 (b)에서의 피에조 전계를 도시하는 곡선에서 플러스/마이너스가 상이한 것은, 전계 방향의 정의의 문제 때문이다. 또한, 곡선의 기울기나 곡률이 상이한 것은, 계산에 이용한 파라미터가 상이하기 때문이다.

[0094] (실시예 3)

[0095] c면으로부터  $\pi$ 축 방향으로 75도의 각도로 경사진 주면을 갖는 웨이퍼 S5, S6 위에, 발광 다이오드 구조(LED3, LED4)를 제작하였다. 발광 다이오드 구조(LED3, LED4)의 발광 파장은 서로 상이하다. 발광 다이오드 구조(LED3, LED4)에서의 발광 파장의 변경은, 우물층의 In 조성을 변경함으로써 행해졌다. In 조성의 변경을 위해, 우물층의 성장 시에 In 원료(예컨대 TMI)의 유량을 변경하였다. 이 활성층의 변경을 제외하고, 발광 다이오드 구조(LED3, LED4)의 제작은 발광 다이오드 구조 LED2와 동일하다.

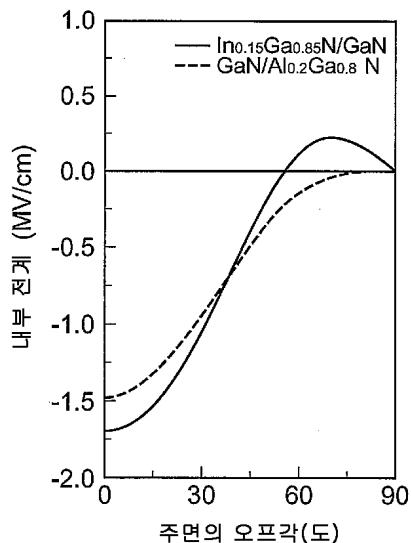

[0096] 도 11은, 상이한 In 조성을 갖는 우물층의 발광 다이오드 구조의 일렉트로 루미네센스를 도시하는 도면이다. 발광 다이오드 구조 LED3의 우물층은 예컨대  $In_{0.16}Ga_{0.84}N$ 이고, 발광 다이오드 구조 LED4의 우물층은 예컨대  $In_{0.20}Ga_{0.80}N$ 이다. 발광 다이오드 구조 LED3(파크 파장: 460 nm) 및 발광 다이오드 구조 LED4(파크 파장: 482 nm)를 비교하면, 이들 파장에서 발광 강도의 차나 반치전폭의 차가 관찰되지 않는다. 이것은, 고효율의 장파장의 발광 소자를 제작하는 데에 매우 좋은 것이다.

[0097] 도 12는,  $InGaN$  우물층의 발광 다이오드 및  $AlGaNInP$  우물층의 발광 다이오드에서의 외부 양자 효율 및 인간의 시감도 곡선을 도시하는 도면이다. 장파장의 광을 발생하는 발광 다이오드 구조를 얻기 위해, 큰 In 조성의 우물층을 제작한다. 발명자들의 의견에 의하면, 도 12에 도시되는 바와 같이, c면 GaN 기판 위의 발광 다이오드 구조에서는,  $InGaN$  우물층의 In 조성의 증가에 따라  $InGaN$ 의 결정성이 저하한다. 이러한 결정성의 저하에 의해, 발광 강도는 저하되고, 스펙트럼의 반치전폭도 커진다. 특히 500 nm를 초과하는 장파장 영역에서는, 높은 외부 양자 효율의 발광 다이오드 등의 발광 소자를 제작할 수 없다.

[0098] 이미 설명한 바와 같이, 발광 소자는 In 원소를 포함하는 GaN계 반도체 우물층을 포함하고 있고, 이 GaN계 반도체 우물층은, GaN계 반도체의  $\pi$ 축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 c면을 기준으로서 경사진 GaN계 반도체면 위에 성장되어 있다. 이 발광 소자에 의하면, 발광 강도의 차나 반치전폭의 차가 관찰되지 않는다. 이것은, 고효율의 장파장의 발광 소자를 제작하는 데에 매우 좋은 것이다.

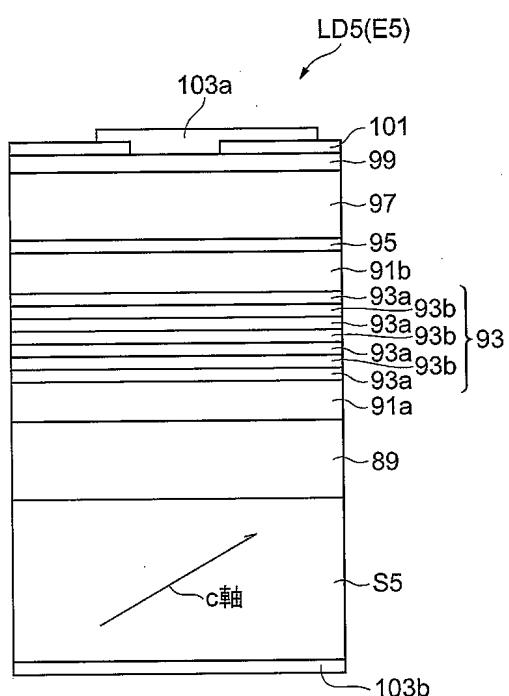

[0099] (실시예 4)

[0100] GaN 웨이퍼 S4와 동등한 품질인 GaN 웨이퍼 S5 위에, 도 13에 도시되는 레이저 다이오드 구조(LD1)의 에피택셜 웨이퍼를 제작하였다. 에피택셜 성장을 위한 원료로서, 트리메틸갈륨(TM), 트리메틸인듐(TMI), 트리메틸알루미늄(TMA), 암모니아( $NH_3$ ), 실란( $SiH_4$ ), 비스시클로펜타디에닐마그네슘( $Cp_2Mg$ )을 이용하였다.

[0101] 63도 내지 80도 미만의 경사각 범위 내의 경사각에 해당하는 GaN 웨이퍼 S5가 준비되었다. GaN 웨이퍼 S5는, 육방정계 GaN에서의  $\pi$ 축 방향으로 c축에 직교하는 평면으로부터 75도의 각도로 경사진 주면을 갖고 있고, 이 경사면은 (20-21)면으로서 나타난다. 이 주면도 경면 연마되어 있다. 웨이퍼 S5 위에 이하의 조건으로 에피택셜 성장을 하였다.

[0102] 우선, 웨이퍼 S5를 성장로 안에 제공하였다. 섭씨 1050도의 온도 및 27 kPa의 내 압력에서,  $NH_3$ 와  $H_2$ 를 흘리면서 10분간 열처리하였다. 이 열처리에 의한 표면 개질에 의해, 웨이퍼 S5 표면에, 오프각에 의해 규정되는 테라스 구조가 형성된다. 이 열처리 후에, GaN계 반도체 영역이 성장된다. 예컨대, 섭씨 1150도에 있어서, TMG, TMA,  $NH_3$ ,  $SiH_4$ 를 성장로에 공급하여, n형 클래드층(89)을 성장시켰다. n형 클래드층(89)은, 예컨대 Si 도핑  $Al_{0.04}Ga_{0.96}N$ 층이고, 그 두께는 예컨대 2 마이크로미터이다.

[0103] 이어서, 섭씨 830도의 기판 온도로, TMG, TMI,  $NH_3$ 를 성장로에 공급하여, 광 가이드층(91a)을 성장시켰다. 광 가이드층(91a)은, 예컨대 언도핑의  $In_{0.02}Ga_{0.98}N$ 층으로 이루어지고, 그 두께는 100 nm이다.

[0104] 이어서, 활성층(93)을 성장시킨다. 섭씨 870도의 기판 온도에서, TMG,  $NH_3$ 를 성장로에 공급하여, 이 성장 온도 T1에서 GaN계 반도체 장벽층(93a)을 성장시켰다. 장벽층(93a)은 예컨대 언도핑 GaN이고, 그 두께는 15 nm이다. 장벽층의 성장 후에, 성장을 중단하고, 섭씨 870도로부터 섭씨 830도로 기판 온도를 변경한다. 변경 후의 성장 온도 T2에서, TMG, TMI,  $NH_3$ 를 성장로에 공급하여, 언도핑  $InGaN$  우물층(93b)을 성장시켰다. 그 두께

는 3 nm이다. 우물층의 성장 후에, TMI의 공급을 정지하고, TMG, NH<sub>3</sub>를 성장로에 공급하면서, 섭씨 830도로부터 섭씨 870도로 기판 온도를 변경하였다. 이 변경 중에도, 언도핑 GaN 장벽층(93a)의 일부가 성장되고 있다. 온도의 변경이 완료된 후에, 언도핑 GaN 장벽층(93a)의 나머지를 성장시켰다. GaN 장벽층(93a)의 두께는 15 nm이다. 이어서, 장벽층의 성장, 온도 변경, 우물층의 성장을 반복하여, InGaN 우물층(93b), GaN 장벽층(93a)을 형성하였다.

[0105] 섭씨 830도의 기판 온도로, TMG, TMI, NH<sub>3</sub>를 성장로에 공급하고, 활성층(93) 위에 광 가이드층(91b)을 성장시켰다. 광 가이드층(91b)은, 예컨대 언도핑의 In<sub>0.02</sub>Ga<sub>0.98</sub>N층으로 이루어지고, 그 두께는 100 nm이다.

[0106] 광 가이드층(91b) 위에, GaN계 반도체 영역이 성장된다. 광 가이드층(91b)의 성장 후에, TMG 및 TMI의 공급을 정지하여, 기판 온도를 섭씨 1100도로 상승시켰다. 이 온도에서, TMG, TMA, NH<sub>3</sub>, Cp<sub>2</sub>Mg을 성장로에 공급하여, 전자 블록층(95) 및 p형 클래드층(97)을 성장시켰다. 전자 블록층(95)은 예컨대 Al<sub>0.12</sub>Ga<sub>0.88</sub>N이고, 그 두께는 예컨대 20 nm였다. p형 클래드층(97)은 예컨대 Al<sub>0.06</sub>Ga<sub>0.94</sub>N이고, 그 두께는 예컨대 400 nm였다. 이 후에, TMA의 공급을 정지하여, p형 컨택트층(99)을 성장시켰다. p형 컨택트층(99)은 예컨대 GaN으로 이루어지고, 그 두께는 예컨대 50 nm였다. 성막 후에, 성장로의 온도를 실온까지 내려, 에피택셜 웨이퍼 E5를 제작하였다.

[0107] 에피택셜 웨이퍼 E5 위에 전극을 형성하였다. 우선, 실리콘 산화막 등의 절연막을 퇴적하고, 이 절연막에 포토리소그래피 및 에칭에 의해 컨택트창을 형성하였다. 컨택트창은, 예컨대 스트라이프 형상이고, 그 폭은 예컨대 10 마이크로미터이다. 이어서, p형 GaN 컨택트층(99) 위에 p 전극(Ni/Au)(103a)을 형성하였다. 이 후에, p 패드 전극(Ti/Au)을 형성하였다. n 전극(Ti/Al)(103b)을 웨이퍼 E5의 이면에 형성하였다. 전극 어닐링(예컨대 섭씨 550도에서 1분)의 단계를 행하여 기판 생산물을 제작하였다. 이 공정 후에, 800 마이크로미터 간격으로 기판 생산물을 벽개하여, 개인 가이드형 레이저 다이오드(LD1)가 얻어졌다. 벽개면으로서는 a면을 이용하였다. 이것은, m축 방향의 오프 기판에서는, m면이 경사져 있어, 공진기 단부면으로서는 부적합하기 때문이다.

[0108] 임계값 전류는 9 kAcm<sup>-2</sup>였다. 이 때의 발진 파장은 405 nm였다. 이 반도체 레이저에서는, LED 모드에서의 발광의 스펙트럼의 반치전폭이 작다. 또한, 이 반도체 레이저의 InGaN층의 In 편석은 작다. 이 LED 모드에서의 발광이, 도 1 및 도 2에서의 XY면 내의 Y 방향에 수직인 방향으로 편광되어 있기 때문에, 상기한 임계값 전류는, c면 위에 형성된 유사한 구조의 반도체 레이저에 비해 크다. 이 방향의 편광은, a면 벽개에 의해 X 방향으로 공진기를 제작했을 때는, 임계값 전류를 증가시키는 편광 방향이 된다. 또한, 이 광의 편광도(P)는 0.15 정도였다.

[0109] 따라서 도 1 및 도 2에서의 Y 방향에 수직인 면을 드라이 에칭[예컨대 반응성 이온 에칭(RIE)]에 의해 형성하고, 이 에칭면을 공진기면으로 하는 공진기를 제작하였다. 이 공진기의 방향에 있어서는, Y 방향으로 공진기가 제작되기 때문에, LED 모드로 본 플러스의 편광도가, 임계값 전류의 저감에 관련하여 유리하게 작용한다. 이 반도체 발광 소자의 임계값 전류는 5 kAcm<sup>-2</sup>였다. 그러므로 공진기를 적절한 방향으로 향하게 하는 것에 의해, 임계값 전류를 내릴 수 있었다.

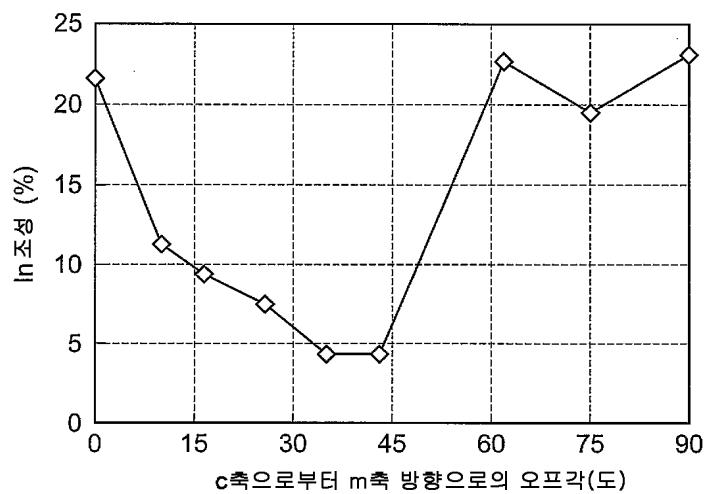

[0110] (실시예 5)

[0111] 여러 오프각의 GaN 웨이퍼 위에 InGaN을 퇴적하여, 그 InGaN의 In 조성을 측정하였다. 도 14는 c축으로부터 m축 방향으로 취한 여러 경사각(오프각)을 갖는 GaN 주면 위에 퇴적된 InGaN의 In 조성과 오프각의 관계를 도시하는 도면이다. 우선, 플롯 P1 ~ P4에서의 오프각을 도시한다:

[0112] 플롯 P1: 63도

[0113] 플롯 P2: 75도

[0114] 플롯 P3: 90도(m면)

[0115] 플롯 P4: 43도

[0116] 플롯 P5: 0도(c면)

[0117] In 조성은, 플롯 P5(c면)로부터 플롯 P4까지 오프각의 증가와 함께 단조롭게 감소하고 있다. 한편, 플롯 P1, P2에서는, 플롯 P5(c면)과 동등한 In 혼입을 나타내고 있다. 플롯 P3(m면)도, 우수한 In 혼입을 나타내지만,

80도 이상의 오프각에서는 In 편석이 커지고, 장파장화에 수반되는 발광 강도의 저하 등의 문제점이 있다.

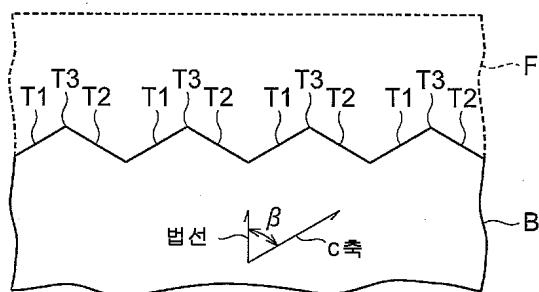

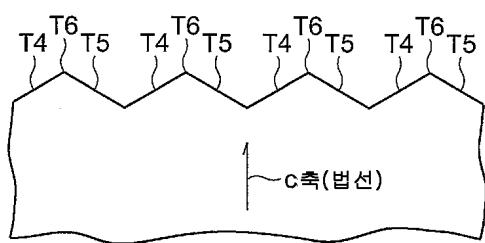

[0118] 도 15의 (a)를 참조하면서, 63도 이상 80도 미만의 범위 내의 오프각  $\beta$ 를 갖는 GaN계 반도체면 위에 In 함유의 GaN계 반도체가 퇴적되는 것을 모식적으로 설명한다. 상기한 경사각 범위의 오프각의 반도체 표면, 예컨대 (20-21)면 부근의 표면에는, (10-11)면으로 이루어지는 테라스 T1과 m면으로 이루어지는 테라스 T2가 도시되어 있다. 반도체 표면은 이들 테라스 T1, T2로 이루어지는 미세한 스텝으로 구성된다. 발명자들의 실험에 의하면, m면뿐만 아니라 (10-11)면에서의 In 혼입은, c면에서의 In 혼입과 동등하거나, 또는 c면에서의 In 혼입보다 우수하다. 또한, In 혼입을 높이기 위해서는, InN의 섬형 성장을 가능하게 하는 충분한 크기의 테라스 폭이 필요하다.

[0119] 10도 내지 50도 범위의 오프각에서는, (10-11)면으로 이루어지는 테라스 T4와 c면으로 이루어지는 테라스 T5가 나타나 있다. 반도체 표면은 이들 테라스 T4, T5로 이루어지는 미세한 스텝으로 구성된다. 이 각도 범위에서는, 오프각이 커질수록 테라스 T4, T5의 폭이 작아지고, 이로 인해, 도 14에 도시되는 바와 같이, 10도 내지 50도 범위의 오프각의 반도체 표면에서는, In의 혼입이 작다. 이것은, c면과 (10-11)면으로 이루어지는 스텝이 반도체 표면에 형성되어 있으면, 테라스 T4, T5 위에서 In이 혼입된다. 그러나, 테라스 T4, T5로 구성되는 테라스 에지(스텝단) T6에 나타나는 화학 결합의 본드의 시점으로부터 검토하면, 테라스 에지 T6에서는 In 원자가 혼입된다.

[0120] 한편, 발명자들의 실험에 의하면, 테라스 T1, T2로 이루어지는 마이크로 스텝 구조에서는, In의 혼입 능력이 양호하다. 이로 인해, 테라스 T1, T2 위뿐만 아니라, 테라스 T1, T2로 구성되는 테라스 에지(스텝단) T3에서도 In이 효율적으로 혼입된다. 테라스 에지 T3에 나타나는 화학 결합의 본드의 시점으로부터의 검토에 의해 뒷받침된다. 혼입된 In은, 암모니아 분위기 중에서의 열처리(우물층의 성장과 장벽층의 성장 사이의 온도 상승) 공정에서, 반도체 표면으로부터 이탈할 가능성성이 낮아진다. 그러므로 예컨대 InGaN으로 이루어지는 우물층을 성장 온도 T1에서 성장시킨 후에 장벽층의 성장 온도 T2로 승온할 때에 우물층의 표면을로 내 분위기에 노출시켜도, 우물층 표면으로부터 이탈하는 In의 양을 저감할 수 있다.

[0121] 50도를 초과하는 오프각의 범위이며 실시예의 (20-21)면으로 대표되는 반도체 표면은, 우수한 In 혼입 능력을 나타낸다. 또한, 이 반도체 표면에 성장된 활성층으로부터의 발광상은, 양호한 균일성을 갖는다. 그 발광 스펙트럼의 반치폭은 좁고, 발광 소자의 광출력도 높다. 또한, 장파장의 발광을 가능하게 하기 위해 In 조성을 증가시킨 우물층을 제작하여도, 발광 효율의 저하가 작다. 그러므로 본 실시형태에 따른 광소자 및 그 제작방법은, InGaN층을 포함하는 광소자를 실현할 때에, 매우 유효한 특성을 갖는다.

[0122] GaN계 반도체막을 성장시키는 방법은, 도 15의 (a)에 도시되는 바와 같이, 복수의 마이크로 스텝을 갖는 표면이 있는 GaN계 반도체 영역(B)을 준비하는 공정과, 구성 원소로서 In을 포함하는 GaN계 반도체막(F)을 마이크로 스텝 표면 위에 성장시키는 공정을 구비한다. 마이크로 스텝은, 주요 구성면으로서 적어도 m면 및 (10-11)면을 포함한다. 또는 GaN계 반도체막을 성장시키는 방법은, GaN계 반도체로 이루어지고 주면을 갖는 반도체 에피택셜 영역(B)을 성장시키는 공정과, 구성 원소로서 In을 함유하는 GaN계 반도체막(F)을 반도체 에피택셜 영역(B)의 주면 위에 성장시키는 공정을 구비한다. 반도체 에피택셜 영역(B)의 주면은, GaN계 반도체의 c축을 따라 연장되는 기준축에 직교하는 면으로부터 상기 제1 GaN계 반도체의 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사져 있다.

[0123] 마이크로 스텝 구조의 일례를 나타낸다. 마이크로 스텝 구조의 높이는, 예컨대 0.3 nm 이상이고, 예컨대 10 nm 이하이다. 그 폭은, 예컨대 0.3 nm 이상이며, 예컨대 500 nm 이하이다. 그 밀도는, 예컨대  $2 \times 10^4 \text{ cm}^{-1}$  이상이고, 예컨대  $3.3 \times 10^7 \text{ cm}^{-1}$  이하이다.

[0124] 63도 이상 80도 미만의 범위의 오프각에서는, 작은 In 편석이 실현되는 이유를 이하와 같이 설명할 수 있다. c면, m면(비극성면), (11-22)면 및 (10-11)면 등의 안정면으로 이루어지는 큰 테라스에서는, In의 마이그레이션이 가능하다. 이 때문에, 원자 반경이 큰 In 원자가 마이그레이션에 의해 모이고, 이 결과, In 편석이 생긴다. 도 8의 (b)에 도시되는 바와 같이, c면 위의 캐소드 루미네센스상은 불균일한 발광을 나타낸다. 한편, 63도 이상 80도 미만의 범위 내의 오프각에 대응하는 반도체면, 예컨대 (20-21)면에서는 테라스 T1, T2의 테라스 폭이 좁기 때문에, In이 테라스 T1, T2 위에서 혼입되었을 때 충분한 In 마이그레이션은 생기지 않는다. 또한 테라스 에지 T3에서 혼입되었을 때도 마찬가지로, 충분한 In 마이그레이션은 생기지 않는다. 이 때문에, 원자의 퇴적시에 In이 흡착된 장소에서 결정에 혼입된다. 퇴적에 있어서, In이 랜덤하게 흡착되기 때문에, 도 8의 (a)에 도시되는 바와 같이, c면 위의 캐소드 루미네센스상은 균일한 발광을 나타낸다.

- [0125] c면 및 m면에서는, 도 14에 도시되는 바와 같이, 양호한 In 혼입을 나타낸다. 그러나, 큰 In 편석이 생기고, 특히 큰 In 조성에서 In 편석이 증가하여, 불균일한 발광상에 기인하는 비발광 영역이 증가한다. 활성층의 In 조성의 증가에 의해, 발광 스펙트럼의 반치전폭이 넓어진다. 한편, c면과 (10-11)면 사이의 오프각에서는, 도 14에 도시되는 바와 같이, In 혼입이 c면에 비해 저하된다. 그러나, (10-11)면과 m면 사이의 오프각에서는, 도 14에 도시되는 바와 같이, In 혼입이 c면에 비해 양호하고, 또한 In 편석도 작다.

- [0126] 이상 설명한 바와 같이, (20-21)면에 의해 대표되는 결정면의 오프각 범위는, 양호한 In 혼입성을 나타내고, 작은 In 편석을 나타낸다. 그러므로 매우 결정성이 좋은 InGaN을 성장시킬 수 있고, 발광 파장에 따라서, 지금까지와 비교하여 넓은 범위에서 In 조성을 변경할 수 있다. 그러므로 양호한 광소자를 제작할 수 있다.

- [0127] 상기한 설명은, (20-21)면을 참조하면서 행해졌지만, (20-2-1)면에 대해서도 마찬가지로 적용된다. 또한, 상기한 설명에 기재된 (20-21)면, (10-11)면, m면 등의 결정면 및 결정 방위는, 그 기재 자체에 의해 특정되는 것뿐만 아니라, 결정학적으로 등가인 면 및 방위도 나타내고 있다. 예컨대 (20-21)면이란 (02-21)면, (0-221)면, (2-201)면, (-2021)면, (-2201)면의 결정학적으로 등가인 면도 대표한다.

- [0128] (실시예 6)

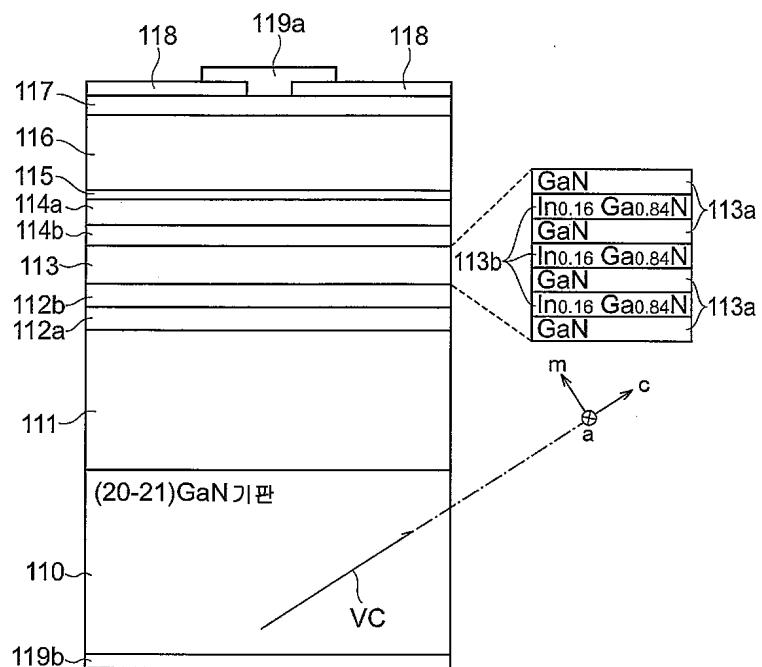

- [0129] 도 16은, 본 실시예에서의 반도체 레이저를 개략적으로 도시하는 도면이다. 도 16에 도시되는 반도체 레이저를 이하와 같이 제작하였다. 우선, (20-21)면을 갖는 GaN 기판(110)을 준비하였다. 이 GaN 기판의 주면[(20-21)면] 위에 이하의 반도체층을 에피택셜 성장시켰다.

- [0130] n형 클래드층(111): Si 도핑 AlGaN, 성장 온도 1150도, 두께 2  $\mu\text{m}$ , Al 조성 0.04;

- [0131] 광 가이드층(112a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0132] 광 가이드층(112b): 언도핑 InGaN, 성장 온도 840도, 두께 50 nm, In 조성 0.01;

- [0133] 활성층(113);

- [0134] 장벽층(113a): 언도핑 GaN, 성장 온도 870도, 두께 15 nm;

- [0135] 우물층(113b): 언도핑 InGaN, 성장 온도 780도, 두께 3 nm, In 조성 0.16;

- [0136] 광 가이드층(114b): 언도핑 InGaN, 성장 온도 840도, 두께 50 nm, In 조성 0.01;

- [0137] 광 가이드층(114a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0138] 전자 블록층(115): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 20 nm, Al 조성 0.12;

- [0139] p형 클래드층(116): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 400 nm, Al 조성 0.06;

- [0140] p형 컨택트층(117): Mg 도핑 GaN, 성장 온도 1000도, 두께 50 nm.

- [0141] p형 컨택트층(117) 위에, 실리콘 산화막 등의 절연막(118)을 퇴적한 후에, 포토리소그래피 및 웨트 에칭을 이용하여 폭 10  $\mu\text{m}$ 의 스트라이프창을 형성하였다. 이 스트라이프창을 통해 p형 컨택트층(117)에 접촉하는 p-전극(Ni/Au)(119a)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. GaN 기판(110)의 a면에는, n-전극(Ni/Al)(119b)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. 이들 공정에 의해 제작된 기판 생산물을 800  $\mu\text{m}$  간격으로 벽개하였다. 공진기를 위한 a면 벽개면에는  $\text{SiO}_2/\text{TiO}_2$  다층막으로 이루어지는 반사막을 형성하여, 개인 가이드형 레이저 다이오드를 제작하였다. 전단부면의 반사율은 80%이고, 후단부면의 반사율은 95%였다.

- [0142] 이 레이저 다이오드의 발진 파장은 452 nm에서 발진하였다. 그 임계값 전류는  $12 \text{ kA/cm}^2$ 이고, 동작 전압(전류 값: 960 mA)은 6.9볼트였다.

- [0143] (실시예 7)

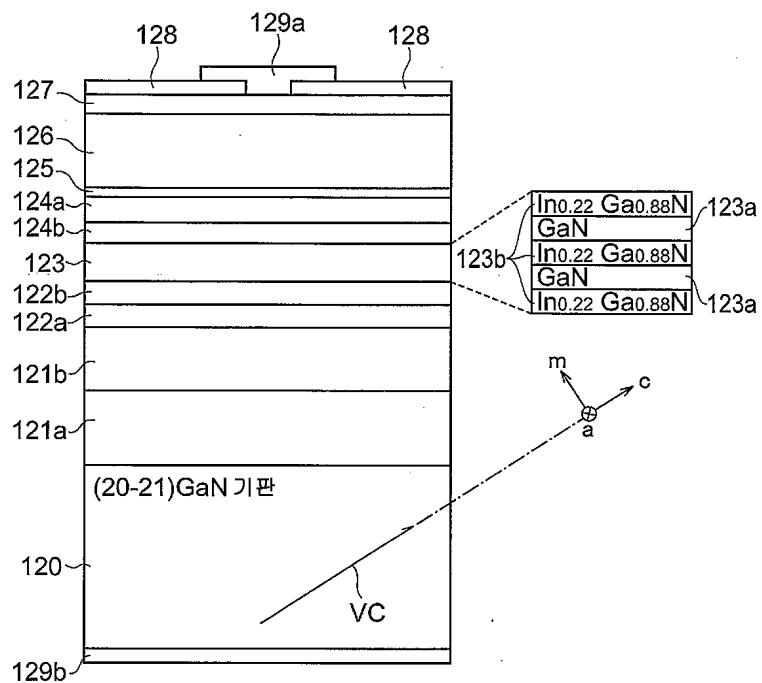

- [0144] 도 17은, 본 실시예에서의 반도체 레이저를 개략적으로 도시하는 도면이다. 도 17에 도시되는 반도체 레이저를 이하와 같이 제작하였다. 우선, (20-21)면을 갖는 GaN 기판(120)을 준비하였다. 이 GaN 기판의 주면[(20-21)면] 위에 이하의 반도체층을 에피택셜 성장시켰다.

- [0145] n형 베퍼층(121a): Si 도핑 GaN, 성장 온도 1050도, 두께 1.5  $\mu\text{m}$ ;

- [0146] n형 클래드층(121b): Si 도핑 AlGaN, 성장 온도 1050도, 두께 500 nm, Al 조성 0.04;

- [0147] 광 가이드층(122a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0148] 광 가이드층(122b): 언도핑 InGaN, 성장 온도 840도, 두께 65 nm, In 조성 0.03;

- [0149] 활성층(123);

- [0150] 장벽층(123a): 언도핑 GaN, 성장 온도 870도, 두께 15 nm;

- [0151] 우물층(123b): 언도핑 InGaN, 성장 온도 750도, 두께 3 nm, In 조성 0.22;

- [0152] 광 가이드층(124b): 언도핑 InGaN, 성장 온도 840도, 두께 65 nm, In 조성 0.03;

- [0153] 광 가이드층(124a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0154] 전자 블록층(125): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 20 nm, Al 조성 0.12;

- [0155] p형 클래드층(126): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 400 nm, Al 조성 0.06;

- [0156] p형 컨택트층(127): Mg 도핑 GaN, 성장 온도 1000도, 두께 50 nm.

- [0157] p형 컨택트층(127) 위에, 실리콘 산화막 등의 절연막(128)을 퇴적한 후에, 포토리소그래피 및 웨트 에칭을 이용하여 폭 10  $\mu\text{m}$ 의 스트라이프창을 형성하였다. 이 스트라이프창을 통해 p형 컨택트층(127)에 접촉하는 p-전극(Ni/Au)(129a)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. GaN 기판(120)의 이면에는, n-전극(Ni/Al)(129b)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. 이를 공정에 의해 제작된 기판 생산물을 800  $\mu\text{m}$  간격으로 a면에서 벽개하였다. 공진기를 위한 a면 벽개면에는  $\text{SiO}_2/\text{TiO}_2$  다층막으로 이루어지는 반사막을 형성하여, 게인 가이드형 레이저 다이오드를 제작하였다. 전단부면의 반사율은 80%이고, 후단부면의 반사율은 95%였다.

- [0158] 이 레이저 다이오드의 발진 파장은 520 nm에서 발진하였다. 그 임계값 전류는  $20 \text{ kA/cm}^2$ 이며, 동작 전압(전류값: 1600 mA)은 7.2 볼트였다.

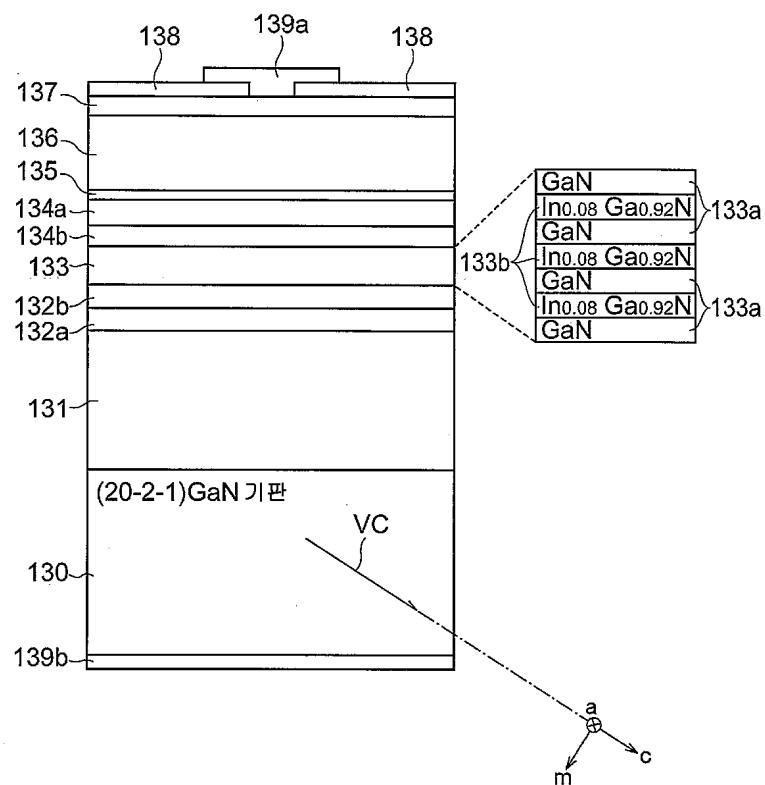

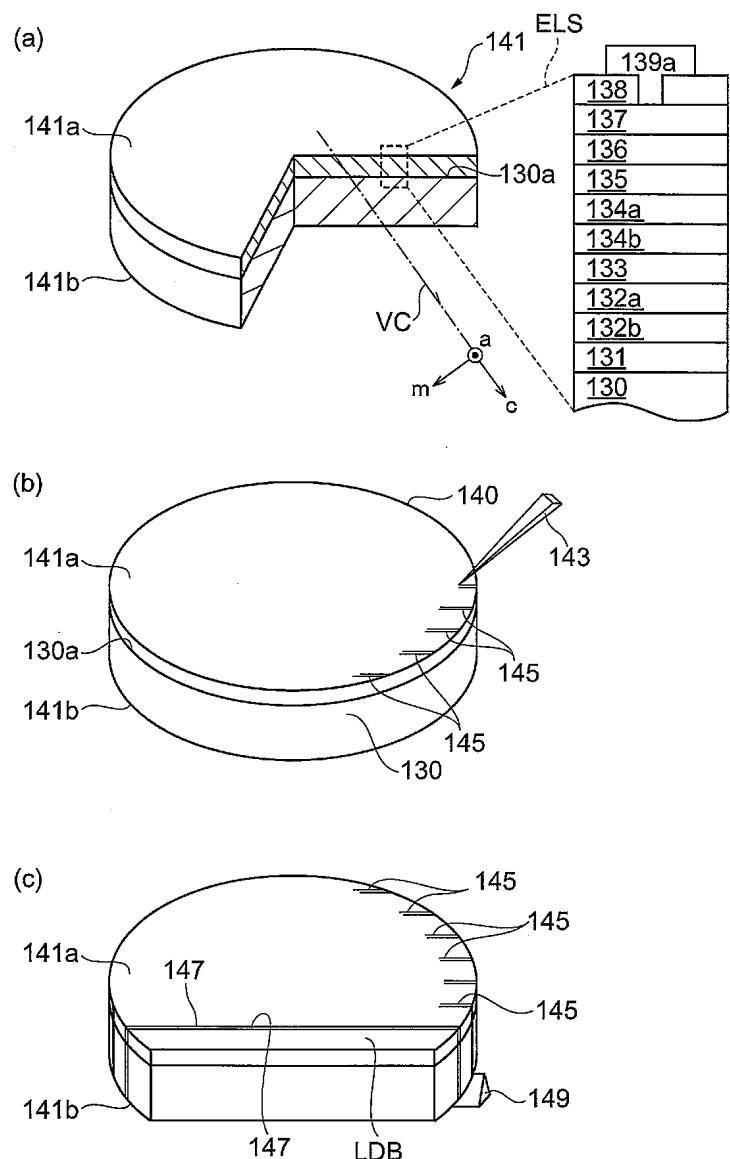

- [0159] (실시예 8)

- [0160] 도 18은, 본 실시예에서의 반도체 레이저를 개략적으로 도시하는 도면이다. 도 18에 도시되는 반도체 레이저를 이하와 같이 제작하였다. 우선, (20-2-1)면을 갖는 GaN 기판(130)을 준비하였다. 이 GaN 기판(130)의 주면 [(20-2-1)면] 위에 이하의 반도체층을 에피택셜 성장시켰다.

- [0161] n형 클래드층(131): Si 도핑 AlGaN, 성장 온도 1050도, 두께 2  $\mu\text{m}$ , Al 조성 0.04;

- [0162] 광 가이드층(132a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0163] 광 가이드층(132b): 언도핑 InGaN, 성장 온도 840도, 두께 50 nm, In 조성 0.02;

- [0164] 활성층(133);

- [0165] 장벽층(133a): 언도핑 GaN, 성장 온도 840도, 두께 15 nm;

- [0166] 우물층(133b): 언도핑 InGaN, 성장 온도 840도, 두께 3 nm, In 조성 0.08;

- [0167] 광 가이드층(134b): 언도핑 InGaN, 성장 온도 840도, 두께 65 nm, In 조성 0.02;

- [0168] 광 가이드층(134a): 언도핑 GaN, 성장 온도 840도, 두께 50 nm;

- [0169] 전자 블록층(135): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 20 nm, Al 조성 0.12;

- [0170] p형 클래드층(136): Mg 도핑 AlGaN, 성장 온도 1000도, 두께 400 nm, Al 조성 0.06;

- [0171] p형 컨택트층(137): Mg 도핑 GaN, 성장 온도 1000도, 두께 50 nm.

- [0172] p형 컨택트층(137) 위에, 실리콘 산화막 등의 절연막(138)을 퇴적한 후에, 포토리소그래피 및 웨트 에칭을 이용하여 폭 10  $\mu\text{m}$ 의 스트라이프창을 형성하였다. 이 스트라이프창을 통해 p형 컨택트층(137)에 접촉하는 p-전극(Ni/Au)(139a)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. GaN 기판(130)의 이면에는, n-전극(Ni/Al)(139b)을 형성하고, 패드 전극(Ti/Au)을 증착하였다. 이를 공정에 의해 제작된 기판 생산물을 800  $\mu\text{m}$  간격으로 a면에서 벽개하였다.

- [0173] 이 레이저 다이오드의 발진 파장은 405 nm에서 발진하였다. 그 임계값 전류는  $9 \text{ kA/cm}^2$ 이고, 동작 전압(전류값: 720 mA)은 5.8 볼트였다.

- [0174] 또한, (20-21)면을 갖는 GaN 기판(m면 +75도 오프 GaN 기판) 및 (20-2-1)면을 갖는 GaN 기판(m면 -75도 오프 GaN 기판)을 성장로의 서셉터 위에 배치하였다. 이들 GaN 기판 위에 동시에, 발광 소자를 위한 반도체 적층을 성장시켰다. 활성층은 양자 우물 구조를 가지며, 우물층은 InGaN으로 이루어지고, 장벽층은 GaN으로 이루어진다. 활성층의 성장 온도로는 800도를 이용하였다.

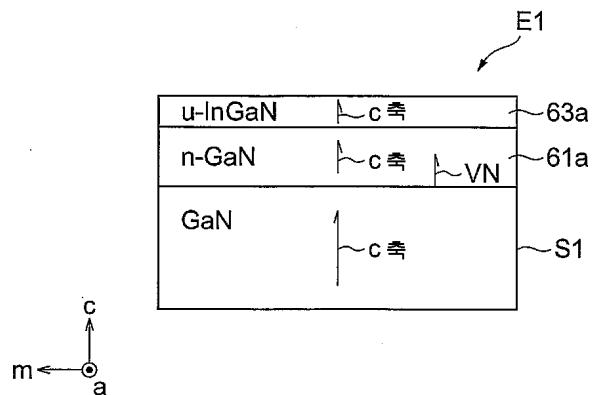

- [0175] 도 19는 m면 +75도 오프 GaN 기판 위의 양자 우물 구조의 포토 루미네센스(PL) 스펙트럼 PL<sub>+75</sub>, 및 m면 -75도 오프 GaN 기판 위의 양자 우물 구조의 PL 스펙트럼 PL<sub>-75</sub>를 도시하는 도면이다. PL 스펙트럼 PL<sub>+75</sub>의 피크 파장은 424 nm이고, PL 스펙트럼 PL<sub>-75</sub>의 피크 파장은 455 nm이다. 피크 파장차는 30 nm 정도이고, 이것은, N면으로부터 경사를 취한 (20-2-1)면의 In 혼입이, Ga면으로부터 경사를 취한 (20-21)면에 비해 큰 것을 나타내고 있다. 도 1에 도시된 기준축(Cx)의 방향으로서 선택된 [000-1]축에 대하여, 기판 주면의 법선이 m축 방향으로 63도 이상 80도 미만의 범위의 경사각을 이를 때, 이 기판 주면은, 양호한 In 혼입 능력을 나타낸다.

- [0176] 상기한 실시예에서는, 기판 주면의 법선이, [000-1]축 및 [0001]축 중 어느 하나에 대하여 63도 이상 80도 미만의 범위의 경사각으로 경사진다. 이로 인해, 실시예에서의 반도체 레이저는, 벽개면으로서 m면을 선택할 수 없고, 벽개면으로서 a면을 이용한다. 지금까지는, 주로 (0001)면으로부터 예각의 각도로 경사진 반극성 기판 위에 반도체 레이저용 에피택셜 적층 구조를 제작해 왔다. 이 반도체 레이저용 에피택셜 적층 구조는, 예컨대 GaN 기판의 주면[예컨대 (20-21)면] 위에 제작된다. 이 GaN 기판 주면의 법선은, [0001]축에 대하여 63도 이상 80도 미만의 범위의 경사각으로 경사진다. 발명자들의 지견에 따르면, a면 벽개에서의 수율은, 예컨대 m면 벽개에서의 수율에 비해 낮다.

- [0177] 도 20은, (000-1)면으로부터 예각의 각도로 경사진 반극성 기판을 이용하여 반도체 발광 소자를 제작하는 방법에서의 주요 흐름을 나타내는 도면이다. 공정 S201에서는, 예컨대 이미 설명된 공정 S101 ~ S113을 행하여 기판 생산물(141)을 제작한다. 기판 생산물(141)은 주면(141a) 및 이면(141b)을 포함한다. 계속되는 설명에서, 기판 생산물(141)은, [000-1]축에 대하여 63도 이상 80도 미만의 범위의 경사각으로 경사지는 GaN 기판의 주면 위에 형성되는 반도체 레이저를 위한 적층 구조를 포함한다. 이해를 쉽게 하기 위해, 도 21의 (a)에는, 실시예 8에서의 적층 구조(ELS)가 직사각형의 파선으로 도시되어 있다. 도 21의 (a)에 도시된 개략 도에서, 절연막(138)의 콘택트 개구는 a축 방향으로 연장되고, 전극(139a)도 a축 방향으로 연장된다. 이에 의하면, 기판 생산물(141)은 예컨대 (20-2-1)면의 주면을 갖는 GaN 기판(130)을 포함한다.

- [0178] 도 20에서의 공정 S202에서는, 도 21의 (b)에 도시되는 바와 같이, GaN 기판(130)의 m축 방향에 맞춰 기판 생산물(141)의 주면(141a)의 표면(141a)에 스크라이브를 행한다. 이 스크라이브는, 예컨대 스크라이버(143)를 이용하여 행해진다. 이 스크라이버(143)를 이용하여, 표면(141a)의 에지에 스크라이브 라인(145)을 형성한다. 스크라이브 라인(145)의 간격은 레이저 공진기의 길이에 맞춰져 있다. 스크라이브 라인(145) 각각은, GaN 기판(130)의 m축 및 c축에 의해 규정되는 평면과 표면(141a)의 교차선의 연장 방향으로 연장된다.

- [0179] 도 20에서의 공정 S203에서는, 기판 생산물(141)에 스크라이브를 실시한 후에, 도 21의 (c)에 도시되는 바와 같이, 기판 생산물(141)을 벽개하여 벽개면(147)을 형성한다. 이 벽개면(147)은 a면을 포함한다. 이 벽개는, 예컨대 블레이드 등의 압박 장치(149)를 이용하여 기판 생산물(141)을 압박함으로써 행한다. 벽개를 야기하는 특정한 스크라이브 라인(145)에 압박 장치(149)를 정렬시킨 후에, 기판 생산물(141)의 이면(141b)에 압박한다. 스크라이브 라인(145)의 선택에 의해, 벽개면의 위치를 제어할 수 있다. 반도체 적층(131 ~ 137)은, GaN 기판(130)의 주면(131a) 위에 에피택셜 성장되기 때문에, 기판 이면의 스크라이브 라인(145)의 방향에 따른 벽개면을 갖는 레이저바(LDB)를 제작할 수 있다.

- [0180] 이 방법에 의하면, [000-1]축에 대하여 m축 방향으로 63도 이상 80도 미만의 범위의 경사각으로 경사진 주면 위에 에피택셜 성장시켜 제작한 기판 생산물(141)의 표면(141a)에 스크라이브를 행한다. 이 스크라이브 방법을 이용하면, 벽개 수율이 양호하다. 또한, 이미 설명한 바와 같이, 기준축의 방향이 [000-1]축의 방향일 때, 발광 특성의 저하가 억제된다.

- [0181] (실시예 9)

- [0182] 상기한 기판 생산물(141)의 표면(141a)에 형성된 스크라이브 홈을 이용하여 기판 생산물(141)을 벽개하여 레이저바를 제작하였다(이하 「-스크라이브」라고 부름). 또한 상기한 웨이퍼 E5의 표면에 형성된 스크라이브

홈을 이용하여 웨이퍼 E5를 벽개하여 레이저바를 제작하였다(이하 「+스크라이브」라고 부름). 발명자들의 실험에 의하면, -스크라이브의 수율은 +스크라이브의 수율의 1.4배였다. -스크라이브는 우수한 벽개 수율을 제공할 수 있다.

[0183] (실시예 10)

[0184] GaN 기판의 (20-21)면에 에피택셜 성장을 실행한 2장의 에피택셜 웨이퍼를 준비하였다. 한쪽 에피택셜 웨이퍼의 표면에 스크라이브 홈을 형성한 후에, 이 에피택셜 웨이퍼를 벽개하여 레이저바를 제작하였다(「+스크라이브」). 또한, 다른쪽 에피택셜 웨이퍼 이면에 스크라이브 홈을 형성한 후에, 이 에피택셜 웨이퍼를 벽개하여 레이저바를 제작하였다(「-스크라이브」). 「-스크라이브」를 이용한 이면 벽개의 수율은, 「+스크라이브」를 이용한 표면 벽개 수율에 비해 1.4배로 향상되었다.

[0185] (20-21)면의 주면(主面)을 갖는 GaN 웨이퍼에서는, 이 주면 위에 GaN계 반도체 에피택셜 영역을 성장시켜 에피택셜 웨이퍼를 제작한 후에, 이 에피택셜 웨이퍼로 기판 생산물을 제작한다. (20-21)면의 GaN 웨이퍼를 이용하여 제작된 기판 생산물에서는, 기판 생산물의 이면(웨이퍼의 이면)에 스크라이브를 실시하는 것이 바람직하다. 이것은, (20-2-1)면에 스크라이브를 실시하는 것이다. GaN의 (20-2-1)면은 Ga면이고, GaN의 (20-21)면은 N면이다. (20-2-1)면은 (20-21)면보다 딱딱하다. 웨이퍼 이면의 (20-2-1)면에 대한 스크라이브에 의해, 벽개 수율을 향상시킬 수 있다.

[0186] 계속해서, GaN계 반도체의 성장에 대해서 설명한다.

[0187] 1. GaN 및 InGaN의 성장 기구(안정면)

[0188] GaN 및 InGaN의 성장 기구에 대해서 설명한다. GaN계 반도체의 성장에서는, 결정 성장 중에 원자 레벨로 평탄한 성장 표면이 형성되는 면방위, 예컨대 c면이 있고, 이 면방위는 「안정면」이라고 불린다. 안정면에서의 GaN의 성장 기구는 이하와 같다. 안정면 위에서의 GaN 성장에서는, 성장 표면은 수 100 nm 오더의 큰 테라스 폭을 갖은 거시적인 원자층 스텝으로부터 형성된다. 이 GaN의 성장 기구는, 그 성장 온도의 점에서 3종류로 분류된다.

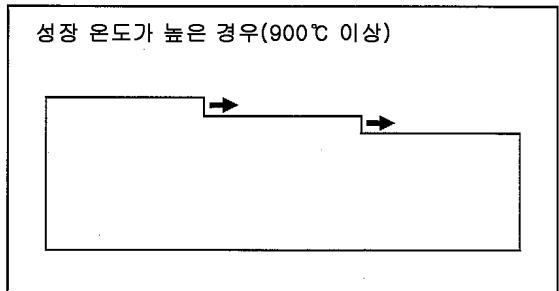

[0189] 도 22는, 성장 온도가 높을 때의 성장 모드 및 성장 온도가 낮을 때의 성장 모드를 모식적으로 도시하는 도면이다. 섭씨 900도를 초과하는 성장로에서의 성장 온도에서는, 도 22의 (a)에 도시되는 성장 모드가 발생한다. 높은 성장 온도에서는, 성장 표면에서의 GaN 분자의 마이그레이션이 크기 때문에, 테라스 위에서 결정중에 혼입되는 경우는 거의 없고, GaN 분자가 킹크라고 불리는 활성화 에너지가 큰 스텝단에 도달한 시점에서 처음으로 결정 중에 혼입된다. 그 결과, 그 성장에서는, 스텝단이 적층형으로 연장된다. 이 성장 모드를 소위 「스텝 플로 성장」이라고 부른다. 도 23은 GaN의 성장 표면의 AFM상을 도시하는 도면이다. 도 23의 (a)를 참조하면, 원자층 스텝이 어느 일정한 방향으로 형성되어 가는 모습을 잘 알 수 있다.

[0190] 한편, 성장로에서의 섭씨 700도 내지 섭씨 900도 정도의 성장 온도에서는, 도 22의 (b)에 도시되는 성장 모드가 발생한다. 낮은 성장 온도에서는, 성장 표면에서의 분자의 마이그레이션이 작기 때문에, 분자는 스텝단에 도달하지 않고, 큰 테라스 위에서 결정에 혼입된다. 분자가 혼입된 부분이 핵이 되고, 스텝이 넓어지는 성장을 한다. 이 성장 모드를 「테라스 위 성장」이라고 부른다. 도 23의 (b)는, 테라스 위 성장에 의해 성장된 GaN의 성장 표면의 AFM상을 도시하는 도면이다. 이 성장에서의 모폴로지에서는 다수의 생성 핵이 형성되고, 또한 다수의 핵으로부터 스텝이 넓어진다. 이로 인해, 스텝이 한 방향으로 연장되는 것이 아니라, 전체 방위로 형성되어 간다.

[0191] 섭씨 700도 이하의 성장 온도에서는, 상기한 성장 모드와 상이한 성장 모드가 발생한다. 매우 낮은 성장 온도에서는, 분자의 마이그레이션이 거의 없기 때문에, GaN 분자가 성장 표면에 도달한 시점에서 바로 결정 중에 혼입된다. 이로 인해, 결정 결함이 매우 도입되기 쉽고, 고품질의 GaN막을 성장시키는 것이 어렵다. 이 성장 모드를 「섬형 성장」이라고 부른다.

[0192] 이어서, c면으로부터 m축 방향으로 경사진 여러 면방위의 결정면에서의 성장을 설명한다. c면으로부터 m축 방향으로 경사진 여러 면방위의 결정면에, 섭씨 1100도의 성장 온도로 GaN을 성장시켰다. 그 표면을 AFM으로 관찰한 바, 도 22의 (a)에 도시하는 바와 같은 거시적인 원자층 스텝이 관찰된 면방위는, 이하의 3종류의 면으로 이루어지는 스텝뿐인 것을 발견하였다. 즉, 이들의 면은, c면, m면, 및 c면으로부터 약 62도로 경사진 {10-11}면이다. 즉, c면을 m축 방향으로 기울인 결정면에서의 성장에서는, 안정면이라고 할 수 있는 면이 상기 3개의 면뿐이다. 3종류의 안정면 이외의 면을 총칭하여 「비안정면」이라고 부른다.

[0193] 계속해서, 안정면 위에서의 InGaN의 성장 기구를 설명한다. InGaN의 성장 기구는 기본적으로 GaN과 같은 것으로

로 생각된다. 상이한 점은, InGaN 성장에서는, InN의 성장 표면에서의 체재 시간은 GaN과 비교하여 짧고, InN의 이탈이 용이하게 발생한다. 이로 인해, 어느 정도 크기의 In 조성의 In을 결정 중에 첨가하고자 할 때에는, 성장 온도를 내려야 하고, 대략 그 온도는 섭씨 900도 이하가 된다. 즉, 안정면 위의 InGaN의 성장은, 테라스 위 성장이 된다.

[0194] 2. GaN 및 InGaN의 성장 기구(비안정면)

비안정면에서의 GaN 및 InGaN의 성장 기구를 설명한다. 섭씨 1100도에서의 성장 온도로 비안정면의 면 위에 성장시킨 GaN 표면의 AFM 관찰에 의하면, 안정면으로부터의 비교적 작은 경사각(「서브 오프각」이라고 부름)의 면방위 위로의 성장에서는, 그 오프각에 가까운 안정면으로부터 형성되는 미세한 스텝이 관찰되었다. 그 테라스 폭은, 안정면 자체의 면방위로의 성장에 비해 작고, 서브 오프각이 클수록 더 작아진다. 안정면에 대하여 대략 2도 정도 경사지게 하면, AFM상에서는 원자층 스텝은 관찰되지 않게 된다. 이를 결과로부터, 안정면 근방에서는 성장 중에 안정면이 나오기 쉽고, 비교적 테라스 폭이 큰 스텝이 형성된다. 도 24의 (a)는, 비안정면에서의 GaN 및 InGaN의 고온 성장에서의 스텝 플로 성장의 성장 기구를 모식적으로 도면이다. 화살표는 성장 방향을 도시한다.

[0196] 한편, 안정면으로부터 크게 경사질 때, 테라스 폭은 작아지고, AFM상에서는 관찰할 수 없는 마이크로 스텝이 형성되어 있는 것을 생각할 수 있다. 또한, 안정면은 상기 3종류밖에 없기 때문에, 이 마이크로 스텝도 안정면으로 이루어지는 마이크로 테라스에 의해 형성되어 있고, 고온에서 성장된 GaN의 표면에서는, 소정 방향으로 스텝이 연장되는 성장을 하고 있는 것으로 생각된다.

[0197] 성장 온도가 낮은 경우의 GaN의 성장 기구를 설명한다. 안정면 근방에서는, 안정면으로 이루어지는 넓은 테라스가 형성되기 쉽고, 성장 표면에서의 분자의 마이그레이션은 작기 때문에, 테라스 위 성장이 지배적으로 된다. 도 24의 (b)는, 비안정면에서의 GaN 및 InGaN의 저온 성장에서의 테라스 위 성장의 성장 기구를 모식적으로 도시하는 도면이다.

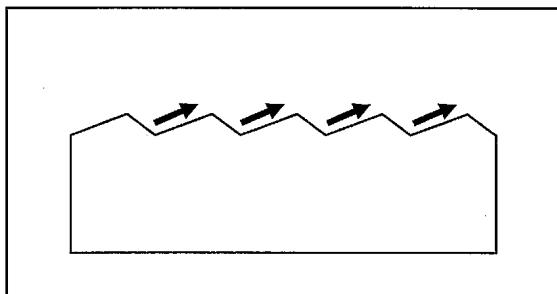

[0198] 한편, 안정면으로부터의 서브 오프각이 큰 면방위의 결정면으로의 성장에서는, 표면의 스텝 밀도가 높아지고, 테라스 폭이 수 nm 오더까지 미세한 것으로 된다. 안정면으로부터의 서브 오프각이 클 때, 테라스 폭이 좁기 때문에 테라스 위 성장의 성장 기구는 잘 일어나지 않는다. 성장 표면에서의 분자의 마이그레이션이 작은 성장 온도일 때라도, 활성화 에너지의 높은 스텝단에 원자가 도달하기 쉬워진다. 즉, 안정면으로부터의 서브 오프각이 커지면, 보다 저온까지 스텝단이 연장되어 가는 성장을 하는 것을 생각할 수 있다. 이 성장은, 스텝 플로 성장에 비하면 테라스 폭의 스케일이 2자릿수 가까이 작기 때문에, 여기서는 「스텝단 성장」이라고 부른다. 도 24의 (c)는, 비안정면에서의 GaN 및 InGaN의 저온 성장에서의 스텝단 성장의 성장 기구를 모식적으로 도시하는 도면이다.

[0199] 상기한 설명으로부터 이하와 같이 되는 것으로 생각된다. 성장 온도가 낮은 경우, 안정면 및 안정면 근방에서는 테라스 위 성장이 지배적이다. 안정면으로부터의 서브 오프각이 커지면, 테라스 위 성장은 점차 약해지고, 스텝단 성장이 지배적으로 된다. 또한 이것은 성장 온도가 낮은 InGaN의 성장 기구와도 일치한다.

[0200] 3. In 혼입에 관해서

[0201] InGaN 성장에 있어서 각 성장면에서의 In 혼입을 설명한다. In 조성을 조사하기 위해, c면으로부터 m축 방향으로 여러 경사 각도로 경사진 GaN 기판 위에, 섭씨 760도로 모두 같은 조건으로 InGaN을 성장시키는 실험을 하였다. 도 25는, 그 실험 결과를 도시하고 있고, 횡축은 c축으로부터 m축 방향으로의 경사각(오프각)을 도시하며, 종축은 성장된 InGaN의 In 조성을 도시한다.

[0202] 각도 In 조성

[0203] 0 21.6

[0204] 10 11.2

[0205] 16.6 9.36

[0206] 25.9 7.54

[0207] 35 4.33

[0208] 43 4.34

|        |    |      |

|--------|----|------|

| [0209] | 62 | 22.7 |

| [0210] | 68 | 29   |

| [0211] | 75 | 19.6 |

| [0212] | 78 | 18.5 |

| [0213] | 90 | 23.1 |

[0214] 도 25를 참조하면, c면에서의 In 혼입은 양호하다. c면으로부터 오프각을 크게 해가면, In의 혼입이 저하되어간다. 오프각을 더 크게 하면, 경사각 40도를 초과한 곳부터 In 혼입이 향상되기 시작한다. 안정면인 {10-11}면의 In 혼입은 c면과 같은 정도로 되어 있다. 오프각을 더 크게 하면, In 혼입이 향상되고, 68도 부근에서 극대값을 나타낸다. 이 각도를 초과할 때, In 혼입은 감소로 바뀐다. In 혼입은, 오프각 80도 주변에서 극소값을 나타낸다. 이 각도를 초과하여 m면에 근접할 때, In 혼입은 향상된다. m면은 c면과 동등 정도의 In 혼입을 나타낸다.

[0215] 이 In 혼입의 상태를 항목 1 및 2에서의 InGaN의 성장 기구에 기초하여 설명한다.

[0216] 우선, 도 22의 (b)에 도시하는 바와 같이, 안정면 근방에서 테라스 위 성장이 지배적인 경우에는, 도 25에 도시되는 바와 같이 In이 잘 혼입된다. 안정면으로 이루어지는 테라스 위에서 In 혼입이 좋은 이유를, 결정 표면의 원자 배열로부터 이하와 같이 설명할 수 있다. 도 26은, 예로서 {10-11}면의 표면 원자 배열을 도시한다. 도 26을 참조하면, c면 c0 및 (10-11)면이 나타나 있다. 도 26에 도시되는 바와 같이, In 원자는 화살표 Y(In)로 도시한 N 원자 2개와 2개의 결합손으로 결합한다. N 원자 2개는 도 26에서의 직교 좌표계(T)에서의 X축 방향으로 나열되어 있다. 이들 2개의 N 원자가, 도 26에서의 직교 좌표계(T)에서의 X축의 플러스(앞쪽) 방향 및 마이너스(안쪽) 방향으로 변위할 수 있고, 이 배치는, 원자 반경이 큰 In 원자를 혼입하기 쉬운 상황으로 있다. 이러한 원자 배열이, 테라스 위 성장에서 In 혼입이 쉬운 이유를 나타내는 것으로 생각된다.

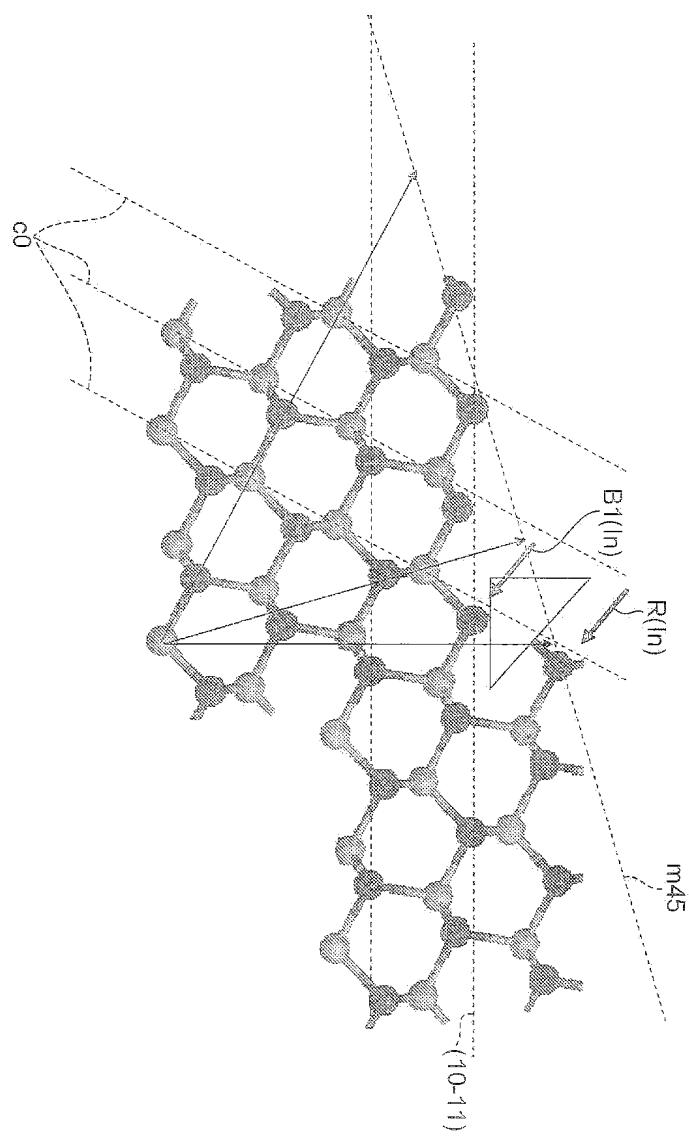

[0217] 동일한 관점에서 스텝단 성장하는 경우의 In 혼입을 설명한다. 도 27은, 예로서 m축 방향으로 45도 정도 기울인 면의 성장 표면의 원자 배열을 도시한다. 도 27을 참조하면, c면 c0, c면으로부터 45도 경사면(m45) 및 (10-11)면이 나타나 있다. 스텝단에 착안해 보면, In 원자는, 화살표 B1(In)로 도시한 N 원자 2개와는 2개의 결합손으로 결합하고, 화살표 R(In)로 도시한 N 원자 1개와는 하나의 결합손으로 결합한다. 이 경우, In 원자와의 결합에 관여하는 화살표 B1(In)로 도시한 N 원자와 화살표 R(In)로 도시한 N 원자의 변위 가능한 방향이 수직 관계에 있고, 또한 원자 반경이 큰 In을 혼입하기 위해서는 3개의 N 원자가 변위해야 하므로, 이 원자 배열은 In이 잘 혼입되지 않는 상태에 있다. 이로 인해, 스텝단 성장에서는 In이 잘 혼입되지 않는 것으로 생각된다. 이들을 고려하면, 도 25의 결과의 일부를 잘 설명할 수 있다. 즉, c면과 {10-11}면 사이의 면방위에서는, 안정면 근방에서는 테라스 위 성장이 지배적이고 In의 혼입은 양호하다. 한편, 안정면으로부터의 서브 오프각이 커짐에 따라, 테라스 위 성장이 약해져 스텝단 성장이 지배적으로 됨으로써 In 혼입이 작아진다.

[0218] 한편, {10-11}면과 m면 사이에서도 동일한 사항이 적용되는 것으로 생각된다.

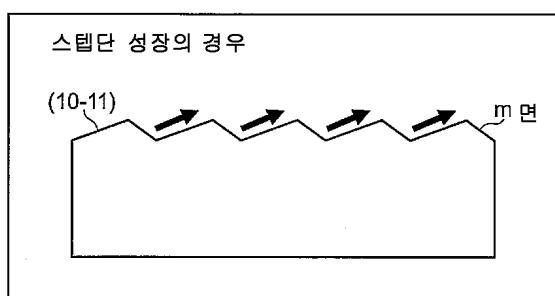

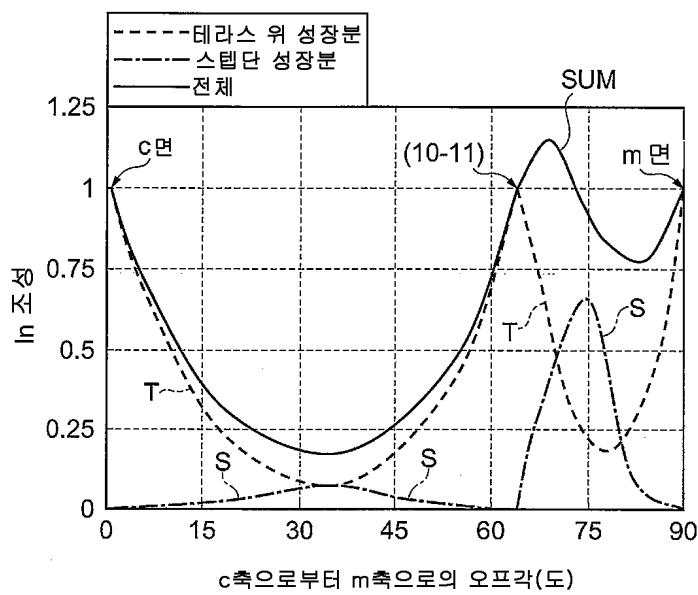

[0219] 그러나, {10-11}면과 m면 사이 중 {10-11}면 근처의 c면으로부터의 오프각이 63도 이상 80도 미만인 범위에서는, 상기와 같은 설명으로는 이해할 수 없는 상태를 나타내고 있다. 그래서, 이 각도 범위에서의 표면 원자 배열을 더 검토하면, 이 각도 범위에서만 스텝단에서도 In이 잘 혼입되는 것을 발견하였다. 도 28은 예로서 c면을 m축 방향으로 오프각 75도로 기울인 면의 표면 스텝의 상태를 모식적으로 도시한 것이다. 상기한 각도 범위에서는, 도 28에 도시한 바와 같이, 성장 표면은 {10-11}면과 m면으로 형성되는 마이크로 스텝으로 이루어져 있다. 그 스텝단이 m축 방향으로 연장되는 스텝단 성장을 한다. 도 29는, 예로서 m축 방향으로 75도 정도 기울인 면의 성장 표면의 원자 배열을 도시한다. 도 29를 참조하면, m면 m0, c면으로부터 75도 경사면 m75 및 (10-11)면이 도시되어 있다. 이 경우, 혼입되는 인듐은, 화살표 R2(In)로 도시한 N 원자 1개와는 하나의 결합손으로 결합하고, 화살표 B2(In)로 도시한 N 원자 1개와는 하나의 결합손으로 결합한다. 이 배치에서는, 2개의 N 원자의 변위 가능한 방향이 대향하는 상태에 있고, 또한 원자 반경이 큰 In을 혼입하기 위해서는 2개의 N 원자만이 변위하는 것이 좋고, 이로 인해, 이 스텝단에서는 In 원자를 혼입하기 쉬운 것으로 생각된다. 또한 다른 각도 범위의 스텝단에 대해서도 그 표면 원자 배열을 검토하였다. 양호한 In 혼입을 나타내는 스텝 단에서의 성장을 가능하게 하는 각도는, 상기 범위만인 것을 발견하였다.

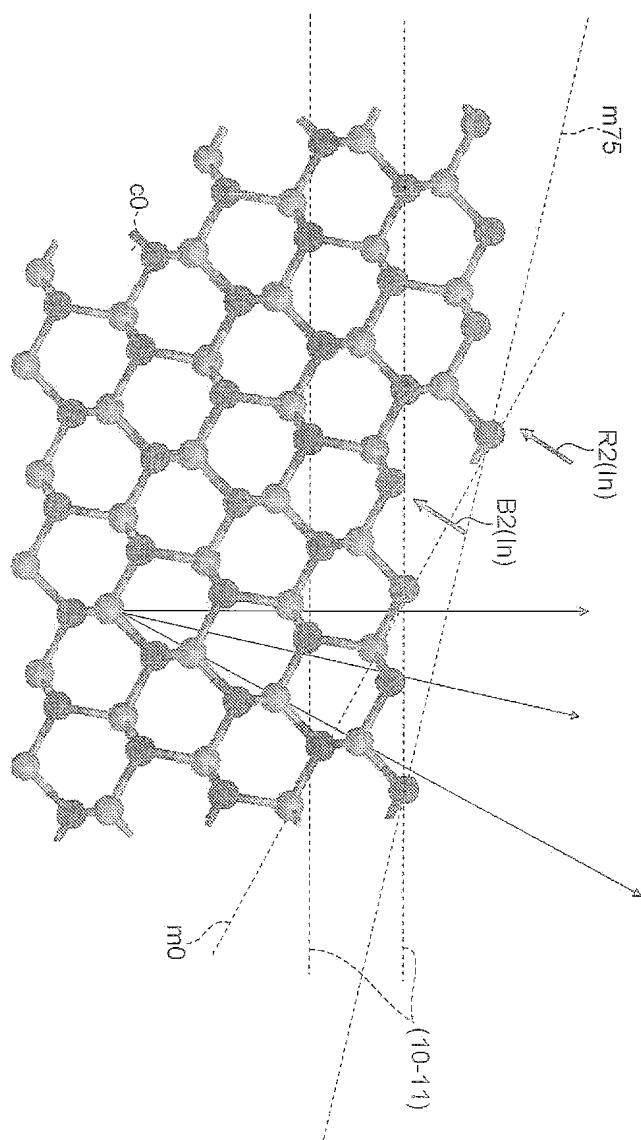

[0220] 이상의 고찰에 기초하여, In 혼입의 오프각 의존성을 예측하였다. 도 30은 In 혼입과 오프각의 관계를 도시하

는 도면이다. In 혼입은 테라스 위 성장 성분과 스텝단 성장 성분 양쪽 모두를 예측하고, 총 In 혼입은, 이들의 합으로 표시된다. 종축에서는, In 혼입량을 c면 위에서의 In 혼입으로 규격화하고 있다. 실선 T는 테라스 위 성장에 의해 혼입되는 In의 양을 나타내고, 실선 S는 스텝단 성장에 의해 혼입되는 In의 양을 나타내며, 실선 SUM은 그 합을 나타낸다. 이와 같이 테라스 위 성장에서는, 테라스 위 성장이 지배적인 안정면 근방에서 In 혼입이 높고, 안정면에서 멀어질수록 테라스 위 성장이 지배적이지 않게 되어 In은 혼입되지 않게 된다.

[0221] 한편, 스텝단 성장은 안정면으로부터 멀어질수록 스텝 밀도가 높아져 지배적으로 된다. 그러나, c면으로부터 경사각 63도 이상 80도 미만의 각도 범위의 외측에서는, 스텝단 성장에 의한 In 혼입은 거의 없다. 경사각 63도 이상 80도 미만의 각도 범위에서만, 스텝단에서 큰 In 혼입이 생기기 때문에, 스텝부 성장이 활발해짐에 따라 In 혼입이 커지는 상태를 나타내게 된다. 그 결과, 실선 SUM으로 나타내는 오프각 의존성으로 되고, 도 30에 도시된 예측은, 도 25에 도시된 실험 결과를 잘 설명하고 있다.

[0222] 4. In 편석에 관한 이상의 결과를 근거로, InGaN막 중의 In 편석을 설명한다. c면 기판 위의 InGaN 활성층을 갖는 광소자에서는, 특별히 활성층의 발광 파장이 장파장이 될수록, 즉 InGaN 결정 중의 In 조성이 높아질수록, InGaN 결정 중의 In 편석이 커진다. 이 결과, InGaN의 결정 품질이 저하되어, 발광 강도의 저하나 발광 파장 반치폭의 증대가 관찰된다. 한편, 발명자들의 실험에 의하면, m축 방향으로의 c축 경사각 63도 이상 80도 미만의 범위에서는, 장파장 영역을 발광하는 InGaN층의 발광 강도 저하는, c면이나 그 외 안정면 위에서의 InGaN층에 비해 작고, 또한 반치폭의 증대도 작다.

[0223] 발명자들은, 그 이유를 성장 기구나 In 혼입에 기초하여 검토했다. 안정면 위에 성장시킨 InGaN막이 큰 In 편석을 나타내는 이유는 다음과 같은 것으로 생각된다. 도 22의 (b)에 도시되는 바와 같이, 테라스 위 성장에서의 In 혼입에 있어서, GaN 및 InN의 분자는, 테라스 위에 도달한 후에 결정 중에 혼입되기 전에, 넓은 테라스 위에서 마이그레이션하고 있다. 그 마이그레이션시에, GaN과 InN의 비혼화성에 의해 InN이 자발적으로 응집된다. 이 응집에 의해, InGaN 결정중에서 In의 편석이 생기는 것으로 생각된다.

[0224] 한편, 도 30에 도시되는 바와 같이, 안정면으로부터의 서브 오프각이 클 때, 스텝단에서 In이 혼입된다. 성장 표면에 도달한 GaN 및 InN의 분자는, 좁은 테라스 위에서는 거의 마이그레이션하지 않고, 즉시 결정 중에 혼입된다. 이로 인해, InGaN 결정 내에서, 혼입된 In은, 거의 랜덤하게 분포되어, In 편석이 작은 것으로 생각된다. 이러한 경향은, 스텝 밀도가 클수록 현저한 것으로 생각된다. 이 때문에, 안정면으로부터의 서브 오프각이 클수록, 균일한 InGaN막을 얻을 수 있다. 그러나, 이미 설명한 바와 같이, 스텝단 성장에서는, 특정 각도 범위를 제외한 경사각에서는 In 혼입이 좋지 않다. 이로 인해, 원하는 In 조성을 얻기 위해서는, 성장 온도를 내려야 한다. 성장 온도의 저하에서는, 지배적인 성장 모드가 스텝단 성장으로부터 섬형 성장으로 변화되고, 이 결과, 결정 결함 등이 증가하여, InGaN 막질이 현저히 악화된다.

[0225] 상기 설명과 같이, In 혼입과 In 편석은 트레이드오프의 관계에 있는 것을 생각할 수 있다. 발명자들은, In 혼입과 In 편석이 양립하는 범위를 발견하였다. 이 각도 범위는, c축으로부터 m축 방향으로 경사각 63도 이상 80도 미만이다. 이 각도 범위에서는, 스텝단 성장에서도 In이 효율적으로 함입되고, 또한 InGaN막에서의 In 편석은 작다. 특히, 70도 이상 80도 미만의 각도 범위에서는, 스텝 밀도가 높아지기 때문에, 보다 In 편석이 작고 균질성이 높은 InGaN막을 성장시킬 수 있다. 또한 In 혼입을 고려하면, 특히 71도 이상 79도 이하의 각도 범위에서, 스텝단 성장과 테라스 위 성장의 밸런스가 양호하다. 그중에서도, 72도 이상 78도 이하의 각도에서, 스텝단 성장과 테라스 위 성장의 밸런스가 가장 좋다. 이로 인해, 원하는 조성을 얻기 위해 InGaN막의 성장 온도를 높이는 것이 가능하고, 또한 결정 결함이 적은 균일한 InGaN막을 성장시킬 수 있다.

[0226] 도 31 및 도 32는, 이상 설명한 In 혼입, In 편석, 및 피에조 전계의 점에서, 각각의 면 및 각도 범위의 특징을 나타내는 도면이다. 도 31 및 도 32에서, 이중 원 심볼은 특히 양호한 특성을 나타내고, 단일 원 심볼은 양호한 특성을 나타내며, 삼각 심볼은 특히 통상의 특성을 나타내고, × 심볼은 떨어지는 특성을 나타낸다. 특징적인 각도로서, c축으로부터 m축 방향으로의 경사각 63도, 70도, 71도, 72도, 78도, 79도, 80도가 표시된다. m 방향 63도 이상 80도 미만의 각도 범위가, 특히 70도 이상 80도 미만의 각도 범위가, 더 나아가서는 71도 이상 79도 이하, 그 중에서도 72도 이상 78도 이하의 각도 범위가, 장파장 영역에서의 광소자, 특히 발광 다이오드 소자나 레이저 다이오드 소자를 제작하는 데에, 그 발광 효율과 발광 반치폭이 작기 때문에 매우 유리하다.

[0227] 상기한 설명에서, 예컨대 면방위 (20-21)나 (10-11)과 같은 기법을 이용하고 있다. 본 실시형태의 설명을 고려할 때, 결정학적으로 등가인 면에서, 당업자는, 본 실시형태에 기재된 발명의 효과를 얻을 수 있는 것으로 생각한다. 따라서 예컨대 「(20-21)」라는 면방위는, 등가인 (2-201), (-2201), (20-21), (-2021), (02-21),

(0-221)를 포함한다고 생각할 수 있다.

[0228] 적합한 실시형태에서 본 발명의 원리를 도시하고 설명하고 있지만, 본 발명은, 그와 같은 원리로부터 일탈하지 않고 배치 및 상세를 변경시킬 수 있으며, 이는 당업자에게 명백한 것이다. 본 발명은, 본 실시형태에 개시된 특정 구성에 한정되는 것이 아니다. 따라서, 특히 청구범위 및 그 정신의 범위에서 오는 모든 수정 및 변경에 권리를 청구한다.

### 산업상 이용가능성

[0229] 최근, GaN계의 발광 소자에 있어서, 장파장의 발광이 요구되고 있고, c면으로부터 경사각을 취한 반극성면이나, m면 및 a면으로 대표되는 비극성면이 주목받고 있다. 그 이유는, 다음과 같다. 장파장의 발광을 얻기 위해 우물층의 In 조성이 증가하기 때문에, 우물층과 장벽층의 격자 상수차가 커지고, 발광층에 큰 왜곡이 생긴다. 이 때, c면과 같은 극성면에서는, 피에조 전계의 동작에 의해, 발광 소자의 양자 효율이 저하된다. 이것을 피하기 위해, 비극성면(a면이나 m면) 등의 여러 결정면에서의 연구가 진행되고 있다. 그러나, 아직 c면 위의 효율을 초과하는 것은 없는 것이 현재의 상황이다. 발명자들은, 기판의 주면이, c면으로부터 m축 방향으로 약 62도의 각도로 경사진 (10-11)면과 m면으로 이루어지는 마이크로 스텝 구조를 형성하기 위해, c면으로부터 m축 방향으로 63도 이상 80도 미만의 각도로 기울인 면에 주목하였다. 특히, c면으로부터 m축 방향에 75도의 경사면인 (20-21)면과, 이 면을 중심으로 하는 c면으로부터 m축 방향으로의 경사각 63도, 더 나아가서는 70도 이상 80도 미만의 영역에 주목하였다. 이 영역에서는, 기판의 주면에 (10-11)면으로 이루어지는 테라스의 폭과 m면으로 이루어지는 테라스의 폭이 작고, 스텝 밀도가 커지며, In 편석이 작아진다.

### 부호의 설명

[0230] 11a, 11b: GaN계 반도체 광소자, VN: 범선 벡터, VC+: [0001] 축방향의 벡터, VC-: [000-1] 축방향의 벡터, Sc: 평면, Cx: 기준축, Ax: 미리 정해진 축, 13: 기판, 13a: 기판의 주면, 15: GaN계 반도체 에피택셜 영역, 17: 활성층, a: 주면 경사각, 19: 반도체 에피택셜층, M1, M2, M3: 표면 모폴로지, 21: GaN계 반도체 영역, 23: n형 GaN 반도체층, 25: n형 InGaN 반도체층, 27: 전자 블록층, 29: 컨택트층, 31: 양자 우물 구조, 33: 우물층, 35: 장벽층, 37: 제1 전극, 39: 제2 전극, A<sub>OFF</sub>: a축 방향의 오프각, 41: n형 클래드층, 43a: 광 가이드층, 43b: 광 가이드층, 45: 전자 블록층, 47: 클래드층, 49: 컨택트층, 51: 제1 전극, 53: 절연막, 55: 제2 전극, 141: 기판 생산물, 141a: 기판 생산물의 주면, 141b: 기판 생산물의 이면, 143: 스크라이버, 145: 스크라이브 라인, 147: 벽개면, 149: 압박 장치, LDB: 레이저바

도면

도면1

도면2

## 도면3

(a)

(b)

## 도면4

(a)

(b)

## 도면5

## 도면6

## 도면7

도면8

도면9

## 도면10

(a)

(b)

## 도면11

도면12

도면13

도면14

도면15

(a)

(b)

도면16

도면17

## 도면18

도면19

도면20

## 도면21

도면22

(a)

(b)

도면23

(a)

(b)

## 도면24

(a)

(b)

(c)

## 도면25

도면26

도면27

도면28

도면29

도면30

### 도면31

| 면                     | 구성면            | 피에조 | In 혼입      | In 편석 |                                                                        |

|-----------------------|----------------|-----|------------|-------|------------------------------------------------------------------------|

| C면 균방                 | C면             | ×   | ○          | ×     | In 혼입은 좋지만, 특히 장파에서 In 편석이 커지고, 비발광 영역이 증가. 반치 폭도 증대되고 피에조 전계의 문제도 발생. |

| C면과 (10-11)면 사이의 면    | C면<br>(10-11)면 | ○~◎ | ×          | △     | In을 넣기 위해 성장 온도를 내려 결정 품질이 저하.                                         |

| (10-11)면 균방           | (10-11)면       | ○   | ○          | ×     | In 혼입은 좋지만, 특히 장파에서 In 편석이 커지고, 비발광 영역이 증가. 반치 폭도 증대.                  |

| m방향 63도 이상, 80도 미만의 면 | (10-11)면<br>m면 | ○   | ○~◎<br>~◎◎ |       | 스텝단 성장에서도 In 혼입이 좋다. In 편석이 작고, 고품질로 균일한 InGaN막 제작 가능.                 |

| m방향 80도 이상, 90도 미만의 면 | (10-11)면<br>m면 | ○   | △          | △     | In을 넣기 위해 성장 온도를 내려 결정 품질이 저하. 테라스 위 성장 성분이 커지고, In 편석도 크다.            |

| m면 균방                 | m면             | ◎   | ○          | ×     | In 혼입은 좋지만, 특히 장파에서 In 편석이 커지고, 비발광 영역이 증가. 반치 폭도 증대.                  |

### 도면32

| 면                        | 구성면            | 피에조 | In 혼입 | In 편석 |                                                      |

|--------------------------|----------------|-----|-------|-------|------------------------------------------------------|

| m 방향 63도 이상, 70도 미만의 면   | (10-11)면<br>m면 | ○   | ◎     | ○     | 테라스 위 성장 성분이 크다. In 혼입은 좋지만, In 편석이 크다.              |

| m 방향 70도 이상, 71도 미만의 면   | (10-11)면<br>m면 | ○   | ◎     | ○     | 스텝단 성장 성분이 증가하는 만큼, In 편석은 개선 경향이 있다.                |

| m 방향 71도 이상, 72도 미만의 면   | (10-11)면<br>m면 | ○   | ○     | ◎     | 스텝단 성장 성분이 증가하는 만큼, 추가로 In 편석은 개선 경향이 있다.            |

| m방향 72도 이상, 78도 이하의 면    | (10-11)면<br>m면 | ○   | ○     | ◎◎    | 테라스 위 성장과 스텝단 성장 성분의 랠런스가 좋고, In 혼입도 양호하고 In 편석도 작다. |

| m방향 78도보다 크고, 79도 이하의 면  | (10-11)면<br>m면 | ○   | ○     | ◎     | In 혼입의 점에서 약간 뒤떨어지지만, 스텝 밀도가 작다.                     |

| m 방향 79도보다 크고, 80도 미만의 면 | m면             | ○   | ○     | ○     | In 혼입의 점에서 약간 뒤떨어진다.                                 |