(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4345835号

(P4345835)

(45) 発行日 平成21年10月14日(2009.10.14)

(24) 登録日 平成21年7月24日(2009.7.24)

(51) Int.Cl.

H01L 23/36 (2006.01)

F 1

H01L 23/36

C

請求項の数 16 (全 11 頁)

(21) 出願番号 特願2007-84580 (P2007-84580)

(22) 出願日 平成19年3月28日 (2007.3.28)

(62) 分割の表示 特願平10-133602の分割

原出願日 平成10年5月15日 (1998.5.15)

(65) 公開番号 特開2007-173877 (P2007-173877A)

(43) 公開日 平成19年7月5日 (2007.7.5)

(審査請求日 平成19年3月28日 (2007.3.28)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100071135

弁理士 佐藤 強

(72) 発明者 原田 嘉治

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72) 発明者 鈴木 俊夫

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72) 発明者 岩宮 広記

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

配線基板上にヒートシンクを介して実装された半導体素子の熱を当該ヒートシンク及び上記配線基板のスルーホールを通じて放熱する構成の半導体装置の製造方法において、前記ヒートシンクをスペーサ部材により前記配線基板との間に隙間部を形成した状態で実装してから、前記配線基板をはんだフローすることにより前記スルーホール及び前記ヒートシンクと前記配線基板との隙間部にはんだを充填したことを特徴とする半導体装置の製造方法。

## 【請求項 2】

配線基板上に実装された半導体素子の熱を当該配線基板のスルーホールを通じて放熱する構成の半導体装置の製造方法において、

前記半導体素子をスペーサ部材により前記配線基板との間に隙間部を形成した状態で実装してから、前記配線基板をはんだフローすることにより前記スルーホール及び前記半導体素子と前記配線基板との隙間部にはんだを充填したことを特徴とする半導体装置の製造方法。

## 【請求項 3】

配線基板上にヒートシンクを介して実装された半導体素子の熱を当該ヒートシンク及び上記配線基板のスルーホールを通じて放熱する構成の半導体装置の製造方法において、

前記ヒートシンクを当該ヒートシンクの下面に形成された溝部が前記配線基板のスルーホールと連通した状態で前記配線基板に接着してから、前記配線基板をはんだフローする

ことにより前記スルーホール及び前記ヒートシンクの溝部にはんだを充填したことを特徴とする半導体装置の製造方法。

【請求項 4】

前記スペーサ部材は、前記配線基板上若しくは前記半導体素子の下面に設けられた凸部であることを特徴とする請求項 1 または 2 記載の半導体装置の製造方法。

【請求項 5】

前記スペーサ部材は、接着剤であることを特徴とする請求項 1 または 2 記載の半導体装置の製造方法。

【請求項 6】

前記スペーサ部材ははんだペーストであり、

10

前記配線基板をリフローすることにより前記半導体素子若しくは前記ヒートシンクを当該配線基板との間に隙間部を形成した状態に保持したことを特徴とする請求項 1 または 2 記載の半導体装置の製造方法。

【請求項 7】

前記はんだペーストが塗布される金属パターンは、前記スルーホールと接続された金属パターンと分離して設けられていることを特徴とする請求項 6 記載の半導体装置の製造方法。

【請求項 8】

前記半導体素子は前記ヒートシンクと伝熱的に一体化された状態でモールドされていると共に、そのモールドパッケージから前記ヒートシンクが外部に露出していることを特徴とする請求項 1 または請求項 3 乃至 7 の何れかに記載の半導体装置の製造方法。

20

【請求項 9】

配線基板上にヒートシンクを介して実装された半導体素子の熱を当該ヒートシンク及び上記配線基板のスルーホールを通じて放熱する構成の半導体装置において、

前記ヒートシンクと前記配線基板との間にスペーサ部材を設けることによって隙間部が形成されており、前記スルーホール及び前記ヒートシンクと前記配線基板との隙間部にははんだが充填されていることを特徴とする半導体装置。

【請求項 10】

配線基板上に実装された半導体素子の熱を当該配線基板のスルーホールを通じて放熱する構成の半導体装置において、

30

前記半導体素子と前記配線基板との間にスペーサ部材を設けることによって隙間部が形成されており、前記スルーホール及び前記半導体素子と前記配線基板との隙間部にははんだが充填されていることを特徴とする半導体装置。

【請求項 11】

配線基板上にヒートシンクを介して実装された半導体素子の熱を当該ヒートシンク及び上記配線基板のスルーホールを通じて放熱する構成の半導体装置において、

前記ヒートシンクの下面には前記配線基板のスルーホールと連通した溝部が形成されており、前記スルーホール及び前記ヒートシンクの溝部にははんだが充填されていることを特徴とする半導体装置。

【請求項 12】

前記スペーサ部材は、前記配線基板上若しくは前記半導体素子の下面に設けられた凸部であることを特徴とする請求項 9 または 10 記載の半導体装置。

40

【請求項 13】

前記スペーサ部材は、接着剤であることを特徴とする請求項 9 または 10 記載の半導体装置。

【請求項 14】

前記スペーサ部材ははんだペーストであることを特徴とする請求項 9 または 10 記載の半導体装置。

【請求項 15】

前記はんだペーストが塗布される金属パターンは、前記スルーホールと接続された金属

50

パターンと分離して設けられていることを特徴とする請求項 1 4 記載の半導体装置。

**【請求項 1 6】**

前記半導体素子は前記ヒートシンクと伝熱的に一体化された状態でモールドされていると共に、そのモールドパッケージから前記ヒートシンクが外部に露出していることを特徴とする請求項 9 または請求項 1 1 乃至 1 5 の何れかに記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、配線基板に実装された半導体素子の熱をスルーホールを通じて放熱する手段を改善した半導体装置及びその製造方法に関する。 10

**【背景技術】**

**【0 0 0 2】**

従来より、配線基板上に実装された半導体素子の熱を放熱する手段として、種々の手段が提案されている。

**【特許文献 1】特開平 4 - 2 7 9 0 9 7 号公報**

**【特許文献 2】特開平 9 - 6 9 5 9 2 号公報**

**【特許文献 3】特開平 8 - 7 8 7 9 5 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0 0 0 3】**

この種の手段の一例として、配線基板に半導体素子を実装した構造において半導体素子が大電力用である場合には、配線基板の熱抵抗が大きいことから、半導体素子からの周囲への放熱性が問題になる。この問題に対処するために、特許文献 1、特許文献 2 のものがある。これらは、図 1 0 に示すように配線基板 1 に熱伝導の良好なスルーホール 2 を形成したり、図 1 1 に示すように配線基板 1 に熱伝導の良好な高熱伝導領域 3 を設けた上で、配線基板 1 上に半導体素子 4 を実装し、当該半導体素子 4 から発生した熱を、熱伝導の良好なスルーホール 2 或いは高熱伝導領域 3 を通じて配線基板 1 の裏面に設けられた放熱層 5 に逃がすことにより、放熱性を高めるものである。

**【0 0 0 4】**

しかしながら、このような構成では、配線基板 1 の裏面側に放熱層 5 を設ける構成であることから、その領域にはコンデンサ或いは抵抗等の部品を実装できないという問題がある。また、図 1 2 に示すように放熱層 5 を配線基板 1 中に設け、表裏の両面に絶縁層 6 を形成する構成の場合は、裏面にも部品が実装できるものの、この絶縁層 6 により放熱性が低下してしまうという不具合を生じる。 30

**【0 0 0 5】**

一方、配線基板の放熱性を高める手段としては、特許文献 3 に示されるように、配線基板にスルーホールを形成し、半導体素子の熱を配線基板の裏面に逃がす構造が提案されている。

しかしながら、通常の配線基板の製造方法で形成されるスルーホールは 0 . 3 ~ 1 . 0 mm 程度の孔の内壁に 10 ~ 20  $\mu$ m 程度の銅のメッキが施されているだけでほとんどは空洞であり、熱伝導の効果は小さい。この場合、スルーホール内を例えははんだで充填することによる熱伝導を高めることが望ましいが、半導体素子或いはその他の部品を配線基板に実装する工程においてスルーホール内にははんだを充填することができるものの、スルーホール内をはんだが完全に充填することはできない。つまり、半導体素子を配線基板にはんだ付けする構成では、通常他の表面実装部品と同様にはんだペースト印刷によりはんだをスルーホールに充填することができるが、1 回の印刷で供給されるはんだ量は厚さにして約 100  $\mu$ m 程度が普通であり、スルーホール内を完全に埋めるには十分ではない。このため、十分なはんだ量を供給するためには、ペーストの複数回印刷或いはディスペンスによるはんだ供給を追加して実施する必要があり、工程増加につながる。 40

**【0 0 0 6】**

10

20

30

40

50

本発明は上記事情に鑑みてなされたもので、その目的は、配線基板上に実装された半導体素子の熱をスルーホールを通じて確実に放熱することができる半導体装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0008】

請求項3の発明によれば、ヒートシンクを配線基板に接着した状態では、ヒートシンクの下面に形成された溝部が配線基板のスルーホールと連通する。

そして、配線基板をはんだフローすると、スルーホール内をはんだが上昇して充填されると共に、はんだがヒートシンクの溝部内に濡れ拡がって充填される。これにより、ヒートシンクに実装された半導体素子の熱はヒートシンクの溝部内及びスルーホール内に充填されたはんだを通じて効率よく放熱される。 10

【0009】

請求項2の発明によれば、半導体素子を配線基板上に実装すると、スペース部材により半導体素子と配線基板との間に隙間部が形成される。

そして、配線基板をはんだフローすると、スルーホール内にはんだが上昇して充填されると共に、半導体素子と配線基板との隙間部にはんだが濡れ拡がって充填される。これにより、半導体素子の熱は当該半導体素子と配線基板との間の隙間部及びスルーホール内に充填されたはんだを通じて効率よく放熱される。

【0010】

請求項1の発明によれば、ヒートシンクを配線基板上に実装すると、スペース部材によりヒートシンクと配線基板との間に隙間部が形成される。 20

そして、配線基板をはんだフローすると、スルーホール内にはんだが上昇して充填されると共に、ヒートシンクと配線基板との間の隙間部にはんだが濡れ拡がって充填される。これにより、半導体素子の熱はヒートシンクと配線基板との隙間部及びスルーホール内に充填されたはんだを通じて効率よく放熱される。

【0011】

請求項7の発明によれば、はんだペーストが溶解することによりはんだが濡れ拡がるもの、はんだペーストが塗布される金属パターンはスルーホールと接合された金属パターンと分離して設けられているので、はんだがスルーホールまで濡れ拡がってしまうことはなく、半導体素子またはヒートシンクと配線基板との間に隙間部を確実に形成することができる。 30

請求項8の発明によれば、本発明をICパッケージに適用することが可能となる。

また、請求項9乃至16の発明によれば、上記請求項1乃至8と同様の効果を奏する半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0012】

(参考の形態)

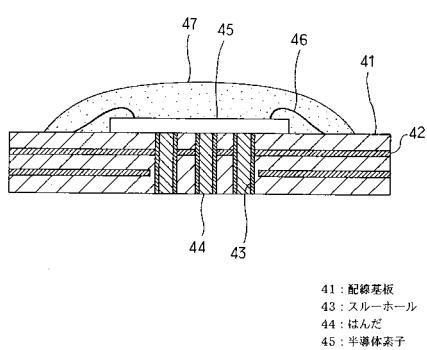

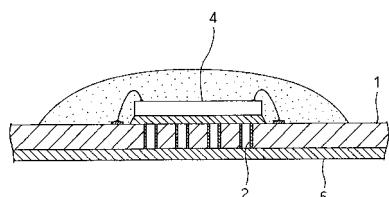

以下、本発明の参考の形態を図1及び図2を参照して説明する。

図1は半導体装置の断面を模式的に示している。この図1において、プリント基板41には内層配線による放熱層42が形成されていると共に、その放熱層42を貫通するようにスルーホール43が形成されている。このスルーホール43の内部ははんだ44がほぼ完全にボイド無く充填されている。 40

【0013】

プリント基板41においてスルーホール43上となる位置にICチップ45が実装されており、そのICチップ45とプリント基板41とがワイヤ46により接続されている。また、ICチップ45全体は封止樹脂47で充填されている。このような構成により、ICチップ45の熱はスルーホール43に充填されたはんだ44を通じてプリント基板41の裏面及び放熱層42に効果的に放熱することができる。

【0014】

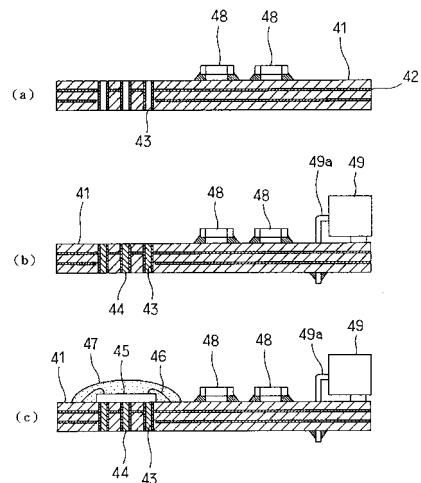

図2は上記構成の半導体装置の製造工程を示している。

10

20

30

40

50

(a) まず、プリント基板41の表面に表面実装部品48をはんだ印刷法を使用したりフローはんだ付けによりはんだ付けする。

(b) 次に、リード部品49のリード49aをプリント基板41のスルーホールに挿入し、プリント基板41の裏面からはんだフローではんだ付けする。このとき、ICチップ45が実装されるべき部位にある放熱用のスルーホール43内に表面張力によりはんだ44が上昇して充填される。

(c) その後、プリント基板41のスルーホール43上となる位置にICチップ45を実装し、ワイヤ46によりICチップ45上の電極とプリント基板41上の電極とを接続してから、封止樹脂47を充填する。これにより、COB(Chip On Board)実装が完成する。

10

#### 【0015】

このような構成によれば、はんだフローによるはんだ付けを、スルーホール43上にICチップ45が実装されていない状態で行うようにしたので、スルーホール43の基板表面側の開口が保たれ、スルーホール43へのはんだの充填を円滑に行うことができ、ボイドの発生を防止することができる。

#### 【0016】

この場合、スルーホール43を有する構造においてははんだフローによるはんだ付けは必ず必要であることから、工程が増加することはない。

また、この参考の形態は、図1に示すような部品構成の場合の工程であるが、この他の場合にも、はんだ充填時にスルーホール43の開口部が保たれる工程であれば、自由に工程順序は設定可能である。

20

#### 【0017】

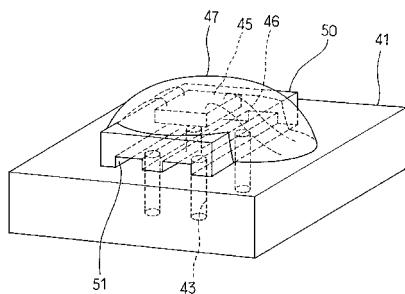

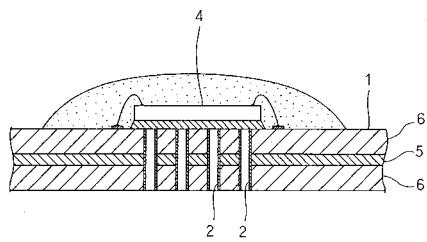

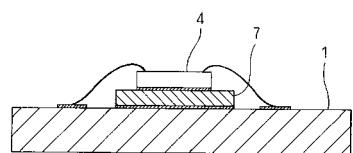

##### (第1の実施の形態)

次に本発明の第1の実施の形態を、半導体装置を斜視して模式的に示す図3及び断面を模式的に示す図4を参照して説明する。この第1の実施の形態は、半導体基板の製作順序を変更することなくスルーホール内にはんだをボイドなく充填したことを特徴とする。

即ち、上記参考の形態では、表面実装部品48とICチップ45の実装とは別工程になるが、これらの部品を同一工程または連続工程での実装の方がライン上都合が良い場合が多い。特に、両者共はんだ付け実装の場合は、1回のはんだ印刷で両者共実装可能であり、効率がよい。

30

また、リード部品のような比較的大形の部品がある上でのCOB実装は、ワイヤボンド工程等で難点もあるため、避ける方が好ましい場合もある。

#### 【0018】

しかしながら、このような構成を採用した場合は、図2に示す工程順が(a) (c) (b)となり、はんだフロー時にはスルーホール43の開口部がICチップ45により閉鎖されてしまって、はんだフロー時にははんだがスルーホール43を上昇しなくなり、ボイドが発生するようになる。

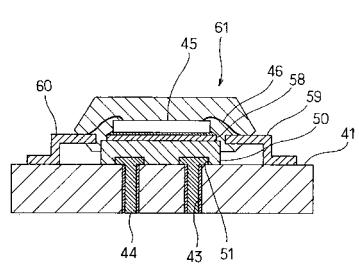

#### 【0019】

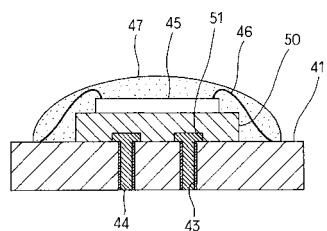

そこで、この第1の実施の形態では、ICチップ45の下にヒートシンク50を使用するようにした。このヒートシンク50はICチップ45が短時間で大電力を発生する場合などは一時的な熱の吸収のために従来構造でも使用されるものであり、斯様なICチップ45の実装に際しては新たな付加構成材料とはならない。但し、従来のヒートシンクは通常箱形の形状であるが、本実施の形態のヒートシンクはスルーホール43の開口部を閉鎖しないように下面に溝部51を設けた構造が採用されている。

40

#### 【0020】

この場合、プリント基板41上にヒートシンク50を接着すると共に、そのヒートシンク50上にICチップ45を接着した状態ではんだフローすると、プリント基板41のスルーホール43はヒートシンク50の溝部51を通じて開口しているので、はんだフロー時にははんだがスルーホール43を上昇するようになる。このとき、ヒートシンク50の溝部51の中もはんだが濡れ拡がって充填されることから、ヒートシンク50の熱伝導効果

50

及び吸熱効果も向上する。

【0021】

このような構成によれば、従来の製造方法を採用しながら、スルーホール43及びヒートシンク50の溝部51にはんだをボイドなく充填することができるので、ICチップ45の放熱性を高めながら容易に実施することができる。

この場合、ヒートシンク50の形状は、図3及び図4に示す形状に限定されることなく、スルーホール43の開口部の抜け道を形成する形状であればどのような形状であってもよい。

尚、本実施の形態では、封止樹脂47はヒートシンク50の溝部51によるスルーホール43の抜け道を閉鎖しないように塗布する必要がある。

10

【0022】

(第2の実施の形態)

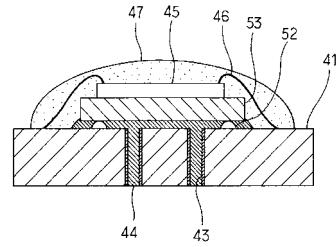

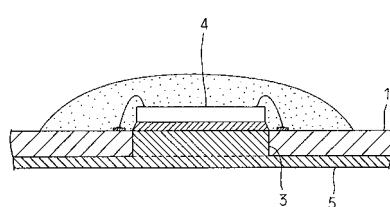

次に本発明の第2の実施の形態を半導体装置の断面を模式的に示す図5を参照して説明する。

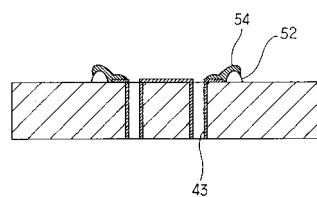

上記第1の実施の形態では、ヒートシンクに溝部を形成する等の加工を施したが、本実施の形態では、従来通りの箱形の単純な構造のヒートシンクを用いることを特徴とする。

即ち、プリント基板41の表面に部分的に凸部52(スペーサ部材に相当)を形成し、その上にヒートシンク53を載置することで、プリント基板41とヒートシンク53との間に隙間部を形成し、その隙間部を通じてスルーホール43の抜け道を形成するようにした。この凸部52はダムシルク印刷により形成することができる。このダムシルク印刷とは、通常のCOB実装構造で用いられるもので、液状封止樹脂の流れ止めのため、ICチップ周囲に印刷で形成される枠を形成するのに用いられるもので、高さが数十μm~数百μm程度のものである。このダムシルク印刷時に凸部52も同時に印刷することにより工程及びコストが増加することはない。勿論、この凸部52は通常のシルク印刷により形成するようにしてもよいものの、この場合、凸部52の高さは低くなる。

20

【0023】

このような構成によれば、第1の実施の形態と同様な作用効果を得ることができる。

尚、凸部52としては小さな絶縁性部品を接着によりプリント基板41に設けるようにしてもよい。

また、ヒートシンク53の下面是平面でよいことから、ヒートシンク53を用いることなくICチップ45をプリント基板41に直接装着する構成にも適用できる。この場合、ICチップ44下面がはんだ接合可能な材料となっていれば、フローはんだによるはんだがICチップ45に直接接合されるため、熱伝導効果は高くなる。

30

【0024】

また、ICチップ45の下面にバンプを形成することによりICチップ45とプリント基板41との間に隙間部を形成するようにしてもよい。

また、ヒートシンク53またはICチップ45をプリント基板41に接着剤により装着するようにしてもよく、この場合は、スルーホール43の開口部を閉鎖しなければ凸部に接着しても、或いはプリント基板41の表面に直接接着してもよい。

40

【0025】

さらに、ヒートシンク53またはICチップ45をプリント基板41にはんだで接続する場合は、プリント基板41上の電極にしかはんだを接合することができないが、凸部52の高さが十分に高く、はんだペーストの印刷の高さがそれより低い場合は、電極上のみ印刷したのでは接合が困難となるため、図6に示すようにはんだペースト54(スペーサ部材に相当)を凸部52の上へもはみ出して印刷する。このとき、はんだペースト54がスルーホール43を塞がないようにする必要がある。

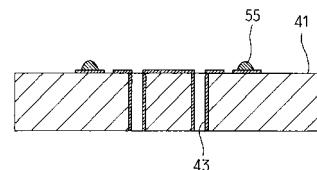

【0026】

また、はんだまたは接着剤(スペーサ部材に相当)によりICチップ45とプリント基板41との間に隙間部を形成するようにしてもよい。つまり、図7に示すように、はんだ(または接着剤)55をスルーホール43の開口部を塞がないように部分的に塗布または

50

印刷して I C チップ 4 5 を実装した状態でリフローすることによりプリント基板 4 1 に接合する。

このとき、はんだ（または接着剤）5 5 は I C チップ 4 5 の全面には拡散せず隙間ができる、その隙間の高さははんだまたは接着剤の接合高さ分だけ確保されることになる。

【 0 0 2 7 】

このような構成によれば、特別な形状のヒートシンクを用いたり、プリント基板 4 1 上に特別な部品を接合したりすることなく、スルーホール 4 3 内にはんだをボイドなく充填することができるので、I C チップ 4 5 の放熱性を高めることができる。

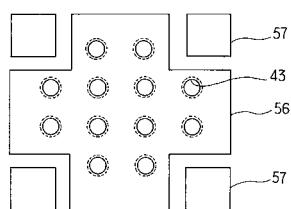

【 0 0 2 8 】

尚、I C チップ 4 5 をプリント基板 4 1 にはんだ接合する場合は、溶融したはんだは電極上を横に濡れ拡がる性質があるため、プリント基板上の電極パターンは図 8 に示すようにスルーホール 4 3 につながる電極 5 6 とはんだが接合される電極 5 7（金属パターンに相当）を分離して形成するのが望ましい。10

また、いずれの構成においても封止樹脂は第 1 の実施の形態と同様、スルーホールの抜け道を塞ぐことのないように塗布する必要がある。

【 0 0 2 9 】

（第 3 の実施の形態）

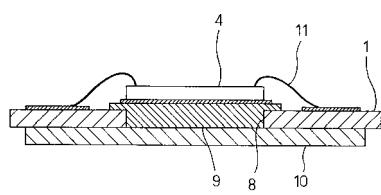

次に本発明をモールド I C に適用した第 3 の実施の形態を半導体装置の断面を模式的に示す図 9 を参照して説明する。

即ち、上記第 1 の実施の形態と同一形状のヒートシンク 5 0 上にリードフレーム 5 8 を介して I C チップ 4 5 が実装されており、その I C チップ 4 5 上の電極がワイヤ 4 5 によりリードフレーム 5 9, 6 0 と接続されている。20

【 0 0 3 0 】

ここで、I C チップ 4 5 全体は樹脂によりパッケージされており、斯様な構成のモールド I C 6 1 の下面からヒートシンク 5 0 の下面が露出している。この場合、モールド I C 6 1 がプリント基板 4 1 に実装された状態で、プリント基板 4 1 に形成されたスルーホール 4 3 とヒートシンク 5 0 の溝部 5 1 とが連通するようになる。

そして、このような構成のモールド I C 6 1 をはんだフローすると、はんだがスルーホール 4 3 内を上昇してヒートシンク 5 0 の溝部 5 1 に濡れ拡がって充填されるようになる。30

【 0 0 3 1 】

このような構成によれば、モールド I C 6 1 をプリント基板 4 1 に実装した状態ではんだフローすることができるので、第 2 の実施の形態と同様の作用効果を得ることができる。

尚、モールド I C 6 1 にヒートシンクがない場合であっても、モールド I C 6 1 自体の下面に溝等を設けても同様な作用効果を得ることができる。

【 図面の簡単な説明 】

【 0 0 3 2 】

【 図 1 】本発明の参考の形態における半導体装置の断面を示す模式図

【 図 2 】製造工程を示す図

40

【 図 3 】本発明の第 1 の実施の形態における半導体装置を示す斜視図

【 図 4 】半導体装置の断面を示す模式図

【 図 5 】本発明の第 2 の実施の形態における半導体装置の断面を示す模式図

【 図 6 】変形の形態におけるプリント基板の断面を示す模式図

【 図 7 】変形の形態におけるプリント基板の断面を示す模式図

【 図 8 】電極を示す図

【 図 9 】本発明の第 3 の実施の形態におけるモールド I C の断面を示す模式図

【 図 1 0 】従来例における半導体装置の断面を示す模式図

【 図 1 1 】他の従来例を示す図 1 0 相当図

【 図 1 2 】他の従来例を示す図 1 0 相当図

50

【図13】他の従来例を示す図10相当図

【図14】他の従来例を示す図10相当図

【符号の説明】

【0033】

図面中、41はプリント基板(配線基板)、43はスルーホール、44ははんだ、45はICチップ(半導体素子)、50はヒートシンク、52は凸部(スペーサ部材)、53はヒートシンク、54ははんだペースト(スペーサ部材)、55ははんだ(スペーサ部材)、56は電極(金属パターン)、61はモールドICである。

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図14】

【図13】

---

フロントページの続き

審査官 日比野 隆治

(56)参考文献 特開平08-213510 (JP, A)

特開平09-153564 (JP, A)

特開平06-077347 (JP, A)

特開平09-246290 (JP, A)

特開平07-106721 (JP, A)

特開平06-260532 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/36

H05K 3/40