# PATENT SPECIFICATION

(11)1 599 552

(21) Application No. 516/78 (31) Convention Application (22) Filed 6 Jan. 1978

(31) Convention Application No. 52/000505

(32) Filed 6 Jan. 1977 in

(33) Japan (JP)

(44) Complete Specification published 7 Oct. 1981

(51) INT CL<sup>3</sup> G03B 13/20

(52) Index at acceptance

H4D 271 275 276 711 730 747 760 761 773 775 77X 782

G2A 202 209 C1 C23 LK

## (54) RANGE DETECTING METHOD AND APPARATUS

(71) We, CANON KABUSHIKI, KAISHA, a Japanese company of 30-2, 3chome, Shimomaruko, Ohta-ku, Tokyo, Japan, do hereby declare the invention, for which we pray that a patent may be granted to us and the method by which it is to be performed, to be particularly described in

and by the following statement:-

This invention relates to a range detecting method and apparatus, and more particularly, it is concerned with a range detecting method and apparatus in which the range of an object is measured by electrically detecting a relative displacement between two images of the object using the distance measurement principle of a base line double-image coincidence type range finder. In the methods and devices to be described herein image signals concerning the two images are obtained by scanning the two images, the relative displacement between the two images being detected by processing these image signals.

There have previously been proposed various types of electric double-image coincidence detection type range detecting method and apparatus as outlined above, or automatic focus adjusting devices for photographic cameras, etc. using such range finding devices. More particularly various known range finding devices operate to form two images of an object with a relative displacement according to the object distance upon photo-electric light receiving means, the displacement, or positional difference, between these two images is determined from outputs of the light receiving means thereby permitting calculation of the distances to the object for

the range finding.

25

For example, according to Japanese Patent Publication No. 48-5733, there is proposed a range detecting method and apparatus in the form of an automatic focus adjusting device, wherein a pair of photoconductive elements which are so constructed that their resistance values may vary in accordance with positional changes

in an image on the light receiving surfaces thereof are juxtaposed, and then images of the one and the same object are formed on these elements by means of a range finding optical system comprising a pair of focussing lenses fixedly disposed at a certain separation on the base line so that a distance to the object may be detected by measuring the difference between the resistance values of these two elements by utilizing the principle that a relative displacement of the image forming position on each element corresponds to a distance to the object.

In this disclosed device, however, the photo-conductive element per se is of a very specific structure, and accordingly the use of a pair of such elements presents a difficulty in the matching of the response characteristics of both such elements. As a result the precision of detection is impaired by an increased error signal, and inaccurate distance measurement will arise since coincidence of the resistance values in both elements does not accurately represent a correspondence of the positions of the images on the respective elements.

With a view to overcoming this problem,

there has been proposed a range detecting device, or an automatic focus adjusting device, in which image signals concerning the two images are obtained by scanning them using a photo-electric light receiving means, and then the relative displacement is measured using the two image scanning signals, and the object distance is calculated, or the focus of the objective lens system in a camera is automatically adjusted using the data concerning this relative displacement.

For example, U.S. Patent No. 3,898,676, teaches an automatic focus adjusting device of a construction, wherein arrays of photosensors are used as the photo-electric light receiving means for receiving the two images, and, by driving these photo-sensor arrays simultaneously, photo-electric outputs of the photo-sensors in the arrays one obtained in a timed sequence to thereby

50

55

65

70

75

80

70

80

85

90

95

120

scan the two images simultaneously in a purely electrical manner, and image signals thus obtained on these two images are converted to continuous waveform signals by low pass filters. Such wave form signals are introduced into a phase discriminator to detect a phase difference between these image scanning signals, and a servo-motor is actuated by an output from the phase discriminator to cause the objective lens system to shift along its optical axis, in association with which one of the two images is shifted with respect to the other, whereby the "in-focus position" of the objective lens system to the object is indicated when the phase difference between the image scanning signals for the two images becomes zero, in other words, a point where the relative displacement between the two images on the respective photosensor arrays becomes zero.

Also, according to Laid-Open Japanese Patent Application No. 51-45556 there is proposed a method and an apparatus for detecting the range of an object, in which self-scanning image sensors (a kind of photo-sensor array) are utilized as the photo-electric light receiving means for receiving light from two images of the object, then the two images are repeatedly scanned by these image sensors, the time of commencement of scanning of one of the image sensors being varied by a variable delay circuit relative to the time of commencement of the scanning of the other image sensor, while coincidence and noncoincidence of the image signals concerning the two images obtained from the image sensors is detected by means of a coincidence detection circuit, and the relative displacement of the two images, i.e. representative of the object distance, is determined directly from the period between the start times of the scans by the two image sensors in a scanning operation during which coincidence is detected by the abovementioned coincidence detection

In the methods and devices as disclosed in these U.S. Patent No. 3 898 676 and Laid-Open Japanese Patent Application No. 51-45556, the two images of an object to be formed by the range finding optical system are scanned purely electrically using photosensor arrays or image sensors known as, in particular, Photo-Diode Array, CCD (Charge Coupled Device), or BBD (Bucket Brigade Device), and so on, and the image scanning signals concerning the two images 60 to be obtained at this time are used for the distance detection or focus detection. In particular, since the image is scanned in a purely electrical manner utilizing the photosensor arrays or image sensors, accurate signal corresponding exactly to the image

pattern can be used, on account of which further improvement in precision of the distance detection or the focus detection can be expected.

However, these methods and apparatuses as have heretofore been proposed contain therein many problems still to be solved such as, for example, concrete method for processing the abovementioned image scanning signals as one aspect, hence their reduction in practice is far-reaching.

For example, in the device proposed in the above-described U.S. Patent No. 3,898,676, as already mentioned above, the image scanning signals are converted to the waveform signals by causing them to pass through low pass filters, after which the waveform signals are introduced into the phase discriminator, where detection is conducted to detect any phase difference between the two signals. In this case, since the phase discriminator deals with the waveform signals, in particular, the device becomes complicated in construction, and hence unreliable in operation, and it is not possible accurately to detect small phase differences. Accordingly the operation of the phase discriminator as the automatic focussing device is unavoidably inaccurate.

Also, in the device as proposed in the above-discussed Laid-Open Japanese Patent Application No. 51-45556, there is merely adopted a differential amplifier or a combination of the differential amplifier and a comparator as the circuit for 100 detecting coincidence and non-coincidence of the two image scanning signals. In view, however, of the fact that the signals which the circuit deals with are time-sequential output signals from the image sensors, it is almost impossible to carry out detection of the coincidence and non-coincidence of the image scanning signals with such simple circuit construction.

Furthermore, in the method and 110 apparatus as proposed in this Japanese application, the scanning start timing of one of the image sensors it caused to vary with respect to the scanning start timing of the other image sensor by the use of a variable 115 delay circuit, and a period between the scanning start timings for these two image sensors is taken as the object distance. However, as has so far been well recognized, in utilizing the self-scanning type image sensors such as the photo-diode array of the charge accumulation type, CCD, or BBD, etc., if the scanning start timing, i.e., the timing for imparting the start pulse, is varied, the integration time, i.e., the effective light receiving time, also varies with the result that the level of the output signal varies. Accordingly, in the proposed method and device, since the scanning start timing of one of the image 130

sensors is caused to vary by the variable delay circuit with respect to the scanning start timing of the other image sensor, the two image scanning signals obtained are subject to variation in level so that a proper comparison of these two image scanning signals for detection of coincidence, cannot be made. Accordingly, the accuracy of the distance information obtained, or of the focusing operation so performed is in auestion.

According to the present invention there is provided a method of detecting the range of an object, comprising the steps of:—

deriving first and second mutually spaced images of the object from radiation passing from the object along different optical paths;

15

deriving quantized data concerning each of N successive elements of the first image and quantized data concerning each of M successive elements of the second image, wherein M is greater than N; and

detecting, on the basis of the quantized data concerning the N successive elements of the first image and the quantized data concerning the M successive elements of the second image, a location, within the M successive elements of the second image, of 30 one set of N successive elements which is most similar to the N successive elements of the first image, the said location being indicative of the said range of the object, the quantized data deriving step comprising the steps of:-

electrically sensing the elements of the first and second images to produce an electrical representation of each of the

40 setting the value of a variable quantization standard on the basis of at least a portion of the electrical representations produced by a previous said sensing step, and

45 quantizing, on the basis of the quantization standard so set, each of the electrical representations produced by the sensing step to produce the said quantized data.

50 According to the invention there is also provided a device for detecting the range of an object, comprising:-

optical means arranged to form first and second mutually spaced images of the object from radiation passing from the object along different optical paths;

image sensing means arranged for sensing the first and second images to produce an electrical representation of each of successive elements of the first and second images;

quantization standard setting means for setting the value of a variable quantization standard on the basis of at least a portion of the electrical representations produced by the sensing means;

quantization means for quantizing each of the electrical representations produced by the sensing means on the basis of the quantization standard previously set by the quantization standard determination means to produce quantized data concerning each of the elements of the first and second images; and

a detection system for receiving the quantized data from the quantization means and for detecting, on the basis of quantized data concerning N successive elements of the first image and quantized data concerning M successive elements of the second image, where M is greater than N, a location, within the M successive elements of the second image, of one set of N successive elements which is most similar to the N successive elements of the first image, the said location being indicative of the range of the object.

The value of said variable quantization standard may be derived from the electrical representations, produced by said previous sensing step, of the N elements of the said first image only. This value may be derived from that electrical representation having the greatest magnitude out of said at least a portion of electrical representations.

The variable quantization standard may comprise a threshold level determined by a preset proportion of said greatest magnitude.

The quantization step may comprise comparing each of the electrical representations with the quantization standard so as to produce as the quantized data, binary data on each element of said first and second images.

The quantized values are, in devices described herein, stored, as inputs, in first and second storage means where coincidence and non-coincidence of the quantized data signals stored therein are detected by coincidence detection means, while one of the sets of quantized data signals is caused to shift bit by bit relative to the other, and the shift bit quantity required until the quantized data signals of the same bit numbers concerning these first and second images become optimumly coincided are counted, thereby determining object distance from this shift bit quantity.

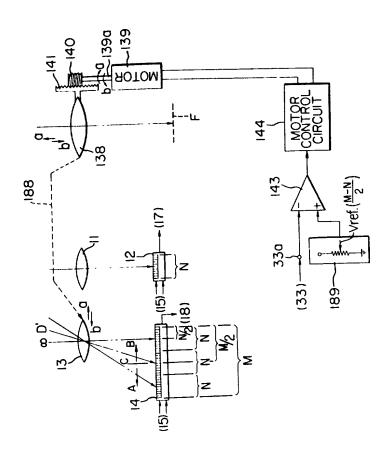

Preferred embodiments of the invention will now be described by way of example with reference to the accompanying drawings, in which:-

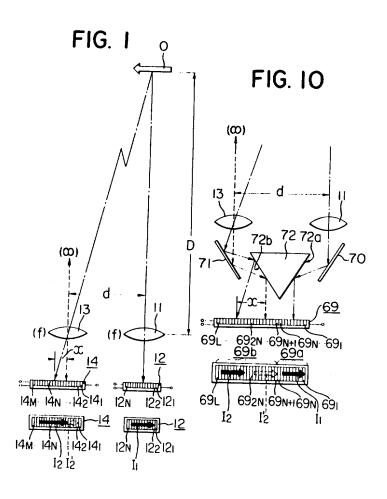

Figure 1 is a schematic diagram for explanation of the principle of the range detection according to the present invention:

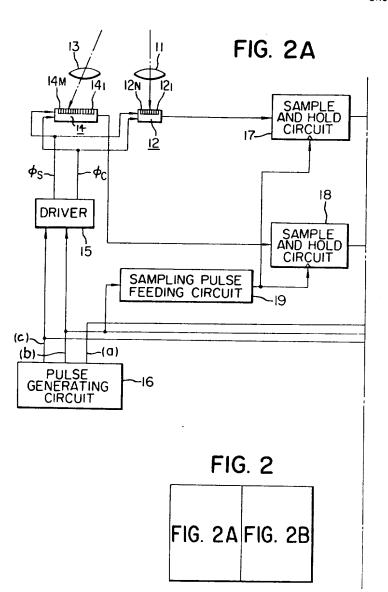

Figure 2 is a combination chart of Figures 2A and 2B which are block diagrams 85

90

65

70

75

80

95

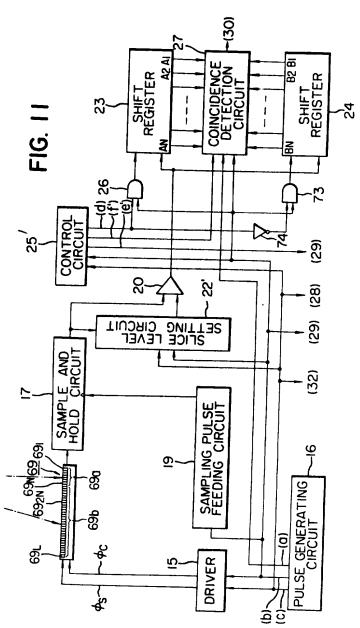

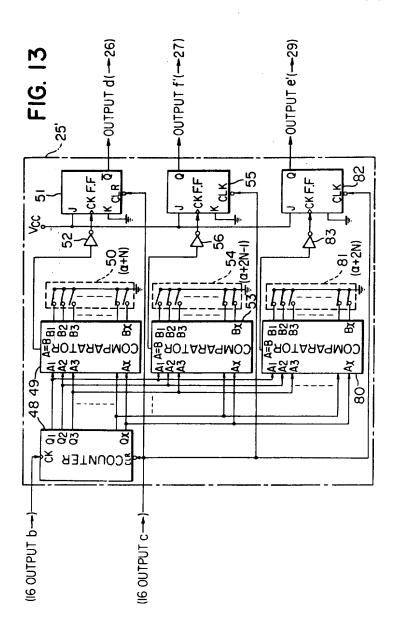

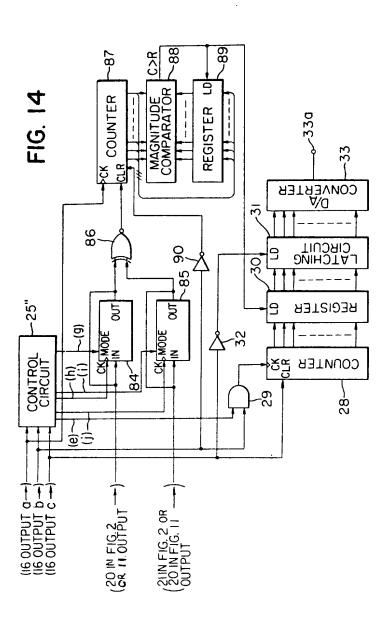

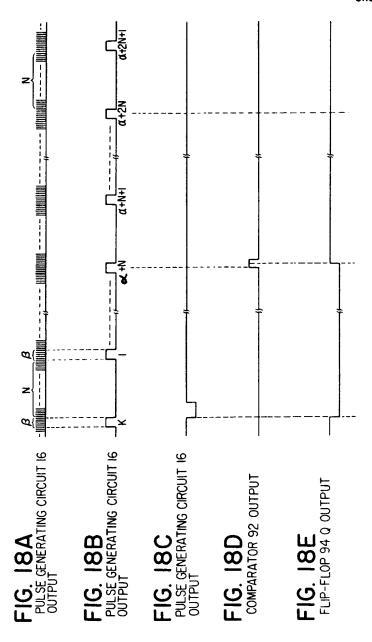

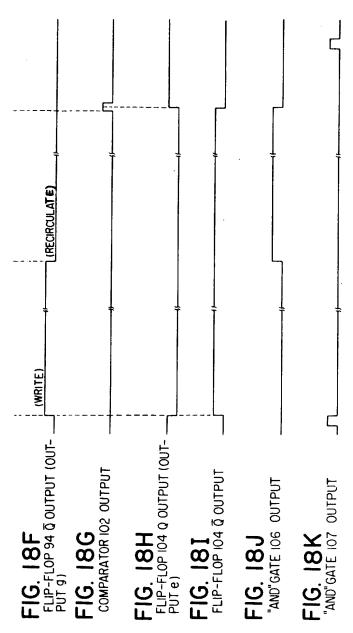

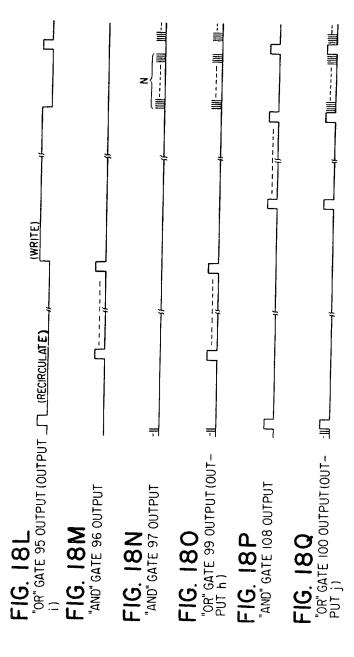

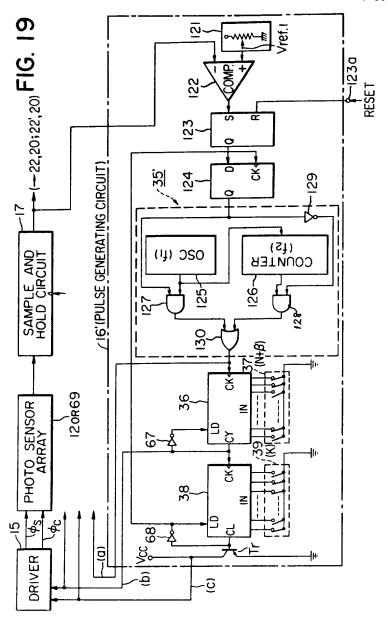

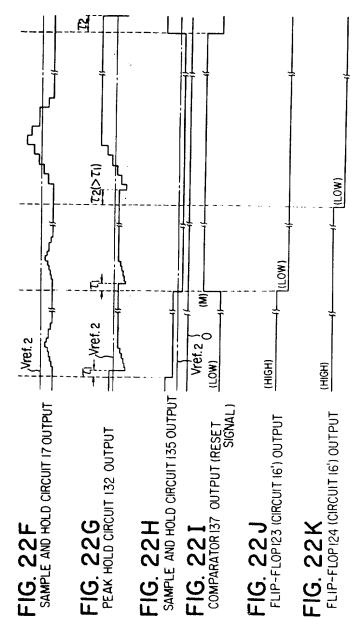

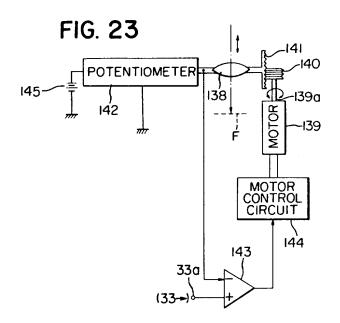

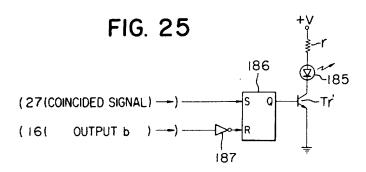

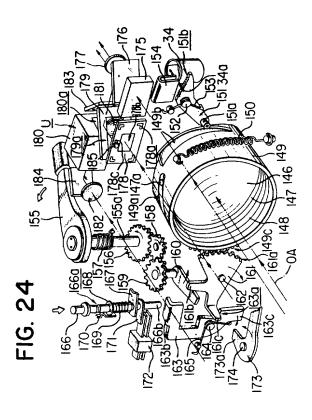

1,599,552 4 construction shown in Figure 14 is applied showing one embodiment of the circuit to the embodiment shown in Figure 11; construction of the present invention; Figures 3A to 3Q show various output Figures 18A to 18Q show various waveforms of the outputs from various waveforms of the outputs from the principal part of the circuit block diagram shown in circuit blocks in the control circuit shown in Figure 2; Figure 17; Figure 19 is a circuit construction Figure 4 is a circuit construction diagram diagram showing one concrete example of showing one concrete example of the pulse the pulse generating circuit, in which the generating circuit in the circuit construction light receiving time of the sensor arrays may 10 shown in Figure 2; 75 be automatically adjusted in accordance Figure 5 is a circuit construction diagram showing one concrete example of the slice with brightness of an object to be detected; level setting circuit in the circuit Figures 20A to 20I show various output waveforms of the outputs from the principal construction shown in Figure 2; circuit in the range detecting device shown Figure 6 is a circuit construction diagram in Figure 2 or 11 as well as in the pulse showing one concrete example of the generating circuit shown in Figure 19; control circuit in the circuit construction Figure 21 is a circuit construction shown in Figure 2; diagram showing one concrete example of Figure 7 is a circuit diagram of one the automatic resetting circuit applicable to concrete example of the coincidence 20 the pulse generating circuit shown in Figure 85 detecting circuit in the circuit construction shown in Figure 2; Figures 22A to 22K show various output Figures 8A to 8G show various output waveforms of the outputs from the principal waveforms of the outputs from the principal circuit blocks in the automatic resetting 25 part of the circuit block diagram in the circuit shown in Figure 21, the range coincidence detecting circuit of Figure 7; detecting device shown in Figure 2 or 11 as Figure 9 is a circuit diagram showing well as the pulse generating circuit shown in another concrete example of the Figure 19: coincidence detecting circuit in the circuit Figure 23 is a schematic diagram showing construction shown in Figure 2; 30 95 a general construction of one embodiment, Figure 10 is a schematic diagram showing in which the range detecting device shown another embodiment of the present in Figure 2 or 11 is applied to the automatic invention, in particular, the optical layout of focus adjusting system in optical apparatuses and appliances such as the device; 35 Figure 11 is a block diagram of an 100 photographic cameras, etc.; electrical circuit used in the construction of Figure 24 is a perspective view of a Figure 10 showing the construction of the principal mechanical construction of one principal elements different from the circuit concrete example, in which the range construction shown in Figure 2; detecting device shown in Figure 2 is Figure 12 is a circuit construction applied to the automatic focus adjustment 105 diagram showing one concrete example of system in a photographic camera; the slice level setting circuit shown in Figure 25 is a schematic circuit diagram Figure 11; showing a general construction of one Figure 13 is a circuit construction embodiment of the display circuit for displaying termination of the range diagram showing another concrete example of the control circuit applicable to the detecting operation in the automatic focus circuit shown in Figure 11; adjustment system shown in Figure 24; and Figure 26 is a schematic diagram showing Figure 14 is a block diagram of still a general construction of other another embodiment of the present embodiment, in which the range detecting invention showing a construction of the device shown in Figure 2 is applied to the main elements different from that shown in automatic focus adjustment system in Figure 2 or 11; Figure 15 is a circuit construction optical apparatuses and appliances such as diagram showing one concrete example of cameras, etc. Referring first to Figure 1, the principle 120 the control circuit when the circuit construction shown in Figure 14 is applied of the present invention will be explained. In the drawing, reference numerals 11 and to the embodiment shown in Figure 2; 13 designate a pair of focusing lenses for

range finding which are fixedly disposed at a

certain spacing defining a base line length,

and numerals 12 and 14 refer to photo-

sensor arrays fixedly disposed in

correspondence to the focusing lenses 11 and 13. The sensor array 12 consists of N

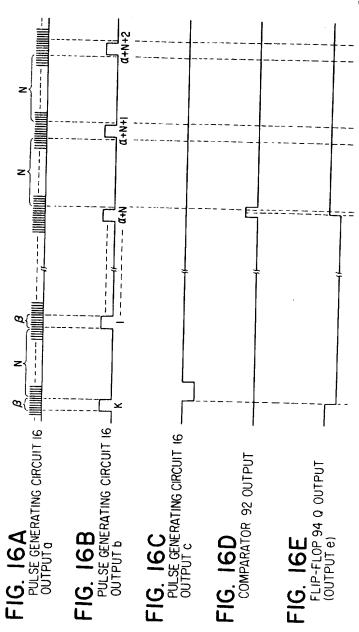

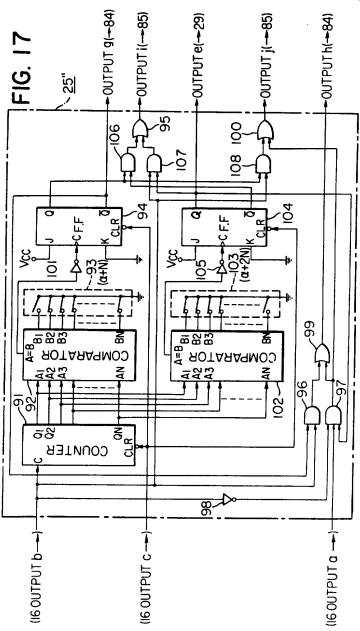

Figures 16A to 16K show various output

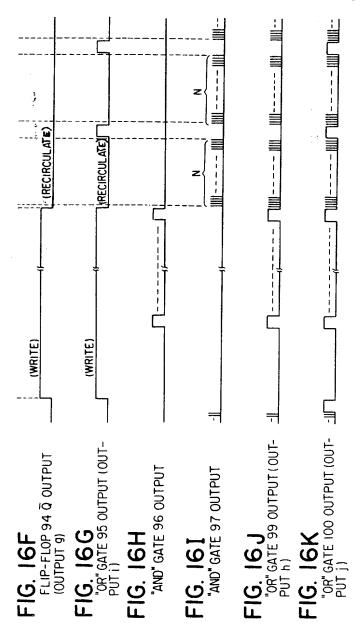

Figure 17 is a circuit construction

waveforms of the outputs from each circuit

block diagram in the control circuit shown

diagram showing one concrete example of

the control circuit when the circuit

in Figure 15;

70

75

85

90

95

105

115

numbers of very small photo-sensors  $12_1$ ,  $12_2$ , ...,  $12_N$  disposed linearly and regularly. The other sensor array 14 is of such a construction that M (where M is a number sufficiently larger than N) photo-sensors  $14_1$ ,  $14_2$ , ...,  $14_M$  of the same configuration as those photo-sensors  $12_1$ ,  $12_2$ , ...,  $12_N$  in the sensor array 12 are arranged linearly and regularly in the same manner.

In such constructional arrangement, an image of an object O is focussed on the sensor arrays 12 and 14 by the focussing lenses 11 and 13, respectively. In this case, the set of the lens 11 and the sensor array 12 is used for collimating the object O, hence the image I<sub>1</sub> of the object O formed by the lens 11 can always be focussed on a substantially fixed position on the sensor array 12 due to the optical axis of the lens 11 being made to coincide with the object O. In contrast to this, the image I, of the object formed by the lens 13 is at a relatively displaced position on the sensor array 14 with respect to the focussing position of the image  $\tilde{I}_1$  on the abovementioned sensor array 12 by an amount according to the distance upto the object O. The relative displacement of the focussing position of the image I<sub>2</sub> on the sensor array 14 with respect to the focussing position of the image I<sub>1</sub> on the sensor array 12 can be converted to a displacement variable x of the image of the object O from its focussing position on the sensor array 14 (this being designated by I'2 in the drawing) when the object is at infinity and the optical axis of the lens 13 intersects the object O, whereby a distance D to the object O can be

detected from this displacement variable x. In more detail, if the base line length between the lenses 11 and 13 is d and their focal length is f, the distance D up to the object O is represented from the abovementioned displacement variable x of the image position, as follows:—

### D=d.f/x

The displacement variable x can be determined from the size of the photosensors 14<sub>1</sub>, 14<sub>2</sub>, ..., 14<sub>M</sub> in the sensor array 14 and from the number of photosensors covering this displacement.

In order to determine this displacement variable x, the apparatus disclosed herein is so constructed that trains of image element signals are taken out time-sequentially from the photo-sensor arrays 12 and 14, respectively, in equal numbers (for example, N) and thereafter, these image element signal trains are consecutively converted into quantized, e.g. binary signals to be introduced as inputs into separate storage means. The quantized image element signal trains from the sensor array

12 are stored in one of the storage means, while the quantized image element signal trains from the sensor array 14 are sequentially shifted bit-by-bit, for example, by clock pulses, etc. in the other storage means. The stored signals are examined for coincidence between one storage means and the other every time a shifting takes place, and, count values obtained by counting the clock pulses used for shifting the quantized image element signal trains in the other storage means until the stored values in both storage means become most similar to each other, from the start of the shifting of the quantized image element signal trains from the sensor array 14 are used to determine the value of the abovementioned displacement variable x, and thus also the distance to the object O.

In the following, one physical embodiment of the present invention will be explained bearing in mind the general principle described in the forgoing.

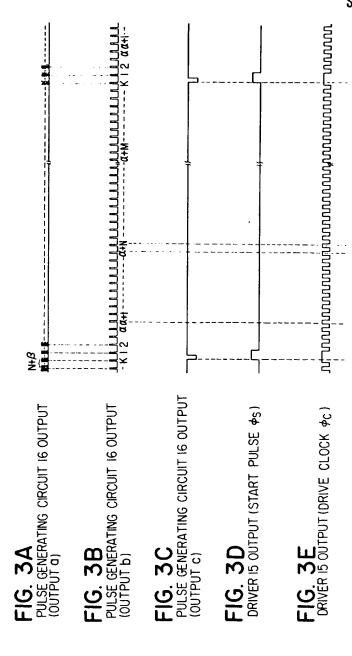

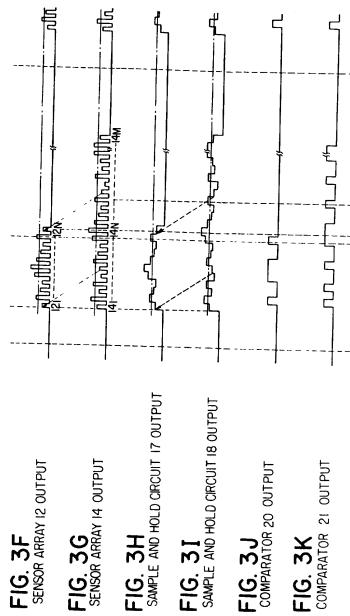

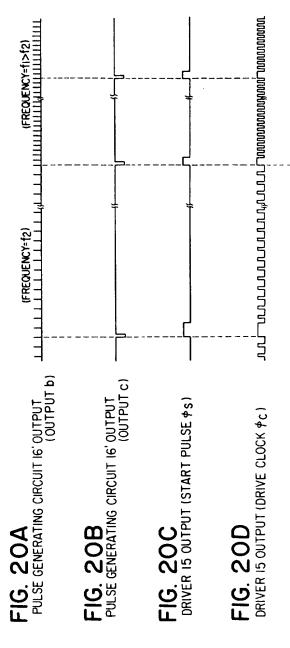

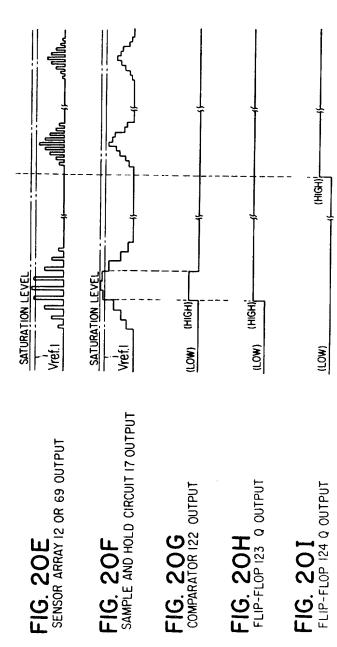

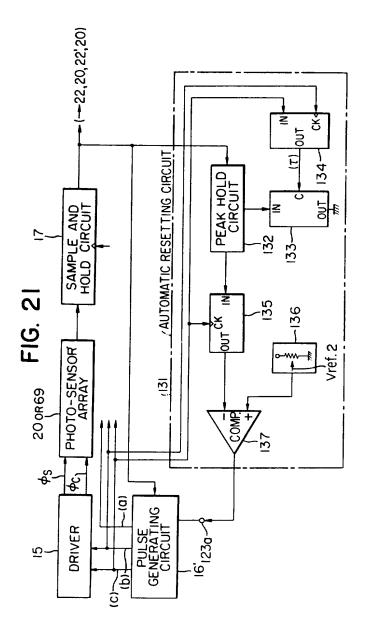

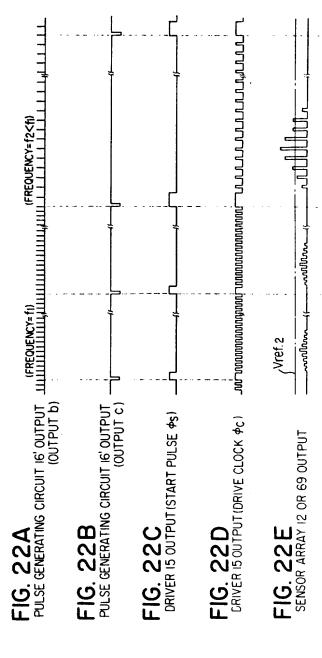

In Figure 2, which is composed of Figures 2A and 2B and which shows one embodiment of the present invention, the optical layout is exactly same as that shown in Figure 1 with the exception that selfscanning type sensor arrays are used as the photo-sensor arrays 12 and 14. In the drawing, a reference numeral 16 designates a pulse generating circuit which generates reference clock pulses required for driving the abovementioned sensor arrays 12 and 14 as well as sequential controls of the circuit elements to be described in the following. The circuit is so constructed that it may generate first reference clock pulses (output a) shown in Figure 3(A), second reference clock pulses (output b) shown in Figure 3(B) at a frequency determined by dividing the frequency of the first reference clock pulses by a factor  $M+\beta$ , and, further, third reference clock pulses (output c) shown in Figure 3( $\dot{C}$ ) at frequency determined by dividing the frequency of the second reference clock pulses by K (where: K is a number sufficiently larger than the number M of the sensors in the sensor array 14). A reference numeral 15 designates a driver for driving the abovementioned sensor arrays 12 and 14 based on the abovementioned second and third reference clock pulses to be generated as outputs from the pulse generating circuit 16. In this embodiment, the driver is so constructed that it may produce a start pulse 0, as shown in Figure 3(D) based on the third reference clock pulse (output c) and a drive clock  $\emptyset_c$  as shown in Figure 3(E) based on the second reference clock pulse (output b), and that, by applying these signals to the sensor arrays 12 and 14, it may output time-sequentially the image element signals from each

of the photo-sensors  $12_1 \dots 12_N$  and  $14_1$ ...  $14_{M}$  in the sensor arrays  $1\ddot{2}$  and 14, respectively, as shown in Figures 3(F) and (G). Incidentally, a four or two phase drive clock  $\emptyset_e$  is in practice used to drive the photosensor arrays. For the sake of ready understanding, however, the explanation herein will be made with reference to a drive

clock having a single phase. Reference numerals 17 and 18 designate sample and hold circuits which are connected respectively to the sensor arrays 12 and 14, and which, by being applied from a sampling pulse feeding circuit 19 with sampling pulses occurring simultaneously with the image element signals output from the sensor arrays 12 and 14 introduce thereinto the image element signal outputs from the sensor arrays 12 and 14 and hold them until subsequent sampling pulse is applied. Consequently, pulse-shaped image scanning signals from the sensor arrays 12 and 14 as shown in Figure 3(F) and (G) are converted by these sample and hold circuits 17 and 18 into continuous 100% duty signals, as shown in Figure 3(h) and (i), respectively. The abovementioned sampling pulse feeding circuit 19 is so constructed that it may introduce the second reference clock pulses (output b) from the pulse generating circuit 16 as the input thereinto where the clock pulses are shaped into pulses coincided with the output timing of the image element signals from the sensor arrays 12 and 14, after which the thus shaped pulses are applied to the sample and hold circuits 17 and 18 as the sampling pulses, whereby the sample and hold circuits 17 and 18 become able to capture and hold a peak in the rising (or a trailing) of the image element signals from the sensor arrays 12 and 14. Incidentally, where there is used a photo-sensor device such as a combination of photo-diode arrays and CCD, in which the continuous 100% duty signals, are directly obtainable, the sample and hold circuits 17 and 18 are not required.

Numerals 20 and 21 refer to comparators for binary conversion, by comparing each of the output signal levels from the sensors 12,  $\dots$  12<sub>N</sub> and 14<sub>1</sub>  $\dots$  14<sub>M</sub> in the sensor arrays 12 and 14 after the sampling and holding by the sample and hold circuits 17 and 18 with a slice level set in a slice level setting circuit 22 to produce an output "high" level signal when the signal level is higher than the slice level, and an output "low" level signal when the signal level is lower than the slice level. By these comparators 20 and 21, each of the output signals from each of the sensors 12, ... 12<sub>N</sub> and 14<sub>1</sub> ... 14<sub>M</sub> of the sensor arrays 12 and 14 after the sampling and holding operations by the abovementioned sample and hold circuits 17 and 18 are converted

into binary quantized signals as shown in Figure 3(J) and (K). The slice level to be established in the slice level setting circuit 22 is automatically determined on the basis of the outputs from sensor array 12 so as to produce optimum binary signal trains for comparison. The manner of predetermining the slice level will be described in greater detail later herein.

Reference numerals 23 and 24 respectively designate serial-in-parallel-out type shift registers for storing the respective quantized image element signal trains (cf. Figure 3, (J) and (K)) output from the respective comparators 20 and 21. In this embodiment, the shift registers are of N-bit  $(A_1 \ldots A_N \text{ and } B_1 \ldots B_N)$  construction in correspondence to the number of sensors in the sensor array 12, and are driven by the second referenc clock pulse (output b) from the pulse generating circuit 16 at the same clock speed in conformity with the emission speed of the image element signals from the sensor arrays 12 and 14. Accordingly, these shift registers function in such a manner that each of the quantized image element signals output by the comparators 20 and 21 is sequentially stored, while shifting the signals bit-by-bit for every clock pulse, and the thus stored quantized values can be produced as parallel outputs.

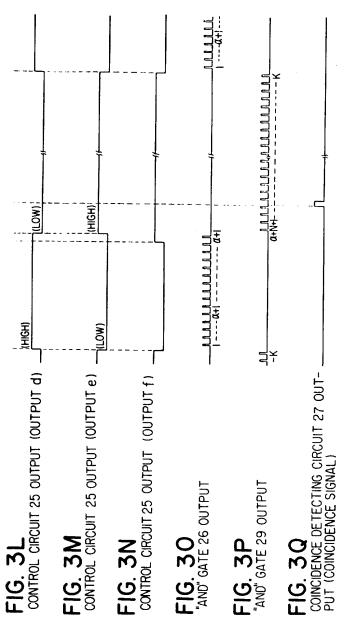

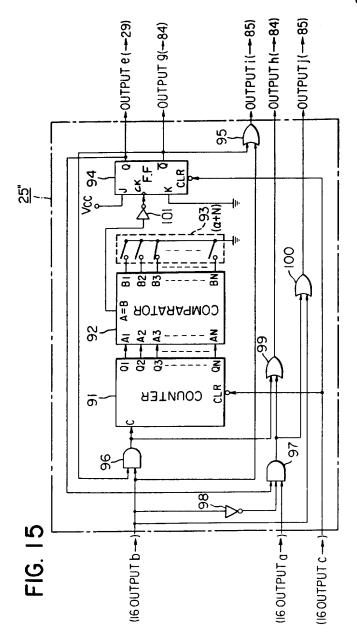

A reference numeral 25 designates a control circuit which controls feeding of the clock pulse for shifting to the shift register 23, feeding of the second reference clock pulse (output b) from the abovementioned pulse generating circuit 16 to a counter 28 which counts the number of second reference clock pulses (output b), and, further, operations of a coincidence detecting circuit to be described later. The control circuit is so constructed that is introduces as the inputs thereinto both the second reference clock pulse (output b) and the third reference clock pulse (output c) from the abovementioned pulse generating circuit 16, then applies to an "AND" gate 26 provided for congate 26 provided for confeeding of the shift trolling clock pulse to the shift register signal (output d) as shown Figure 3(L) which maintains a high level during a period from the generation of the third reference clock pulse (output c) upto the generation of the α+Nth pulse of the second reference clock pulse (output b) in the pulse generating circuit 16, and maintains a low level during a period from the generation of the  $\alpha$ +Nth pulse of the second reference clock pulse (output b) upto the generation, again, of the third reference clock pulse (output c), and applies to an "AND" gate 29 provided for controlling feeding of the abovementioned second reference clock pulse (output b) to

85

95

the abovementioned counter 28 a signal which is the complement of the abovementioned output d, i.e., a signal (output e) which maintains a low level during a period from the generation of the third reference clock pulse (output c) upto the generation of the  $\alpha+Nth$ pulse of the second reference clock pulse (output b) and maintains a high level during a period from the generation of the α+Nth pulse of the second reference clock pulse upto the generation, again, of the third reference clock pulse (output c), as shown in Figure 3(M), and applies to the coincidence detecting circuit 27 a signal (output f) which maintains a low level during a period from the generation of the third reference clock pulse (output c) upto the generation of the  $\alpha+N-1$ st pulse of the second reference clock pulse (output b) and maintains a high level during a period from the generation of the  $\alpha+N-1$ st pulse of the second reference clock pulse upto the generation, again of the third reference clock pulse, as shown in Figure 3(N).

Accordingly, the shift register 23 is to be fed with only the first to  $\alpha$ +Nth pulses of the second reference clock pulse (output b) through the "AND" gate 26 after through the "AND" gate 26 after generation of the third reference clock pulse (output c) as shown in Figure 3(O), on account of which it is caused to stop its shifting operation at the time of completion of the storage of the quantized image element signals from all of the sensors 12, ...  $12_N$  in the sensor array 12, and then to hold these stored values. In contrast to this, the shift register 24, is shift-connected so far as the second reference clock pulse (output b) from the pulse generating circuit 16 is imparted thereto, so that the stored signals in the register 24 are shifted bit-by-bit once every clock pulse (output b) with respect to the stored signals in the shift register 23 by the pulses after the  $\alpha+N+st$ . As a result, sets of N quantized image element signals, each set being displaced for one bit, (14, ...  $14_{N} \rightarrow 14_{2} \dots 14_{N+1} \rightarrow 14_{3} \dots 14_{N+2} \rightarrow \dots$ ) are produced in parallel as the outputs upon successive shifting operations.

Further, since the "AND" gate 29 permits the abovementioned second reference clock pulse (output b) to pass therethrough only during the period when the output e from the control 25 is at the high level as shown in Figure 3P, the counter 28 receives at its clock input CK, those pulses after the  $\alpha+N+1$ st of the second reference clock pulse (output b), and counts the these pulses, i.e., it counts the number of shifts of the quantized image element signals in the shift register 24 after stoppage of the shifting operations in the abovementioned shift register 23, or, more particularly,

number of relative shifts between the quantized image element signal trains from the sensor 14 and the quantized image element signal trains from the sensor array 12. Incidentally, the contents of the counter 28 can be cleared by application of the abovementioned third reference clock pulse (output c) to its clear terminal CLR.

Incidentally, it will be understood from Figures 3(B) to 3(G) that the value of " $\alpha$ " corresponds to a delay between the first pulse of the second reference clock (output b) from the pulse generating circuit upon generation of the third reference clock pulse (output c) and the start of output of image element signals from the sensor arrays 12 and 14. This number " $\alpha$ " may be arbitrarily selected in conformity to this delay from the abovementioned first pulse until the output image element signals from the sensor arrays commences in accordance with the mode of driving by the driver as well as the characteristics of the sensor array to be employed.

A reference numeral 27 designates a coincidence detecting circuit which detects coincidence and non-coincidence of the N stored quantized signals in both shift registers 23 and 24. In this embodiment, the circuit 27 is so constructed that it may produce an output coincidence signal as shown in Figure 3(Q) when it has detected the optimumly coincided state, if not a perfect coincidence of the signals in the corresponding stages of the shift registers. This coincidence detecting circuit 27 is also controlled by the output f (Figure 3N) from the control circut 25 in such a manner that it may conduct the coincidence detection between the stored signals in the shift registers 23 and 24 only during the period when the output f is at the high level, the details of which will be explained later.

A numeral 30 refers to a register which reads thereinto a counted value of the abovementioned counter 28, in response to the coincidence output signal from the coincidence detecting circuit 27, at the time when the detection circuit 27 has detected the maximum coincidence between the stored signals in both shift registers 23 and 24. The abovementioned coincidence detecting circuit 27 is so connected that the coincided signal therefrom may be applied to a load terminal LD of the register 30.

A numeral 31 refers to a latching circuit which takes thereinto for latching the recorded values in the abovementioned register 30 in response to the third reference clock pulse (output c) from the pulse generating circuit 16, i.e., at every time the scanning of the object images by the sensor arrays 12 and 14 commences. This latching circuit is so connected that the third

75

70

80

85

90

95

100

105

110

115

120

reference clock pulse (output c) may be applied thereto through an inverter 32

A reference numeral 33 designates a D/A converter which is so constructed that it may receive as an input thereto a latched value in the abovementioned latching circuit 31, and may process this input value in accordance with the equation for determining the distance, i.e., D=f.d/x which has been explained in relation to Figure 1, to produce an output signal (e.g., a voltage value) denoting the distance D. A reference numeral 34 designates a meter as an indicating device to indicate the distance upto the object for the range detection, and is connected to an output terminal 33a of the D/A converter 33.

In the above-described construction, the set of the lens 11 and the sensor array 12 are collimated with respect to the object for the range detection, and an image to be a reference of the object is focussed by the lens 11 on a substantially fixed position on the sensor array 12. On the other hand, when the second and third reference clock pulses as shown in Figure 3B and 3C are generated from the pulse generating circuit 16 with the object image being formed on the sensor array 14 at a relatively displaced position thereon depending on the distance to the object, the driver 15 is actuated, whereby the image element signals are output time-sequentially from the sensors in the sensor arrays 12 and 14 (Figure 3F and G). These image element signals are then converted into continuous wave signals as shown in Figure 3H and I by means of the sample and hold circuits 17 and 18, after which these full wave signals are compared by the comparators 20 and 21 with the slice level established in the slice level setting circuit 22, and then applied to the shift registers 23 and 24, while being converted to quantized signals. At this time, the control circuit 25 applies

the high level signal (output d) to the "AND" gate 26 as shown in Figure 3L in response to the third reference clock pulse (output c) from the pulse generating circuit 16. Accordingly, the shift registers 23 and 24 sequentially store the quantized image element signal trains to be output from the abovementioned comparators 20 and 21 while being driven by the second reference 55 clock pulse (output b) from the pulse generating circuit 16, and shifting bit-by-bit, and produce these stored signals in the form of parallel outputs.

In this sequence operation, the control circuit 25 applies to the "AND" gate 29 the low level signal (output e) as shown in Figure 3(M), so that feeding of the second reference clock pulse (output b) from the pulse generating circuit 16 to the counter 28 is interrupted (vide Figure 3 (P)). When the

$\alpha$ +Nth pulse output of the second reference clock pulse (output b) from the pulse generating circuit 16 is produced, the control circuit 25 at this time instant applies to the "AND" gate 26 the low level signal (output d) as shown in Figure 3(L) to interrupt feeding of the second reference clock pulse (output b) from the pulse generating circuit 16 to the shift register 23 to thereby stop the shifting operation (accordingly, the shift register 23 holds the quantized image element signal trains from the whole sensors  $12_1 cdots 12_N$  in the sensor array 12 (vide Figure 3(O)) and to apply to the "AND" gate 29 the high level signal (output e) as shown in Figure 3(M) to cause feeding of the second reference clock pulse (output b) from the pulse generating circuit 16 to the counter 28 to start (vide Figure 3(P)). Accordingly, the shifting operation of the shift register 24 alone is continued with respect to the pulses commencing at the  $\alpha+N+1$ st of the second reference clock pulse (output b), and counting of the second reference clock pulse (output b) by the counter 28 commences at the  $\alpha+N+1$ st pulse of this second reference clock pulse. On the other hand, the coincidence

detecting circuit 27 starts the coincidence detection of the recorded values in both shift registers 23 and 24 at the moment when the quantized image element signals from all of the sensors 12, to 12, in the sensor array 12 are stored in the shift register 23 by the output f of the abovementioned control circuit 25, the signal level of which changes from low to high when the  $\alpha+N-1$ st output pulse of the second reference clock pulse (output b) from the pulse generating circuit 16 is produced as shown in Figure 3(N) and, at the same time, the quantized image element signals from the first N sensors, i.e. sensors 14, to 14, of the sensor array 14 have been recorded in the shift register 24, and, in the course of the shift register 24 alone being subjected to the bit-by-bit shifting operations by the pulses commencing with the  $\alpha+N+1$ st pulse of the second reference clock pulse (output b) and the train of N quantized image element signals stored therein being shifted sequentially such as to represent, successively, image elements 14, to 14, then 142 to 14, to 14, then 14<sub>3</sub> to 14<sub>N+2</sub> and so on, when the circuit 27 detects a state of coincidence or substantial coincidence between the quantized signals stored in the registers 23 and 24 it produces an output coincidence signal 30 as shown in Figure 3(Q) to the register 30. The register 30, the load terminal LD of which has been applied with the coincidence signals from the coincidence detecting circuit 27 then reads thereinto counted values of the abovementioned counter 28. Accordingly, 130

80

85

the recorded values of the register 30 at this moment become the distance information to the object. Thereafter, the recorded values of the register 30 are latched by the latching circuit 31 in response to the third reference clock pulse output (output c) from the pulse generating circuit 16 at the start of the subsequent scanning operation of the object images, after which they are converted into, for example, voltage values, by means of the D/A converter 33. The output of the D/A converter drives the meter 34 which thereby indicates the distance information by the deflection of its indicator needle 34a, of the meter 34 being connected to an output terminal 33a of the converter 33. It may, of course, be possible to indicate digitally this information by the use of a digital indicating element in place of the analog indicating means as illustrated. In this case, the values latched by the latching circuit 33 are converted into digital codes for indication, based on which the abovementioned digital indicating element may be driven.

20

In the following practical examples of the pulse generating circuit 16, the slice level setting circuit 22, the control circuit 25, and the coincidence detecting circuit 27 in the circuit construction shown in Figures 2A and 2B will be described in detail.

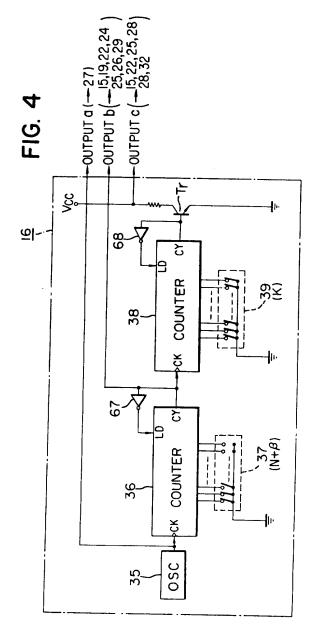

First, the pulse generating circuit 16, may, for example, be of a construction as shown in Figure 4. In the drawing, a numeral 35 refers to an oscillator which, in this embodiment, has been so pre-adjusted as to generate the first reference clock pulse shown in Figure 3A. A numeral 36 refers to a first counter coupled to receive therein clock pulses from the oscillator 35 through its clock input terminal CK and to count these pulses. The counter 36 is so constructed that it may produce an output signal from its carry output terminal CY every time the count value reaches a carry value set in a first switching circuit 37 provided for setting the carry value. A reference numeral 38 designates a second counter which receives thereinto a carry signal from the first counter 36 through its clock input terminal CK and counts such carry signals. The counter 38 is so constructed that it may produce a carry output signal from its carry output terminal CY every time the count value arrives at a carry value, set in a second switching circuit 39 for setting the carry value for the counter 38. Also, a reference symbol Tr designates a transistor, to the collector side of which a voltage Vcc is applied, the emitter of which is connected to the earth, and the base of which is connected to the carry output terminal of the second counter 38

According to such construction, the first reference clock pulses as shown in Figure

3A are produced as the output a from the oscillator 35; every time the count value in the first counter 36, produced by counting the first reference clock pulses (output a), reaches the value set by the first switch circuit 37, a pulse is generated in a signal line connected to the carry output terminal CY of the counter 36. Also, every time the count value in the second counter 38, produced by counting the carry signals from the first counter 36, reaches the value set by the second switch circuit 39, a pulse is generated in the signal line connected to the collector side of the transistor Tr due to its conduction or response to the carry output signal from the second counter. Here, if a constant  $N+\beta$  is set by the combination of selective closure of the switches in the first switch circuit 37, and a constant K is set by the selective closure of the switches in the second switch circuit 39 in consideration of the abovementioned number  $\alpha$  and the number M of the sensors in the sensor array 14, the second reference clock pulse (output b) as shown in Figure 3B can be obtained from the signal line connected to the carry output terminal CY of the first counter 36 at every time the first counter 36 counts  $N+\beta$  first reference clock pulses (output a) from the oscillator 35, and also the third reference clock pulse (output c) shown in Figure 3C can be obtained from the signal line connected to the collector side of the abovementioned transistor Tr the third reference as the output c at every time the second counter 38 counts K carry signals from the first counter 36. Incidentally, each of the carry signals of the counters 36 and 38 is fed back to the respective load terminal LD thereof through the respective inverters 67 and 68. This feed back operation is for causing these counters 36 and 38 to introduce thereinto the values set in the switch circuits 37 and 39 respectively as the respective carry values when the counters 36 and 38 have completed counting upto the values already set in the switch circuits 37 and 39.

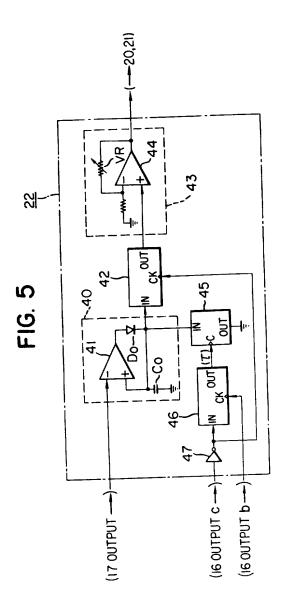

Next, the slice level setting circuit 22, may, for example, be of a construction as shown in Figure 5. In the drawing, a reference numeral 40 designates a peak hold circuit which holds sequentially the output peak values from the abovementioned sample and hold circuit 17. This peak hold circuit 40 consists of a differential amplifier 41, a capacitor Co to hold the peak values, and a diode Do for prevention of back flow. A numeral 42 refers to a sample and hold circuit which is so connected as to sample and hold the peak values held in the capacitor Co in the abovementioned peak hold circuit 40 in response to the third reference clock pulse from the abovementioned pulse generating 70

75

80

85

- -

95

100

105

110

115

120

125

85

95

100

circuit 16 by its application to the clock input terminal CK through an inverter 47. A reference numeral 43 designates an operational circuit for determining a slice level on the basis of an output from the sample and hold circuit 42. This operational circuit consists of an operational amplifier 44 and a variable resistor VR for setting a constant to determine the slice level, wherein an output from the operational amplifier 44 is imparted to the abovementioned comparators 20 and 21 as the slice level. A numeral 45 refers to an analog switch for clearing the peak values held in the peak hold circuit 40. This analog switch is so constructed that it is connected to the capacitor Co in the peak hold circuit 40 and becomes conductive by application of the third reference clock pulse (output c) from the abovementioned pulse generating circuit 16 to its control terminal c through the inverter 47 and a shift register 46 to clear the values held in the capacitor Co. The shift register 46 is provided for delaying a timing to render the analog switch 45 to be conductive after a predetermined time τ from the generation of the third reference clock pulse (output c) in the pulse generating circuit 16. In this embodiment, this shift register 46 is so constructed that, after the third clock pulse (output c) is introduced as an input thereinto at its input terminal in through the inverter 47, this third clock pulse may be applied to the control terminal c of the analog switch 45 at the time when a number, corresponding to the bit construction number, of second reference clock puises (output b) as shown in Figure 3B have been applied to its clock input terminal CK, whereby the value held in the capacitor Co becomes cleared or response to the third reference clock pulse (output c) but with the abovementioned time delay  $\tau$  after the completion by the abovementioned sample and hold circuit 42 of the sampling and holding of the values held in the capacitor Co. The bit construction number of the shift register 46 in this case may be kept below the number  $\alpha$ as already explained in connection with Figure 2

According to such construction, the peak values of the output from the sample and hold circuit 17 (i.e., the peak values of the output from the sensor array 12) are first held in the capacitor Co in the peak hold circuit 40 at the time of scanning of the object image by the sensor array 12, and after termination of the scanning operations, when the third reference clock pulse output (output c) as shown in Figure 3C is generated from the pulse generating circuit 16 at the start of the subsequent scanning operation, the sample and hold circuit 42, in response to this subsequent

scanning, takes thereinto the peak values held in the abovementioned capacitor Co, and applies the values to the operational circuit 43. In the operational circuit 43 which has received the output from the sample and hold circuit 42, the operational amplifier 44 determines the slice level on the basis of the output from the sample and hold circuit 42, i.e., the peak value of the output from the sample and hold circuit 17 during the previous scanning of the object image and a slice level determining constant set in the variable resistor VR, and then forwards the thus determined slice level, as the output, to the comparators 20 and 21 for use in the quantizing operation, whereby both comparators 20 and 21 convert the outputs from the sample and hold circuits 17 and 18 into quantized signals on the basis of the slice level determined by the operational circuit 43.

As stated in the foregoing, the capacitor Co in the abovementioned peak hold circuit 40 is cleared of the hold values in the previous scanning by the analog switch 45 to become conductive in response to the output from the shift register 46 after lapse of the abovementioned delay time  $\tau$  since the sample and hold circuit 42 has sampled and held the values held in the capacitor Co. Thereafter, the capacitor Co starts holding the peak values of the output from the sample and hold circuit 17 during the subsequent scanning of the object image by the sensor array 12.

Thus, in the construction of the slice level setting circuit 22 shown in Figure 5, the slice level at the time of a current scanning operation of the object image is automatically established upon the basis of the peak value of the output from the sensor array obtained during the previous scanning operation of the object image.

For the slice level determining constant to be set in the variable resistor VR in the abovementioned operational circuit 43, experiments have revealed that a constant of from 0.6 to 0.8 or so, i.e., a value which renders the output level from the operational amplifier 44 to be 60% to 80% of the peak level of the output from the sensor array 12 is preferable.

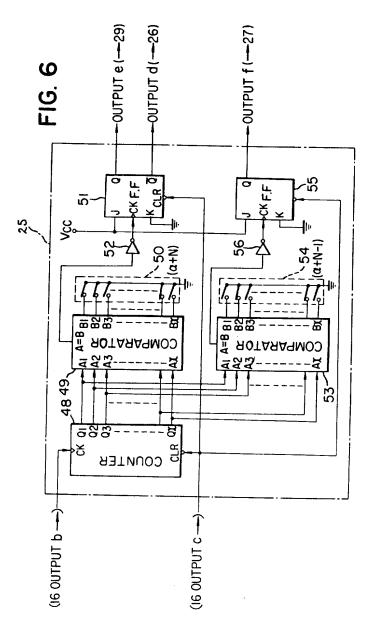

Thirdly, the control circuit 25 may, for example, be of a construction as shown in Figure 6. In the drawing, a reference numeral 48 designates a counter which introduces the second reference clock pulse (output b) as shown in Figure 3B from the pulse generating circuit 16 as the input thereto through its clock input terminal CK to be counted thereby, and which is cleared of its contents by the third reference clock pulse (output c as shown in Figure 3C). A numeral 49 refers to a first comparator which compares the counted value of the

counter 48 with a value set by a first constant setting switch circuit 50, and produces a coincided signal output when the counted value of the counter 48 becomes coincided with the value set by the first switch circuit 50. A numeral 51 refers to a first J-K type flip-flop which introduces into its clock input terminal CK the coincided signal from the first comparator 49 through an inverter 52. A reference numeral 53 designates a second comparator which compares the count value of the counter 48 with a value established by a second constant setting switch circuit 54, and produces a coincided signal output when the count value of the counter 48 becomes coincided with the value set by the second switch circuit 54. A reference numeral 55 denotes a second J-K type flip-flop which introduces the coincided signal from the second comparator 53 as an input into its clock input terminal CK through an inveter 56. Each of the abovementioned first and second flip-flops 51 and 55 is of such a construction that a voltage Vcc is applied to its input terminal J, its input terminal K is connected to the earth, and its clear terminal CLR receives the third reference clock pulse (output c) from the pulse generating circuit 16 as is the case with the abovementioned counter 48. In this construction, outputs Q and  $\overline{Q}$  of

the first flip-flop 51 are first considered. In the state wherein the first flip-flop 51 is cleared by the third reference clock pulse (output c) from the pulse generating circuit 16, the output  $\overline{Q}$  is at a "high" level, while the output Q is at a "low" level. When the counter 48 starts its counting operation from the first pulse of the second reference clock pulse (output b) after it is cleared by the third reference clock pulse (output c), and its count value has reached the value set by the first switch circuit 50, a coincided signal output is produced from the first comparator 49, whereby the first flip-flop 51 which receives this coincided signal through the inverter 52 is inverted, with the result that the output  $\overline{Q}$  changes from the "high" level to the "low" level, and the output Q changes from the "low" level to the "high" level. Subsequently, when cleared again by the abovementioned third reference clock pulse (output c), the output  $\overline{Q}$  reinstates its level from "low" to "high", and the output q from "high" to "low". Consequently, when a constant  $\alpha+N$  is set by the selective closure of the switches in the first switch circuit 50, the first flip-flop 51 will become inverted at the time that the count value of the counter 48 reaches  $\alpha+N$ . On account of this the outputs Q and Q take the "high" level and the "low" level, respectively, during the period from the generation of the

third reference clock pulse (output c) from the pulse generating circuit 16 to the generation of the  $\alpha$ +Nth pulse of the second reference clock pulse (output b). Thereafter, the outputs  $\overline{Q}$  and  $\overline{Q}$ , respectively take the "low" level and the "high" level until the third reference clock pulse (output c) is again generated in the subsequent stage. As the result, the output Q of the first flip-flop 51 can be utilized as the output d shown in Figure 3L for controlling the "AND" gate 26, and the output Q can be utilized as the output e shown in Figure 3M for controlling the 'AND" gate 29.

Considering now the output Q from the second flip-flop 55, it shows the same change as the output Q of the first flip-flop 51, as is apparent from the foregoing explanations. Accordingly, when the constant  $\alpha+N-1$  is set by the selective closure of the switches in the second switch circuit 54, the second flip-flop 55 is inverted when the count value of the counter 48 reaches  $\alpha+N-1$ . On account of this, the output Q thereof is at the "low" level during the period from the generation of the third reference clock pulse (output c) from the pulse generating circuit 16 to the generation of the  $\alpha+N-1$ st pulse of the second reference clock pulse (output b), thereafter, "high" level until the third it takes reference clock pulse (output c) is again generated subsequently. As the result, the output Q of this flip-flop 55 can be utilized as the output f shown in Figure 3N for controlling the coincidence detecting circuit 27.

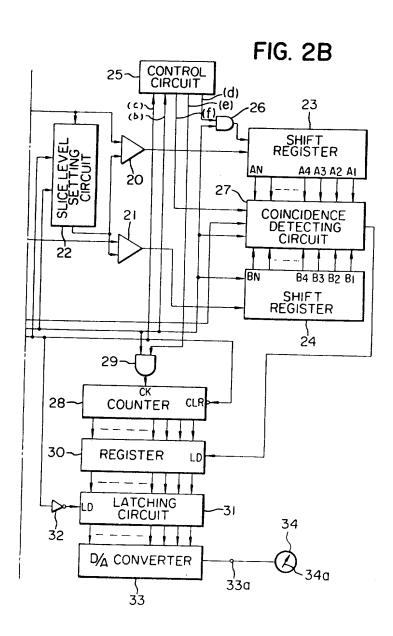

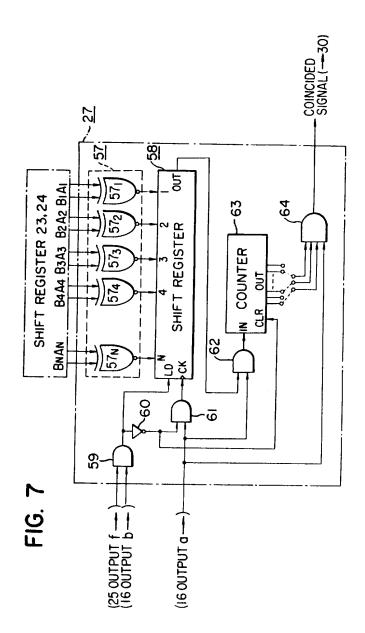

Lastly, the coincidence detecting circuit 27, may, for example, be of a construction 105 as shown in Figure 7 or in Figure 9.

Here, a particular point should be mentioned. In the coincidence detection between the recorded values in the shift registers 23 and 24, it is ideal that 110 coincidence is signified between recorded values in the shift registers 23 and 24 when all of the outputs from the corresponding bits in these shift registers 23 and 24 are perfectly coincident. However, it occurs from time to time that when the outputs from each of the sensors 12, to 12, and 14, to 14<sub>M</sub> in the respective sensor arrays 12 and 14 are converted into quantized signals by comparing them with the slice level set in 120 the slice level setting circuit 22 through the comparators 20 and 21, those output signals which are very close to the slice level are determined in some cases as being at the "high" level, and in other cases as being at the "low" level. Accordingly, since probability of the perfect coindence between the recorded values in the shift registers 23 and 24 becomes extremely low in practice, it is more practical to adopt 130

70

75

80

25

55

such a method that satisfactory coincidence is considered to have been attained, if the recorded values in the corresponding bits coincide at a predertermined ratio.

Explaining first the embodiment shown in Figure 7, the construction of the coincidence detecting circuit 27 is such that coincidence between the recorded values in the shift registers 23 and 24 is signified at the time instant when quantized image element signals recorded in the mutually corresponding bits  $A_1 - B_1$ ,  $A_2 - B_2$ , ...,  $A_N - B_N$  in the shift registers 23 and 24 are coincided at and above a predetermined

In the drawing, a reference numeral 57 designates a group of gates consisting of exclusive "NOR" gates 57, to 57, (i.e., in number corresponding to the bit numbers in the shift registers 23 and 24, or N numbers). In this construction, the outputs from the mutually corresponding bits A<sub>1</sub>—B<sub>1</sub>, ...,  $A_{N}$ — $B_{N}$  in the shift registers 23 and 24 are introduced as the inputs into their respectively corresponding exclusive "NOR" gates 57, to 57, and the gates produce "high" level output signals when the recorded values in mutually corresponding bits  $A_1 - B_1, \ldots, A_N - B_N$  are equal, and "low" level output signals when they are different.

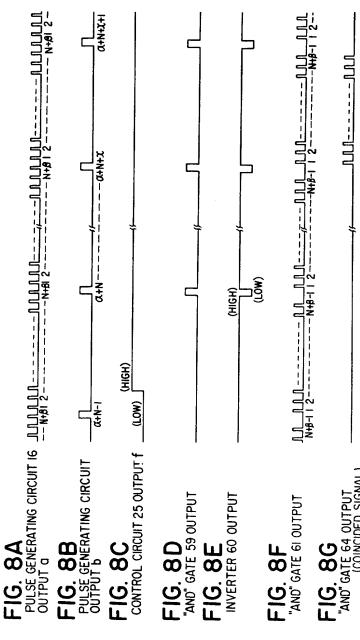

A numeral 58 refers to a shift register of N-bit construction which receives and stores the outputs from each of the exclusive "NOR" gates 57, to 57, in the group of gates 57 in the respective bits 1 to N corresponding thereto at every time the second reference clock pulse (output b shown in Figure 3B) and Figure 8B from the pulse generating circuit 16 is applied to its load terminal LD through an "AND" gate 59. The "AND" gate 59 has been supplied with the output f from the control circuit 25 (as shown in Figure 3N and Figure 8C), and the shift register 58 is, accordingly, supplied with pulses after the  $\alpha$ +Nth pulse of the abovementioned second reference clock pulse (output b) as shown in Figure 8E, whereby the outputs from the gates 57 are introduced from the time instantly when the N quantized image element signals from the first N sensors 14, to 14, in the sensor array 14 are recorded in the shift register 24, and thereafter the outputs from the gates 57 are repeatedly introduced at every shifting of the shift register 24.

A reference numeral 61 designates an "AND" gate which imparts the first reference clock pulse (output a as shown in Figure 3A and Figure 8A) from the pulse generating circuit 16 to the clock input terminal CK of the shift register 58. Further, outputs (Figure 8D) from the "AND" gate 59 are imparted to this "AND" gate 61 with the phase being inverted by an inverter 60 as coincided at a predetermined ratio and

shown in Figure 8E. Accordingly, as shown in Figure 8F, the first reference clock pulse (output a) is applied to the shift register 58 only when the output from the "AND" gate 59 is at the low level, i.e., with a timing which does not carry out shifting in the shift register 24, whereby the recorded values of each bit in the shift register are produced sequentially and in series as the outputs.

A reference numeral 62 denotes an "AND" gate which takes an "AND" between the output of the shift register 58 and the first reference clock pulse (output a) to produce only "high" level signal outputs among those outputs from the shift register 58. A reference numeral 63 designates a counter which counts the number of the "high" level signal outputs from the "AND" gate 62. This counter is so controlled that it is cleared by the signals (Figure 8E) from the inverter 60 at every time the second reference clock pulse (output b) trails, (i.e., the output of the inverter 60 rises) and that it counts the output numbers from the "AND" gate 62 only when the second reference clock pulse (output b) is at the low level, (i.e., when the output from the inverter 60 is at the "high' level). Accordingly, the counted values of the counter 63 denote the coincided numbers of the recorded values in the mutually corresponding bits  $A_1 - B_1$ ,  $A_N - B_N$  of the shift registers 23 and 24.

According to the abovementioned construction, the instant at which the count value of the counter 63 becomes N corresponds to the time when the recorded values in both shift register 23 and 24 are in the perfect coincidence. However, the determination of the coincidence of the recorded values in both shift registers 23 and 24 as the time when the count values of the counter 63, have become N is not practical realistic in view of the considerations described in the foregoing. In this embodiment, therefore, there is adopted such a circuit construction that imparts outputs of arbitrary bits in the counter 63 (the more significant bits may preferably be included) to the "AND" gate 64 together with the first reference clock pulse (output a), and produces high level signal output (Figure 8G) from the "AND" gate 64 when the preselected bit outputs in the counter 63 are all at the high level.

According to such construction, when the counted values of the counter 63 have become greater than a value previously established by the selection of the aforesaid arbitrary bits, in other words, when the recorded values in the mutually corresponding bits  $A_1 - B_1 \dots A_N - B_N$  in the shift registers 23 and 24 have become

80

90

95

65

above, "high" level signal outputs are produced from the "AND" gate 64, and these "high" level signals can be utilized as the coincided signals as already mentioned

in the foregoing.

In the construction of the coincidence detecting circuit 27 shown in Figure 7, the coincided signals (Figure 3Q) are obtained in the form of  $N+\beta-1$  pulses corresponding to the first pulse to the  $N+\beta$ -1st pulse in the first reference clock pulse (output a), as shown in Figure 8G. However, as will be understandable from Figure 8A to 8G and the foregoing explanations, since these  $N+\beta-1$  coincided pulses are all generated within a pulse-to-pulse time duration of the second reference clock pulse (output b), they may safely be applied as the load signals to the register 30 in the form in which they are generated. Also, when the construction as shown in Figure 7 is used as the coincidence detecting circuit 27, the latching circuit as shown in Figure 2 may be dispensed with.

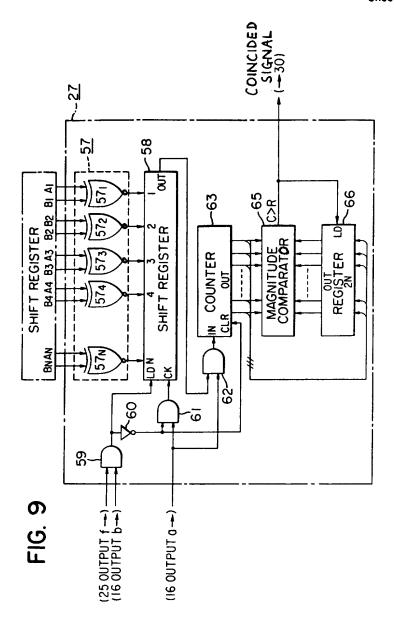

The embodiment shown in Figure 9 is a modification of that shown in Figure 7, which is so constructed that coincidence between the recorded values in the shift registers 23 and 24 is detected by detecting the time instant when the count value of the counter 63 is at a maximum, in other words, when the numbers of coincidence between the recorded values in the mutually corresponding bits  $A_1 - B_1, \ldots, A_N - B_N$  of the shift registers 23 and 24 have become maximum. In the drawing, the same elements and signals as those in Figure 7 are designated with the same reference

symbols. In the drawing, a reference numeral 65 designates a magnitude comparator which is capable of determining the relative magnitude of the recorded values in a register 66 and the counted values in the counter 63. The comparator is so constructed that it may produce "high" level signal outputs when the counted values C of the counter 63 is greater than the recorded values R of the register 66 (C>R), and that, while the "high" level signals from the comparator 65 are applied to the load terminal LD of the register 66 as the load signals, they may also be applied to the load terminal LD of the register 30 in

Figure 2. Accordingly, these registers 66 and 30 are able to introduce thereinto the counted values of the counters 63 and 28 at that instant in response to the high level signal outputs from the comparator 65 when such are produced. According to such construction, so

far as the high level signal outputs are continuously produced from the comparator 65, the registers 66 and 30 introduce thereinto the counted values of the

counters 63 and 28 at every time and in response to such output signals produced. On account of this, at the termination of one scanning operation of the object image, the values recorded in these registers 66 and 30 will be the maximum counted values of the counter 63 and the counted values of the counter 28 at the instant when the counted values of the counter 63 have become maximum, respectively. Consequently, as explained above in connection with Figure 2, if the recorded values of the register 30 are latched by the latching circuit 31 at the start of the subsequent scanning, the output from the latching circuit 31 at this time represents the shift numbers of the shift register 24 which have been spent until the recorded values in the shift registers 23 and 24 become optimumly coincided, i.e., the so-called object distance.

As is apparent from the foregoing explanations, no coincided signals as shown in Figure 3Q can be obtained with the construction of the coincidence detecting circuit 27 shown in Figure 9, but the counted values of the counter 28 at the instant when the recorded values in the shift registers 23 and 24 have become optimumly matched may be accurately recorded in the register 30.

In the following, another embodiment of the range detecting method and apparatus according to the present invention will be explained in reference to Figures 10 and 1-1. This embodiment differs from the embodiment shown in Figure 2 in that a single photo-sensor array is utilized in place of a pair of photo-sensor arrays 12 and 14. Accordingly, the relevant figures of drawing show only the construction of those main parts which particularly differs from that of the afore-described embodiment, and in which the similar component elements to those in the previous embodiment are designated by the same reference symbols, and the explanations will be directed to those parts alone which differ from the previous embodiment.

In Figure 10, reference numerals 11 and 13 designate a pair of focussing lenses fixedly disposed at a definite spacing defining a base line length d, as in the previous embodiment.

In this embodiment, the optical layout of the component elements is such that a single photo-sensor array 69 consisting of L photo-sensors 69, to 69, (where: L is a number sufficiently larger than 2N such as, for example, L=N+M in view of the embodiment in Figure 2) may be disposed in confrontation to these lenses 11 and 13 so as, on the one hand, to constantly focus an image I<sub>1</sub> of an object for the range detection formed by the lens 11 at a substantially definite position on a first sensor region 69a 130

75

85

containing the initial N numbers of sensors 69, to 69, of the sensor array 69 by way of an obliquely fixed mirror 70 and a reflecting surface 72a of a reflecting prism 72 (hence the combination of the lens 11 and the first sensor region 69a may be applied for collimation to the object for the range detection, same as described in the foregoing), and, on the other hand, to focus an image I<sub>2</sub> of the object formed by the lens 13 at a position corresponding to a distance to the object on a second sensor region 69b containing (L-N) sensors, namely sensors  $69_{N+1}$  to  $69_L$ , by way of an obliquely fixed mirror 71 and another reflecting surface 72b of the reflecting prism 72.

According to such construction, if it is assumed that the object is at infinity, the image thereof to be formed by the lens 13 is focussed at a position designated by a reference symbol  $I'_2$  (within a range of the sensors  $69_{N+1}$  to  $69_{2N}$ ) in the drawing along a route shown by a dash line. Contrary to this, when the object is at a finite distance, the object image is focussed at a position designated by a reference symbol I, along a route shown by a solid line in the drawing.

Accordingly, when the value of a relative displacement variable x of the focussing position of the image I<sub>2</sub> to the focussing position I'2 of the image of the object at infinity is determined the distance to the object can be ascertained. In order to measure this displacement variable x the embodiment of the present invention shown in Figure 10 operates in such a manner that quantized image element signal trains from the N numbers of the sensors  $69_1$  to  $69_N$  in the first sensor region 69a are first introduced as the input into first storage means at the time when the image element signals are time sequentially taken out of each of the sensors 69, to 69, in the sensor array 69, then quantized image element signal trains from the sensors of the same numbers in the second sensor region 69b as the output are introduced into the second storage means as the input thereto to cause the quantized image element signal trains in this second storage means to sequentially shift relative to the signals in the first storage means. In this way, the degree of shifting during a period from the start of the relative shifting operation up to a time when the stored values in both storage means can be considered as being substantially coincided with each other is determined, by counting individual shifts, and the shift count value is converted into the above-mentioned displacement quantity x i.e., the distance information of the object

The physical circuit construction of the embodiment shown in Figure 10 will now be

for the range detection.

explained in more detail in reference to Figure 11.

In the drawing, a reference numeral 22' designates a slice level setting circuit corresponding to the slice level setting circuit 22 in Figure 2. In this circuit construction, the slice level setting circuit 22' is so designed that it may set the slice level based on the peak value of the outputs from the first sensor region 69a of the sensor array 69 in correspondence to the slice level setting circuit 22 in Figure 2, the details of which will be described later. Similarly, a numeral 25' refers to a control circuit which corresponds to the control circuit 25 in Figure 2. This control circuit 25' is so constructed that, in conformity with changes in the sensor array, it may first impart to the "AND" gate 29 a signal, as an output e', which maintains a low level during a period from the generation of the third reference clock pulse output (output c shown in Figure 3C) from the pulse generating circuit 16 upto termination of the  $\alpha+2N$ th pulse output of the second reference clock pulse (output b shown in Figure 3B), and, thereafter, maintains a high level upto a time when the third reference clock pulse output (output c) is again produced, that is, a signal which causes the counter 28 to count pulses after the  $\alpha+2N+1$ st pulse of the second reference clock pulse (output b); and, on the other hand, impart to the coincidence detecting circuit 27 a signal, as an output f', which maintains a low level during a period from the generation of the third reference clock pulse putput (output c) upto the termination of the  $\alpha+2N-1$ st pulse output of the second reference clock pulse (output b), and, thereafter, maintains a high level upto a time when the third reference clock pulse output (output c) is again produced, that is, a signal to start the coincidence detection at the time instant when the quantized image element signals from the initial N sensors (i.e. the sensors  $69_{n+1}$  to  $69_{2N}$ ) in the second sensor region 69b of the sensor array 69 are recorded in the shift register 24 (the details of this operation will be described later).

Incidentally, an "AND" gate 73 same as 115 the "AND" gate 26 provided in the shift register 23 is also provided in the shift register 24 so that the control signal (output d shown in Figure 3L) to be imparted to the "AND" gate 26 from the control circuit 25' may also be imparted to the "AND" gate 73 through an inverter 74. According to this construction, of the second reference clock pulse outputs (output b) from the pulse generating circuit 16, the first to the  $\alpha$ +Nth 125 pulses alone are fed to the shift register 23, while the  $\alpha+N+1$ st to the Kth pulses alone are fed to the shift register 24. Accordingly even if the data lines to the quantizing

70

80

90

95

110

comparator 20 in both shift registers 23 and 24 are common, the quantized image element signal trains from the N numbers of the sensors 69<sub>1</sub> to 69<sub>N</sub> in the first sensor region 69a are introduced as input into the shift register 23 alone, while the quantized image element signal trains from the N sensors in the second sensor region 69b are introduced as input into the shift register 24 alone. Moreover, in the shift register 24, there is carried out the sequential shifting of the quantized image element signal trains by the clock pulses after the  $\alpha+2N+1$ st. Accordingly, the circuit construction shown in Figure 11 performs the same distance detecting operations as in the circuit construction shown in Figure 2.

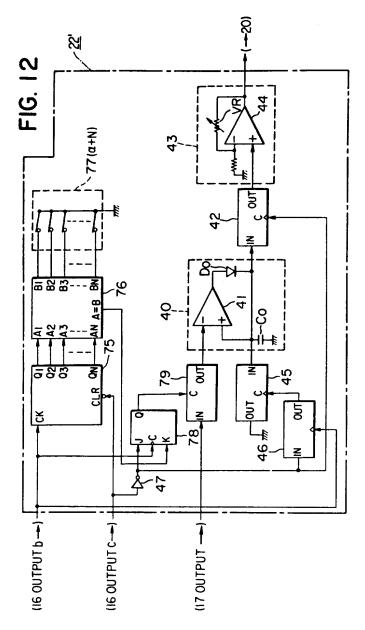

The slice level setting circuit 22' has a circuit construction as shown, for example, in Figure 12. The illustrated construction, besides the construction shown in Figure 5, is further added with a construction which restricts feeding of the sensor output to the peak hold circuit 40 to an output from the first sensor region 69a in

the sensor array 69 alone.

20

In the drawing, a reference numeral 75 designates a counter which counts the second reference clock pulse (output b) from the pulse generating circuit 16; 76 refers to a comparator which compares the counted values in the counter 75 with a constant set in a constant setting switch circuit 77, and produces an output coincidence signal when the counted values have become coincided with the constant set in the switch circuit 77; 78 refers to a J—K type flip-flop which is so connected in the circuit construction that it may be set by receiving in its input terminal J the third reference clock pulse (output c) from the pulse generating circuit 16 through the inverter 47, and in that set state produce from its output terminal Q the input J as an output in synchronism with the second reference clock pulse (output b) received at its clock terminal C, and that it may be reset by receiving a coincided signal from the comparator 76 in its input terminal K; and 79 designates an analog switch which is so circuit-connected that it may receive the output Q from the flip-flop 78 in its control terminal, and, when the output Q assumes the "high" level, become conductive in response thereto to enable the output from the sample and hold circuit 17 to be imparted to the peak hold circuit 40.

According to such circuit construction, the flip-flop 78 is in a set condition during a period from the generation of the third reference clock pulse (output c) upto coincidence of the counted values in the counter 75 with the constant already set in the switch circuit 77; during this set condition, the flip-flop produces as an

output its input J (which is a high level signal) from its output terminal Q with a timing corresponding to the second reference clock pulse (output b), whereby the analog switch 79 is rendered on-and-off with this output Q with a timing corresponding to the second reference clock pulse. Accordingly, while the flip-flop 78 is in the set condition, an output from the sample and hold circuit 17 is applied to the peak hold circuit 40 with a timing corresponding to the sampling operation at this sample and hold circuit 17, whereby the slice level is determined by the operational circuit 43 on the basis of the hold value in the peak hold circuit 40, i.e., the peak value of the output from the sample and hold circuit 17, through the process as already discussed in connection with Figure 5.

Accordingly, whenever the constant  $\alpha+N$ is set by the switch circuit 77, the flip-flop 78 is kept at its set condition during a period of from generation of the third reference clock pulse (output c) up to the termination of the output of all of image element signals the first sensor region 69a in the sensor array 69. Accordingly, only the outputs from the first sensor region 69a of the sensor 69 are supplied to the peak hold circuit 40. As the result, the slice level is set on the basis of the peak values in the outputs from the first sensor region 69a of the sensor array 69.