(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6356352号

(P6356352)

(45) 発行日 平成30年7月11日(2018.7.11)

(24) 登録日 平成30年6月22日(2018.6.22)

(51) Int.Cl.

G 0 1 T 1/20 (2006.01)

F 1

G O 1 T 1/20

G O 1 T 1/20B

D

請求項の数 16 (全 15 頁)

(21) 出願番号 特願2017-525905 (P2017-525905)

(86) (22) 出願日 平成27年10月30日 (2015.10.30)

(65) 公表番号 特表2018-500549 (P2018-500549A)

(43) 公表日 平成30年1月11日 (2018.1.11)

(86) 國際出願番号 PCT/EP2015/075193

(87) 國際公開番号 WO2016/074945

(87) 國際公開日 平成28年5月19日 (2016.5.19)

審査請求日 平成30年2月20日 (2018.2.20)

(31) 優先権主張番号 14193004.0

(32) 優先日 平成26年11月13日 (2014.11.13)

(33) 優先権主張国 歐州特許庁 (EP)

早期審査対象出願

(73) 特許権者 590000248

コーニンクレッカ フィリップス エヌ

ヴェ

KONINKLIJKE PHILIPS

N. V.

オランダ国 5656 アーネー アイン

ドーフェン ハイテック キャンパス 5

H i g h T e c h C a m p u s 5,

N L - 5 6 5 6 A E E i n d h o v e

n

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

最終頁に続く

(54) 【発明の名称】最適化された効率を有するピクセル化されたシンチレータ

## (57) 【特許請求の範囲】

## 【請求項 1】

ピクセル化されたシンチレータを製造するための方法であつて、

第1の焼結収縮係数を有するピクセル化シンチレータ構造を設けるステップであり、該

ピクセル化シンチレータ構造は、間隙によつて離隔された頂部及び底部を双方が持つ2つ

の隣接したピクセルを有する、ステップと、

前記2つの隣接したピクセルの前記底部で前記2つの隣接したピクセルの双方と機械的

に接觸する接続構造を設けるステップであり、該接続構造は、前記第1の焼結収縮係数よ

りも大きい第2の焼結収縮係数を有する、ステップと、

前記ピクセル化シンチレータ構造及び前記接続構造を焼結するステップと、

を有する方法。

10

## 【請求項 2】

前記接続構造はベース層であり、且つ

前記ピクセル化シンチレータ構造は前記ベース層上に堆積される、

請求項1に記載の方法。

## 【請求項 3】

前記ベース層は、0.2mmと2mmとの間の厚さを持ち、且つ

前記ピクセル化シンチレータ構造は、0.2mmと5mmとの間の厚さを持つ、

請求項2に記載の方法。

## 【請求項 4】

20

当該方法は更に、

第3の焼結収縮係数を有する中間層構造を設けるステップであり、前記第3の焼結収縮係数は、前記第2の焼結収縮係数よりも小さく、且つ前記第1の焼結収縮係数よりも大きく、前記中間層構造は、前記ベース層及び前記ピクセル化シンチレータ構造と機械的に接触する、ステップ

を有し、

前記中間層構造は、前記ベース層及び前記ピクセル化シンチレータ構造と共に焼結される、

請求項2又は3に記載の方法。

【請求項5】

10

前記接続構造を除去するステップ、

を更に有する請求項1乃至4の何れか一項に記載の方法。

【請求項6】

前記接続構造は、前記2つの隣接したピクセルを離隔させる前記間隙の中に設けられる、請求項1乃至5の何れか一項に記載の方法。

【請求項7】

前記ピクセル化シンチレータ構造を設けるステップは、積層レイヤ造形によって行われる、請求項1乃至6の何れか一項に記載の方法。

【請求項8】

前記2つの隣接したピクセルは各々、0.05mmと2mmとの間の幅を持ち、前記設けられたピクセル化シンチレータ構造の前記間隙は、前記焼結するステップ後に150μm未満の幅を持つ、請求項1乃至7の何れか一項に記載の方法。

20

【請求項9】

前記第1の焼結収縮係数と前記第2の焼結収縮係数との間の比は、0.95と0.2との間である、請求項1乃至8の何れか一項に記載の方法。

【請求項10】

30

前記ピクセル化シンチレータ構造は、第1の相対量で結合材を有するシンチレーション用セラミック材料を有し、

前記接続構造は、第2の相対量で結合材を有するシンチレーション用セラミック材料を有し、且つ

前記第1の相対量と前記第2の相対量とが異なる、

請求項1乃至9の何れか一項に記載の方法。

【請求項11】

前記ピクセル化シンチレータ構造を反射コーティング材料でコーティングするステップ、

を更に有する請求項1乃至10の何れか一項に記載の方法。

【請求項12】

第1の焼結収縮係数を有し、且つ、間隙によって離隔され且つ頂部及び底部を持つ2つの隣接したピクセルを有する、ピクセル化シンチレータ構造と、

前記2つの隣接したピクセルの前記底部で前記2つの隣接したピクセルの双方と機械的に接触する接続構造であり、当該接続構造は、前記第1の焼結収縮係数よりも大きい第2の焼結収縮係数を有する、接続構造と、

を有するピクセル化されたシンチレータ。

40

【請求項13】

前記ピクセル化シンチレータ構造の前記2つの隣接したピクセルは各々、0.05mmと2mmとの間の幅を持ち、且つ

前記ピクセル化シンチレータ構造は、0.2mmと5mmとの間の厚さを持つ、

請求項12に記載のピクセル化されたシンチレータ。

【請求項14】

請求項1乃至11の何れか一項に記載の方法によって製造されたピクセル化されたシン

50

チレータ、を有する検出器。

【請求項 15】

請求項 14 に記載の検出器を有する撮像装置。

【請求項 16】

前記間隙は  $150 \mu m$  未満の幅を持つ、請求項 12 又は 13 に記載のピクセル化されたシンチレータ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シンチレータの分野に関する。特に、本発明は、ピクセル化されたシンチレータを製造する方法、及びピクセル化されたシンチレータに関する。 10

【背景技術】

【0002】

放射線検出器におけるシンチレータは、間隙によって隔てられた個々のピクセルのアレイを有することがある。そのようなピクセル化されたシンチレータは、シンチレーション用のセラミック材料から形成されることができる。

【0003】

特許文献 1 ( U S 2 0 1 2 / 0 3 0 8 8 3 7 A 1 ) に、 3 D インクジェットプリンティングによるセラミック成形本体の生産力のある調製のためのプロセスが記載されている。

【先行技術文献】

20

【特許文献】

【0004】

【特許文献 1】米国特許出願公開第 2 0 1 2 / 0 3 0 8 8 3 7 号明細書

【発明の概要】

【0005】

ピクセル化されたシンチレータの効率を最適化することが望ましくあり得る。本発明の態様が、独立項にて記述される。利点及び更なる実施形態が、従属項、明細書、及び図面にて説明される。

【0006】

本発明の第 1 の態様は、ピクセル化されたシンチレータを製造するための方法に関する。当該方法は、第 1 の焼結収縮係数を有するピクセル化シンチレータ構造を設けるステップを有し、ピクセル化シンチレータ構造は、間隙によって離隔された頂部及び底部を双方が持つ 2 つの隣接ピクセルを有する。さらに、当該方法は、2 つの隣接ピクセルの底部で 2 つの隣接ピクセルの双方と機械的に接触する接続構造を設けるステップを有し、接続構造は、第 1 の焼結収縮係数よりも大きい第 2 の焼結収縮係数を有する。また、当該方法は、ピクセル化シンチレータ構造及び接続構造を焼結するステップを有し、第 1 の焼結収縮係数と第 2 の焼結収縮係数との間の差異のために上記間隙が縮小される。 30

【0007】

本発明の要旨は、より高い又は最適化された効率を有するピクセル化シンチレータを製造するための方法を提供することに見られ得る。これは、相異なる焼結収縮係数が、2 つの隣接ピクセルを隔てる間隙が焼結プロセス中に縮小されることを生じさせるようにして、相異なる焼結収縮係数を有するシンチレータ構造及び接続構造という 2 つの異なる構造を設けることによって実現され得る。 40

【0008】

この製造方法は、少なくとも部分的に、積層造形 (アディティブ造形) のステップ、すなわち、付加レイヤ造形 (added layer manufacturing ; A L M) 及び / 又は 3 D プリンティングのステップを有し得る。例えば、ピクセル化シンチレータ構造及び / 又は接続構造が、付加レイヤ造形及び / 又は 3 D プリンティングによって製造され得る。付加レイヤ造形及び / 又は 3 D プリンティングのプロセスは、小さい懸濁液滴の立て続けの堆積 (インクジェットプリンティング) 及び / 又は薄い局所的に硬化された層の堆積を有し得る 50

。一般に、積層造形すなわち A L M 及び / 又は 3 D プリンティングは、シンチレータ構造がレイヤ毎に製造されることを可能にする。設けられた構造すなわちシンチレータ構造及び / 又は接続構造は、バインダ材料内に所謂グリーン相粒子を有し得る。これらのバインダ材料内のグリーン相粒子が、焼結ステップとしても参照する加熱工程の後に、セラミックシンチレータを形成し得る。ピクセル化シンチレータ構造及び / 又は接続構造は、例えば、積層造形によって堆積され得る。例えば、ピクセル化シンチレータ構造及び / 又は接続構造が加工面上に堆積され得る。

【 0 0 0 9 】

シンチレータは、高エネルギー光子及び / 又は電離放射線によって（例えば、X 線によって）励起されるときにシンチレーションを呈するデバイスを指し得る。ピクセル化シンチレータは、当該ピクセル化シンチレータのその他のピクセルとは独立にシンチレーションを放つように構成された複数の分離されたピクセルを有し得る。ピクセル化シンチレータのピクセルは、例えば、正方形又は円形の断面を有し得る。換言すれば、ピクセル化シンチレータ構造のピクセルは、直方体又は円筒の形状を有し得る。しかしながら、ピクセル化シンチレータ構造のピクセルはまた、別の形状を有していてもよい。

10

【 0 0 1 0 】

ピクセル化されたシンチレータ、すなわち、ピクセル化シンチレータ構造及び / 又は接続構造は、タリウムドープされたヨウ化セシウム Cs I : Tl、又はその他のセラミックシンチレーション材料を有することができる。例えば、ピクセル化されたシンチレータ、すなわち、ピクセル化シンチレータ構造及び / 又は接続構造は、ヨウ化セシウム、又は硫化亜鉛、又はヨウ化ナトリウム、又はオキシオルトケイ酸ルテチウム、又は酸化ビスマスゲルマニウム、又はその他のシンチレーション材料を有する群から選択される材料を有することができる。特に、核医学での撮像及び熱量測定で使用されるシンチレーション無機結晶の一種である GSO として知られているオキシオルトケイ酸ガドリニウム、又はシンチレーション結晶としての主用途を持つ無機化合物である LYSO としても知られるオキシオルトケイ酸ルテチウムイットリウムのようなシンチレーション材料が使用され得る。

20

【 0 0 1 1 】

また、ピクセル化されたシンチレータ、すなわち、ピクセル化シンチレータ構造及び / 又は接続構造では、例えば、少量の活性剤不純物を有することが多いハロゲン化アルカリ金属である Na I (Tl) (タリウムでドープされたヨウ化ナトリウム) といった、無機シンチレータが使用されてもよい。他の無機ハロゲン化アルカリ結晶は、例えば：Cs I (Tl)、Cs I (Na)、Cs I (純)、Cs F、KI (Tl)、Li I (Eu) である。幾つかの非アルカリ結晶は、Ba F<sub>2</sub>、Ca F<sub>2</sub> (Eu)、Zn S (Ag)、Ca W O<sub>4</sub>、Cd W O<sub>4</sub>、YAG (Ce) (Y<sub>3</sub>Al<sub>5</sub>O<sub>12</sub> (Ce)) を含み得る。さらに、ピクセル化されたシンチレータ、すなわち、ピクセル化シンチレータ構造及び / 又は接続構造では、イットリウムアルミニウムガーネット；YAG、Y<sub>3</sub>Al<sub>5</sub>O<sub>12</sub>、又はガーネット群若しくはケイ酸塩鉱物のその他の合成結晶材料が使用されてもよく、あるいは、何らかの金属間化合物若しくは合金、又は例えばイットリウム、セリウム、テルビウム、ガリウム若しくはガドリニウムのような希土類金属を含むその他の金属化合物が使用されてもよい。

30

【 0 0 1 2 】

ピクセル化シンチレータ構造を設けることは、ピクセル化シンチレータ構造を付加するステップを指し得る。例えば、ピクセル化シンチレータ構造は、積層造形すなわち A L M 及び / 又は 3 D プリンティングによって付加され得る。また、ピクセル化シンチレータ構造は、最初に付加され得るものである接続構造の上に付加され得る。

40

【 0 0 1 3 】

本発明の文脈において、焼結収縮係数なる用語は、ピクセル化シンチレータ構造及び接続構造それぞれの材料の特性を表し得る。焼結収縮係数は、焼結中のそれぞれの材料の収縮率を指し得る。例えば、焼結収縮係数は、百分率の単位で表され得る。焼結収縮係数は、その材料から作られた塊の長さの収縮のパーセンテージを指し得る。例えば、20 % の

50

焼結収縮係数は、焼結中に物体の長さが20%だけ縮むことを意味し得る。材料の焼結収縮係数は、例えば、この材料から作られた塊の長さを焼結前後に測定することによって決定され得る。この場合、焼結収縮係数は、焼結前の長さと焼結後の長さとの差を焼結前の長さで割ることによって計算され得る。例えば、ピクセル化シンチレータ構造の第1の焼結収縮係数が20%に達するとともに、接続構造の第2の焼結収縮係数が40%に達するとして得る。しかしながら、これらは単なる例示の値であり、別のものであってもよい。ピクセル化シンチレータ構造及び接続構造の焼結収縮係数は、例えば、ピクセル化シンチレータ構造及び接続構造のためのバインダ材料の具体的な相対量を選択することによって達成され得る。

## 【0014】

10

相異なる焼結収縮係数はまた、ピクセル化シンチレータ構造及び接続構造に対して相異なるセラミック材料を選択することによっても達成され得る。

## 【0015】

2つの隣接したピクセルは、互いの隣に位置するとともに間隙によって離隔された、シンチレータ構造の2つのピクセルを指し得る。換言すれば、間隙が、2つの隣接ピクセル間に位置し得る。シンチレータ構造はまた、3つ以上のピクセルを有することができ、これら複数のピクセルの各ピクセルが、間隙によって隣接ピクセルから隔てられ得る。

## 【0016】

接続構造は、2つの隣接ピクセルを接続するとともに2つの隣接ピクセルと機械的に接觸する構造体を指し得る。接続構造を実現することには様々な方法が存在する。例えば、接続構造は、2つの隣接ピクセルの下に置かれ得るものであるベースレイヤとして実現され得る。しかしながら、接続構造はまた、2つの隣接ピクセルの間に位置してもよく、すなわち、2つの隣接ピクセルを隔てる間隙の中に位置してもよい。さらに、接続構造はまた、連続した構造体を指してもよいし、2つの隣接ピクセルの双方と機械的に接觸する複数の孤立した接続構造を指してもよい。接続構造が隣接ピクセルの双方と機械的に接觸するという特徴は、接続構造の収縮が2つの隣接ピクセルに伝達されて、2つの隣接ピクセル間の間隙が縮小されることになるという特徴を表し得る。間隙の縮小は、間隙の幅の減少に關係し得る。

20

## 【0017】

30

ピクセル化シンチレータ構造及び接続構造を焼結するステップは、シンチレータ構造及び接続構造の加熱工程を指し得る。例えば、1600と1800との間の温度で焼結が行われる。焼結は大気圧で行われてもよい。さらに、ピクセル化シンチレータ構造及び接続構造の焼結の間、これらが焼結中に収縮し得るように、これらの構造の幾何学配置(コオメトリ)を固定する必要はないとし得る。すなわち、焼結ステップは、ピクセル化シンチレータ構造及び接続構造の幾何学配置が固定されないようにして実行され得る。

## 【0018】

40

記載された方法のステップは、記載された順序で実行されてもよいし、別の順序で又は互いに並行して実行されてもよい。例えば、ピクセル化シンチレータ構造を設けることは、接続構造を設けることの前、間、又は後に実行され得る。故に、ピクセル化シンチレータ構造はまた、接続構造と同時に設けられてもよい。

## 【0019】

この方法を用いることで、2つの隣接ピクセル間の間隙が最小化されるように、すなわち、ピクセル化シンチレータがより大きな検出器表面を有するように、ピクセル化されたシンチレータを製造することができる。斯くて、シンチレータの効率が最適化される。

## 【0020】

例示的な一実施形態によれば、接続構造はベース層であり、該ベース層上にピクセル化シンチレータ構造が堆積される。

## 【0021】

50

例えば、ベース層が最初に設けられ、後続ステップにて、該ベース層上にピクセル化シンチレータ構造が堆積される。ベース層は、ピクセル化シンチレータ構造の下に位置する

連続層とし得る。さらに、接続構造は、ベース層とし得るとともに加工面上に堆積されることができ、該ベース層上にピクセル化シンチレータ構造が堆積され得る。

【0022】

斯くして、ベース層は、ピクセル化シンチレータ構造とは独立に設けられ、すなわち、ここに記載される製造方法の別工程で設けられ得る。換言すれば、ベース層及びシンチレータ構造を設けるための装置は、最初にベース層を設け、後続工程でピクセル化シンチレータ構造を設けるように構成されることができる。

【0023】

例示的な更なる一実施形態によれば、ベース層は、0.2mmと2mmとの間の厚さを持ち、ピクセル化シンチレータ構造は、0.2mmと5mmとの間の厚さを持つ。

10

【0024】

例示的な更なる一実施形態によれば、当該方法は更に、接続構造を除去するステップを有する。例えばベース層である接続構造は、例えば、研削によって除去され得る。

【0025】

例示的な更なる一実施形態によれば、当該方法は更に、第3の焼結収縮係数を有する中間層構造を設けるステップを有し、第3の焼結収縮係数は、第1の焼結収縮係数よりも大きく、且つ第2の焼結収縮係数よりも小さい。さらに、中間層構造は、ベース層及びピクセル化シンチレータ構造と機械的に接触する。また、中間層構造は、ベース層及びピクセル化シンチレータ構造と共に焼結される。

【0026】

20

換言すれば、ベース層とピクセル化シンチレータ構造との間に中間層構造が設けられ、中間層構造は、相異なる焼結収縮係数に起因し得るベース層とピクセル化シンチレータ構造との間の応力を低減することができるよう、中間の焼結収縮係数を有する。斯くして、シンチレータの反りを回避する又は少なくとも抑制することができる。また、中間層構造はそれ自体、この中間層が焼結収縮係数の勾配を有するよう、異なる焼結収縮係数を持つ複数の異なる層を有することができる。中間層構造を、ベース層と各ピクセルとの間に置かれる別々の中間層構造として設けること、すなわち、各画素が当該画素とベース層との間に置かれた中間層構造を有するように設けることも可能である。

【0027】

例示的な更なる一実施形態によれば、接続構造は、2つの隣接ピクセルを離隔させる間隙の中に設けられる。接続構造は、例えば、2つの隣接ピクセル間を隔てる間隙を連続的に充填してもよいし、2つの隣接ピクセル間を隔てる間隙の中に孤立した点として設けられてもよい。

30

【0028】

換言すれば、接続構造は、例えばピクセル化シンチレータ構造の底部にて、シンチレータピクセル間に設けられ得る。ピクセル間の孤立した点として、すなわち、連続構造としてではなく、接続構造を設けることにより、ピクセル化シンチレータ構造の反りが更に抑制され又は回避され得る。また、接続構造は、例えば下端といった、間隙の一端にのみ置かれて得る。焼結の後、2つの隣接ピクセルを離隔させる間隙の中に接続構造を有するピクセル化シンチレータ構造の部分（例えば、下端）は、例えば検索によって、除去されることができる。

40

【0029】

例示的な更なる一実施形態によれば、ピクセル化シンチレータ構造を設けることは、積層レイヤ造形によって行われる。さらに、接続構造及び/又は中間層構造を設けることも、積層レイヤ造形によって行われてもよい。

【0030】

本発明の文脈において、積層レイヤ造形はまた、3Dプリンティングを指すことがあり、それは、小さい懸濁液滴の立て続けの堆積（インクジェットプリンティング）によって、又は薄い局所的に硬化された層の立て続けの堆積によって実行され得る。

【0031】

50

例示的な更なる一実施形態によれば、設けられたピクセル化シンチレータ構造のピクセルは、0.05 mmと2 mmとの間の幅を持ち、設けられたピクセル化シンチレータ構造の間隙は、焼結後に150 μm未満の幅を持つ。好ましくは、設けられたピクセル化シンチレータ構造の間隙の幅は、焼結後に、100 μm未満、より好ましくは50 μm未満、よりいっそう好ましくは10 μm未満の幅を有し得る。

【0032】

例示的な更なる一実施形態によれば、第1の焼結収縮係数と第2の焼結収縮係数との間の比は、0.95と0.2との間である。例えば、ピクセル化シンチレータ構造は、20%に達する第1の焼結収縮係数を有することができ、接続構造は、40%に達する第2の焼結収縮係数を有することができる。

10

【0033】

このような比の第1及び第2の焼結収縮係数を用いることで、間隙の収縮がピクセルの収縮よりも強くなつて、シンチレータ表面及びシンチレータの効率が向上される。

【0034】

例示的な更なる一実施形態によれば、設けられたピクセル化シンチレータ構造は、第1の相対量で結合材（バインディング材料）を有するシンチレーション用セラミック材料を有する。設けられた接続構造は、第2の相対量で結合材を有するシンチレーション用セラミック材料を有する。結合材の第1の相対量及び結合材の第2の相対量は相異なる。

【0035】

結合材の相対量は、シンチレータ構造及び接続構造それぞれにおける結合材の粒子濃度を指し得る。結合材の第1の相対量と結合材の第2の相対量との間の差異が、第1の焼結収縮係数が第2の焼結収縮係数とは異なることを生じさせ得る。

20

【0036】

例示的な他の一実施形態によれば、当該方法は更に、ピクセル化シンチレータ構造を反射コーティング材料でコーティングするステップを有する。ピクセル化シンチレータ構造をコーティングすることにより、ピクセルを離隔させる間隙が光反射材料で充填され得る。

【0037】

例えば、反射性の例えは白色の粒子を有するエポキシ材料といった光反射材料で、ピクセル化シンチレータ構造がコーティングされ得る。このエポキシ材料は、TiO<sub>2</sub>充填されたエポキシリフレクタとし得る。これに代えて、Al又はAgの薄い反射層がピクセル化シンチレータ構造に適用されてもよい。

30

【0038】

本発明の他の一態様は、第1の焼結収縮係数を持つピクセル化シンチレータ構造を有するピクセル化されたシンチレータに関し、ピクセル化シンチレータ構造は、間隙によって離隔された2つの隣接ピクセルを有する。当該ピクセル化されたシンチレータは更に、上記2つの隣接ピクセルの双方と機械的に接触した接続構造を有し、接続構造は、第1の焼結収縮係数よりも大きい第2の焼結収縮係数を有する。

【0039】

ここに記載される方法に關して記述されたピクセル化されたシンチレータの特徴はまた、本発明のこの態様に従つたピクセル化されたシンチレータをも記述又は規定し得る。本発明のこの態様に従つたピクセル化されたシンチレータは、例えば、ここに記載される方法の中間プロダクトであり得る。例えば、このピクセル化されたシンチレータは、焼結プロセスの前に出現し得る。このピクセル化されたシンチレータは、当該ピクセル化されたシンチレータを焼結した後に間隙がピクセルよりももっと収縮されるという特性を有することができ、それにより、シンチレータ表面及びシンチレータの効率が最大化されるようになる。

40

【0040】

更なる一態様は、間隙によって離隔された2つの隣接ピクセルを有するピクセル化シンチレータ構造を有するピクセル化されたシンチレータに関し、この間隙は150 μm未満

50

の幅を持つ。好ましくは、ピクセル化シンチレータ構造の間隙の幅は、100 μm未満、より好ましくは50 μm未満、よりいっそう好ましくは10 μm未満の幅を有し得る。

【0041】

このピクセル化されたシンチレータは、本発明の文脈にて記述された方法で製造され得る。故に、このピクセル化されたシンチレータは、ここに記載される方法の最終プロダクトに関係し得る。例えば、このピクセル化されたシンチレータは、例えばALM及び/又は3Dプリンティングといった付加レイヤ造形によって製造される。また、ピクセル化シンチレータ構造は、記載される方法に関する記述されるように焼結され得る。このピクセル化されたシンチレータは、記載される製造方法で使用される材料を有し得る。故に、ピクセル化シンチレータ構造は、例えば、タリウムドープされたヨウ化セシウムCsI:Tl、又はここに記載されるその他のセラミックシンチレーション材料といった、シンチレーション用セラミック材料を有し得る。

【0042】

例示的な一実施形態によれば、ピクセル化シンチレータ構造のピクセルは、0.05m mと2mmとの間の幅を持つ。また、ピクセル化シンチレータ構造は、0.2mmと5mmとの間の厚さを持つ。

【0043】

本発明の更なる一態様は、本発明の文脈にて記述されたピクセル化されたシンチレータを有する検出器に関する。

【0044】

この検出器は、例えばX線検出器といった放射線検出器とし得る。

【0045】

本発明の更なる一態様は、本発明の文脈にて記述された検出器を有する撮像装置に関する。

【0046】

この撮像装置は、例えばX線撮像装置といった医用撮像装置とし得る。

【0047】

本発明のこれら及びその他の態様が、以下に記載される実施形態を参照して明らかになる。

【図面の簡単な説明】

【0048】

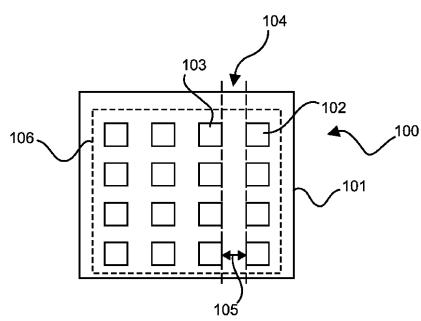

【図1】本発明の例示的な一実施形態に従ったピクセル化されたシンチレータを示している。

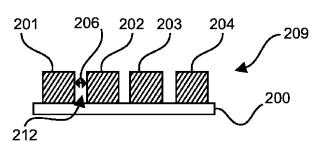

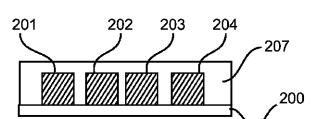

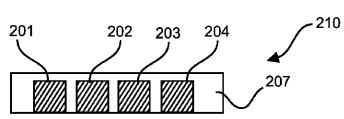

【図2A】図2A-2Eは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

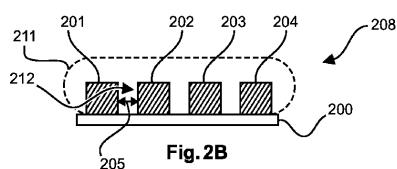

【図2B】図2A-2Eは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

【図2C】図2A-2Eは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

【図2D】図2A-2Eは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

【図2E】図2A-2Eは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

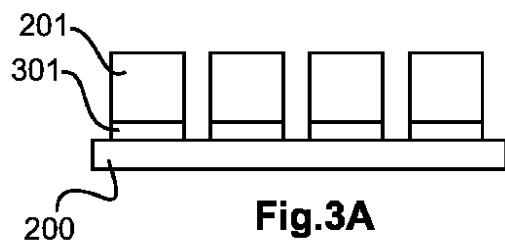

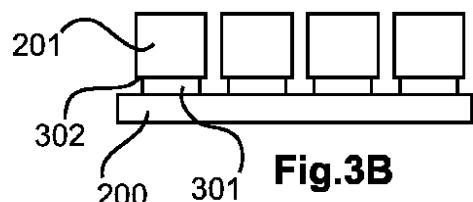

【図3A】図3A及び3Bは、本発明の例示的な実施形態に従った、焼結の前及び後の、中間層を有するピクセル化されたシンチレータを示している。

【図3B】図3A及び3Bは、本発明の例示的な実施形態に従った、焼結の前及び後の、中間層を有するピクセル化されたシンチレータを示している。

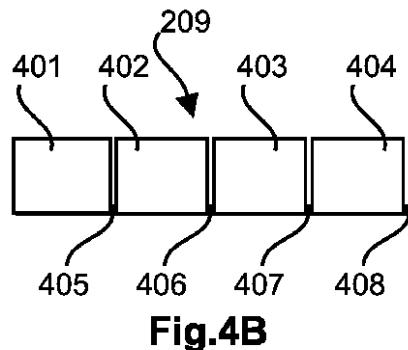

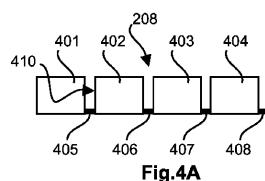

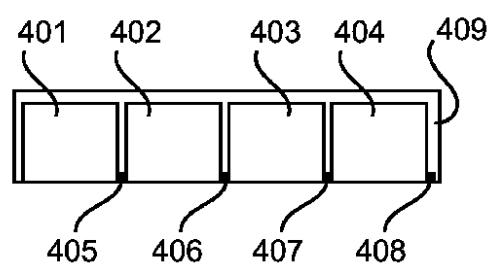

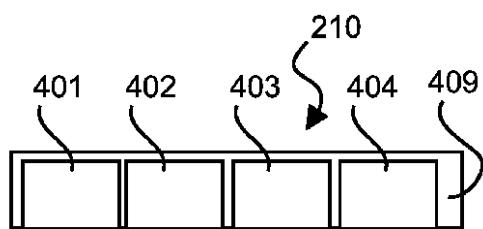

【図4A】図4A-4Dは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

【図4B】図4A-4Dは、本発明の例示的な実施形態に従ったピクセル化されたシンチ

10

20

30

40

50

レータの様々な製造ステップを示している。

【図4C】図4A - 4Dは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

【図4D】図4A - 4Dは、本発明の例示的な実施形態に従ったピクセル化されたシンチレータの様々な製造ステップを示している。

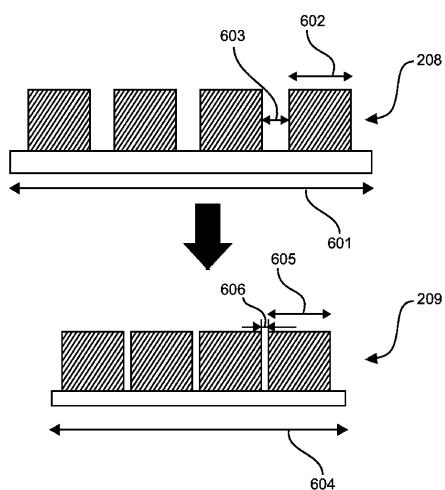

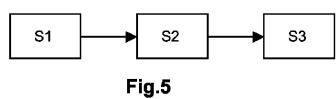

【図5】本発明の例示的な一実施形態に従った方法のフローチャートを示している。

【図6】焼結前後の本発明の例示的な一実施形態に従ったピクセル化されたシンチレータを示している。

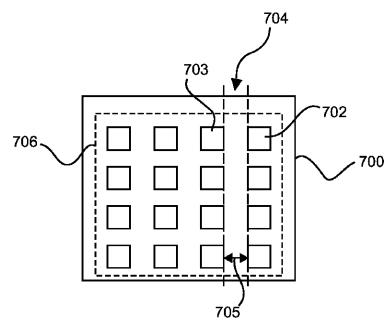

【図7】本発明の例示的な一実施形態に従った検出器を示している。

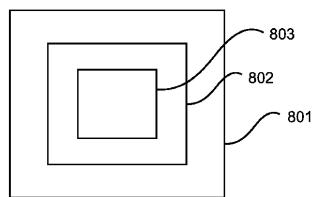

【図8】本発明の例示的な一実施形態に従った撮像装置を示している。これらの図は、

模式的であり、縮尺通りではない。同じ参照符号が複数の異なる図で使用されている場合

、それらは同一又は同様の要素を指しているとし得る。しかしながら、同様又は同一の要素

が異なる参照符号を付されることもある。

【発明を実施するための形態】

【0049】

明瞭化のため、これらの例示的な実施形態においては、少数のピクセルを有するピクセル化されたシンチレータが示される。しかしながら、ピクセル化されたシンチレータはまた、もっと多数のピクセルを有することができ、例えば、 $16 \times 16$ ピクセル、又は他の数のピクセルを有し得る。

【0050】

図1は、本発明の例示的な一実施形態に従ったピクセル化されたシンチレータ100を示している。ピクセル化されたシンチレータ100は、第1の焼結収縮係数を持つピクセル化シンチレータ構造106を有しており、ピクセル化シンチレータ構造106は、間隙104によって離隔された2つの隣接したピクセル102、103を有している。さらに、ピクセル化されたシンチレータ100は、2つの隣接ピクセル102、103の双方と、これら2つの隣接ピクセルの底面でのみ機械的に接触した接続構造101を有しており、接続構造101は、第1の焼結収縮係数よりも大きい第2の焼結収縮係数を有する。焼結収縮係数は、例えば図6を参照して説明される。

【0051】

この例示的な実施形態において、接続構造101はベース層であり、その上にピクセル化シンチレータ構造106が設けられている。ベース層101はまた、例えば、積層造形及び/又は3Dプリンティングによって設けられ、連続した平面層として形成される。

【0052】

この例示的な実施形態に従ったピクセル化されたシンチレータ100は、ここに記載される方法の中間プロダクトであり、焼結工程の前として示されている。焼結前、2つの隣接ピクセル102と103とを隔てる間隙104は、例えば $100 \mu m$ 以上に達する幅105を持つ。焼結後、間隙104の幅105は $50 \mu m$ 未満となる。

【0053】

図2A - 2Eは、ここに記載されるピクセル化されたシンチレータを製造する方法の様々な中間プロダクトを示している。これらの図は、側面図にて示されている。

【0054】

図2Aには、記載される方法に従って設けられる、この実施形態ではベース層200である接続構造200が示されている。ベース層200は、第2の焼結収縮係数を有する。

【0055】

図2Bには、ピクセル化シンチレータ構造211を配設した後の中間プロダクトが示されている。ピクセル化シンチレータ構造211は、ベース層200上に堆積され、複数の離隔されたピクセル201、202、203及び204を有している。隣接するピクセル201と202とが、幅205を持つ間隙212によって隔てられる。この中間プロダクトは、焼結前のピクセル化されたシンチレータ208であり、2つの隣接ピクセル201と202とを隔てる間隙212の幅205は、例えば $100 \mu m$ に達する。ピクセル化シ

10

20

30

40

50

ンチレータ構造は、ベース層 200 の第 2 の焼結収縮係数よりも小さい第 1 の焼結収縮係数を有する。

【0056】

図 2 C には、焼結後のピクセル化されたシンチレータ 209 (ここに記載される方法の中間プロダクト) が示されている。焼結工程の間に、ピクセル 201、202、203 及び 204、並びにベース層 200 が収縮している。しかしながら、ベース層 200 の大きめの第 2 の焼結収縮係数により、ベース層 200 がピクセル 201、202、203 及び 204 よりもいっそう収縮しており、その結果、間隙 212 の幅 206 が、ピクセル 201、202、203 及び 204 よりもいっそう収縮している。

【0057】

図 2 D には、ベース層 200 上に位置するピクセル 201、202、203 及び 204 が例えればエポキシリフレクタといったコーティング材料 207 でコーティングされた後の、ここに記載される方法の中間プロダクトが示されている。

【0058】

図 2 E には、ベース層 200 が除去された (例えれば、研削により除去された) 後の、最終的なピクセル化されたシンチレータ 210 が示されている。故に、ピクセル 201、202、203 及び 204 を有するピクセル化シンチレータ構造、並びにコーティング材料 207 のみが残存している。

【0059】

図 3 A 及び 3 B に、焼結工程の前及び後のピクセル化されたシンチレータを示す。このピクセル化されたシンチレータは、中間層構造 301 を有している。図 3 A には、焼結前のピクセル化されたシンチレータが、この例ではベース層 200 である接続構造 200 と、離隔された複数のピクセルとを有しており、各ピクセル 201 とベース層 200 との間に中間層構造 301 が置かれていることが示されている。この例示的な実施形態によれば、最初にベース層 200 が設けられ、続いて中間層構造 301 が設けられる。中間層構造 301 は、ピクセル 201 が設けられることになる位置に配設された複数の離隔された中間層構造 301 を有するようにして設けられる。しかしながら、中間層構造 301 はまた、ベース層 200 上に置かれた連続層として設けられてもよい。

【0060】

図 3 B には、焼結工程後の、中間層構造を有するピクセル化されたシンチレータが示されている。中間層構造 301 は、ベース層 200 の第 2 の焼結収縮係数よりも小さく且つピクセル化シンチレータ構造のピクセル 201 の第 1 の焼結収縮係数よりも大きい第 3 の焼結収縮係数を持っているので、中間層構造 301 は中間的な収縮を有する。換言すれば、中間層構造 301 は、焼結工程中に、ベース層 200 ほど収縮せず、ピクセル 201 よりも収縮する。斯くして、より小さい応力のみが、ピクセル 201 を有するピクセル化シンチレータ構造とベース層 200 との間に発生する。

【0061】

図 4 A - 4 D には、ここに記載される方法の中間プロダクトが示されており、ここでは、接続構造が、ピクセル化シンチレータ構造のピクセル間に置かれた複数の分離された接続構造を有している。

【0062】

図 4 A には、複数のピクセル 401、402、403 及び 404 が設けられ、これらのピクセル間に置かれた分離された接続構造 405、406、407 及び 408 を接続構造が有することが示されている。換言すれば、隣接するピクセル 401 と 402 とが間隙 410 によって離隔され、間隙 410 の中に接続構造 405 が置かれている。斯くして、接続構造 405 は、隣接ピクセル 401 及び 402 の双方と機械的に接觸する。同様に、接続構造 406 及び 407 も、2 つの隣接ピクセル 402 と 403 又は 403 と 404 との間の間隙の中に置かれている。故に、図 4 A には、焼結前のピクセル化されたシンチレータ 208 が示されている。接続構造 405、406、407 及び 408 は、間隙全体を充填しないようにして設けられ得る。例えれば、それらはそれぞれ、ピクセル化シンチレータ

10

20

30

40

50

構造及び間隙の下側部分のみに設けられ得る。

【0063】

図4Bには、焼結後のピクセル化されたシンチレータ209が示されている。焼結中に、ピクセル401、402、403及び404、並びに接続構造405、406、407及び408が収縮している。しかしながら、接続構造の第2の焼結収縮係数が、ピクセル401、402、403及び404を有するピクセル化シンチレータ構造の第1の焼結収縮係数よりも大きいため、ピクセル間の間隙がピクセルよりもいっそう収縮している。

【0064】

図4Cには、ピクセル401、402、403及び404並びに接続構造405、406、407及び408をコーティング材料409で（例えば、エポキシリフレクタで）コーティングした後の、ここに記載される方法で製造されるピクセル化されたシンチレータが示されている。図4Dには、最終的なピクセル化されたシンチレータ210が示されており、接続構造405、406、407及び408が位置していたピクセル401、402、403及び404の下側部分が除去（例えば、研削により除去）されている。故に、ピクセル化シンチレータ構造のピクセル401、402、403及び404、並びにコーティング材料409のみが残存している。

【0065】

例示的な実施形態では、ピクセル化シンチレータ構造がコーティング材料でコーティングされて接続構造が除去されることが示されているが、この工程が行われないピクセル化シンチレータも存在し得る。

【0066】

図5には、本発明の例示的な一実施形態に従ったピクセル化されたシンチレータを製造する方法のフローチャートが示されている。この方法のステップS1は、第1の焼結収縮係数を有するピクセル化シンチレータ構造を設けるステップに関係し、ピクセル化シンチレータ構造は、間隙によって離隔された2つの隣接ピクセルを有する。ステップS2は、2つの隣接ピクセルの双方と機械的に接触する接続構造を設けることに関係し、接続構造は、第1の焼結収縮係数よりも大きい第2の焼結収縮係数を有する。ステップS3にて、ピクセル化シンチレータ構造及び接続構造の焼結が実行されて、間隙が縮小される。

【0067】

ステップS1、S2及びS3が順次に実行されることが示されているが、これらのステップはまた、異なる順序で実行されてもよい。例えば、ステップS2がステップS1の前に実行され得る。また、ステップS1及びS2を同時に実行することができる。例えば、図4A-4Dに示したように2つの隣接ピクセル間に接続構造を設けるとき、ピクセル化シンチレータ構造及び接続構造は、例えば同じプリントヘッドを用いて、同じ方法ステップで設けられ得る。

【0068】

図6は、焼結前の、本発明の例示的な一実施形態に従ったピクセル化されたシンチレータ208と、焼結後の同じピクセル化されたシンチレータ209とを示している。このピクセル化されたシンチレータは、例えば、図2A-2Eに関して記述されたものに相当する。焼結前において、接続構造すなわちベース層は長さ $S_p$ 601を持ち、ピクセルは幅 $P_p$ 602を持ち、そして、2つの隣接ピクセル間の間隙は幅 $G_p$ 603を持っている。焼結後において、接続構造は長さ $S_s$ 604を持ち、ピクセルは幅 $P_s$ 605を持ち、そして、2つの隣接ピクセル間の間隙は幅 $G_s$ 606を持っている。ピクセル化シンチレータ構造の第1の焼結収縮係数 $C_1$ は、

$$C_1 = (P_p - P_s) / P_p$$

として計算されることがある。接続構造の第2の焼結収縮係数 $C_2$ は、

$$C_2 = (S_p - S_s) / S_p$$

として計算されることがある。

【0069】

前述したように、第2の焼結収縮係数は、第1の焼結収縮係数よりも大きく、すなわち

10

20

30

40

50

、ベース層は、焼結中に、ピクセル化シンチレータ構造よりも大きい収縮を有する。間隙の焼結収縮係数は、第2の焼結収縮係数  $C_2$  に略等しい。

【0070】

図7は、本発明の文脈にて記述されたピクセル化されたシンチレータ706を有する検出器700を示している。このピクセル化されたシンチレータは、間隙704によって離隔された少なくとも2つの隣接ピクセル702及び703を有する焼結されたピクセル化シンチレータを有する。間隙704の幅705は150μmよりも小さい。

【0071】

図8は、本発明の文脈にて記述された検出器802(例えば、図7に示した検出器)を有する撮像装置801を示している。検出器802は、ピクセル化されたシンチレータ803を有している。

10

【0072】

開示の実施形態へのその他の変形が、図面、本開示及び添付の請求項の検討から、請求項に係る発明を実施する当業者によって理解されて実現され得る。請求項において、用語“有する”はその他の要素又はステップを排除するものではなく、不定冠詞“a”又は“a n”は複数であることを排除するものではない。特定の複数の手段が相互に異なる従属項に記載されているという単なる事実は、それらの手段の組合せが有利に使用され得ないということを指し示すものではない。請求項中の如何なる参照符号も、範囲を限定するものとして解されるべきでない。

【図1】

Fig. 1

【図2C】

Fig. 2C

【図2D】

Fig. 2D

【図2A】

Fig. 2A

【図2E】

Fig. 2E

【図2B】

Fig. 2B

【図3A】

【図4B】

【図3B】

【図4A】

【図4C】

【図4D】

Fig.4D

【図6】

【図5】

Fig.6

【図7】

Fig. 7

【図8】

Fig. 8

---

フロントページの続き

(74)代理人 100091214

弁理士 大貫 進介

(72)発明者 ヤコブス, ヨーハネス ウィルヘルミス マリア

オランダ国 5656 アーエー アンドーフェン ハイテック キャンパス 5

(72)発明者 ウィメルス, オンノ ヤン

オランダ国 5656 アーエー アンドーフェン ハイテック キャンパス 5

(72)発明者 フアン ウーケル, ジャック ジュール

オランダ国 5656 アーエー アンドーフェン ハイテック キャンパス 5

審査官 道祖土 新吾

(56)参考文献 特開2001-220232(JP, A)

特開2009-189801(JP, A)

特開2004-117347(JP, A)

国際公開第2012/161304(WO, A1)

特開2001-099941(JP, A)

国際公開第2016/006484(WO, A1)

米国特許出願公開第2010/0127180(US, A1)

特開2005-300190(JP, A)

(58)調査した分野(Int.Cl., DB名)

G01T 1/20

G21K 4/00