(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6359892号

(P6359892)

(45) 発行日 平成30年7月18日(2018.7.18)

(24) 登録日 平成30年6月29日(2018.6.29)

(51) Int.Cl.

F 1

|              |           |      |        |         |

|--------------|-----------|------|--------|---------|

| H01L 29/786  | (2006.01) | H01L | 29/78  | 6 1 8 E |

| H01L 21/8242 | (2006.01) | H01L | 29/78  | 6 1 8 B |

| H01L 27/108  | (2006.01) | H01L | 27/108 | 3 2 1   |

| H01L 21/336  | (2006.01) | H01L | 29/78  | 3 7 1   |

| H01L 29/788  | (2006.01) | H01L | 27/108 | 6 7 1 C |

請求項の数 3 (全 45 頁) 最終頁に続く

(21) 出願番号

特願2014-131751 (P2014-131751)

(22) 出願日

平成26年6月26日 (2014.6.26)

(65) 公開番号

特開2015-29087 (P2015-29087A)

(43) 公開日

平成27年2月12日 (2015.2.12)

審査請求日

平成29年6月21日 (2017.6.21)

(31) 優先権主張番号

特願2013-136451 (P2013-136451)

(32) 優先日

平成25年6月28日 (2013.6.28)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 桑原 秀明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 遠藤 佑太

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 立石 真理

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 高橋 正弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

酸化物半導体層と、

前記酸化物半導体層と重なるゲート電極層と、

前記酸化物半導体層と前記ゲート電極層の間のゲート絶縁層と、

前記酸化物半導体層と電気的に接続されたソース電極層及びドレイン電極層と、

前記酸化物半導体層を介して前記ゲート絶縁層と重なる絶縁層と、を有し、

前記酸化物半導体層は、第1の層と、前記第1の層と前記絶縁層との間の第2の層とを有し、

前記第1の層及び前記第2の層はそれぞれ、10nm以下のサイズの結晶を含み、

前記第1の層は、電子線のプローブ径を1nm以上10nm以下に収束させたナノビーム電子線回折における回折パターンにおいて、円周状に配置された複数のスポットが観察される第1の領域を有し、且つ前記第1の領域は、前記第1の層の断面方向からの透過型電子顕微鏡による観察において結晶構造が観察されず、

前記第2の層は、電子線のプローブ径を1nm以上10nm以下に収束させたナノビーム電子線回折における回折パターンにおいて、円周状に配置された複数のスポットが観察される第2の領域を有し、且つ前記第2の領域は、前記第2の層の断面方向からの透過型電子顕微鏡による観察において結晶構造が観察されず、

前記第1の層及び前記第2の層はそれぞれ、In-M-Zn酸化物 (Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf) で表記される酸化物半導体層であり、且

10

20

つ、前記第2の層のインジウムに対するMの原子数比は前記第1の層のインジウムに対するMの原子数比よりも高いことを特徴とする半導体装置。

【請求項2】

請求項1において、

前記絶縁層は、前記酸化物半導体層上に接して設けられ、且つ第1の開口部を有し、

前記第1の開口部を介して、前記酸化物半導体層と、前記ソース電極層及び前記ドレイン電極層の一方とが接する半導体装置。

【請求項3】

請求項2において、

前記第2の層は、前記第1の開口部と重なる第2の開口部を有し、

10

前記ソース電極層及び前記ドレイン電極層の一方は、前記第1の開口部及び前記第2の開口部を介して、前記第1の層と接する半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書で開示する発明は、半導体装置および半導体装置の作製方法に関する。

【0002】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路、表示装置、発光装置及び電子機器はすべて半導体装置である。

20

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは、集積回路（IC）や画像表示装置（単に表示装置とも表記する。）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体膜としてシリコン系半導体材料が広く知られているが、その他の材料として半導体特性を示す金属酸化物（酸化物半導体）が注目されている。

【0004】

例えば、酸化物半導体として、In、Zn、Ga、Snなどを含む非晶質酸化物を用いてトランジスタを作製する技術が特許文献1で開示されている。

30

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006-165529号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

酸化物半導体を用いたトランジスタは、比較的容易にトランジスタ特性を得られるものの、物性が不安定になりやすく、信頼性の確保が困難である。

【0007】

40

そこで、本発明の一態様は、酸化物半導体を含み、信頼性の高い半導体装置を提供することを課題の一とする。

【0008】

なお、上記の課題の記載は、他の課題の存在を妨げるものではない。上記以外の課題は、明細書等の記載から自ずと明らかになるものであり、明細書等の記載から上記以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0009】

開示する発明の一態様は、酸化物半導体層及び酸化物半導体層と接する絶縁層を含む積層構造を含み、酸化物半導体層は、チャネルが形成される第1の層と、第1の層と絶縁層と

50

の間に設けられ、第1の層の伝導帯下端のエネルギーよりも真空準位に近い伝導帯下端のエネルギーを有する第2の層とを含む。上記において、第2の層は、酸化物半導体層と接する絶縁層と、チャネルとの間に欠陥準位が形成されることを抑制するバリア層として機能する。また、第1の層及び第2の層は、それぞれ巨視的には原子配列に周期性が見られない程度に極微細な結晶部を含む。例えば、1 nm以上10 nm以下の範囲で原子配列に周期性が確認される結晶部を含む。結晶部を含む第1の層及び第2の層は、非晶質酸化物半導体層と比較して欠陥準位密度が低減された酸化物半導体層であり、該酸化物半導体層を適用することで、欠陥準位密度に起因するトランジスタの電気特性の変動を抑制することができる。

【0010】

10

より具体的には、例えば以下の構成とすることができます。

【0011】

本発明の一態様は、酸化物半導体層と、酸化物半導体層と互いに重なるゲート電極層と、酸化物半導体層とゲート電極層の間のゲート絶縁層と、酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、酸化物半導体層を介してゲート絶縁層と互いに重なる絶縁層と、を有し、酸化物半導体層は、チャネルが形成される第1の層と、第1の層と絶縁層との間の第2の層との積層構造を含み、第1の層及び第2の層はそれぞれ、10 nm以下のサイズの結晶を含み、第1の層及び第2の層はそれぞれ、In-M-Zn酸化物（Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf）で表記される酸化物半導体層であり、且つ、第2の層のインジウムに対するMの原子数比は第1の層のインジウムに対するMの原子数比よりも高いことを特徴とする半導体装置である。

20

【0012】

また、本発明の一態様は、酸化物半導体層と、酸化物半導体層と互いに重なるゲート電極層と、酸化物半導体層とゲート電極層の間のゲート絶縁層と、酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、酸化物半導体層を介してゲート絶縁層と互いに重なる絶縁層と、を有し、酸化物半導体層は、チャネルが形成される第1の層と、第1の層と絶縁層との間の第2の層と、第1の層とゲート絶縁層との間の第3の層と、を含み、第1の層乃至第3の層はそれぞれ、10 nm以下のサイズの結晶を含み、第1の層、第2の層及び第3の層はそれぞれ、In-M-Zn酸化物（Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf）で表記される酸化物半導体層であり、且つ、第2の層のインジウムに対するMの原子数比及び第3の層のインジウムに対するMの原子数比はそれぞれ、第1の層のインジウムに対するMの原子数比よりも高いことを特徴とする半導体装置である。

30

【0013】

上記の半導体装置において、第3の層は、電子線のプローブ径を1 nm以上10 nm以下に収束させたナノビーム電子線回折における回折パターンにおいて、円周状に配置された複数のスポットが観察される。

【0014】

40

また、上記の半導体装置において、第1の層及び第2の層は、電子線のプローブ径を1 nm以上10 nm以下に収束させたナノビーム電子線回折における回折パターンにおいて、円周状に配置された複数のスポットが観察される。

【0015】

また、上記の半導体装置において、第2の層の伝導帯下端のエネルギーは、第1の層の伝導帯下端のエネルギーよりも0.05 eV以上2 eV以下の範囲で真空準位に近いことが好ましい。

【0016】

50

また、上記の半導体装置において、絶縁層は、酸化物半導体層上に接して設けられ、絶縁層に設けられたコンタクトホール（開口部とも呼ぶ）において、酸化物半導体層と、ソース電極層又はドレイン電極層とが電気的に接続してもよい。この場合、ソース電極層及びドレイン電極層は、絶縁層に及び第2の層に設けられたコンタクトホールにおいて、第1

の層と電気的に接続することが好ましい。

**【0017】**

また、上記の半導体装置において、ソース電極層及びドレイン電極層は、第1の層の側面及び上面の一部と接するように設けられ、第3の層は、ソース電極層及びドレイン電極層から露出した第1の層の一部と接するように、ソース電極層及びドレイン電極層上に設けられていてもよい。

**【発明の効果】**

**【0018】**

本発明の一態様によって、信頼性の高い半導体装置を提供することができる。

**【図面の簡単な説明】**

10

**【0019】**

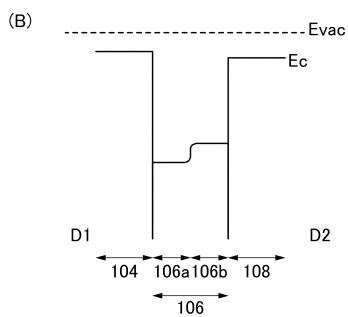

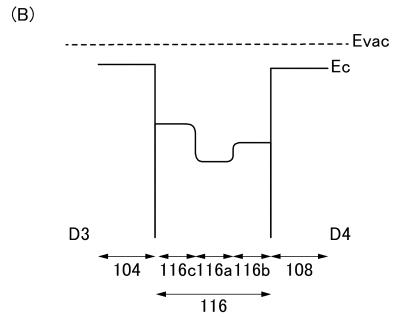

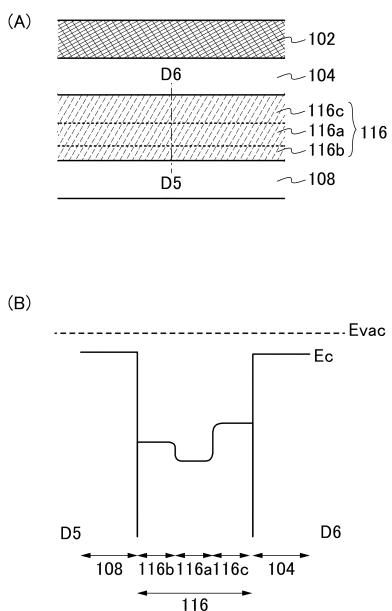

**【図1】**本発明の一態様の半導体装置に含まれる積層構造の一例及びそのバンド図を示す模式図。

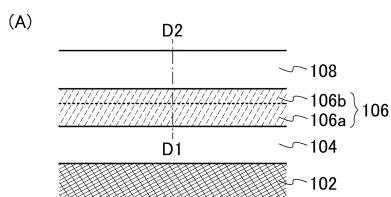

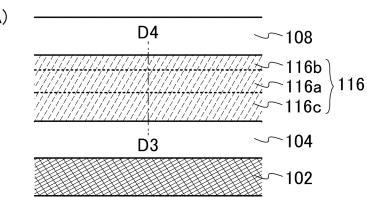

**【図2】**本発明の一態様の半導体装置に含まれる積層構造の一例及びそのバンド図を示す模式図。

**【図3】**本発明の一態様の半導体装置に含まれる積層構造の一例及びそのバンド図を示す模式図。

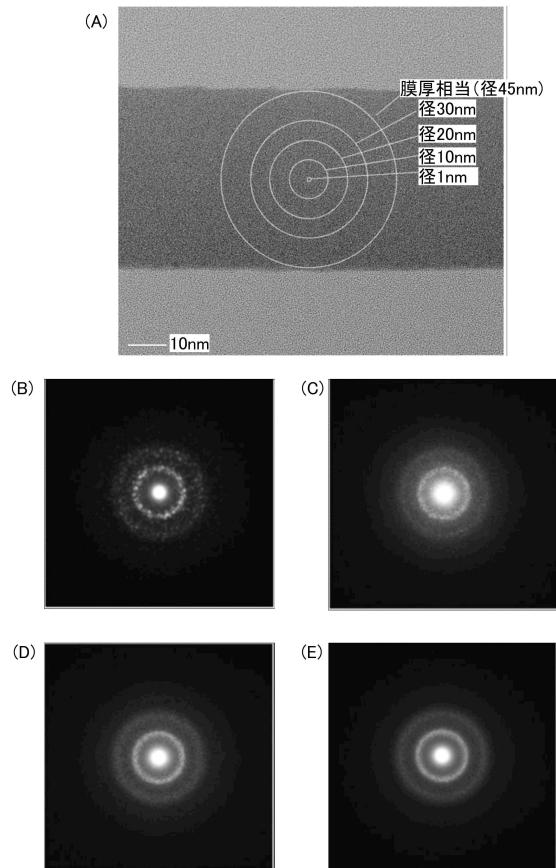

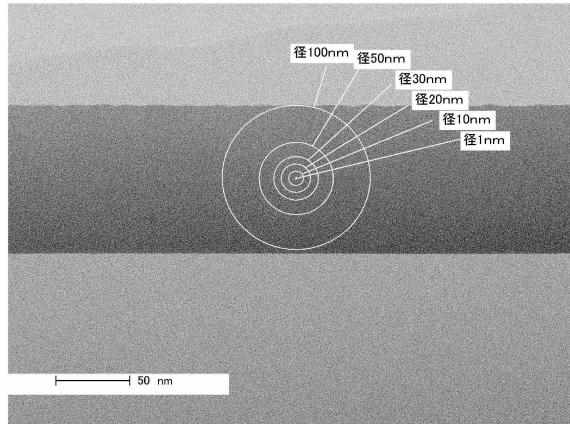

**【図4】**ナノ結晶酸化物半導体層の断面TEM像及びナノビーム電子線回折パターンを示す図。

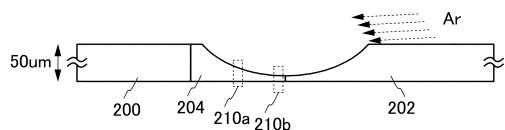

**【図5】**参考例の試料の作製方法を示す模式図。

20

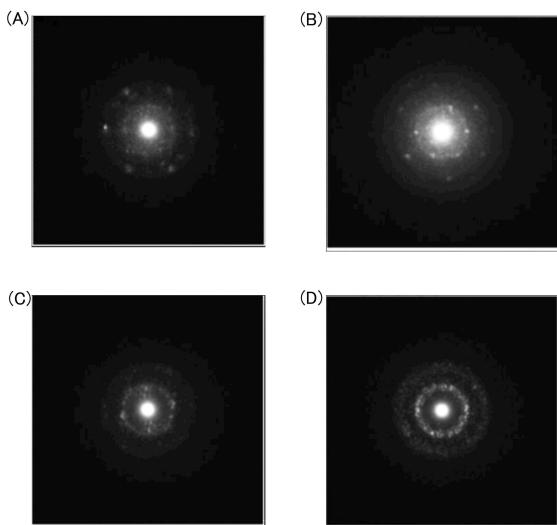

**【図6】**ナノ結晶酸化物半導体層のナノビーム電子線回折パターンを示す図。

**【図7】**ナノ結晶酸化物半導体層の断面TEM像を示す図。

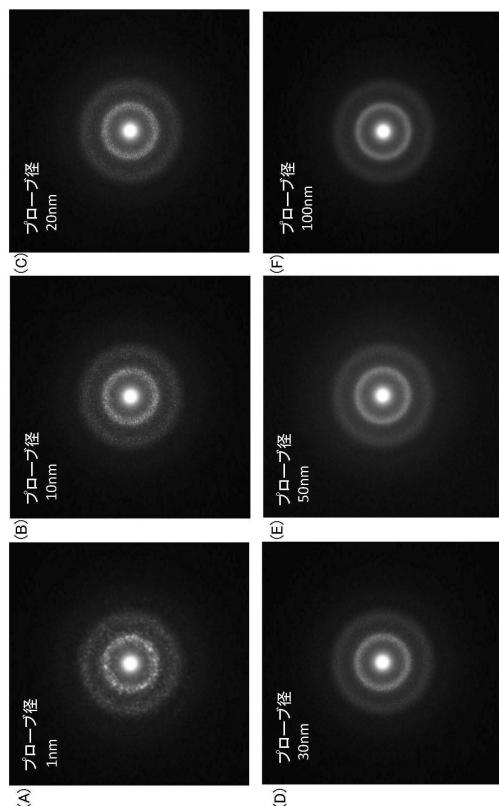

**【図8】**ナノ結晶酸化物半導体層のナノビーム電子線回折パターンを示す図。

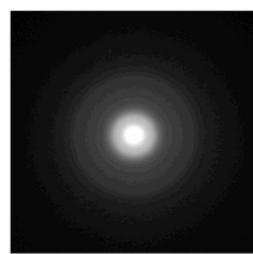

**【図9】**石英ガラス基板のナノビーム電子線回折パターンを示す図。

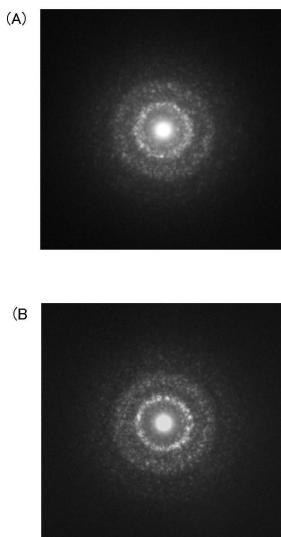

**【図10】**ナノ結晶酸化物半導体層のナノビーム電子線回折パターンを示す図。

**【図11】**ナノ結晶酸化物半導体層のXRDスペクトルの測定結果を示す図。

**【図12】**半導体装置の一態様を示す平面図及び断面図。

**【図13】**半導体装置の一態様を示す平面図及び断面図。

**【図14】**半導体装置の作製方法の一例を示す図。

**【図15】**半導体装置の一態様を示す平面図及び断面図。

30

**【図16】**半導体装置の一態様を示す平面図及び断面図。

**【図17】**半導体装置の作製方法の一例を示す図。

**【図18】**本発明の一態様の半導体装置の回路図。

**【図19】**本発明の一態様の半導体装置の回路図及び概念図。

**【図20】**実施の形態に係る表示パネルの構成を説明する図。

**【図21】**実施の形態に係る電子機器のブロック図を説明する図。

**【図22】**実施の形態に係る電子機器の外観図を説明する図。

**【発明を実施するための形態】**

**【0020】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

40

**【0021】**

なお、以下に説明する本発明の構成において、同一部分又は同様の機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を有する部分を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

**【0022】**

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭

50

化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0023】

なお、本明細書等において、第1、第2等として付される序数詞は、便宜上用いるものであり、工程順又は積層順を示すものではない。そのため、例えば、「第1の」を「第2の」又は「第3の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

【0024】

(実施の形態1)

本実施の形態では、本発明の一態様の半導体装置に含まれる酸化物半導体層について、図1乃至図11を参照して説明する。

10

【0025】

図1(A)は、本発明の一態様の半導体装置に含まれる積層構造の一例を示す模式図である。本発明の一態様の半導体装置は、ゲート電極層102と、ゲート電極層102上のゲート絶縁層104と、ゲート絶縁層104上の酸化物半導体層106と、酸化物半導体層106上の絶縁層108と、の積層構造を含む。

【0026】

酸化物半導体層106は、第1の層106aと、第1の層106aと絶縁層108との間の第2の層106bとの積層構造を有する。

20

【0027】

第1の層106a及び第2の層106bは、巨視的には原子配列に周期性が見られない程度に極微細な結晶部を含む酸化物半導体層である。具体的には、第1の層106a及び第2の層106bはそれぞれ、1nm以上10nm以下、又は1nm以上3nm以下のサイズの結晶部(以下、本明細書等においてナノ結晶(nc:nano crystal)とも表記する。)を含む。

【0028】

第1の層106a及び第2の層106bに含まれる結晶部は、当該結晶部の大きさに近い、又は結晶部の大きさよりも小さいプローブ径(例えば、1nm以上30nm以下)の電子線を照射して得られる電子線回折パターンにおいて、円を描くように(リング状に)輝度の高い領域を有し、且つ輝度の高い領域内に複数のスポット(輝点)が観察される。複数のスポットが円周状に配置されることで、リング状に輝度の高い領域を形成している、と言い換えることもできる。

30

【0029】

また、電子線回折による測定範囲を、平面方向及び奥行き方向ともに、含まれる結晶部の大きさに近い範囲以下、又は結晶部の大きさよりも小さい範囲以下に縮小することで、電子線回折パターンにおいて、結晶状態を示す規則性を有するスポットが観察される場合がある。平面方向の測定範囲を縮小するには、電子線のプローブ径を縮小(例えば、1nm以上30nm以下)すればよい。また、奥行き方向の測定範囲を縮小するには、例えば、イオンミリング加工等によって10nm以下に薄片化された領域を測定すればよい。

【0030】

40

なお、第1の層106a及び第2の層106bとともに、断面方向及び平面方向の双方の電子線回折パターンにおいて、上述のリング状の輝度の高い領域内に配置された複数のスポットを確認することが可能である。結晶部が、断面方向または平面方向の指向性を持たずして膜中にランダムに含まれることで、断面方向の電子線回折パターンで確認されるスポットと、平面方向の電子線回折パターンで確認されるスポットとは、同様の傾向を示す。

【0031】

なお、酸化物半導体層中に含まれる結晶部が、10nm以下であって用いるプローブ径よりも大きい結晶部を有すると、断面方向と平面方向との電子線回折パターンにおいて異なる傾向がみられる場合がある。例えば、断面方向にプローブ径よりも大きい原子配列の周期性を有し、平面方向にプローブ径と同等又はプローブ径よりも小さい原子配列の周期性

50

を有する結晶部を測定する場合、断面方向の電子線回折パターンで確認されるスポットは、平面方向の電子線回折パターンで確認されるスポットよりもプロードとなることがある。また、第1の層106a及び第2の層106bはそれぞれ、断面方向及び平面方向の電子線回折パターンの傾向が同様である領域と、異なる傾向がみられる領域と、を有する場合がある。例えば、第1の層106aにおいて、第2の層106bとの界面近傍においては、断面方向及び平面方向の電子線回折パターンに異なる傾向が見られ、ゲート絶縁層104との界面近傍においては、断面方向及び平面方向の電子線回折パターンが同様の傾向を示す場合がある。

#### 【0032】

なお、上述したように、第1の層106a及び第2の層106bにおいて原子配列に周期性を有する領域は、例えば1nm以上10nm以下と微小な範囲であり、また、異なる結晶部間では結晶方位に秩序性が見られない。したがって、第1の層106a及び第2の層106bはそれぞれ膜全体では配向性が見られない。そのため、酸化物半導体層106の分析方法によっては、第1の層106a及び第2の層106bに含まれる結晶部を解析することができずに、非晶質酸化物半導体層と区別がつかない場合ある。

#### 【0033】

例えば、結晶部を含む第1の層106a又は第2の層106bをそれぞれ、断面方向及び平面方向から透過型電子顕微鏡（TEM：Transmission Electron Microscope）によって観察しても、結晶構造を明確には確認することが困難である。

#### 【0034】

また、酸化物半導体層106に対して、第1の層106a及び第2の層106bに含まれる結晶部よりも大きい径のX線を用いるX線回折（XRD：X-Ray Diffraction）装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。

#### 【0035】

さらに、第1の層106a又は第2の層106bに対して、結晶部よりも大きいプローブ径（例えば、100nm以上）の電子線を用いる電子線回折（制限視野電子線回折ともいう。）では、ハローパターンのような回折パターンが観測される場合がある。

#### 【0036】

また、電子線のプローブ径を大きくするに伴って、上述したリング状の輝度の高い領域がプロードとなり、リングの幅が広くなることが確認される。また、プローブ径を例えば、50nm以上とすると、リング状の輝度の高い領域内にスポットを観察することが困難となる。

#### 【0037】

本実施の形態で示すナノ結晶を含む酸化物半導体層（以下、ナノ結晶酸化物半導体層とも表記する。）は、非晶質酸化物半導体層と比較して、膜密度が高く緻密な膜である。酸化物半導体層は、欠陥が少ない程、又は、水素等の不純物濃度が低い程、膜密度が高くなる。酸化物半導体層にとって、酸素欠陥及び/又は水素等の不純物は、欠陥準位の生成要因となるため、ナノ結晶を含む第1の層106a及び第2の層106bは、非晶質酸化物半導体層と比較して欠陥準位密度が低減された領域であるといえる。なお、本明細書等において非晶質酸化物半導体層とは、例えば、原子配列が無秩序であり、結晶成分を有さない酸化物半導体層を指す。

#### 【0038】

また、第1の層106aと、第2の層106bには、少なくともインジウム及び亜鉛を構成元素として有する金属酸化物を用いることが好ましい。また、第1の層106aと第2の層106bの構成元素を同一とし、両者の組成を異ならせてよい。

#### 【0039】

なお、本実施の形態において、第1の層106a及び第2の層106bはともに少なくともインジウム及び亜鉛を含むナノ結晶酸化物半導体層であり、材料や成膜条件によっては

10

20

30

40

50

、各領域同士の界面が不明確になる場合もある。よって、図1においては、第1の層106aと第2の層106bの界面を模式的に点線で図示している。これは以降の各図面においても同様である。

#### 【0040】

第1の層106aがIn-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf)で表記される酸化物半導体層である場合、第2の層106bとしては、第1の層106aと同様にIn-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf)で表記され、第1の層106aよりもインジウムに対するMの原子数比が高い酸化物半導体層とすることが好ましい。

#### 【0041】

より具体的には、第2の層106bとして、第1の層106aよりも前述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物半導体層を適用する。前述の元素Mは、インジウムよりも酸素と強く結合するため、インジウムに対するMの原子数比の高い酸化物半導体は、膜中での酸素欠損が生じにくい。すなわち、第2の層106bは、第1の層106aよりも酸素欠損が生じにくい酸化物半導体層である。なお、インジウムに対するMの原子数比が高い程、酸化物半導体層のエネルギーギャップ(バンドギャップ)が大きくなるため、インジウムに対するMの原子数比が高すぎると、第2の層106bは絶縁層として機能する。従って、第2の層106bが半導体層として機能しうる程度にインジウムに対するMの原子数比を調整することが好ましい。

#### 【0042】

第1の層106a及び第2の層106bがそれぞれ、少なくともインジウム、亜鉛およびM(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、第1の層106aを $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、第2の層106bを $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]とすると、 $y_2 / x_2$  を $y_1 / x_1$  よりも大きくすることが好ましい。 $y_2 / x_2$  は $y_1 / x_1$  よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、第1の層106aにおいて、 $y_1$  が $x_1$  以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_1$  が $x_1$  の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_1$  は $x_1$  の3倍未満であることが好ましい。

#### 【0043】

なお、第1の層106aがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。また、第2の層106bがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。

#### 【0044】

また、第2の層106bは、伝導帯下端のエネルギーが第1の層106aよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

#### 【0045】

このような構造において、ゲート電極層102に電界を印加すると、酸化物半導体層106のうち、伝導帯下端のエネルギーが最も小さい層である第1の層106aがキャリアの主な移動経路(チャネル)となる。ここで、チャネル形成領域(第1の層106a)と絶縁層108との間に第2の層106bを含むことにより、酸化物半導体層106と絶縁層108との界面において不純物及び欠陥により形成されうるトラップ準位と、チャネル形成領域との間には隔たりがある。この結果、第1の層106aを流れる電子がトラップ準位に捕獲されにくく、トランジスタのオン電流を増大させることが可能であると共に、電

10

20

30

40

50

界効果移動度を高めることができる。また、トラップ準位に電子が捕獲されると、該電子がマイナスの固定電荷となり、トランジスタのしきい値電圧の変動要因となる。しかしながら、第1の層106aとトラップ準位との間に隔たりがあるため、トラップ準位における電子の捕獲を低減することが可能であり、しきい値電圧の変動を低減することができる。

#### 【0046】

なお、第1の層106a及び第2の層106bは、各層を単に積層するのではなく連続接合（ここでは特に伝導帯の下端のエネルギーが各層の間で連続的に変化する構造）が形成されるように作製する。すなわち、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないような積層構造とする。仮に、積層された第1の層106aと第2の層106bとの間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界面でキャリアがトラップされ、あるいは再結合して、消滅してしまう。

#### 【0047】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体層にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa ~  $1 \times 10^{-4}$  Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。

#### 【0048】

図1(B)は、図1(A)の積層構造のD1-D2におけるバンド構造の一部を模式的に示している。ここでは、酸化物半導体層106と接する絶縁層であるゲート絶縁層104及び絶縁層108として酸化シリコン層を設けた場合について説明する。なお、図1(B)において、Evacは真空準位のエネルギーを示し、Ecは伝導帯下端のエネルギーを示す。

#### 【0049】

図1(B)に示すように、第1の層106a及び第2の層106bにおいて、伝導帯下端のエネルギーは障壁が無くなだらかに変化する。換言すると、連続的に変化するともいうことができる。これは、第1の層106aと第2の層106bが共通の元素を含み、双方の領域間で、酸素が相互に移動することで混合層が形成されるためであるということができる。

#### 【0050】

図1(B)より、酸化物半導体層106において第1の層106aがウェル（井戸）となり、チャネル領域が第1の層106aに形成されることがわかる。なお、酸化物半導体層106は、伝導帯下端のエネルギーが連続的に変化しているため、第1の層106aと第2の層106bとが連続接合している、ともいえる。

#### 【0051】

第2の層106bと絶縁層108との界面近傍には、絶縁層108の構成元素（例えばシリコン）または炭素等の不純物や、欠陥に起因したトラップ準位が形成され得るもの、チャネルが形成される第1の層106aとの間に第2の層106bが設けられることにより、第1の層106aとトラップ準位とを遠ざけることができる。ただし、第1の層106aと第2の層106bとのエネルギー差が小さい場合、第1の層106aの電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。したがって、第1の層106aと第2の層106bの伝導帯下端のエネルギー差を、0.05 eV以上、好ましくは0.15 eV以上とすると、トランジスタのしきい値電圧の変動が低減され、安定した電気特性となるため好適である。

#### 【0052】

10

20

30

40

50

酸化物半導体層を用いた半導体装置において、信頼性の向上のためにはチャネルとして機能する酸化物半導体層およびその界面の欠陥準位密度を低減する必要がある。特に、酸化物半導体層を用いたトランジスタのしきい値電圧のマイナス方向への変動は、チャネルとして機能する酸化物半導体層及びその界面の酸素欠損に起因する欠陥準位が原因であると考えられる。

#### 【0053】

そこで、本実施の形態に示すように、非晶質酸化物半導体層と比較して欠陥準位密度の低減された第1の層106a及び第2の層106bを含む酸化物半導体層をトランジスタに用いることで、当該トランジスタの、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタの信頼性を向上させることができる。

10

#### 【0054】

図2(A)は、本発明の一態様の半導体装置に含まれる積層構造の他の一例を示す模式図である。図2(A)に示す積層構造は、図1(A)の積層構造と同様に、ゲート電極層102と、ゲート電極層102上のゲート絶縁層104と、ゲート絶縁層104上の酸化物半導体層116と、酸化物半導体層116上の絶縁層108と、を含み、酸化物半導体層116は、チャネルが形成される第1の層116aと、第1の層116aと絶縁層108との間の第2の層116bと、第1の層116aとゲート絶縁層104との間の第3の層116cと、を含む。

#### 【0055】

図2(A)に含まれる酸化物半導体層116は、チャネルとして機能する第1の層116aとゲート絶縁層104との間に、第3の層116cを含む点で、図1(A)に示した酸化物半導体層106と相違し、その他の構成は、図1(A)と同様とすることができる。例えば、酸化物半導体層116の第1の層116aは、先に示した酸化物半導体層106の第1の層106aについての説明を参照することができ、酸化物半導体層116の第2の層116bは、先に示した酸化物半導体層106の第2の層106bについての説明を参照することができる。

20

#### 【0056】

酸化物半導体層116に含まれる第1の層116a、第2の層116b及び第3の層116cは、それぞれナノ結晶を含む酸化物半導体層である。また、第3の層116cは、第1の層116a及び第2の層116bと同様に、少なくともインジウム及び亜鉛を構成元素として有する金属酸化物を用いることが好ましい。また、第1の層116a乃至第3の層116cの構成元素を同一とし、それぞれの組成を異ならせててもよい。

30

#### 【0057】

第1の層116aがIn-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf)で表記される酸化物半導体層である場合、第3の層116cとしては、第1の層116aと同様にIn-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf)で表記され、第1の層116aよりもインジウムに対するMの原子数比が高い酸化物半導体層とすることが好ましい。すなわち、第3の層116cは、第1の層116aよりも酸素欠損が生じにくい酸化物半導体層である。より具体的には、第3の層116cとして、第1の層116aよりも前述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物半導体層を適用する。

40

#### 【0058】

また、第3の層116c、第1の層116a、及び第2の層116bが、少なくともインジウム、亜鉛およびM(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、第3の層116cをIn:M:Zn=x<sub>3</sub>:y<sub>3</sub>:z<sub>3</sub>[原子数比]、第1の層116aをIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub>[原子数比]、第2の層116bをIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub>[原子数比]とすると、y<sub>3</sub>/x<sub>3</sub>およびy<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも大きくなることが好ましい。y<sub>3</sub>/x<sub>3</sub>およびy<sub>2</sub>/x<sub>2</sub>はy<sub>1</sub>/x<sub>1</sub>よりも1.5倍以上、好ましくは2倍以上、さ

50

らに好ましくは3倍以上とする。このとき、第1の層116aにおいて、 $y_1$ が $x_1$ 以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_1$ が $x_1$ の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_1$ は $x_1$ の3倍未満であることが好ましい。

#### 【0059】

なお、第3の層116cがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。また、第1の層116aがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。また、第2の層116bがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInとMの原子数比率は好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。10

#### 【0060】

なお、第3の層116cと、第2の層116bとは、異なる構成元素を含む層としてもよいし、同じ構成元素を同一の原子数比で、又は異なる原子数比で含む層としてもよい。

#### 【0061】

また、第3の層116c及び第2の層116bは、伝導帯下端のエネルギーが第1の層116aよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。20

#### 【0062】

図2(A)の積層構造のD3-D4におけるバンド構造の模式図を図2(B)に示す。

#### 【0063】

図2(B)に示すように、酸化物半導体層116において第1の層116aがウェル(井戸)となり、チャネル領域が第1の層116aに形成される。なお、酸化物半導体層116は、伝導帯下端のエネルギーが連続的に変化しているため、第3の層116cと第1の層116aと第2の層116bとが連続接合している、ともいえる。30

#### 【0064】

チャネルとして機能する第1の層116aの上層又は下層に設けられる第3の層116c又は第2の層116bはバリア層として機能し、酸化物半導体層116に接する絶縁層(ゲート絶縁層104及び絶縁層108)と、酸化物半導体層116との界面に形成されるトラップ準位の影響が、トランジスタのキャリアの主な経路(キャリアパス)となる第1の層106aへと及ぶことを抑制することができる。

#### 【0065】

例えば、酸化物半導体層に含まれる酸素欠損は、酸化物半導体のエネルギーギャップ内の深いエネルギー位置に存在する局在準位として顕在化する。このような局在準位にキャリアがトラップされることで、トランジスタの信頼性が低下するため、酸化物半導体層に含まれる酸素欠損を低減することが必要となる。図2に示す積層構造においては、第1の層116aと比較して酸素欠損の生じにくい酸化物半導体層である第3の層116c及び第2の層116bを第1の層116aの上下に接して設けることで、チャネルとして機能する第1の層116aにおける酸素欠損を低減することができる。40

#### 【0066】

また、酸化物半導体層116が、構成元素の異なる絶縁層(例えば、酸化シリコン膜を含む下地絶縁層)と接する場合、2層の界面に界面準位が形成され、該界面準位はチャネルを形成することがある。このような場合、しきい値電圧の異なる第2のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。しかしながら、図2に示す積層構造を含むトランジスタにおいては第1の層116a乃至第3の層116c50

はそれぞれ、少なくともインジウム及び亜鉛を含んで構成されるため、チャネルとして機能する第1の層116aの界面に界面準位を形成しにくくなる。よって、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。

#### 【0067】

また、ゲート絶縁層104と酸化物半導体層116との界面にチャネルが形成される場合、該界面で界面散乱が起こり、トランジスタの電界効果移動度が低くなる。しかしながら、本実施の形態の積層構造を含むトランジスタにおいては、チャネルが形成される第1の層116aとゲート絶縁層104との間に、酸化物半導体を含んでなる第3の層116cが設けられており、第3の層116cと第1の層116aとの界面ではキャリアの散乱が起こりにくい。よって、該トランジスタの電界効果移動度を高くすることができる。 10

#### 【0068】

また、第3の層116c及び第2の層116bはそれぞれ、ゲート絶縁層104及び絶縁層108の構成元素が、チャネルが形成される第1の層116aへ混入して、不純物による準位が形成されることを抑制するためのバリア層としても機能する。

#### 【0069】

なお、図2(B)では、第3の層116cの伝導帯下端のエネルギーが、第2の層116bの伝導帯下端のエネルギーよりも真空準位に近い場合を例に示したが、本発明の一態様はこれに限られるものではない。第3の層116c及び第2の層116bは、それぞれが少なくとも第1の層116aの伝導帯下端のエネルギーよりも真空準位に近い伝導帯下端のエネルギーを有していればよく、第3の層116cは第2の層116bの伝導帯下端のエネルギーのよりも真空準位から離れた伝導帯下端のエネルギーを有していてもよいし、両者が同じエネルギーであってもよい。 20

#### 【0070】

また、以上の説明においては、少なくとも第1の層及び第2の層を含む酸化物半導体層がゲート絶縁層を介してゲート電極層上に設けられたボトムゲート構造について述べたが、本発明の一態様はこれに限られるものではない。

#### 【0071】

図3(A)に、本発明の一態様の半導体装置に含まれる積層構造の他の一例を示す模式図を示す。図3(A)に示す積層構造は、絶縁層108と、絶縁層108上の酸化物半導体層116と、酸化物半導体層116上のゲート絶縁層104と、ゲート絶縁層104上のゲート電極層102と、を含み、酸化物半導体層116は、チャネルが形成される第1の層116aと、第1の層116aと絶縁層108との間の第2の層116bと、第1の層116aとゲート絶縁層104との間の第3の層116cと、を含む。 30

#### 【0072】

また、図3(A)の積層構造のD5-D6におけるバンド構造の一部を図3(B)に模式的に図示する。

#### 【0073】

図3に示す積層構造は、図2に示す積層構造の積層順を逆としてトップゲート構造とした場合を例に示している。各々の層の構成は先の説明と同様とすることができる。図3に示すトップゲート構造の詳細は、図2についての説明を参照することができ、同様の効果を奏することが可能である。 40

#### 【0074】

なお、図3においては、第1の層116aの上下に重なる第2の層116b及び第3の層116cがそれぞれ設けられたトップゲート型の構造を示したが、本発明の一態様はこれに限られない。例えば、第1の層116a上に重なる酸化物半導体層を設けて2層とし、その2層の酸化物半導体層上方にゲート電極層を有するトップゲート型の構造に適用してもよい。

#### 【0075】

以上示したように、本実施の形態の積層構造を含むトランジスタは、酸化物半導体層においてチャネルが形成される第1の層と絶縁層との間に、第2の層を有することで、酸化物 50

半導体層の界面とチャネルを遠ざけることができるため、界面準位のチャネルへの影響を抑制することが可能となる。

#### 【0076】

また、第1の層116a乃至第3の層116cは、非晶質酸化物半導体と比較して欠陥準位密度の低減されたナノ結晶酸化物半導体で構成される。欠陥準位密度の低減された第1の層乃至第3の層を含む酸化物半導体層をトランジスタに用いることで、当該トランジスタの、電気特性の変動を低減し、信頼性を向上させることができる。

#### 【0077】

##### (参考例)

本参考例では、本実施の形態の酸化物半導体層に含まれるナノ結晶について、ナノビーム電子線回折パターンを用いて説明する。

#### 【0078】

酸化物半導体層の断面方向のナノビーム電子線回折パターン 本参考例で用いる試料1の作製方法を以下に示す。試料1では、第1の層に相当する酸化物半導体層の一例として、In-Ga-Zn系酸化物膜を石英ガラス基板上に膜厚50nmで成膜した。その成膜条件は、In:Ga:Zn = 1:1:1(原子数比)である酸化物ターゲットを用いて、酸素雰囲気下(流量45sccm)、圧力0.4Pa、直流(DC)電源0.5kW、基板温度を室温とした。また、酸化物半導体層を成膜後、450で窒素雰囲気下にて1時間の第1の加熱処理、及び、450で窒素及び酸素雰囲気下にて1時間の第2の加熱処理を行った。

10

20

#### 【0079】

第2の加熱処理後の酸化物半導体層を、Arイオンを用いたイオンミリング法によって50nm程度(40nm±10nm)に薄片化した。はじめに、薄片化の補強のために酸化物半導体層が成膜された石英ガラス基板をダミー基板と貼り合わせた後、切断及び研磨によって、厚さ約50μmまで薄片化した。その後、図5に示すように、酸化物半導体層204が設けられた石英ガラス基板200及びダミー基板202に対して、低角度(およそ3°)からアルゴンイオンを照射して、イオンミリングを行い、50nm程度(40nm±10nm)に薄片化された領域210aを形成し、その断面を観察した。

#### 【0080】

第1及び第2の加熱処理後の酸化物半導体層を、50nm程度(40nm±10nm)に薄片化した試料1の断面TEM像を図4(A)に示す。また、図4(A)に示す断面を、ナノビーム電子線回折によって測定した電子線回折パターンを図4(B)~図4(E)に示す。図4(B)は、プローブ径を1nmに収束させた電子線を照射した電子線回折パターンである。図4(C)は、プローブ径を10nmに収束させた電子線を照射した電子線回折パターンである。図4(D)は、プローブ径を20nmに収束させた電子線を照射した電子線回折パターンである。そして、図4(E)は、プローブ径を30nmに収束させた電子線を照射した電子線回折パターンである。

30

#### 【0081】

図4(B)に示すように、試料1の断面方向の電子線回折パターンにおいて、リング状の輝度の高い領域を有し、且つ輝度の高い領域内に複数のスポット(輝点)が観察される。また、図4(C)~図4(E)より、電子線のプローブ径を大きくして測定範囲を広げると、当該複数のスポットは徐々にプロードとなり、リング状の輝度の高い領域の幅も広がっていくことが確認される。

40

#### 【0082】

本参考例の試料1に含まれる結晶部の大きさが10nm以下、又は5nm以下である場合、酸化物半導体層を50nm程度に薄片化した試料1では、奥行き方向の測定範囲が該結晶部の大きさよりも大きくなるため、測定範囲内に複数の結晶部が含まれることがある。そこで、試料1と同じ作製方法で作製した酸化物半導体層を10nm以下、好ましくは5nm以下、より好ましくは3nm以下に薄片化した領域を試料2とし、その断面をナノビーム電子線回折によって観察した。

50

**【0083】**

A<sub>r</sub>イオンを用いてイオンミリングを行い、図5に示すように、10nm以下、例えば5~10nmに薄片化された領域210bを形成し、その断面を観察した。

**【0084】**

図6(A)~図6(D)に、10nm以下に薄片化した試料2の任意の4点を、プローブ径を1nmに収束させた電子線を用いて測定したナノビーム電子線回折パターンを示す。

**【0085】**

図6(A)及び図6(B)では、特定の面に配向した結晶状態を示す規則性を有するスポットが観察される。ここから、本実施の形態に係る酸化物半導体層は、確かに結晶部を有していることがわかる。一方で、図6(C)及び図6(D)では、リング状の輝度の高い領域内に配置された複数のスポットが観察される。10

**【0086】**

上述したように、ナノ結晶酸化物半導体層に含まれる結晶部の大きさは、例えば、10nm以下、または5nm以下と極微細である。よって、例えば、試料を10nm以下に薄片化し、且つ電子線を1nmに収束して、測定範囲を平面方向及び奥行き方向ともに縮小(例えば、一つの結晶部の大きさよりも小さい領域まで縮小)した場合、測定する領域によつては、特定の面に配向した結晶状態を示す規則性を有するスポットを観察することができる。また、測定する領域に複数の結晶部が含まれると、結晶部を透過した電子線が結晶の大きさよりも大きく広がることで、奥行き方向の結晶のスポットが観測されうる。この場合、ナノビーム電子線回折パターンにおいて複数のスポットが観測されると考えることができる。20

**【0087】**

次に、試料1及び試料2とは組成の異なる酸化物半導体層を、試料3として作製し、ナノビーム電子線を照射して電子線回折パターンを確認した。試料3は、本実施の形態の酸化物半導体層において第2の層又は第3の層に相当する酸化物半導体層の一例である。

**【0088】**

試料3の作製方法を以下に示す。試料3では、In-Ga-Zn系酸化物膜を石英ガラス基板上に膜厚100nmで成膜した。その成膜条件は、In:Ga:Zn=1:3:2(原子数比)である酸化物ターゲットを用いて、酸素及びアルゴン雰囲気下(A<sub>r</sub>流量30sccm、酸素流量15sccm)、圧力0.4Pa、直流(DC)電源0.5kW、基板温度を室温とした。30

**【0089】**

成膜した酸化物半導体層を、50nm程度(40nm±10nm)に薄片化した試料3の断面TEM像を図7に示す。また、図7に示す断面を、ナノビーム電子線回折によって測定した電子線回折パターンを図8(A)、図8(B)、図8(C)、図8(D)、図8(E)及び図8(F)に示す。図8(A)は、プローブ径を1nmに収束させた電子線を照射した電子線回折パターンである。図8(B)は、プローブ径を10nmに収束させた電子線を照射した電子線回折パターンである。図8(C)は、プローブ径を20nmに収束させた電子線を照射した電子線回折パターンである。図8(D)は、プローブ径を30nmに収束させた電子線を照射した電子線回折パターンである。図8(E)は、プローブ径を50nmに収束させた電子線を照射した電子線回折パターンである。そして、図8(F)は、プローブ径を100nmに収束させた電子線を照射した電子線回折パターンである。40

**【0090】**

図8に示すように、試料1と組成の異なる試料3においても、断面方向の電子線回折パターンにおいて、リング状の輝度の高い領域を有し、且つ輝度の高い領域内に複数のスポット(輝点)が観察される。また、図8(A)、図8(B)、図8(C)、図8(D)、図8(E)及び図8(F)より、電子線のプローブ径を大きくして測定範囲を広げると、当該複数のスポットは徐々にブロードとなり、リング状の輝度の高い領域の幅も広がっていくことが確認される。50

**【0091】**

石英ガラス基板におけるナノビーム電子線回折パターン 図9に、石英ガラス基板におけるナノビーム電子線回折パターンを示す。図9の測定条件は、図4(B)及び図8(A)と同様とし、電子線のプローブ径を1nmに収束させた。

**【0092】**

図9より、非晶質構造を有する石英ガラス基板では、特定のスポットに回折されずメインスポットから輝度が連続的に変化するハローパターンが観測される。このように、非晶質構造を有する膜においては、極微小な領域の電子線回折を行ったとしても、本実施の形態の酸化物半導体層で観察されるような円周状に配置された複数のスポットが観察されない。従って、本参考例の試料1乃至試料3で観察される円周状に配置された複数のスポットは、本参考例の酸化物半導体層に特有のものであることが確認される。10

**【0093】**

酸化物半導体層の断面方向及び平面方向のナノビーム電子線回折パターン 次いで、成膜した酸化物半導体層について、断面方向及び平面方向からそれぞれ電子線を照射した電子線回折パターンを比較した。比較に用いた試料4の作製方法を以下に示す。

**【0094】**

試料4では、In-Ga-Zn系酸化物膜を石英ガラス基板上に膜厚50nmで成膜した。その成膜条件は、In:Ga:Zn = 1:1:1(原子数比)である酸化物ターゲットを用いて、酸素雰囲気下(流量45sccm)、圧力0.4Pa、直流(DC)電源0.5kW、基板温度を室温とした。20

**【0095】**

成膜した酸化物半導体層に対して平面方向から電子線を照射したナノビーム電子線回折パターンを図10(A)に示す。また、酸化物半導体層を50nm程度に薄片化した後、断面方向に電子線を照射したナノビーム電子線回折パターンを図10(B)に示す。図10(A)及び図10(B)は、ともにプローブ径を1nmに収束させた電子線を照射した電子線回折パターンである。

**【0096】**

図10(A)及び図10(B)に示すように、平面方向の電子線回折パターンにおいても、断面方向の電子線回折パターンと同様にリング状の輝度の高い領域を有し、且つ輝度の高い領域内に複数のスポット(輝点)が観察された。したがって、本参考例の試料4では、膜中の断面方向または平面方向に偏ることなく、略一様に結晶部を含むことが確認された。30

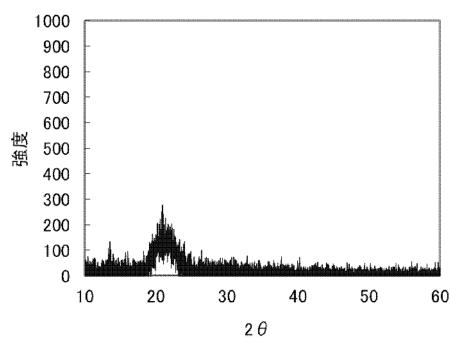

**【0097】**

X線回折による分析 次いで、石英ガラス基板上に酸化物半導体層が設けられた試料5をX線回折(XRD:X-Ray Diffraction)を用いて分析した。図11にout-of-plane法を用いてXRDスペクトルを測定した結果を示す。なお、試料5の作製方法は、上述の試料4と同様とした。

**【0098】**

図11において、縦軸はX線回折強度(任意単位)であり、横軸は回折角 $2\theta$ (deg.)である。なお、XRDスペクトルの測定は、Bruker AXS社製X線回折装置D-8 ADVANCEを用いた。40

**【0099】**

図11に示すように、 $2\theta = 20 \sim 23^\circ$ 近傍に石英に起因するピークが観察されるものの、酸化物半導体層に含まれる結晶部に起因するピークは確認できない。したがって、図11の結果からも、本参考例の酸化物半導体層に含まれる結晶部は、極微細な結晶部であることが示唆される。

**【0100】**

以上示したように、本実施の形態に係る酸化物半導体層に含まれる結晶部の大きさは、例えば、10nm以下、または5nm以下であることが推測される。本実施の形態に係る酸化物半導体層は、例えば、1nm以上10nm以下の結晶部(ナノ結晶(nano

c r y s t a l ) ) を含む酸化物半導体層である。

**【 0 1 0 1 】**

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【 0 1 0 2 】**

( 実施の形態 2 )

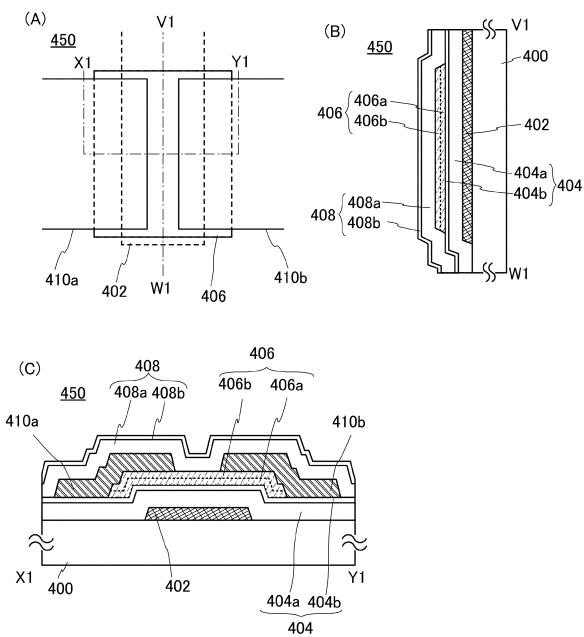

本実施の形態では、実施の形態 1 で示した積層構造を有する半導体装置について、図 1 2 乃至図 1 7 を参照して説明する。

**【 0 1 0 3 】**

<トランジスタの構成例 1 >

10

図 1 2 に半導体装置の構成例を示す。図 1 2 では、半導体装置の一例として、ボトムゲート構造のトランジスタを図示している。図 1 2 ( A ) は、トランジスタ 4 5 0 の平面図であり、図 1 2 ( B ) は、図 1 2 ( A ) の V 1 - W 1 における断面図であり、図 1 2 ( C ) は、図 1 2 ( A ) の X 1 - Y 1 における断面図である。なお、図 1 2 ( A ) では煩雑になることを避けるため、構成要素の一部（例えば、絶縁層 4 0 8 等）を省略して図示している。これは以降の平面図においても同様である。

**【 0 1 0 4 】**

図 1 2 に示すトランジスタ 4 5 0 は、基板 4 0 0 上に設けられたゲート電極層 4 0 2 と、ゲート電極層 4 0 2 上のゲート絶縁層 4 0 4 と、ゲート絶縁層 4 0 4 上に設けられ、ゲート電極層 4 0 2 と互いに重なる酸化物半導体層 4 0 6 と、酸化物半導体層 4 0 6 と電気的に接続するソース電極層 4 1 0 a 及びドレイン電極層 4 1 0 b と、酸化物半導体層 4 0 6 を介してゲート絶縁層 4 0 4 と互いに重なる絶縁層 4 0 8 と、を含む。

20

**【 0 1 0 5 】**

トランジスタ 4 5 0 に含まれる酸化物半導体層 4 0 6 は、チャネルが形成される第 1 の層 4 0 6 a と、第 1 の層 4 0 6 a と絶縁層 4 0 8 との間の第 2 の層 4 0 6 b との積層構造を含む。第 1 の層 4 0 6 a 及び第 2 の層 4 0 6 b はそれぞれナノ結晶を含む酸化物半導体層であり、図 1 で示した第 1 の層 1 0 6 a 及び第 2 の層 1 0 6 b にそれぞれ相当する。

**【 0 1 0 6 】**

上述したように、第 1 の層 4 0 6 a 及び第 2 の層 4 0 6 b は、それぞれインジウム及び亜鉛を構成元素として含み、且つ、第 2 の層 4 0 6 b の伝導帯下端のエネルギーは、第 1 の層 4 0 6 a の伝導帯下端のエネルギーよりも 0 . 0 5 e V 以上 2 e V 以下の範囲で真空準位に近い。

30

**【 0 1 0 7 】**

第 1 の層 4 0 6 a 及び第 2 の層 4 0 6 b がナノ結晶を含むことで、酸化物半導体層 4 0 6 は非晶質酸化物半導体と比較して欠陥準位密度の低減された酸化物半導体層とすることができます。また、酸化物半導体層 4 0 6 においてチャネルが形成される第 1 の層 4 0 6 a と絶縁層 4 0 8 との間に第 2 の層 4 0 6 b を含むことで、酸化物半導体層 4 0 6 と絶縁層 4 0 8 との間に形成されうるトラップ準位が、チャネルに与える影響を低減又は抑制することが可能となる。従って、トランジスタ 4 5 0 の電気特性を安定化させることができる。

**【 0 1 0 8 】**

40

また、酸化物半導体層 4 0 6 においてチャネルが形成される第 1 の層 4 0 6 a は、水素が可能な限り低減されていることが好ましい。具体的には、第 1 の層 4 0 6 a において、二次イオン質量分析法 ( S I M S : Secondary Ion Mass Spectrometry ) により得られる水素濃度を、 $2 \times 1 0^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 1 0^{19}$  atoms / cm<sup>3</sup> 以下、 $1 \times 1 0^{19}$  atoms / cm<sup>3</sup> 以下、 $5 \times 1 0^{18}$  atoms / cm<sup>3</sup> 以下、 $1 \times 1 0^{18}$  atoms / cm<sup>3</sup> 以下、 $5 \times 1 0^{17}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $1 \times 1 0^{16}$  atoms / cm<sup>3</sup> 以下とする。

**【 0 1 0 9 】**

トランジスタ 4 5 0 においてゲート絶縁層 4 0 4 は、絶縁層 4 0 4 a 及び絶縁層 4 0 4 b

50

の積層構造を有する。絶縁層404a及び絶縁層404bはそれぞれ、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化アルミニウム、窒化酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物などを用いることができる。なお、本実施の形態では、絶縁層404a及び絶縁層404bの積層構造でなるゲート絶縁層404を設ける場合を例に示すが、これに限られず、単層構造のゲート絶縁層としてもよいし、三層以上の積層構造を含むゲート絶縁層としてもよい。

#### 【0110】

ゲート絶縁層404において、ゲート電極層402に接する絶縁層404aとして、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等の窒化物絶縁膜を形成することで、ゲート電極層402を構成する金属元素の拡散を防ぐことができるため好ましい。

10

#### 【0111】

また、絶縁層404aとして、窒化シリコン膜又は窒化酸化シリコン膜を用いることがより好ましい。窒化シリコン膜又は窒化酸化シリコン膜は、酸化シリコン膜と比較して比誘電率が高く、同等の静電容量を得るのに必要な膜厚が大きいため、ゲート絶縁層を物理的に厚膜化することができる。例えば、絶縁層404aの膜厚を300nm以上400nm以下とすることができる。よって、トランジスタ450の絶縁耐圧の低下の抑制又は絶縁耐圧を向上させることができ、半導体装置の静電破壊を抑制することができる。

#### 【0112】

また、絶縁層404aとして好適に用いることのできる窒化物絶縁膜は、緻密な膜を形成可能でゲート電極層402の金属元素の拡散を防ぐことができる一方で、欠陥準位密度や内部応力が大きいので、酸化物半導体層406との界面を形成するとしきい値電圧の変動を引き起こす恐れがある。よって、絶縁層404aとして窒化物絶縁膜を形成する場合には、酸化物半導体層406との間に絶縁層404bとして酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム等の酸化物絶縁膜を設けることが好ましい。酸化物半導体層406と窒化物絶縁膜でなる絶縁層404aとの間に酸化物絶縁膜でなる絶縁層404bを形成することで、ゲート絶縁層404と酸化物半導体層406の界面を安定化することが可能となる。

20

#### 【0113】

絶縁層404bの膜厚は、例えば25nm以上150nm以下とすることができる。なお、酸化物半導体層406と接する絶縁層404bに酸化物絶縁膜を用いることで、酸化物半導体層406に酸素を供給することも可能である。酸化物半導体中に含まれる酸素欠損は、酸化物半導体をn型化し、電気特性の変動を引き起こすため、絶縁層404bから酸素を供給し、酸素欠損を補填することは、信頼性の向上に有効である。

30

#### 【0114】

または、ゲート絶縁層404として、ハフニウムシリケート(HfSiO<sub>x</sub>)、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、窒素が添加されたハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでトランジスタのゲートリーキを低減できる。

40

#### 【0115】

また、トランジスタ450において、酸化物半導体層406の上層に接して設けられる絶縁層408としては、酸素を含む絶縁層(酸化物絶縁層)、換言すると酸素を放出することが可能な絶縁層を含むことが好ましい。絶縁層408から酸素を放出することで、酸化物半導体層406(より具体的にはチャネルが形成される第1の層406a)へ酸素を供給し、酸化物半導体層406の膜中又は界面の酸素欠損を補填することが可能となるためである。なお、酸素を放出することが可能な絶縁層としては、酸化シリコン層、酸化窒化シリコン層、又は酸化アルミニウム層を適用することができる。

#### 【0116】

本実施の形態では、絶縁層408を、絶縁層408a及び絶縁層408bの積層構造とし

50

、絶縁層408aとして、酸化物半導体の酸素欠損を低減することが可能な酸化物絶縁膜を用い、絶縁層408bとして外部からの不純物が酸化物半導体層406に移動するのを防ぐことが可能な窒化物絶縁膜を用いている。以下に、絶縁層408aとして好適に用いることが可能な酸化物絶縁膜、及び絶縁層408bとして好適に用いることが可能な窒化物絶縁膜の詳細について説明する。

#### 【0117】

酸化物絶縁膜は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、TDS分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上である酸化物絶縁膜である。なお、上記TDS分析時における基板温度としては100以上700以下、または100以上500以下の範囲が好ましい。10

#### 【0118】

絶縁層408aとして用いることが可能な酸化物絶縁膜としては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。

#### 【0119】

絶縁層408bとして用いることが可能な窒化物絶縁膜は、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する。絶縁膜124として窒化物絶縁膜を設けることで、半導体層110からの酸素の外部への拡散と、外部から半導体層110への水素、水等の侵入を防ぐことができる。窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する窒化物絶縁膜の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。20

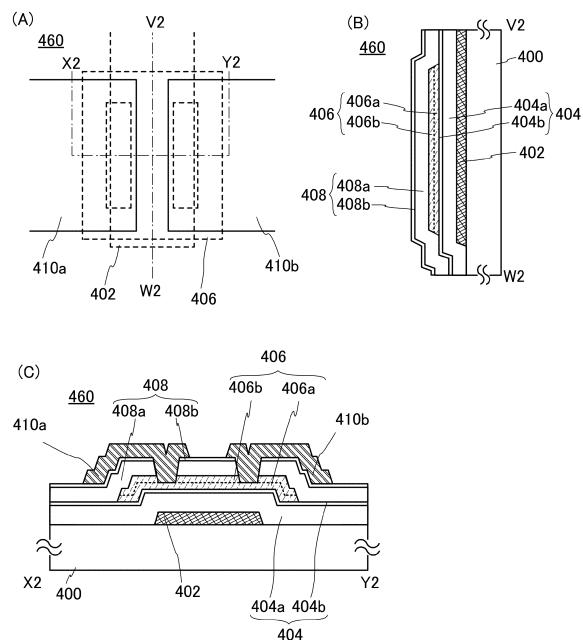

#### 【0120】

<トランジスタの構成例2>

図13に、トランジスタ450の変形例としてトランジスタ460を図示する。図13(A)は、トランジスタ460の平面図であり、図13(B)は、図13(A)のV2-W2における断面図であり、図13(C)は、図13(A)のX2-Y2における断面図である。30

#### 【0121】

図13に示すトランジスタ460は、基板400上に設けられたゲート電極層402と、ゲート電極層402上のゲート絶縁層404と、ゲート絶縁層404上に設けられ、ゲート電極層402と互いに重なる酸化物半導体層406と、酸化物半導体層を介してゲート絶縁層404と互いに重なる絶縁層408と、絶縁層408に設けられたコンタクトホールにおいて酸化物半導体層406と電気的に接続するソース電極層410a及びドレイン電極層410bとを含む。トランジスタ460において、ゲート絶縁層404は、絶縁層404a及び絶縁層404bを含む。また、絶縁層408は、絶縁層408a及び絶縁層408bを含む。40

#### 【0122】

図13に示すトランジスタ460は、ソース電極層410a及びドレイン電極層410bと、絶縁層408との積層順が、図12に示すトランジスタ450と相違する。すなわち、トランジスタ450では、島状の酸化物半導体層406を覆うようにソース電極層410a及びドレイン電極層410bとなる導電膜を形成後、該導電膜を加工してソース電極層410a及びドレイン電極層410bを形成し、ソース電極層410a及びドレイン電極層410bから露出した酸化物半導体層406の一部を覆うようにソース電極層41050

a 及びドレイン電極層 410b 上に絶縁層 408 を形成する。従って、トランジスタ 450 では島状の酸化物半導体層 406 の側面及び上面の一部に接するように、ソース電極層 410a 及びドレイン電極層 410b が形成される。

#### 【0123】

一方、トランジスタ 460 では、島状の酸化物半導体層 406 を覆うように絶縁層 408 を形成し、絶縁層 408 にコンタクトホールを形成した後、該コンタクトホールにおいて酸化物半導体層 406 と接続するソース電極層 410a 及びドレイン電極層 410b を形成する。従って、トランジスタ 460 では、酸化物半導体層 406 の上面の一部に接するようにソース電極層 410a 及びドレイン電極層 410b が形成される。但し、絶縁層 408 へのコンタクトホールの形成条件によっては、酸化物半導体層 406 の一部が同時にエッチングされる場合がある。例えば、第 2 の層 406b と絶縁層 408 にコンタクトホールが形成され、ソース電極層 410a 及びドレイン電極層 410b と第 1 の層 406a とが接する場合がある。10

#### 【0124】

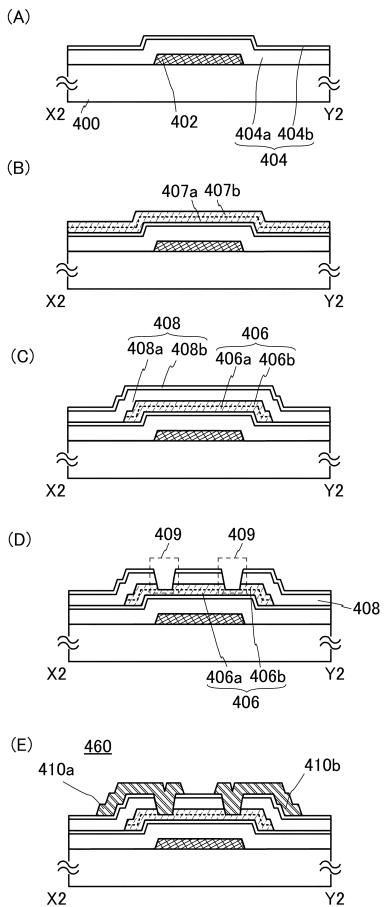

トランジスタ 460 に含まれるその他の構成は、トランジスタ 450 と同様の構成とすることができる。

#### 【0125】

##### <トランジスタの作製方法 1>

以下に、トランジスタ 460 の作製方法の一例について、図 14 を参照して説明する。

#### 【0126】

まず、基板 400 上に、ゲート電極層 402（これと同じ層で形成される配線を含む）を形成し、ゲート電極層 402 上にゲート絶縁層 404 を形成する（図 14（A）参照）。

#### 【0127】

基板 400 の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板 400 として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 400 として用いてもよい。なお、基板 400 として、ガラス基板を用いる場合、第 6 世代（1500 mm × 1850 mm）、第 7 世代（1870 mm × 2200 mm）、第 8 世代（2200 mm × 2400 mm）、第 9 世代（2400 mm × 2800 mm）、第 10 世代（2950 mm × 3400 mm）等の大面積基板を用いることで、大型の表示装置を作製することができる。30

#### 【0128】

また、基板 400 として、可撓性基板を用い、可撓性基板上に直接、トランジスタ 460 を形成してもよい。本発明の一態様の半導体装置に含まれる酸化物半導体層は、室温で成膜することが可能であるため、耐熱性の低い可撓性基板であっても好適に用いることが可能である。または、基板 400 とトランジスタ 460 との間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板 400 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 460 は耐熱性の劣る基板や可撓性の基板にも転載できる。40

#### 【0129】

ゲート電極層 402 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極層 402 としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイド等のシリサイド膜を用いてもよい。ゲート電極層 402 は単層構造としてもよいし、積層構造としてもよい。ゲート電極層 402 はテーパ形状としてもよく、例えばテーパ角を 15° 以上 70° 以下とすればよい。ここで、テーパ角とは、テーパ形状を有する層の側面と、当該層の底面との間の角度を指す。50

## 【0130】

また、ゲート電極層402の材料は、酸化インジウム酸化スズ、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウムスズ酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウムスズ酸化物等の導電性材料を適用することもできる。

## 【0131】

または、ゲート電極層402の材料として、窒素を含むIn-Ga-Zn系酸化物、窒素を含むIn-Sn系酸化物、窒素を含むIn-Ga系酸化物、窒素を含むIn-Zn系酸化物、窒素を含むSn系酸化物、窒素を含むIn系酸化物、金属窒化物膜（窒化インジウム膜、窒化亜鉛膜、窒化タンタル膜、窒化タングステン膜など）を用いてもよい。これらの材料は、5電子ボルト以上の仕事関数を有するため、これらの材料を用いてゲート電極層402を形成することでトランジスタのしきい値電圧をプラスにすることができ、ノーマリオフのスイッチングトランジスタを実現できる。10

## 【0132】

ゲート絶縁層404としては、プラズマCVD法、スパッタリング法等により、酸化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、窒化シリコン層、酸化アルミニウム層、酸化ハフニウム層、酸化イットリウム層、酸化ジルコニウム層、酸化ガリウム層、酸化タンタル層、酸化マグネシウム層、酸化ランタン層、酸化セリウム層、及び酸化ネオジム層を一種以上含む絶縁層を用いることができる。なお、ゲート絶縁層404は、上述の絶縁層の材料を用いた積層構造としてもよい。20

## 【0133】

なお、後に形成される酸化物半導体層406と接する絶縁層404bは、酸化物絶縁層であることが好ましく、化学量論的組成よりも過剰に酸素を含有する領域（酸素過剰領域）を有することがより好ましい。絶縁層404bに酸素過剰領域を形成するには、例えば酸素雰囲気下にて絶縁層404bを形成すればよい。又は、成膜後の絶縁層404bに酸素を導入して酸素過剰領域を形成してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

## 【0134】

本実施の形態では、絶縁層404aとして、窒化シリコン膜を形成し、絶縁層404bとして酸化窒化シリコン膜を形成する。30

## 【0135】

次いで、ゲート絶縁層404上に第1の層406aとなる第1の酸化物半導体膜407aと、第2の層406bとなる第2の酸化物半導体膜407bとを積層する。

## 【0136】

本実施の形態において第1の酸化物半導体膜407aには、In-M-Zn酸化物（MはAl、Ti、Ga、Y、Zr、La、Ce、Nd、またはHf）で表記される酸化物半導体を用いる。また、InとMの原子数比率は、好ましくは、Inが50atomic%未満、Mが50atomic%以上、さらに好ましくは、Inが25atomic%未満、Mが75atomic%以上とする。40

## 【0137】

また、本実施の形態において第2の酸化物半導体膜407bには、In-M-Zn酸化物（MはAl、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属）で表記され、第1の酸化物半導体膜407aよりもインジウムに対するMの原子数比が高い酸化物半導体を適用する。具体的には、第1の酸化物半導体膜407aよりも元素Mを1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物半導体を用いることが好ましい。元素Mはインジウムよりも酸素と強く結合するため、酸素欠損が生じることを抑制する機能を有する。よって、第2の酸化物半導体膜407bは第1の酸化物半導体膜407aよりも酸素欠損が生じにくい酸化物半導体膜とすることができます。50

## 【0138】

また、第2の酸化物半導体膜407bとして、伝導帯下端のエネルギーが第1の酸化物半導体膜407aよりも真空準位に近い酸化物半導体を適用する。例えば、第2の酸化物半導体膜407bの伝導帯下端のエネルギーと、第1の酸化物半導体膜407aの伝導帯下端のエネルギーとの差が、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上、且つ2eV以下、1eV以下、0.5eV以下、または0.4eV以下とすることが好ましい。

## 【0139】

例えば、第2の酸化物半導体膜407bにおいて、InとMの原子数比率は、好ましくは、Inが25atomic%以上、Mが75atomic%未満、さらに好ましくは、Inが34atomic%以上、Mが66atomic%未満とする。10

## 【0140】

また、例えば、第1の酸化物半導体膜407aとしてIn:Ga:Zn = 1:1:1または3:1:2の原子数比のIn-Ga-Zn酸化物を用いることができる。また、第2の酸化物半導体膜407bとしてIn:Ga:Zn = 1:3:2、1:3:4、1:3:6、1:6:4、または1:9:6の原子数比のIn-Ga-Zn酸化物を用いることができる。なお、第1の酸化物半導体膜407a、及び第2の酸化物半導体膜407bの原子数比はそれぞれ、上記の原子数比のプラスマイナス20%の変動を含む。

## 【0141】

なお、これらに限られず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、第1の酸化物半導体膜407a、第2の酸化物半導体膜407bのキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。20

## 【0142】

第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bの成膜方法は、スパッタリング法、MBE (Molecular Beam Epitaxy) 法、CVD法、パルスレーザ堆積法、ALD (Atomic Layer Deposition) 法等を適宜用いることができる。

## 【0143】

なお、成膜後の酸化物半導体膜中の酸素欠損を低減するために、酸素を含む雰囲気下にて第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを形成することが好ましい。また、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bの界面に不純物が混入しないように、第1の酸化物半導体膜407aを成膜後、大気開放することなく連続的に第2の酸化物半導体膜407bを成膜することが好ましい。30

## 【0144】

例えば、多結晶を含有するスパッタリングターゲットを用いて、スパッタリング法によって第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを形成することで、ナノ結晶を含む第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを形成することができる。40

## 【0145】

また、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを成膜する際、できる限り膜中に含まれる水素濃度を低減させることが好ましい。水素濃度を低減させるには、例えば、スパッタリング法を用いて成膜を行う場合には、成膜室内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下、より好ましくは-120以下にまで高純度化したガスを用いることで酸化物半導体膜208に水分等が取り込まれることを可能な限り防ぐことができる。

## 【0146】

また、成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオ50

ポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプは、例えば、水素分子、水(H<sub>2</sub>O)など水素原子を含む化合物、炭素原子を含む化合物、等の排気能力が高いため、クライオポンプを用いて排気した成膜室で成膜した膜中に含まれる不純物の濃度を低減できる。

#### 【0147】

また、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bをスパッタリング法で成膜する場合、成膜に用いる金属酸化物ターゲットの相対密度(充填率)は90%以上100%以下、好ましくは95%以上99.9%以下とする。相対密度の高い金属酸化物ターゲットを用いることにより、成膜される膜を緻密な膜とすることができる。

10

#### 【0148】

なお、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bは、室温下にて成膜することが好ましい。第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを室温下にて成膜することで、生産性よくナノ結晶を含有する酸化物半導体膜を形成することが可能となる。

#### 【0149】

次いで、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを所望の領域に加工することで、第1の層406a及び第2の層406bを含む島状の酸化物半導体層406を形成する。なお、酸化物半導体層406への加工の際に、ゲート絶縁層404の一部(第1の層406a及び第2の層406bから露出した領域)がエッチングされ膜厚が減少することがある。

20

#### 【0150】

島状の酸化物半導体層406を形成後、熱処理を行うことが好ましい。熱処理は、250以上650以下、好ましくは300以上400以下、より好ましくは320以上370以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、又は減圧雰囲気で行えばよい。また、熱処理の雰囲気は、不活性ガス雰囲気で熱処理を行った後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。ここでの加熱処理によって、ゲート絶縁層404及び酸化物半導体層406の少なくとも一から水素や水などの不純物を除去することができる。なお、当該熱処理は、第1の酸化物半導体膜407a及び第2の酸化物半導体膜407bを島状に加工する前に行つてもよい。

30

#### 【0151】

次に、酸化物半導体層406上に絶縁層408を形成する(図14(C)参照)。

#### 【0152】

絶縁層408としては、先のゲート絶縁層404と同様の材料を単層で又は積層で用いることができる。

#### 【0153】

本実施の形態では、絶縁層408を酸化物絶縁層でなる絶縁層408a及び窒化物絶縁層でなる絶縁層408bの積層構造とし、絶縁層408aとして酸化窒化シリコン膜、絶縁層408bとして窒化シリコン膜を形成する。なお、絶縁層408aは、化学量論的組成よりも過剰に酸素を含有する領域(酸素過剰領域)を有することがより好ましい。

40

#### 【0154】

絶縁層408aを形成後に熱処理を行うことが好ましい。熱処理によって、絶縁層408aに含まれる酸素の一部を酸化物半導体層406に移動させ、酸化物半導体層406中の酸素欠損を補填することができる。熱処理の条件は、酸化物半導体層406を形成後の熱処理と同様とすることができます。

#### 【0155】

次に、絶縁層408を所望の領域に加工することで、酸化物半導体層406に達するコンタクトホール409を形成する(図14(D)参照)。

#### 【0156】

50

なお、コンタクトホール409は、酸化物半導体層406の一部が露出するように形成する。コンタクトホール409の形成時に、酸化物半導体層406の第2の層406bを少なくとも一部を除去して、該コンタクトホール409と重なる第2の層406bの膜厚を低減することが好ましい。または、コンタクトホール409の形成時に第1の層406aの一部が露出するように第2の層406bにコンタクトホールを形成することが好ましい。

#### 【0157】

第2の層406bの一部を除去、又は第2の層406bにコンタクトホールを形成することで、酸化物半導体層406において、後に形成されるソース電極層410a及びドレイン電極層410bと接する位置の膜厚をその他の膜厚よりも低減することができる。これによって、酸化物半導体層406とソース電極層410a及びドレイン電極層410bとのコンタクト抵抗を低減することができるため好ましい。上述したように、第2の層406bは、第1の層406aと比較して、インジウムに対して元素M(Mは、Al、Ga、Ge、Y、Zr、Sn、La、Ce又はHf)の原子数比が高い領域である。インジウムに対する元素Mの原子数比が高い程、酸化物半導体層のエネルギーギャップ(バンドギャップ)が大きくなるため、第2の層406bは、第1の層406aよりも絶縁性の高い酸化物膜である。従って、後に形成されるソース電極層410a及びドレイン電極層410bと、酸化物半導体層406とのコンタクト抵抗を低減するためには、第2の層406bの膜厚を低減又は第2の層406bを一部除去することは有効である。

#### 【0158】

コンタクトホール409の形成方法としては、例えば、ドライエッチング法を用いることができる。ただし、コンタクトホール409の形成方法としては、これに限定されず、ウェットエッチング法、またはドライエッチング法とウェットエッチング法を組み合わせた形成方法としてもよい。

#### 【0159】

次いで、コンタクトホール409及び絶縁層408上に導電膜を形成し、これを加工することで、ソース電極層410a及びドレイン電極層410bを形成する(図14(E)参照)。

#### 【0160】

ソース電極層410a及びドレイン電極層410bとなる導電膜の材料としては、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタンクスチタンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いることができる。例えば、アルミニウム膜上にチタン膜を積層する二層構造、タンクスチタン膜上にチタン膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。また、導電膜は、例えば、スパッタリング法を用いて形成することができる。

#### 【0161】

以上の工程によって、チャネル保護型のトランジスタ460を形成することができる。

#### 【0162】

<半導体装置の構成例3>

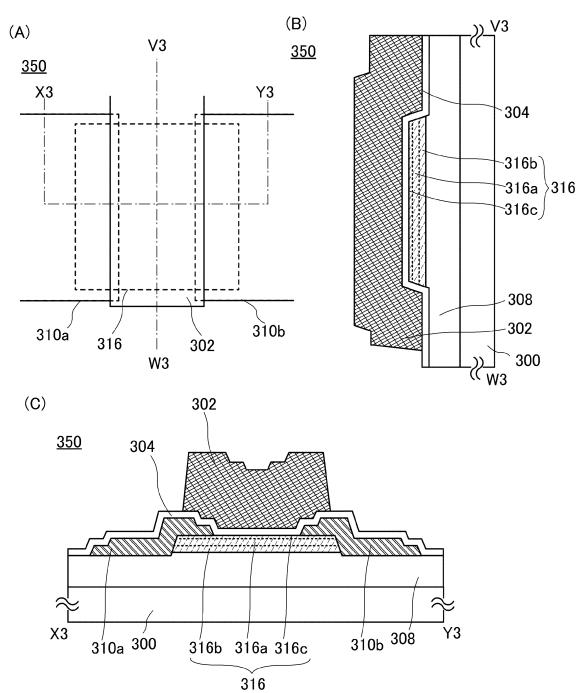

図15にトランジスタ350の構成例を示す。トランジスタ350は、実施の形態1で図3を用いて説明した積層構造を有するトップゲート構造のトランジスタである。図15(A)は、トランジスタ350の平面図であり、図15(B)は図15(A)のV3-W3における断面図であり、図15(C)は図15(A)のX3-Y3における断面図である。

10

20

30

40

50

**【 0 1 6 3 】**

なお、トランジスタ350の構成要素は、積層順が異なる以外は多くの部分で先に示したトップゲート構造のトランジスタと共に通している。よって、詳細な構成については、先の説明を参照することが可能であるため記載を省略することがある。

**【 0 1 6 4 】**

図15に示すトランジスタ350は、基板300上に設けられた絶縁層308上に、島状の酸化物半導体層316と、酸化物半導体層316と電気的に接続するソース電極層310a及びドレイン電極層310bと、ソース電極層310a及びドレイン電極層310bから露出した酸化物半導体層316の一部と接するゲート絶縁層304と、ゲート絶縁層304を介して酸化物半導体層316と互いに重なるゲート電極層302と、を含む。

10

**【 0 1 6 5 】**

トランジスタ350に含まれる酸化物半導体層316は、チャネルが形成される第1の層316aと、第1の層316aと絶縁層308との間の第2の層316bと、第1の層316aとゲート絶縁層304との間の第3の層316cと、の積層構造を含む。第1の層316a、第2の層316b及び第3の層316cはそれぞれナノ結晶を含む酸化物半導体層であり、実施の形態1で示した第1の層106a、第2の層106b及び第3の層106cにそれぞれ相当する。

**【 0 1 6 6 】**

また、第1の層316a、第2の層316b及び第3の層316cは、それぞれインジウム及び亜鉛を構成元素として含み、且つ、第2の層316b及び第3の層316cの伝導帯下端のエネルギーは、それぞれ第1の層316aの伝導帯下端のエネルギーよりも0.05eV以上2eV以下の範囲で真空準位に近い。

20

**【 0 1 6 7 】**

トランジスタ350において、下地絶縁層として機能する絶縁層308は、基板300からの不純物の拡散を防止する役割を有する他、第2の層316b及び/又は第1の層316aに酸素を供給する役割を担う。よって、絶縁層308には酸素を含む絶縁層を用いるものとする。詳細は、絶縁層408aと同様の構成とすることができます。絶縁層308から酸素が供給されることで、酸化物半導体層316における酸素欠損を低減することができる。なお、基板300に他の半導体素子が形成されている場合、絶縁層308は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるようにC M P ( C h e m i c a l M e c h a n i c a l P o l i s h i n g ) 法等で平坦化処理を行うことが好ましい。

30

**【 0 1 6 8 】**

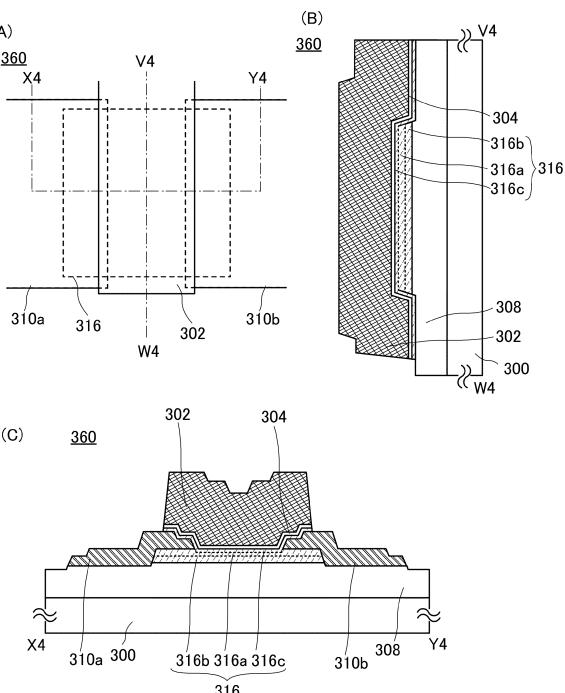

<半導体装置の構成例4>

図16にトランジスタ360の構成例を示す。トランジスタ360は、トランジスタ350とは一部が異なる構成を有するトップゲート構造のトランジスタである。図16(A)は、トランジスタ360の平面図であり、図16(B)は図16(A)のV4-W4における断面図であり、図16(C)は図16(A)のX4-Y4における断面図である。

**【 0 1 6 9 】**

図16に示すトランジスタ360は、基板300上に設けられた絶縁層308上に、島状の酸化物半導体層316と、酸化物半導体層316と電気的に接続するソース電極層310a及びドレイン電極層310bと、酸化物半導体層316と接するゲート絶縁層304と、ゲート絶縁層304を介して酸化物半導体層316と互いに重なるゲート電極層302と、を含む。

40

**【 0 1 7 0 】**

酸化物半導体層316は、第1の層316a、第2の層316b及び第3の層316cを含む。第2の層316bは絶縁層308上に接して設けられ、第1の層316aは第2の層316b上に接して設けられる。ソース電極層310a及びドレイン電極層310bは、島状の第2の層316b及び第1の層316aの一側面及び第1の層316aの上面の一部を覆うように設けられる。また、第3の層316cは、ソース電極層310a及びド

50

レイン電極層 310b 上に位置し、ソース電極層 310a 及びドレン電極層 310b から露出した第 1 の層 316a の一部と接している。

**【0171】**

図 16 (B) に示すように、トランジスタ 360 は W 長方向の断面において、島状の第 2 の層 316b 及び第 1 の層 316a の側面を第 3 の層 316c が覆い、さらに第 3 の層 316c の側面をゲート絶縁層 304 によって覆う構成を有する。当該構成とすることで、酸化物半導体層 316 の W 長方向端部において生じうる寄生チャネルの影響を低減することができる。

**【0172】**

また、図 16 (A) 及び図 16 (C) に示すように、第 3 の層 316c 及びゲート絶縁層 304 は、ゲート電極層 302 と同一の平面形状を有しており、換言すると、断面図において第 3 の層 316c の上端部は、ゲート絶縁層 304 の下端部と一致し、ゲート絶縁層 304 の上端部は、ゲート電極層 302 の下端部と一致する。このような形状は、ゲート電極層 302 をマスクとして（または、ゲート電極層 302 を形成したマスクと同じマスクを用いて）、第 3 の層 316c 及びゲート絶縁層 304 を加工することで、形成することができる。なお、本明細書等において「同一」又は「一致」の表現は、厳密に同一、又は一致であることを要しない趣旨で用いるものであり、略同一又は略一致を範疇に含む。例えば、同一のマスクを用いたエッチングによって得られた形状における一致の程度を包含する。

**【0173】**

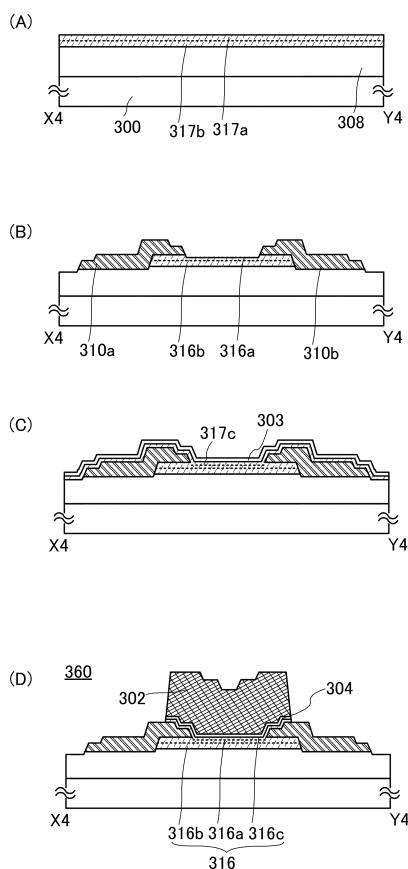

<半導体装置の作製方法 2 >

図 16 に示すトランジスタ 360 の作製方法の一例を図 17 を用いて説明する。

**【0174】**

まず、基板 300 上に、絶縁層 308 及び第 2 の層 316b となる第 2 の酸化物半導体膜 317b 及び第 1 の層 316a となる第 1 の酸化物半導体膜 317a を形成する（図 17 (A) 参照）。

**【0175】**

絶縁層 308 は、単層としても積層としてもよい。但し、少なくとも後に形成される酸化物半導体層 316 と接する領域は、酸素を含む材料で形成する。また、過剰に酸素を含む層とすることが好ましい。

**【0176】**

また、絶縁層 308 は、膜中の水素濃度が低減されていることが好ましい。よって、絶縁層 308 を成膜後、水素の除去を目的とした熱処理（脱水化処理又は脱水素化処理）を行うことが好ましい。なお、熱処理によって絶縁層 308 から酸素が脱離することがある。そのため、脱水化又は脱水素化処理を行った絶縁層 308 に対して酸素を導入する処理を行うことが好ましい。

**【0177】**

第 2 の酸化物半導体膜 317b は、第 2 の酸化物半導体膜 407b と同様の材料及び方法で形成することができる。また、第 1 の酸化物半導体膜 317a は、第 1 の酸化物半導体膜 407a と同様の材料及び方法で形成することができる。

**【0178】**

第 2 の酸化物半導体膜 317b 及び第 1 の酸化物半導体膜 317a を形成後、熱処理を行うことが好ましい。熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、又は減圧雰囲気で行えばよい。また、熱処理の雰囲気は、不活性ガス雰囲気で熱処理を行った後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。

**【0179】**

次いで、第 2 の酸化物半導体膜 317b 及び第 1 の酸化物半導体膜 317a を加工して島状の第 2 の層 316b 及び第 1 の層 316a を形成する。ここでは、第 2 の層 316b 及び第 1 の層 316a は同一のマスクを用いたエッチングによって加工することができる。

10

20

30

40

50

よって、第2の層316bと第1の層316aの平面形状は同一であり、第2の層316bの上端部と第1の層316aの下端部とは一致している。

#### 【0180】

なお、第2の層316b及び第1の層316aへの加工の際に、第2の酸化物半導体膜317bのオーバーエッティングによって絶縁層308の一部（島状の第2の層316bから露出した領域）がエッティングされ膜厚が減少することがある。

#### 【0181】

次に、第1の層316a上に導電膜を形成し、該導電膜を加工してソース電極層310a及びドレイン電極層310bを形成する（図17（B）参照）。

#### 【0182】

なお、本実施の形態において、ソース電極層310a及びドレイン電極層310bの端部は階段状に複数の段を設けた形状とする。当該端部の加工は、アッシングによってレジストマスクを後退させる工程とエッティングの工程を交互に複数回行うことで形成することができる。

#### 【0183】

なお、本実施の形態においては、ソース電極層310a及びドレイン電極層310bの端部に二つの段を設けた形状を例示しているが、段数は三つ以上であってもよいし、加工途中にレジストのアッシングを行わずに段数を1つとしてもよい。ソース電極層310a及びドレイン電極層310bの膜厚が厚いほど、当該段数を増やすことが好ましい。なお、ソース電極層310a及びドレイン電極層310bの端部は対称的でなくともよい。また、各階段形状の上面と断面との間に任意の曲率半径を有する曲面が形成されていてよい。

#### 【0184】

ソース電極層310a及びドレイン電極層310bを上記のような複数の段を設けた形状とすることで、それらの上方に形成される膜、具体的には、第3の層316c、ゲート絶縁層304などの被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。

#### 【0185】

なお、ソース電極層310a及びドレイン電極層310bの加工の際に、導電膜のオーバーエッティングによって、絶縁層308の一部及び第1の層316aの一部（ソース電極層310a及びドレイン電極層310bから露出した領域）がエッティングされ膜厚が減少することがある。

#### 【0186】

なお、ソース電極層310a及びドレイン電極層310bとなる導電膜が残渣物として第1の層316a上に残存すると、該残渣物が第1の層316a中又は界面において不純物準位を形成することがある。または、該残渣物によって、第1の層316aから酸素が引き抜かれてしまい、酸素欠損が形成されることがある。

#### 【0187】

よって、ソース電極層310a及びドレイン電極層310bを形成後、第1の層316a表面に該残渣物除去処理を施してもよい。残渣物除去処理は、エッティング（例えば、ウェットエッティング）による処理、もしくは、酸素又は一酸化二窒素を用いたプラズマ処理によって行うことができる。当該残渣物除去処理によって、ソース電極層310a及びドレイン電極層310b間に露出した第1の層316aの一部の膜厚が1nm以上3nm以下程度減少することがある。

#### 【0188】

次いで、ソース電極層310a及びドレイン電極層310b上に第3の層316cとなる第3の酸化物半導体膜317c及びゲート絶縁層304となるゲート絶縁膜303を積層して形成する（図17（C）参照）。

#### 【0189】

なお、第3の酸化物半導体膜317cとゲート絶縁膜303とを大気に開放せずに連続的

10

20

30

40

50

に形成すると、第3の酸化物半導体膜317c表面に水素や水分などの不純物が吸着することを防止することができるため、好ましい。

**【0190】**

第3の酸化物半導体膜317cは、第2の酸化物半導体膜317bと同様の材料及び方法を用いて形成することができる。

**【0191】**

ゲート絶縁膜303は、ゲート絶縁層404と同様の材料及び方法を用いて形成することができる。

**【0192】**

次いで、ゲート絶縁膜403上にゲート電極層302を形成する。その後、該ゲート電極層302をマスクとして第3の酸化物半導体膜317c及びゲート絶縁膜303を加工して、第3の層316c及びゲート絶縁層304を形成する(図17(D)参照)。ゲート電極層302をマスクとして自己整合的に第3の層316c及びゲート絶縁層304の加工を行うと、マスク枚数を増加することができないため好適である。10

**【0193】**

ゲート電極層302は、ゲート電極層402と同様の材料及び方法を用いて形成することができる。

**【0194】**

第3の酸化物半導体膜317cを第3の層316cへと加工することで、第3の層316cに含有されるインジウムの外方拡散を抑制することができる。インジウムの外方拡散は、トランジスタの電気特性の変動を引き起こす要因や、工程中の成膜室内の汚染要因となるため、ゲート電極層302をマスクとした第3の層316cへの加工は効果的である。20

**【0195】**

以上によって、トランジスタ360を作製することができる。

**【0196】**

本実施の形態で示すトランジスタは、実施の形態1の積層構造を含み、酸化物半導体層においてチャネルが形成される第1の層と絶縁層との間に、第3の層を有することで、酸化物半導体層の界面とチャネルを遠ざけることができるため、界面準位のチャネルへの影響を抑制することが可能となる。また、第1の層乃至第3の層は、非晶質酸化物半導体と比較して欠陥準位密度の低減されたナノ結晶酸化物半導体で構成される。欠陥準位密度の低減された第1の層乃至第3の層を含む酸化物半導体層をトランジスタに用いることで、当該トランジスタの電気特性の変動を低減し、信頼性を向上させることができる。30

**【0197】**

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0198】**

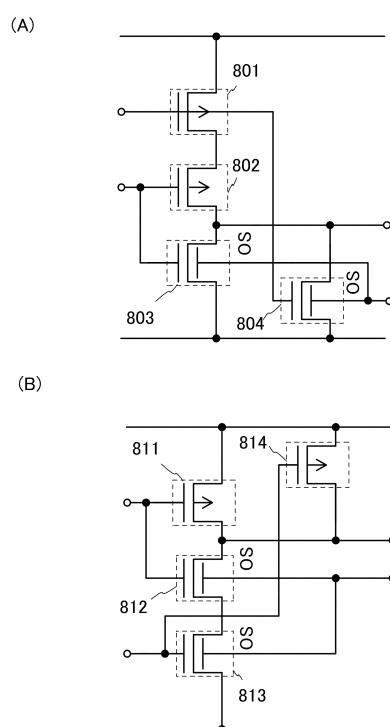

(実施の形態3)

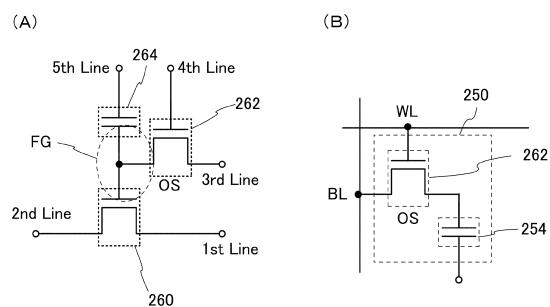

本発明の一態様に係る半導体装置の一例として、論理回路であるNOR型回路の回路図の一例を図18(A)に示す。図18(B)はNAND型回路の回路図である。

**【0199】**

図18(A)に示すNOR型回路において、pチャネル型トランジスタであるトランジスタ801、802は、チャネル形成領域に酸化物半導体以外の半導体材料(例えば、シリコンなど)を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ803、804は、酸化物半導体を含み実施の形態2で示すトランジスタと同様な構造を有するトランジスタを用いる。40

**【0200】**

シリコンなどの半導体材料を用いたトランジスタは高速動作が容易である。一方、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

**【0201】**

論理回路の小型化のために、nチャネル型のトランジスタであるトランジスタ803、804を用いる。50

04は、pチャネル型のトランジスタであるトランジスタ801、802上に積層されることが好ましい。例えば、単結晶シリコン基板を用いてトランジスタ801、802を形成し、絶縁層を介してトランジスタ801、802上にトランジスタ803、804を形成することが可能である。

#### 【0202】

また、図18(B)に示すNAND型回路では、pチャネル型トランジスタであるトランジスタ811、814は、チャネル形成領域に酸化物半導体以外の半導体材料(例えば、シリコンなど)を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ812、813は、酸化物半導体層を含み、上記実施の形態2で示すトランジスタと同様な構造を有するトランジスタを用いる。

10

#### 【0203】

また、図18(A)に示すNOR回路と同様に、論理回路の小型化のために、nチャネル型のトランジスタであるトランジスタ812、813は、pチャネル型のトランジスタであるトランジスタ811、814上に積層されることが好ましい。

#### 【0204】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、消費電力を十分に低減することができる。

#### 【0205】

また、異なる半導体材料を用いた半導体素子を積層することにより、微細化及び高集積化を実現し、かつ安定で高い電気的特性を付与された半導体装置、及び該半導体装置の作製方法を提供することができる。

20

#### 【0206】

また、本発明の一態様に係る酸化物半導体層を含むトランジスタの構成を適用することで、信頼性が高く、安定した特性を示すNOR型回路とNAND型回路を提供することができる。

#### 【0207】

なお、本実施の形態では、実施の形態2に示すトランジスタを使用したNOR型回路とNAND型回路の例を示したが、特に限定されず、実施の形態2に示すトランジスタを使用したAND型回路やOR回路などを形成することもできる。

30

#### 【0208】

または、本実施の形態や、別の実施の形態で述べたトランジスタと、表示素子とを組み合わせて、表示装置を構成することが可能である。例えば、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置の一例としては、EL(エレクトロルミネッセンス)素子(有機物及び無機物を含むEL素子、有機EL素子、無機EL素子)、LED(白色LED、赤色LED、緑色LED、青色LEDなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイパネル(PDP)、デジタルマイクロミラーデバイス(DMD)、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(FED)又はSED方式平面型ディスプレイ(SED:Surface-conduction Electron-emitter Display)などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。

40

50

**【0209】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0210】****(実施の形態4)**

本実施の形態では、実施の形態2に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置（記憶装置）の一例を、図面を用いて説明する。

**【0211】**

図19(A)は、本実施の形態の半導体装置を示す回路図である。

10

**【0212】**

図19(A)に示すトランジスタ260は、酸化物半導体以外の半導体材料（例えば、シリコンなど）を用いたトランジスタを適用することができ、高速動作が容易である。また、トランジスタ262には本発明の一態様の酸化物半導体層を含み実施の形態2で示すトランジスタと同様な構造を有するトランジスタを適用することができ、その特性により長時間の電荷保持を可能とする。

**【0213】**

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、本実施の形態に示す半導体装置に用いるトランジスタとしては、pチャネル型トランジスタを用いることもできる。

20

**【0214】**

図19(A)において、第1の配線(1st Line)とトランジスタ260のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ260のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ262のソース電極層又はドレイン電極層の一方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ262のゲート電極層とは、電気的に接続されている。そして、トランジスタ260のゲート電極層と、トランジスタ262のソース電極層又はドレイン電極層の他方は、容量素子264の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子264の電極の他方は電気的に接続されている。

30

**【0215】**

図19(A)に示す半導体装置では、トランジスタ260のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

**【0216】**

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ262がオン状態となる電位にして、トランジスタ262をオン状態とする。これにより、第3の配線の電位が、トランジスタ260のゲート電極層、および容量素子264に与えられる。すなわち、トランジスタ260のゲート電極層には、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベル電荷、Highレベル電荷という）のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ262がオフ状態となる電位にして、トランジスタ262をオフ状態とすることにより、トランジスタ260のゲート電極層に与えられた電荷が保持される（保持）。

40

**【0217】**

トランジスタ262のオフ電流は極めて小さいため、トランジスタ260のゲート電極層の電荷は長時間にわたって保持される。

**【0218】**

次に情報の読み出しについて説明する。第1の配線に所定の電位（定電位）を与えた状態で、第5の配線に適切な電位（読み出し電位）を与えると、トランジスタ260のゲート

50

電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ260をnチャネル型とすると、トランジスタ260のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ260のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ260を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ260のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $> V_{th\_H}$ ) となれば、トランジスタ260は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $< V_{th\_L}$ ) となっても、トランジスタ260は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

#### 【0219】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ260が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線に与えればよい。又は、ゲート電極層の状態にかかわらずトランジスタ260が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線に与えればよい。

#### 【0220】

図19(B)に異なる記憶装置の構造の一形態の例を示す。図19(B)は、半導体装置の回路構成の一例を示し、図19(C)は半導体装置の一例を示す概念図である。まず、図19(B)に示す半導体装置について説明を行い、続けて図19(C)に示す半導体装置について、以下説明を行う。

#### 【0221】

図19(B)に示す半導体装置において、ビット線BLとトランジスタ262のソース電極またはドレイン電極とは電気的に接続され、ワード線WLとトランジスタ262のゲート電極層とは電気的に接続され、トランジスタ262のソース電極またはドレイン電極と容量素子254の第1の端子とは電気的に接続されている。

#### 【0222】

酸化物半導体を用いたトランジスタ262は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ262をオフ状態とすることで、容量素子254の第1の端子の電位(あるいは、容量素子254に蓄積された電荷)を極めて長時間にわたって保持することが可能である。

#### 【0223】

次に、図19(B)に示す半導体装置(メモリセル250)に、情報の書き込み及び保持を行う場合について説明する。

#### 【0224】

まず、ワード線WLの電位を、トランジスタ262がオン状態となる電位として、トランジスタ262をオン状態とする。これにより、ビット線BLの電位が、容量素子254の第1の端子に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ262がオフ状態となる電位として、トランジスタ262をオフ状態とすることにより、容量素子254の第1の端子の電位が保持される(保持)。

#### 【0225】

トランジスタ262のオフ電流は極めて小さいため、容量素子254の第1の端子の電位(あるいは容量素子に蓄積された電荷)を長時間にわたって保持することができる。

#### 【0226】

次に、情報の読み出しについて説明する。トランジスタ262がオン状態となると、浮遊状態であるビット線BLと容量素子254とが導通し、ビット線BLと容量素子254の

10

20

30

40

50

間で電荷が再分配される。その結果、ピット線 B L の電位が変化する。ピット線 B L の電位の変化量は、容量素子 254 の第1の端子の電位（あるいは容量素子 254 に蓄積された電荷）によって、異なる値をとる。

#### 【0227】

例えば、容量素子 254 の第1の端子の電位を V、容量素子 254 の容量を C、ピット線 B L が有する容量成分（以下、ピット線容量とも呼ぶ）を C B、電荷が再分配される前のピット線 B L の電位を V B 0 とすると、電荷が再分配された後のピット線 B L の電位は、 $(C_B \times V_{B0} + C \times V) / (C_B + C)$  となる。従って、メモリセル 250 の状態として、容量素子 254 の第1の端子の電位が V 1 と V 0 ( $V_1 > V_0$ ) の2状態をとるとすると、電位 V 1 を保持している場合のピット線 B L の電位 ( $= (C_B \times V_{B0} + C \times V_1) / (C_B + C)$ ) は、電位 V 0 を保持している場合のピット線 B L の電位 ( $= (C_B \times V_{B0} + C \times V_0) / (C_B + C)$ ) よりも高くなることがわかる。10

#### 【0228】

そして、ピット線 B L の電位を所定の電位と比較することで、情報を読み出すことができる。

#### 【0229】

このように、図 19 (B) に示す半導体装置は、トランジスタ 262 のオフ電流が極めて小さいという特徴から、容量素子 254 に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。20

#### 【0230】

次に、図 19 (C) に示す半導体装置について、説明を行う。

#### 【0231】

図 19 (C) に示す半導体装置は、上部に記憶回路として図 19 (B) に示したメモリセル 250 を複数有するメモリセルアレイ 251a 及びメモリセルアレイ 251b を有し、下部に、メモリセルアレイ 251（メモリセルアレイ 251a 及びメモリセルアレイ 251b）を動作させるために必要な周辺回路 253 を有する。なお、周辺回路 253 は、メモリセルアレイ 251 と電気的に接続されている。30

#### 【0232】

図 19 (C) に示した構成とすることにより、周辺回路 253 をメモリセルアレイ 251（メモリセルアレイ 251a 及びメモリセルアレイ 251b）の直下に設けることができるため半導体装置の小型化を図ることができる。

#### 【0233】

周辺回路 253 に設けられるトランジスタは、トランジスタ 262 とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、前記トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。40

#### 【0234】

なお、図 19 (C) に示した半導体装置では、2つのメモリセルアレイ 251（メモリセルアレイ 251a と、メモリセルアレイ 251b）が積層された構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としてもよい。

#### 【0235】

トランジスタ 262 として、本発明の一態様の酸化物半導体層をチャネル形成領域に用いるトランジスタを適用することによって、長期にわたり記憶内容を保持することが可能で50

ある。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

**【0236】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0237】**

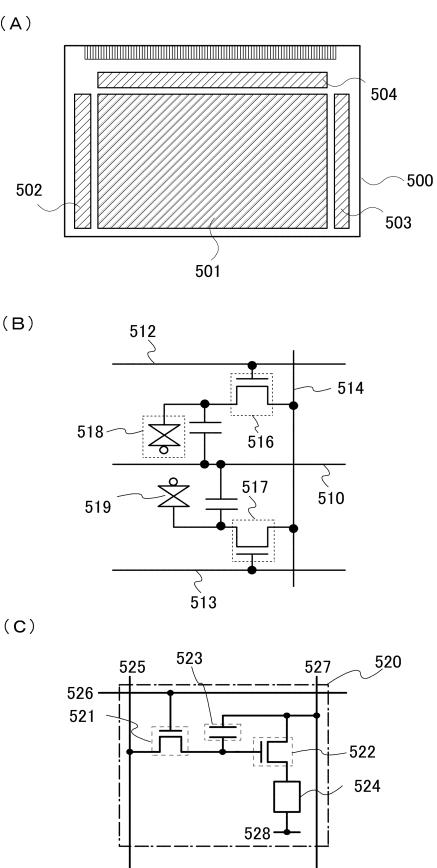

(実施の形態5)

本実施の形態では、本発明の一態様の表示パネルの構成について、図20を参照しながら説明する。

10

**【0238】**

図20(A)は、本発明の一態様の表示パネルの上面図であり、図20(B)は、本発明の一態様の表示パネルの画素に液晶素子を適用する場合に用いることができる画素回路を説明するための回路図である。また、図20(C)は、本発明の一態様の表示パネルの画素に有機EL素子を適用する場合に用いることができる画素回路を説明するための回路図である。

**【0239】**

画素部に配置するトランジスタは、実施の形態2に従って形成することができる。また、当該トランジスタはnチャネル型とすることが容易なので、駆動回路のうち、nチャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。このように、画素部や駆動回路に実施の形態3に示すトランジスタを用いることにより、信頼性の高い表示装置を提供することができる。

20

**【0240】**

アクティブマトリクス型表示装置のブロック図の一例を図20(A)に示す。表示装置の基板500上には、画素部501、第1の走査線駆動回路502、第2の走査線駆動回路503、信号線駆動回路504を有する。画素部501には、複数の信号線が信号線駆動回路504から延伸して配置され、複数の走査線が第1の走査線駆動回路502、及び第2の走査線駆動回路503から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に設けられている。また、表示装置の基板500はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路(コントローラ、制御ICともいう)に接続されている。

30

**【0241】**

図20(A)では、第1の走査線駆動回路502、第2の走査線駆動回路503、信号線駆動回路504は、画素部501と同じ基板500上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板500外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板500上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

**【0242】**

40

<液晶パネル>

また、画素の回路構成の一例を図20(B)に示す。ここでは、VA型液晶表示パネルの画素に適用することができる画素回路を示す。

**【0243】**

この画素回路は、一つの画素に複数の画素電極層を有する構成に適用できる。それぞれの画素電極層は異なるトランジスタに接続され、各トランジスタは異なるゲート信号で駆動できるように構成されている。これにより、マルチドメイン設計された画素の個々の画素電極層に印加する信号を、独立して制御できる。

**【0244】**

トランジスタ516のゲート配線512と、トランジスタ517のゲート配線513には

50

、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能するソース電極層又はドレイン電極層514は、トランジスタ516とトランジスタ517で共通に用いられている。トランジスタ516とトランジスタ517は実施の形態2で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い液晶表示パネルを提供することができる。

#### 【0245】

トランジスタ516と電気的に接続する第1の画素電極層と、トランジスタ517と電気的に接続する第2の画素電極層の形状について説明する。第1の画素電極層と第2の画素電極層の形状は、スリットによって分離されている。第1の画素電極層はV字型に広がる形状を有し、第2の画素電極層は第1の画素電極層の外側を囲むように形成される。

10

#### 【0246】

トランジスタ516のゲート電極層はゲート配線512と接続され、トランジスタ517のゲート電極層はゲート配線513と接続されている。ゲート配線512とゲート配線513に異なるゲート信号を与えてトランジスタ516とトランジスタ517の動作タイミングを異ならせ、液晶の配向を制御できる。

#### 【0247】

また、容量配線510と、誘電体として機能するゲート絶縁層と、第1の画素電極層または第2の画素電極層と電気的に接続する容量電極とで保持容量を形成してもよい。

#### 【0248】

マルチドメイン構造は、一画素に第1の液晶素子518と第2の液晶素子519を備える。第1の液晶素子518は第1の画素電極層と対向電極層との間の液晶層とで構成され、第2の液晶素子519は第2の画素電極層と対向電極層との間の液晶層とで構成される。

20

#### 【0249】

なお、図20(B)に示す画素回路は、これに限定されない。例えば、図20(B)に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサ、又は論理回路などを追加してもよい。

#### 【0250】

##### <有機ELパネル>

また、画素の回路構成の他の一例を図20(C)に示す。ここでは、有機EL素子を用いた表示パネルの画素構造を示す。

30

#### 【0251】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極の一方から電子が、他方から正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、電子および正孔が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

#### 【0252】

図20(C)は、適用可能な画素回路の一例を示す図である。ここではnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。なお、本発明の一態様の酸化物半導体層は、nチャネル型のトランジスタのチャネル形成領域に用いることができる。また、当該画素回路は、デジタル時間階調駆動を適用することができる。

40

#### 【0253】

適用可能な画素回路の構成及びデジタル時間階調駆動を適用した場合の画素の動作について説明する。

#### 【0254】

画素520は、スイッチング用トランジスタ521、駆動用トランジスタ522、発光素子524及び容量素子523を有している。スイッチング用トランジスタ521は、ゲート電極層が走査線526に接続され、第1電極(ソース電極層及びドレイン電極層の一方)が信号線525に接続され、第2電極(ソース電極層及びドレイン電極層の他方)が駆

50

動用トランジスタ 522 のゲート電極層に接続されている。駆動用トランジスタ 522 は、ゲート電極層が容量素子 523 を介して電源線 527 に接続され、第 1 電極が電源線 527 に接続され、第 2 電極が発光素子 524 の第 1 電極（画素電極）に接続されている。発光素子 524 の第 2 電極は共通電極 528 に相当する。共通電極 528 は、同一基板上に形成される共通電位線と電気的に接続される。

#### 【0255】

スイッチング用トランジスタ 521 および駆動用トランジスタ 522 は実施の形態 3 で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い有機 E L 表示パネルを提供することができる。

#### 【0256】

10 発光素子 524 の第 2 電極（共通電極 528）の電位は低電源電位に設定する。なお、低電源電位とは、電源線 527 に設定される高電源電位より低い電位であり、例えば GND 、 0 V などを低電源電位として設定することができる。発光素子 524 の順方向のしきい値電圧以上となるように高電源電位と低電源電位を設定し、その電位差を発光素子 524 に印加することにより、発光素子 524 に電流を流して発光させる。なお、発光素子 524 の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。

#### 【0257】

なお、容量素子 523 は駆動用トランジスタ 522 のゲート容量を代用することにより省略できる。駆動用トランジスタ 522 のゲート容量については、チャネル形成領域とゲート電極層との間で容量が形成されていてもよい。

#### 【0258】

次に、駆動用トランジスタ 522 に入力する信号について説明する。電圧入力電圧駆動方式の場合、駆動用トランジスタ 522 が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を、駆動用トランジスタ 522 に入力する。なお、駆動用トランジスタ 522 を線形領域で動作させるために、電源線 527 の電圧よりも高い電圧を駆動用トランジスタ 522 のゲート電極層にかける。また、信号線 525 には、電源線電圧に駆動用トランジスタ 522 の閾値電圧  $V_{th}$  を加えた値以上の電圧をかける。

#### 【0259】

30 アナログ階調駆動を行う場合、駆動用トランジスタ 522 のゲート電極層に発光素子 524 の順方向電圧に駆動用トランジスタ 522 の閾値電圧  $V_{th}$  を加えた値以上の電圧をかける。なお、駆動用トランジスタ 522 が飽和領域で動作するようにビデオ信号を入力し、発光素子 524 に電流を流す。また、駆動用トランジスタ 522 を飽和領域で動作させるために、電源線 527 の電位を、駆動用トランジスタ 522 のゲート電位より高くする。ビデオ信号をアナログとすることで、発光素子 524 にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

#### 【0260】

なお、画素回路の構成は、図 20 (C) に示す画素構成に限定されない。例えば、図 20 (C) に示す画素回路にスイッチ、抵抗素子、容量素子、センサ、トランジスタ又は論理回路などを追加してもよい。

#### 【0261】

40 以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0262】

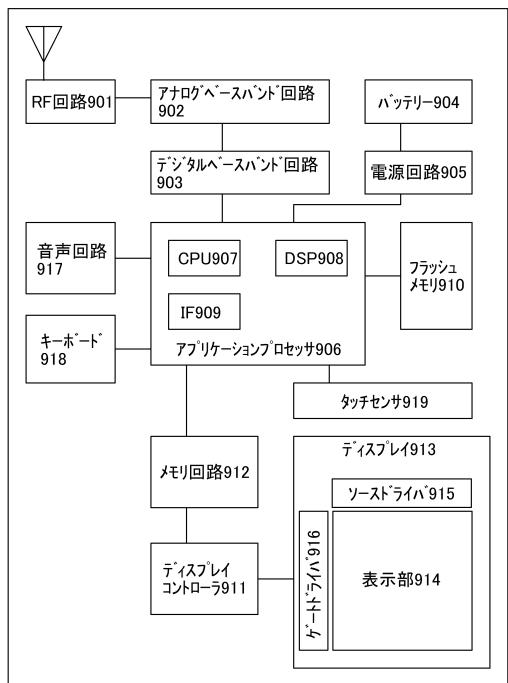

##### (実施の形態 6)

本実施の形態では、本発明の一態様の酸化物半導体層を用いた半導体装置および電子機器の構成について、図 21 および図 22 を参照しながら説明する。

#### 【0263】

図 21 は、本発明の一態様の酸化物半導体層を適用した半導体装置を含む電子機器のプロック図である。

10

20

30

40

50

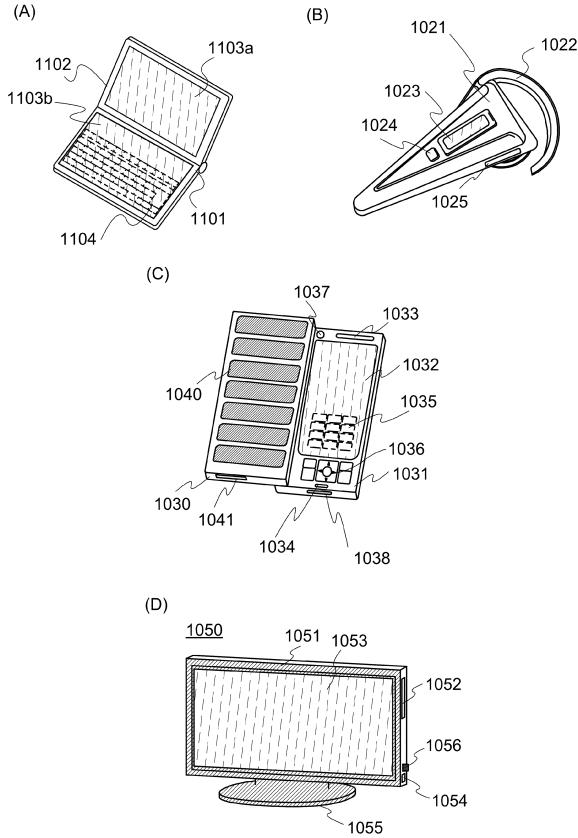

**【 0 2 6 4 】**

図22は、本発明の一態様の酸化物半導体層を適用した半導体装置を含む電子機器の外観図である。

**【 0 2 6 5 】**

図21に示す電子機器はR F回路901、アナログベースバンド回路902、デジタルベースバンド回路903、バッテリー904、電源回路905、アプリケーションプロセッサ906、フラッシュメモリ910、ディスプレイコントローラ911、メモリ回路912、ディスプレイ913、タッチセンサ919、音声回路917、キー ボード918などより構成されている。

**【 0 2 6 6 】**

10

アプリケーションプロセッサ906はC P U 907、D S P 908、インターフェイス(I F)909を有している。また、メモリ回路912はS R A MまたはD R A Mで構成することができる。

**【 0 2 6 7 】**

実施の形態2で説明するトランジスタを、メモリ回路912に適用することにより、情報の書き込みおよび読み出しが可能な信頼性の高い電子機器を提供することができる。

**【 0 2 6 8 】**

また、実施の形態2で説明するトランジスタを、C P U 907またはD S P 908に含まれるレジスタ等に適用することにより、情報の書き込みおよび読み出しが可能な信頼性の高い電子機器を提供することができる。

20

**【 0 2 6 9 】**

なお、実施の形態2で説明するトランジスタのオフリーク電流が極めて小さい場合は、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたメモリ回路912を提供できる。また、パワーゲーティングされている期間に、パワーゲーティング前の状態をレジスタ等に記憶することができるC P U 907またはD S P 908を提供することができる。

**【 0 2 7 0 】**

また、ディスプレイ913は表示部914、ソースドライバ915、ゲートドライバ916によって構成されている。

**【 0 2 7 1 】**

表示部914はマトリクス状に配置された複数の画素を有する。画素は画素回路を備え、画素回路はゲートドライバ916と電気的に接続されている。

30

**【 0 2 7 2 】**

実施の形態2で説明するトランジスタを、画素回路またはゲートドライバ916に適宜用いることができる。これにより、信頼性の高いディスプレイを提供することができる。

**【 0 2 7 3 】**

電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

40

**【 0 2 7 4 】**

図22(A)は、携帯型の情報端末であり、本体1101、筐体1102、表示部1103a、1103bなどによって構成されている。表示部1103bはタッチパネルとなつてあり、表示部1103bに表示されるキーボードボタン1104を触ることで画面操作や、文字入力を行うことができる。勿論、表示部1103aをタッチパネルとして構成してもよい。実施の形態3で示したトランジスタをスイッチング素子として液晶パネルや有機発光パネルを作製して表示部1103a、1103bに適用することにより、信頼性の高い携帯型の情報端末とすることができます。

**【 0 2 7 5 】**

図22(A)に示す携帯型の情報端末は、様々な情報(静止画、動画、テキスト画像など

50

)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

#### 【0276】

また、図22(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

#### 【0277】

図22(B)は、携帯音楽プレイヤーであり、本体1021には表示部1023と、耳に装着するための固定部1022と、スピーカー、操作ボタン1024、外部メモリスロット1025等が設けられている。実施の形態3で示したトランジスタをスイッチング素子として液晶パネルや有機発光パネルを作製して表示部1023に適用することにより、より信頼性の高い携帯音楽プレイヤーとすることができます。10

#### 【0278】

さらに、図22(B)に示す携帯音楽プレイヤーにアンテナやマイク機能や無線機能を持たせ、携帯電話と連携させれば、乗用車などを運転しながらワイヤレスによるハンズフリーでの会話も可能である。

#### 【0279】

図22(C)は、携帯電話であり、筐体1030及び筐体1031の二つの筐体で構成されている。筐体1031には、表示パネル1032、スピーカー1033、マイクロフォン1034、ポインティングデバイス1036、カメラ用レンズ1037、外部接続端子1038などを備えている。また、筐体1030には、携帯電話の充電を行う太陽電池セル1040、外部メモリスロット1041などを備えている。また、アンテナは筐体1031内部に内蔵されている。実施の形態3で説明するトランジスタを表示パネル1032に適用することにより、信頼性の高い携帯電話とすることができます。20

#### 【0280】

また、表示パネル1032はタッチパネルを備えており、図22(C)には映像表示されている複数の操作キー1035を点線で示している。なお、太陽電池セル1040で出力される電圧を各回路に必要な電圧に昇圧するための昇圧回路も実装している。30

#### 【0281】

例えば、昇圧回路などの電源回路に用いられるパワートランジスタも実施の形態3で説明するトランジスタの酸化物半導体層の膜厚を2μm以上50μm以下とすることで形成することができる。

#### 【0282】

表示パネル1032は、使用形態に応じて表示の方向が適宜変化する。また、表示パネル1032と同一面上にカメラ用レンズ1037を備えているため、テレビ電話が可能である。スピーカー1033及びマイクロフォン1034は音声通話に限らず、テレビ電話、録音、再生などが可能である。さらに、筐体1030と筐体1031は、スライドし、図22(C)のように展開している状態から重なり合った状態とすることで形成することができる。40

#### 【0283】

外部接続端子1038はACアダプタ及びUSBケーブルなどの各種ケーブルと接続可能であり、充電及びパソコンコンピュータなどとのデータ通信が可能である。また、外部メモリスロット1041に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

#### 【0284】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってよい。

#### 【0285】

図22(D)は、テレビジョン装置の一例を示している。テレビジョン装置1050は、筐体1051に表示部1053が組み込まれている。表示部1053により、映像を表示することが可能である。また、筐体1051を支持するスタンド1055にCPUが内蔵されている。実施の形態3で説明するトランジスタを表示部1053およびCPUに適用することにより、信頼性の高いテレビジョン装置1050とすることができます。

#### 【0286】

テレビジョン装置1050の操作は、筐体1051が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

#### 【0287】

なお、テレビジョン装置1050は、受信機やモデムなどを備えた構成とする。受信機により一般的なテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双向方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

#### 【0288】

また、テレビジョン装置1050は、外部接続端子1054や、記憶媒体再生録画部1052、外部メモリスロットを備えている。外部接続端子1054は、USBケーブルなどの各種ケーブルと接続可能であり、パソコン用コンピュータなどとのデータ通信が可能である。記憶媒体再生録画部1052では、ディスク状の記録媒体を挿入し、記録媒体に記憶されているデータの読み出し、記録媒体への書き込みが可能である。また、外部メモリスロットに差し込まれた外部メモリ1056にデータ保存されている画像や映像などを表示部1053に映し出すことも可能である。

#### 【0289】

また、実施の形態2で説明するトランジスタのオフリード電流が極めて小さい場合は、当該トランジスタを外部メモリ1056やCPUに適用することにより、消費電力が十分に低減された信頼性の高いテレビジョン装置1050とすることができます。

#### 【0290】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【符号の説明】

##### 【0291】

|       |         |

|-------|---------|

| 102   | ゲート電極層  |

| 104   | ゲート絶縁層  |

| 106   | 酸化物半導体層 |

| 106 a | 層       |

| 106 b | 層       |

| 106 c | 層       |

| 108   | 絶縁層     |

| 110   | 半導体層    |

| 116   | 酸化物半導体層 |

| 116 a | 層       |

| 116 b | 層       |

| 116 c | 層       |

| 124   | 絶縁膜     |

| 200   | 石英ガラス基板 |

| 202   | ダミー基板   |

| 204   | 酸化物半導体層 |

| 208   | 酸化物半導体膜 |

| 208 a | 酸化物半導体層 |

| 208 b | 酸化物半導体層 |

10

20

30

40

50

|         |          |    |

|---------|----------|----|

| 2 1 0 a | 領域       |    |

| 2 1 0 b | 領域       |    |

| 2 5 0   | メモリセル    |    |

| 2 5 1   | メモリセルアレイ |    |

| 2 5 1 a | メモリセルアレイ |    |

| 2 5 1 b | メモリセルアレイ |    |

| 2 5 3   | 周辺回路     |    |

| 2 5 4   | 容量素子     |    |

| 2 6 0   | トランジスタ   | 10 |

| 2 6 2   | トランジスタ   |    |

| 2 6 4   | 容量素子     |    |

| 3 0 0   | 基板       |    |

| 3 0 2   | ゲート電極層   |    |

| 3 0 3   | ゲート絶縁膜   |    |

| 3 0 4   | ゲート絶縁層   |    |

| 3 0 8   | 絶縁層      |    |

| 3 1 0 a | ソース電極層   |    |

| 3 1 0 b | ドレイン電極層  |    |

| 3 1 4 a | 酸化物半導体層  |    |

| 3 1 4 b | 酸化物半導体層  | 20 |

| 3 1 6   | 酸化物半導体層  |    |

| 3 1 6 a | 層        |    |

| 3 1 6 b | 層        |    |

| 3 1 6 c | 層        |    |

| 3 1 7 a | 酸化物半導体膜  |    |

| 3 1 7 b | 酸化物半導体膜  |    |

| 3 1 7 c | 酸化物半導体膜  |    |

| 3 5 0   | トランジスタ   |    |

| 3 6 0   | トランジスタ   |    |

| 4 0 0   | 基板       | 30 |

| 4 0 2   | ゲート電極層   |    |

| 4 0 3   | ゲート絶縁膜   |    |

| 4 0 4   | ゲート絶縁層   |    |

| 4 0 4 a | 絶縁層      |    |

| 4 0 4 b | 絶縁層      |    |

| 4 0 6   | 酸化物半導体層  |    |

| 4 0 6 a | 層        |    |

| 4 0 6 b | 層        |    |

| 4 0 7 a | 酸化物半導体膜  |    |

| 4 0 7 b | 酸化物半導体膜  | 40 |

| 4 0 8   | 絶縁層      |    |

| 4 0 8 a | 絶縁層      |    |

| 4 0 8 b | 絶縁層      |    |

| 4 0 9   | コンタクトホール |    |

| 4 1 0 a | ソース電極層   |    |

| 4 1 0 b | ドレイン電極層  |    |

| 4 5 0   | トランジスタ   |    |

| 4 6 0   | トランジスタ   |    |

| 5 0 0   | 基板       |    |

| 5 0 1   | 画素部      | 50 |

|         |               |    |

|---------|---------------|----|

| 5 0 2   | 走査線駆動回路       |    |

| 5 0 3   | 走査線駆動回路       |    |

| 5 0 4   | 信号線駆動回路       |    |

| 5 1 0   | 容量配線          |    |

| 5 1 2   | ゲート配線         |    |

| 5 1 3   | ゲート配線         |    |

| 5 1 4   | ドレイン電極層       |    |

| 5 1 6   | トランジスタ        |    |

| 5 1 7   | トランジスタ        |    |

| 5 1 8   | 液晶素子          | 10 |

| 5 1 9   | 液晶素子          |    |

| 5 2 0   | 画素            |    |

| 5 2 1   | スイッチング用トランジスタ |    |

| 5 2 2   | 駆動用トランジスタ     |    |

| 5 2 3   | 容量素子          |    |

| 5 2 4   | 発光素子          |    |

| 5 2 5   | 信号線           |    |

| 5 2 6   | 走査線           |    |

| 5 2 7   | 電源線           |    |

| 5 2 8   | 共通電極          | 20 |

| 8 0 1   | トランジスタ        |    |

| 8 0 2   | トランジスタ        |    |

| 8 0 3   | トランジスタ        |    |

| 8 0 4   | トランジスタ        |    |

| 8 1 1   | トランジスタ        |    |

| 8 1 2   | トランジスタ        |    |

| 8 1 3   | トランジスタ        |    |

| 8 1 4   | トランジスタ        |    |

| 9 0 1   | R F 回路        |    |

| 9 0 2   | アナログベースバンド回路  | 30 |

| 9 0 3   | デジタルベースバンド回路  |    |

| 9 0 4   | パッテリー         |    |

| 9 0 5   | 電源回路          |    |

| 9 0 6   | アプリケーションプロセッサ |    |

| 9 0 7   | C P U         |    |

| 9 0 8   | D S P         |    |

| 9 1 0   | フラッシュメモリ      |    |

| 9 1 1   | ディスプレイコントローラ  |    |

| 9 1 2   | メモリ回路         |    |

| 9 1 3   | ディスプレイ        | 40 |

| 9 1 4   | 表示部           |    |

| 9 1 5   | ソースドライバ       |    |

| 9 1 6   | ゲートドライバ       |    |

| 9 1 7   | 音声回路          |    |

| 9 1 8   | キー ボード        |    |

| 9 1 9   | タッチセンサ        |    |

| 1 0 2 1 | 本体            |    |

| 1 0 2 2 | 固定部           |    |

| 1 0 2 3 | 表示部           |    |

| 1 0 2 4 | 操作ボタン         | 50 |

|           |             |    |

|-----------|-------------|----|

| 1 0 2 5   | 外部メモリスロット   |    |

| 1 0 3 0   | 筐体          |    |

| 1 0 3 1   | 筐体          |    |

| 1 0 3 2   | 表示パネル       |    |

| 1 0 3 3   | スピーカー       |    |

| 1 0 3 4   | マイクロフォン     |    |

| 1 0 3 5   | 操作キー        |    |

| 1 0 3 6   | ポインティングデバイス |    |

| 1 0 3 7   | カメラ用レンズ     |    |

| 1 0 3 8   | 外部接続端子      | 10 |

| 1 0 4 0   | 太陽電池セル      |    |

| 1 0 4 1   | 外部メモリスロット   |    |

| 1 0 5 0   | テレビジョン装置    |    |

| 1 0 5 1   | 筐体          |    |

| 1 0 5 2   | 記憶媒体再生録画部   |    |

| 1 0 5 3   | 表示部         |    |

| 1 0 5 4   | 外部接続端子      |    |

| 1 0 5 5   | スタンド        |    |

| 1 0 5 6   | 外部メモリ       |    |

| 1 1 0 1   | 本体          | 20 |

| 1 1 0 2   | 筐体          |    |

| 1 1 0 3 a | 表示部         |    |

| 1 1 0 3 b | 表示部         |    |

| 1 1 0 4   | キーボードボタン    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

| (51)Int.Cl. |                  | F I            |

|-------------|------------------|----------------|

| H 01 L      | 29/792 (2006.01) | G 02 F 1/1368  |

| G 02 F      | 1/1368 (2006.01) | H 05 B 33/14 A |

| H 01 L      | 51/50 (2006.01)  | H 05 B 33/14 Z |

| H 05 B      | 33/14 (2006.01)  |                |

審査官 棚田 一也

(56)参考文献 特開2006-165529(JP,A)

特開2011-091375(JP,A)

再公表特許第2011/039853(JP,A1)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| H 01 L | 29 / 786  |

| G 02 F | 1 / 1368  |

| H 01 L | 21 / 336  |

| H 01 L | 21 / 8242 |

| H 01 L | 27 / 108  |

| H 01 L | 29 / 788  |

| H 01 L | 29 / 792  |

| H 01 L | 51 / 50   |

| H 05 B | 33 / 14   |