(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5332041号

(P5332041)

(45) 発行日 平成25年11月6日(2013.11.6)

(24) 登録日 平成25年8月9日(2013.8.9)

(51) Int.CI.

HO4N 5/335 (2011.01)

F 1

HO4N 5/335

請求項の数 14 (全 30 頁)

(21) 出願番号 特願2009-205918 (P2009-205918)

(22) 出願日 平成21年9月7日 (2009.9.7)

(65) 公開番号 特開2010-239604 (P2010-239604A)

(43) 公開日 平成22年10月21日 (2010.10.21)

審査請求日 平成24年3月9日 (2012.3.9)

(31) 優先権主張番号 特願2009-61550 (P2009-61550)

(32) 優先日 平成21年3月13日 (2009.3.13)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2009-61551 (P2009-61551)

(32) 優先日 平成21年3月13日 (2009.3.13)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】 固体撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光信号を電気信号に変換する光電変換素子を含む画素が複数行列状に配置され、各画素を行ごとに順次走査しながら選択行の各画素の信号を列ごとに配線された複数の垂直読出線を介して出力する撮像手段と、

前記垂直読出線を介して出力された各画素の信号を保持する複数の保持手段と、

前記複数の保持手段のそれぞれに対応して設けられ、当該保持手段によって保持される画素の信号をアナログ信号からデジタル値に変換する複数の変換手段とを含み、

前記複数の変換手段のそれぞれは、当該保持手段によって保持される画素の信号に応じて前記デジタル値の中の上位ビットを生成する第1の生成手段と、

当該保持手段によって保持される画素の信号および前記第1の生成手段によって生成された上位ビットに応じて前記デジタル値の中の下位ビットを生成する第2の生成手段と、

前記第1の生成手段によって生成された上位ビットと前記第2の生成手段によって生成された下位ビットとを加算して前記デジタル値を出力する加算手段とを含み、

前記第1の生成手段は、

当該保持手段によって画素の信号が保持されるノードと容量結合された複数の容量素子と、

前記複数の容量素子の対極の電圧を順次切替えることにより、前記ノードの電位を階段状に変化させる制御手段と、

前記ノードの電位と所定電位とを比較する比較手段と、

10

20

前記比較手段による比較結果に応じて、前記デジタル値の上位ビットを決定する決定手段とを含む、固体撮像装置。

**【請求項 2】**

前記保持手段は、照射時における画素の信号を保持し、

前記比較手段は、非照射時における画素の信号の電位と、前記保持手段によって画素の照射時における信号が保持されるノードの電位とを比較する、請求項 1 記載の固体撮像装置。

**【請求項 3】**

前記第 2 の生成手段は、当該保持手段によって画素の信号が保持されるノードと容量結合された容量素子と、

10

前記容量素子の対極の電圧をスロープ状に変化させる制御手段と、

前記容量素子の対極の電圧の変化開始でカウントを開始するカウンタのカウント値を、前記比較手段による比較結果に応じて保持するカウンタ値保持手段とを含む、請求項 1 または 2 記載の固体撮像装置。

**【請求項 4】**

前記カウンタは、グレイコードカウンタである、請求項 3 記載の固体撮像装置。

**【請求項 5】**

前記カウンタ値保持手段によって保持された前記グレイコードカウンタ値を、バイナリコードに変換する変換回路を含む、請求項 4 記載の固体撮像装置。

20

**【請求項 6】**

前記比較手段はコンパレータであり、比較時には 2 入力ともフローティング状態である、請求項 1 ~ 5 のいずれかに記載の固体撮像装置。

**【請求項 7】**

前記変換手段は、行列状に配置された画素の各列に対して 1 つ設けられる、請求項 1 記載の固体撮像装置。

**【請求項 8】**

前記変換手段がある行の画素の信号をアナログ信号からデジタル値に変換し、それと並行して、対応する保持手段が次の行の画素の信号を保持する、請求項 1 記載の固体撮像装置。

30

**【請求項 9】**

前記変換手段は、対応する 1 つの保持手段に対して複数設けられ、

保持手段が保持する画素の信号が行ごとに、対応する複数の保持手段に順次与えられて並行して変換処理が行なわれる、請求項 1 記載の固体撮像装置。

**【請求項 10】**

光信号を電気信号に変換する光電変換素子を含む画素が複数行列状に配置され、各画素を行ごとに順次走査しながら選択行の各画素の信号を列ごとに配線された複数の垂直読出線を介して出力する撮像手段と、

前記垂直読出線を介して出力された各画素の信号をアナログ信号からデジタル値に変換する複数の変換手段とを含み、

40

前記複数の変換手段のそれぞれは、初期電圧を前記デジタル値の中の上位ビットのそれぞれに対応する電圧ずつ変化させながら画素信号の電圧と比較し、比較結果に応じて前記上位ビットの各ビットを決定する第 1 の決定手段と、

前記画素信号の電圧および前記第 1 の決定手段によって決定された上位ビットに応じて、前記デジタル値の中の下位ビットを決定する第 2 の決定手段とを含む、固体撮像装置。

**【請求項 11】**

前記第 1 の決定手段は、初期電圧の電位をサンプリングして保持するサンプリング保持手段と、

前記サンプリング保持手段と容量結合された第 1 の容量を有する第 1 の容量素子と、前記第 1 の容量の半分の第 2 の容量を有する第 2 の容量素子とを少なくとも含む複数の容量素子と、

50

前記第1の容量素子の対極を第1の電圧から第2の電圧に変化させ、前記サンプリング保持手段の電圧を変化させて前記画素信号の電圧と比較し、比較結果を保持する第1の保持手段と、

前記第2の容量素子の対極を前記第1の電圧から前記第2の電圧に変化させ、前記サンプリング保持手段の電圧を変化させて前記画素信号の電圧と比較し、比較結果を保持する第2の保持手段と含む、請求項10記載の固体撮像装置。

**【請求項12】**

光信号を電気信号に変換する光電変換素子を含む画素が複数行列状に配置され、各画素を行ごとに順次走査しながら選択行の各画素の信号を列ごとに配線された複数の垂直読出線を介して出力する撮像手段と、

前記垂直読出線を介して出力された各画素の信号をアナログ信号からデジタル値に変換する複数の変換手段とを含み、

前記複数の変換手段のそれぞれは、前記垂直読出線を介して出力された画素信号の電位をサンプリングして保持するサンプリング保持手段と、

前記サンプリング保持手段によって保持される画素信号の電圧を前記デジタル値の中の上位ビットのそれに対応する電圧ずつ変化させながらリファレンス電圧と比較し、比較結果に応じて前記上位ビットの各ビットを決定する第1の決定手段と、

前記リファレンス電圧および前記第1の決定手段によって決定された上位ビットに応じて、前記デジタル値の中の下位ビットを決定する第2の決定手段とを含む、固体撮像装置。

10

**【請求項13】**

前記第1の決定手段は、前記サンプリング保持手段と容量結合された第1の容量を有する第1の容量素子と、前記第1の容量の半分の第2の容量を有する第2の容量素子とを少なくとも含む複数の容量素子と、

前記第1の容量素子の対極を第1の電圧から第2の電圧に変化させ、前記サンプリング保持手段によって保持される画素信号の電圧を変化させて前記リファレンス電圧と比較し、比較結果を保持する第1の保持手段と、

前記第2の容量素子の対極を前記第1の電圧から前記第2の電圧に変化させ、前記サンプリング保持手段によって保持される画素信号の電圧を変化させて前記リファレンス電圧と比較し、比較結果を保持する第2の保持手段とを含む、請求項12記載の固体撮像装置。

20

**【請求項14】**

前記第2の決定手段は、オーバレンジのデジタルアナログ変換器によって構成される、請求項10～13のいずれかに記載の固体撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、アナログ／デジタル変換器（以下、A D C（Analog/Digital Converter））と呼ぶ。）を内蔵した固体撮像装置に関し、特に、限られたスペースに配置することができるA D Cを内蔵した固体撮像装置に関する。

40

**【背景技術】**

**【0002】**

従来、カメラといえばフィルム型のものが主流であったが、最近になってデジタル型のカメラがそれに取って代わりだしている。さらに、デジタルカメラにおける画質の向上は著しく、最新型のデジタルカメラは、フィルムカメラの性能をもじのぐような状況になってしまっている。また、デジタルカメラには、C C D（Charge Coupled Device）やC M O S（Complementary Metal Oxide Semiconductor）イメージセンサといった方式があるが、カメラの高性能化の観点から、C M O Sデバイスを搭載しやすいC M O Sイメージセンサに対する注目が高まっている。

**【0003】**

50

C M O S イメージセンサには、アナログイメージセンサとデジタルイメージセンサとの2種類がある。どちらも一長一短があるものの、データ処理速度の観点からデジタルイメージセンサへの期待が大きい。具体的には、デジタルイメージセンサを用いると動画の撮影が可能となるだけではなく、後段の画像処理と組合せて様々な応用が考えられる。

#### 【 0 0 0 4 】

たとえば、テニスラケットにボールが当たる瞬間や、運動会で運動場を回りながらゴールする子供の顔写真のアップを、その方向にカメラを向けておくだけで、カメラが自動的にシャッターチャンスを判定し、自動的にシャッターを押してくれるようなことも可能となる。こうした処理を実現するためには、撮影した画像を瞬時に画像処理 I P ( Intellectual Property ) に転送する必要があり、アナログ情報である撮影情報をデジタル情報である画像処理用情報に変換することが必要となる。10

#### 【 0 0 0 5 】

このような背景から、デジタルカメラ向けの A D C の研究開発が盛んに行なわれてきている。C M O S イメージセンサにおける最も大きな問題は、画素の情報をすべてデジタル値に変換するため、データ処理量が非常に多いことである。単純に1つのA D C で処理するとし、たとえば画素数が1 0 0 0 万画素であり、一般的な動画処理レートである3 0 f p s ( frame per second ) で処理を行なうとすると、3 n s の間に1画素の情報をA / D 変換、データ転送する必要があり、非現実的なものとなる。このため、行列状に配置された画素の信号を、列ごとに配線された垂直読出線を介してA D C に取り込み、選択された行の画素の信号を順次A / D 変換する構成がとられている。これに関連する技術として、20 下記の特許文献1～2に開示された発明がある。

#### 【 0 0 0 6 】

特許文献1に開示された発明は、列並列A D C 搭載のC M O S イメージセンサにおいて、高解像度A D 変換を高速に実行可能とすることを目的とする。列並列A D C 搭載のC M O S イメージセンサにおいて、スロープの傾きが異なる参照電圧V r e f 1～V r e f 4 と参照電圧V r e f 5 とを用いるとともに、単位画素の出力電圧V x と参照電圧V r e f 1～V r e f 4 とを比較する比較回路と、参照電圧V r e f 1～V r e f 4 と参照電圧V r e f 5 とを比較する比較回路とをカラム処理回路に有する。そして、2つの比較回路およびアップ／ダウンカウンタの各動作によって高解像度A D 変換を高速に実行する。30

#### 【 0 0 0 7 】

特許文献2は、A D 変換時間がカウント期間によって決定されており、特に2回目のカウント期間に依存し、2回目のカウント期間がA D 変換期間の大勢を占めているために、A D 変換期間の短縮が難しいことに着目してなされたものである。列並列A D C 搭載のC M O S イメージセンサにおいて、2回目のA D 変換を行う前に、A D 変換範囲内の複数の判定電圧を用いて列信号線の信号電圧V x のレベル判定を行い、その判定結果を基に複数の参照電圧R A M P 1～R A M P n の中から列信号線の信号電圧V x に適した参照電圧R A M P を選択してA D 変換を行うことで、2回目のA D 変換時間を短縮する。30

#### 【先行技術文献】

##### 【特許文献】

##### 【 0 0 0 8 】

【特許文献1】特開2 0 0 8 - 0 9 8 7 2 2 号公報

【特許文献2】特開2 0 0 6 - 3 5 2 5 9 7 号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【 0 0 0 9 】

上述のように、A D C が、選択された行の画素の信号を垂直読出線を介して取り込み、順次A / D 変換する構成においては、A D C を含んだコラム回路を画素アレイの上下方向に配置する必要がある。たとえば、コラム回路を画素アレイの上下に配置することで、コラム回路の横幅を画素ピッチの2倍とすることができる。しかしながら、たとえば画素サイズが5 μ m なら、それでもその2倍の1 0 μ m にA D C などの回路を収めなければなら50

ない。

**【0010】**

このため、列ごとに幅  $10 \mu m$ 、高さ  $1 mm$  以上といった非常に細長いコラム回路を配置しなければならない。このように、ADC の設計には、非常に大きな制約があるといった問題がある。

**【0011】**

また、このような制約のもと、固体撮像装置に設けられる ADC による AD 变換のさらなる高速化が求められている。

**【0012】**

本発明は、上記問題点を解決するためになされたものであり、その一実施例の目的は、

限られたスペースに配置することが可能な ADC を含んだ固定撮像装置を提供することである。

10

**【0013】**

他の目的は、AD 变換を高速に行なうことが可能な ADC を含んだ固体撮像装置を提供することである。

**【課題を解決するための手段】**

**【0014】**

本発明の一実施例によれば、固体撮像装置が提供される。垂直読出線を介して出力された画素の信号がノードに電位として保持される。複数のコンデンサが、画素の信号が保持されるノードと容量結合されている。トランジスタを制御して複数のコンデンサの対極の電圧を順次切替えることにより、ノードの電位を階段状に下降させる。比較器は、ノードの電位と画素の暗状態における電位とを比較しており、ノードの電位の方が低くなったときにデジタル値の上位ビットを決定する。それに続いて、デジタル値の下位ビットの変換が開始される。

20

**【発明の効果】**

**【0015】**

この実施例によれば、ADC の構成を簡略化することができ、限られたスペースに ADC を配置することが可能となる。

**【図面の簡単な説明】**

**【0016】**

30

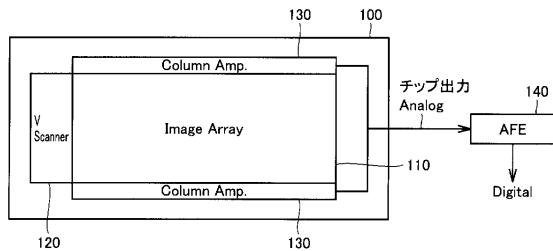

【図1】アナログイメージセンサの構成例を示す図である。

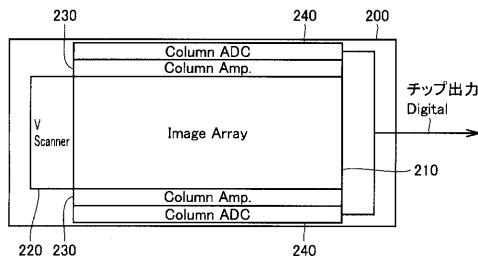

【図2】デジタルイメージセンサの構成例を示す図である。

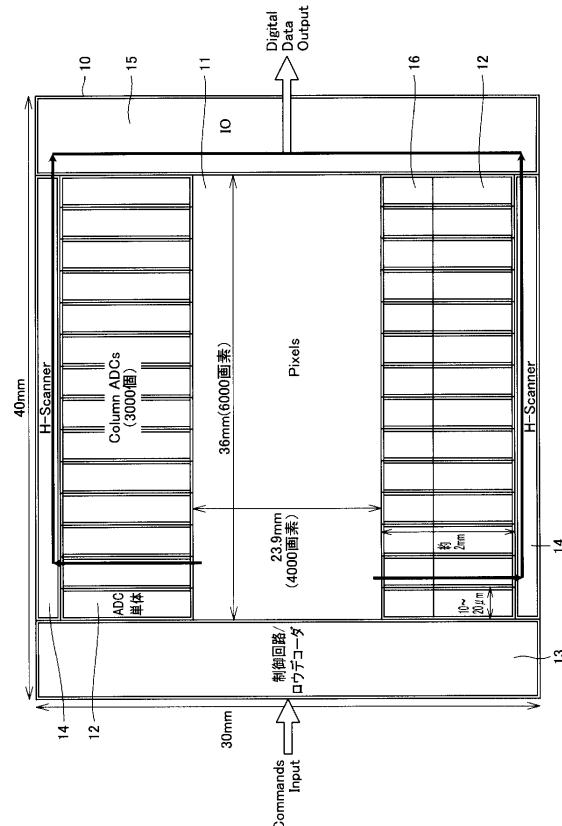

【図3】固体撮像装置の各部の配置例を示す図である。

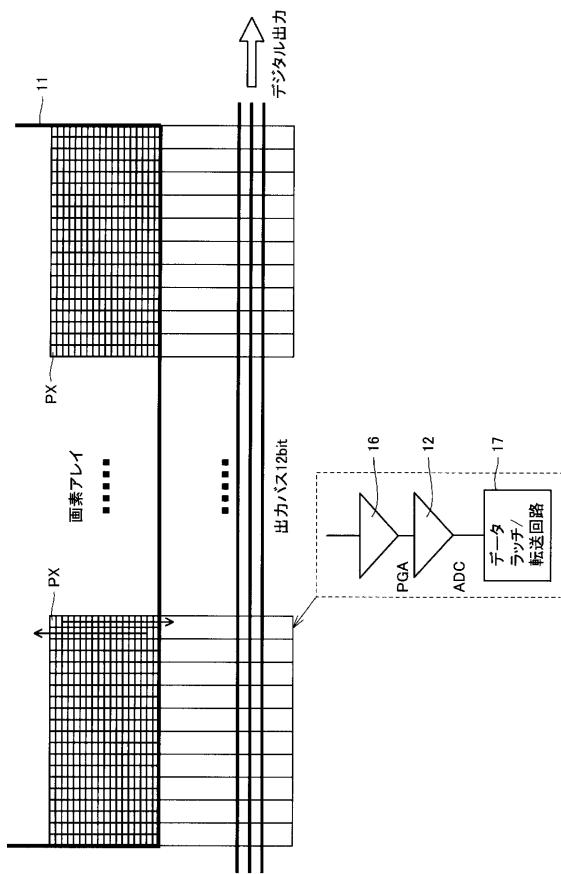

【図4】図3に示す固体撮像装置10の画素アレイ11およびコラム回路の部分を拡大した図である。

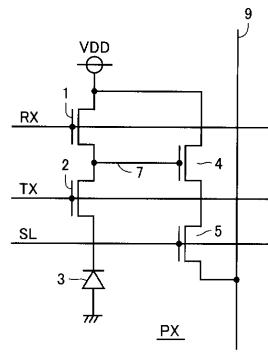

【図5】図4に示す画素PXの電気的等価回路を示す図である。

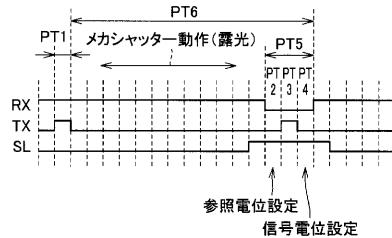

【図6】図5に示す画素PXの信号読出時の動作を説明するためのタイミングチャートである。

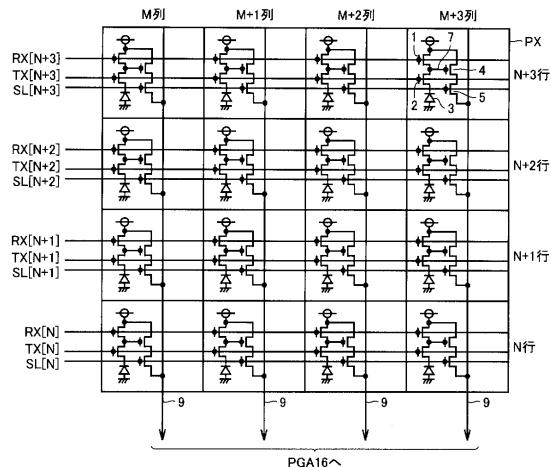

【図7】画素アレイ11の要部の構成を示す図である。

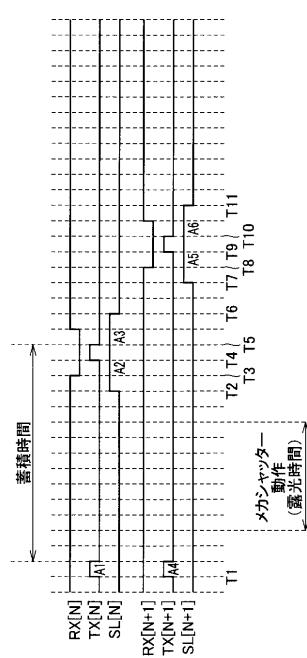

【図8】図7に示す画素アレイ11のデータ読出時の動作を示すタイミングチャートである。

40

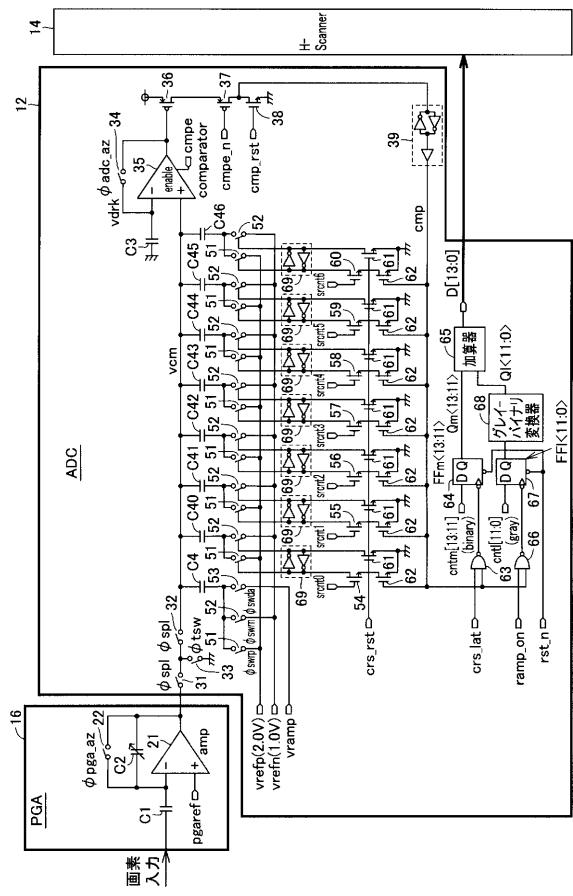

【図9】本発明の第1の実施の形態におけるADCおよびPGAの構成例を示す図である。

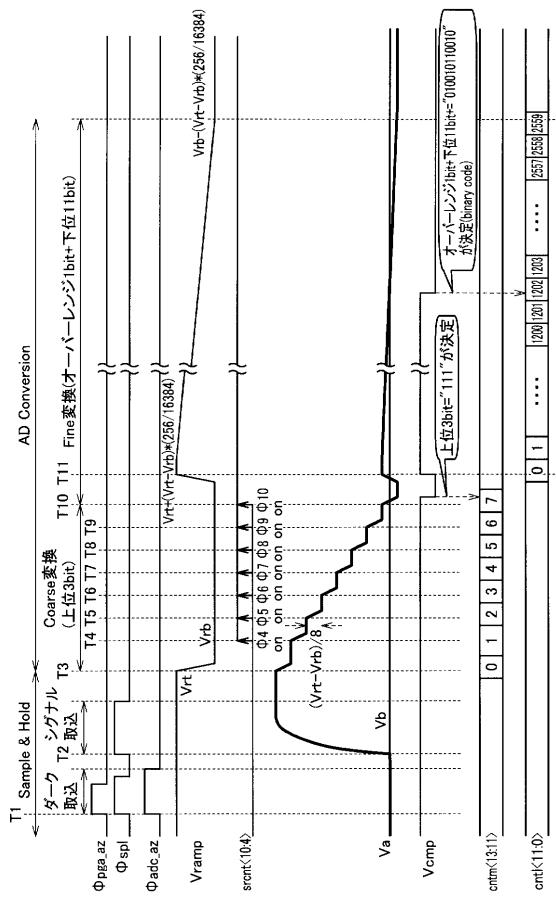

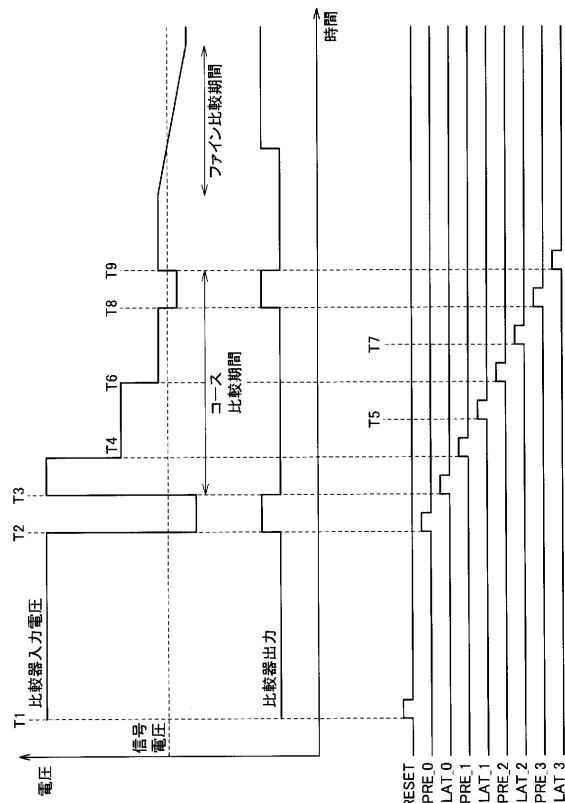

【図10】図9に示すADC12およびPGA16による画素信号の読み出し動作を説明するためのタイミングチャートである。

【図11】図10のタイミングチャートに示す動作をさらに詳細に説明するためのタイミングチャートである。

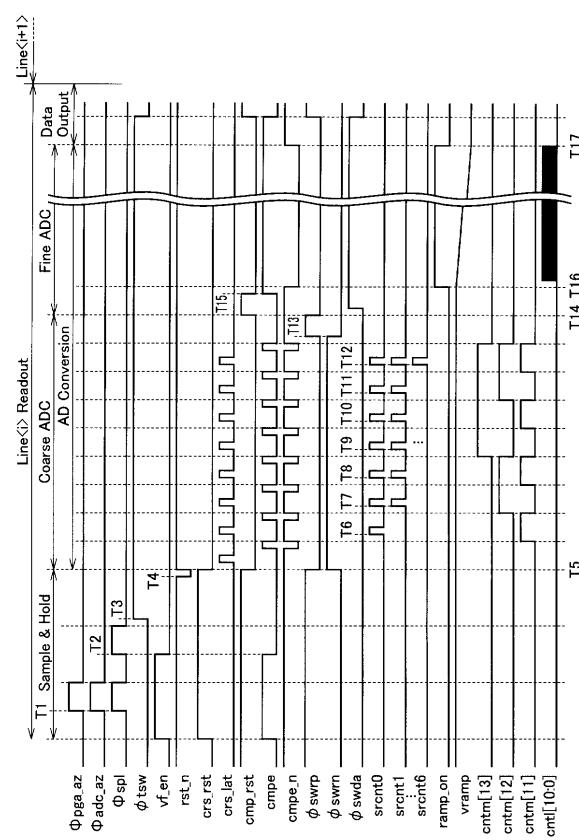

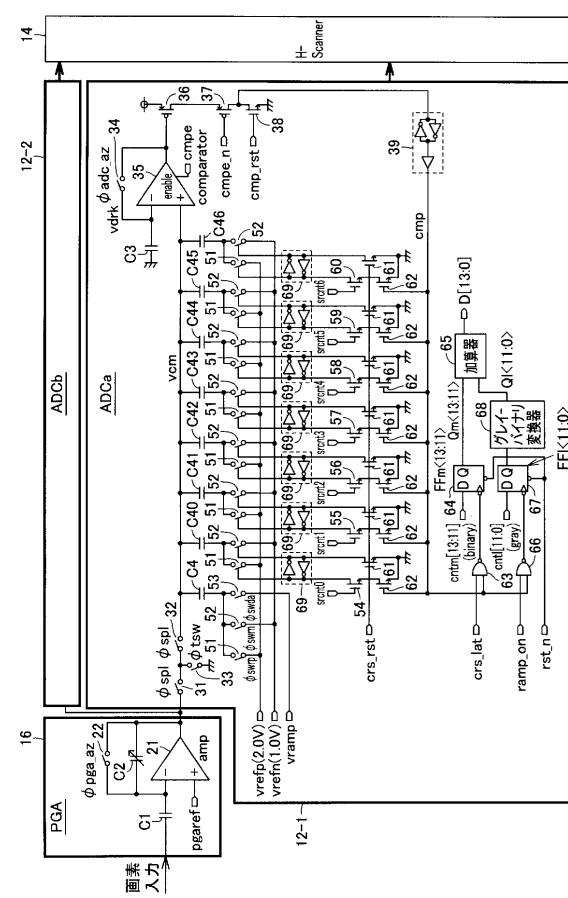

【図12】本発明の第2の実施の形態におけるADCおよびPGAの構成例を示す図である。

【図13】第1の実施の形態の固体撮像装置における画素情報の読み出し動作（非インタ

50

ーリープ方式)の各ステージのタイミングを説明するための図である。

【図14】第2の実施の形態の固体撮像装置における画素情報の読み出し動作(インターリープ方式)の各ステージのタイミングを説明するための図である。

【図15】本発明の第3の実施の形態の固体撮像装置における画素情報の読み出し動作(パイプライン方式)の各ステージのタイミングの一例を説明するための図である。

【図16】本発明の第3の実施の形態の固体撮像装置における画素情報の読み出し動作(パイプライン方式)の各ステージのタイミングの他の一例を説明するための図である。

【図17】積分型ADCの構成例とその動作を説明するための図である。

【図18】サブレンジ方式のADCの構成例とその動作を説明するための図である。

【図19】本発明の第4の実施の形態におけるADCの構成例を示す図である。 10

【図20】図19に示す第4の実施の形態におけるADCの構成をさらに詳細に説明するための図である。

【図21】本発明の第4の実施の形態におけるADCの動作を説明するためのタイミングチャートである。

【図22】本発明の第5の実施の形態におけるADCの構成例を示す図である。

【図23】図22に示す第5の実施の形態におけるADCの構成をさらに詳細に説明するための図である。

【図24】本発明の第5の実施の形態におけるADCの動作を説明するためのタイミングチャートである。

#### 【発明を実施するための形態】

##### 【0017】

本発明の実施の形態における固体撮像装置の詳細を説明する前に、その背景となる技術について説明する。

##### 【0018】

図1は、アナログイメージセンサの構成例を示す図である。このイメージセンサ100は、画素アレイ(Image Array)110と、垂直方向(列方向)に画素の走査を行なうV-Scanner120と、列(コラム)ごとに配置されるコラムアンプ(Column Amp.)130とを含む。

##### 【0019】

コラムアンプ130は、V-Scanner120による走査によって順次送られてくる画素の信号を増幅し、そのアナログ信号をチップ外に配置されたAFE(Analog Front End)140に出力する。AFE140は、イメージセンサ100から出力されたアナログ信号をデジタル信号に変換して出力する。 30

##### 【0020】

このようなアナログイメージセンサ100においては、オフチップAFE140の処理によって、全画素の出力に対して均一な特性が得られるといった利点がある。その反面、アナログ信号の転送速度には限界があり、動画などの高フレームレートの処理には向きである、別途AFE設計が必要であるといった欠点がある。

##### 【0021】

図2は、デジタルイメージセンサの構成例を示す図である。このイメージセンサ200は、画素アレイ(Image Array)210と、垂直方向に画素の走査を行なうV-Scanner220と、列(コラム)ごとに配置されるコラムアンプ(Column Amp.)230と、コラムアンプ230から出力されるアナログ信号をデジタル信号に変換するコラムADC(Column ADC)240とを含む。 40

##### 【0022】

コラムアンプ230は、V-Scanner220による走査によって順次送られてくる画素の信号を増幅してコラムADC240に出力する。コラムADC240は、コラムアンプ230から出力されたアナログ信号をデジタル信号に変換してチップ外部に出力する。

##### 【0023】

10

20

30

40

50

このようなデジタルイメージセンサにおいては、デジタル転送のため高速化が可能であり、既存の L V D S ( Low Voltage Differential Signaling ) などのデータ出力 I / F ( Interface ) を流用可能であるといった利点がある。また、コラム A D C 2 4 0 がコラムアンプ 2 3 0 に直結されるため低ノイズ、高精度設計が可能であるといった利点もあり、アナログイメージセンサであれば 1 2 ビット精度 ( 2 5 0  $\mu$  V ) のところを 1 4 ビット精度 ( 6 0  $\mu$  V ) にすることができる。その反面、コラム A D C ごとの特性ばらつきが発生するといった欠点がある。ただし、線形性 F P N ( Fixed Pattern Noise ) はデジタル補正が可能である。

#### 【 0 0 2 4 】

図 3 は、固体撮像装置の各部の配置例を示す図である。この固体撮像装置 1 0 は、画素アレイ 1 1 と、画素の列ごとに配置されたコラム A D C 1 2 および P G A ( Programmable Gain Amplifier ) 1 6 と、固体撮像装置 1 0 の全体的な制御および画素アレイ 1 1 の行方向の選択処理を行なう制御回路 / ロウデコーダ 1 3 と、コラム A D C 1 2 から出力されるデジタル信号を水平方向に転送する H - S c a n n e r 1 4 と、H - S c a n n e r 1 4 によって転送されたデジタル信号をチップ外部に出力する I O ( Input Output ) 部 1 5 とを含む。10

#### 【 0 0 2 5 】

この固体撮像装置 1 0 の幅は 4 0 m m 程度であり、そのうち 3 6 m m の幅に水平方向の 6 0 0 0 画素分のセンサが配置されている。また固定撮像装置 1 0 の高さは 3 0 m m 程度であり、そのうち 2 3 . 9 m m の高さに垂直方向の 4 0 0 0 画素分のセンサが配置されている。20

#### 【 0 0 2 6 】

コラム A D C 1 2 は、画素アレイ 1 1 の上下に配置されており、2 列の画素の幅に 1 つ のコラム A D C 1 2 が配置される構成となっている。したがって、コラム A D C 1 2 は、画素アレイ 1 1 を挟んで上下に各 3 0 0 0 個が配置される。

#### 【 0 0 2 7 】

このコラム A D C 1 2 および P G A 1 6 の横幅は画素ピッチの 2 倍であるため、1 0 ~ 2 0  $\mu$  m 程度の幅となる。また、コラム A D C 1 2 と P G A 1 6 との高さの和は 2 m m 程度であるため、非常に細長い形状となってしまう。この制約のもとでコラム A D C 1 2 を設計しなければならないため、小面積で簡単な回路構成であり、省電力化が可能であることが必須となる。30

#### 【 0 0 2 8 】

図 4 は、図 3 に示す固体撮像装置 1 0 の画素アレイ 1 1 およびコラム回路の部分を拡大した図である。画素アレイ 1 1 の画素 P X の 2 列に対して 1 個のコラム回路が設けられており、それぞれのコラム回路は、A D C 1 2 と、P G A ( Programmable Gain Amplifier ) 1 6 と、データラッチ / 転送回路 1 7 とを含む。

#### 【 0 0 2 9 】

P G A 1 6 は、列方向の画素 P X から順次送られてくる画素出力を增幅して A D C 1 2 に出力する。A D C 1 2 は、P G A 1 6 から受けたアナログ信号をデジタル信号に変換してデータラッチ / 転送回路 1 7 に出力する。データラッチ / 転送回路 1 7 は、行方向の画素出力のデジタル値を順次シフトし、3 0 0 0 画素分のデジタル信号を外部に出力する。なお、画素アレイ 1 1 の上部にも同様の回路が配置される。40

#### 【 0 0 3 0 】

図 5 は、図 4 に示す画素 P X の電気的等価回路を示す図である。画素 P X は、光信号を電気信号に変換するフォトダイオード 3 と、転送制御線上の転送制御信号 T X に従ってフォトダイオード 3 によって生成された電気信号を伝達する転送トランジスタ 2 と、リセット制御線上のリセット制御信号 R X に従ってフローティングディフュージョン 7 を所定の電圧レベルにリセットするリセットトランジスタ 1 とを含む。

#### 【 0 0 3 1 】

さらに、フローティングディフュージョン 7 上の信号電位に従って電源ノード上の電源50

電圧 VDD をソースフォロアモードで伝達するソースフォロアトランジスタ 4 と、行選択制御線上の行選択信号 SL に従ってソースフォロアトランジスタ 4 により伝達された信号を垂直読出線 9 上に伝達する行選択トランジスタ 5 とを含む。トランジスタ 1, 2, 4 および 5 は、一例として、N チャネル MOS トランジスタで構成される。したがって、この画素 PX は CMOS イメージセンサの画素である。

#### 【0032】

図 6 は、図 5 に示す画素 PX の信号読出時の動作を説明するためのタイミングチャートである。以下、図 6 を参照して、図 5 に示す画素 PX の信号読出動作について説明する。

#### 【0033】

期間 PT1において、リセット制御信号 RX がハイレベル（以下、H レベルと略す。）10 の状態で、転送制御信号 TX が H レベルに設定される。リセットトランジスタ 1 および転送トランジスタ 2 がともにオン状態となり、フォトダイオード 3 により変換された電気信号が初期化される。すなわち、フォトダイオード 3 において、先のサイクルにおいて光電変換により蓄積された電荷が放出される。

#### 【0034】

転送制御信号 TX がロウレベル（以下、L レベルと略す。）となり、転送トランジスタ 2 がオフ状態となると、フォトダイオード 3 における光電変換動作が再び行なわれ、信号電荷が蓄積される。この状態において、リセット制御信号 RX は H レベルを維持し、リセットトランジスタ 1 はオン状態を維持する。リセット制御信号 RX が電源電圧 VDD レベルのとき、フローティングディフィュージョン 7 は、電源電圧 VDD から、このリセットトランジスタ 1 のしきい値電圧分低い電圧レベルに維持される。20

#### 【0035】

次いで、まず行選択信号 SL が H レベルとなり、行選択トランジスタ 5 が導通し、ソースフォロアトランジスタ 4 によるソースフォロア動作により、このフローティングディフィュージョン 7 上の電位に応じた電位の信号が垂直読出線 9 上に伝達される。この後、画素読出期間 PT5 が開始される。

#### 【0036】

画素読出期間 PT5においては、まず、期間 PT2において、リセット制御信号 RX が L レベルとなり、リセットトランジスタ 1 がオフ状態となる。フローティングディフィュージョン 7 上の信号電位に応じた信号が、垂直読出線 9 上に伝達され、図示しない読出回路に含まれる参照用の容量素子が充電される。この期間 PT2において、画素 PX の信号の参照電位の設定が行なわれる。これは、後述する画素の暗状態の情報のサンプリングに相当する。30

#### 【0037】

次いで、期間 PT3において、転送制御信号 TX が H レベルとなり、転送トランジスタ 2 が導通し、フォトダイオード 3 により光電変換されて蓄積された電荷が、フローティングディフィュージョン 7 へ伝達される。これに応じて、垂直読出線 9 の電位が画素からの電荷に応じた電位に変化する。転送制御信号 TX が L レベルとなると、垂直読出線 9 上の電位に従って、図示しない読出回路に含まれる信号電荷蓄積容量素子が期間 PT4において充電される。これは、後述する画素の明状態の情報のサンプリングに相当する。40

#### 【0038】

次いで、期間 PT2 および PT4においてそれぞれ読出された参照電位および信号電位が差動増幅されて、画素 PX の信号（画素信号）が読出される。

#### 【0039】

1 つの画素に対して 2 回サンプリングを行ない、初期電位および信号電位を比較することにより、いわゆる相関二重サンプリング動作を行なって、画素 PX におけるノイズの影響を相殺し、フォトダイオード 3 により生成された電気信号を読出す。

#### 【0040】

画素 PX の信号の読出が完了すると、次いで行選択信号 SL が L レベルとなり、行選択トランジスタ 5 がオフ状態となる。50

**【 0 0 4 1 】**

画素  $P_X$  は行列状に配列されており、1行の画素について、並列に、画素信号の読み出が行なわれる。画素  $P_X$  においては、リセット期間  $PT_1$  の完了後、この読み出期間  $PT_5$  が完了するまでの期間  $PT_6$  の間、フォトダイオード 3 においては、光信号を電気信号に変換して、信号電荷を生成する。

**【 0 0 4 2 】**

図 5 に示すように、画素  $P_X$  は、フォトダイオード 3 と、N チャネル MOS トランジスタで構成されており、垂直読み出線 9 上には、行選択トランジスタ 5 を介して画素信号が読み出される。したがって、CCD イメージセンサと異なり、この行選択トランジスタ 5 および垂直読み出線 9 の選択順序はランダムに設定することができる。

10

**【 0 0 4 3 】**

図 7 は、画素アレイ 11 の要部の構成を示す図である。図 7 においては、第 N 行から第  $(N + 3)$  行および第 M 列から第  $(M + 3)$  列の 4 行 4 列に配列される画素  $P_X$  を代表的に示す。画素  $P_X$  は、図 5 に示す画素  $P_X$  と同一の構成を有する。

**【 0 0 4 4 】**

画素  $P_X$  が行列状に配列されており、各行それぞれごとに、リセット制御信号  $R_X[i]$ 、転送制御信号  $T_X[i]$  および行選択制御信号  $S_L[i]$  の組が与えられる。ここで、 $i$  は N から  $N + 3$  のいずれかである。画素列それぞれに対応して、垂直読み出線 9 が配置される。

**【 0 0 4 5 】**

20

図 8 は、図 7 に示す画素アレイ 11 のデータ読み出時の動作を示すタイミングチャートである。以下、図 8 を参照して、図 7 に示す画素アレイ 11 の画素信号読み出動作について説明する。

**【 0 0 4 6 】**

時刻  $T_1$  において、第 N 行および第  $(N + 1)$  行に対する転送制御信号  $T_X[N]$  および  $T_X[N + 1]$  が H レベルへ駆動される。リセット制御信号  $R_X[N]$  および  $R_X[N + 1]$  は H レベルであり、リセットトランジスタ 1 はオン状態にある。時刻  $T_1$  から始まる期間  $A_1$  および  $A_4$  において、第 N 行および第  $(N + 1)$  行において、フォトダイオード 3 の蓄積電荷の放出が行なわれ、これに応じて、これらの第 N 行および第  $(N + 1)$  行において、図 5 に示すフローティングディフュージョン 7 が、所定の初期電圧レベルにリセットされる。

30

**【 0 0 4 7 】**

所定時間が経過すると、時刻  $T_2$  において、第 N 行に対する行選択信号  $S_L[N]$  が H レベルに立上がる。これにより、第 N 行において、画素  $P_X$  内の行選択トランジスタ 5 がオン状態となり、対応の垂直読み出線 9 にソースフォロアトランジスタ 4 が結合される。

**【 0 0 4 8 】**

次いで、リセット制御信号  $R_X[N]$  が L レベルに立下がり、第 N 行において各画素内においてリセットトランジスタ 1 がオフ状態となり、フローティングディフュージョン 7 がリセット電位レベルに維持される。

**【 0 0 4 9 】**

40

時刻  $T_4$  において、転送制御信号  $T_X[N]$  が H レベルとなり、第 N 行の画素において転送トランジスタ 2 がオン状態となり、フォトダイオード 3 により生成された信号電荷が、フローティングディフュージョン 7 に伝達される。このとき、行選択信号  $S_L[N]$  が H レベルであり、各垂直読み出線 9 に、このフローティングディフュージョン 7 の電位に従って画素信号が読み出される。

**【 0 0 5 0 】**

この第 N 行の画素の読み出動作完了後、リセット制御信号  $R_X[N]$  が H レベルとなり、再びフローティングディフュージョン 7 が、初期電圧レベルにリセットトランジスタ 1 を介して充電される。

**【 0 0 5 1 】**

50

時刻 T 6において、行選択信号 S L [ N ] が L レベルとなり、行選択トランジスタ 5 がオフ状態となり、その第 N 行の画素の信号電荷の読出が完了する。

#### 【 0 0 5 2 】

次いで、第 ( N + 1 ) 行の画素の信号の読出が行なわれる。すなわち、時刻 T 7 において、行選択信号 S L [ N + 1 ] が H レベルに立上がり、この第 ( N + 1 ) 行の画素 P X のソースフォロアトランジスタが、対応の垂直読出線 9 に結合される。

#### 【 0 0 5 3 】

次いで時刻 T 8 において、リセット制御信号 R X [ N + 1 ] が L レベルとなり、フローティングディフュージョン 7 に対する追加動作が完了する。

#### 【 0 0 5 4 】

時刻 T 9 において、転送制御信号 T X [ N + 1 ] が H レベルとなり、フォトダイオード 3 の生成した信号電荷に従ってフローティングディフュージョン 7 の電位が変化し、この電位に従って画素信号が垂直読出線 9 上に読出される。

#### 【 0 0 5 5 】

時刻 T 11 において、行選択信号 S L [ N + 1 ] が L レベルに立下がり、第 N 行および第 ( N + 1 ) 行の画素に対する読出が完了する。以上の動作を繰り返すことにより、列方向の画素の情報が順次 P G A 16 に出力される。

#### 【 0 0 5 6 】

##### ( 第 1 の実施の形態 )

図 9 は、本発明の第 1 の実施の形態における A D C および P G A の構成例を示す図である。 P G A 16 は、差動増幅器 ( a m p ) 21 と、スイッチ 22 と、コンデンサ C 1 と、可変コンデンサ C 2 とを含む。差動増幅器 21 の正入力にはリファレンス電圧 p g a r e f が接続され、負入力にはコンデンサ C 1 を介して画素入力信号が接続される。差動増幅器 21 の出力は、負帰還用の可変コンデンサ C 2 およびスイッチ 22 に接続されると共に、 A D C 12 内のスイッチ 31 に接続される。また、可変コンデンサ C 2 によって P G A 16 のゲインを変更可能である。

#### 【 0 0 5 7 】

A D C 12 は、スイッチ 31 ~ 34 および 51 ~ 53 と、比較器 ( c o m p a r a t o r ) 35 と、 P チャネル M O S トランジスタ 36 および 37 と、 N チャネル M O S トランジスタ 38 および 54 ~ 62 と、保持回路 39 および 69 と、 N A N D 回路 63 および 66 と、フリップフロップ ( F F ) 64 および 67 と、加算器 65 と、グレイ - バイナリ変換器 68 と、コンデンサ C 3 ~ C 4 および C 40 ~ C 46 とを含む。

#### 【 0 0 5 8 】

比較器 35 の正入力には、 P G A 16 から出力される増幅された画素入力がスイッチ 31 および 32 を介して接続される。また、比較器 35 の負入力には、比較器 35 の出力がスイッチ 34 を介して接続されると共に、画素の暗状態の情報を保持するコンデンサ C 3 が接続される。

#### 【 0 0 5 9 】

F F 64 は、図示しない 3 ビットカウンタの出力値を保持するものであり、比較器 35 の正入力と負入力とが一致し、 c o a r s e ラッチ信号 c r s \_ l a t が H レベルに変化するときにカウンタの出力値 c n t m < 13 : 11 > を保持して加算器 65 に出力する。この 3 ビットのカウンタの出力値は、 A D 変換後のデジタル値の上位 3 ビットに相当し、バイナリコードである。なお、図示しない 3 ビットカウンタは図 3 に示す制御回路 / ロウデコーダ 13 内に設けられる。

#### 【 0 0 6 0 】

F F 67 は、図示しない 12 ビットカウンタの出力値を保持するものであり、比較器 35 の正入力と負入力とが一致し、 r a m p \_ o n 信号が H レベルのときにカウンタの出力値 c n t l < 11 : 0 > を保持して出力する。この 12 ビットのカウンタの出力値は 1 ビットのオーバレンジを含んでおり、 A D 変換後のデジタル値の下位 11 ビットに相当し、グレイコードである。なお、図示しない 12 ビットカウンタは図 3 に示す制御回路 / ロウ

10

20

30

40

50

デコーダ13内に設けられる。

【0061】

グレイ・バイナリ変換器68は、FF67から出力される12ビットのグレイコードをバイナリコードQ<sub>1<11:0></sub>に変換して、加算器65に出力する。

【0062】

加算器65は、FF64から出力される3ビットのQ<sub>m<13:11></sub>と、FF67から出力される12ビットのQ<sub>1<11:0></sub>とを加算し、H-scanner14に出力する。

【0063】

コンデンサC4およびC40～C46は等しい電気容量を有しており、vcmと容量結合されている。これらのコンデンサに接続されるスイッチ51～53を順次切替えることにより、コンデンサC4およびC40～C46の対極をVrtからVrbに順次切替えて、vcmの電位が8つのレンジのどこに属するかを判定する。また、トランジスタ54～62は、スイッチ51および52の切替えを制御するものであるが、動作の詳細については後述する。

10

【0064】

なお、図9に示すspl、tsw、adc\_az、cmpe、cmpe\_n、cmp\_rst、swrp、swrn、swda、srcnt0～srcnt6、vrefp、vrefn、vramp、crs\_rst、crs\_lat、ramp\_on、rst\_nなどの信号は、図3に示す制御回路／ロウデコーダ13によって生成される信号であり、上下各3000個のコラムADC12に共通に与えられる。

20

【0065】

図10は、図9に示すADC12およびPGA16による画素信号の読み出し動作を説明するためのタイミングチャートである。この読み出し動作は、サンプル&ホールド(Sample & Hold)、AD変換(AD Conversion)およびデータ出力(Data Output)の3ステージによって構成され、i行の画素情報の読み出し動作を示している。また、AD変換ステージは、Coarse AD変換ステージおよびFine AD変換ステージの2段階に分けられる。

【0066】

まず、時刻T1においてサンプル&ホールドステージが開始され、PGAオートゼロ信号pgaaaz、ADCオートゼロ信号adc\_az、およびサンプリング信号splがHレベルになると、スイッチ31, 32および34がオン状態になる。このとき、ノードvcmには画素の暗状態の情報がサンプリングされて保持される。比較器35は、コンデンサC3の正極電位(vdrk)に画素の暗状態の情報を電位として保持させる。

30

【0067】

そして、時刻T2において、再度spl信号がHレベルになると、PGA16から出力される画素の明状態の情報がノードvcmに電位としてサンプリングされて保持される。このとき、vf\_en信号およびcmpe信号がLレベルとなる。vf\_en信号は、比較器35をオペアンプとして動作させるか、コンパレータとして動作させるかを選択するための信号であり、vf\_en信号がHレベルのときにオペアンプとして動作させ、Lレベルのときにコンパレータとして動作させる。また、cmpe信号は、Hレベルのときに比較器35の出力をイネーブルとする信号である。

40

【0068】

時刻T3において、tsw信号がLレベルからHレベルに変化し、スイッチ33をオン状態にすることによりPGA16の出力を初期化する。そして、時刻T4において、rst\_n信号がLレベルになると、FF64および67がクリアされる。

【0069】

そして、時刻T5において、Coarse AD変換ステージが開始され、swrp信号がHレベルからLレベルに変化すると共に、swrn信号がLレベルからHレベルに変化することにより、コンデンサC4に接続されるスイッチ51がオン状態からオフ状

50

態に変化すると共にスイッチ 5 2 がオフ状態からオン状態に変化する。その結果、 $v_{cm}$  と容量結合されたコンデンサ C 4 の対極が  $v_{refp} (2.0V)$  から  $v_{refn} (1.0V)$  に変化する。このとき、 $v_{cm}$  の電位が  $(V_{rt} - V_{rb}) / 8$  だけ下降する。

#### 【0070】

また、 $crs\_rst$  信号が H レベルから L レベルに変化するが、保持回路 6 9 のそれぞれの右側端子が L レベルを保持し、左側端子が H レベルを保持しており、コンデンサ C 4 0 ~ 4 6 の夫々に接続されるトランジスタ 5 1 がオン状態を維持し、トランジスタ 5 2 がオフ状態を維持する。

#### 【0071】

時刻 T 5 以降、上位 3 ビットカウンタの出力  $cntm [13 : 11]$  の変化に同期して 10

、 $crs\_lat$  信号、 $cmp_e$  信号および  $cmp_e_n$  信号のそれぞれに 8 パルスが出力される。

#### 【0072】

時刻 T 6 において、 $sreqnt0$  信号が L レベルから H レベルに変化すると、トランジスタ 5 4 がオン状態となる。このとき、トランジスタ 6 2 はオン状態となっているため、コンデンサ C 4 0 に接続されるスイッチ 5 1 がオフ状態となり、スイッチ 5 2 がオン状態となる。その結果、 $v_{cm}$  と容量結合されたコンデンサ C 4 0 の対極が  $v_{refp} (2.0V)$  から  $v_{refn} (1.0V)$  に変化し、 $v_{cm}$  の電位がさらに  $(V_{rt} - V_{rb}) / 8$  だけ下降する。

#### 【0073】

時刻 T 7 において、さらに  $sreqnt1$  信号が L レベルから H レベルに変化すると、トランジスタ 5 5 がオン状態となる。このとき、トランジスタ 6 2 はオン状態となっているため、コンデンサ C 4 1 に接続されるスイッチ 5 1 がオフ状態となり、スイッチ 5 2 がオン状態となる。その結果、 $v_{cm}$  と容量結合されたコンデンサ C 4 1 の対極が  $v_{refp} (2.0V)$  から  $v_{refn} (1.0V)$  に変化し、 $v_{cm}$  の電位がさらに  $(V_{rt} - V_{rb}) / 8$  だけ下降する。

#### 【0074】

時刻 T 8 ~ T 12 において同様の動作が行なわれ、 $v_{cm}$  の電位を  $(V_{rt} - V_{rb}) / 8$  ずつ下降させる。そして、 $v_{cm}$  の電位が  $v_{drk}$  の電位よりも低くなると、比較器 3 5 は L レベルを出力する。このとき、トランジスタ 3 6 がオン状態となり、保持回路 3 9 は  $cmp$  信号を H レベルから L レベルに変化させる。FF 6 4 は、NAND 回路 6 3 から出力される信号の立ち上がりで 3 ビットカウンタの出力  $cntm <13 : 11>$  の値を保持する。

#### 【0075】

時刻 T 13 において、 $swrp$  信号が L レベルから H レベルに変化すると共に、 $swrn$  信号が H レベルから L レベルに変化することにより、コンデンサ C 4 に接続されるスイッチ 5 1 がオフ状態からオン状態に変化すると共にスイッチ 5 2 がオン状態からオフ状態に変化する。その結果、 $v_{cm}$  と容量結合されたコンデンサ C 4 の対極が  $v_{refn} (1.0V)$  から  $v_{refp} (2.0V)$  に変化する。

#### 【0076】

時刻 T 14 において、Fine AD 変換ステージが開始されると、 $cmp\_rst$  信号が H レベルになり、保持回路 3 9 が  $cmp$  信号を H レベルにする。そして、時刻 T 15 において、 $cmp\_rst$  信号を L レベルにし、 $cmp_e$  信号を H レベルにする。そして、時刻 T 16 において、 $cmp_e_n$  信号を L レベルにし、 $rampon$  信号を H レベルにする。

#### 【0077】

図 11 は、図 10 のタイミングチャートに示す動作をさらに詳細に説明するためのタイミングチャートである。まず、時刻 T 1 において、PGA オートゼロ信号  $pga\_az$ 、ADC オートゼロ信号  $adc\_az$ 、およびサンプリング信号  $spl$  が H レベルになると、比較器 3 5 は、コンデンサ C 3 の正極電位 ( $v_{drk}$ ) に画素の暗状態の情報を

10

20

30

40

50

電位として保持させる。

#### 【0078】

時刻 T 2において、再度 s p l 信号が H レベルになると、P G A 1 6 から出力される画素の明状態の情報がノード v c m に電位としてサンプリングされて保持される。図 1 1 においては、画素の暗状態の電位を V a 、画素の明状態の電位を V b としている。

#### 【0079】

時刻 T 3において、v c m と容量結合されたコンデンサ C 4 の対極が v r e f p ( 2 . 0 V ) から v r e f n ( 1 . 0 V ) に変化する。このとき、v c m の電位が ( V r t - V r b ) / 8 だけ下降する。また、3 ビットカウンタの出力値 c n t m < 1 3 : 1 1 > は、" 0 " となっている。

10

#### 【0080】

時刻 T 4において、v c m と容量結合されたコンデンサ C 4 0 の対極が v r e f p ( 2 . 0 V ) から v r e f n ( 1 . 0 V ) に変化する。このとき、v c m の電位がさらに ( V r t - V r b ) / 8 だけ下降する。また、3 ビットカウンタの出力値 c n t m < 1 3 : 1 1 > は、" 1 " となっている。

#### 【0081】

時刻 T 5 ~ T 9 において同様の動作が行なわれ、時刻 T 1 0 において v c m の電位がさらに ( V r t - V r b ) / 8 だけ下降したときに、v c m の電位 V b が v d r k の電位 V a よりも低くなり、保持回路 3 9 が c m p ( V c m p ) 信号に L レベルを出力する。このとき、3 ビットカウンタの出力 c n t m [ 1 3 : 1 1 ] の値 " 1 1 1 " が、A D 変換後のデジタル値の上位 3 ビットとして決定される。すなわち、この画素情報のデジタル値が、1 4 3 3 6 (= 2 0 4 8 × 7) 画素情報 1 6 3 8 3 (= 2 0 4 8 × 8 - 1) であることを示している。

20

#### 【0082】

また、時刻 T 1 0 以降において、F i n e A D 変換ステージが実施され、画素情報が上記範囲のいずれにあるかが判定される。時刻 T 1 1 において、s w d a を H レベルにしてスイッチ 5 3 をオン状態にすると共に、コンデンサ C 4 の対極電位である v r a m p を、V r t + ( V r t - V r b ) × ( 2 5 6 / 2 0 4 8 ) まで引き上げる。このとき、制御回路 / ロウデコーダ 1 3 内に設けられた 1 2 ビットカウンタが 1 0 進数換算で " 0 " からカウントアップを開始する。

30

#### 【0083】

それ以降、V r a m p の電位を V r b - ( V r t - V r b ) × ( 2 5 6 / 2 0 4 8 ) までスロープ状に引き下げる。コンデンサ C 4 の対極電位の下降終了時点で、1 2 ビットカウンタの値が 1 0 進数換算で " 2 5 5 9 " となる。

#### 【0084】

これにより、v c m の電位が、C o a r s e A D 変換ステージ終了時点よりも ( V r t - V r b ) × { 1 + ( 2 5 6 / 2 0 4 8 ) } × ( 1 / 8 ) だけ引き上げられる。そして、v c m の電位がスロープ状に下降し、C o a r s e A D 変換ステージ終了時点よりも ( V r t - V r b ) × { 1 - ( 2 5 6 / 2 0 4 8 ) } × ( 1 / 8 ) だけ引き下げられた状態に達する。

40

#### 【0085】

ノード v c m の電位が v d r k の電位よりも低くなると、比較器 3 5 は L レベルを出力する。このとき、トランジスタ 3 6 がオン状態となり、保持回路 3 9 は c m p 信号を H レベルから L レベルに変化させる。

#### 【0086】

F F 6 7 は、N A N D 回路 6 6 から出力される信号の立ち上がりで 1 2 ビットカウンタの出力 c n t l [ 1 1 : 0 ] の値を保持する。図 1 1 においては、F F 6 7 によって 1 0 進数換算で " 1 2 0 2 " が保持される。グレイ - バイナリ変換器 6 8 は、F F 6 7 から出力されるグレイコードを受け、バイナリコード Q 1 < 1 1 : 0 > に変換して加算器 6 5 に出力する。

50

## 【0087】

**C o a r s e A D** 変換ステージにおいてデジタル値の上位 3 ビットが確定し、**F i n e A D** 変換ステージにおいて 1 ビットのオーバレンジを含むデジタル値の下位 12 ビットが確定する。図 11においては、10 進数換算でそれぞれ“14336”および“1202”であるので、加算器 65 は、 $D < 13 : 0 > = Qm < 13 : 11 > + Q1 < 11 : 0 > - 256$  を演算することにより、10 進数換算で“15282”を出力する。

## 【0088】

以上説明したように、本実施の形態における固定撮像装置によれば、コンデンサ C3 の正極電位 (v d r k) に画素の暗状態の情報を電位として保持させることにより A D 変換を行なうようにしたので、個々の A D C の回路構成を簡略化することができ、限られたスペースに搭載することが可能となった。また、上述の回路構成とすることによって、消費電力を削減することが可能となった。またさらに、本実施の形態における固体撮像装置によれば、**C o a r s e A D** 変換ステージにおいて画素情報の上位ビットを決定し、**F i n e A D** 変換ステージにおいて画素情報の下位ビットを決定するようにしたので、A D 変換をさらに高速に行なうことが可能となった。10

## 【0089】

## (第 2 の実施の形態)

図 12 は、本発明の第 2 の実施の形態における A D C および P G A の構成例を示す図である。図 9 に示す第 1 の実施の形態における A D C および P G A の構成例と比較して、1 つの P G A に対して 2 つの A D C が設けられており、インターリープ方式で A D 変換を行なう点が異なる。したがって、重複する構成および機能の詳細な説明は繰り返さない。20

## 【0090】

制御回路 / ロウデコーダ 13 は、A D C a 12 - 1 用の制御信号と、A D C b 12 - 2 用の制御信号とを別々に生成する。すなわち、s p l、t s w、a d c \_ a z、c m p e、c m p e \_ n、c m p \_ r s t、s w r p、s w r n、s w d a、s r c n t 0 ~ s r c n t 6、v r e f p、v r e f n、v r a m p、c r s \_ r s t、c r s \_ l a t、r a m p \_ o n、r s t \_ nなどの信号が 2 組生成され、それぞれの制御信号群が A D C a 12 - 1 および A D C b 12 - 2 に与えられて別々のタイミングで動作することにより、インターリープが実現される。

## 【0091】

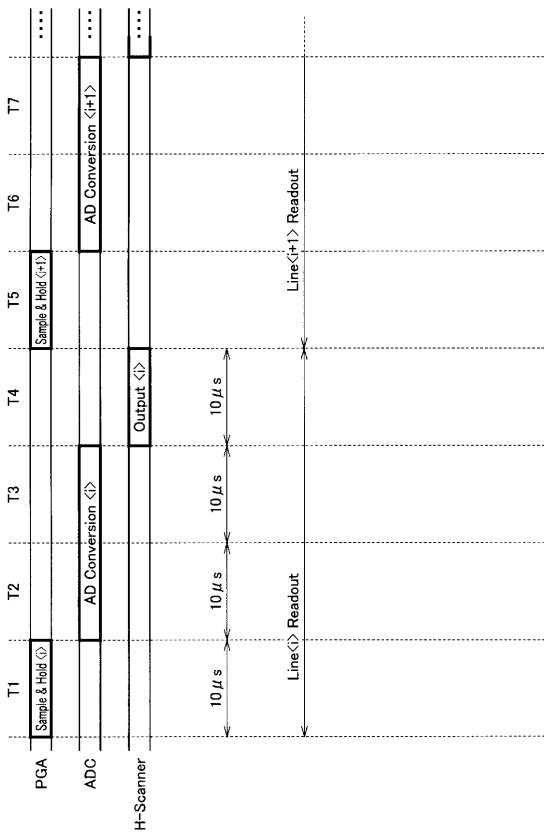

図 13 は、第 1 の実施の形態の固体撮像装置における画素情報の読み出し動作（非インターリープ方式）の各ステージのタイミングを説明するための図である。図 13 においては、サンプル & ホールドステージに要する時間を 10 μs、A D 変換ステージに要する時間を 20 μs、データ出力ステージに要する時間を 10 μs としている。

## 【0092】

期間 T1 において、P G A 16 が i 行の画素情報のサンプル & ホールドステージを実施する。期間 T2 ~ T3 において、A D C 12 が i 行の画素情報の A D 変換ステージを実施する。そして、T4 において、H - S c a n n e r 14 が i 行のデジタル変換された後の画素情報のデータ出力ステージを実施する。

## 【0093】

i 行の画素情報の読み出し動作が終了すると、期間 T5 ~ T8 において i + 1 行の画素情報の読み出し動作が実施される。図 13 に示すように、i 行の画素の読み出し動作が終了した後に i + 1 行の画素情報の読み出し動作が行なわれるため、1 行の読み出し動作に 40 μs を要する。フレームレートにすると、6 . 3 フレーム / s となる。40

## 【0094】

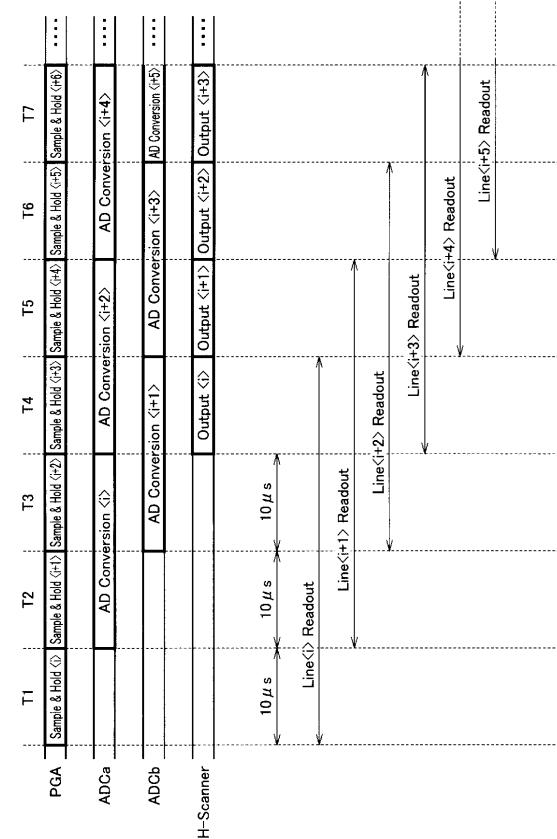

図 14 は、第 2 の実施の形態の固体撮像装置における画素情報の読み出し動作（インターリープ方式）の各ステージのタイミングを説明するための図である。図 14 においても、サンプル & ホールドステージに要する時間を 10 μs、A D 変換ステージに要する時間を 20 μs、データ出力ステージに要する時間を 10 μs としている。

## 【0095】

10

20

30

40

50

期間T1において、PGA16がi行の画素情報のサンプル&ホールドステージを実施する。期間T2～T3において、ADCa12-1がi行の画素情報のAD変換ステージを実施する。これと並行して、期間T2において、PGA16がi+1行の画素情報のサンプル&ホールドステージを実施する。また、期間T3において、PGA16がi+2行の画素情報のサンプル&ホールドステージを実施すると共に、ADCb12-2がi+1行の画素情報のAD変換ステージを開始する。

#### 【0096】

期間T4において、PGA16がi+3行の画素情報のサンプル&ホールドステージを実施する。このとき、ADCa12-1がi+2行の画素情報のAD変換ステージを開始する。また、ADCb12-2はi+1行の画素情報のAD変換ステージを継続して実施している。また、H-Scanner14がi行の画素情報のデータ出力ステージを実施する。

10

#### 【0097】

このように、PGA16がサンプリングした画素情報を2つのADCに交互に出力することにより、見かけ上、1行の読み出し動作に要する時間は10μsとなる。フレームレートにすると、25フレーム/sという高フレームレートを実現できる。

#### 【0098】

以上説明したように、本実施の形態における固体撮像装置によれば、PGA16がサンプリングした画素情報を2つのADCに交互に出力し、2つのADCが並行してAD変換ステージを実施するようにしたので、第1の実施の形態において説明した効果に加えて、読み出し動作をさらに高速に行なうことができ、高フレームレートを実現することが可能となった。

20

#### 【0099】

##### (第3の実施の形態)

本発明の第3の実施の形態における固体撮像装置の構成は、第1の実施の形態において説明した固体撮像装置の構成と同様である。したがって、重複する構成および機能の詳細な説明は繰り返さない。

#### 【0100】

図13に示すように、各ステージが並行して実施されない場合には、1行の読み出し動作に40μsを要してしまう。本発明の第3の実施の形態の固体撮像装置においては、パイプライン方式を用いてAD変換を高速に行なうものである。

30

#### 【0101】

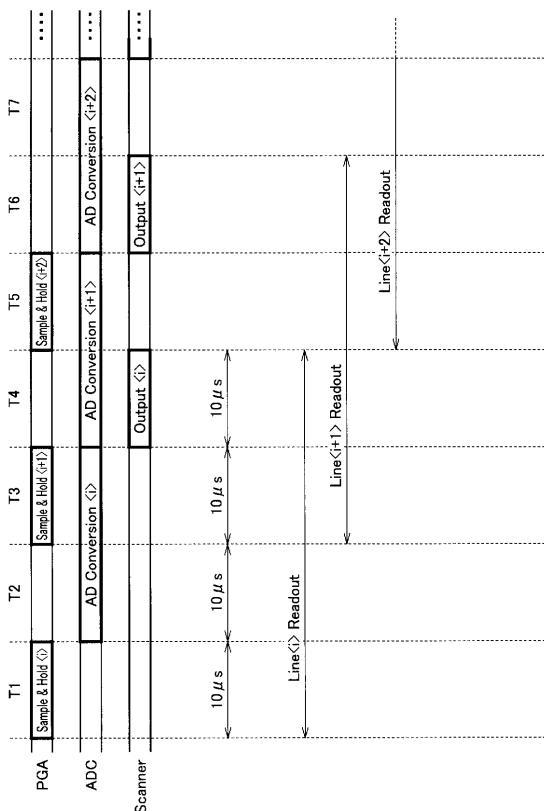

図15は、本発明の第3の実施の形態の固体撮像装置における画素情報の読み出し動作(パイプライン方式)の各ステージのタイミングの一例を説明するための図である。図15においても、サンプル&ホールドステージに要する時間を10μs、AD変換ステージに要する時間を20μs、データ出力ステージに要する時間を10μsとしている。

#### 【0102】

期間T1において、PGA16がi行の画素情報のサンプル&ホールドステージを実施する。期間T2～T3において、ADC12がi行の画素情報のAD変換ステージを実施する。これと並行して、期間T3において、PGA16がi+1行の画素情報のサンプル&ホールドステージを実施する。

40

#### 【0103】

期間T4～T5において、ADC12がi+1行の画素情報のAD変換ステージを実施する。これと並行して、期間T4において、H-Scanner14がi行のデジタル変換された後の画素情報のデータ出力ステージを実施する。また、期間T5において、PGA16がi+2行の画素情報のサンプル&ホールドステージを実施する。

#### 【0104】

このように、ADC12がある行の画素情報のAD変換ステージを実施しているときに、PGA16が次の行の画素情報のサンプル&ホールドステージを実施することにより、見かけ上、1行の読み出し動作に要する時間は20μsとなる。フレームレートにすると

50

、 12.5 フレーム / s という中フレームレートを実現できる。

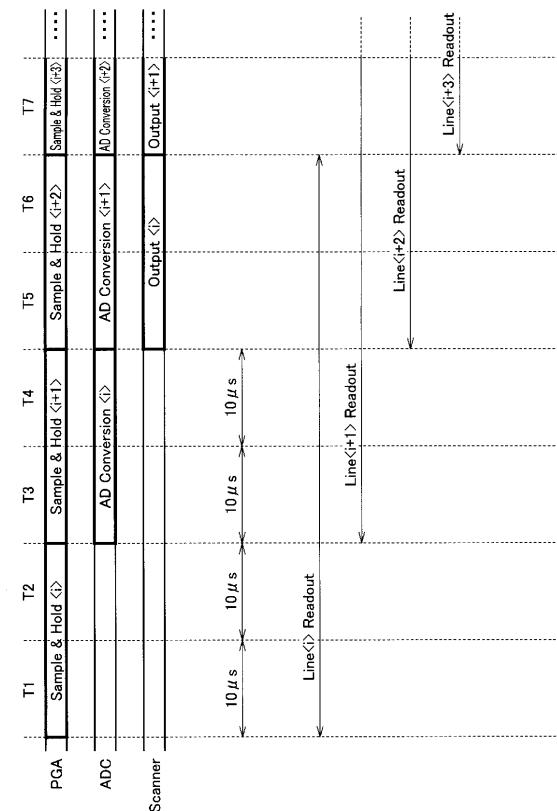

#### 【 0105 】

図 16 は、本発明の第 3 の実施の形態の固体撮像装置における画素情報の読み出し動作（パイプライン方式）の各ステージのタイミングの他の一例を説明するための図である。図 16 においては、サンプル & ホールドステージに要する時間、A D 変換ステージに要する時間、データ出力ステージに要する時間をすべて 20 μ s としている。

#### 【 0106 】

期間 T1 ~ T2 において、P G A 16 が i 行の画素情報のサンプル & ホールドステージを実施する。期間 T3 ~ T4 において、A D C 12 が i 行の画素情報の A D 変換ステージを実施する。これと並行して、期間 T3 ~ T4 において、P G A 16 が i + 1 行の画素情報のサンプル & ホールドステージを実施する。10

#### 【 0107 】

期間 T5 ~ T6 において、H - S c a n n e r 14 が i 行のデジタル変換された後の画素情報のデータ出力ステージを実施する。これと並行して、期間 T5 ~ T6 において、A D C 12 が i + 1 行の画素情報の A D 変換ステージを実施し、P G A 16 が i + 2 行の画素情報のサンプル & ホールドステージを実施する。

#### 【 0108 】

このように、A D C 12 がある行の画素情報の A D 変換ステージを実施しているときに、P G A 16 が次の行の画素情報のサンプル & ホールドステージを実施することにより、見かけ上、1 行の読み出し動作に要する時間は 20 μ s となる。フレームレートにすると、12.5 フレーム / s という中フレームレートを実現できる。これは、図 15 を用いて説明したパイプライン方式と同様である。20

#### 【 0109 】

図 15 を用いて説明したパイプライン方式と異なるのは、サンプル & ホールドステージおよびデータ出力ステージも 20 μ s としている点である。サンプル & ホールドステージを 10 μ s から 20 μ s に延長することにより、各画素に蓄積されている光電効果によって発生した電荷を十分に変換でき、図 15 に示すパイプライン方式よりも S / N 比を向上させることができる。

#### 【 0110 】

また、データ出力ステージを 10 μ s から 20 μ s に延長することにより、H - S c a n n e r 14 の基準クロック周波数を下げる事ができ、設計が容易に行なえるようになる。また、基準クロック周波数を下げる事により、H - S c a n n e r 14 で発生するノイズを低減することもできる。30

#### 【 0111 】

図 15 および図 16 に示すパイプライン方式を用いる場合、上述のようにフレームレートを高くすることができる。しかしながら、サンプル & ホールドステージ、A D 変換ステージ、およびデータ出力ステージの 3 ステージのうち 2 ステージ以上が常に同時に実行されるため、あるステージで発生するノイズが同時進行している他のステージに伝わってしまう可能性がある。このようなノイズによって、精度低下、最悪の場合には誤動作が引き起こされる可能性がある。40

#### 【 0112 】

ノイズ耐性は、回路方式、仕様、レイアウトなどによって異なるため、一概には論じられないが、図 13 に示すようなフレームレートは低下するがノイズを出し難い構成とするか、図 15 および図 16 に示すようなフレームレートは高くなるがノイズが発生しやすい構成とするかは、適宜選択されるべきであろう。

#### 【 0113 】

以上説明したように、本実施の形態における固体撮像装置によれば、A D C 12 がある行の画素情報の A D 変換ステージを実施しているときに、P G A 16 が次の行の画素情報のサンプル & ホールドステージを実施するようにしたので、第 1 の実施の形態において説明した効果に加えて、読み出し動作をさらに高速に行なうことができ、フレームレートを50

高くすることが可能となった。

**【0114】**

なお、各実施の形態においては、V<sub>ram p</sub>の電位をスロープ状に引き下げる方法を記載したが、V<sub>ram p</sub>の電位をスロープ状に引き上げるようにも同様の効果を得ることができる。つまり、V<sub>ram p</sub>の電位をスロープ状に変化させればよい。

**【0115】**

次に別観点の発明について説明する。上述の第1～第3の実施の形態についてさらに検討した結果、以下の課題が明らかとなつた。

**【0116】**

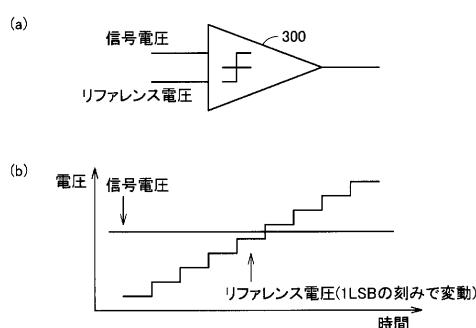

図17は、積分型ADCの構成例とその動作を説明するための図である。図17(a)に示すように、積分型ADCは比較器300によって構成され、画素の信号を信号電圧として受け、リファレンス電圧と比較することによりAD変換を行なう。10

**【0117】**

積分型ADCにおいては、初期設定時にカウンタの値をクリアした後、カウンタのカウントアップを開始する。図17(b)に示すように、リファレンス電圧を最小電圧または最大電圧から1 LSB(Least Significant Bit)ずつ変化させて、階段状に上昇または下降させる。そして、比較器300は、信号電圧とリファレンス電圧との比較を行ない、比較結果が反転したときのカウンタの値をデジタル値とする。積分型ADCにおいては、このような比較法をとるため、NをADC分解能とするとAD変換には $2^N$ (2のN乗)に比例した時間が必要になる。20

**【0118】**

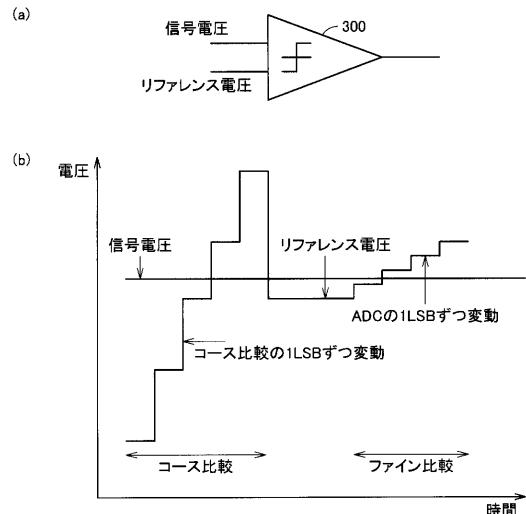

図18は、サブレンジ方式のADCの構成例とその動作を説明するための図である。図18(a)に示すように、サブレンジ方式のADCの構成は、図17(a)に示す積分型ADCの構成と同様である。

**【0119】**

サブレンジ方式においては、ADCの分解能であるNビットをコースビット(上位Mビット)とファインビット(下位(N-M)ビット)とに分割して、比較器300による比較が行なわれる。

**【0120】**

図18(b)に示すように、まずコース比較が行なわれるが、このときリファレンス電圧を最小電圧または最大電圧からコースビットの1 LSBずつ変化させる。図18(b)に示すように、コース比較においては、リファレンス電圧を粗く変化させながら、比較器300が信号電圧とリファレンス電圧との比較を行なう。そして、比較結果が反転したときにコースビットを決定する。30

**【0121】**

次に、ファイン比較が行なわれるが、このときリファレンス電圧をコース比較で決定したコースビットに相当する領域で電圧をADC(ファインビット)の1 LSBずつ変化させる。図18(b)に示すように、ファイン比較においては、リファレンス電圧を細かく変化させながら、比較器300が信号電圧とリファレンス電圧との比較を行なう。そして、比較結果が反転したときにファインビットを決定する。40

**【0122】**

サブレンジ方式のADCにおいては、コースビットとファインビットとを加算した値がデジタル値となる。このような比較法をとるため、AD変換には $2^M \times$ コース比較時間 +  $2^{(N-M)} \times$ ファイン比較時間が必要になる。

**【0123】**

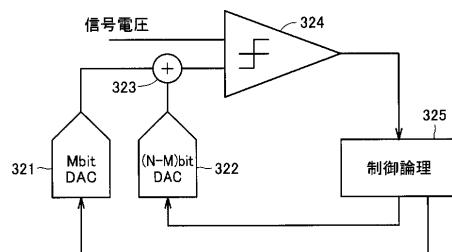

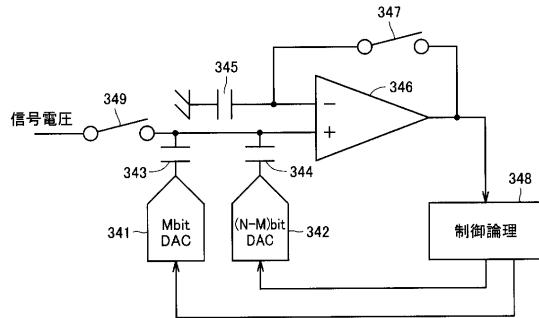

(第4の実施の形態)

図19は、本発明の第4の実施の形態におけるADCの構成例を示す図である。このADCは、MbitDAC321と、(N-M)bitDAC322と、加算器323と、比較器324と、制御論理325とを含む。本実施の形態においては、ADCの分解能であるNビットをコースビット(上位Mビット)とファインビット(下位(N-M)ビット)50

) とに分割し、MbitDAC321がコース比較を行ない、(N-M)bbitDAC322がファイン比較を行なう。

#### 【0124】

加算器323は、MbitDAC321から出力されるコースビットと、(N-M)bbitDAC322から出力されるファインビットとを加算する。また、制御論理325は、MbitDAC321によるコース比較および(N-M)bbitDAC322によるファイン比較を制御する。

#### 【0125】

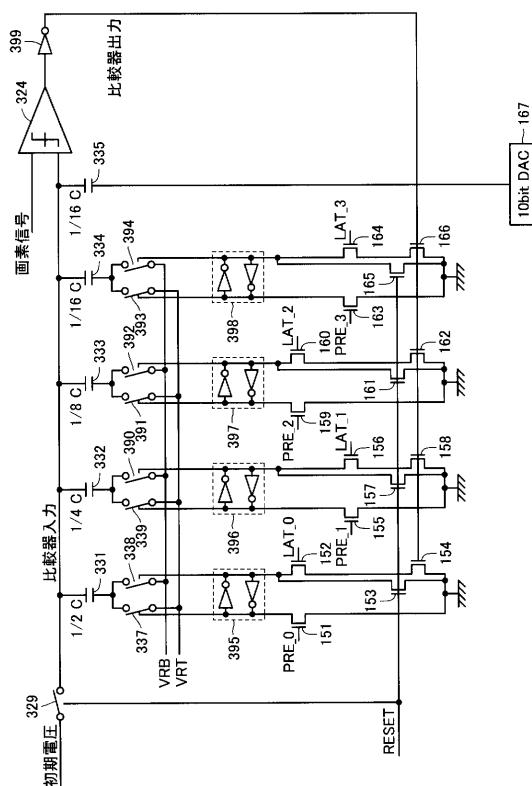

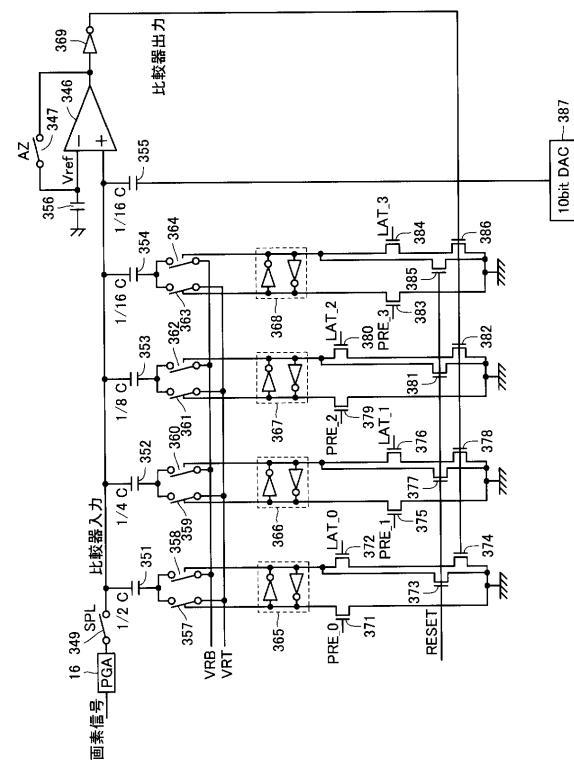

図20は、図19に示す第4の実施の形態におけるADCの構成をさらに詳細に説明するための図である。ADCは、比較器324と、スイッチ329, 337～339および390～394と、コンデンサ331～335と、保持回路395～398と、インバータ399と、NチャネルMOSトランジスタ151～166と、10bitDAC167とを含む。

10

#### 【0126】

10bitDAC167は、図19に示す(N-M)bbitDAC322に相当する。その構成自体は特に限定されない。

#### 【0127】

コンデンサ331は、比較器入力線と容量結合されており、コンデンサ331に接続されるスイッチ337および338を切替えることにより、コースビットの中の最上位ビットの比較が行なわれる。このコンデンサ331の容量は1/2Cである。

20

#### 【0128】

コンデンサ332は、比較器入力線と容量結合されており、コンデンサ332に接続されるスイッチ339および390を切替えることにより、コースビットの中の第2ビットの比較が行なわれる。このコンデンサ332の容量は、コンデンサ331の容量の半分である1/4Cである。

#### 【0129】

コンデンサ333は、比較器入力線と容量結合されており、コンデンサ333に接続されるスイッチ391および392を切替えることにより、コースビットの中の第3ビットの比較が行なわれる。このコンデンサ333の容量は、コンデンサ332の容量の半分である1/8Cである。

30

#### 【0130】

コンデンサ334は、比較器入力線と容量結合されており、コンデンサ334に接続されるスイッチ393および394を切替えることにより、コースビットの中の最下位ビットの比較が行なわれる。このコンデンサ334の容量は、コンデンサ333の容量の半分である1/16Cである。

#### 【0131】

コンデンサ335は、比較器入力線と容量結合されており、対極が10bitDAC167に接続されている。このコンデンサ335の容量は、コンデンサ334の容量と同じ1/16Cである。

#### 【0132】

なお、トランジスタ151～166に接続される制御信号であるプリセット信号PRE\_0～PRE\_3、ラッチ信号LAT\_0～LAT\_3、リセット信号RESETなどは、図19に示す制御論理325によって生成される。

40

#### 【0133】

図21は、本発明の第4の実施の形態におけるADCの動作を説明するためのタイミングチャートである。まず、時刻T1において、RESET信号がHレベルになると、スイッチ329がオン状態になると共に、トランジスタ153, 157, 161および165がオン状態となる。このとき、比較器入力線に初期電圧が与えられると共に、保持回路395～398のそれぞれの右側端子がLレベルを保持し、左側端子がHレベルを保持する。その結果、スイッチ337, 339, 391および393がオン状態となり、スイッチ

50

338, 390, 392 および 394 がオフ状態となって、コンデンサ 331～334 のそれぞれに電圧 VRT が接続される。

#### 【0134】

時刻 T2において、PRE\_0 信号がHレベルになると、トランジスタ 151 がオン状態となり、保持回路 395 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 337 がオフ状態となり、スイッチ 338 がオン状態となって、コンデンサ 331 に電圧 VRB が接続される。このとき、比較器入力線の電圧が (VRT - VRB) / 2 だけ下降する。

#### 【0135】

信号電圧よりも比較器入力電圧の方が低くなるので、比較器 324 はLレベルを出力し、インバータ 399 の出力である比較器出力がHレベルになる。その結果、トランジスタ 154 がオン状態となる。10

#### 【0136】

時刻 T3において、LAT\_0 信号がHレベルになると、トランジスタ 152 がオン状態となる。このとき、トランジスタ 154 もオン状態になっているため、保持回路 395 の右側端子がLレベルとなり、左側端子がHレベルとなる。その結果、スイッチ 337 がオン状態となり、スイッチ 338 がオフ状態となって、コンデンサ 331 に接続される電圧が VRT に戻される。なお、保持回路 395 は、右側端子の値“0”を保持する。

#### 【0137】

時刻 T4において、PRE\_1 信号がHレベルになると、トランジスタ 155 がオン状態となり、保持回路 396 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 339 がオフ状態となり、スイッチ 390 がオン状態となって、コンデンサ 332 に電圧 VRB が接続される。このとき、比較器入力線の電圧が (VRT - VRB) / 4 だけ下降する。20

#### 【0138】

信号電圧よりも比較器入力電圧の方が高いので、比較器 324 はHレベルを出力し、インバータ 399 の出力である比較器出力がLレベルのままとなる。その結果、トランジスタ 158 はオフ状態のままとなる。

#### 【0139】

時刻 T5において、LAT\_1 信号がHレベルになると、トランジスタ 156 がオン状態となる。このとき、トランジスタ 158 がオフ状態になっているため、保持回路 396 の右側端子がHレベルを維持し、左側端子がLレベルを維持する。その結果、スイッチ 339 がオフ状態を維持し、スイッチ 390 がオン状態を維持し、コンデンサ 332 に接続される電圧は VRB のままである。なお、保持回路 396 は、右側端子の値“1”を保持する。30

#### 【0140】

時刻 T6において、PRE\_2 信号がHレベルになると、トランジスタ 159 がオン状態となり、保持回路 397 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 391 がオフ状態となり、スイッチ 392 がオン状態となって、コンデンサ 333 に電圧 VRB が接続される。このとき、比較器入力線の電圧が (VRT - VRB) / 8 だけ下降する。40

#### 【0141】

信号電圧よりも比較器入力電圧の方が高いので、比較器 324 はHレベルを出力し、インバータ 399 の出力である比較器出力がLレベルのままとなる。その結果、トランジスタ 162 はオフ状態のままとなる。

#### 【0142】

時刻 T7において、LAT\_2 信号がHレベルになると、トランジスタ 160 がオン状態となる。このとき、トランジスタ 162 がオフ状態になっているため、保持回路 397 の右側端子がHレベルを維持し、左側端子がLレベルを維持する。その結果、スイッチ 391 がオフ状態を維持し、スイッチ 392 がオン状態を維持し、コンデンサ 333 に接続50

される電圧はVRBのままとなる。なお、保持回路397は、右側端子の値“1”を保持する。

#### 【0143】

時刻T8において、PRE\_3信号がHレベルになると、トランジスタ163がオン状態となり、保持回路398の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ393がオフ状態となり、スイッチ394がオン状態となって、コンデンサ334に電圧VRBが接続される。このとき、比較器入力線の電圧が(VRT - VRB) / 16だけ下降する。

#### 【0144】

信号電圧よりも比較器入力電圧の方が低くなるので、比較器324はLレベルを出力し、インバータ399の出力である比較器出力がHレベルになる。その結果、トランジスタ166がオン状態となる。10

#### 【0145】

時刻T9において、LAT\_3信号がHレベルになると、トランジスタ164がオン状態となる。このとき、トランジスタ166もオン状態になっているため、保持回路398の右側端子がLレベルとなり、左側端子がHレベルとなる。その結果、スイッチ393がオン状態となり、スイッチ394がオフ状態となって、コンデンサ334に接続される電圧がVRTに戻される。なお、保持回路398は、右側端子の値“0”を保持する。

#### 【0146】

このようにして、保持回路395～398に保持される値“0110”がコースビットとして確定する。そして、それ以降(N-M)bitDAC322が制御されてファイン比較が行なわれ、ファインビットが確定する。確定したコースビットおよびファインビットは、図3に示すH-Scanner14によって水平方向に順次転送される。20

#### 【0147】

以上の説明においては、比較器入力電圧を初期電圧からコースビットの各ビットに対応する電圧ずつ順次下降させるようにしたが、比較器入力電圧を初期電圧からコースビットの各ビットに対応する電圧ずつ順次上昇させるような構成にしてもよい。

#### 【0148】

以上説明したように、本実施の形態における固体撮像装置によれば、コースビットの各ビットに対応する電圧ずつ比較器入力電圧を初期電圧から順次下降または上昇させ、比較器324に比較器入力電圧と信号電圧とを比較させてコースビットの各ビットを決定するといった逐次比較(2分岐探索)を行なうようにした。そのため、AD変換に必要な時間がM×コース比較時間 + 2(N-M) × ファイン比較時間となり、AD変換を高速に行なうことが可能となった。30

#### 【0149】

##### (第5の実施の形態)

図22は、本発明の第5の実施の形態におけるADCの構成例を示す図である。このADCは、MbitDAC341と、(N-M)bitDAC342と、コンデンサ343～345と、高利得アンプ346と、スイッチ347および349と、制御論理348とを含む。本実施の形態においても、ADCの分解能であるNビットをコースビット(上位Mビット)とファインビット(下位(N-M)ビット)とに分割し、MbitDAC341がコース比較を行ない、(N-M)bitDAC342がファイン比較を行なう。40

#### 【0150】

図23は、図22に示す第5の実施の形態におけるADCの構成をさらに詳細に説明するための図である。ADCは、高利得アンプ346と、スイッチ347, 349, 357～364と、コンデンサ351～355と、保持回路365～368と、インバータ369と、NチャネルMOSトランジスタ371～386と、10bitDAC387とを含む。

#### 【0151】

10bitDAC387は、図22に示す(N-M)bitDAC342に相当する。

50

その構成自体は特に限定されない。

**【0152】**

高利得アンプ346の正入力には、PGA16から出力される増幅された画素入力がスイッチ349を介して接続される。また、高利得アンプ346の負入力には、高利得アンプ346の出力がスイッチ347を介して接続されると共に、画素の暗状態の情報（非照射時における画素の情報）を保持するコンデンサ356が接続される。

**【0153】**

コンデンサ351は、比較器入力線と容量結合されており、コンデンサ351に接続されるスイッチ357および358を切替えることにより、コースピットの中の最上位ビットの比較が行なわれる。このコンデンサ351の容量は1/2Cである。

10

**【0154】**

コンデンサ352は、比較器入力線と容量結合されており、コンデンサ352に接続されるスイッチ359および360を切替えることにより、コースピットの中の第2ビットの比較が行なわれる。このコンデンサ352の容量は、コンデンサ351の容量の半分である1/4Cである。

**【0155】**

コンデンサ353は、比較器入力線と容量結合されており、コンデンサ353に接続されるスイッチ361および362を切替えることにより、コースピットの中の第3ビットの比較が行なわれる。このコンデンサ353の容量は、コンデンサ352の容量の半分である1/8Cである。

20

**【0156】**

コンデンサ354は、比較器入力線と容量結合されており、コンデンサ354に接続されるスイッチ363および364を切替えることにより、コースピットの中の最下位ビットの比較が行なわれる。このコンデンサ354の容量は、コンデンサ353の容量の半分である1/16Cである。

**【0157】**

コンデンサ355は、比較器入力線と容量結合されており、対極が10bitDAC387に接続されている。このコンデンサ355の容量は、コンデンサ354の容量と同じ1/16Cである。

**【0158】**

30

なお、トランジスタ371～386に接続される制御信号であるPRE\_0～PRE\_3、LAT\_0～LAT\_3、RESETなどは、図22に示す制御論理348によって生成される。

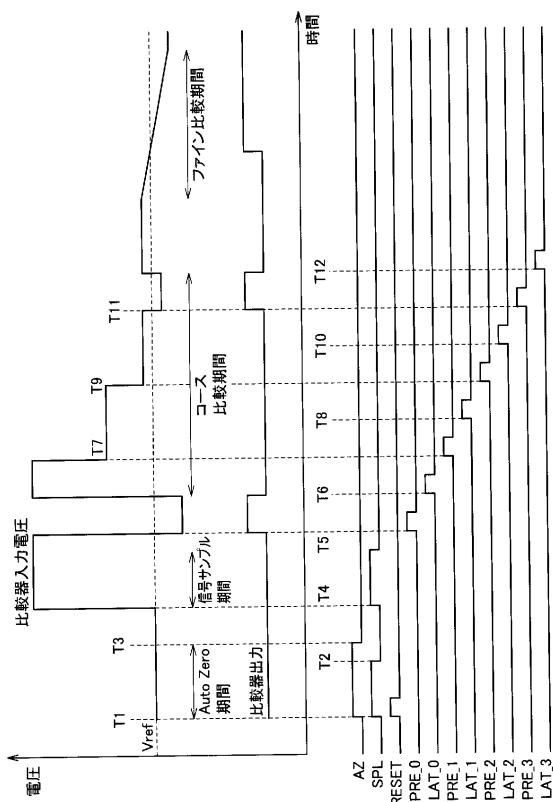

**【0159】**

図24は、本発明の第5の実施の形態におけるADCの動作を説明するためのタイミングチャートである。まず、時刻T1において、オートゼロ信号AZおよびサンプリング信号SPLがHレベルになると、スイッチ347および349がオン状態になる。このとき、比較器入力線には画素の暗状態の情報がサンプリングされる。高利得アンプ346は、コンデンサ356の正極電位(Vref)に画素の暗状態の情報を電位として与える。

**【0160】**

40

また、時刻T1において、RESET信号がHレベルになり、トランジスタ373, 377, 381および385がオン状態となる。このとき、保持回路365～368のそれぞれの右側端子がLレベルを保持し、左側端子がHレベルを保持する。その結果、スイッチ357, 359, 361および363がオン状態となり、スイッチ358, 360, 362および364がオフ状態となって、コンデンサ351～354のそれぞれに電圧VRTが接続される。

**【0161】**

時刻T2において、SPL信号がLレベルとなり、比較器入力線には画素の暗状態の情報が保持される。また、時刻T3において、AZ信号がLレベルになると、コンデンサ356の正極電位(Vref)に画素の暗状態の情報を電位として保持される。

50

**【 0 1 6 2 】**

時刻 T 4において、再度 S P L 信号がHレベルになると、P G A 1 6 から出力される画素の明状態の情報（照射時における画素の情報）が比較器入力線に電位としてサンプリングされて保持される。

**【 0 1 6 3 】**

時刻 T 5において、P R E \_ 0 信号がHレベルになると、トランジスタ 3 7 1 がオン状態となり、保持回路 3 6 5 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 3 5 7 がオフ状態となり、スイッチ 3 5 8 がオン状態となって、コンデンサ 3 5 1 に電圧 V R B が接続される。このとき、比較器入力線の電圧が (V R T - V R B) / 2 だけ下降する。

10

**【 0 1 6 4 】**

リファレンス電圧 V r e f よりも比較器入力電圧の方が低くなるので、高利得アンプ 3 4 6 はLレベルを出力し、インバータ 3 6 9 の出力である比較器出力がHレベルになる。その結果、トランジスタ 3 7 4 がオン状態となる。

**【 0 1 6 5 】**

時刻 T 6において、L A T \_ 0 信号がHレベルになると、トランジスタ 3 7 2 がオン状態となる。このとき、トランジスタ 3 7 4 もオン状態になっているため、保持回路 3 6 5 の右側端子がLレベルとなり、左側端子がHレベルとなる。その結果、スイッチ 3 5 7 がオン状態となり、スイッチ 3 5 8 がオフ状態となって、コンデンサ 3 5 1 に接続される電圧が V R T に戻される。なお、保持回路 3 6 5 は、右側端子の値“0”を保持する。

20

**【 0 1 6 6 】**

時刻 T 7において、P R E \_ 1 信号がHレベルになると、トランジスタ 3 7 5 がオン状態となり、保持回路 3 6 6 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 3 5 9 がオフ状態となり、スイッチ 3 6 0 がオン状態となって、コンデンサ 3 5 2 に電圧 V R B が接続される。このとき、比較器入力線の電圧が (V R T - V R B) / 4 だけ下降する。

**【 0 1 6 7 】**

リファレンス電圧 V r e f よりも比較器入力電圧の方が高いので、高利得アンプ 3 4 6 はHレベルを出力し、インバータ 3 6 9 の出力である比較器出力がLレベルのままとなる。その結果、トランジスタ 3 7 8 はオフ状態のままとなる。

30

**【 0 1 6 8 】**

時刻 T 8において、L A T \_ 1 信号がHレベルになると、トランジスタ 3 7 6 がオン状態となる。このとき、トランジスタ 3 7 8 がオフ状態になっているため、保持回路 3 6 6 の右側端子がHレベルを維持し、左側端子がLレベルを維持する。その結果、スイッチ 3 5 9 がオフ状態を維持し、スイッチ 3 6 0 がオン状態を維持し、コンデンサ 3 5 2 に接続される電圧は V R B のままとなる。なお、保持回路 3 6 6 は、右側端子の値“1”を保持する。

**【 0 1 6 9 】**

時刻 T 9において、P R E \_ 2 信号がHレベルになると、トランジスタ 3 7 9 がオン状態となり、保持回路 3 6 7 の右側端子がHレベルとなり、左側端子がLレベルとなる。その結果、スイッチ 3 6 1 がオフ状態となり、スイッチ 3 6 2 がオン状態となって、コンデンサ 3 5 3 に電圧 V R B が接続される。このとき、比較器入力線の電圧が (V R T - V R B) / 8 だけ下降する。

40

**【 0 1 7 0 】**

リファレンス電圧 V r e f よりも比較器入力電圧の方が高いので、高利得アンプ 3 4 6 はHレベルを出力し、インバータ 3 6 9 の出力である比較器出力がLレベルのままとなる。その結果、トランジスタ 3 8 2 はオフ状態のままとなる。

**【 0 1 7 1 】**

時刻 T 1 0 において、L A T \_ 2 信号がHレベルになると、トランジスタ 3 8 0 がオン状態となる。このとき、トランジスタ 3 8 2 がオフ状態になっているため、保持回路 3 6

50

7 の右側端子が H レベルを維持し、左側端子が L レベルを維持する。その結果、スイッチ 361 がオフ状態を維持し、スイッチ 362 がオン状態を維持し、コンデンサ 353 に接続される電圧は VRB のままとなる。なお、保持回路 367 は、右側端子の値 “1” を保持する。

#### 【 0172 】

時刻 T11において、PRE\_3 信号が H レベルになると、トランジスタ 383 がオン状態となり、保持回路 368 の右側端子が H レベルとなり、左側端子が L レベルとなる。その結果、スイッチ 363 がオフ状態となり、スイッチ 364 がオン状態となって、コンデンサ 354 に電圧 VRB が接続される。このとき、比較器入力線の電圧が (VRT - VRB) / 16 だけ下降する。

10

#### 【 0173 】

リファレンス電圧 Vref よりも比較器入力電圧の方が低くなるので、高利得アンプ 346 は L レベルを出力し、インバータ 369 の出力である比較器出力が H レベルになる。その結果、トランジスタ 386 がオン状態となる。

#### 【 0174 】

時刻 T12において、LAT\_3 信号が H レベルになると、トランジスタ 384 がオン状態となる。このとき、トランジスタ 386 もオン状態になっているため、保持回路 368 の右側端子が L レベルとなり、左側端子が H レベルとなる。その結果、スイッチ 363 がオン状態となり、スイッチ 364 がオフ状態となって、コンデンサ 354 に接続される電圧が VRT に戻される。なお、保持回路 368 は、右側端子の値 “0” を保持する。

20

#### 【 0175 】

このようにして、保持回路 365 ~ 368 に保持される値 “0110” がコースビットとして確定する。そして、それ以降 (N-M) bit DAC 342 が制御されてファイン比較が行なわれ、ファインビットが確定する。確定したコースビットおよびファインビットは、図 3 に示す H-Scanner 14 によって水平方向に順次転送される。

#### 【 0176 】

以上の説明においては、比較器入力電圧を画素信号の電圧からコースビットの各ビットに対応する電圧ずつ順次下降させるようにしたが、比較器入力電圧を画素信号の電圧からコースビットの各ビットに対応する電圧ずつ順次上昇させるような構成にしてもよい。

#### 【 0177 】

30

以上説明したように、本実施の形態における固体撮像装置によれば、コースビットの各ビットに対応する電圧ずつ比較器入力電圧を画素信号の電圧から順次下降または上昇させ、高利得アンプ 346 に比較器入力電圧とリファレンス電圧 Vref とを比較させてコースビットの各ビットを決定するといった逐次比較（2 分岐探索）を行なうようにした。そのため、AD 変換に必要な時間が  $M \times$  コース比較時間 +  $2^{(N-M)} \times$  ファイン比較時間となり、AD 変換を高速に行なうことが可能となった。

#### 【 0178 】

##### （第 6 の実施の形態）

本発明の第 4 および第 5 の実施の形態における固体撮像装置は、Mbit DAC 321 または 341 が 4 ビットのコース比較を行ない、(N-M) bit DAC 322 または 342 が 10 ビットのファイン比較を行なうものであった。

40

#### 【 0179 】

本発明の第 6 の実施の形態における固体撮像装置は、(N-M) bit DAC 322 および 342 が、たとえば 10.2 ビットのオーバレンジ DAC によって構成される。そして、Mbit DAC 321 または 341 によって確定されたコースビットと、(N-M) bit DAC 322 または 342 によって確定されたファインビットとを加算するときに、オーバレンジに相当する値だけ減算してデジタル値とする点のみが異なる。したがって、重複する構成および機能の詳細な説明は繰り返さない。

#### 【 0180 】

以上説明したように、本実施の形態における固体撮像装置によれば、(N-M) bit

50

DACをオーバレンジのDACによって構成するようにしたので、第4および第5の実施の形態において説明した効果に加えて、サブレンジ間のつなぎ補正を容易に行なえるようになった。

#### 【0181】

今回開示された実施の形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

#### 【符号の説明】

#### 【0182】

1, 2, 4, 5, 36~38, 54~62, 151~166, 371~386 トランジスタ、3 フォトダイオード、9 垂直読出線、10 固体撮像装置、11, 110, 210 画素アレイ、12 ADC、13 制御回路／ロウデコーダ、14 H-Sanner、15 I/O部、16 PGA、17 データラッチ／転送回路、21 差動増幅器、22, 31~34, 51~53 スイッチ、39, 69 保持回路、40, 63, 66 NAND回路、41, 64, 67 FF、42, 68 グレイ・バイナリ変換器、65 加算器、100 アナログイメージセンサ、120, 220 V-Scanner、130, 230 コラムアンプ、140 AFE、200 デジタルイメージセンサ、240 コラムADC、C1~C4, C40~C46 コンデンサ、321, 341 Mbit DAC、322, 342 (N-M)bit DAC、323 加算器、324 比較器、325, 348 制御論理、329, 337~339, 347, 349, 357~364, 390~394 スイッチ、331~335, 343~345, 351~355 コンデンサ、346 高利得アンプ、365~368, 395~398 保持回路、369, 399 インバータ、167, 387 10bit DAC。

10

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【図11】

【図10】

【図12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図22】

【図23】

【図24】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 宇都宮 裕人

東京都千代田区大手町二丁目 6番 2号 株式会社ルネサステクノロジ内

(72)発明者 堂阪 勝己

東京都千代田区大手町二丁目 6番 2号 株式会社ルネサステクノロジ内

(72)発明者 加藤 宏

東京都千代田区大手町二丁目 6番 2号 株式会社ルネサステクノロジ内

(72)発明者 森下 玄

東京都千代田区大手町二丁目 6番 2号 株式会社ルネサステクノロジ内

(72)発明者 佐々木 史康

東京都千代田区大手町二丁目 6番 2号 株式会社ルネサステクノロジ内

審査官 木方 庸輔

(56)参考文献 特開2005-027232 (JP, A)

特開平04-162828 (JP, A)

特開2008-098722 (JP, A)

特開2006-352597 (JP, A)

特開2009-239694 (JP, A)

特開2011-035701 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 04 N 5 / 335