## **PCT**

#### WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification  $^{\,6}$  :

${\bf (11) \ International \ Publication \ Number:}$

WO 97/03236

C30B 31/12, C23C 16/46

(43) International Publication Date:

30 January 1997 (30.01.97)

(21) International Application Number:

PCT/US96/11440

**A2**

(22) International Filing Date:

9 July 1996 (09.07.96)

Published

(30) Priority Data:

08/499,986

10 July 1995 (10.07.95)

US

(71) Applicant: MATTSON TECHNOLOGY, INC. [US/US]; 3550 West Warren Avenue, Fremont, CA 94538 (US).

(72) Inventors: JOHNSGARD, Kristian, E.; 13560 Indian Rock Way, Los Gatos, CA 95030 (US). MATSON, Brad, S.; 19251 Black Road, Los Gatos, CA 95030 (US). MCDI-ARMID, James; 4210 Remillard Court, Pleasanton, CA 94566 (US). ZEITLIN, Vladimir, J.; 146 Muir Avenue, Santa Clara, CA 95051 (US).

(74) Agent: MURPHY, Michael, J.; Wilson, Sonsini, Goodrich & Rosati, 650 Page Mill Road, Palo Alto, CA 94304-1050 (US).

Without international search report and to be republished upon receipt of that report.

DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(81) Designated States: JP, KR, European patent (AT, BE, CH, DE,

(54) Title: SYSTEM AND METHOD FOR THERMAL PROCESSING OF A SEMICONDUCTOR SUBSTRATE

#### (57) Abstract

A semiconductor substrate processing system and method using a stable heating source with a large thermal mass relative to conventional lamp heated systems. The system dimensions and processing parameters are selected to provide a substantial heat flux to the wafer while minimizing heat loss to the surrounding environment (particularly from the edges of the heat source and wafer). The heat source provides a wafer temperature uniformity profile that has a low variance across temperature ranges at low pressures. A resistively heated block is substantially enclosed within an insulated vacuum cavity used to heat the wafer. A vacuum region is preferably provided between the heated block and the insulating material as well as between the insulating material and the chamber wall. Heat transfer across the vacuum regions is primarily achieved by radiation, while heat transfer through the insulating material is achieved by conduction. The wafer is placed on or near the heated block within the vacuum cavity for heating by conduction and radiation. The rate of heating may be controlled by varying pressure across a range of very low pressures.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| ΑT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| ΑU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| BJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | TJ | Tajikistan               |

| DK | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

# SYSTEM AND METHOD FOR THERMAL PROCESSING OF A SEMICONDUCTOR SUBSTRATE

## **BACKGROUND OF THE INVENTION**

#### 1. Field of the Invention

The field of the present invention relates in general to semiconductor processing.

More particularly, the field of the invention relates to a system and method for thermally processing a semiconductor substrate using a stable temperature heat source.

## 2. Background

25

Diffusion furnaces have been widely used for thermal processing of semiconductor device materials (such as semiconductor wafers or other semiconductor substrates). The furnaces typically have a large thermal mass that provides a relatively uniform and stable temperature for processing. However, in order to achieve uniform results, it is necessary for the conditions in the furnace to reach thermal equilibrium after a batch of wafers is inserted into the furnace. Therefore, the heating time for wafers in a diffusion furnace is relatively long, typically exceeding ten minutes.

As integrated circuit dimensions have decreased, shorter thermal processing steps for some processes, such as rapid thermal anneal, are desirable to reduce the lateral diffusion of dopants and the associated broadening of feature dimensions. Thermal process duration may also be limited to reduce forward diffusion so the semiconductor junction in the wafer does not shift. As a result, the longer processing times inherent in conventional diffusion furnaces have become undesirable for many processes. In addition, increasingly stringent requirements for process control and repeatability have made batch processing undesirable for many applications.

As an alternative to diffusion furnaces, single wafer rapid thermal processing (RTP) systems have been developed for rapidly heating and cooling wafers. Most RTP systems use high intensity lamps (usually tungsten-halogen lamps or arc lamps) to selectively heat a wafer within a cold wall clear quartz furnace. Since the lamps have very low thermal mass, the wafer can be heated rapidly. Rapid wafer cooling is also easily achieved since the heat source may be turned off instantly without requiring a slow temperature ramp down. Lamp heating of the wafer minimizes the thermal mass effects of the process chamber and allows rapid real time control over the wafer temperature. While single wafer RTP reactors

provide enhanced process control, their throughput is substantially less than batch furnace systems.

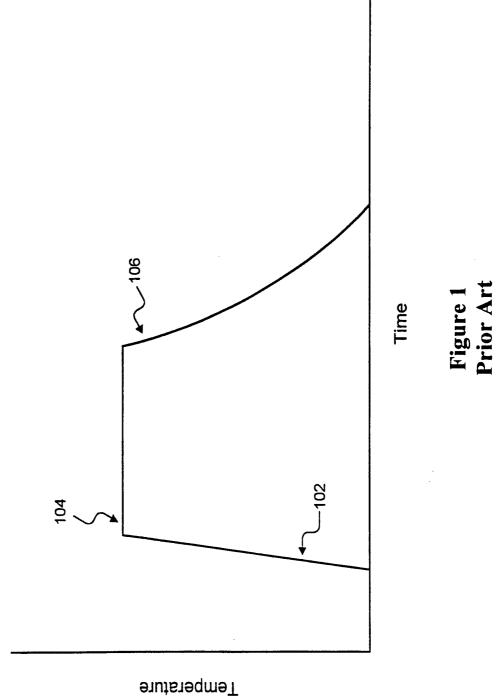

Figure 1 is a graph illustrating a desired heating profile for a wafer during rapid thermal processing in a lamp heated RTP system. In particular, the solid line in Figure 1 is a plot of the temperature of the center of a wafer over the duration of a rapid thermal annealing process. As shown in Figure 1, the wafer may be heated at a rapid rate as indicated at 102 in Figure 1. Lamp radiation may be rapidly adjusted as a desired processing temperature is approached in order to achieve a constant processing temperature, as indicated at 104. At the end of the processing step, the lamp radiation may be quickly reduced to allow cooling as indicated at 106.

While RTP systems allow rapid heating and cooling, it is difficult to achieve repeatable, uniform wafer processing temperatures using RTP, particularly for larger wafers (200 mm and greater). The temperature uniformity is sensitive to the uniformity of the optical energy absorption as well as the radiative and convective heat losses of the 15 wafer. Wafer temperature nonuniformities usually appear near wafer edges because radiative heat losses are greatest at the edges. During RTP the wafer edges may, at times, be several degrees (or even tens of degrees) cooler than the center of the wafer. At high temperatures, generally greater than eight hundred degrees Celsius (800°C), this nonuniformity may produce crystal slip lines on the wafer (particularly near the edge). To minimize the formation of slip lines, insulating rings are often placed around the perimeter of the wafer to shield the wafer from the cold chamber walls. Nonuniformity is also undesirable since it may lead to nonuniform material properties such as alloy content, grain size, and dopant concentration. These nonuniform material properties may degrade the circuitry and decrease yield even at low temperatures (generally less than 800°C). For instance, temperature uniformity is critical to the formation of titanium silicide by post deposition annealing. In fact, the uniformity of the sheet resistance of the resulting titanium silicide is regarded as a standard measure for evaluating temperature uniformity in RTP systems.

Temperature levels and uniformity must therefore be carefully monitored and controlled in RTP systems. Optical pyrometry is typically used due to its noninvasive nature and relatively fast measurement speed which are critical in controlling the rapid

heating and cooling in RTP. However, accurate temperature measurement using optical pyrometry depends upon the accurate measurement of the intensity of radiation emitted from the wafer and upon the wafer's radiation emitting characteristics or emissivity. Emissivity is typically wafer dependent and depends on a range of parameters, including temperature, chamber reflectivity, the wafer material (including dopant concentration), surface roughness, and surface layers (including the type and thickness of sub-layers), and will change dynamically during processing as layers grow on the surface of the wafer. In addition, radiation from heat sources, particularly lamps, reflect off the wafer surface and interfere with optical pyrometry. This reflected radiation erroneously augments the measured intensity of radiation emitted from the wafer surface and results in inaccurate temperature measurement.

Increasingly complex systems have been developed for measuring emissivity and for compensating for reflected radiation. One approach uses two optical pyrometers — one for measuring the radiation from the lamps and one for measuring the radiation from the wafer. The strength of the characteristic AC ripple in radiation emanated from the lamp can be compared to the strength of the AC ripple reflected from the wafer to determine the wafer's reflectivity. This, in turn, can be used to essentially subtract out reflected radiation in order to isolate the emitted radiation from the wafer for determining temperature using Planck's equation. See, e.g., U.S. Patent 5,166,080 to Schietinger et al. However, such systems may require complex circuitry to isolate the AC ripple and perform the calculations that effectively eliminate reflected radiation. Such systems also require an additional optical sensor and other components.

Another approach for measuring wafer temperature and compensating for the effects of emissivity uses an infrared laser source that directs coherent light into a beam splitter. From the beam splitter, the coherent light beam is split into numerous incident beams which travel to the wafer surface via optical fiber bundles. The optical fiber bundles also collect the reflected coherent light beams as well as radiated energy from the wafer. In low temperature applications, transmitted energy may be collected and measured as well. The collected light is then divided into separate components from which radiance, emissivity, and temperature may be calculated. See, e.g., U.S. Patent 5,156,461 to Moslehi et al. It is a disadvantage of such systems that a laser and other complex components are

required. Such systems, however, are advantageous because they may provide measurements of wafer temperature at multiple points along the wafer surface which may be useful for detecting and compensating for temperature nonuniformities.

In order to compensate for temperature nonuniformities, a heater with multiple independently controlled heating zones may be required. One approach is to use a multizone lamp system arranged in a plurality of concentric circles. The lamp energy may be adjusted to compensate for temperature differences detected using multi-point optical pyrometry. However, such systems often require complex and expensive lamp systems with separate temperature controls for each zone of lamps. For instance, U.S. Patent 5,268,989 to Moslehi et al. discloses a multi-zone heater with sixty five tungsten-halogen 10 lamps arranged into four heating zones. In addition, a light interference elimination system is disclosed which uses light pipes in seven dummy lamps to measure lamp radiation as well as five or more light pipes for measuring radiation across the surface of the wafer. The light interference elimination system uses the radiation of the dummy lamps to determine the fraction of total radiation from the wafer surface that is reflected from the lamps as opposed to emitted from the wafer surface. The emitted radiation can then be isolated and used to detect temperature across the wafer surface, which in turn can be used to control the lamp heating zones.

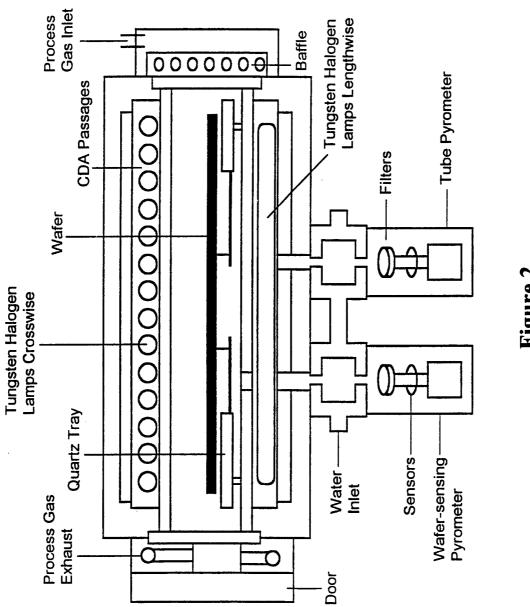

A widely used exemplary RTP system is the Heatpulse<sup>TM</sup> 8108 system from AG

Associates shown in cross section in Figure 2. According to published technical specifications, this system uses twenty eight tungsten halogen lamps in cross configuration with ten software controlled heat zones. In process specifications for this system, the uniformity of titanium silicide formation on a 200 mm wafer is reported to be 1.5% nonuniformity added to as-sputtered titanium wafer uniformity. A throughput of around twenty five (25) wafers per hour is reported for this process.

While multi-zone lamp systems have enhanced wafer temperature uniformity, their complexity has increased cost and maintenance requirements. In addition, other problems must be addressed in lamp heated RTP systems. For instance, many lamps use linear filaments which provide heat in linear segments and as a result are ineffective or inefficient at providing uniform heat to a round wafer even when multi-zone lamps are used. Furthermore, lamp systems tend to degrade with use which inhibits process repeatability

and individual lamps may degrade at different rates which reduces uniformity. In addition, replacing degraded lamps increases cost and maintenance requirements.

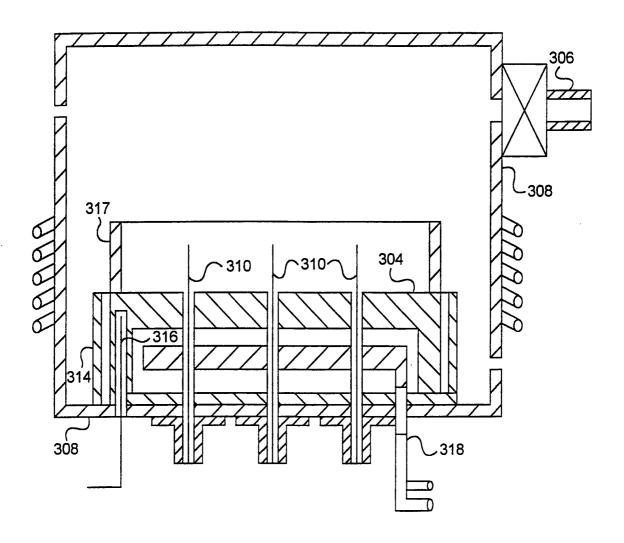

In order to overcome the disadvantages of lamp heated RTP systems, a few systems have been proposed which use a resistively heated plate. Such heated plates provide a relatively large thermal mass with a stable temperature. Figure 3 shows a side cross sectional view of a conventional heated plate rapid thermal processor. Referring to Figure 3. a wafer may be placed on or near a heated plate 304 for thermal processing. The wafer enters the chamber through a port 306 formed in the chamber wall 308. The wafer is placed on support pins 310 which may be raised and lowered for loading and unloading the wafer. For processing, the wafer is lowered onto or close to the heated plate 304. The heated plate is heated by a resistive heater 312, and the wafer is rapidly heated by conduction, convection, and radiation from the heated plate. Since the heated plate is a constant and substantial source of heat, a reflective heat shield 314 may be necessary in order to protect the chamber walls 308. Temperature is monitored in the system of Figure 3 using a thermocouple 316 disposed in the heater plate, as opposed to an optical pyrometer which may be affected by emissivity variations. However, it is the temperature of the heated plate 304 that is directly measured by the thermocouple and not the temperature of the wafer.

While the heated plate 304 provides a stable, repeatable heating source with a large thermal mass, similar to a diffusion furnace, the chamber walls 308 be cooled. This allows a wafer to be rapidly heated by lowering the wafer onto the heated plate for a short period of time and rapidly cooled by removing the wafer from the plate. In addition, a radiation absorbing material may be used to coat the top surface of the chamber to enhance cooling as the wafer is raised by the pins after heating. See U.S. Patents 5,060,354 and 5,252,807 to Chizinsky.

While heated plate rapid thermal processors provide a stable temperature on the heated plate that may be measured using a thermocouple, problems may be encountered with wafer temperature nonuniformities. Wafers may be heated by placing them near the heated plate rather than on the plate. In such systems, the edges of the wafer may have large heat losses which lead to nonuniformities as in lamp heated RTP systems. Even when a wafer is placed in contact with a heated plate, there may be nonuniformities. The heated

plate itself may have large edge losses, because: 1) the corners and edges of the plate may radiate across a wider range of angles into the chamber; 2) vertical chimney effects may cause larger convective heat losses at the edges of the heated plate; and 3) the edges of the heated plate may be close to cold chamber walls. These edge losses on the plate may, in turn, impose temperature nonuniformities upon a wafer placed on the plate.

In addition, heat loss and temperature uniformity across the wafer surface varies with temperature and pressure. Conductive heat transfer between two objects (such as the wafer and the cold chamber wall) is proportional to the temperature difference between the objects and radiative heat transfer is proportional to the difference of the temperatures raised to the fourth power  $(T_1^4-T_2^4)$ . Thus, the difference between temperatures across the wafer surface will increase at higher processing temperatures. In addition, the pressure in the chamber may affect the wafer temperature profile since heat transfer at low pressures is predominantly carried out by radiation, while heat transfer at higher pressures involves a combination of radiation, conduction and convection.

As with lamp heated RTP systems, a variety of techniques may be used to enhance wafer temperature uniformity. For instance, the reactor of Figure 3 includes a wall 317 extending upward from the perimeter of the heated plate. The wall 317 is intended to help maintain the uniformity of the temperature across the diameter of the wafer, as the wafer is displaced on the pins, away from the heated plate. However, it is believed that the cold chamber walls, which are close to and directly exposed to the upstanding wall and portions of the heated plate, will induce temperature and process nonuniformities. In addition, the effect of the wall will vary across temperature and pressure ranges.

Conventional heated plate processing systems also tend to be energy inefficient.

The heated plate is maintained at a high temperature with constant conductive, convective and radiative losses to the cold chamber walls. While conductive and convective losses may be reduced at lower pressures, this inhibits the heat transfer to the wafer. At low pressures where heating is primarily radiative, the wafer may be significantly cooler than the heated plate particularly when proximity heating is used. This makes the wafer temperature difficult to control. Further, at low pressures where radiation is the primary mechanism for heat transfer, the variance in wafer temperature uniformity across temperature ranges may be greater because heat transfer by radiation is proportional to the

25

difference between surface temperatures raised to the fourth power  $(T_1^4-T_2^4)$ . Thus, decreasing pressure to increase energy efficiency may make the wafer temperature and uniformity more difficult to control.

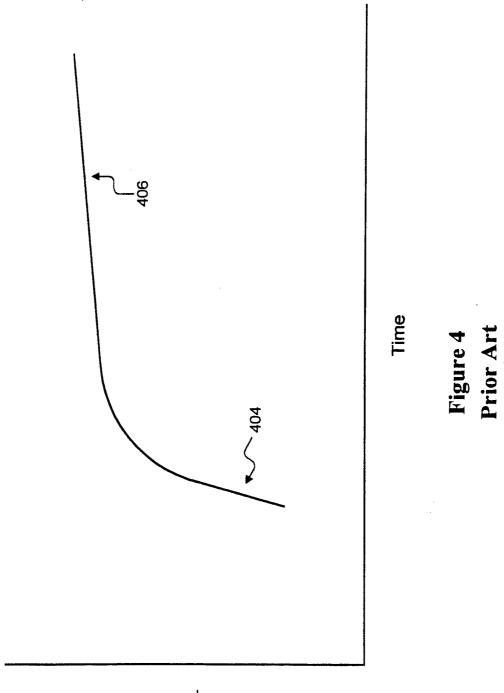

Another disadvantage associated with conventional heated plate processors is that their large thermal mass prevents the rate of heating from being rapidly adjusted to achieve desired temperature profiles, such as the rapid thermal anneal profile shown in Figure 1. When a wafer is placed near a constant temperature heat source, such as a heated plate with a large thermal mass, it has an asymptotic temperature profile over time as shown in Figure 4. The wafer initially heats rapidly as shown by the portion of the curve indicated at 404. As the wafer temperature approaches the temperature of the plate, the rate of heating slows and the temperature of the wafer approaches the temperature of the heated plate asymptotically as shown by the portion of the curve indicated at 406. Since the large thermal mass prevents the temperature of the heated plate from being rapidly adjusted, the desired temperature profile of Figure 1 will not be achieved.

Additional problems may also be encountered in conventional heated plate processors. In particular, a graphite heater may be desired due to its advantageous heating properties; however, graphite heaters are often fragile and easily damaged by shear strain. Thus, a graphite heater may be damaged when it is clamped or mounted to a support or electrode, and it is often difficult to provide a reliable electrical connection between a graphite heater and a power source. In addition, if a heater is mounted with a vertical support as indicated at 318 in Figure 3, it may expand vertically during heating. This necessitates a clearance distance between the resistive heater and the heated block to allow for different levels of expansion at different temperatures. However, for efficient heating it is preferred that the resistive heater be closely spaced to the heated block.

As a result of the problems associated with conventional heated plate rapid thermal processors, they have not been adopted in the industry as a viable alternative to lamp heated RTP systems. A 1993 survey of RTP equipment covering twenty two different vendors' products indicates that, at the time of the survey, only one non-lamp system was available. See Roozeboom, "Manufacturing Equipment Issues in Rapid Thermal Processing," Rapid Thermal Processing at 349-423 (Academic Press 1993). The only non-lamp system listed uses a resistively heated bell jar with two temperature zones and is not a

heated plate reactor. See U.S. Patent 4,857,689 to Lee. Currently, the RTP market is dominated by lamp based systems and despite the many problems associated with such systems, they have been widely accepted over proposed heated plate approaches. Despite the potential that heated plate approaches offer for a stable and repeatable heat source, it is believed that problems with energy efficiency, uniformity, temperature and heating rate control, and the deployment of fragile, noncontaminating resistive heaters have made such systems unacceptable in the marketplace.

What is needed is a system and method for rapid thermal processing with a stable and repeatable heating source that provides a high level of uniformity across a wide range of temperatures. Preferably, the heating source would be maintained at a high temperature without necessitating rapid heating and cooling of the heating source. In addition, such a system would preferably be energy efficient while providing accurate wafer temperature control that is substantially independent of variances in wafer emissivity and would allow a cold walled chamber to be used. Preferably such a system would also provide substantially improved throughput over conventional single wafer RTP systems while maintaining a high level of process control and wafer temperature uniformity. Such a system would also preferably provide a compact heating source that is not significantly larger than the wafers being heated.

What is also needed is a system and method for thermal processing of a wafer using a heating source with a relatively large, stable thermal mass while allowing the rate of heating to be rapidly adjusted to achieve desired temperature profiles. Preferably such a system would allow a wafer to be heated at a rapid rate until a desired temperature is achieved and then allow the rate of heating to be quickly adjusted to maintain the temperature at a relatively constant level. In addition, such a system would preferably allow thermal processing of wafers with a temperature profile, uniformity and throughput competitive with conventional lamp RTP systems.

What is also needed is an improved system and method for deploying a fragile, resistive heater. Preferably such a system would allow a graphite heater to be mounted to a power source with an improved electrical connection and with substantially reduced potential for damage due to shear strain. In addition, such a system would preferably allow

-9-

a graphite heater to be mounted closely to a heated block without significant vertical expansion across a wide range of temperatures.

5

Preferably, each of the above features would be combined in a single compact, cost-effective RTP system and method.

### **SUMMARY OF THE INVENTION**

One aspect of the present invention provides a semiconductor substrate processing system and method using a stable heating source with a large thermal mass relative to conventional lamp heated systems. The system dimensions and processing parameters are preferably selected to provide a substantial heat flux to the wafer while minimizing heat loss to the surrounding environment (particularly from the edges of the heat source and wafer). The heat source provides a wafer temperature uniformity profile that has a low variance across temperature ranges at low pressures. This may be accomplished in one embodiment of the invention by insulating a resistively heated block at the edges and corners using a noncontaminating, substantially nontransmissive insulating material. Preferably, the entire block is substantially enclosed within an insulated vacuum cavity used to heat the wafer. A vacuum region is preferably provided between the heated block and the insulating material as well as between the insulating material and the chamber wall. Heat transfer across the vacuum regions is primarily achieved by radiation, while heat transfer through the insulating material is achieved by conduction. The wafer is placed on or near the heated block within the vacuum cavity for heating by conduction and radiation.

It is an advantage of this aspect of the present invention that the reactor heating profile may be statically adjusted to provide a high level of processing uniformity across a wide range of temperatures. In addition, a consistent uniformity profile may be maintained across a wide range of temperatures at vacuum pressures with a single zone heater even though radiative heat transfer is predominant and is exponentially dependent on temperature. This allows titanium silicide anneal to be performed with virtually no added nonuniformity which is a significant improvement over typical lamp systems with multiple, independently controlled heating zones. It is a further advantage that a compact heat source may be closely spaced to cold chamber walls without substantial temperature nonuniformities. This provides a smaller footprint for the reactor without diminishing uniformity and allows the chamber to be easily purged to control pressure. It is a further

20

advantage of this aspect of the present invention that energy efficiency is substantially improved without substantially increasing variance in wafer temperature uniformity across temperature ranges.

A further aspect of the present invention provides a system and method for rapidly adjusting the rate of heating provided by a heat source without substantially changing the temperature of the heat source. This may be accomplished in one embodiment of the invention by adjusting the processing pressure to adjust the heating rate. Preferably, a wafer is initially heated at a pressure that allows conductive and radiative heat transfer. As a desired processing temperature is approached, the pressure may be lowered to reduce the amount of conductive heat transfer and thereby reduce the rate of heating. In particular, it is desirable to vary the pressure in this manner across a range of low pressures where a small change in pressure has a large effect on the rate of heating. Preferably, multiple pressures are used to provide a rapid heat ramp up to a processing temperature that is then maintained at a relatively constant level.

It is an advantage of this aspect of the present invention that a wide variety of process temperature profiles may be achieved using a heater at a substantially constant temperature and/or having a relatively large thermal mass. It is a further advantage of this aspect of the present invention that rapid thermal processing may be carried out using a stable heating source.

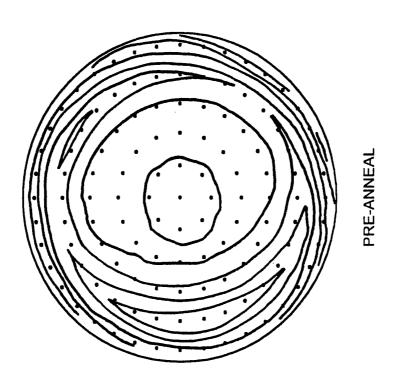

Yet another aspect of the present invention provides a system and method for uniformly heating multiple wafers at a time using a stable heating source. In one embodiment this capability is provided by using an oval shaped heating block and a resistive heater. The resistance of the heater is varied across the span of the block to provide uniform and repeatable heating for two wafers placed on the block at the same time. It is an advantage of this aspect of the present invention that wafer throughput is substantially increased without a substantial decrease in process control and uniformity.

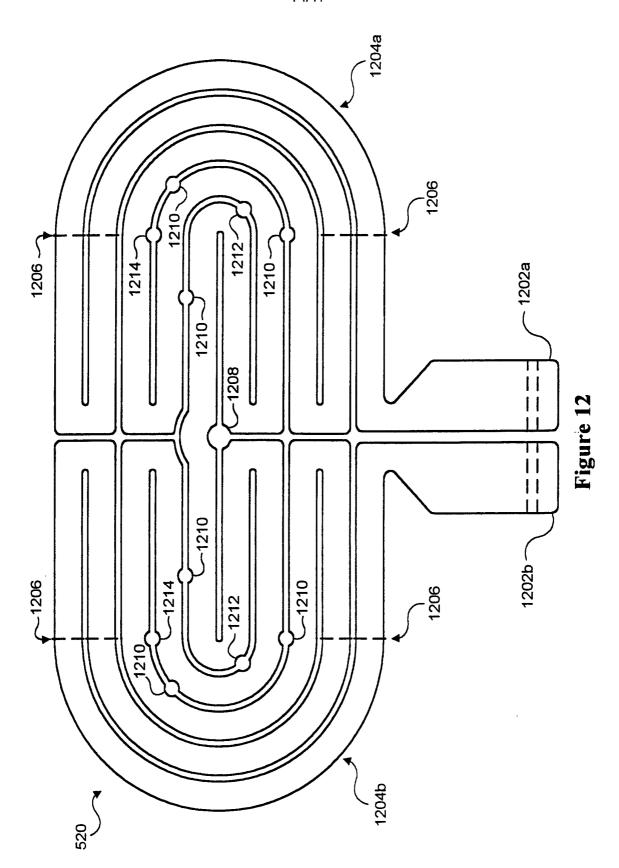

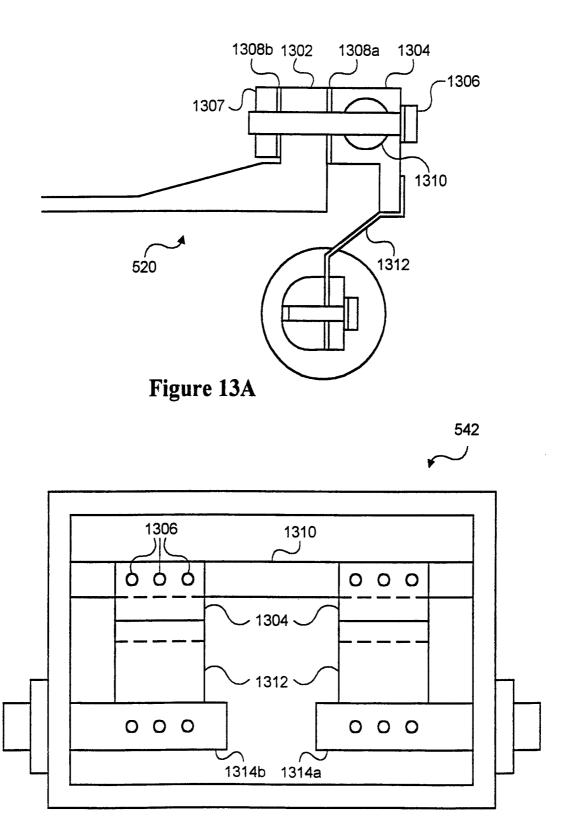

Further aspects of the present invention provide an improved system and method for deploying a fragile resistive heater. In one embodiment, a mounting block may be placed on a rod that holds it in place while allowing the block to swivel, so shear stress does not have to be placed on the heater during mounting. Further, clamps may be positioned such that thermal expansion causes compressive stress to hold the heater in

25

place without shear stress. Additionally, a flexible conductive sheet may be used to provide power to the mounting block. Preferably the conductive sheet flexes to reduce shear stress on the heater. Preferably, the heater is also mounted horizontally to avoid substantial vertical expansion.

It is an advantage of these aspects of the present invention that an expensive and fragile graphite heater may be used with substantially reduced risk of damage due to shear stress. It is a further advantage that a heater may be closely spaced to an object being heated without requiring substantial clearance for thermal expansion.

In addition, aspects of the present invention provide for improved coupling of a resistive heater to a power source. In one embodiment, a malleable conductive material is clamped between a resistive heater and power source to provide an improved electrical connection. In addition, coatings are removed from each clamped surface of the resistive heater to improve conduction between the heater and a power source.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other features and advantages of the present invention will become more apparent to those skilled in the art from the following detailed description in conjunction with the appended drawings in which:

Figure 1 is a graph of a desired wafer temperature profile for a rapid thermal annealing process;

Figure 2 shows a side cross sectional view of a conventional lamp RTP system;

Figure 3 is a side cross sectional view of a conventional heated plate rapid thermal processor;

Figure 4 is a graph of the temperature of a wafer over time as it is heated by a constant temperature heat source at a constant pressure;

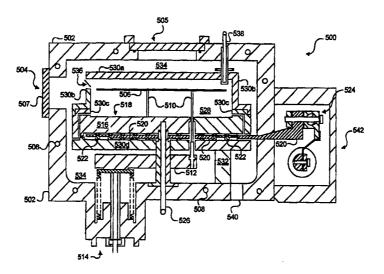

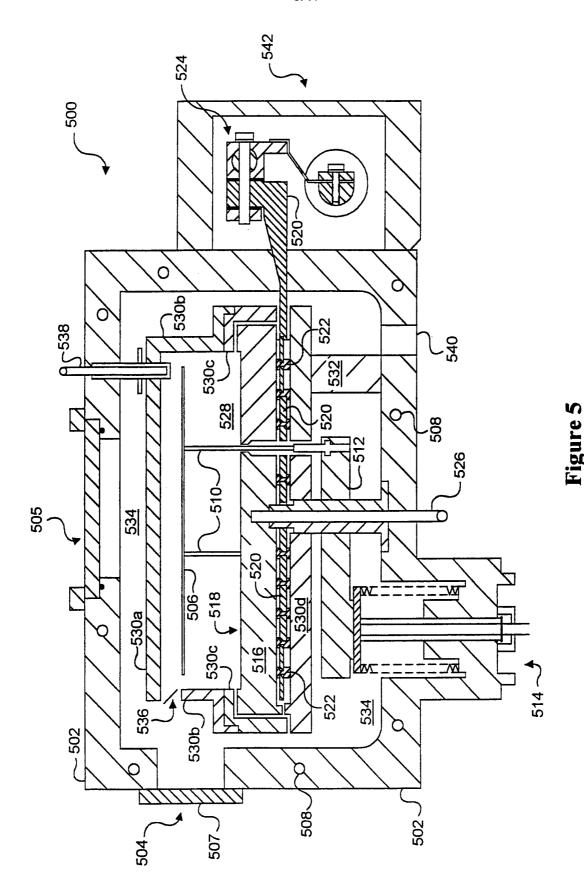

Figure 5 is a side cross sectional view of a thermal processing chamber according to a first embodiment of the present invention;

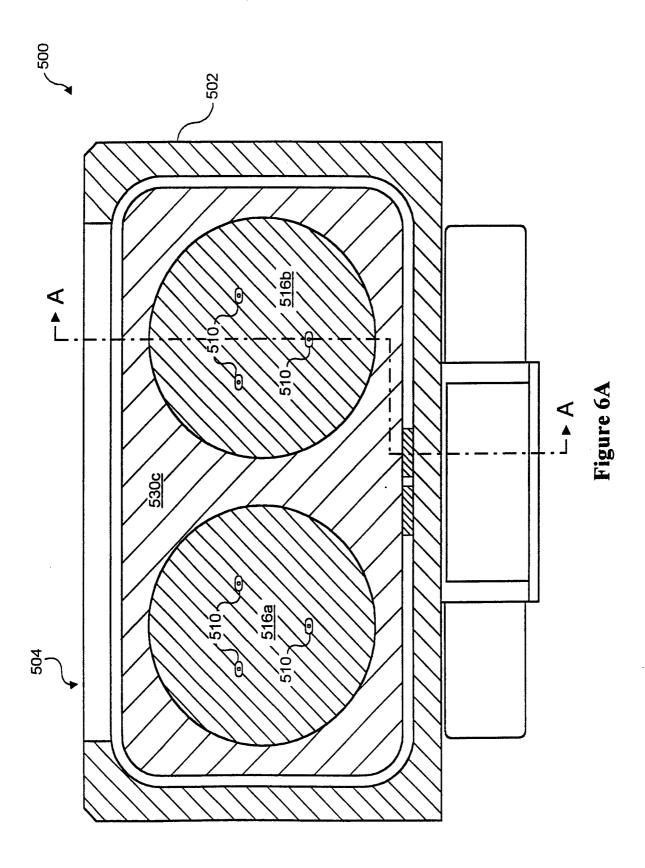

Figure 6A is a top cross sectional view of a thermal processing chamber according to the first embodiment with insulating hoods removed;

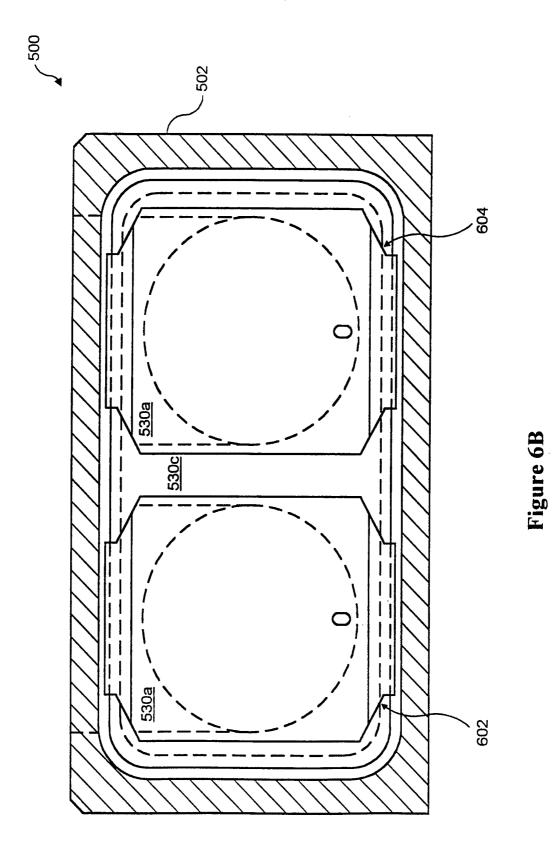

Figure 6B is a top cross sectional view of a thermal processing chamber according to the first embodiment with insulating hoods in place;

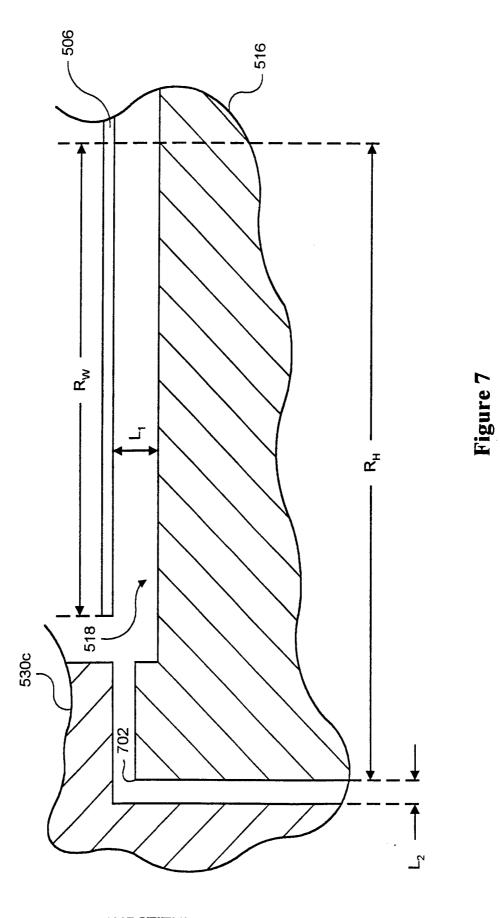

Figure 7 is a side cross sectional view of a portion of the thermal processing chamber shown in Figure 5;

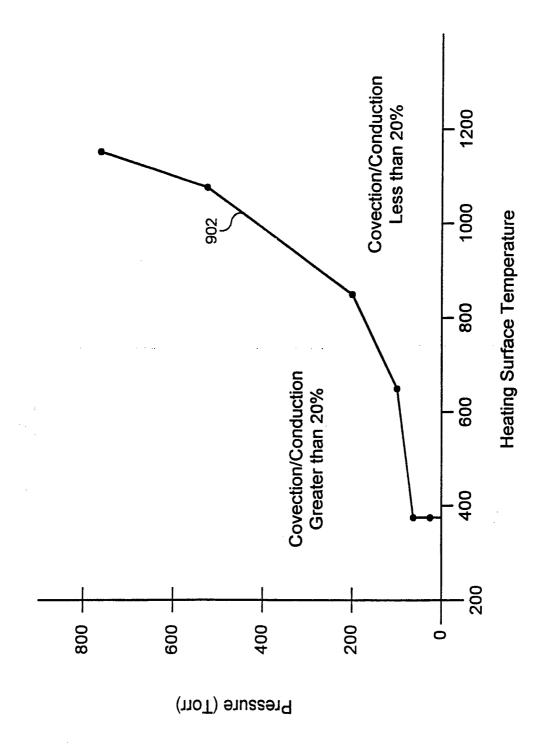

Figure 8 is a table illustrating the percent of heat transfer between two surfaces due to radiation, conduction, and convection at various pressures and temperatures; Figure 9 is a graph illustrating the relationship between heat transfer by radiation, conduction, and convection at various temperatures and pressures;

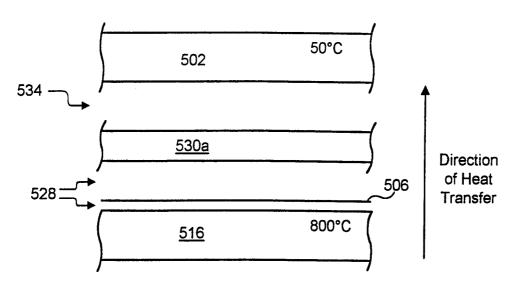

Figure 10A illustrates a one dimensional model for estimating heat transfer in the chamber according to the first embodiment;

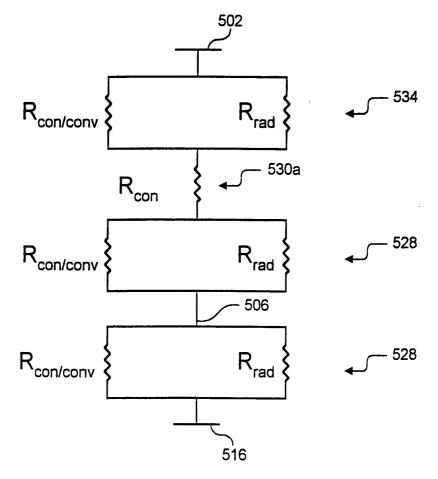

Figure 10B is a thermal equivalent circuit for the heat transfer model shown in Figure 10A;

Figure 10C is a table illustrating the temperature of chamber surfaces calculated using the model of Figure 10A at various heating surface to wafer gaps;

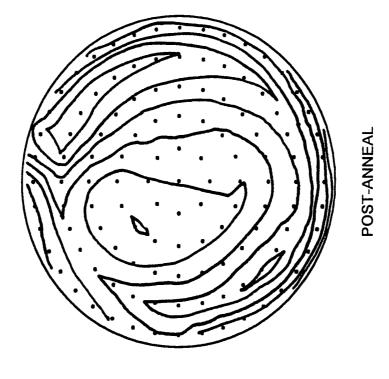

Figure 11 shows wafer sheet resistance uniformity maps before and after titanium silicide anneal in the thermal processing chamber according to the first embodiment;

Figure 12 is a top view of a resistive heater according to the first embodiment;

Figure 13A is a side cross sectional view of a heater mounting mechanism according to the first embodiment;

Figure 13B is a front view of a heater mounting mechanism according to the first embodiment;

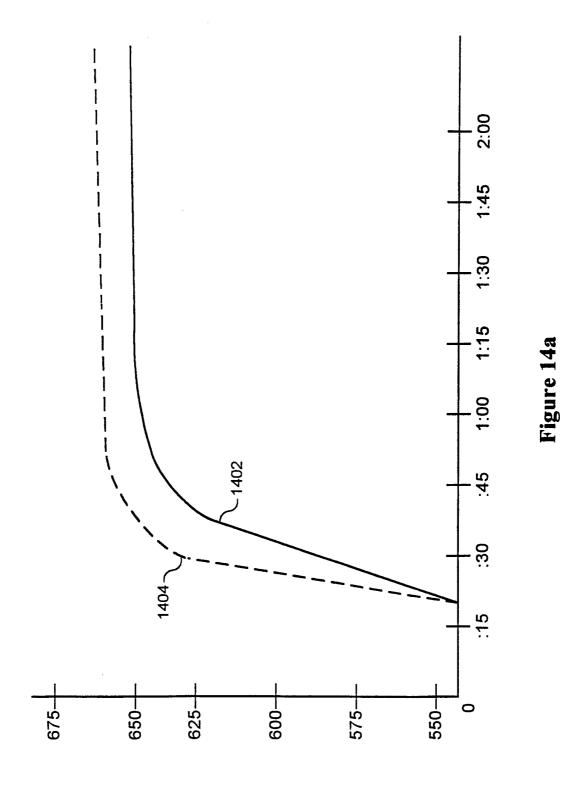

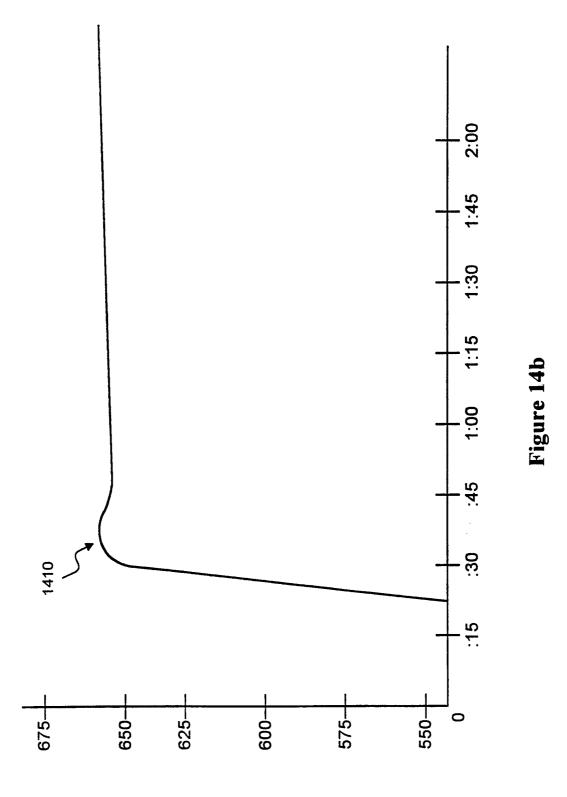

Figure 14A is a graph illustrating the temperature of wafers heated at 2 Torr and 50 Torr in the chamber according to the first embodiment; and

Figure 14B is a graph illustrating the temperature of a wafer heated at multiple pressures during processing in a chamber according to the first embodiment.

#### **DETAILED DESCRIPTION**

One aspect of the present invention allows a stable heating source to be used for rapid thermal processing. The following description is presented to enable any person skilled in the art to make and use the invention. Descriptions of specific designs are provided only as examples. Various modifications to the preferred embodiment will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other embodiments and applications without departing from the spirit and scope of the invention. Thus, the present invention is not intended to be limited to the

embodiment shown, but is to be accorded the widest scope consistent with the principles and features disclosed herein.

Figure 5 is a side cross sectional view of a thermal processing chamber, generally indicated at 500, according to the first embodiment of the present invention. Figure 6A is a top cross sectional view of the thermal processing chamber according to the first embodiment with insulating hoods removed, and Figure 6B is a top cross sectional view of the thermal processing chamber according to the first embodiment with insulating hoods in place. The first embodiment of the present invention is preferably designed for use in conjunction with the Aspen™ wafer handling system available from Mattson Technology Inc., assignee of record of the present invention. The Aspen™ system allows two wafers to be handled at a time and, as indicated in Figure 6A, the chamber according to the first embodiment has two wafer processing stations. The dashed line A in Figure 6A indicates the location of the side cross section of Figure 5 which shows one of these processing stations. Aspects of the present invention allow a single stable heat source to be used for uniformly processing two wafers at a time. As will be described further below, titanium silicide anneal may be carried out in the chamber of the first embodiment with a throughput of approximately ninety (90) wafers per hour and a process uniformity better than typical multi-zone lamp systems. Of course, a wide variety of processes may be carried out and alternative embodiments may be optimized for processing a single wafer at a time. Techniques described below may also be applied to allow uniform processing of more than two wafers at a time.

15

Referring to Figure 5, the chamber walls 502 in the first embodiment form an outer port 504 through which a semiconductor substrate, such as wafer 506, may be introduced into the chamber 500. A conventional load lock mechanism (such as provided by the Aspen<sup>TM</sup> system) may be used for inserting and removing wafer 506 through outer port 504. After the wafer has been loaded into chamber 500, a plate 507 is used to cover outer port 504. In addition, a viewing window 505 may be provided for, among other things, end point detection, in situ process monitoring and wafer top surface temperature measurement. If a window is used for these purposes, a small hole or clear section must be provided through any internal chamber surfaces, such as insulating walls, to allow the wafer

to be viewed. When a window is not used, a nontransmissive plate may be used to cover the viewing port for improved insulation.

Chamber walls 502 are relatively cold, preferably being maintained at an average temperature less than one hundred degrees Celsius (100°C). In the first embodiment, chamber walls 502 are aluminum and are cooled by cooling channels 508. Water or another cooling media may be pumped through cooling channels 508 to cool the aluminum chamber walls 502.

After the wafer is introduced into the chamber, it is placed upon narrow pins 510 which comprise silicon carbide or ceramic in the first embodiment. The pins are mounted on a pin support plate 512 that may be raised and lowered by an elevational mechanism 514, such as a pneumatic or electromechanical lift with a vacuum sealed bellows. After the wafer is loaded into the chamber and placed on pins 510, the elevational mechanism 514 is lowered to place wafer 506 close to or onto a heated block 516 for thermal processing.

The heated block preferably has a large thermal mass that provides a stable and repeatable heat source for heating wafer 506. Preferably, heated block 516 provides a heating surface 518 within the chamber that is substantially parallel to the wafer to allow heat transfer across the entire backside surface area of the wafer. Heated block 516 comprises a material that will not contaminate wafer 506 even when the wafer is placed in contact with the heated block at high temperatures (greater than 500°C) and low pressures (less than 100 Torr). In the first embodiment, heated block 516 comprises silicon carbide coated graphite, although other materials that will not react with the wafer at processing temperatures such as silicon carbide or quartz may be used as well. A material with high thermal conductivity is preferred to allow heat to uniformly dissipate through the block. Insulating techniques described below are used to prevent sharp temperature gradients from forming in the heated block due to heat losses at the edges of the block.

15

20

The heated block is approximately one (1) inch thick in the first embodiment and provides a thermal mass substantially larger than the wafer which is only about thirty five thousandths (.035) of an inch thick. It is preferred that heated block 516 be at least ten times thicker than the wafer that is being processed. This provides a stable temperature heat source for thermally processing wafer 506.

In the first embodiment, a single heated block 516 extends across most of the chamber and provides a generally rectangular heating surface large enough to process two wafers at a time as shown in Figure 6A. The exposed regions 516a and 516b in Figure 6A are portions of the same heated block. Using a single heated block provides a simplified and cost effective design. However, the heated block cannot be easily rotated to rotate the wafers during processing. Wafer rotation is often desired to enhance uniformity in semiconductor processing. The thermal processing chamber of the first embodiment provides exceptional processing uniformity even with a simplified non-rotating design. In alternative embodiments, a separate rotating heating plate may be provided for each wafer to further enhance uniformity. The wafers could also be held slightly above the heated plate and rotated on pins. However, the chamber according to the first embodiment provides excellent uniformity without rotation, so a simplified and cost effective design is preferred.

The heated block is heated by a resistive heater 520 positioned below the heated block. The resistive heater preferably comprises silicon carbide coated graphite although other materials may also be used. The design of the resistive heater is described in detail below with reference to Figure 12. Heater support pins 522 space the resistive heater from heated block 516 by a short distance (approximately .125 of an inch). A power source (not shown) is connected to the heater by a heater mounting mechanism 524 in a separate heater mounting chamber 542 described in detail below with reference to Figures 13A and 13B. Current is driven through resistive heater 520 to heat the heated block 516 which in turn acts as a stable heat source for wafer 506. The power applied to the resistive heater may be adjusted to control the temperature of the heated block. A thermocouple 526 or other temperature sensor may be used to measure the temperature of the heated block. An optical pyrometer or thermocouple (not shown) may also be used to measure the wafer temperature directly. The temperature sensors send signals indicative of the temperature of the heated block and/or wafer to a conventional temperature control system (not shown). The temperature control system then causes a transformer or other power source to apply an appropriate amount of power to the resistive heater to achieve the desired processing temperature. Typically temperatures between five hundred degrees Celsius (500°C) and

15

one thousand degrees Celsius (1000°C) are used for thermal processing in the chamber according to the first embodiment.

Of course other mechanisms may be used to provide a stable heat source. For instance, an RF coil could be used to induce a current in a conductive plate within the chamber or lamps could be used to heat the backside of a conductive block. However, the resistive heater and heated block of the first embodiment provide an exceptionally stable and durable heat source and are preferred.

In order to reduce heat loss and enhance uniformity, heated block 516 and wafer 506 are enclosed within an insulated heating chamber 528. Heating chamber 528 is formed by insulating walls 530a-d spaced apart from heater 520, heated block 516 and wafer 506. The insulating walls 530a-d preferably comprise a material that has a low thermal conductivity. In addition, insulating walls 530a-d are preferably highly reflective and substantially nontransmissive to thermal radiation (particularly in the visible and infrared regions). Thus, insulating walls 530a-d substantially prevent heat transfer by direct radiation from within heating chamber 528 to cold chamber walls 502. In the first embodiment, insulating walls 530a-d comprise opaque quartz with a thermal conductivity of approximately three and one half Watts per centimeter Kelvin (3.5 W/cmK). Opaque quartz is highly preferred in the first embodiment because it is durable and inert in virtually all processes, has a high reflectivity and low conductivity, and may be used to form an insulating wall using a single intrinsic piece of material. Opaque Silica Glass OP-1 from Nippon Silica Glass U.S.A., Inc. is an exemplary opaque quartz that may be used in the first embodiment. In contrast to transparent quartz, opaque quartz is white with a nearly ideal opaque appearance. This is due to the special structure of the material which has a well-controlled distribution of micropores in the otherwise dense matrix, scattering light and thermal radiation in a very efficient and homogeneous way. Thus, the direct transmission of radiation is nearly completely suppressed (less than 1% transmission across wavelengths from 200 to 5000 nm for 3 mm path length). The surface of the opaque quartz is preferably treated to inhibit flaking and the release of particulates. This is accomplished in the first embodiment by exposing the surfaces of the opaque quartz to high temperatures which glaze the surfaces. This forms a shallow layer (approximately 1 mm

deep) of clear durable quartz on the exterior surfaces of the insulating walls which acts as a protective coating.

Of course, other heat resistant insulating materials, such as alumina and silicon carbide, could be used for the insulating walls. In addition, the insulating walls may be formed from a transmissive material such as clear quartz coated with a reflective material such as alumina, silicon carbide, or silicon nitride. However, these alternatives tend to be less durable than glazed opaque quartz, often flake and spall, and may interfere with the chemistry of some processes.

It is preferred that the material used for the insulating walls have a thermal conductivity less than five Watts per centimeter Kelvin (5 W/cmK) in the first embodiment although it will be readily understood that the thickness, thermal conductivity, and transmission of the material may be varied to achieve a desired level of insulation. Additional insulating walls may also be positioned between the heating chamber and chamber walls to improve insulation. In particular, the heating chamber may be enclosed within multiple insulating housings with vacuum regions formed between the housings.

15

As shown in Figure 5, four opaque quartz insulating walls — a top 530a, side 530b, base 530c, and bottom 530d — are used to form heating chamber 528 in the first embodiment. The top 530a and side 530b insulating walls may be formed from a single piece of opaque quartz which provides an insulating hood that may be placed over each wafer processing station as indicated in Figure 6B. As shown in Figure 5, the base 530c and bottom 530d insulating walls are closely spaced to the heated block 516 and resistive heater 520. In the first embodiment, the base 530c and bottom 530d insulating walls substantially encapsulate the heat source except for exposed circular regions of the heating surface which are shaped to receive the wafers as shown at 516a and 516b in Figure 6A. This helps channel the heat flux from the heat source through a circular region normal to the wafer surface and reduces lateral thermal gradients. In addition, the heating surface extends radially from the circular region underneath the base insulating wall 530c. This helps isolate the wafer from any temperature drop off at the edge of the heated block. As shown in Figure 5, the heated block forms shallow pockets for receiving the wafers in the circular regions that are left exposed by the base insulating wall 530c. The pockets are between one sixteenth (.0625) and one eighth (.125) of an inch deep in the first

15

30

embodiment and may be flat, slightly concave with the center of the pocket being slightly lower (approximately.003 inches) than the perimeter of the pocket, or stepped with the center recessed relative to a ledge formed about the outer radius of the pocket. Recessed pockets help retain heat at the edges of the wafer and the pocket shape may affect temperature uniformity across the wafer surface. Nevertheless, outstanding process uniformities have been achieved at six hundred degrees Celsius (600°C) and eight hundred degrees Celsius (800°C) using both flat and recessed pocket designs.

The top cross section of Figure 6A shows the chamber of the first embodiment without the top 530a and side insulating wall 530b. Figure 6B shows a top view of the chamber with insulating hoods (which provide the top 530a and side 530b insulating walls) placed over each wafer processing station as indicated at 602 and 604. As shown in Figure 6B, a separate insulating hood is placed over each wafer pocket although a single hood enclosing both pockets may be used as well. Other configurations, such as cylindrical hoods around each wafer pocket, may also be used.

Preferably the insulating walls have a thickness in the range of from twenty five hundredths (.25) to one (1) inch although the thickness may be varied depending upon the thermal conductivity and transmission of the material. In the first embodiment, the top, side, and base insulating walls are approximately three hundred seventy five thousandths (.375) of an inch thick and the bottom insulating wall (which is close to the graphite heater) is approximately six hundred twenty five thousandths (.625) of an inch thick. The bottom insulating wall 530d is spaced from the chamber walls 502 by support leg 532. The support leg 532 also comprises an insulating material such as opaque quartz to minimize conductive heat transfer from the bottom insulating wall 530d to the chamber walls 502. While several support legs may be used, it is desirable to minimize the cross section of the thermally conductive path formed between the bottom insulating wall 530d and the bottom chamber wall by any support legs. In the first embodiment, the support leg 532 has a relatively small cross section (substantially less than 10% of the surface area of the bottom insulating wall) to prevent a large conductive path from being formed between the insulating walls and chamber walls.

The insulating walls 530a-d substantially enclose the heating chamber 528 and form an outer insulating chamber 534 between the insulating walls and the cold chamber walls.

The insulating walls form an inner port 536 between the heating chamber 528 and insulating chamber 534 to allow a wafer to be inserted into the heating chamber. A piece of insulating material may be used to cover the inner port 536 during processing to provide additional insulation. Generally, heat is transferred in the first embodiment from the heated plate 516, across the heating chamber 528 to the insulating walls 530a-d, through the insulating walls 530a-d and across the insulating chamber 534 to the cold chamber walls 502. Of course, some heat may be transferred through support leg 532 by conduction and through inner port 536 by direct radiation (unless an opaque cover is used). However, a substantial majority (more than 90%) of the radiation from the heated block 516 is intercepted by the insulating walls 530a-d and only a small portion of the bottom insulating wall (less than 10%) is in contact with the support leg. Thus, the rate of heat transfer in the first embodiment is substantially dependent upon the thermal resistance across the heating chamber 528, through the insulating walls 530a-d, and across the insulating chamber 534.

The thermal resistance across the heating chamber and insulating chamber can be adjusted by adjusting the processing pressure. Tube 538 provides a gas inlet and gas exhaust port 540 provides a gas outlet. The tube 538 is connected to a conventional gas source (not shown) and gas exhaust port 540 is connected to a conventional vacuum pump (not shown) which allows the pressure in the chamber to be controlled. In the first embodiment, pressures from seven hundred sixty (760) Torr (atmospheric) down to less 20 than one tenth (.1) of a Torr may be achieved. As will be described further below, pressures less than one hundred (100) Torr, and in particular pressures between two (2) Torr and fifty (50) Torr, are preferred in the first embodiment.

15

The low pressure, insulating walls, and other thermal properties (described further below) allow a very compact chamber design to be used with a high level of uniformity. In the first embodiment, the heated block 516 is approximately ten (10) inches wide which is only slightly wider than the wafer and its edges may be within one (1) inch of the cold chamber walls. The base insulating wall 530c is approximately one hundred twenty five thousandths (.125) of an inch from the edge of heated block 516 and the distance from the base insulating wall to the chamber wall (across the insulating chamber 534) is less than 30 half an inch. Thus, the width of the heated block is more than eighty percent (80%) of the interior width of the processing chamber. In addition, the heated block occupies more than temperature uniformity may be achieved using this compact design even though the heated block may be heated in excess of one thousand degrees Celsius (1000°C) and the chamber walls may be cooled to an average temperature of less than one hundred degrees Celsius (100°C) with water or other cooling media. However, in order to maintain an acceptable level of uniformity, the chamber dimensions and materials and the processing parameters in the first embodiment must be carefully selected to control heat transfer across heating chamber 528, through insulating walls 530a-d, and across insulating chamber 534. In order to control heat transfer in the first embodiment, it is important to understand the mechanisms of heat transfer in these three regions.

Heat may be transferred across the heating chamber and insulating chamber by conduction, radiation, and convection. Heat transfer through the insulating wall occurs primarily by conduction — the insulating wall is opaque so there is little if any radiative heat transfer, and since the insulating wall is solid, there are no convective currents. The basic mechanisms of conduction, radiation, and convection, will now be discussed with reference to the equations in Table 1 below. For further information see, e.g., F. Kreith, Principles of Heat Transfer (3d. ed 1973).

10

### Table 1

$$(1) \quad q = \frac{k \cdot \Delta T}{L}$$

(2)

$$Gr = \frac{g \cdot \rho^2 \cdot \beta \cdot L^3 \cdot \Delta T}{\mu^2}$$

(3)

$$q = \frac{\sigma(T_h^4 - T_c^4)}{[((1/\epsilon_h) - 1) + 1 + ((1/\epsilon_s) - 1)] \cdot (T_h - T_c)}$$

5

In conductive heat transfer energy exchange takes place from a region of high temperature to a region of low temperature by the kinetic motion or direct impact of molecules, as in the case of a gas at rest, and by the drift of electrons in solids. Equation 1 in Table 1 describes the conductive heat transfer between two planar surfaces where q is the rate of heat transfer,  $\Delta T$  is the difference in temperature between the two surfaces, L is the distance between the two surfaces, and k is the thermal conductivity of the material through which the heat is transferred. The heat transfer by conduction is proportional to  $\Delta T$  and is inversely proportional to L. In addition, for a gas, the thermal conductive resistance can be increased at very low pressure (the rarified gas regime) due to the increased mean free path for the gas molecules. Thus, heat transfer by conduction is reduced at very low pressures.

Natural convection involves heat transfer when a hot surface is below a cold surface and takes place through fluid currents. Heat is transferred to a portion of the fluid near the hot surface. This heated fluid expands thereby creating a lower density buoyant cell. This heated buoyant cell moves up away from the hot surface and is displaced by a cooler more dense cell. This exchange or current of hot and cold cells enhances the heat transfer.

Natural convection is a complex mode of heat transfer that is not easily calculated, although it may be estimated using a ratio called Grashof's number. A low Grashof's number (less than 10,000) generally indicates low convective heat transfer while a high Grashof's number indicates high convective heat transfer. Equation 2 in Table 1 is the equation for Grashof's number where g is the acceleration of gravity (-9.8m/s²),  $\rho$  is the density of the fluid (which is proportional to pressure and inversely proportional to temperature for a gas),  $\beta$  is the compressibility of the fluid (which is inversely proportional to temperature for a gas),  $\beta$  is the distance between the surfaces,  $\alpha$  is the temperature difference between the surfaces, and  $\beta$  is the viscosity of the fluid. Thus, heat transfer by natural convection is proportional to  $\alpha$  the pressure squared (due to the  $\alpha$ 0 term), and the distance cubed ( $\alpha$ 1). Thus, convective heat transfer is substantially eliminated at low pressures across short distances.

Heat transfer by radiation is the transfer of energy by electromagnetic waves radiated between two surfaces. An equation for heat transfer by radiation between two parallel plates is set forth as equation 3 in Table 1 where  $\sigma$  is the Stefan-Boltzmann constant (5.6697x10-8 W/(m²K⁴)),  $_{The}$  is the temperature of the hotter surface,  $_{c}$  is the temperature of the cooler surface,  $_{c}$  is the emissivity of the hotter surface, and  $_{c}$  is the emissivity of the cooler surface. Radiation is proportional to the difference between  $_{c}$  and  $_{c}$  and  $_{c}$  and  $_{c}$ .

The thermal processing chamber of the first embodiment provides enhanced processing uniformity across a wide range of temperatures and improved process repeatability by minimizing heat transfer from heated block 516 and wafer 506 to the cold chamber walls 502 while providing a high rate of heat transfer from the heating surface 518 to the wafer 506. In addition, the relative distances between wafer 506 and heating surface 518, the heating surface 518 and insulating walls 530, and insulating walls 530 and cold chamber walls 502 are carefully balanced with the processing pressure to achieve improved uniformity and repeatability.

It is desirable to achieve a high rate of heat transfer from heating surface 518 to wafer 506 in the first embodiment such that the wafer is rapidly heated to a temperature approximately equal to the temperature of the heating surface. This allows the heating surface to provide a stable and repeatable heating source for the wafer. In addition, the

temperature of the wafer can be approximated using a thermocouple embedded in the heating surface. Some conventional approaches for improving the heat transfer from a heater to a wafer involve spacing the wafer from the heater and providing a gas to induce convective currents between the heater and the wafer. However, it is also desirable in the first embodiment to minimize heat transfer from the edges of the wafer and heating surface to cold chamber walls to avoid nonuniformities in wafer temperature. In this respect, convective currents are distinctly undesirable. Further, it is desirable to minimize overall heat loss from the chamber for improved energy efficiency, while still providing a sufficient rate of thermal transfer to the wafer.

10

It is also desirable to provide a stable heating environment with a heating surface having a large thermal mass. In contrast to conventional diffusion furnaces, the thermal environment should not be greatly disturbed by the introduction of relatively cool wafers. Therefore, initially there should be a high thermal resistance between the wafer and the surrounding environment. Thereafter, it is desirable to reduce the thermal resistance between the heating surface and the wafer to provide substantially uniform heating across the wafer surface. At the same time, a high thermal resistance should be maintained at the edges of the wafer and the edges of the heating surface to avoid sharp thermal gradients and temperature nonuniformities. While active heaters, heat shields and insulation have been used at the edges of wafers and hot plates, conventional approaches are often undesirable since the heat transfer varies greatly across temperature ranges leading to under-heating of the wafer edges at some temperatures and overheating at others.

The chamber dimensions, chamber materials and processing parameters in the first embodiment are selected to overcome many of the problems associated with conventional thermal processors. In particular, the conditions set forth in Table 2 are satisfied in the first embodiment such that desired thermal characteristics are attained.

10

## Table 2

(1)

$$\frac{L_2}{L_1} > \frac{25R_W}{R_{tr}}$$

$(2) \quad \Delta T_{AV} < \frac{T_H}{2}$

(3)  $\Delta T_{Edge} < \frac{T_H}{5}$

Conductive heat transfer from the heated block 516 to the chamber walls 502 in the first embodiment is substantially reduced by adjusting the processing pressure and distances between the heated block and surrounding chamber surfaces. However, it is desirable to have significant conductive heat transfer from the heating surface 518 to the wafer 506. Figure 7 illustrates a portion of the chamber of Figure 5 and shows the arrangement of heated block 516, wafer 506 and base insulating wall 530c. L<sub>1</sub> indicates the distance from the heating surface to the wafer and L<sub>2</sub> indicates the average distance from the side edge of the heated block to the nearest heat receiving surface in the chamber (which in the first embodiment is base insulating wall 530c). In order to reduce conductive heat loss at the edge of the heated block and to reduce heat loss by natural convection, it is desirable to increase L<sub>2</sub> and decrease pressure. However, in order to conductively heat wafer 506 it is desirable to increase pressure and decrease L1. Further, to the extent that there are gradients at the edge of heated block 516, it is desirable to have the radius of the wafer,  $R_{w}$ , be smaller than the average distance from the center of the wafer to the edge of the heated block,  $R_{\rm H}$  to isolate the wafer from the gradients. These factors are balanced in the first embodiment according to the first condition in Table 2 where  $L_2$  is the average distance from the edge of the heated block to the nearest chamber surface receiving heat,  $L_1$  is the

distance between the wafer and the heating surface,  $R_{\rm w}$  is the radius of the wafer, and  $R_{\rm H}$  is the average distance from the center of the wafer to the nearest edge of the heated block.

Generally, if this condition is satisfied,  $L_2$  will be greater than  $L_1$  so there will be a higher thermal resistance to conduction between the heated block and surrounding chamber surfaces than between the heating surface and the wafer. At higher pressures  $L_2$  must be larger since convective heat loss from the heated block will be larger. However, R<sub>W</sub>/R<sub>H</sub> can be decreased to some extent to isolate the wafer from any thermal gradients at the edge of the heated block. In the first embodiment L<sub>2</sub> is approximately one hundred twenty five thousandths (.125) of an inch and  $L_1$  is less than five thousandths (.005) of an inch (preferably wafer 506 is placed substantially in contact with heated block 516). Thus, L<sub>2</sub> is much greater than  $L_1$  and  $L_2/L_1$  is at least twenty five (25).  $R_W$  is approximately four (4) inches and R<sub>H</sub> is at least 5 inches (the smallest radius from the center of the wafer to the edge of the heated plate is approximately 5 inches and due to the elongated shape of the heated block, the average radius R<sub>H</sub> would be larger). Therefore, R<sub>W</sub>/R<sub>H</sub> is at least eight tenths (.8). Thus, 25  $R_W/R_H$  is less than twenty (20) which is less than the ratio of  $L_2/L_1$ (which is more than 25) in accordance with the first condition set forth in Table 2. A very small  $L_1$  (less than .01 inch) is preferred in the first embodiment since the above condition may be satisfied with a smaller  $L_2$  and  $R_{\rm H}$  and therefore a compact chamber design may be used. Proximity heating is avoided in the compact chamber design of the first embodiment to avoid temperature nonuniformities induced by conductive heat losses. While conductive heat losses are limited in the first embodiment, conduction does play an important role in heating the wafer.

Convective heat transfer, on the other hand, is substantially eliminated in the first embodiment since vertical chimney effects along the edges of the heated block might otherwise induce unacceptable thermal gradients. In addition, by substantially eliminating convection the energy efficiency of the chamber is greatly enhanced. Further, since the wafer is preferably positioned very close to the heating surface, convection does not play a major role in heating the wafer. Therefore, eliminating convective heat losses improves the efficiency of the system without substantially degrading wafer heating. Convective heat transfer is substantially eliminated in the first embodiment by lowering the processing pressure. As pressure is lowered from atmospheric pressure, convective heat transfer is

reduced. At some point, convective heat transfer is substantially eliminated and further reduction in pressure does not substantially reduce heat transfer (unless the pressure is reduced to a very low value within the rarified gas regime which reduces conductive heat transfer). The pressure in the first embodiment is maintained below the level at which convective heat transfer is substantially eliminated. Preferably, the pressure is less than eighty (80) Torr with pressures of fifty (50) Torr, ten (10) Torr, and two (2) Torr typically being used in processing as will be described further below.

At very low pressures, heat transfer is further reduced. In the first embodiment, this phenomena reduces heat transfer between the heated plate and wafer at pressures less than about ten (10) Torr. It is believed that this phenomenon is based upon the thermal conductive properties of a gas between two closely spaced surfaces where the mean free path of the molecules in the gas is on the order of the distance between the surfaces (the rarified gas regime). At very low pressures (when the mean free path is the largest) and at small distances, it is believed that the equation for conductive heat transfer (shown in Table 1) must be modified to reflect the fact that the mean free path of molecules in the gas is constrained by the closely spaced surfaces.

It is believed that the first equation in Table 1 must be modified to explain the variance in the heating rate across low pressures when the surfaces are closely spaced. In particular, it is believed that an effective distance,  $L_{\rm eff}$ , must be substituted for the geometric distance, L, between the surfaces (which in this case is the distance between the wafer and the heating surface). The effective distance,  $L_{\rm eff}$ , is equal to the geometric distance, L, plus twice the mean free path of molecules in the gas,  $2\lambda$ . Since conductive heat transfer is inversely proportional to  $L_{\rm eff}$ , changing the mean free path by altering pressure can drastically change the rate of conductive heating when the mean free path is significant relative to the geometric distance, L. This occurs at low pressures (generally less than 50 Torr and less than ten (10) Torr in the first embodiment) when the wafer is placed very near (and preferably in contact with) the heating surface.

Therefore, both conduction and convection are reduced in the first embodiment by reducing chamber pressure. Preferably, conduction and convection account for less than twenty percent (20%) of the heat transfer from the heated block to the insulating walls. The effect of pressure on heat transfer may be illustrated using a model of heat transfer

between two parallel surfaces. The first surface is assumed to be a graphite block at six hundred degrees Celsius (600°C) or eight hundred degrees Celsius (800°C) and the second surface is assumed to be a conductive wall at fifty degrees Celsius (50°C). The material properties and dimensions were held constant, and heat transfer by radiation, convection and conduction was estimated at various pressures. It will be understood that this example is merely illustrative of the effects of pressure on heat transfer and is not representative of actual heat transfer in the first embodiment. Figure 8 is a table showing the estimated percentages of heat transfer due to radiation, convection and conduction at pressures of two (2) Torr, two hundred (200) Torr, and seven hundred sixty (760) Torr with graphite block temperatures of six hundred degrees Celsius (600°C) and eight hundred degrees Celsius (800°C). The total estimated heat flux and Biot Number are also shown. The Biot Number is equal to (h·L)/k where h is the convective heat transfer coefficient (which decreases with pressure), L is the thickness of the graphite block, and k is the thermal conductivity of the block. A low Biot Number indicates good temperature uniformity across the block. Thus, a thermally conductive block held at low pressure provides the most uniform heating source. Thus, for uniform wafer heating it is desirable to lower pressure in the first embodiment so long as a sufficient heat flux to the wafer is maintained. Figure 9 is a graph illustrating the pressure at which conduction and convection are estimated to account for less than twenty percent (20%) of heat transfer. For the first embodiment, the pressure in the heating chamber is preferably maintained below the level indicated by line 902 in Figure 9 during processing.

15

As a result, radiation is the primary mode of heat transfer to the insulating walls in the first embodiment. Radiative heat transfer from the heated block to the insulating walls is proportional to the temperature of the heated block raised to the fourth power, T<sub>H</sub><sup>4</sup>, minus the temperature of the insulating walls raised to the fourth power, T<sub>i</sub><sup>4</sup>. Due to the exponential dependence on temperature, it is desirable to reduce the average temperature difference ΔT<sub>AV</sub> between the heated block and radiation receiving chamber surfaces (in this case, the insulating walls). As shown in the second condition in Table 2, it is desirable to limit ΔT<sub>AV</sub> to less than one half the average temperature of the heated block (THE/2) to limit radiative losses and potential induced thermal gradients. ΔT<sub>AV</sub> can be defined more generally as the average temperature of a heating surface used to heat a wafer minus the

average temperature of cooler chamber surfaces that receive direct radiation from the heating surface.  $\Delta T_{AV}$  can be measured experimentally using thermocouples to sense the temperatures across the heating surface and radiation receiving surfaces.

The second condition in Table 2 is satisfied in the first embodiment by using substantially nontransmissive insulating walls with a low thermal conductance to block substantially all direct radiation from the heated block (across more than 90% of the heating surface of the heated block). Generally, the radiation must be absorbed by the insulating walls 530a-d, conducted through the insulating walls 530a-d, and radiated across the insulating chamber 534 to reach the cold chamber walls 502. Further, the heating chamber 528 and insulating chamber 534 are maintained at low pressure in the first embodiment (less than 100 Torr and typically less than 20 Torr). Thus, heat must be transferred from the heated block 516 across a first vacuum region (i.e., the heating chamber 528) to the insulating walls 530a-d. The heat must then be conducted through the insulating walls 530a-d which have a low thermal conductivity (preferably less than 5 W/cmK). Then the heat must be transferred across a second vacuum region (i.e., the insulating chamber 534) to reach the cold chamber walls 502. This double vacuum insulation allows the insulating walls 530a-d to be maintained at an average temperature that is more than one half the average temperature of the heated block at thermal equilibrium even though a cold outer chamber wall is used. This reduces the rate of 20 radiative heat transfer from the heated block (and wafer) to the insulating walls which otherwise may cause unacceptable temperature nonuniformities.

Figure 10A is a one dimensional heat transfer model which is used to illustrate heat transfer in the first embodiment from the heated block 516 across a portion of the heating chamber 528 to the wafer 506, from the wafer 506 across the rest of the heating chamber 528 to the top insulating wall 530a, through the insulating wall 530a, across the insulating chamber 534 and to the chamber wall 502. For this example, the heated block is assumed to be at eight hundred degrees Celsius (800°C) and the chamber wall is at fifty degrees Celsius (50°C). The gas in the chamber is nitrogen at ten (10) Torr. The emissivity of the heated block is approximately eight tenths (.8); the emissivity of the wafer is approximately sixty nine hundredths (.69); the emissivity of the top insulating wall is approximately five hundredths (.05); and the emissivity of the aluminum chamber walls is approximately

25

twenty five hundredths (.25). The wafer is thirty five thousandths (.035) of an inch thick and the top insulating wall is three hundred seventy five thousandths (.375) of an inch thick. The insulating wall has a thermal conductivity of three and one half Watts per centimeter Kelvin (3.5 W/cmK).

Figure 10B illustrates a thermal "equivalent circuit" for the heat transfer model with thermal resistances shown as resistors. Figure 10B illustrates that parallel paths of conduction/convection,  $R_{\text{con/conv}}$ , and radiation,  $R_{\text{rad}}$ , allow heat transfer from the heating surface to the wafer, from the wafer to the insulating wall, and from the insulating wall to the chamber wall. Heat transfer through the insulating wall 530a is by conduction only. The equations for conduction, convection and radiation described previously may be used to determine the theoretical heat transfer across the four regions (block to wafer, wafer to insulating wall, through insulating wall, and insulating wall to chamber walls) with the temperatures of the wafer,  $T_{\rm w}$ , lower surface of the insulating walls,  $T_{\rm L}$ , and upper surface of the insulating walls,  $T_{\rm U}$ , and the heat flux being unknowns. This leads to four equations with four unknowns which can be solved using techniques known in the art.

Figure 10C is a table of temperatures calculated using the above heat transfer model for given distances between the heated block and wafer at a given heating surface temperature (800°C) and pressure (10 Torr). As shown in Figure 10C, the average temperature of the top insulating wall is maintained at an average temperature over six hundred degrees Celsius (600°C) with an average heating surface temperature <sub>THE</sub> of eight hundred degrees Celsius (800°C). Therefore, ΔT<sub>AV</sub> is less than two hundred degrees Celsius (200°C) which easily satisfies the second condition in Table 2. This greatly reduces radiative heat losses (by a factor of roughly two or three) relative to the radiative heat losses in the absence of the insulating wall.

It will also be noted from Figure 10C that the wafer temperature,  $T_w$ , is very close to the temperature of the heating surface when the wafer is positioned close to the heating surface. This indicates a low conductive thermal resistance for small gaps which, as described above with reference to the first condition in Table 2, is desired in the first embodiment. Preferably, the wafer is placed in substantial contact with the heating surface during processing. The wafer temperature  $T_w$  quickly decreases as the wafer is moved away from the heating surface at ten (10) Torr as indicated in Figure 10C. This is due to

the high conductive resistance across the gap at low vacuum pressure. Thus, the gap should be limited as necessary to achieve a desired wafer temperature.

The base insulating wall 530c is closer to the heated block than the top insulating wall 530a used in the heat transfer model of Figure 10. Therefore, the base insulating wall 530c tends to be hotter than the top insulating wall 530a and radiation from the edge of the heating surface is further reduced. This is desirable since radiative losses from the edge of the heating surface can lead to undesired lateral thermal gradients. In order to avoid thermal gradients due to excessive edge radiation, it is preferred that the third condition in Table 2 be satisfied where  $T_{\text{edge}}$  is the average temperature of chamber surfaces receiving direct radiation from the corner edge of the heating surface (shown at 702 in Figure 7), and  $_{ ext{THE}}$  is the average temperature of the heating surface. As indicated by the third condition, it is preferred that the average temperature  $T_{\text{edge}}$  of all chamber surfaces that receive direct radiation from corner edge 702 have a relatively high temperature at thermal equilibrium relative to the heating surface. To the extent that there are significant radiative edge losses, it is desirable to extend the heating surface 518 radially outward from the wafer edges in order to compensate (i.e., by increasing R<sub>H</sub>/R<sub>w</sub>). The third condition in Table 2 is satisfied in the first embodiment since substantially all direct radiation from the corner edge 702 of the heating surface is intercepted by the closely spaced base insulating wall 530c. Unlike many conventional systems, there is no direct radiative path from the edge of the heated block to cold chamber walls or other chamber surfaces with temperatures less than one half of the average temperature of the heated block.

In the first embodiment all of the conditions set forth in Table 2 are satisfied and pressure is reduced to very low levels. This provides a very energy efficient chamber and allows a compact design to be used. In addition, a high level of wafer temperature uniformity is maintained across a range of temperatures even though the cold chamber walls are relatively close to the edges of the heated block and wafer.