## (12) 发明专利

(10) 授权公告号 CN 110419093 B

(45) 授权公告日 2023.12.01

(21) 申请号 201880017633.X

(51) Int.CI.

(22) 申请日 2018.03.21

H01L 21/02 (2006.01)

(65) 同一申请的已公布的文献号

H01L 21/3065 (2006.01)

申请公布号 CN 110419093 A

H01L 21/311 (2006.01)

(43) 申请公布日 2019.11.05

(56) 对比文件

(30) 优先权数据

CN 1707748 A, 2005.12.14

62/482,872 2017.04.07 US

US 2006286776 A1, 2006.12.21

(85) PCT国际申请进入国家阶段日

US 5273920 A, 1993.12.28

2019.09.11

US 9484202 B1, 2016.11.01

(86) PCT国际申请的申请数据

CN 102205942 A, 2011.10.05

PCT/US2018/023474 2018.03.21

JP 2000031058 A, 2000.01.28

(87) PCT国际申请的公布数据

JP 2008192724 A, 2008.08.21

W02018/187034 EN 2018.10.11

JP H07252657 A, 1995.10.03

(73) 专利权人 应用材料公司

CN 103700576 A, 2014.04.02

地址 美国加利福尼亚州

US 2016343580 A1, 2016.11.24

(72) 发明人 程睿 A·B·玛里克 陈一宏

US 2013337236 A1, 2013.12.19

(74) 专利代理机构 上海专利商标事务所有限公司 31100

US 2010075503 A1, 2010.03.25

专利代理人 汪骏飞 侯颖婧

审查员 何欢

权利要求书2页 说明书12页 附图6页

## (54) 发明名称

侧壁间隔件内的所述图案化特征。

通过改善氧化硅的成核/粘附来改善膜粗糙度的处理方法

## (57) 摘要

在一个实施方式中，提供了一种在处理腔室中在基板上形成非晶硅层的方法。所述方法包括在基板上方沉积预确定的厚度的牺牲介电层。所述方法进一步包括通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征。所述方法进一步包括对所述图案化特征进行等离子体处理。所述方法进一步包括在所述图案化特征以及所述基板的所述暴露表面上沉积非晶硅层。所述方法进一步包括使用各向异性蚀刻选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的

CN 110419093 B

1. 一种在处理腔室中在基板上形成非晶硅层的方法,包括:

在基板上沉积预确定的厚度的牺牲介电层;

通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征;

在所述图案化特征上形成自组装单层(“SAM”);

在所述SAM以及所述基板的所暴露的上表面上沉积非晶硅层;以及

使用各向异性蚀刻处理选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的侧壁间隔件内的所述图案化特征。

2. 如权利要求1所述的方法,进一步包括在所述图案化特征上形成所述SAM之前对所述图案化特征进行等离子体处理,其中执行所述等离子体处理包括:

使处理气体流入所述处理腔室中;以及

在所述处理腔室中产生等离子体以处理所述基板的所述图案化特征。

3. 如权利要求2所述的方法,其中所述处理气体包括氩。

4. 如权利要求2所述的方法,其中所述处理气体包括氩、氢、氮、一氧化二氮、氨以及以上项的组合中的一种。

5. 如权利要求2所述的方法,其中对所述图案化特征进行所述等离子体处理和在所述图案化特征以及所述基板的所暴露的上表面上沉积所述非晶硅层是在同一个处理腔室中进行的。

6. 如权利要求1所述的方法,其中所述牺牲介电层包括氧化硅。

7. 如权利要求1所述的方法,其中在所述图案化特征以及所述基板的所暴露的上表面上沉积所述非晶硅层包括将所述图案化特征暴露于硅前驱物以形成具有包括氢的可脱气物质的非晶硅膜。

8. 如权利要求7所述的方法,进一步包括将所述非晶硅膜暴露于惰性除气环境以从所述非晶硅膜去除所述可脱气物质来形成经除气的非晶硅膜。

9. 如权利要求8所述的方法,其中所述硅前驱物包括乙硅烷、丙硅烷、丁硅烷、异丁硅烷、新戊硅烷、环戊硅烷、己硅烷、环己硅烷以及以上项的组合中的一种或多种。

10. 如权利要求9所述的方法,其中所述硅前驱物是乙硅烷。

11. 如权利要求8所述的方法,其中所述惰性除气环境基本上由惰性气体组成。

12. 如权利要求11所述的方法,其中所述惰性气体包括氩、氦和氮中的一种或多种。

13. 如权利要求12所述的方法,其中于所述硅前驱物和所述惰性除气环境中的每一个的暴露发生在50毫托至200托的压力范围内。

14. 如权利要求13所述的方法,其中于所述硅前驱物和所述惰性除气环境中的每一个的暴露发生在350摄氏度至700摄氏度的温度范围内。

15. 如权利要求14所述的方法,其中每次于所述硅前驱物和所述惰性除气环境中的暴露都生长出具有在5Å至20Å的范围内的厚度的所述经除气的非晶硅膜。

16. 如权利要求15所述的方法,进一步包括从所述基板去除所述图案化特征。

17. 如权利要求16所述的方法,其中通过使用热化学气相沉积处理进行在所述图案化

特征以及所述基板的所暴露的上表面上沉积所述非晶硅层。

18.一种在处理腔室中在基板上形成非晶硅层的方法,包括:

在基板上沉积预确定的厚度的牺牲介电层;

通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征;

对所述图案化特征进行等离子体处理;

在所述等离子体处理的图案化特征上形成自组装单层(“SAM”);

在所述SAM以及所述基板的所暴露的上表面上沉积非晶硅层;以及使用各向异性蚀刻处理选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的侧壁间隔件内的所述图案化特征。

## 通过改善氧化硅的成核/粘附来改善膜粗糙度的处理方法

### 技术领域

[0001] 本文所述的实施方式整体涉及集成电路的制造，并且具体地涉及间隔件的形成。

### 背景技术

[0002] 集成电路已发展成可在单个芯片上包括数百万个晶体管、电容器和电阻器的复杂器件。芯片设计的发展一直涉及更快的电路和更高的电路密度。对具有更大的电路密度的更快的电路的需求对用来制造这种集成电路的材料提出了相应的需求。具体地，随着集成电路部件的尺寸减小到亚微米级，现在必须使用低电阻率导电材料以及低介电常数绝缘材料以从此类部件中获得合适的电气性能。然而，这些低介电常数绝缘材料通常存在粗糙度问题，这增加了随后沉积的膜中的粗糙度并可能影响膜之间的粘附。

[0003] 因此，需要形成具有减小的粗糙度的薄膜的改善的方法。

### 发明内容

[0004] 本文所述的实施方式整体涉及集成电路的制造，并且具体地涉及间隔件的形成。在一个实施方式中，提供了一种在处理腔室中在基板上形成非晶硅层的方法。所述方法包括在基板上沉积预确定的厚度的牺牲介电层。所述方法进一步包括通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征。所述方法进一步包括对所述图案化特征进行等离子体处理。所述方法进一步包括在所述图案化特征以及所述基板的暴露上表面上沉积非晶硅层。所述方法进一步包括使用各向异性蚀刻处理选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的侧壁间隔件内的所述图案化特征。

[0005] 在另一个实施方式中，提供了一种在处理腔室中在基板上形成非晶硅层的方法。所述方法包括在基板上沉积预确定的厚度的牺牲介电层。所述方法进一步包括通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征。所述方法进一步包括在所述图案化特征上形成自组装单层（“SAM”）。所述方法进一步包括在所述SAM以及所述基板的暴露上表面上沉积非晶硅层。所述方法进一步包括使用各向异性蚀刻处理选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的侧壁间隔件内的所述图案化特征。

[0006] 在又一个实施方式中，提供了一种在处理腔室中在基板上形成非晶硅层的方法。所述方法包括在基板上沉积预确定的厚度的牺牲介电层。所述方法进一步包括通过去除所述牺牲介电层的部分以暴露所述基板的上表面来在所述基板上形成图案化特征。所述方法进一步包括对所述图案化特征进行等离子体处理。所述方法进一步包括在所述等离子体处理的图案化特征上形成自组装单层（“SAM”）。所述方法进一步包括在所述SAM以及所述基板的暴露上表面上沉积非晶硅层。所述方法进一步包括使用各向异性蚀刻处理选择性地从所述图案化特征的上表面和所述基板的所述上表面去除所述非晶硅层以提供填充在由所述非晶硅层形成的侧壁间隔件内的所述图案化特征。

[0007] 附图简要说明

[0008] 为了能够详细地理解本公开的上述特征的方式,可以通过参考实施方式获得上面简要地概述的实施方式的更具体的描述,其中一些实施方式在附图中示出。然而,应当注意,附图仅示出了本公开的典型实施方式,因此不应视为限制本公开的范围,因为本公开可以允许其它同等有效的实施方式。

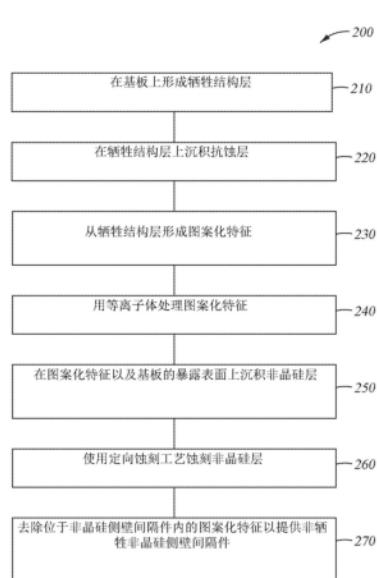

[0009] 图1描绘了可以用于实践本文所述的实施方式的设备的示意图;

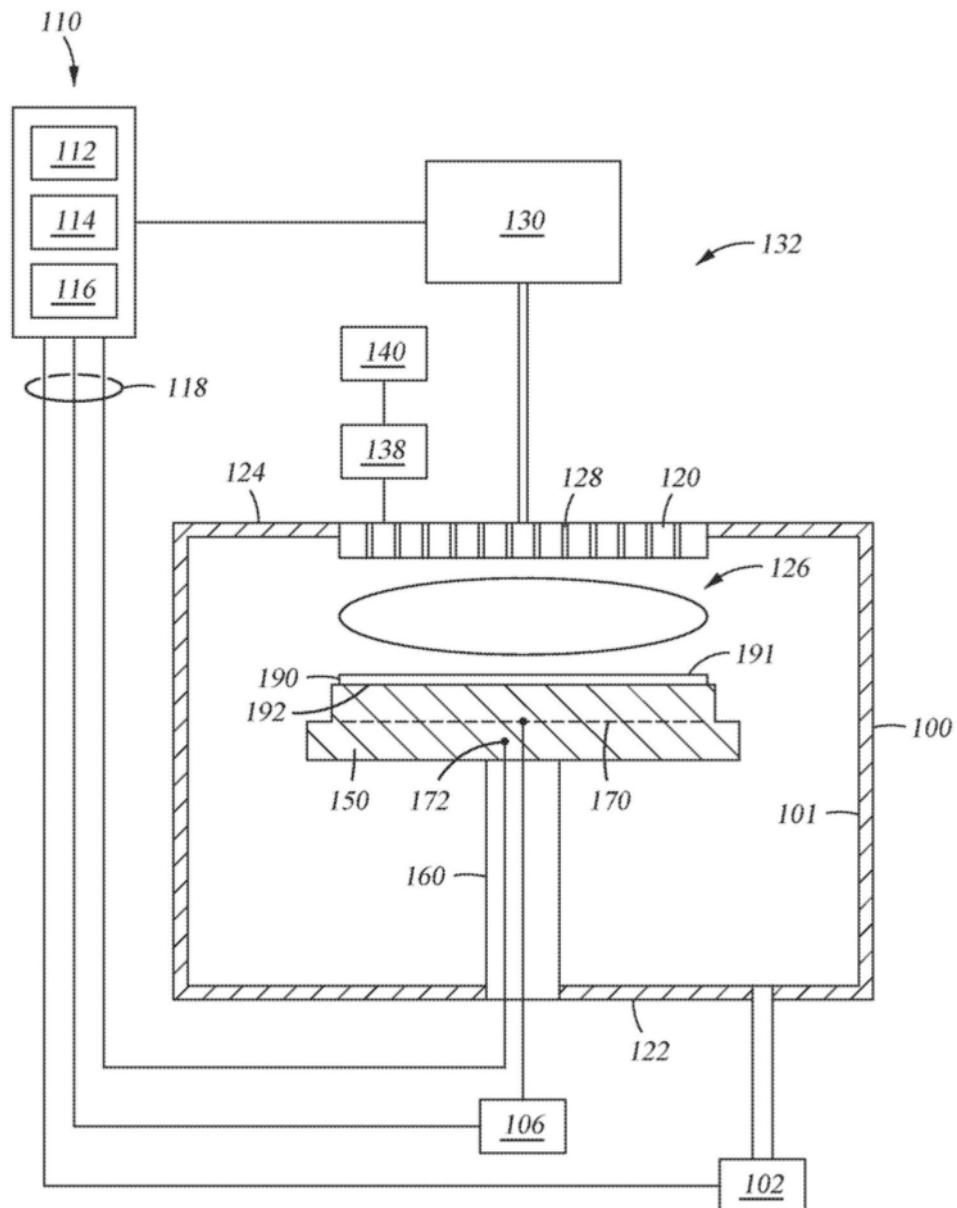

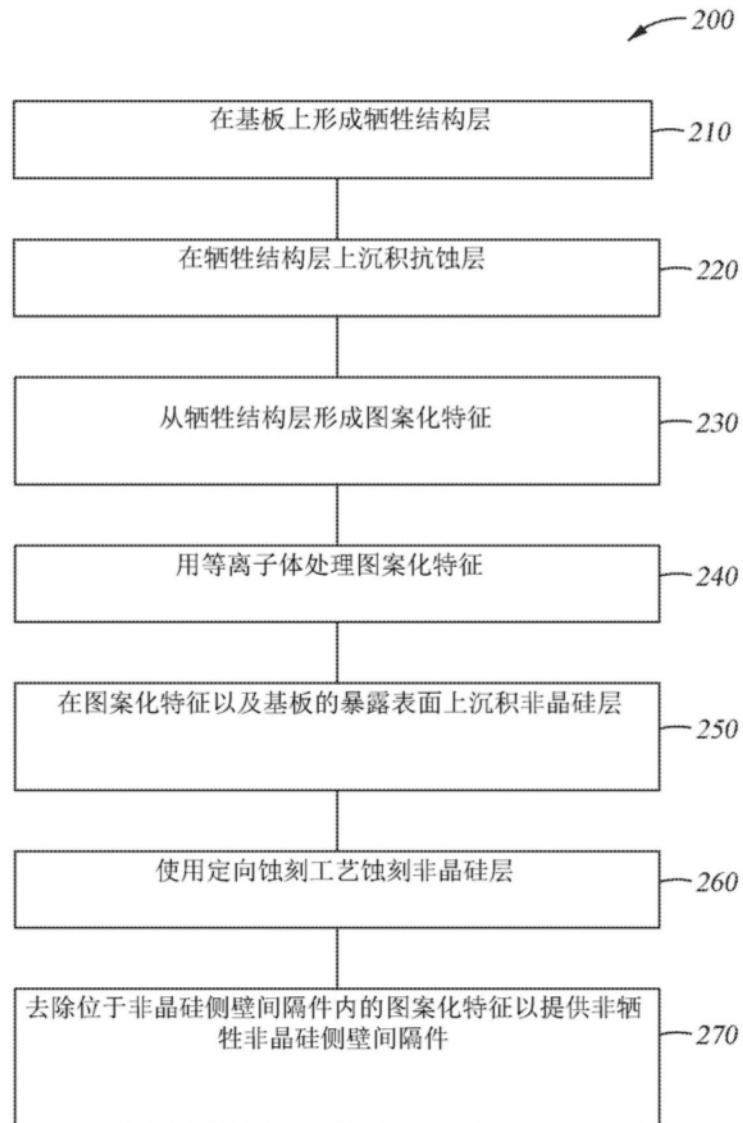

[0010] 图2是描绘如本文所述的用于用等离子体处理形成间隔件的方法的一个实施方式的处理流程图;

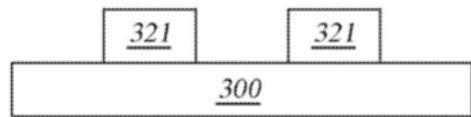

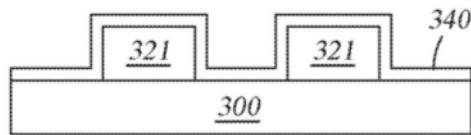

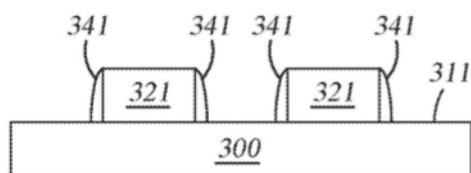

[0011] 图3A-3E是根据图2的处理流程图形成的结构的示意性侧视图;

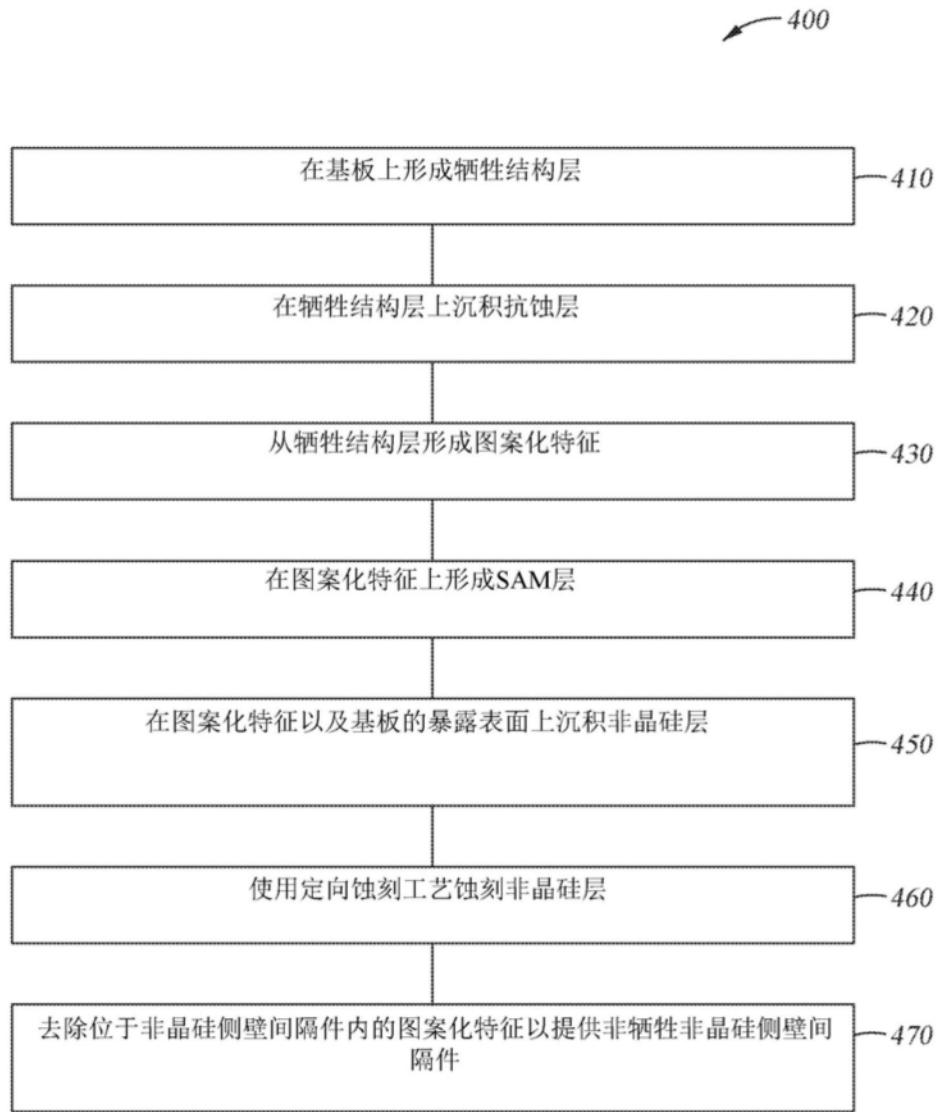

[0012] 图4是描绘根据本文所述的实施方式的用于间隔件形成的方法的另一个实施方式的处理流程图;

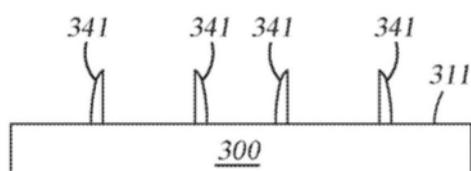

[0013] 图5A-5F是根据图4的处理流程图形成的结构的示意性侧视图;以及

[0014] 图6是描绘根据本文所述的实施方式的用于间隔件形成的方法的另一个实施方式的处理流程图。

[0015] 为了便于理解,在可能情况下,使用相同的附图标记标示各图共有的相同要素。设想的是,一个实施方式的元素和特征可以有利地并入其它实施方式而无需进一步叙述。

## 具体实施方式

[0016] 以下公开内容描述了膜和用于在基板上沉积间隔件膜的技术。某些细节在以下描述并在图1至图6中阐述以提供对本公开的各种实施方式的透彻理解。描述通常与沉积和蚀刻处理相关联的所熟知的结构和系统的其它细节未在以下公开内容中阐述,以免不必要地模糊对各种实施方式的描述。

[0017] 附图中所示的许多细节、尺寸、角度和其它特征仅是对特定实施方式的说明。因此,在不脱离本公开的精神或范围的情况下,其它实施方式可以具有其它细节、部件、尺寸、角度和特征。另外,可以在没有下面描述的若干细节的情况下实践本公开的进一步实施方式。

[0018] 下面将参考可以通过使用任何合适的薄膜沉积系统进行的热CVD和/或等离子体增强化学气相沉积(PECVD)处理来描述本文所述的实施方式。合适的系统的示例包括可从加利福尼亚州圣克拉拉市应用材料公司(Applied Materials, Inc. of Santa Clara, Calif)购得的可使用DXZ®处理腔室的CENTURA®系统、PRECISION5000®系统、PRODUCER®系统、PRODUCER®GT™系统、PRODUCER®XP Precision™系统和PRODUCER®SE™系统。也可以采用能够执行热CVD和PECVD处理的其它工具以受益于本文所述的实施方式。另外,可以使用能够实现本文所述的热CVD和/或PECVD处理的任何系统以获利。本文所述的设备描述是说明性的,并且不应当被理解或解释为限制本文所述的实施方式的范围。

[0019] 在氧化物堆叠上沉积非晶硅膜期间,在非晶硅膜和下面的氧化膜之间观察到粗糙度和粘附性问题。本文所述的实施方式中的一些提供了在非晶硅沉积之前处理下面的氧化物膜的方法,这减小了在氧化物上的非晶硅膜的粗糙度以及改善非晶硅与氧化物堆叠之间的粘附/成核。在本公开的一些实施方式中,为了减小粗糙度,就在沉积非晶硅膜之前,将下

面的氧化物膜暴露于等离子体处理和/或自组装单层(SAM)处理。希望不受理论束缚,但是据信,等离子体处理工艺改变存在于氧化硅表面上的悬空键以减小粗糙度并改善粘附性。

[0020] “自组装单层”(“SAM”)一般是指附着(例如,通过化学键)到表面的并相对于该表面且甚至相对于彼此采取优选的取向的分子层。SAM通常包括有组织两亲分子层,其中分子的一端,即“头基”,表现出对基板的特定的可逆的亲和力。头基的选择将取决于SAM的应用,其中SAM化合物的类型是基于所利用的基板。一般,头基连接到烷基链,其中尾部或“末端”可以被官能化,例如,以改变润湿性和界面性质。已经表明,自组装单层有足够的时间来完全地覆盖表面,从而改变表面性质。形成SAM的分子将选择性地附着到在另一种材料上方的一种材料(例如,硅对比电介质),并且如果具有足够的密度,那么可以成功地阻挡后续沉积,从而允许在未涂覆SAM的材料上选择性地沉积。

[0021] 图1描绘了基板处理系统132的示意图,该基板处理系统132可以用于执行根据本文所述的实施方式的氧化物处理和后续的非晶硅层沉积。合适的系统的示例包括可从加利福尼亚州圣克拉拉市应用材料公司购得的可使用DxZ<sup>TM</sup>处理腔室的CENTURA<sup>®</sup>系统、PRECISION5000<sup>®</sup>系统、PRODUCER<sup>TM</sup>系统、PRODUCER GT<sup>TM</sup>和PRODUCER SE<sup>TM</sup>处理腔室。设想的是,其它处理系统(包括可从其它制造商获得的那些处理系统)可以适于实践本文所述的实施方式。

[0022] 基板处理系统132包括耦接到气体面板130和控制器110的处理腔室100。处理腔室100一般包括顶壁124、侧壁101和底壁122,它们一起限定处理容积126。用于支撑基板的支撑基座150提供在处理腔室100的处理容积126中。支撑基座150由杆160支撑,并且典型地可以由铝、陶瓷和其它合适的材料制成。可以使用位移机构(未示出)在处理腔室100内在竖直方向上移动支撑基座150。

[0023] 支撑基座150可以包括嵌入式加热元件170,嵌入式加热元件170适于控制支撑在支撑基座150的表面192上的基板190的温度。可以通过从电源106将电流施加到嵌入式加热元件170来进行电阻地加热支撑基座150。嵌入式加热元件170可以由封装在镍-铁-铬合金(例如,INCOLOY<sup>®</sup>)鞘管中的镍-铬导线制成。从电源106供应的电流由控制器110调节,以控制由嵌入式加热元件170产生的热量,从而在膜沉积期间将基板190和支撑基座150维持在基本上恒定的温度。可以调整所供应的电流以选择性地将支撑基座150的温度控制在约100摄氏度至约700摄氏度之间。

[0024] 诸如热电偶的温度传感器172可以嵌入支撑基座150中来以常规的方式监测支撑基座150的温度。控制器110使用测量的温度来控制提供给嵌入式加热元件170的功率,以将基板维持在期望温度。

[0025] 真空泵102耦接到形成在处理腔室100的底部中的端口。真空泵102用于维持处理腔室100中的期望的气体压力。真空泵102还排空来自处理腔室100的该处理的后处理气体和副产物。

[0026] 基板处理系统132可以进一步包括用于控制腔室压力的附加设备,例如,定位在处理腔室100与真空泵102之间的阀(例如,节流阀和隔离阀)以控制腔室压力。

[0027] 具有多个孔隙128的喷头120设置在支撑基座150上方的处理腔室100的顶部上。喷头120的孔隙128用于将处理气体引入处理腔室100中。孔隙128可以具有不同的尺寸、数量、分布、形状、设计和直径,以便于各种处理气体流动来满足不同的处理要求。喷头120连接到

气体面板130，气体面板130允许各种气体在处理期间供应到处理容积126。由离开喷头120的处理气体混合物形成等离子体，以增强处理气体的热分解，从而导致材料沉积在基板190的表面191上。

[0028] 喷头120和支撑基座150可以在处理容积126中形成一对间隔开的电极。一个或多个RF电源140通过匹配网络138向喷头120提供偏置电位，以便于在喷头120和支撑基座150之间产生等离子体。或者，RF电源140和匹配网络138可以耦接到喷头120、支撑基座150，或耦接到喷头120和支撑基座150，或耦接到设置在处理腔室100外的天线(未示出)。在一个实施方式中，RF电源140可以在约50kHz至约13.6MHz的频率提供约100瓦至约3,000瓦。在另一个实施方式中，RF电源140可以在约50kHz至约13.6MHz的频率提供约500瓦特与约1,800瓦特之间的功率。

[0029] 控制器110包括中央处理单元(CPU)112、存储器116和支持电路114，支持电路114用于控制处理顺序并调节来自气体面板130的气流。CPU 112可以是可用于工业设置的任何形式的通用计算机处理器。软件例程可以存储在存储器116中，诸如随机存取存储器、只读存储器、软盘或硬盘驱动器，或其它形式的数字存储装置。支持电路114常规地耦接到CPU 112，并且可以包括高速缓存、时钟电路、输入/输出系统、电源等。控制器110与基板处理系统132的各种部件之间的双向通信通过统称为信号总线118的多条信号电缆来处理，其中一些信号总线在图1中示出。

[0030] 在一个实施方式中，基板190的表面191是基本上平面的。或者，基板190可以具有图案化结构，在其中形成有沟槽、孔或通孔的表面。基板190还可以具有基本上平坦的表面，该基本上平坦的表面具有在其上或其中形成的期望高度的结构。虽然基板190被示出为单个主体，但是应当理解，基板190可以含有用于形成半导体器件(诸如金属触点、沟槽隔离、栅极、位线或任何其它互连特征)的一种或多种材料。基板190可以包括用于制造半导体器件的一个或多个金属层、一种或多种介电材料、半导体材料以及以上项的组合。例如，取决于应用，基板190可以包括氧化物材料、氮化物材料、多晶硅材料等。

[0031] 在需要存储器应用的一个实施方式中，基板190可以包括硅基材料、氧化物材料和氮化物材料，它们之间夹有或不夹有多晶硅。在另一个实施方式中，基板190可以包括沉积在基板(未示出)表面上的多个交替氧化物和氮化物材料(即，氧化物-氮化物-氧化物(ONO))。在各种实施方式中，基板190可以包括多个交替氧化物和氮化物材料、一种或多种氧化物或氮化物材料、多晶硅或非晶硅材料，与非晶碳交替的氧化物、与多晶硅交替的氧化物、与掺杂硅交替的未掺杂硅、与掺杂多晶硅交替的未掺杂多晶硅、或与掺杂非晶硅交替的未掺杂非晶硅。基板可以是在其上执行膜处理的任何基板或材料表面。例如，基板190可以是诸如晶体硅、氧化硅、氮氧化硅、氮化硅、应变硅、硅锗、钨、氮化钛、掺杂或未掺杂多晶硅、掺杂或未掺杂硅晶片以及图案化或未图案化晶片、绝缘体上硅(SOI)、碳掺杂氧化硅、氮化硅、掺杂硅、锗、砷化镓、玻璃、蓝宝石、低k电介质以及以上项的组合的材料。

[0032] 图2是描绘如本文所述的用于用等离子体处理形成间隔件的方法200的一个实施方式的处理流程图。图3A-3E是根据图2的处理形成的结构的示意性侧视图。形成处理可以在有或没有等离子体的情况下进行。沉积可以通过热CVD处理或PECVD处理进行。设想的是，选择自对准双图案化处理用于说明目的。本公开的概念同样地适用于其它处理，例如，单或双图案化方案，诸如通孔/孔收缩处理、自对准三重图案化(SATP)处理或自对准四重图案化

(SAQP) 处理等,这些处理可能涉及在各种半导体处理(诸如NAND闪存应用、DRAM应用或CMOS应用等)中根据需要使用具有可变线宽和间距的保护性间隔件或保护性牺牲层等。

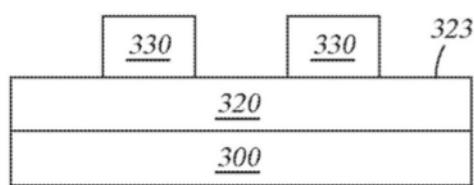

[0033] 方法200在操作210处由在基板300上形成牺牲结构层320开始。基板可以类似于基板190。牺牲结构层320可以是硅基材料,诸如氧化硅、氮化硅或多晶硅。或者,牺牲结构层320可以是碳基材料,诸如非晶碳。在期望碳基牺牲结构层的情况下,牺牲结构层320可以是非晶碳和氢的组合(氢化非晶碳膜)。一种示例性非晶碳膜可以是从加利福尼亚州圣克拉拉市应用材料公司购得的可剥离的先进图膜(Advanced Patterning Film<sup>TM</sup>) (APF) 材料。设想的是,用于牺牲结构层320的材料的选择可以根据相对于待形成在其上的保形保护层的蚀刻/灰化速率而改变。虽然未示出,但是在使用碳基牺牲结构层的某些实施方式中,可以在碳基牺牲结构层上沉积一个或多个抗反射涂层以控制在光刻图案化处理期间的光的反射。合适的抗反射涂层可以包括二氧化硅、氮氧化硅、氮化硅或以上项的组合。一个示例性抗反射涂层可以是从加利福尼亚州圣克拉拉市应用材料公司购得的DARC<sup>TM</sup>材料。

[0034] 基板300可以具有基本上平坦的表面323,如图所示。或者,基板300可以具有图案化结构,在其中形成有沟槽、孔或通孔的表面。虽然基板300被示出为单个主体,但是基板300可以包括用于形成半导体器件(诸如金属触点、沟槽隔离、栅极、位线或任何其它互连特征)的一种或多种材料。在一个实施方式中,基板300可以包括用于制造半导体器件的一个或多个金属层、一种或多种介电材料、半导体材料以及以上项的组合。例如,取决于应用,基板300可以包括氧化物材料、氮化物材料、多晶硅材料等。在需要存储器应用的情况下,基板300可以包括硅基板材料、氧化物材料和氮化物材料,它们之间夹有或不夹有多晶硅。

[0035] 在操作220处,在牺牲结构层320上沉积抗蚀层330,诸如光刻胶材料,如图3A所示。

[0036] 在操作230处,使用标准光刻和蚀刻技术在基板300上产生由牺牲结构层320形成的图案化特征321,如图3B所示。图案化特征可以由任何合适的材料形成,例如氧化物,诸如二氧化硅、氮氧化硅,或氮化物,诸如氮化硅。图案化特征有时被称为定位符、心轴或芯,并且基于所使用的光刻胶材料而具有特定线宽和/或间距。可以通过对抗蚀层330进行修整处理来调整图案化特征321的宽度。在已经将图案转移到牺牲结构层320中之后,使用合适的光刻胶剥离处理去除任何残余的光刻胶和硬掩模材料(如果使用了的话)。

[0037] 在操作240处,可以对牺牲结构层320执行等离子体处理。希望不受理论束缚,但是据信等离子体处理工艺减小牺牲结构层320的表面粗糙度。在一个实施方式中,在形成牺牲结构层的同一个腔室中进行等离子体处理。在一个实施方式中,等离子体处理在形成非晶硅层的同一个腔室中进行。或者,等离子体处理可以在不同等离子体处理腔室中进行。

[0038] 根据本公开的一个实施方式,可以通过将在基板上形成有牺牲结构层的基板定位在等离子体处理腔室(诸如图1的等离子体腔室)中以使处理气体流到等离子体处理腔室并在等离子体处理腔室中撞击等离子体来执行等离子体处理。在一个实施方式中,处理气体可以是氩(Ar)、氢(H<sub>2</sub>)、氨(NH<sub>3</sub>)、氮(N<sub>2</sub>)、一氧化二氮(N<sub>2</sub>O)或以上项的组合。在一个实施方式中,等离子体是电容耦合等离子体(CCP)或电感耦合等离子体(ICP)。

[0039] 在等离子体处理期间,处理腔室可以维持在约100摄氏度至约500摄氏度之间的温度。处理气体可以以约20sccm至约20,000sccm之间的流率流到处理腔室。腔室压力可以在约0.01托至约50托之间(例如,在约0.1托至20托之间)。RF功率被施加到处理腔室中的处理气体以在处理腔室中产生等离子体。在一个实施方式中,可以在约50kHz至约13.6MHz的频

率下提供约50瓦特与约3,000瓦特之间(例如,约100瓦特与约3,000瓦特之间;或约50瓦特与约2,000瓦特之间)的RF功率。在一些实施方式中,频率是约2MHz、13.56MHz,或包括2MHz和13.56MHz的混合频率。在一些实施方式中,在等离子体处理期间,基板被偏置。施加到基板的偏置可以在0瓦特与1000瓦特之间。等离子体处理可以进行约5秒至约600秒之间(例如,约10秒至约300秒之间)的持续时间。

[0040] 在操作250处,非晶硅层340保形地或基本上保形地沉积在图案化特征321以及基板300的暴露表面上,如图3C所示。根据本文所述的实施方式形成非晶硅层340。非晶硅层340的厚度可以在约5Å与约200Å之间。

[0041] 在一些实施方式中,可以通过最大化硅前驱物的分压同时最小化基板温度来实施保形非晶硅(a-Si)沉积。合适的硅前驱物包括但不限于聚硅烷( $\text{Si}_x\text{H}_y$ )。例如,聚硅烷包括乙硅烷( $\text{Si}_2\text{H}_6$ )、丙硅烷( $\text{Si}_3\text{H}_8$ )、丁硅烷( $\text{Si}_4\text{H}_{10}$ )、异三硅烷、新戊硅烷( $\text{Si}_5\text{H}_{12}$ )、环戊硅烷( $\text{Si}_5\text{H}_{10}$ )、己硅烷( $\text{C}_6\text{H}_{14}$ )、环己硅烷( $\text{Si}_6\text{H}_{12}$ )或一般是 $\text{Si}_x\text{H}_y$ (其中x=2或更大),或以上项的组合。例如,具有适中的处理温度和高蒸气压的乙硅烷可以单独地或与其它物质组合地用作硅前驱物。

[0042] 在一些实施方式中,硅前驱物基本上仅含乙硅烷。如本文所用,短语“基本上仅乙硅烷”是指至少95%的活性物质是乙硅烷。其它气体,诸如载气和惰性气体,可以包括在该量中。

[0043] 沉积的膜包括可从膜放出或排出的可脱气物质,例如氢。惰性除气环境为气态物质提供了放出机会,从而使最终膜的起泡最小化。惰性除气环境可以包括允许或促使去除膜的可脱气物质的任何条件。例如,除气环境可以基本上由惰性气体组成。就这一点所用,“基本上由……组成”是指没有干扰沉积的膜的脱气的气态物质。可以存在其它反应物质而不抑制膜的除气,同时除气环境仍然基本上由惰性气体组成。在一些实施方式中,惰性除气环境是在沉积的膜上基本上不发生化学反应的环境。例如,可能基本上没有可与沉积的膜反应的化学物质。在一些实施方式中,除气环境不使用UV光、等离子体或微波辐射来引起可脱气物质的除气。

[0044] 在一个或多个实施方式中,通过化学气相沉积处理沉积非晶硅膜。尽管可以使用类似的处理腔室,但是化学气相沉积(CVD)处理与原子层沉积(ALD)不同。ALD处理是自限制处理,其中使用二元(或更高阶)反应沉积单层材料。该处理继续进行,直到基板表面上的所有可用活性位点都已反应。CVD处理不是自限制的,并且膜可以生长到任何预确定的厚度。

[0045] 合适的惰性气体包括但不限于氩、氦、氮和/或以上项的混合物中的一种或多种。在一些实施方式中,惰性除气环境基本上不包括氧。就这一点所用,“基本上不含氧”是指惰性除气环境在邻近基板表面的环境条件下具有小于约1% (基于原子)的氧原子。

[0046] 在一个或多个实施方式中,可脱气物质包括氢。就这一点所用,包括氢的可脱气物质可以包括 $\text{SiH}_2$ 、 $\text{SiH}_3$ 、 $\text{SiH}_4$ 和/或其它低阶硅烷中的一种或多种。

[0047] 可以针对前驱物暴露和除气环境独立地控制处理腔室、或处理腔室的区域中的压力。在一些实施方式中,于硅前驱物和除气环境中的每一个的暴露在约50毫托至约200托的压力下发生。在一些实施方式中,硅前驱物在大于或等于约500毫托、或大于或等于约1托、或大于或等于约5托、或大于或等于约10托、或大于或等于约20托、或大于或等于约30托的压力下被暴露于基板。

[0048] 基板表面暴露于前驱物或除气环境的温度可以根据例如所形成的器件以及前驱物的热预算而变化。在一些实施方式中,于前驱物和除气环境中的每一个的暴露在约350摄氏度至约700摄氏度的温度范围内发生。在一个或多个实施方式中,卤化硅前驱物在约375摄氏度至约600摄氏度的温度范围内、或约400摄氏度至约550摄氏度的温度范围内被暴露于基板。

[0049] 在一些实施方式中,基于乙硅烷的保形a-Si处理在低于约450摄氏度的基板温度下沉积,并且乙硅烷分压大于或等于约20托。在示例性实施方式中,基板在约400摄氏度至约550摄氏度的温度范围内在大于或等于约20托的压力下被暴露于硅前驱物。

[0050] 在操作260处,在已经在图案化特征321上保形地沉积非晶硅层340之后,各向异性地蚀刻(竖直蚀刻)非晶硅层340以在区域311中暴露基板300的上表面并暴露图案化特征321的上表面,从而导致图案化特征321(由牺牲结构层320形成)由非牺牲非晶硅基侧壁间隔件341保护,如图3D所示。

[0051] 在操作270处,使用常规的等离子体蚀刻处理或其它合适的湿法剥离处理去除图案化特征321(由牺牲结构层320形成),留下非牺牲非晶硅基侧壁间隔件341,如图3E所示。等离子体蚀刻处理可以通过将氟基蚀刻化学物质引入在基板上方的等离子体中来完成。由于改善的材料质量和覆盖率,非牺牲非晶硅基侧壁间隔件341不会损坏,因为它们具有对基于氟的反应蚀刻化学物质或基于湿法剥离的化学物质的非常好的选择性。在去除图案化特征321之后,剩余非牺牲非晶硅基侧壁间隔件341可以用作用于蚀刻下面的层、层堆叠或结构的硬模。特别地,根据该图案化处理的非牺牲非晶硅基侧壁间隔件341的密度是图案化特征321的密度的两倍,非牺牲非晶硅基侧壁间隔件341的间距是图案化特征321的间距的一半。非牺牲非晶硅基侧壁间隔件341可以用作硬模以图案化下面的材料层。

[0052] 图4是描绘根据本文所述的实施方式的用于间隔件形成的方法400的另一个实施方式的处理流程图。图5A-5E是根据图4的处理流程图形成的结构的示意性侧视图。形成处理可以在有或没有等离子体的情况下进行。沉积可以通过热CVD处理或PECVD处理进行。设想的是,选择自对准双图案化处理用于说明目的。本公开的概念同样地适用于其它处理,例如,单或双图案化方案,诸如通孔/孔收缩处理、自对准三重图案化(SATP)处理或自对准四重图案化(SAQP)处理等,这些处理可能涉及在各种半导体处理(诸如NAND闪存应用、DRAM应用或CMOS应用等)中根据需要使用具有可变线宽和间距的保护性间隔件或保护性牺牲层等。

[0053] 方法400在操作410处由在基板500上形成牺牲结构层520开始。基板可以类似于基板190。牺牲结构层520可以是硅基材料,诸如氧化硅、氮化硅或多晶硅。或者,牺牲结构层520可以是碳基材料,诸如非晶碳。在期望碳基牺牲结构层的情况下,牺牲结构层520可以是非晶碳和氢的组合(氢化非晶碳膜)。一种示例性非晶碳膜可以是从加利福尼亚州圣克拉拉市应用材料公司(Applied Materials, Inc. of Santa Clara, Calif)购得的可剥离的先进图膜(Advanced Patterning Film<sup>TM</sup>) (APF)材料。设想的是,用于牺牲结构层520的材料的选择可以根据相对于待形成在其上的保形保护层的蚀刻/灰化速率而变。虽然未示出,但是在使用碳基牺牲结构层的某些实施方式中,可以在碳基牺牲结构层上沉积一个或多个抗反射涂层以控制在光刻图案化处理期间的光的反射。合适的抗反射涂层可以包括二氧化硅、氮氧化硅、氮化硅或以上项的组合。一个示例性抗反射涂层可以是从加利福尼亚州圣克

拉市应用材料公司购得的DARC<sup>TM</sup>材料。

[0054] 基板500可以具有基本上平坦的表面523,如图所示。或者,基板500可以具有图案化结构,在其中形成有沟槽、孔或通孔的表面。虽然基板500被示出为单个主体,但是基板500可以包括用于形成半导体器件(诸如金属触点、沟槽隔离、栅极、位线或任何其它互连特征)的一种或多种材料。在一个实施方式中,基板500可以包括用于制造半导体器件的一个或多个金属层、一种或多种介电材料、半导体材料以及以上项的组合。例如,取决于应用,基板500可以包括氧化物材料、氮化物材料、多晶硅材料等。在期望存储器应用的情况下,基板500可以包括硅基板材料、氧化物材料和氮化物材料,它们之间夹有或不夹有多晶硅。

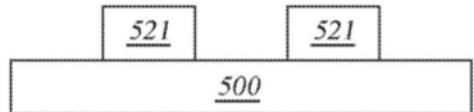

[0055] 在操作420处,在牺牲结构层520上沉积抗蚀层530,诸如光刻胶材料,如图5A所示。

[0056] 在操作430处,使用标准光刻和蚀刻技术在基板500上产生由牺牲结构层520形成的图案化特征521,如图5B所示。图案化特征可以由任何合适的材料形成,例如氧化物,诸如二氧化硅、氮氧化硅,或氮化物,诸如氮化硅。图案化特征有时被称为定位符、心轴或芯,并且基于所使用的光刻胶材料而具有特定线宽和/或间距。可以通过对抗蚀层530进行修整处理来调整图案化特征521的宽度。在已经将图案转移到牺牲结构层520中之后,使用合适的光刻胶剥离处理去除任何残余的光刻胶和硬掩模材料(如果使用了的话)。

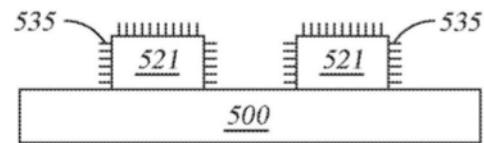

[0057] 在操作440处,将基板500暴露于SAM前驱物以在图案化特征521上形成SAM 535。希望不受理论束缚,但是据信,SAM 535改善非晶硅层与图案化特征521的粘附性。据信,SAM 535有助于将非晶硅层锚固到图案化特征521。取决于所使用的材料和所使用的SAM前驱物,SAM前驱物可以是基于溶液的前驱物或气态前驱物。SAM前驱物可以包括SAM分子、形成SAM分子的前驱物或两者。吸附的SAM分子形成SAM 535。

[0058] SAM 535包括SAM分子的有组织层,该有组织层可以是两亲的,其中分子的一端,即头基,表现出对形成图案化特征521的氧化硅材料的特定的可逆的亲和力。头基通常连接到烷基链,其中末端“R”可以被官能化。通过以下方式形成SAM 535:头基化学吸附到图案化特征521上,接着疏水性尾基的二维组织化学吸附到图案化特征521上。通过将基板500浸入含有SAM分子的稀释溶液中,可以从溶液发生SAM吸附。在一个实施方式中,从溶液经由旋涂沉积SAM 535。通过将基板500暴露于气态前驱物,也可以从气相沉积发生SAM吸附。可以通过调整SAM分子的烷基链的碳链长度来调整SAM 535的厚度。一般,SAM 535可以仅形成在具有与SAM分子的化学反应能力的表面上。

[0059] 在图5C中描绘的实施方式中,选择用于形成SAM 535的SAM前驱物以仅与图案化特征521(例如,氧化硅材料)的暴露表面和随后沉积的非晶硅层的暴露表面发生化学反应。通过这样做,SAM 535可以主要地形成在图案化特征521的暴露表面上。

[0060] 可利用的SAM材料的示例包括下文描述的材料,包括这些材料的组合物、混合和接枝物,还有具有适于在半导体制造工艺中阻挡随后沉积的材料的沉积的其它SAM材料。在一个实施方式中,SAM材料可以是羧酸材料,诸如甲基羧酸、乙基羧酸、丙基羧酸、丁基羧酸、戊基羧酸、己基羧酸、庚基羧酸、辛基羧酸、壬基羧酸、癸基羧酸、十一烷基羧酸、十二烷基羧酸、十三烷基羧酸、十四烷基羧酸、十五烷基羧酸、十六烷基羧酸、十七烷基羧酸、十八烷基羧酸和十九烷基羧酸。

[0061] 在另一个实施方式中,SAM材料可以是膦酸材料,诸如甲基膦酸、乙基膦酸、丙基膦酸、丁基膦酸、戊基膦酸、己基膦酸、庚基膦酸、辛基膦酸、壬基膦酸、癸基膦酸、十一烷基膦

酸、十二烷基膦酸、十三烷基膦酸、十四烷基膦酸、十五烷基膦酸、十六烷基膦酸、十七烷基膦酸、十八烷基膦酸和十九烷基膦酸。

[0062] 在另一个实施方式中，SAM材料可以是硫醇材料，诸如甲基硫醇、乙基硫醇、丙基硫醇、丁基硫醇、戊基硫醇、己基硫醇、庚基硫醇、辛基硫醇、壬基硫醇、癸基硫醇、十一烷基硫醇、十二烷基硫醇、十三烷基硫醇、十四烷基硫醇、十五烷基硫醇、十六烷基硫醇、十七烷基硫醇、十八烷基硫醇和十九烷基硫醇。

[0063] 在另一个实施方式中，SAM材料可以是硅烷基胺材料，诸如三(二甲氨基)甲基硅烷、三(二甲氨基)乙基硅烷、三(二甲氨基)丙基硅烷、三(二甲氨基)丁基硅烷、三(二甲氨基)戊基硅烷、三(二甲氨基)己基硅烷、三(二甲氨基)庚基硅烷、三(二甲氨基)辛基硅烷、三(二甲氨基)壬基硅烷、三(二甲氨基)癸基硅烷、三(二甲氨基)十一烷基硅烷、三(二甲氨基)十二烷基硅烷、三(二甲氨基)十三烷基硅烷、三(二甲氨基)十四烷基硅烷、三(二甲氨基)十五烷基硅烷、三(二甲氨基)十六烷基硅烷、三(二甲氨基)十七烷基硅烷、三(二甲氨基)十八烷基硅烷和三(二甲氨基)十九烷基硅烷。

[0064] 在另一个实施方式中，SAM材料可以是氯基硅烷材料，诸如甲基三氯硅烷、乙基三氯硅烷、丙基三氯硅烷、丁基三氯硅烷、戊基三氯硅烷、己基三氯硅烷、庚基三氯硅烷、辛基三氯硅烷、壬基三氯硅烷、癸基三氯硅烷、十一烷基三氯硅烷、十二烷基三氯硅烷、十三烷基三氯硅烷、十四烷基三氯硅烷、十五烷基三氯硅烷、十六烷基三氯硅烷、十七烷基三氯硅烷、十八烷基三氯硅烷和十九烷基三氯硅烷。

[0065] 在另一个实施方式中，SAM材料可以是氧基硅烷材料，诸如甲基三甲氧基硅烷、甲基三乙氧基硅烷、乙基三甲氧基硅烷、乙基三乙氧基硅烷、丙基三甲氧基硅烷、丙基三乙氧基硅烷、丁基三甲氧基硅烷、丁基三乙氧基硅烷、戊基三甲氧基硅烷、戊基三乙氧基硅烷、己基三甲氧基硅烷、己基三乙氧基硅烷、庚基三甲氧基硅烷、庚基三乙氧基硅烷、辛基三甲氧基硅烷、辛基三乙氧基硅烷、壬基三甲氧基硅烷、壬基三乙氧基硅烷、癸基三甲氨基、癸基三乙氨基、十一烷基三甲氧基硅烷、十一烷基三乙氧基硅烷、十二烷基三甲氧基硅烷、十二烷基三乙氧基硅烷、十三烷基三甲氧基硅烷、十三烷基三乙氧基硅烷、十四烷基三甲氧基硅烷、十四烷基三乙氧基硅烷、十五烷基三甲氧基硅烷、十五烷基三乙氧基硅烷、十六烷基三甲氧基硅烷、十六烷基三乙氧基硅烷、十七烷基三甲氧基硅烷、十七烷基三乙氧基硅烷、十八烷基三甲氧基硅烷、十八烷基三乙氧基硅烷、十九烷基三甲氧基硅烷和十九烷基三乙氧基硅烷。

[0066] 在另一个实施方式中，SAM材料可以具有氟化R基，诸如(1,1,2,2-全氟癸基)三氯硅烷、三氯(1,1,2,2-全氟辛基)硅烷、(十三氟-1,1,2,2-四氢辛基)三氯硅烷、(十三氟-1,1,2,2-四氢辛基)三乙氧基硅烷、(十三氟-1,1,2,2-四氢辛基)甲基二氯硅烷、(十三氟-1,1,2,2-十四氟辛基)二甲基氯硅烷和(十七氟-1,1,2,2-四氢癸基)三氯硅烷等。设想的是，前述材料的组合物和混合物在本公开的范围内。

[0067] 通过将基板500浸入含有SAM分子的稀释溶液中，可以从溶液发生SAM吸附。在一个实施方式中，SAM 535从溶液经由旋涂沉积。通过将基板500暴露于气态前驱物，也可以从气相沉积发生SAM吸附。可以通过调整SAM分子的烷基链的碳链长度来调整SAM 535的厚度。一般，SAM 535可以形成在具有与SAM分子的化学反应能力的表面上。

[0068] 在一个实施方式中，SAM吸附可以是气相沉积处理。在该实施方式中，SAM分子可以

在安瓿中蒸发，安瓿维持在约25摄氏度与约300摄氏度之间（诸如约125摄氏度与约200摄氏度之间）的温度。基板500可以维持在约25摄氏度与约400摄氏度之间（诸如约50摄氏度与约200摄氏度之间的温度，例如，约100摄氏度与约175摄氏度之间）的温度。基板处理环境（诸如处理腔室的处理容积）的压力可以维持在约1mT与约1520T之间（诸如约5T和约600T之间）的压力。载气可以用于促进气相SAM分子和载气的输送，这取决于处理腔室的容积，可以以约25sccm与约3000sccm之间（诸如在约50sccm与约1000sccm之间）的流率输送。合适的载气包括气体，诸如稀有气体等，气体在有助于将SAM分子输送到基板表面的SAM吸附条件下一般是惰性的。在操作440中，可以将SAM分子暴露于基板500长达约1秒与约48小时之间（诸如约1分钟与约120分钟之间）的时间量。

[0069] 在操作450处，非晶硅层540保形地或基本上保形地沉积在图案化特征521以及基板500的暴露表面上，如图5D所示。根据本文所述的实施方式形成非晶硅层540。非晶硅层540的厚度可以在约5Å与约200Å之间。

[0070] 在一些实施方式中，可以通过最大化硅前驱的分压同时最小化基板温度来实施保形非晶硅(a-Si)沉积。合适的硅前驱物包括但不限于聚硅烷( $\text{Si}_x\text{H}_y$ )。例如，聚硅烷包括乙硅烷( $\text{Si}_2\text{H}_6$ )、丙硅烷( $\text{Si}_3\text{H}_8$ )、丁硅烷( $\text{Si}_4\text{H}_{10}$ )、异三硅烷、新戊硅烷( $\text{Si}_5\text{H}_{12}$ )、环戊硅烷( $\text{Si}_5\text{H}_{10}$ )、己硅烷( $\text{C}_6\text{H}_{14}$ )、环己硅烷( $\text{Si}_6\text{H}_{12}$ )或一般是 $\text{Si}_x\text{H}_y$ （其中x=2或更大），或以上项的组合。例如，具有适中的处理温度和高蒸气压的乙硅烷可以单独地或与其它物质组合地用作硅前驱物。

[0071] 在一些实施方式中，硅前驱物基本上仅含乙硅烷。如本文所用，短语“基本上仅含乙硅烷”是指至少95%的活性物质是乙硅烷。其它气体，诸如载气和惰性气体，可以包括在该量中。

[0072] 沉积的膜包括可从膜放出或排出的可脱气物质，例如氢。惰性除气环境为气态物质提供了放出机会，从而最小化最终膜的起泡最小化。惰性除气环境可以包括允许或促使去除膜的可脱气物质的任何条件。例如，除气环境可以基本上由惰性气体组成。就这一点所用，“基本上由……组成”是指没有干扰沉积的膜的脱气的气态物质。可以存在其它反应物质而不抑制膜的除气，同时除气环境仍然基本上由惰性气体组成。在一些实施方式中，惰性除气环境是在沉积的膜上基本上不发生化学反应的环境。例如，可能基本上没有可与沉积的膜反应的化学物质。在一些实施方式中，除气环境不使用UV光、等离子体或微波辐射来引起可脱气物质的除气。

[0073] 在一个或多个实施方式中，通过化学气相沉积处理沉积非晶硅膜。尽管可以使用类似的处理腔室，但是化学气相沉积(CVD)处理与原子层沉积(ALD)不同。ALD处理是自限制处理，其中使用二元(或更高阶)反应沉积单层材料。该处理继续进行，直到基板表面上的所有可用活性位点都已反应。CVD处理不是自限制的，并且膜可以生长到任何预确定的厚度。

[0074] 合适的惰性气体包括但不限于氩、氦、氮和/或以上项的混合物中的一种或多种。在一些实施方式中，惰性除气环境基本上不包括氧。就这一点所用，“基本上不含氧”是指惰性除气环境在邻近基板表面的环境条件中具有小于约1%（基于原子）的氧原子。

[0075] 在一个或多个实施方式中，可脱气物质包括氢。就这一点所用，包括氢的可脱气物质可以包括 $\text{SiH}_2$ 、 $\text{SiH}_3$ 、 $\text{SiH}_4$ 和/或其它低阶硅烷中的一种或多种。

[0076] 可以针对前驱物暴露和除气环境独立地控制处理腔室、或处理腔室的区域中的压

力。在一些实施方式中，于硅前驱物和除气环境中的每一个的暴露在约50毫托至约200托的压力下发生。在一些实施方式中，硅前驱物在大于或等于约500毫托、或大于或等于约1托、或大于或等于约5托、或大于或等于约10托、或大于或等于约20托、或大于或等于约30托的压力下被暴露于基板。

[0077] 基板表面暴露于前驱物或除气环境的温度可以根据例如所形成的器件以及前驱物的热预算而变化。在一些实施方式中，于前驱物和脱气环境中的每一个的暴露发生在约350摄氏度至约700摄氏度的温度范围内。在一个或多个实施方式中，卤化硅前驱物在约375摄氏度至约600摄氏度的温度范围内、或约400摄氏度至约550摄氏度的温度范围内被暴露于基板。

[0078] 在一些实施方式中，基于乙硅烷的保形a-Si处理在低于约450摄氏度的基板温度下沉积，并且乙硅烷分压大于或等于约20托。在示例性实施方式中，基板在约400摄氏度至约550摄氏度的温度范围内在大于或等于约20托的压力下被暴露于硅前驱物。

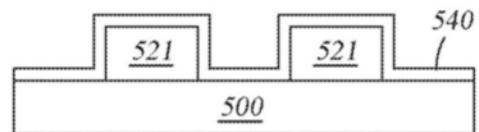

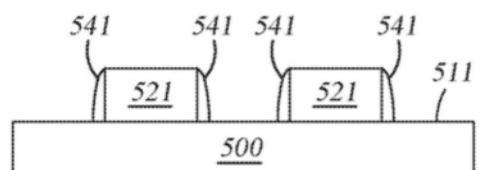

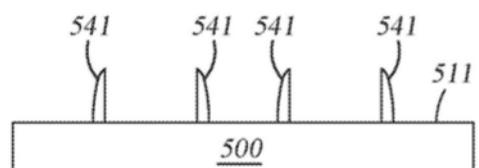

[0079] 在操作460处，在已经在图案化特征521上保形地沉积非晶硅层540之后，各向异性地蚀刻(竖直蚀刻)非晶硅层540以在区域511中暴露基板500的上表面并暴露图案化特征521的上表面，从而导致图案化特征521(由牺牲结构层520形成)由非牺牲非晶硅基侧壁间隔件541保护，如图5E所示。

[0080] 在操作470处，使用常规的等离子体蚀刻处理或其它合适的湿法剥离处理去除图案化特征521(由牺牲结构层520形成)，留下非牺牲非晶硅基侧壁间隔件541，如图5F所示。等离子体蚀刻处理可以通过将氟基蚀刻化学物质引入在基板上方的等离子体中来完成。由于改善的材料质量和覆盖率，非牺牲非晶硅基侧壁间隔件541不会损坏，因为它们具有对基于氟的反应蚀刻化学物质或基于湿法剥离的化学物质的非常好的选择性。在去除图案化特征521之后，剩余非牺牲非晶硅基侧壁间隔件541可以用作用于蚀刻下面的层、层堆叠或结构的硬模。特别地，根据该图案化处理的非牺牲非晶硅基侧壁间隔件541的密度是光刻图案化特征521的密度的两倍，非牺牲非晶硅基侧壁间隔件541的间距是图案化特征521的间距的一半。非牺牲非晶硅基侧壁间隔件541可以用作硬模以图案化下面的材料层。

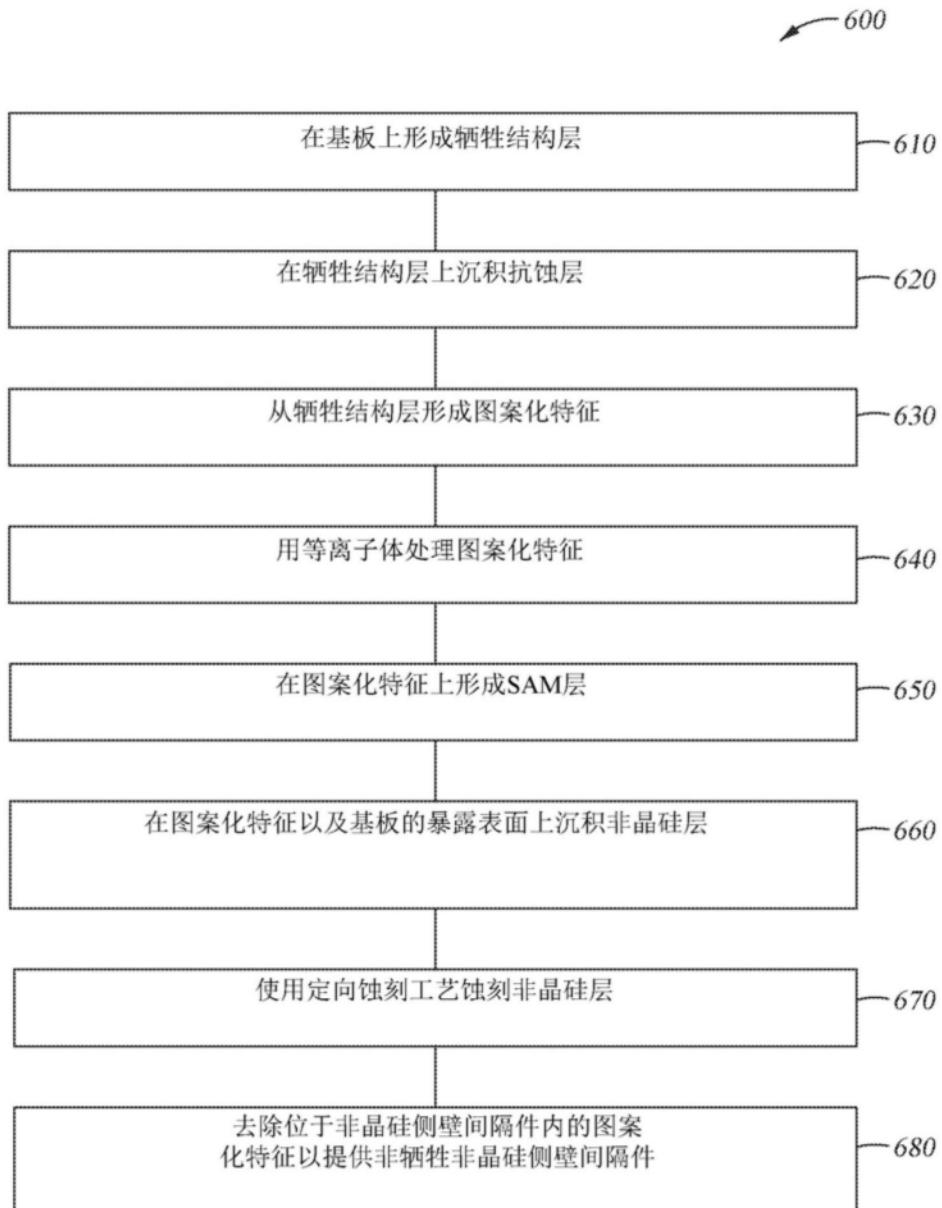

[0081] 图6是描绘根据本文所述的实施方式的用于间隔件形成的方法600的另一个实施方式的处理流程图。方法600类似于方法200和方法400，不同之处在于方法600结合方法400的等离子体处理处理和方法400的SAM形成。在操作610处，在基板上形成牺牲结构层，这类似于操作210和操作410。在操作620处，在牺牲结构层上形成抗蚀层，这类似于操作220和操作420。在操作630处，从牺牲结构层形成图案化特征，这类似于操作230和操作430。在操作640处，用等离子体处理图案化特征，这类似于操作240。在操作650处，在图案化特征上形成SAM，这类似于操作440。在操作660处，在图案化特征以及基板的暴露表面上形成非晶硅层，这类似于操作250和操作450。在操作670处，使用定向蚀刻处理蚀刻非晶硅层，这类似于操作260和操作460。在操作680处，位于非晶硅侧壁间隔件内的图案化特征提供非牺牲非晶硅侧壁间隔件。

[0082] 总之，本公开的一些实施方式提供了用于非晶硅间隔件形成的改善的方法。本文所述的改善的方法中的一些提供高保形性、低图案负载和BEOL相容的处理温度。本文所述的改善的方法中的一些进一步提供了下面的氧化物膜的减小的粗糙度和与随后沉积的非晶硅膜的改善的粘附性。在一些实施方式中，将下面的氧化物膜暴露于等离子体处理，这减

小了随后沉积的非晶硅膜的粗糙度以及改善下面的氧化物膜与非晶硅膜之间的粘附性。在一些实施方式中，在下面的氧化物层上形成SAM以改善与随后沉积的非晶硅层的粘附性。

[0083] 当介绍本公开的要素或其示例性方面或实施方式时，冠词“一”、“一个”、“该”和“所述”旨在表示存在一个或多个该要素。

[0084] 术语“包含”、“包括”和“具有”旨在是包括性的并表示可能存在除所列要素之外的其它要素。

[0085] 虽然前述内容针对的是本公开的实施方式，但是可以在不脱离本公开的基本范围的情况下设计本公开的其它和进一步实施方式，并且本公开的范围由所附权利要求书确定。

图1

图2

图3A

图3B

图3C

图3D

图3E

图4

图5A

图5B

图5C

图5D

图5E

图5F

图6