(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4635584号

(P4635584)

(45) 発行日 平成23年2月23日(2011.2.23)

(24) 登録日 平成22年12月3日(2010.12.3)

(51) Int.Cl.

F 1

H02M 3/28 (2006.01)

H02M 3/28

H

H02M 3/335 (2006.01)

H02M 3/28

Q

H02M 3/335

E

請求項の数 6 (全 21 頁)

(21) 出願番号

特願2004-347863 (P2004-347863)

(22) 出願日

平成16年11月30日(2004.11.30)

(65) 公開番号

特開2006-158137 (P2006-158137A)

(43) 公開日

平成18年6月15日(2006.6.15)

審査請求日

平成19年8月1日(2007.8.1)

(73) 特許権者 000003067

T D K 株式会社

東京都中央区日本橋一丁目13番1号

(74) 代理人 100109656

弁理士 三反崎 泰司

(74) 代理人 100098785

弁理士 藤島 洋一郎

(72) 発明者 村井 康弘

東京都中央区日本橋一丁目13番1号 T

D K 株式会社内

審査官 安池 一貴

最終頁に続く

(54) 【発明の名称】スイッチング電源装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1ないし第4のスイッチング素子を含み、前記第1および第2のスイッチング素子の一端同士が互いに接続されて第1の接続点を構成すると共に前記第3および第4のスイッチング素子の一端同士が互いに接続されて第2の接続点を構成し、前記第1および第3のスイッチング素子の他端同士と前記第2および第4のスイッチング素子の他端同士との間に印加される直流入力電圧を交流電圧に変換するスイッチング回路と、

前記第1および第2のスイッチング素子のうちの少なくとも一方と並列に外付け接続された第1の容量素子と、

1次側入力および2次側出力を有すると共にこの1次側入力が前記第1の接続点と前記第2の接続点との間に接続され、前記交流電圧を変圧するトランスと、

前記第1の接続点から前記トランスの1次側入力を経由して前記第2の接続点に至る経路内に挿入され、前記第1の容量素子と共に、ZVS (Zero Volt Switching) 動作を行うための共振回路を構成するインダクタと、

前記トランスの2次側出力と接続され、前記トランスによって変圧された交流電圧に基づいて直流出力電圧を生成する出力回路と、

前記第1および第4のスイッチング素子、または前記第2および第3のスイッチング素子に対してそれぞれ、固定側スイッチング素子としての前記第1および第2のスイッチング素子を基準として、シフト側スイッチング素子としての前記第4および第3のスイッチング素子との間にスイッチング位相差をなすように、これらのスイッチング素子を位相シ

フト制御により駆動するスイッチング駆動回路と、

前記出力回路の負荷の大きさに応じて、前記第1の容量素子のうちの少なくとも1つの容量値が変化するように制御する容量素子制御回路と

を備えたことを特徴とするスイッチング電源装置。

**【請求項2】**

前記第3および第4のスイッチング素子のうちの少なくとも一方と並列に外付け接続された第2の容量素子を更に備え、

前記容量素子制御回路は、前記第1および第2の容量素子のうち、前記第1の容量素子における容量値のみが変化するように制御する

ことを特徴とする請求項1に記載のスイッチング電源装置。

10

**【請求項3】**

前記容量素子制御回路は、前記出力回路の負荷が小さくなるに応じて、前記第1の容量素子のうちの少なくとも1つの容量値が小さくなるように制御する

ことを特徴とする請求項1または請求項2に記載のスイッチング電源装置。

**【請求項4】**

前記第1ないし第4のスイッチング素子はそれぞれ寄生容量を有し、

前記容量素子制御回路は、前記第1の容量素子とこの第1の容量素子に並列接続されたスイッチング素子との間の接続をオン・オフ制御することによって、前記第1の容量素子の容量値が変化するように制御する

ことを特徴とする請求項1ないし請求項3のいずれか1項に記載のスイッチング電源装置。

20

**【請求項5】**

前記第1の容量素子のうちの少なくとも1つが、互いに並列接続された複数のコンデンサから構成され、

前記容量素子制御回路は、これら複数のコンデンサを用いて前記第1の容量素子の容量値が変化するように制御する

ことを特徴とする請求項1ないし請求項3のいずれか1項に記載のスイッチング電源装置。

**【請求項6】**

前記容量素子制御回路は、前記複数のコンデンサのそれぞれの接続を選択的にオン・オフ制御することによって、前記第1の容量素子の容量値が変化するように制御する

30

ことを特徴とする請求項5に記載のスイッチング電源装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、位相シフト方式によるフルブリッジ型のスイッチング電源装置に関する。

**【背景技術】**

**【0002】**

従来より、スイッチング電源装置として種々のタイプのものが提案され、実用に供されている。そのうちの1つとして、いわゆる位相シフト方式によるフルブリッジ型のスイッティング電源装置が挙げられる。

40

**【0003】**

この位相シフト方式によるフルブリッジ型のスイッティング電源装置では、スイッティング回路としてブリッジ接続された4つのスイッティング素子を含み、これらのスイッティング素子によって、直流入力電圧が交流電圧に変換される。そしてこの交流電圧がトランスによって変圧され、さらに出力回路によって整流および平滑化されることで、直流出力電圧が出力される。

**【0004】**

また、これらのスイッティング素子は、すべて同一のオン幅および周波数で駆動されるが、そのタイミングについてみると2つのスイッティング素子対に区分される。一方のスイッ

50

チング素子対を構成する 2 つのスイッチング素子はともに、時間軸上における固定タイミングでオンするように制御される。他方のスイッチング素子対を構成する 2 つのスイッチング素子はともに、時間軸上における可変タイミングでオンするように制御される。これら 2 対のスイッチング素子によるスイッチング動作によって、トランスの 1 次側巻線に流れる電流が双方向に切り替わり、トランスが励磁される。ここで、これら 4 つのスイッチング素子による 2 対の組み合わせは、スイッチング動作のいかなる場面においても、直流入力電圧が印加された入力端子が電気的に短絡されないように設定される。また、固定タイミングでオンするように制御されるスイッチング素子対と、可変タイミングでオンするように制御されるスイッチング素子対との間に生じるスイッチング位相差が、検出した出力電圧等に基づいて制御され、出力電圧が安定化されるようになっている。

10

#### 【0005】

さらに、これら 4 つのスイッチング素子にはコンデンサが並列接続されており、これらのコンデンサとトランスのリーケージインダクタンスとにより共振回路が構成され、その共振特性を利用することでゼロボルトスイッチング (ZVS ; Zero Volt Switching) 動作が実現され、スイッチング素子の短絡損失が低減されるようになっている。

#### 【0006】

例えば、本出願人は特許文献 1において、共振回路を構成するインダクタンスとして、トランスのリーケージインダクタンスに加えて独立したインダクタを設け、その共振特性を調整するようにした位相シフト方式によるフルブリッジ型のスイッチング電源装置を提案している。この構成によれば、より確実に ZVS 動作を実現し、スイッチング素子の短絡損失を低減させることができる。

20

#### 【0007】

【特許文献 1】国際公開第 01/071896 号パンフレット

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、上記特許文献 1 のスイッチング電源装置では、主に定格負荷領域（例えば、出力電流が 6.5 ~ 8.5 A 程度の領域）での動作を対象としており、それよりも軽負荷の領域（例えば、出力電流が 2.0 A 程度の領域）では、共振回路のインダクタに蓄積されるエネルギーが小さくなるため、ドレイン - ソース間電圧を下げることができず、スイッチング素子のターンオン時に大きな短絡損失が発生してしまうという問題がある。このような軽負荷領域での効率低下は、例えば軽負荷領域での高効率化が要求されるハイブリッド自動車等におけるスイッチング電源装置の適用を困難なものとしてしまい、改善の余地があった。

30

#### 【0009】

なお、同文献では、負荷の大きさに応じて、共振回路のインダクタンスを変化させる技術についても提案されている。しかしながら、同文献の図 24 に示されているように、共振回路のインダクタンスを可変のものとすることで全体的に効率が向上してはいるが、依然として軽負荷領域では、定格負荷領域と比べて効率が低下してしまっている。

#### 【0010】

40

このように、従来の技術では、定格負荷領域における高効率を維持しつつ、それよりも負荷の小さい軽負荷領域においても高効率化が可能なスイッチング電源装置を得るのは困難であり、改善の余地があった。

#### 【0011】

本発明はかかる問題点に鑑みてなされたもので、その目的は、定格負荷領域における高効率を維持しつつ、それよりも負荷の小さい軽負荷領域においても高効率化が可能なスイッチング電源装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0012】

本発明のスイッチング電源装置は、第 1 ないし第 4 のスイッチング素子を含み、第 1 お

50

より第2のスイッチング素子の一端同士が互いに接続されて第1の接続点を構成すると共に第3および第4のスイッチング素子の一端同士が互いに接続されて第2の接続点を構成し、第1および第3のスイッチング素子の他端同士と第2および第4のスイッチング素子の他端同士との間に印加される直流入力電圧を交流電圧に変換するスイッチング回路と、第1および第2のスイッチング素子のうちの少なくとも一方と並列に外付け接続された第1の容量素子と、1次側入力および2次側出力を有すると共にこの1次側入力が第1の接続点と第2の接続点との間に接続され、上記交流電圧を変圧するトランスと、第1の接続点からトランスの1次側入力を経由して第2の接続点に至る経路内に挿入され、第1の容量素子と共にZVS動作を行うための共振回路を構成するインダクタと、トランスの2次側出力と接続され、トランスによって変圧された交流電圧に基づいて直流出力電圧を生成する出力回路と、第1および第4のスイッチング素子、または第2および第3のスイッチング素子に対してそれぞれ、固定側スイッチング素子としての第1および第2のスイッチング素子を基準として、シフト側スイッチング素子としての第4および第3のスイッチング素子との間にスイッチング位相差をなすように、これらのスイッチング素子を位相シフト制御により駆動するスイッチング駆動回路と、出力回路の負荷の大きさに応じて、第1の容量素子のうちの少なくとも1つの容量値が変化するように制御する容量素子制御回路とを備えたものである。

## 【0013】

ここで、「外付け接続」とは、容量素子を例えば第1ないし第4のスイッチング素子の寄生容量のみにより構成するのではないことを意味する。また、「スイッチング位相差」とは、スイッチング素子がオン状態となる駆動信号相互間のタイミング差を意味するものである。

## 【0014】

本発明のスイッチング電源装置では、第1ないし第4のスイッチング素子を含むスイッチング回路によって直流入力電圧が交流電圧に変換され、この交流電圧がトランスによって変圧され、この変圧された交流電圧に基づいて、出力回路により直流出力電圧が生成される。第1ないし第4のスイッチング素子は、スイッチング駆動回路によって所定のスイッチング位相差をなすように位相シフト制御により駆動され、上記第1の容量素子およびインダクタが構成する共振回路によるZVS動作によって、スイッチング位相差をなすスイッチング素子の短絡損失が抑制される。また、容量素子制御回路によって、この第1の容量素子のうちの少なくとも1つの容量値が、出力回路の負荷の大きさに応じて変化するようになされる。すなわち、出力回路の負荷の大きさに応じて、共振回路の特性が適切なものとなるように設定される。

## 【0015】

本発明のスイッチング電源装置では、第3および第4のスイッチング素子のうちの少なくとも一方と並列に外付け接続された第2の容量素子を更に設けると共に、容量素子制御回路が、第1および第2の容量素子のうち、第1の容量素子における容量値のみが変化するよう制御するのが好ましい。

## 【0016】

本発明のスイッチング電源装置では、第1ないし第4のスイッチング素子がそれぞれ寄生容量を有し、容量素子制御回路が、第1の容量素子とこの第1の容量素子に並列接続されたスイッチング素子との間の接続をオン・オフ制御することによって、第1の容量素子の容量値が変化するように制御する構成が可能である。

## 【0017】

本発明のスイッチング電源装置では、容量素子制御回路が、出力回路の負荷が小さくなるに応じて、第1の容量素子のうちの少なくとも1つの容量値が小さくなるように制御する構成が好ましい。

## 【0018】

本発明のスイッチング電源装置では、第1の容量素子のうちの少なくとも1つが、互いに並列接続された複数のコンデンサから構成され、容量素子制御回路が、これら複数のコ

ンデンサを用いて第1の容量素子の容量値が変化するように制御するように構成することが可能である。またこの場合において、容量素子制御回路が、これら複数のコンデンサのそれぞれの接続を選択的にオン・オフ制御することによって、容量素子の容量値が変化するように制御するように構成することが可能である。

#### 【発明の効果】

#### 【0019】

本発明のスイッチング電源装置によれば、共振回路によってスイッチング位相差をなすスイッチング素子の短絡損失を抑制すると共に、容量素子制御回路によって、この共振回路を構成する第1の容量素子のうちの少なくとも1つの容量値を、出力回路の負荷の大きさに応じて変化させるようにしたので、出力回路の負荷の大きさに応じて共振回路の特性を適切なものとすることができる、定格負荷領域における高効率を維持しつつ、軽負荷領域を含む広範な領域において高効率化を図ることが可能となる。

また、第1の容量素子が、第1および第2のスイッチング素子のうちの少なくとも一方と並列に外付け接続されているようにしたので、第3および第4のスイッチング素子側にコンデンサを接続した場合と比べて、特に軽負荷の領域（例えば、出力電流が10A未満の領域）における効率をより向上させることが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0021】

以下、本発明を実施するための最良の形態（以下、単に実施の形態という。）について、図面を参照して詳細に説明する。

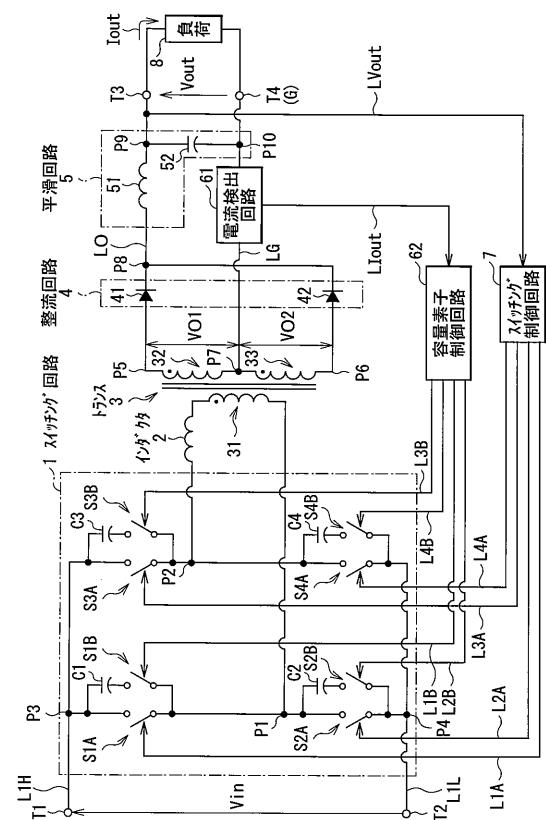

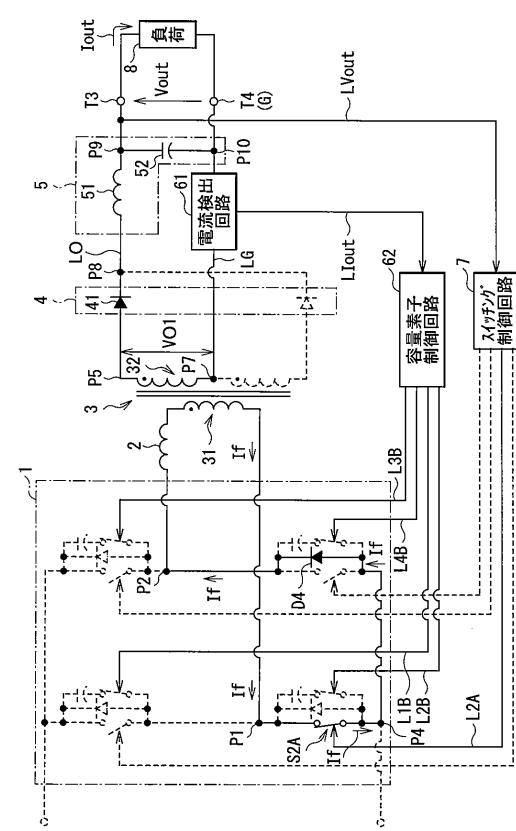

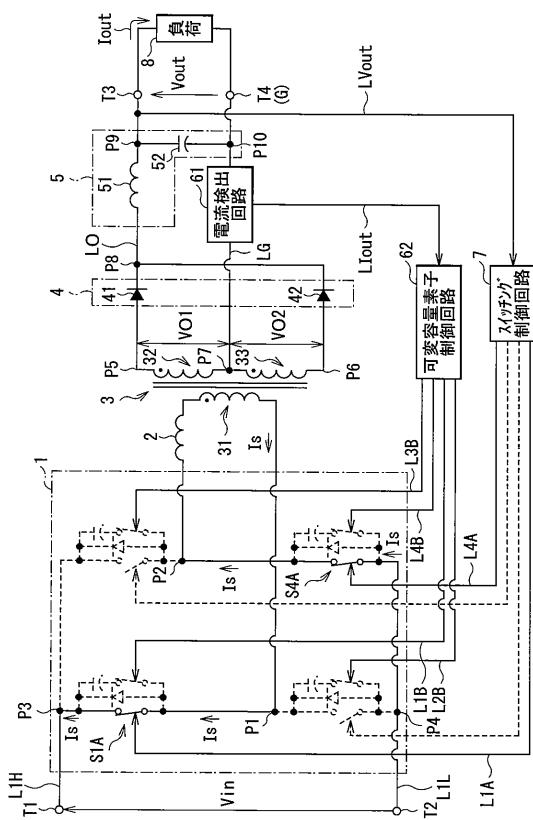

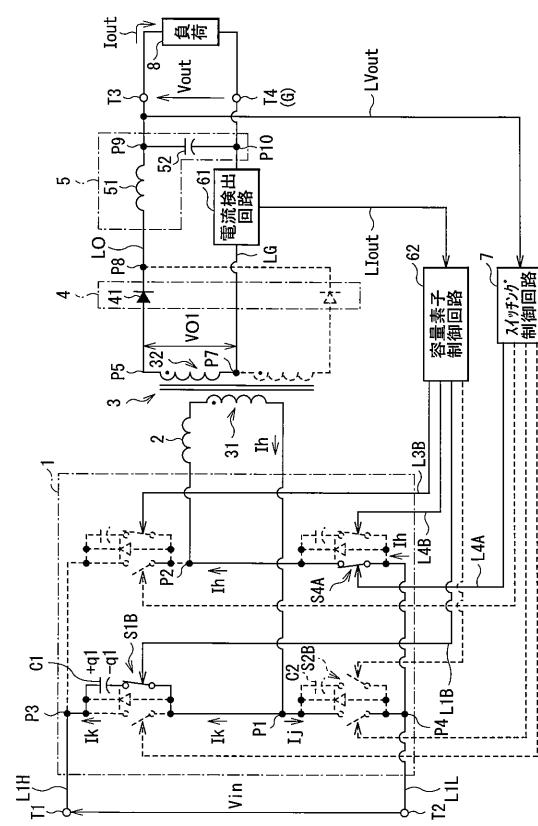

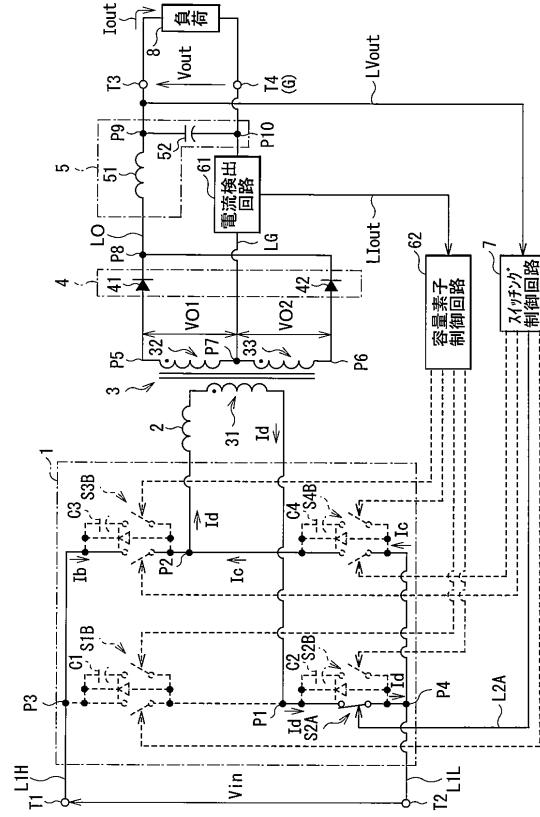

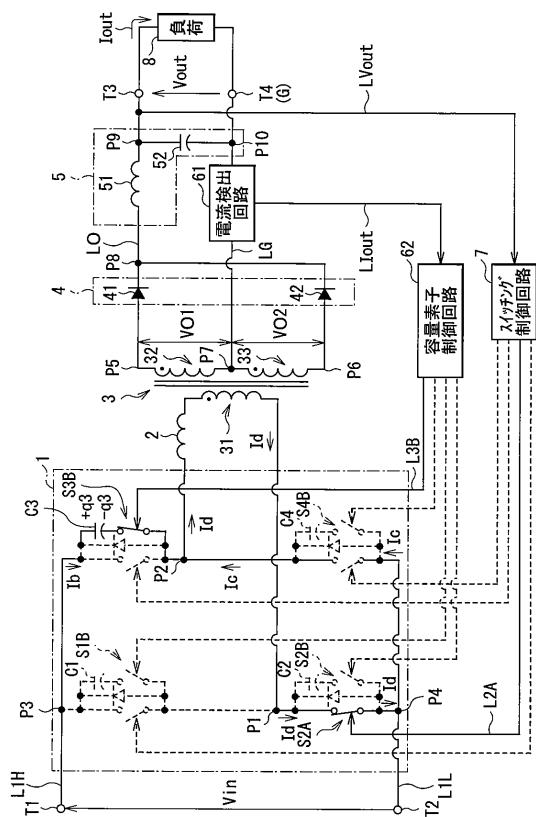

#### 【0022】

図1は、本発明の一実施の形態に係るスイッチング電源装置の構成を表すものである。このスイッチング電源装置は、図示しない高圧側電源から供給される高圧の直流入力電圧 $V_{in}$ を変換し、より低い直流出力電圧 $V_{out}$ を出力するDC-DCコンバータとして機能するものであり、後述するように位相シフト方式によるフルブリッジ型のスイッチング電源装置である。

#### 【0023】

このスイッチング電源装置は、1次側高圧ライン $L_{1H}$ と1次側低圧ライン $L_{1L}$ との間に設けられたスイッチング回路1と、インダクタ2と、1次側巻線31および2次側巻線32, 33を有し、その1次側巻線31の一端がインダクタ2を介してスイッチング回路1に接続されたトランス3とを備えている。1次側高圧ライン $L_{1H}$ の入力端子 $T_1$ と1次側低圧ライン $L_{1L}$ の入力端子 $T_2$ との間には、図示しない高圧側電源から直流入力電圧 $V_{in}$ が印加されるようになっている。このスイッチング電源装置はまた、トランス3の2次側に設けられた整流回路4と、この整流回路4に接続された平滑回路5と、この平滑回路5とトランス3との間に配置された電流検出回路61と、この電流検出回路61に接続された容量素子制御回路62と、平滑回路5に接続されたスイッチング駆動回路7とを備えている。なお、上記の高圧側電源は、高圧バッテリであってもよいし、あるいは交流発電機と整流回路との組み合わせであってもよいし、さらに、それらの組み合わせであってもよい。

#### 【0024】

スイッチング回路1は、スイッチング素子S1A～S4Aと、これらスイッチング素子S1A～S4Aのそれぞれと並列に外付け接続されたコンデンサC1～C4と、これらコンデンサC1～C4の接続をそれぞれ切断するコンデンサ切断素子S1B～S4Bとを有している。これらスイッチング素子S1A～S4Aは互いにブリッジ接続されており、具体的には、スイッチング素子S1A, S2Aの一端同士が互いに接続されて接続点P1を構成すると共に、スイッチング素子S3A, S4Aの一端同士が互いに接続されて接続点P2を構成している。また、スイッチング素子S1A, S3Aの他端同士が互いに接続されて接続点P3を構成すると共に、スイッチング素子S2A, S4Aの他端同士が互いに接続されて接続点P4を構成し、これら接続点P3, P4は、それぞれ入力端子T1, T2に接続されている。スイッチング回路1はこのような構成により、入力端子T1, T2

10

20

30

40

50

間に印加される直流入力電圧  $V_{in}$  を交流電圧に変換するようになっている。

【0025】

なお、スイッチング素子  $S1A \sim S4A$  はそれぞれ、例えば MOS-FET (Metal Oxide Semiconductor-Field Effect Transistor) などの三端子スイッチ素子により構成され、コンデンサ切断素子  $S1B \sim S4B$  はそれぞれ、例えばバイポーラトランジスタや IGBT (Insulated Gate Bipolar Transistor) などのバイポーラ出力のスイッチ素子により構成される。コンデンサ切断素子  $S1B \sim S4B$  をバイポーラ出力のスイッチ素子により構成するのは、電流を双方向に流すことができ、またオフ状態としたときに電流を完全に遮断することができるからである。

【0026】

インダクタ 2 は、その一端がスイッチング素子  $S3A, S4A$  の一端同士と接続点  $P2$  で接続され、その他端がトランス 3 の 1 次側巻線 3 1 の一端に接続されている。このインダクタ 2 は、スイッチング回路 1 内のコンデンサ  $C1 \sim C4$  と共に共振回路を構成し、この共振回路による共振特性を利用することで、後述するようにスイッチング素子  $S1A \sim S4A$  における短絡損失を抑制するようになっている。なお、このインダクタ 2 の配置はこの位置には限られず、接続点  $P1$  からトランスの 1 次側巻線 3 1 を経由して接続点  $P2$  に至る経路内に挿入されればよい。また、このインダクタ 2 の代わりに、もしくはインダクタ 2 に加えて、トランス 3 における 1 次側巻線 3 1 のリーケージインダクタンス (図示せず) を用いて共振回路を構成するようにしてもよい。

【0027】

トランス 3 の 1 次側巻線 3 1 は、その一端がインダクタ 2 の他端に接続され、その他端がスイッチング素子  $S1A, S2A$  の一端同士と接続点  $P1$  で接続されている。また、2 次側巻線 3 2, 3 3 の一端はそれぞれ接続点  $P7$  (センタタップ) で互いに接続され、それらの他端はそれぞれ、ダイオード  $41, 42$  のアノードと接続点  $P5, P6$  で接続されている。また、接続点  $P7$  (センタタップ) は接地ライン  $LG$  および電流検出回路 6 1 を介して出力端子  $T4$  に導かれている。つまり、このスイッチング電源装置はセンタタップ型のものである。このトランス 3 は、スイッチング回路 1 によって変換された交流電圧を降圧し、一対の 2 次側巻線 3 2, 3 3 の他端 (接続点  $P5, P6$ ) から、互いに 180 度位相が異なる交流電圧  $V_{O1}, V_{O2}$  を出力するようになっている。なお、この場合の降圧の度合いは、1 次側巻線 3 1 と 2 次側巻線 3 2, 3 3 との巻数比によって定まる。

【0028】

整流回路 4 は、一対のダイオード  $41, 42$  から構成される両波整流型のものである。ダイオード  $41$  のアノードは、2 次側巻線 3 2 の他端と接続点  $P5$  で接続され、ダイオード  $42$  のアノードは、2 次側巻線 3 3 の他端と接続点  $P6$  で接続されている。また、これらダイオード  $41, 42$  のカソード同士は、接続点  $P8$  で互いに接続されると共に、出力ライン  $LO$  に接続されている。つまり、この整流回路 4 はカソードコモン接続の構造を有しており、トランス 3 の交流出力電圧  $V_{O1}, V_{O2}$  の各半波期間をそれぞれダイオード  $41, 42$  によって個別に整流して直流電圧を得るようになっている。

【0029】

平滑回路 5 は、チョークコイル 5 1 と平滑コンデンサ 5 2 を含んで構成されている。チョークコイル 5 1 は、出力ライン  $LO$  に挿入配置されており、その一端はダイオード  $41, 42$  のカソード同士と接続点  $P8$  で接続され、その他端は平滑コンデンサ 5 2 の一端および出力ライン  $LO$  の出力端子  $T3$  と接続点  $P9$  で接続されている。平滑コンデンサ 5 2 は、出力ライン  $LO$  (具体的には、接続点  $P9$ ) と接地ライン  $LG$  (具体的には、接続点  $P10$ ) との間に接続されている。出力ライン  $LO$  の端部には、出力端子  $T4$  が設けられている。平滑回路 5 はこのような構成により、整流回路 4 で整流された直流電圧を平滑化して直流出力電圧  $V_{out}$  を生成し、これを出力端子  $T3, T4$  から負荷 8 へ供給するようになっている。

【0030】

電流検出回路 6 1 は、接地ライン  $LG$  に挿入配置 (具体的には、接続点  $P7, 10$  の間

10

20

30

40

50

に配置)されて、出力電流  $I_{out}$  に対応する信号  $L_{I_{out}}$  を出力するようになっている。なお、1次側巻線 3 1 に流れる電流は出力電流  $I_{out}$  に比例しているので、図 1 の構成とは異なり、電流検出回路 6 1 を、接続点 P 1 からインダクタ 2 および 1 次側巻線 3 1 を介して接続点 P 2 に至る経路内に挿入配置するようにしてもよい。また、図 1 の構成とは異なり、電流検出回路 6 1 を、図示しない高圧側電源からスイッチング回路 1 に流れる電流を検出するように配置してもよい。

#### 【0031】

容量素子制御回路 6 2 は、電流検出回路 6 1 から出力された信号  $L_{I_{out}}$  に基づいて、スイッチング回路 1 内のコンデンサ C 1 ~ C 4 の容量値が変化するように制御するものである。具体的には、本実施の形態のスイッチング電源装置では、コンデンサ切断素子 S 1 B ~ S 4 B に対してそれぞれコンデンサ切断信号  $L_{1B} ~ L_{4B}$  を供給し、例えばコンデンサ C 1 ~ C 4 の接続をオン・オフ制御することで、スイッチング素子 S 1 A ~ S 4 A に並列な容量値が変化するように制御するようになっている。このようにして容量素子制御回路 6 2 は、後述するように共振回路の共振特性を負荷 8 の大きさ(出力電流  $I_{out}$  の大きさ)に応じて適切に変化させるようになっている。なお、前述のようにスイッチング素子 S 1 A ~ S 4 A を MOS - FET により構成した場合には、この MOS - FET の寄生容量も、スイッチング素子 S 1 A ~ S 4 A に並列な容量として利用することができる。

#### 【0032】

スイッチング駆動回路 7 は、出力電圧  $V_{out}$  に対応する信号  $L_{V_{out}}$ (出力ライン LO の接続点 P 9 から供給される)に基づいて、スイッチング回路 1 内のスイッチング素子 S 1 A ~ S 4 A を駆動するものである。具体的には、本実施の形態のスイッチング電源装置では、スイッチング素子 S 1 A ~ S 4 A に対してそれぞれスイッチング駆動信号  $L_{1A} ~ L_{4A}$  を供給し、これらスイッチング素子 S 1 A ~ S 4 A をオン・オフ制御するようになっている。また、スイッチング駆動回路 7 は、後述するようにこれらスイッチング素子 S 1 A ~ S 4 A に対してスイッチング位相制御を行い、スイッチング位相差を適切に設定することで、直流出力電圧  $V_{out}$  を安定化させるようになっている。

#### 【0033】

ここで、スイッチング素子 S 1 A ~ S 4 A はそれぞれ、本発明における「第 1 ないし第 4 のスイッチング素子」の一具体例に対応するものであり、コンデンサ C 1 ~ C 4 およびコンデンサ切断素子 S 1 B ~ S 4 B は、本発明における「容量素子」の一具体例に対応するものである。また、1 次側巻線 3 1 および 2 次側巻線 3 2, 3 3 はそれぞれ、本発明における「1 次側入力」および「2 次側出力」の一具体例に対応するものであり、整流回路 4 および平滑回路 5 は、本発明における「出力回路」の一具体例に対応するものである。また、接続点 P 1, P 2 はそれぞれ、本発明における「第 1 の接続点」および「第 2 の接続点」の一具体例に対応するものであり、接続点 P 3, P 4 はそれぞれ、本発明における「第 1 および第 3 のスイッチング素子の他端同士」ならびに「第 2 および第 4 のスイッチング素子の他端同士」の一具体例に対応するものである。

#### 【0034】

次に、図 2 ~ 図 13 を参照して、以上のような構成のスイッチング電源装置の動作を、負荷 8 の大きさ(出力電流  $I_{out}$  の大きさ)に応じて、定格負荷領域(例えば、出力電流  $I_{out}$  が 50 A 以上の領域)と、軽負荷領域(例えば、出力電流  $I_{out}$  が 30 A 未満の領域)と、中間負荷領域(例えば、出力電流  $I_{out}$  が 30 A 以上 50 A 未満の領域)とに分けて説明する。なお、以下の回路図においては、スイッチング素子 S 1 A ~ S 4 A およびコンデンサ C 1 ~ C 4 と並列接続されたダイオード D 1 ~ D 4 についても考慮するものとする。これらダイオード D 1 ~ D 4 としては、前述のようにスイッチング素子 S 1 A ~ S 4 A を MOS - FET により構成した場合には、この MOS - FET の寄生ダイオードを利用することができ、寄生ダイオードを持たない他の三端子スイッチ素子により構成した場合には、外付け接続したものを利用する。

#### 【0035】

まず、定格負荷領域における動作を説明する。

10

20

30

40

50

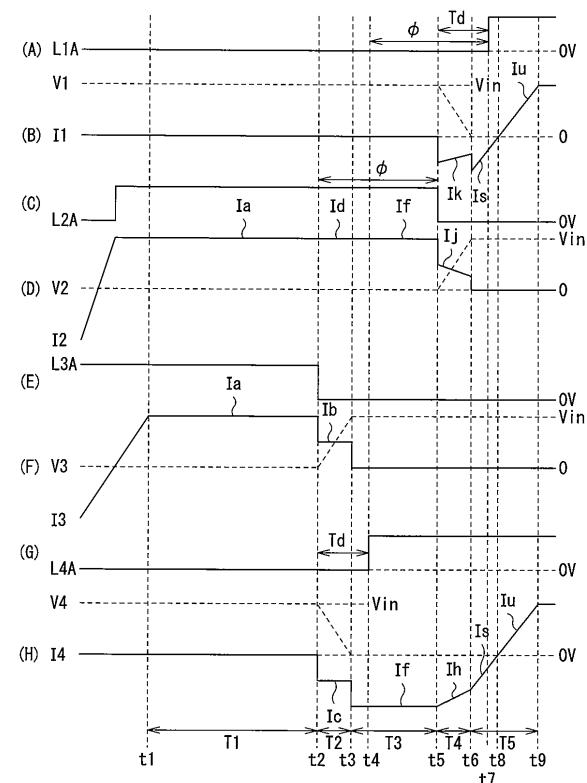

## 【0036】

図2は、定格負荷領域におけるスイッチング電源装置の各部の電圧波形を表すもので、(A)はスイッチング駆動信号L1Aの電圧波形を示し、(B)は並列接続されたスイッチング素子S1AとダイオードD1とコンデンサC1とからなる回路に流れる電流I1の波形を実線で、スイッチング素子S1Aの両端間の電圧V1(スイッチング素子S1Aが例えばMOS-FETにより構成されている場合には、ドレイン-ソース間の電圧。以下同様。)の波形を点線で示し、(C)はスイッチング駆動信号L2Aの電圧波形を示し、(D)は並列接続されたスイッチング素子S2AとダイオードD2とコンデンサC2とからなる回路に流れる電流I2の波形を実線で、スイッチング素子S2Aの両端間の電圧V2の波形を点線で示し、(E)はスイッチング駆動信号L3Aの電圧波形を示し、(F)は並列接続されたスイッチング素子S3AとダイオードD3とコンデンサC3とからなる回路に流れる電流I3の波形を実線で、スイッチング素子S3Aの両端間の電圧V3の波形を点線で示し、(G)はスイッチング駆動信号L4Aの電圧波形を示し、(H)は並列接続されたスイッチング素子S4AとダイオードD4とコンデンサC4とからなる回路に流れる電流I4の波形を実線で、スイッチング素子S4Aの両端間の電圧V4の波形を点線で示している。なお、ここに示した例では、電圧V1~V4の最大値=Vinとする。

## 【0037】

図1に示したスイッチング電源装置において、ブリッジ接続されたスイッチング素子S1A~S4Aは、スイッチング制御回路7から供給されるスイッチング駆動信号L1A~L4Aにより、すべて同一のオン幅および周波数となるように駆動される。そしてこれらスイッチング素子S1A~S4Aのスイッチング動作により、トランス3の1次側巻線31に流れる電流が双方向に切り替えられ、それによってトランス3が励磁される。トランス3の2次側巻線32, 33に生じた交流電圧は、整流回路4によって整流され、平滑回路5によって平滑化されることで、直流出力電圧Voutとして、出力端子T3, T4から負荷8に供給される。

## 【0038】

スイッチング素子S1A~S4Aが駆動されるタイミングについてみると、これらのスイッチング素子は、2つのスイッチング素子対に区分される。具体的には、スイッチング素子S1Aおよびスイッチング素子S2Aはともに、時間軸上における固定タイミングでオンするように制御され、「固定側スイッチング素子」と称される。また、スイッチング素子S3Aおよびスイッチング素子S4Aはともに、時間軸上における可変タイミングでオンするように制御され、「シフト側スイッチング素子」と称される。

## 【0039】

また、これらスイッチング素子S1A~S4Aは、スイッチング動作のいかなる状態においても、直流入力電圧Vinが印加された入力端子T1, T2が電気的に短絡されない組み合わせおよびタイミングで駆動される。具体的には、スイッチング素子S1Aおよびスイッチング素子S2A(固定側スイッチング素子)は、同時にオンとなることはない。また、スイッチング素子S3Aおよびスイッチング素子S4A(シフト側スイッチング素子)も、同時にオンとなることはない。これらが同時にオンとなるのを回避するためにとられる時間的間隔は、デッドタイムTdと称される。

## 【0040】

スイッチング素子S1Aおよびスイッチング素子S4Aは同時にオンとなる期間を有し、この同時にオンとなる期間において、トランス3の1次側巻線31が励磁される。これらスイッチング素子S1Aおよびスイッチング素子S4Aは、スイッチング素子S1A(固定側スイッチング素子)を基準としてスイッチング位相差 $\theta$ をなすように動作する。これらが同時にオンとなる期間は、このスイッチング位相差 $\theta$ を制御することにより、制御される。

## 【0041】

また同様に、スイッチング素子S2Aおよびスイッチング素子S3Aは同時にオンとなる期間を有し、この同時にオンとなる期間において、トランス3の1次側巻線31が、上

10

20

30

40

50

記の場合とは逆方向に励磁される。これらスイッチング素子 S 2 A およびスイッチング素子 S 3 A は、スイッチング素子 S 2 A (固定側スイッチング素子) を基準としてスイッチング位相差 をなすように動作する。

【 0 0 4 2 】

さらに、出力電圧  $V_{out}$  の制御のために、例えば出力電圧  $V_{out}$  に対応する信号  $L_{V_{out}}$  に基づいて、スイッチング素子 S 1 A とスイッチング素子 S 4 A とのスイッチング位相差 、およびスイッチング素子 S 2 A とスイッチング素子 S 3 A とのスイッチング位相差 がそれぞれ制御され、スイッチング素子 S 1 A およびスイッチング素子 S 4 A が同時にオンになっている時間、ならびにスイッチング素子 S 2 A およびスイッチング素子 S 3 A が同時にオンになっている時間が変化する。これにより、トランス 3 の 1 次側巻線 3 1 に印加される電圧のデューティ比が変化し、出力電圧  $V_{out}$  が安定化される。

10

【 0 0 4 3 】

スイッチング素子 S 2 A がオフとなってから、スイッチング素子 S 1 A がオンとなるまでのデッドタイム  $T_d$  の期間中に、スイッチング素子 S 1 A に並列接続されたコンデンサ C 1 、スイッチング素子 S 2 A に並列接続されたコンデンサ C 2 、インダクタ 2 およびトランス 3 の励磁インダクタンスにより、共振回路が構成される。この共振回路による共振作用を利用して、コンデンサ C 1 に蓄積されていた電荷が全て放出された後にスイッチング素子 S 1 A をオンにすることにより、ZVS 動作を達成でき、コンデンサ C 1 の短絡損失およびそれに伴うノイズの発生が抑制される。スイッチング素子 S 2 A においても同様であり、コンデンサ C 2 に蓄積されていた電荷が全て放出された後にスイッチング素子 S 2 A をオンにすることにより、ZVS 動作を達成でき、コンデンサ C 2 の短絡損失およびそれに伴うノイズの発生が抑制される。

20

【 0 0 4 4 】

また、スイッチング素子 S 3 A がオフとなってから、スイッチング素子 S 4 A がオンとなるまでのデッドタイム  $T_d$  の期間中に、スイッチング素子 S 3 A に並列接続されたコンデンサ C 3 、スイッチング素子 S 4 A に並列接続されたコンデンサ C 4 、インダクタ 2 およびチョークコイル 5 1 のインダクタンスをトランス 3 の 1 次側に換算したインダクタにより、共振回路が構成される。この共振回路による共振作用を利用して、コンデンサ C 4 に蓄積されていた電荷が全て放出された後にスイッチング素子 S 4 A をオンにすることにより、ZVS 動作を達成でき、コンデンサ C 4 の短絡損失およびそれに伴うノイズの発生が抑制される。スイッチング素子 S 3 A においても同様であり、コンデンサ C 3 に蓄積されていた電荷が全て放出された後にスイッチング素子 S 3 A をオンにすることにより、ZVS 動作を達成でき、コンデンサ C 3 の短絡損失およびそれに伴うノイズの発生が抑制される。

30

【 0 0 4 5 】

なお、スイッチング素子 S 1 A ~ S 4 A にそれぞれ並列接続されたコンデンサ C 1 ~ C 4 は、電流検出回路 6 1 から出力された出力電流  $I_{out}$  に対応する信号  $L_{I_{out}}$  に基づいて容量素子制御回路により生成されたコンデンサ切断信号  $L_{1B} ~ L_{4B}$  によって、その接続がオン・オフ制御される。ただし、定格負荷領域ではこれらコンデンサ C 1 ~ C 4 は常に接続され、インダクタ 2 と共に共振回路を構成するようになっている。

40

【 0 0 4 6 】

ここで、スイッチング電源装置の動作をさらに詳しく説明する。このスイッチング電源装置では、図 2 に示した各部の電圧電流波形およびスイッチング駆動信号  $L_{1A} ~ L_{4A}$  から、回路の動作上、大きく分けて 5 つのステージ (期間  $T_1 ~ T_5$  ) が考えられる。以下、図 2 に加えて図 3 ~ 図 10 を参照して、各ステージについて説明する。

【 0 0 4 7 】

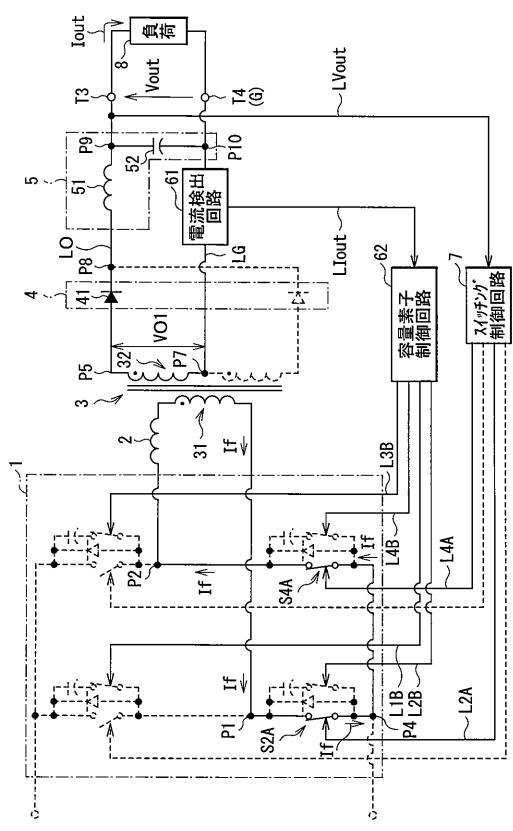

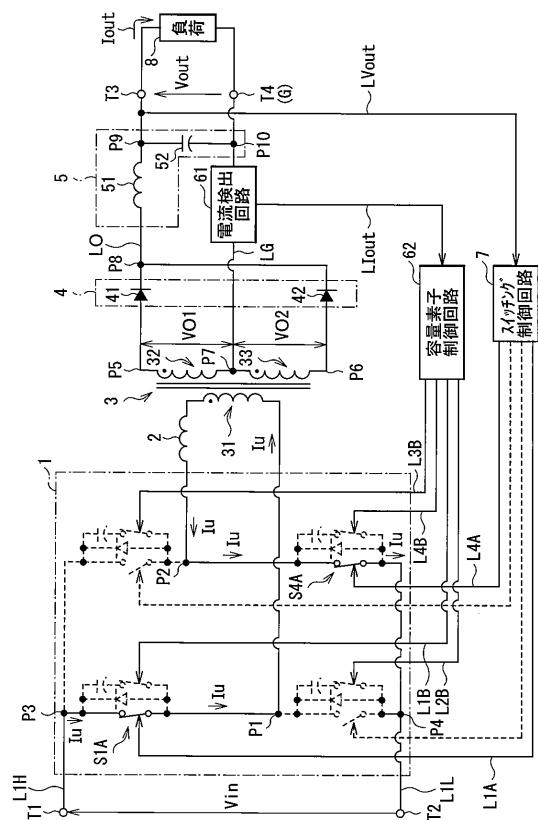

< 第 1 のステージ >

第 1 のステージは、図 2 の期間  $T_1$  に対応する。図 3 は、図 1 に示したスイッチング電源装置において、第 1 のステージで働く回路部分を実線で示したものである。この第 1 のステージは、スイッチング素子 S 2 A とスイッチング素子 S 3 A とがオン状態になり、ス

50

イッティング電源装置の入力側から出力側へ電力を伝送している期間である。スイッティング素子 S 1 A およびスイッティング素子 S 4 A はオフ状態にある。ここで、スイッティング素子 S 2 A とスイッティング素子 S 3 A とに流れる電流  $I_a$  は、出力電流  $I_{out}$  とトランス 3 の巻数比とによって定まる。この第 1 のステージは、スイッティング素子 S 3 A がターンオフするまで継続する。

【 0 0 4 8 】

< 第 2 のステージ >

第 2 のステージは、図 2 の期間  $T_2$  に対応する。図 4 は、図 1 に示したスイッティング電源装置において、第 2 のステージで働く回路部分を実線で示したものである。第 2 のステージは、スイッティング素子 S 3 A に並列接続されたコンデンサ C 3 が充電される ( $+q_3$ ,  $-q_3$ ) と共に、スイッティング素子 S 4 A に並列接続されたコンデンサ C 4 に蓄積されていた電荷 ( $+q_4$ ,  $-q_4$ ) が放電される期間である。第 2 のステージでは、スイッティング素子 S 3 A がオフになる。また、スイッティング素子 S 1 A およびスイッティング素子 S 4 A はオフ状態を継続する。このようにスイッティング素子 S 3 A がオフとなつことで、上記のようにコンデンサ C 3 が充電されると共に、コンデンサ C 4 に蓄積されていた電荷が放電される。第 2 のステージでは、トランス 3 が電力伝送を行っているので、コンデンサ C 3 は一定電流  $I_b$  で充電され、コンデンサ C 4 の蓄積電荷は一定電流  $I_c$  で放電される。よって、図 2 に示したように、スイッティング素子 S 3 A の両端間の電圧  $V_3$  およびスイッティング素子 S 4 A の両端間の電圧  $V_4$  は、直線的に変化する。この第 2 のステージは、スイッティング素子 S 4 A に並列接続されたダイオード D 4 が導通し、スイッティング素子 S 3 A の両端間の電圧  $V_3$  が直流入力電圧  $V_{in}$  によりクランプされるまで継続する。

【 0 0 4 9 】

< 第 3 のステージ >

第 3 のステージは、図 2 の期間  $T_3$  に対応する。図 5 および図 6 は、図 1 に示したスイッティング電源装置において、第 3 のステージで働く回路部分を実線で示したものである。第 3 のステージは、インダクタ 2 に蓄積されていたエネルギーが、スイッティング素子 S 4 A に並列接続されたダイオード D 4 とスイッティング素子 S 2 A とを通じて放出される期間である(図 5)。よって、ダイオード D 4 およびスイッティング素子 S 2 A に流れる電流  $I_f$  はほとんど変化しない。図 2 に示すように、第 3 のステージの途中で、スイッティング素子 S 4 A がターンオンし、ダイオード D 4 に流れていた電流  $I_f$  がスイッティング素子 S 4 A に流れるようになるが(図 6)、基本的な動作状態は変化しない。第 3 のステージは、スイッティング素子 S 2 A がターンオフするまで継続する。

【 0 0 5 0 】

< 第 4 のステージ >

第 4 のステージは、図 2 の期間  $T_4$  に対応する。図 7 は、図 1 に示したスイッティング電源装置において、第 4 のステージで働く回路部分を実線で示したものである。第 4 のステージでは、第 2 のステージと異なり、トランス 3 が短絡状態となっているため、スイッティング素子 S 2 A がターンオフすると、スイッティング素子 S 1 A に並列接続されたコンデンサ C 1、スイッティング素子 S 2 A に並列接続されたコンデンサ C 2 およびインダクタ 2 が共振する。そのため、図 2 に示したように、コンデンサ C 1 に流れる電流  $I_k$ 、スイッティング素子 S 1 A の両端間の電圧  $V_1$ 、コンデンサ C 2 に流れる電流  $I_j$  およびスイッティング素子 S 2 A の両端間の電圧  $V_2$  は、三角関数的に変化する。第 4 のステージは、スイッティング素子 S 1 A に並列接続されたダイオード D 1 が導通するまで継続する。

【 0 0 5 1 】

< 第 5 のステージ >

第 5 のステージは、図 2 の期間  $T_5$  に対応する。図 8 ~ 図 10 は、図 1 に示したスイッティング電源装置において、第 5 のステージで働く回路部分を実線で示したものである。第 5 のステージでは、まず、スイッティング素子 S 1 A に並列接続されたダイオード D 1 が導通したことにより、インダクタ 2 に蓄積されていたエネルギーが、スイッティング素子 S 4 A とダイオード D 1 とを通じて図示しない高圧側電源に回生される(図 8)。この第 5 の

10

20

30

40

50

ステージの途中で、スイッチング素子 S 1 A がターンオン（図 9）するが、基本的な動作状態は変化しない。インダクタ 2 に流れる電流  $I_s$  がゼロになると（図 2）、インダクタ 2 に充電電流  $I_u$  が流れる（図 10）。充電電流  $I_u$  は、整流回路 4 内のダイオード D 1 に流れる電流が出力電流  $I_{out}$  に等しくなるまで流れ続ける。よって、図 2 に示したように、この第 5 のステージにおいて流れる電流は、直線的に変化する。また、インダクタ 2 に流れる電流  $I_s$  がゼロになる前にスイッチング素子 S 1 A もしくはスイッチング素子 S 2 A をターンオンさせることで、デッドタイム  $T_d$  の期間中の再共振が防止される。

#### 【 0 0 5 2 】

このように、定格負荷領域では、従来のようにスイッチング素子 S 1 A ~ S 4 A にコンデンサ C 1 ~ C 4 を並列接続し、これらコンデンサ C 1 ~ C 4 とインダクタ 2 とにより適切な共振回路を構成することで、その共振特性を利用して ZVS 動作が達成され、スイッチング位相制御されるスイッチング素子同士の短絡損失が抑制される。

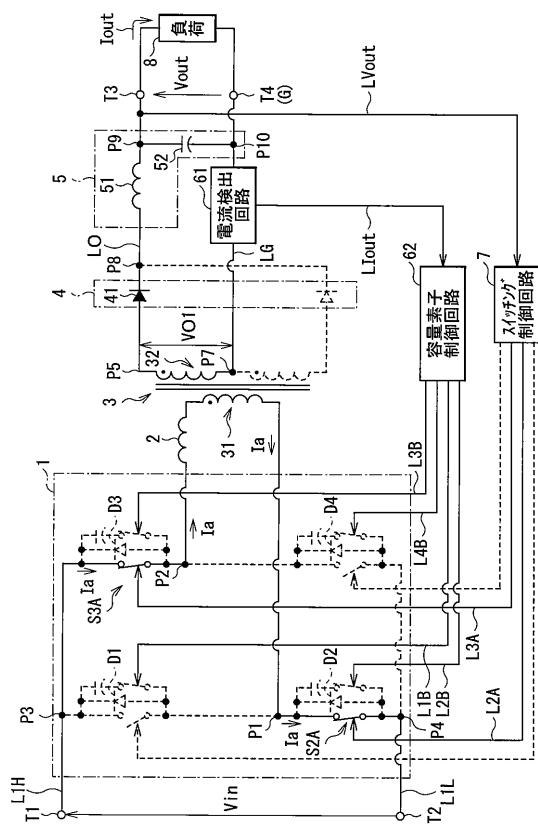

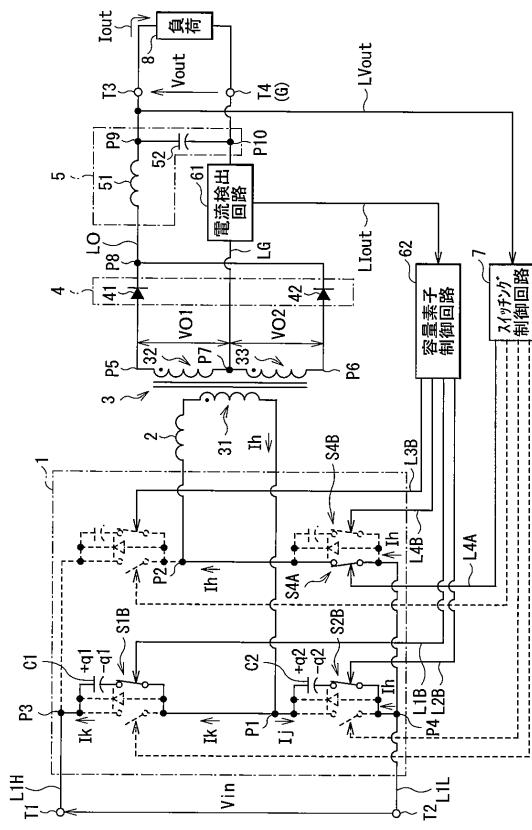

#### 【 0 0 5 3 】

次に、軽負荷領域における動作を説明する。

#### 【 0 0 5 4 】

この軽負荷領域では、電流検出回路 6 1 によって出力電流  $I_{out}$  がこの領域の値であることが検出されると、容量素子制御回路 6 2 によって、スイッチング素子 S 1 A に並列接続されたコンデンサ C 1 およびスイッチング素子 S 2 A に並列接続されたコンデンサ C 2 、すなわち固定側スイッチング素子のコンデンサの接続が切断される。よって、例えば前述の第 4 のステージ（図 7）においては、図 11 に示したような回路構成となる。なお、図 11 に示した回路構成では、コンデンサ C 1, C 2 の接続が切断されているため、図 7 に示した回路構成とは異なり、そのままでは LC 共振回路が成立しなくなってしまう。そこで、前述のように例えばスイッチング素子 S 1 A ~ S 4 A を MOS-FET により構成した場合には、この MOS-FET の微小な寄生容量を利用し、スイッチング素子 S 1 A ~ S 4 A を他の素子により構成した場合には、容量の小さいコンデンサを外付け接続して利用するようとする。

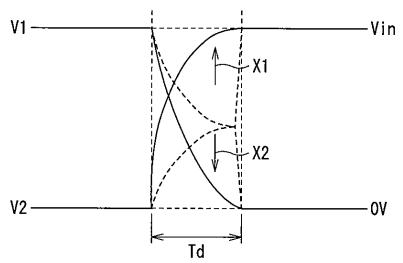

#### 【 0 0 5 5 】

このように、固定側スイッチング素子のコンデンサ C 1, C 2 の接続を切断することで、共振回路の容量値 C を小さくし、以下の式（1）により、共振回路のインピーダンス Z を大きくすることができる。ここで、式（1）中の L は、共振回路のインダクタンスを表している。よって、共振回路のインピーダンス Z を大きくすることで、以下の式（2）により、スイッチング素子 S 2 A の両端間の電圧 V 4 のピーク値 V 2 (peak) を大きくすることができ、またスイッチング素子 S 1 A の両端間の電圧 V 1 の最小値も小さくすることができる（それぞれ、図 12 の矢印 X 1, X 2）。なお、式（2）中の n は、トランジスタ 3 における 1 次側巻線 3 1 と 2 次側巻線 3 2, 3 3 との巻数比を表している。

#### 【 0 0 5 6 】

$$Z = \{ L / (2C) \}^{1/2} \quad \dots (1)$$

$$V_2(\text{peak}) = n \cdot I_{out} \cdot Z \quad \dots (2)$$

#### 【 0 0 5 7 】

ここで、図 12 に示したように、共振回路による ZVS 動作をしやすくするためには、以下の式（3）により、このスイッチング素子 S 4 A の両端間の電圧 V 4 のピーク値 V 4 (peak) を直流入力電圧  $V_{in}$  以上の値にすればよい。したがって、コンデンサ C 1 およびコンデンサ C 2 の接続を切断し、共振回路のインピーダンス Z を大きくすることで、共振回路による ZVS 動作をしやすくし、定格負荷領域と同様に、軽負荷領域においてもスイッチング素子の短絡損失を抑制することができる。また、たとえ ZVS 動作が達成できなかったとしても、共振回路の容量値 C を小さくしているので、以下の式（4）により、スイッチング素子の短絡損失  $P_{loss}$  を小さく抑えることができる。なお、式（4）中の V および f はそれぞれ、コンデンサの両端間の電圧、および共振回路の共振周波数を表している。

#### 【 0 0 5 8 】

10

20

30

40

50

$$V_2(\text{peak}) = V_{in} \dots (3)$$

$$P_{loss} = (1/2) \cdot C \cdot V^2 \cdot f \dots (4)$$

## 【0059】

最後に、中間負荷領域における動作を説明する。

## 【0060】

この中間負荷領域では、電流検出回路61によって出力電流Ioutがこの領域の値であることが検出されると、容量素子制御回路62によって、固定側スイッチング素子のコンデンサC1, C2のいずれか一方の接続が切断される。よって、例えばコンデンサC2の接続を切断した場合、例えば前述の第4のステージ(図7)においては、図13に示したような回路構成となる。

10

## 【0061】

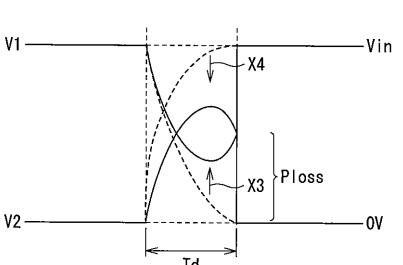

前述の軽負荷領域とは異なり、固定側スイッチング素子のコンデンサC1, C2のいずれか一方のみの接続を切断するのは、中間負荷領域では両方のコンデンサの接続を切断すると、以下の式(5)により共振回路の共振角周波数が軽負荷領域の場合と比べて高くなりすぎると共に、もともと共振時のエネルギーも軽負荷領域の場合と比べて大きいため、図14の矢印X3で示したように、スイッチング素子S1Aの両端間の電圧V1がターンオフする際に直流入力電圧Vin近くまで戻ってしまう傾向があるからである(この際、図14の矢印X4で示したように、スイッチング素子S2Aの両端間の電圧V2も下がってしまう)。このように、スイッチング素子S1Aの両端間の電圧V1がターンオフする際に直流入力電圧Vin近くまで戻ってしまうと、スイッチング素子の短絡損失Plossが大きくなってしまう。したがって、固定側スイッチング素子のコンデンサC1, C2のいずれか一方のみの接続を切断することで、共振回路のインピーダンスZを大きくすると共に共振回路の共振角周波数が高くなりすぎないようにし、定格負荷領域および軽負荷領域と同様に、中間負荷領域においてもスイッチング素子の短絡損失Plossを抑制することができる。

20

## 【0062】

$$= \{ 1 / (2LC) \}^{1/2} \dots (5)$$

## 【0063】

次に、具体例として、図1の構成のスイッチング電源装置において、スイッチング素子S1A～S4AをMOS-FETにより構成すると共にコンデンサ切断素子S1B～S4BをIGBTにより構成し、固定側スイッチング素子のコンデンサC1, C2 = 3300pFおよびシフト側スイッチング素子のコンデンサC3, C4 = 1000pFを外付け接続した場合について説明する。

30

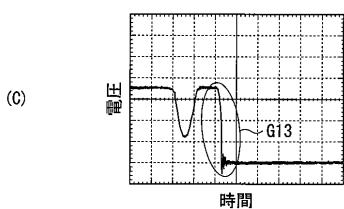

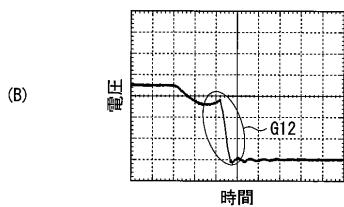

## 【0064】

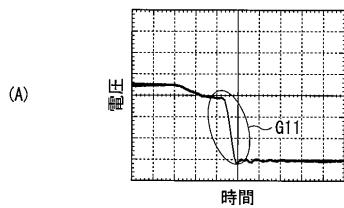

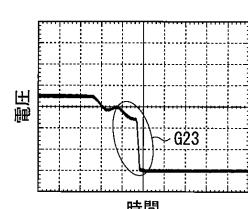

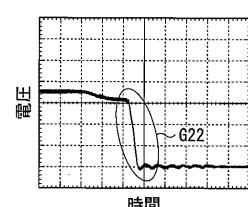

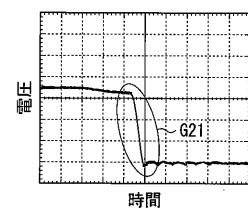

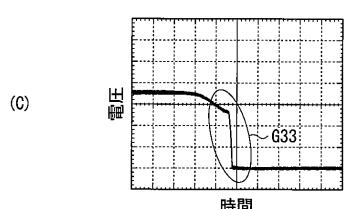

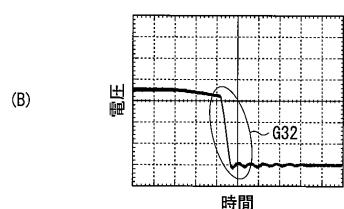

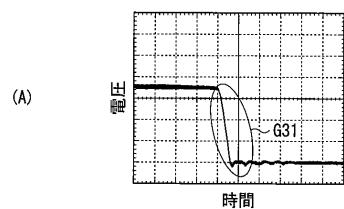

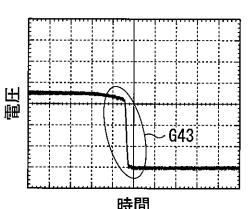

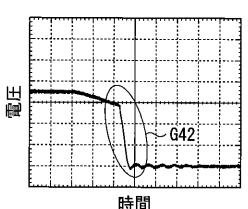

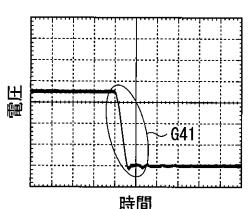

図15～図18はそれぞれ、出力電流Iout = 20A, 10A, 5A, 2Aの場合における、ターンオン時のスイッチング素子S1Aの両端間の電圧V1の波形を示している。また、各図において、(A)はコンデンサC1, C2の両方を接続している場合を、(B)はコンデンサC2のみを切断している場合を、(C)はコンデンサC1, C2の両方を切断している場合を示している。また、各図の縦軸は電圧(V)を、横軸は時間(nS)を表している。

40

## 【0065】

このように、図15～図18のいずれの場合も、(A) (B) (C)の順に共振回路の容量値Cを小さくしていくのに応じて、共振回路のインピーダンスZが大きくなり、短絡損失Plossが小さくなるよう動作する。よって、それぞれの図中の符号G11～G13, G21～G23, G31～G33, G41～G43に示したように、スイッチング素子S1Aの両端間の電圧V1の波形が下がりやすくなっていることが分かる。

## 【0066】

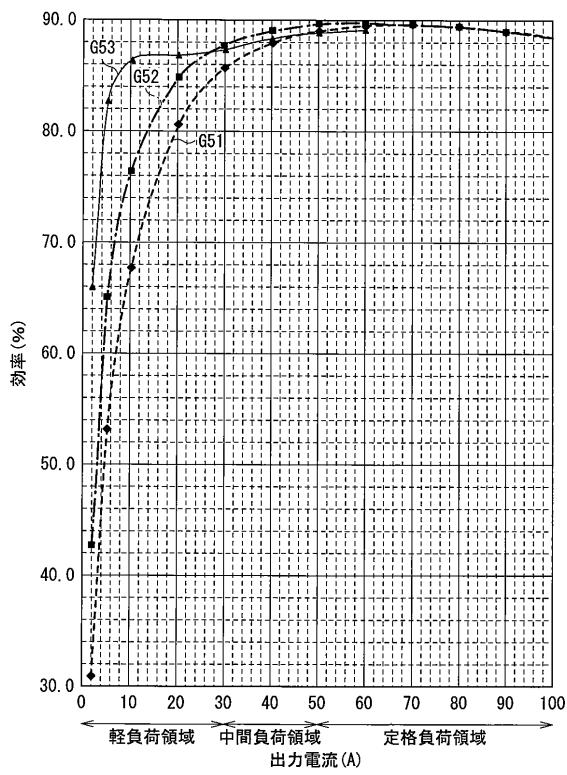

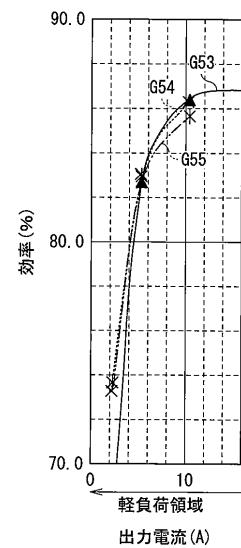

また、図19は、図15～図18のそれぞれの場合におけるスイッチング電源装置の効率を、出力電流対効率特性図としてまとめたものである。ここで、図中の符号G51～G53で示した曲線はそれぞれ、コンデンサC1, C2の両方を接続している場合(図15

50

～図18の(A)図に対応する)、コンデンサC2のみを切断している場合(図15～図18の(B)図に対応する)、およびコンデンサC1、C2の両方を切断している場合(図15～図18の(C)図に対応する)を表している。また、各図の縦軸は効率(%)を、横軸は出力電流Iout(A)を表している。また、図中、一例としてそれぞれ、定格負荷領域を出力電流Ioutが50A以上の領域と、中間負荷領域を出力電流Ioutが30～50Aの領域と、軽負荷領域を出力電流Ioutが0～30Aの領域として表している。

#### 【0067】

このように、軽負荷領域および中間負荷領域では、曲線G51と比べて、曲線G52、G53の場合のほうが効率が向上しており、軽負荷領域では曲線G53の場合が特に効率が向上していることが分かる。よって、負荷が小さくなるに応じて、すなわち出力電流Ioutが小さくなるに応じてコンデンサを切断するように制御することで、スイッチング素子の短絡損失Plossを抑制し、軽負荷領域から定格負荷領域に至る広範な領域において、高効率化を図ることができる。10

#### 【0068】

以上のように、本実施の形態では、スイッチング素子S1A～S4AにコンデンサC1～C4を並列接続することで、これらコンデンサC1～C4とインダクタ2とにより適切な共振回路を構成し、この共振回路の共振特性によってスイッチング位相差をなすスイッチング素子の短絡損失を抑制すると共に、容量素子制御回路62によって、固定側スイッチング素子のコンデンサC1、C2の容量値を、負荷8の大きさ(出力電流Ioutの大きさ)に応じて変化させるようにしたので、負荷8の大きさに応じて共振回路の特性を適切なものとすることができる、定格負荷領域における高効率を維持しつつ、軽負荷領域および中間負荷領域においても高効率化を図ることが可能となる。20

#### 【0069】

以上、実施の形態を挙げて本発明を説明したが、本発明はこの実施の形態に限定されるものではなく、種々の変形が可能である。

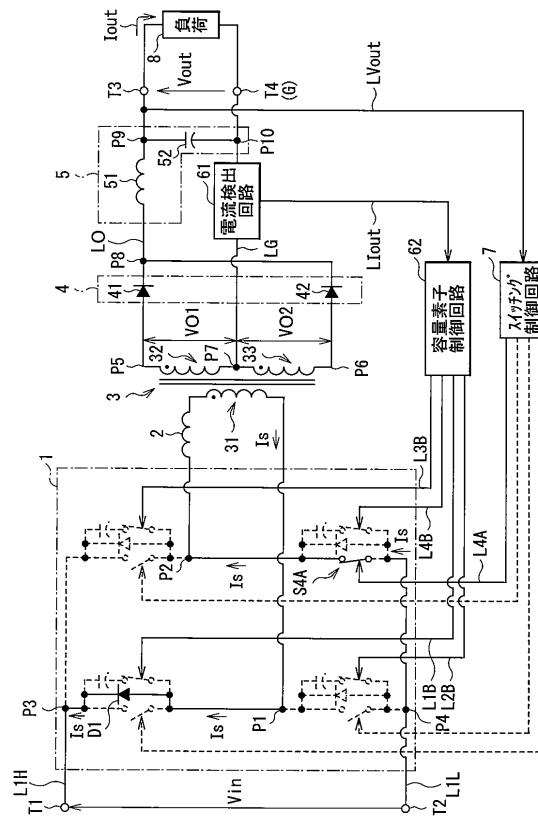

#### 【0070】

例えば、上記実施の形態では、容量素子としてのコンデンサC1～C4が、スイッチング素子S1A～S4Aの全てに並列接続されている場合について説明してきたが、この容量素子としてのコンデンサは、スイッチング素子S1A～S4Aのうちの少なくとも1つと並列接続されればよい。このように構成した場合でも、上記実施の形態の場合と同様の効果を得ることができる。30

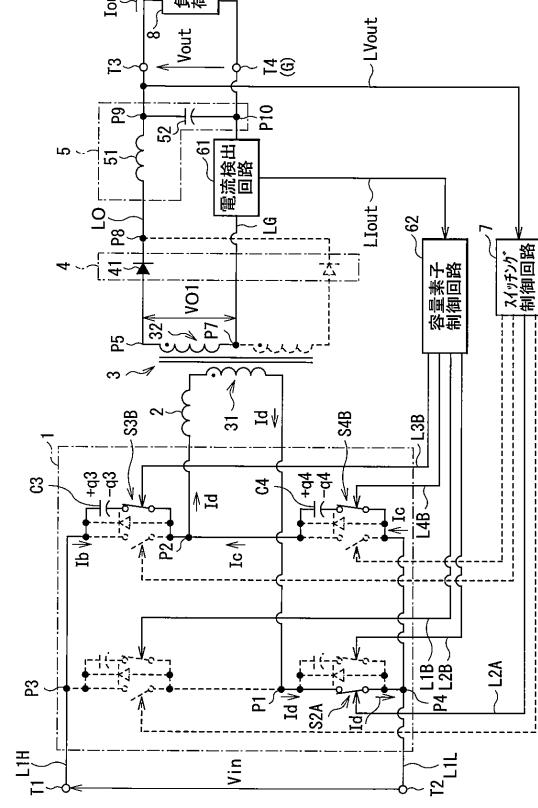

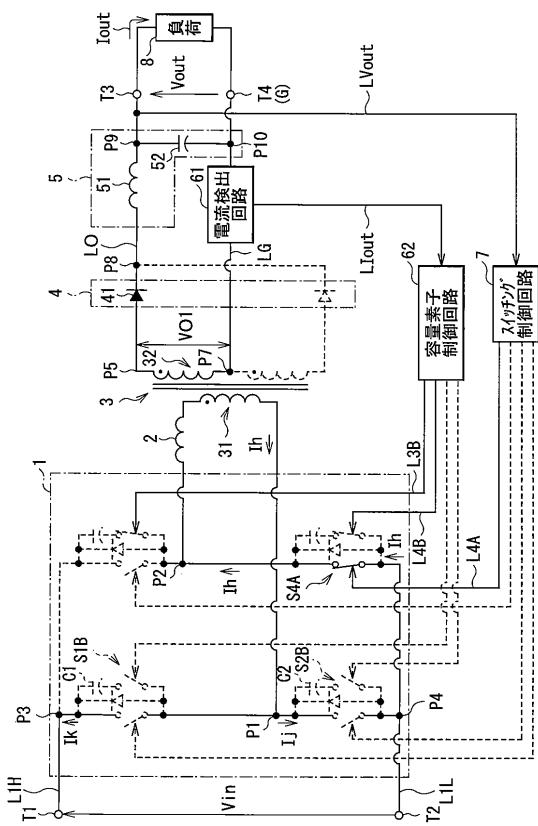

#### 【0071】

また、上記実施の形態では、軽負荷領域および中間負荷領域において、固定側スイッチング素子のコンデンサC1、C2の接続を切断するように制御する場合について説明してきたが、図20(軽負荷領域)および図21(中間負荷領域)に示したように、これに加えてシフト側スイッチング素子のコンデンサC3、C4の接続を切断するように制御してもよく、また、シフト側スイッチング素子のコンデンサC3、C4のみの接続を切断するように制御してもよい。つまり、容量素子制御回路62は、並列接続されているコンデンサC1～C4のうちの少なくとも1つのコンデンサの容量値を変化させるように制御すればよい。例えば、図22は、図20および図21の構成のスイッチング電源装置を、前述の具体例に対応させた場合における出力電流対効率特性を表すものである。ここで、図中の符号G53～G55で示した曲線はそれぞれ、固定側スイッチング素子のコンデンサC1、C2の両方を切断し、かつシフト側スイッチング素子のコンデンサC3、C4の両方を接続している場合(図19の曲線G53)、シフト側スイッチング素子のコンデンサC3のみを接続している場合、およびコンデンサC1～C4のいずれも切断している場合を表している。このように、軽負荷領域のうちでも特に出力電流Ioutが5A以下の領域において、曲線G53と比べて、曲線G54、G55の場合のほうが効率が向上しており、曲線G55の場合が特に効率が向上していることが分かる。よって、固定側スイッチング素子のコンデンサC1、C2に加えて、シフト側スイッチング素子のコンデンサC3、C4の接続を制御するように構成することで、より軽負荷領域における効率を向上させるこ4050

とが可能となる。なお、固定側スイッチング素子のコンデンサ C 1, C 2 の容量値を変化させた場合と、シフト側スイッチング素子のコンデンサ C 3, C 4 の容量値を変化させた場合とで効率を向上させる度合いが異なるのは、前述のようにそれぞれの場合における共振回路のインダクタンス値が異なるためである。つまり、シフト側スイッチング素子のコンデンサ C 3, C 4 により共振回路を構成した場合よりも、固定側スイッチング素子のコンデンサ C 1, C 2 により共振回路を構成した場合のほうがインダクタンス値が小さいので、固定側スイッチング素子のコンデンサ C 1, C 2 の容量値を変化させたほうが、より効率を向上させる効果が大きい。

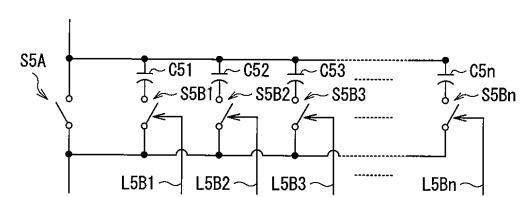

【0072】

また、上記実施の形態では、容量素子としてのコンデンサ C 1 ~ C 4 が、スイッチング素子 S 1 A ~ S 4 A それぞれに対して 1 つずつ並列接続されている場合について説明してきたが、図 23 に示したように、例えば、スイッチング素子 S 5 A に並列接続される容量素子としてのコンデンサを、互いに並列接続された複数のコンデンサ C 5 1 ~ C 5 n から構成するようにしてもよい。ここで、コンデンサ切断素子 S 5 B 1 ~ S 5 B n およびコンデンサ切断信号 L 5 B 1 ~ L 5 B n はそれぞれ、これら複数のコンデンサ C 5 1 ~ C 5 n に対応させたものである。このように容量素子としてのコンデンサを構成し、これら複数のコンデンサ C 5 1 ~ C 5 n の接続を選択的にオン・オフ制御するようにした場合、上記実施の形態における効果に加え、容量素子としてのコンデンサの容量値を多段階に変化させることで、より確実に効率を向上させることが可能となる。

【0073】

さらに、上記実施の形態では、スイッチング電源装置の回路構成を具体的に挙げて説明したが、回路構成はこれに限定されるものではなく、例えば、トランス 3 をセンタタップ型以外の他の回路構成としてもよく、また例えば、整流回路 4 をカソードコモン接続以外の他の回路構成としてもよい。

【図面の簡単な説明】

【0074】

【図 1】本発明の一実施の形態に係るスイッチング電源装置の構成を表す回路図である。

【図 2】図 1 のスイッチング電源装置の動作を説明するためのタイミング図である。

【図 3】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 4】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 5】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 6】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 7】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 8】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 9】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 10】図 1 のスイッチング電源装置の動作を説明するための回路図である。

【図 11】図 1 のスイッチング電源装置の軽負荷領域における動作を説明するための回路図である。

【図 12】軽負荷領域の動作を説明するためのタイミング図である。

【図 13】図 1 のスイッチング電源装置の中間負荷領域における動作を説明するための回路図である。

【図 14】中間負荷領域の動作を説明するためのタイミング図である。

【図 15】スイッチング素子の両端間の電圧波形の一例を表す特性図である。

【図 16】スイッチング素子の両端間の電圧波形の一例を表す特性図である。

【図 17】スイッチング素子の両端間の電圧波形の一例を表す特性図である。

【図 18】スイッチング素子の両端間の電圧波形の一例を表す特性図である。

【図 19】スイッチング電源装置の出力電流対効率特性の一例を表す特性図である。

【図 20】本発明の変形例に係るスイッチング電源装置の構成を表す回路図である。

【図 21】本発明の変形例に係るスイッチング電源装置の構成を表す回路図である。

【図 22】本発明の変形例に係るスイッチング電源装置の出力電流対効率特性の一例を表す特性図である。

10

20

30

40

50

す特性図である。

【図23】本発明の変形例に係るスイッチング電源装置の構成の一部を表す回路図である。

【符号の説明】

【0075】

1 … スイッチング回路、2 … インダクタ、3 … トランス、3 1 … 1次側巻線、3 2, 3 3 … 2次側巻線、4 … 整流回路、5 … 平滑回路、6 1 … 電流検出回路、6 2 … 容量素子制御回路、7 … スイッチング駆動回路、8 … 負荷、S 1 A ~ S 4 A … スイッチング素子、S 1 B ~ S 4 B … コンデンサ切断素子、C 1 ~ C 4 … コンデンサ、L 1 A ~ L 4 A … スイッチング駆動信号、L 1 B ~ L 4 B … コンデンサ切断信号、L 1 H … 1次側高圧ライン、L 1 L … 1次側低圧ライン、L O … 出力ライン、L G … 接地ライン、P 1 ~ P 10 … 接続点、T 1, T 2 … 入力端子、T 3, T 4 … 出力端子、I out … 出力電流、V in … 直流入力電圧、V out … 直流出力電圧。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【図12】

### 【 図 1 3 】

【図14】

【図15】

【図16】

【図17】

【図18】

【図 19】

【図 20】

【図 21】

【図 22】

【図 23】

---

フロントページの続き

(56)参考文献 国際公開第01/071896 (WO, A1)

特開平04-125062 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/28

H02M 3/335