(19) Europäisches Patentamt

European Patent Office

Office européen des brevets

(11) Veröffentlichungsnummer: **0 353 438 B1**

(12)

## EUROPÄISCHE PATENTSCHRIFT

(45) Veröffentlichungstag der Patentschrift: **16.12.92** (51) Int. Cl.<sup>5</sup>: **G08B 27/00**

(21) Anmeldenummer: **89111144.5**

(22) Anmeldetag: **20.06.89**

(54) Einrichtung zur drahtlosen Ferneinschaltung von unterschiedlichen Sirenenprogrammen.

(30) Priorität: **14.07.88 DE 3823824**

(43) Veröffentlichungstag der Anmeldung:

**07.02.90 Patentblatt 90/06**

(45) Bekanntmachung des Hinweises auf die

Patenterteilung:

**16.12.92 Patentblatt 92/51**

(84) Benannte Vertragsstaaten:

**AT CH DE ES FR GB IT LI LU NL SE**

(56) Entgegenhaltungen:

**GB-A- 2 098 833**

**US-A- 4 392 248**

**US-A- 4 476 488**

**IEEE TRANSACTIONS ON BROADCASTING,**

Band BC-26, Nr. 2, Juni 1980, Seiten 25-37,

New York, N.Y., USA

(73) Patentinhaber: **Blaupunkt-Werke GmbH**

**Robert-Bosch-Strasse 200**

**W-3200 Hildesheim(DE)**

(72) Erfinder: **Luber, Günter**

**Schlesierstrasse 22**

**W-3200 Hildesheim(DE)**

Erfinder: **Heuer, Wolfgang**

**Hinterm Kirchdorf 4**

**W-3200 Hildesheim(DE)**

Erfinder: **Maly, Hans Otto**

**Martha-Scale-Weg 7**

**W-3220 Alfeld(DE)**

Erfinder: **Mätzold, Uwe**

**Neue Reihe 8**

**W-3320 Salzgitter 61(DE)**

Erfinder: **Messerschmidt, Rudolf**

**Gartenstrasse 2**

**W-3326 Sibbesse(DE)**

(74) Vertreter: **Eilers, Norbert, Dipl.-Phys.**

**Blaupunkt-Werke GmbH Robert-**

**Bosch-Strasse 200**

**W-3200 Hildesheim(DE)**

**EP 0 353 438 B1**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingeleitet, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99(1) Europäisches Patentübereinkommen).

## Beschreibung

Die Erfindung betrifft das Gebiet der Sirenensteuerung.

Sirenen werden je nach der Art der Gefahr, auf welche die Bevölkerung hingewiesen werden muß, in unterschiedlichen Sequenzen ein- und ausgeschaltet. Im Zuge der Modernisierung der Sirenenanlagen stellt sich die Aufgabe der drahtlosen Fernsteuerung der Sirenen.

Diese Aufgabe läßt sich mit der im Anspruch 1 gekennzeichneten Einrichtung lösen.

Mit den weiteren Ansprüchen sind Weiterbildungen der Erfindung gekennzeichnet.

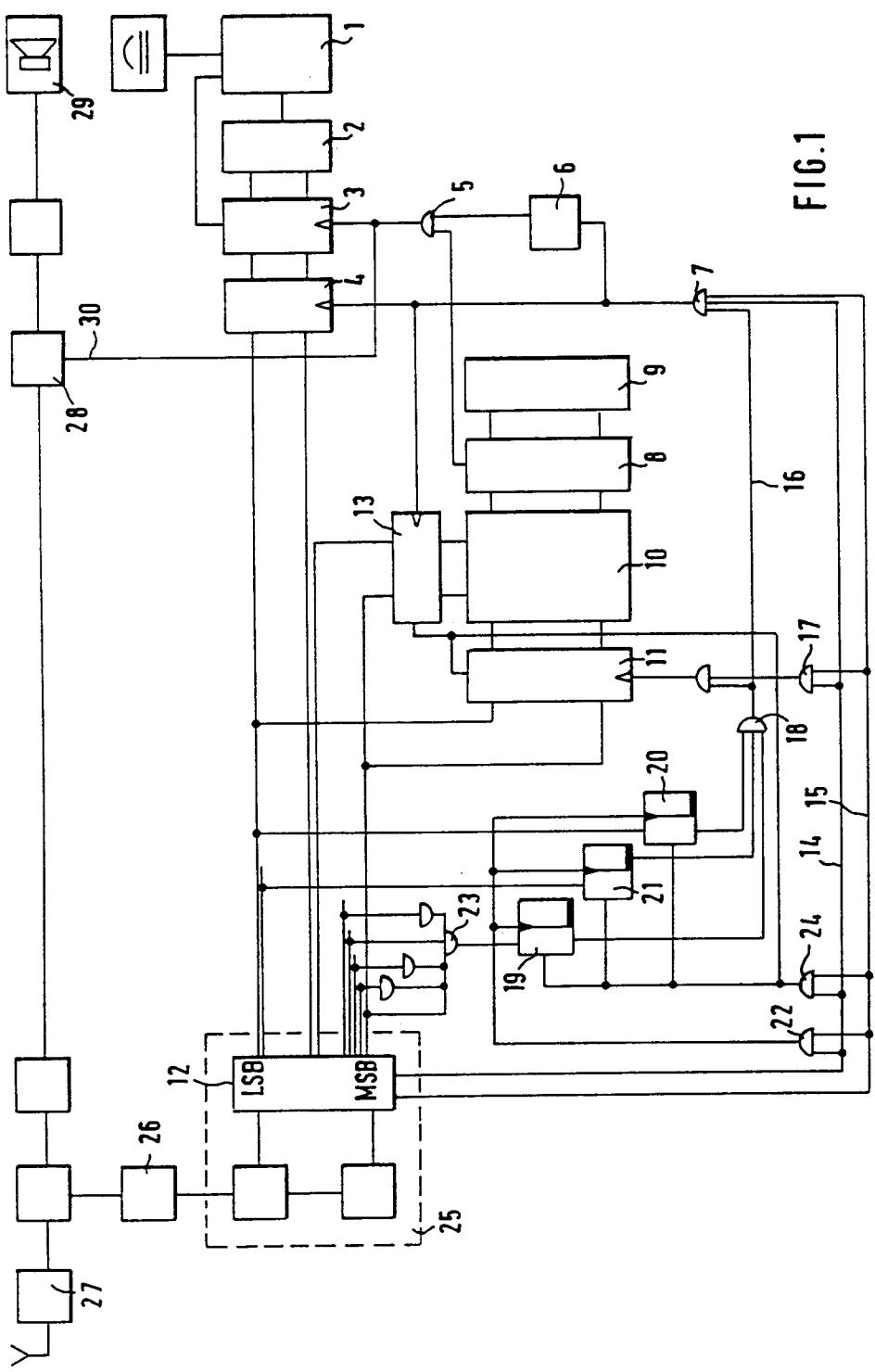

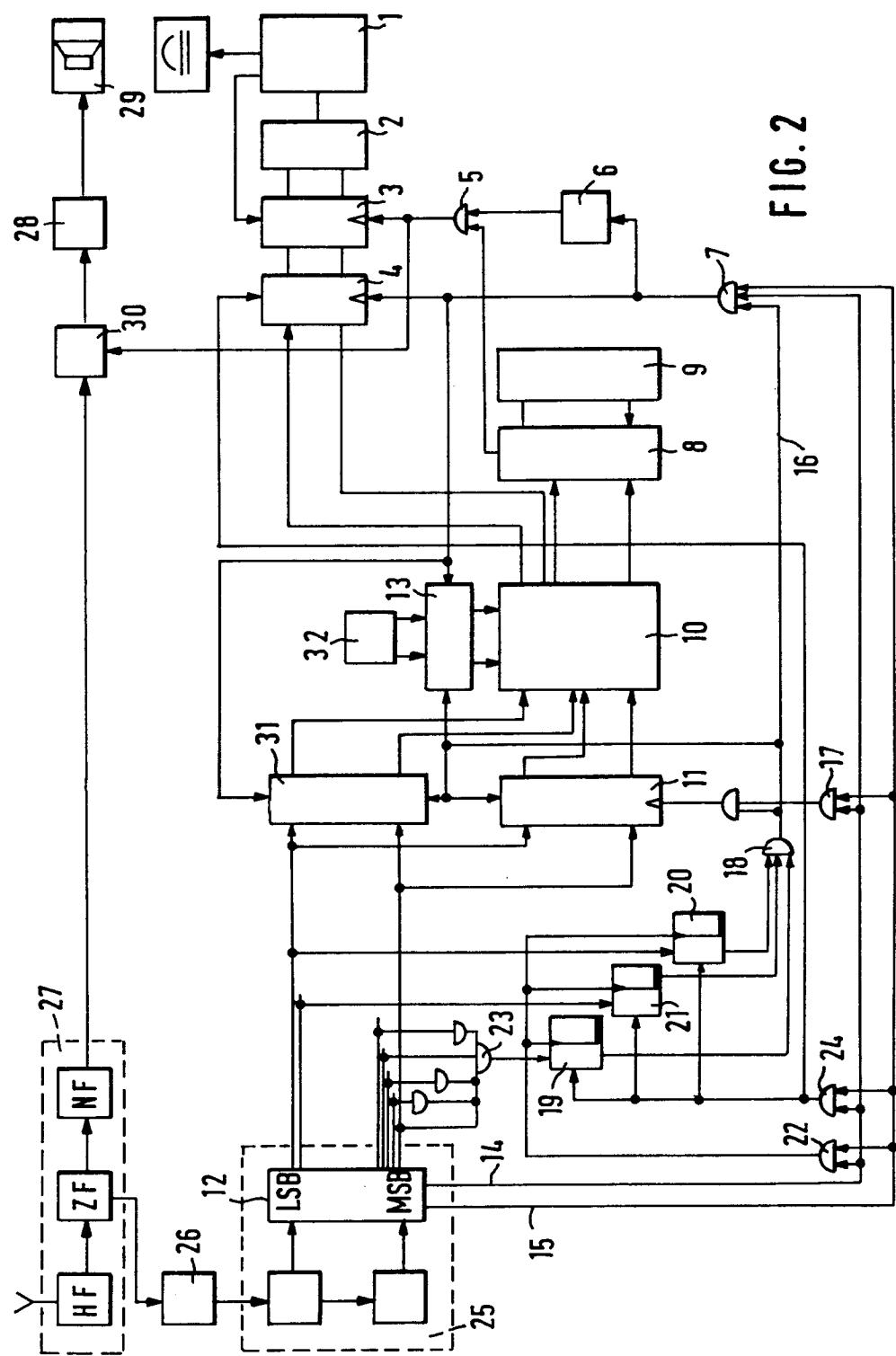

Anhand der Blockschaltbilder werden zwei Ausführungsbeispiele der Erfindung erläutert.

In beiden Ausführungsbeispielen erfolgt die drahtlose Fernsteuerung der Sirenen über ein Signal, das als Amplitudenmodulation eines 57-kHz-Hilfsträgers in einem UKW-Rundfunksendersignal übertragen wird und mit jedem Rundfunktuner empfangbar ist.

Mit einem Rundfunktuner 27 wird der Fernsteuersender eingestellt. Für die Wiedergabe der Hörrundfunksendung, die das Einschaltsignal für die Sirenen im Notfall begleitet, ist an den Rundfunktuner ein Wiedergabeverstärker 28 und an diesen ein Lautsprecher 29 angeschlossen.

Für die Fernsteuerung der Sirene ist ein Ausgang der ZF-Stufe des Rundfunktunlers 27 mit einem 57-kHz-Filter (26) verbunden, an dessen Ausgang zur Demodulation des Steuersignals von der Hilfsträgeramplitude ein Radiodatensignaldecoder 25 angeschlossen ist, der einen Amplitudendemodulator, einen Bittaktregenerator und einen Blockdecoder 12 umfaßt. Der Amplitudendemodulator liefert den Bitstrom für den Blockdecoder 12. Dieser Aufbau des Radiodatensignaldecoders 25 ist allgemein bekannt.

Der Blockdecoder 12 verfügt über einen 16 Bit breiten Signalausgang. Ferner ist an entsprechenden weiteren Ausgängen des Blockdecoders 12 ein Blocktaktbus 14 und ein Blocknummernbus 15 angeschlossen. Diese beiden Busleitungen steuern vier Takte 24, 22, 17, 7, von denen das dem ersten Blocktakt zugeordnete Takttor 24 den Resetimpuls für alle Speicher und Flipflops in der Einrichtung liefert, während ein weiteres, dem zweiten Blocktakt zugeordnetes Takttor 22 die Übernahme von Signalen in drei Flipflops 19, 20, 21 steuert und die beiden übrigen den dritten und dem vierten Blocktakt zugeordneten Takte 17 und 7 die Übernahme von Signalen in die und aus den Speichern der Einrichtung bewirken.

Das Stellsignal für den ersten Flipflop 20 liefert der Lowest Significant Bit (LSB)-Ausgang im 16-Bit-breiten Signalausgang des Blockdecoders 12, das Stellsignal für das zweite Flipflop 21 der Aus-

gang des Blockdecoders, der dem LSB-Ausgang benachbart ist, und das Stellsignal für das dritte Flipflop 19 eine Umschaltung, die eingesamtig an den Most Significant Bit (MSB)-Ausgang und dessen vier benachbarte Bitausgänge des Blockdecoders 12 angeschlossen ist.

Die vom Reset-Impuls direkt steuerbaren Ausgänge der beiden Flipflops 19, 20 und der vom Reset-Impuls indirekt steuerbare Ausgang des dritten Flipflops 21 sind in einem Undtor 18 zusammengeführt, welches über dem Freigabebus 16 die bereits erwähnte Übernahme von Signalen in die Zwischenspeicher der Einrichtung vorbereitet.

Im ersten Ausführungsbeispiel, das in dem ersten Blockschaltbild Figur 1 dargestellt ist, sind die 16 Signalausgänge des Blockdecoders 12 mit den Signaleingängen eines 16-Bit-breiten Zwischenspeichers 11 für die verschlüsselte Sirenenadresse verbunden. Die Signalübernahme wird über das Tor 17 ausgelöst.

Parallel hierzu ist die eine Hälfte der Signalausgänge des Blockdecoders, die den MSB-Ausgang mit umfaßt, mit den Signaleingängen eines 8-Bit-breiten Speichers 13 für das Schlüsselwort verbunden. Die andere Hälfte der Signalausgänge des Blockdecoders 12, die den LSB-Ausgang mit umfaßt, ist mit einem 8-Bit-breiten Zwischenspeicher 4 für das auszulösende Sirenenprogramm verbunden. Die Signalübernahme in diesen Zwischenspeicher 4 wird vom Takttor 7 gesteuert.

Die 16 Ausgänge des Zwischenspeichers 11 und die 8 Ausgänge des Speichers 13 sind an entsprechend viele Signaleingänge einer Adressentschlüsslerschaltung 10 angeschlossen, deren 16-Bit-breiter Ausgang mit den entsprechenden 16-Bit-breiten Signaleingang einer Vergleichsschaltung 8 verbunden ist. Die zweite Information für die Vergleichsschaltung liefert ein Adressenspeicher 9, in dem die vorgegebene 16-Bit-breite Adresse der angeschlossenen Sirene fest gespeichert ist.

Stimmt die Adresse am Ausgang der Entschlüsslerschaltung 10 mit der Adresse im Adressenspeicher überein, dann wird über den Koinzidenzausgang der Vergleichsschaltung ein Übernahmetor 5 im Übernahmeeingang des Endspeichers 3 für den über die Verzögerungsschaltung 6 geleiteten Blocktaktimpuls aus dem Takttor 7 vorbereitet.

Die Signaleingänge dieses 8-Bit-breiten Endspeichers 3 übernehmen die Information über das auszulösende Sirenenprogramm aus dem Zwischenspeicher 4, wenn die Adresse der angeschlossenen Sirenenprogrammeinheit 1 im empfangenen Signal in der Vergleichsschaltung erkannt ist. Der im Endspeicher 3 abgelegte Befehl bestimmt nun die Sequenz des Ein- und Ausschaltens der Sirene. Am Ende jedes Sirenenprogramms wird ein Reset-Impuls von der Programmeinheit 1 auf den Reset-Eingang des Endspeichers

3 zurückgeführt.

Wenn die beschriebene Einrichtung an eine vorhandene Sirene angeschlossen werden soll, ist zwischen dem Endspeicher 3 und der Programmeinheit 1 noch ein Digitalwandler 2 einzufügen, der das empfangene 8-Bit-breite Digitalsignal in ein zugeordnetes Steuersignal der Programmeinheit 1 umsetzt.

Aufgrund der Festlegungen für die Übertragung von Radiodatensignalen enthält der erste Datenblock jeder Probe das Kennzeichen des Senders. In der beschriebenen Einrichtung ist die Kenntnisnahme des Senderkennzeichens jedoch nicht erforderlich, da die Sirenensteuerung in der Regel auf den vorgegebenen Warnsender im UKW-Bereich fest abgestimmt ist. Daher löst der dem ersten Block des Radiodatensignals für die Sirenensteuerung zugeordnete Taktimpuls über das Takttor 24 den Reset der Flipflops 19, 20 und 21 sowie alle Zwischenspeicher aus.

Mit dem dem zweiten Block zugeordneten Taktimpuls werden die Flipflops 19, 20, 21 über das Takttor 22 gesetzt, wenn der Blockdecoder 12 an den Ausgängen, mit denen Flipflops verbunden sind, Signale bereithält.

Mit dem dem dritten Block zugeordneten Taktimpuls werden die an den Blockdecoderausgängen anstehenden Signale dieses dritten Blocks über das Takttor 17 in den Zwischenspeicher 11 übernommen, falls im vorausgehenden Takt der Flipflop 21 nicht gesetzt worden ist.

Über das Takttor 7 werden mit dem dem vierten Block zugeordneten Taktimpuls die Signale an der einen Hälfte der Ausgänge des Blockdecoders 12, die den MSB-Ausgang mit umfassen, als Schlüsselwort in den Zwischenspeicher 13 übernommen und die Signale an den anderen Ausgängen des Blockdecoders als das auszulösende Sirenenprogramm in den Zwischenspeicher 4.

Steht nach dem vierten Blocktakt die richtige Adresse am Ausgang der Adressenentschlüsslerschaltung 10, dann wird mit dem über die Verzögerungsleitung 6 gelaufenen vierten Blocktakt der als Sirenenprogrammbefehl ausgewiesene Inhalt des Zwischenspeichers 4 in den Endspeicher 3 übernommen und damit die Sirenensequenz ausgelöst.

Mit dem ersten Block der nächstfolgenden Gruppe werden dann die Zwischenspeicher und Flipflops wieder zurückgesetzt. Der Endspeicher 3 erhält dagegen einen Rücksetzimpuls erst, wenn die Programmeinheit 1 das Ende der ausgelösten Sirenenwahlsequenz anzeigt.

Erfolgt die Aussendung eines Einschaltbefehls für die Sirenen mit einem normalen Hörrundfunkprogrammsender, so kann die Wiedergabe des normalen Hörfunkprogramms unerwünscht sein. Für diesen Fall ist vor dem NF-Wiedergabeverstär-

ker 28 ein Schalter 30 für die Lautschaltung vorgesehen, dessen Steuereingang mit dem Ausgang des Übernahmetors 5 verbunden ist.

In dem in Figur 2 dargestellten zweiten Ausführungsbeispiel sind die 16 Signalausgänge des Blockdecoders 12 mit zwei je 16-Bit-breiten Eingänge aufweisenden Zwischenspeichern 11 und 31 verbunden. Während der Zwischenspeicher 11 wie im ersten Ausführungsbeispiel die im dritten Blocktakt an den Ausgängen des Blockdecoders anliegenden Informationen aufnimmt, speichert der Zwischenspeicher 31 die im vierten Blocktakt an den Ausgängen des Blockdecoders 12 anliegenden Daten. Dazu ist der Übernahmeeingang des Zwischenspeichers 31 mit dem Ausgang des Takttores 7 verbunden. Der Speicher 13 ist seinerseits an einen Zeitgeber 32 angeschlossen. Dieser Zeitgeber 32, z. B. eine Funkuhr, ruft in dem Speicher 13 für jeweils eine Zeiteinheit ein zugeordnetes, dort abgelegtes Schlüsselwort auf. Mit diesem Schlüsselwort ist sowohl die Sirenenadresse als auch das auszulösende Sirenenprogramm aus den in den Zwischenspeichern 11 und 31 enthaltenen 32-Bit-breiten Datenwort zu entschlüsseln. In dem Vergleicher 8 wird das Adressenwort mit der im Adressenspeicher 9 enthaltenen Adresse der Sirene verglichen, während der Befehl für das auszulösende Sirenenprogramm in den Zwischenspeicher 4 übernommen wird, der dazu im zweiten Ausführungsbeispiel eingangsseitig an sechs Ausgängen der Entschlüsslerschaltung 10 angeschlossen ist.

Die Weiterverarbeitung des im Zwischenspeicher 4 für das Sirenenprogramm abgelegten Befehls und des Ausgangssignals des Vergleichers 8 erfolgt auch im zweiten Ausführungsbeispiel entsprechend dem ersten Ausführungsbeispiel.

## Patentansprüche

1. Einrichtung zur drahtlosen Ferneinschaltung von Sirenenprogrammen, dadurch gekennzeichnet,

- daß eine die Sirenenprogramme enthaltende Programmeinheit (1) an einen Endspeicher (3) angeschlossen ist,

- daß dem Endspeicher (3) ein Zwischenspeicher (4) für das auszulösende Sirenenprogramm und ein Übernahmetor (5) vorgeschaltet sind,

- daß der erste Steuereingang des Übernahmetores (5) über ein Zeitglied (6) mit einem dem vierten Blocktakt zugeordneten Takttor (7) und der zweite Steuereingang mit dem Koinzidenzausgang einer Vergleichsschaltung (8) verbunden sind,

- daß die Vergleichsschaltung eingangsseitig an einen Adressenspeicher (9) und an einen Ausgang einer Adressenent-

- schlüsslerschaltung (10) angeschlossen ist,

- daß der erste Signaleingang der Adressenentschlüsslerschaltung (10) über einen Zwischenspeicher (11, 31) für die Sirenenadresse mit dem Ausgang eines Blockdecoders (12) und der zweite Signaleingang der Adressenentschlüsslerschaltung (10) mit einem Speicher (13) für das Schlüsselwort verbunden ist,

- daß der Übernahmeeingang des Zwischenspeichers (4) für das Sirenenprogramm und der Übernahmeeingang des Speichers (13) für das Schlüsselwort an den Ausgang des dem vierten Blocktakt zugeordneten Takttores (7) angeschlossen sind,

- daß ein Übernahmeeingang des Zwischenspeichers (11) für die Sirenenadresse an ein dem dritten Blocktakt zugeordnetes Takttor (17) angeschlossen ist,

- daß die Eingänge aller Taktore (7 und 17) mit dem Blocktaktbus (14) und dem Blocknummernbus (15) und die dem dritten und vierten Blocktakt zugeordneten zusätzlich mit einem Freigabebus (16) verbunden sind,

- daß der Freigabebus (16) selbst an ein Undtor (18) angeschlossen ist, dessen Signaleingänge mit den Ausgängen von drei Flipflops (19, 20, 21) verbunden sind, von denen der erste Flipflop (19) mit dem MSB-Ausgang und vier benachbarten Ausgängen des Blockdecoders, der zweite Flipflop (20) mit dem LSB-Ausgang des Blockdecoders (12) und der dritte Flipflop (21) mit dem diesem Ausgang direkt benachbarten Ausgang des Blockdecoders verbunden sind,

- daß die Übernahmeeingänge aller drei Flipflops an ein dem zweiten Blocktakt zugeordnetes Takttor (22) angeschlossen sind,

- daß der Resetbus (23) für alle Speicher und alle Flipflops an ein dem ersten Blocktakt zugeordnetes Takttor (24) angeschlossen ist,

- und daß der Blockdecoder (12) Teil eines RDS-Radiodatensignaldecoders (25) ist, der seinerseits mit dem 57-kHz-Hilfsträgerausgang eines UKW-Rundfunkempfängers (27) verbunden ist.

2. Einrichtung nach Anspruch 1, dadurch gekennzeichnet,

daß der Zwischenspeicher (4) für das auszulösende Sirenenprogramm eingangsseitig mit ei-

- nem das MS-Bit umfassenden Teil der Ausgänge des Blockdecoders (12) und der Speicher für das Schlüsselwort (13) eingangsseitig mit dem anderen Teil der Ausgänge des Blockdecoders (12) verbunden ist,

- und daß die Übernahmeeingänge beider Zwischenspeicher an das dem vierten Blocktakt zugeordnete Takttor (7) angeschlossen sind.

3. Einrichtung nach Anspruch 2, dadurch gekennzeichnet,

- daß einer die Sirenenprogramme enthaltenden Programmeinheit (1) ein Digitalwandler (2) vorgeschaltet ist, dessen Signaleingang mit einem 8 Bit breiten Ausgang eines Endspeichers (3) verbunden ist,

- daß dem Endspeicher (3) ein 8 Bit breiter erster Zwischenspeicher (4) und ein Übernahmetor (5) vorgeschaltet sind, dessen erster Steuereingang über ein Zeitglied (6) mit einem ersten Taktor (7) und dessen zweiter Steuereingang mit dem Koinzidenzausgang einer 16 Bit breiten Vergleichsschaltung verbunden sind, die ihrerseits eingangsseitig an einen 16 Bit breiten Adressenspeicher (9) und an einen 16 Bit breiten Ausgang einer Adressenentschlüsslerschaltung (10) angeschlossen ist,

- daß der erste 16 Bit breite Signaleingang der Adressenentschlüsslerschaltung (10) über einen dritten Zwischenspeicher (11) mit dem 16 Bit breiten Ausgang eines Blockdecoders (12) und der zweite 8 Bit breite Signaleingang der Adressenentschlüsslerschaltung (10) mit einem zweiten Zwischenspeicher (13) mit dem 8 Bit breiten, das MS-Bit umfassenden einen Hälfte der Ausgänge der Blockdecoder (12) verbunden ist, während die 8 Bit breite das LS-Bit umfassende Hälfte der Ausgänge des Blockdecoders (12) mit dem 8 Bit breiten Signaleingang des ersten Zwischenspeichers (4) verbunden ist.

4. Einrichtung nach Anspruch 1, dadurch gekennzeichnet,

daß der Speicher für das Schlüsselwort (13) eingangsseitig mit einem Zeitgeber (32) verbunden ist und der Zwischenspeicher für das auszulösende Sirenenprogramm (4) eingangsseitig an einen Teil der Ausgänge der Adressenentschlüsslerschaltung (10) angeschlossen ist.

5. Einrichtung nach einem der vorhergehenden

Ansprüche,

dadurch gekennzeichnet,

daß der Schalteingang der Lautschaltung eines

NF-Wiedergabeverstärkers (28), der einem die

NF-Signale abgebenden Lautsprecher (29) vor-

geschaltet ist, mit dem Ausgang des ersten

Übernahmetores (5) verbunden ist.

5

**Claims**

1. Device for the wire-less remote switching-on of siren programs, characterised in that

- a program unit (1) containing the siren programs is connected to a final memory (3),

- a buffer store (4) for the siren program to be initiated and a transfer gate (5) are connected upstream of the final memory (3),

- the first control input of the transfer gate (5) is connected via a timer (6) to a timing gate (7) allocated to the fourth block cycle, and the second control input is connected to the coincidence output of a comparator circuit (8),

- the comparator circuit is connected on the input side to an address memory (9) and to an output of an address decoder circuit (10),

- the first signal input of the address decoder circuit (10) is connected via a buffer store (11, 31) for the siren address to the output of a block decoder (12), and the second signal input of the address decoder circuit (10) is connected to a memory (13) for the code word,

- the transfer input of the buffer store (4) for the siren program and the transfer input of the memory (13) for the code word are connected to the output of the timing gate (7) allocated to the fourth block cycle,

- a transfer input of the buffer store (11) for the siren address is connected to a timing gate (17) allocated to the third block cycle,

- the inputs of all timing gates (7 and 17) are connected to the block clock bus (14) and to the block number bus (15), and those allocated to the third and fourth block cycle are additionally connected to an enable bus (16),

- the enable bus (16) itself is connected to an AND gate (18) whose signal inputs are connected to the outputs of three flipflops (19, 20, 21), of which the first flipflop (19) is connected to the MSB output and four adjacent outputs of the

10

15

20

25

30

35

40

45

50

55

block decoder, the second flipflop (20) is connected to the LSB output of the block decoder (12), and the third flipflop (21) is connected to the output of the block decoder which is directly adjacent to the LSB output,

- the transfer inputs of all three flipflops are connected to a timing gate (22) allocated to the second block cycle,

- the reset bus (23) for all the memories and all the flipflops is connected to a timing gate (24) allocated to the first block cycle,

- and in that the block decoder (12) is part of an RDS radio data signal decoder (25) which, for its part, is connected to the 57 kHz auxiliary carrier output of a VHF broadcast radio receiver (27).

2. Device according to Claim 1, characterised in that the buffer store (4) for the siren program to be initiated is connected on the input side to a part of the outputs of the block decoder (12) comprising the most significant bit, and the memory for the code word (13) is connected on the input side to the other part of the outputs of the block decoder (12), and in that the transfer inputs of both buffer stores are connected to the timing gate (7) allocated to the fourth block cycle.

3. Device according to Claim 2, characterised in that

- a program unit (1) containing the siren programs has a digital converter (2) connected upstream of it whose signal input is connected to an 8-bit-wide output of a final memory (3),

- the final memory (3) has an 8-bit-wide first buffer store (4) and a transfer gate (5) connected upstream of it, whose first control input is connected via a timer (6) to a first timing gate (7) and whose second control input is connected to the coincidence output of a 16-bit-wide comparator circuit which, for its part, is connected on the input side to a 16-bit-wide address memory (9) and to a 16-bit-wide output of an address decoder circuit (10),

- the first 16-bit-wide signal input of the address decoder circuit (10) is connected via a third buffer store (11) to the 16-bit-wide output of a block decoder (12), and the second 8-bit-wide signal input of the address decoder circuit (10) is connected to a second buffer store (13), with the 8-bit-wide one half of the outputs of the block decoder (12) comprising the most

- significant bit, while the 8-bit-wide half of the outputs of the block decoder (12) comprising the least significant bit is connected to the 8-bit-wide signal input of the first buffer store (4). 5

4. Device according to Claim 1, characterised in that the memory for the code word (13) is connected on the input side to a timer (32), and the buffer store for the siren program (4) [sic] to be initiated is connected on the input side to a part of the outputs of the address decoder circuit (10). 10

5. Device according to one of the preceding claims, characterised in that the switching input of the volume circuit of an AF reproduction amplifier (28), which is connected upstream of a loudspeaker (29) emitting the AF signals, is connected to the output of the first transfer gate (5). 15

- Revendications**

1. Dispositif de télécommande sans fil de programme de sirène, caractérisé en ce 25

- qu'une unité de programme comprenant des programmes de sirène (1) est raccordée à une mémoire finale (3),

- qu'en amont de la mémoire finale (3) est branchée une mémoire intermédiaire (4) pour le programme de sirène à déclencher ainsi qu'une porte de prise en charge (5), 30

- que la première entrée de commande de la porte de prise en charge (5) est reliée via un circuit de temporisation (6) à une porte (7) de synchronisation correspondant à la quatrième impulsion de bloc et que la deuxième entrée de commande est reliée à la sortie de coïncidence d'un circuit comparateur (8), 35

- que le circuit comparateur est branché du côté entrée à une mémoire d'adresses (9) et à une sortie d'un circuit (10) de décodage d'adresse, 40

- que la première entrée de signal du circuit (10) de décodage d'adresse est reliée via une mémoire intermédiaire (11, 31) pour l'adresse de sirène à la sortie d'un décodeur de blocs (12) et la deuxième entrée de signal du circuit (10) de décodage de l'adresse à une mémoire (13) pour le mot clef, 45

- que l'entrée de prise en charge de la mémoire intermédiaire (4) pour le programme de sirène et l'entrée de prise en charge de la mémoire (13) pour le mot 50

- clef sont raccordées à la sortie de la porte de synchronisation (7) correspondant à la quatrième impulsion de bloc, qu'une entrée de prise en charge de la mémoire intermédiaire (11) pour l'adresse de sirène est branchée à une porte de synchronisation (17) correspondant à la troisième impulsion de bloc,

- que les entrées de toutes les portes de synchronisation (7 et 17) sont raccordées au bus cadencé de bloc (14) et au bus de mémorisation de bloc (15) et celles qui correspondent à la troisième et quatrième séquence de bloc sont raccordées en plus à un bus de déblocage (16),

- que le bus de déblocage (16) lui-même est raccordé à une porte ET (18), dont les entrées de signaux sont reliées aux sorties de trois bascules (19, 20, 21) dont la première bascule (19) est reliée à la sortie MSB et à quatre sorties voisines du décodeur de blocs, la deuxième bascule (20) est reliée à la sortie LSB du décodeur de blocs (12) et la troisième bascule (21) est reliée à la sortie du décodeur de blocs directement voisine de cette sortie,

- que les entrées de prise en charge des trois bascules sont raccordées à une porte de synchronisation (22) correspondant à la deuxième séquence de bloc,

- que le bus de reset (23) de toutes les mémoires et de toutes les bascules est raccordé à une porte de synchronisation (24) correspondant à la première impulsion de bloc,

- et que le décodeur de bloc (12) fait partie d'un décodeur de signaux de données radio RDS, qui de son côté est branché à une sortie de porteuse 57 kHz d'un récepteur radio (27) d'ondes ultra courtes.

2. Dispositif selon la revendication 1, caractérisé en ce que la mémoire intermédiaire (4) du programme de sirène à déclencher est reliée du côté entrée à une partie comprenant le bit MS des sorties du décodeur de blocs (12) et la mémoire de mot clef (13) est reliée du côté entrée à l'autre partie des sorties du décodeur de blocs (12), et que les entrées de prise en charge des deux mémoires intermédiaires sont branchées à la porte de synchronisation (7) correspondant à la quatrième impulsion de bloc. 55

3. Dispositif selon la revendication 2, caractérisé en ce

- qu'un convertisseur numérique (2) est branché en amont d'une unité de programme (1) contenant les programmes de sirène, dont l'entrée de signal est raccordée à une sortie 8 bit d'une mémoire finale (3), 5

- qu'une première mémoire intermédiaire (4) de 8 bit et une porte de prise en charge (5) sont raccordées en amont de la mémoire finale (3), porte dont la première entrée de commande est raccordée par l'intermédiaire d'un circuit de temporisation (6) à une première porte de synchronisation (7) et dont la deuxième entrée de commande est raccordée à la sortie de coïncidence d'un circuit comparateur de 16 bit, qui de son côté est raccordé à une mémoire d'adresse (9) de 16 bit et à une sortie 16 bit d'un circuit de décodage d'adresses (10), 10

- que la première entrée de signal à 16 bit du circuit de décodage d'adresse (10) est reliée via une troisième mémoire intermédiaire (11) à la sortie à 16 bit d'un décodeur de blocs (12) et la deuxième entrée de signal à 8 bit au circuit de décodage d'adresse (10) à une deuxième mémoire (13) intermédiaire à la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le MS - Bit, tandis que la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le LS - Bit est raccordée à l'entrée de signal 8 bit de la première mémoire intermédiaire (4). 15

- que la première entrée de signal à 16 bit du circuit de décodage d'adresse (10) est reliée via une troisième mémoire intermédiaire (11) à la sortie à 16 bit d'un décodeur de blocs (12) et la deuxième entrée de signal à 8 bit au circuit de décodage d'adresse (10) à une deuxième mémoire (13) intermédiaire à la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le MS - Bit, tandis que la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le LS - Bit est raccordée à l'entrée de signal 8 bit de la première mémoire intermédiaire (4). 20

- que la première entrée de signal à 16 bit du circuit de décodage d'adresse (10) est reliée via une troisième mémoire intermédiaire (11) à la sortie à 16 bit d'un décodeur de blocs (12) et la deuxième entrée de signal à 8 bit au circuit de décodage d'adresse (10) à une deuxième mémoire (13) intermédiaire à la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le MS - Bit, tandis que la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le LS - Bit est raccordée à l'entrée de signal 8 bit de la première mémoire intermédiaire (4). 25

- que la première entrée de signal à 16 bit du circuit de décodage d'adresse (10) est reliée via une troisième mémoire intermédiaire (11) à la sortie à 16 bit d'un décodeur de blocs (12) et la deuxième entrée de signal à 8 bit au circuit de décodage d'adresse (10) à une deuxième mémoire (13) intermédiaire à la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le MS - Bit, tandis que la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le LS - Bit est raccordée à l'entrée de signal 8 bit de la première mémoire intermédiaire (4). 30

- que la première entrée de signal à 16 bit du circuit de décodage d'adresse (10) est reliée via une troisième mémoire intermédiaire (11) à la sortie à 16 bit d'un décodeur de blocs (12) et la deuxième entrée de signal à 8 bit au circuit de décodage d'adresse (10) à une deuxième mémoire (13) intermédiaire à la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le MS - Bit, tandis que la moitié à 8 bit des sorties de décodeur de blocs (12) comprenant le LS - Bit est raccordée à l'entrée de signal 8 bit de la première mémoire intermédiaire (4). 35

4. Dispositif selon la revendication 1, caractérisé en ce que la mémoire pour le mot clé (13) est reliée du côté entrée à une mémoire (32) et que la mémoire intermédiaire du programme de sirène à déclencher (4) est raccordée du côté entrée à une partie des sorties du circuit (10) de décodage des adresses. 40

5. Dispositif selon l'une des revendications précédentes, caractérisé en ce que l'entrée de commande du circuit haut parleur d'un amplificateur de retransmission BF (28), qui est branchée en amont du haut-parleur (25) émettant les signaux BF, est reliée à la sortie de la première porte de prise en charge (5). 45

- 50

FIG. 2