【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成17年10月27日(2005.10.27)

【公開番号】特開2003-124441(P2003-124441A)

【公開日】平成15年4月25日(2003.4.25)

【出願番号】特願2002-202557(P2002-202557)

【国際特許分類第7版】

H 01 L 27/10

G 11 C 29/00

【F I】

H 01 L 27/10 4 3 1

H 01 L 27/10 4 8 1

G 11 C 29/00 6 0 5 C

【手続補正書】

【提出日】平成17年7月7日(2005.7.7)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

固体メモリデバイスの段を形成し、

前記段内の欠陥領域を特定し、及び

前記段内の欠陥領域を回避するように、前記段のアドレス論理回路をプログラミングすることを含む、固体メモリデバイスを製造する方法。

【請求項2】

前記段が予備の線を含み、前記予備の線に接続されたアドレス論理回路が、前記特定された線を置き換えるために符号化され、未使用の予備の線が切断される、請求項1に記載の方法。

【請求項3】

前記デバイスの少なくとも1つの追加の段が形成され、各追加の段の前記アドレス論理回路が、欠陥を回避するようにプログラミングされる、請求項1に記載の方法。

【請求項4】

前記アドレス論理回路が、前記段内の欠陥領域に関連する線を特定し、前記特定された線内のリンクが開放されるまで、前記特定された線を流れる電流密度を増加させることによりプログラミングされる、請求項1に記載の方法。

【請求項5】

前記電流密度が、前記リンクに光を照射することにより増加する、請求項4に記載の方法。

【請求項6】

アドレス線を含む、固体メモリデバイスの段を形成し、

前記段内の欠陥領域に関連する前記線を特定し、及び

前記特定された線が開放されるまで、前記特定された線を流れる電流密度を増加させることを含む、固体メモリデバイスを製造する方法。

【請求項7】

前記線が、光導電性材料から作成されたリンクを含み、前記特定された線が、前記特定された線に電流を流し、かつ前記特定された線のリンクに光を照射することにより開放さ

れる、請求項 6 に記載の方法。

【請求項 8】

前記段が予備の線を含み、前記予備の線に接続されたアドレス論理回路が、前記特定された線を置き換えるために符号化され、未使用の予備の線が切断される、請求項 6 に記載の方法。

【請求項 9】

前記デバイスの少なくとも 1 つの追加の段が形成され、各追加の段の欠陥領域に関連する線が特定されて開放される、請求項 6 に記載の方法。

【請求項 10】

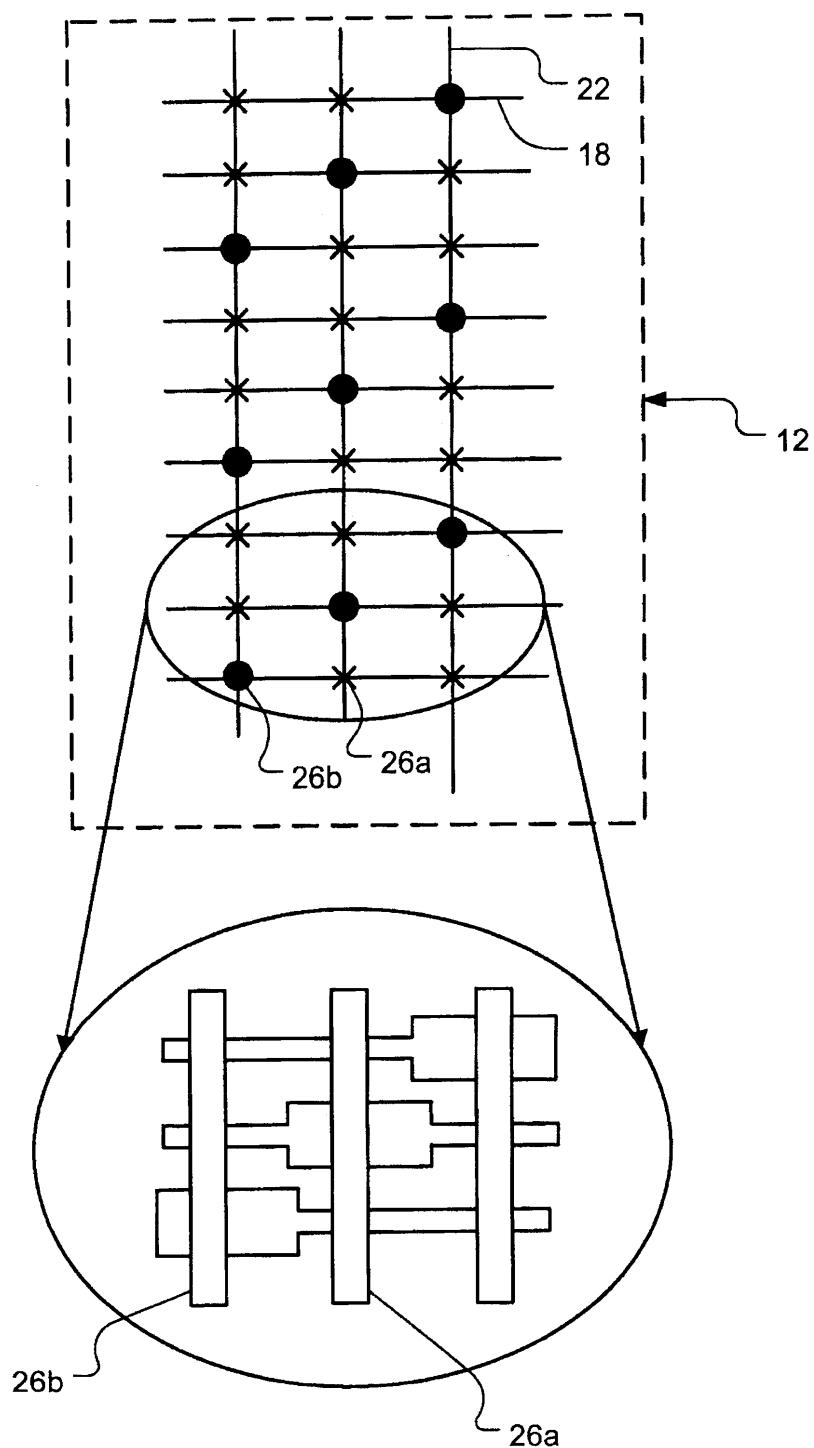

複数のメインメモリエレメントと、

複数のアドレス線および予備の線と、

前記アドレス線によって前記メインメモリエレメントに接続されたアドレスエレメントの第 1 のグループを含むアドレス論理回路と、及び

前記予備の線によって前記メインメモリに接続されたアドレスエレメントの第 2 のグループを含む予備論理回路とを含む、固体メモリデバイスの段。

【請求項 11】

前記線が、光導電性材料から作成されたリンクを含む、請求項 10 に記載の固体メモリデバイスの段。

【請求項 12】

前記リンクが、供給抵抗である、請求項 11 に記載の固体メモリデバイスの段。

【請求項 13】

前記予備論理回路が、プログラム可能なダイオードベースの論理回路である、請求項 10 に記載の固体メモリデバイスの段。

【請求項 14】

前記ダイオードベースの論理回路が、光導電性材料から作成されたプログラム可能なアドレスエレメントを含む、請求項 13 に記載の固体メモリデバイスの段。

【請求項 15】

前記段の欠陥を特定し、

前記特定された欠陥に関連するアドレス線を切断し、及び

前記切断されたアドレス線に関連するアドレスエレメントを置き換えるように、前記予備論理回路のアドレスエレメントをプログラミングすることを含む、請求項 10 のデバイスをプログラミングする方法。

【請求項 16】

未使用の予備の線のリンクに光を照射することにより、任意の未使用の予備の線を切断することをさらに含む、請求項 15 に記載の方法。

【請求項 17】

誤り訂正が許容可能なレベルにあるように、著しい数の欠陥が回避される、請求項 15 に記載の方法。

【請求項 18】

基板と、及び

前記基板上の複数の段とを含み、

各段が、複数のメインメモリエレメント、複数のアドレス線および予備の線、前記アドレス線により前記メインメモリエレメントに接続されたアドレスエレメントの第 1 のグループを含むアドレス論理回路、及び前記予備の線により前記メインメモリに接続されたアドレスエレメントの第 2 のグループを含む予備論理回路を含む、固体メモリデバイス。

【請求項 19】

前記基板に、各段の欠陥管理を実行するための回路をさらに含む、請求項 18 に記載のデバイス。

【請求項 20】

各段の欠陥を特定し、

各段の前記特定された欠陥に関連するアドレス線を切断し、及び前記切断されたアドレス線に関連するアドレスエレメントを置き換えるように、前記予備論理回路をプログラミングすることを含む、請求項18のデバイスをプログラミングする方法。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0003

【補正方法】変更

【補正の内容】

【0003】

ダイオードベース(diode-based)の固体OTPメモリが、2001年6月5日に出願された譲受人の米国特許出願第09/875,356号に開示される。従来のメモリと比較すると、ダイオードベースのメモリは、高い耐衝撃性、少ない消費電力、速いアクセス速度、適度な転送速度および良好な記憶容量を有する。ダイオードベースのメモリは、ポータブル装置の標準的なポータブルインターフェース(たとえば、PCMCIA、CF)に適合することができる。

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図5a

【補正方法】変更

【補正の内容】

【図5a】