(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 601 09 307 T2 2006.04.13

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 316 090 B1

(51) Int Cl.<sup>8</sup>: G11C 5/00 (2006.01)

(21) Deutsches Aktenzeichen: 601 09 307.0

(86) PCT-Aktenzeichen: PCT/NO01/00348

(96) Europäisches Aktenzeichen: 01 985 301.9

(87) PCT-Veröffentlichungs-Nr.: WO 02/025665

(86) PCT-Anmeldetag: 24.08.2001

(87) Veröffentlichungstag

der PCT-Anmeldung: 28.03.2002

(97) Erstveröffentlichung durch das EPA: 04.06.2003

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 09.03.2005

(47) Veröffentlichungstag im Patentblatt: 13.04.2006

(30) Unionspriorität:

20004236 24.08.2000 NO

(84) Benannte Vertragsstaaten:

AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT,

LI, LU, MC, NL, PT, SE, TR

(73) Patentinhaber:

Thin Film Electronics ASA, Oslo, NO

(72) Erfinder:

THOMPSON, Michael, Ithaca, US; WOMACK,

Richard, Albuquerque, US; GUSTAFSSON, Göran,

S-582 16 Linköping, SE; CARLSSON, Johan, S-589

29 Linköping, SE

(54) Bezeichnung: NICHTFLUECHTIGE PASSIVE SPEICHERARRAY UND SEIN LESEVERFAHREN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine nicht-flüchtige passive Matrixspeichereinrichtung, umfassend ein elektrisch polarisierbares dielektrisches Speichermaterial, welches eine Hysterese umfasst, insbesondere ein ferroelektrisches Material, wobei das Speichermaterial eingebettet in einer Schicht zwischen einem ersten Satz und einem zweiten Satz von jeweiligen parallelen Adressierungselektroden vorgesehen ist, wobei die Elektroden des ersten Satzes Wortleitungen der Speichereinrichtung bilden und in im Wesentlichen einer orthogonalen Beziehung zu den Elektroden des zweiten Satzes vorgesehen sind, wobei die Letzteren Bitleitungen der Speichereinrichtung bilden, wobei eine Speicherzelle mit einer kondensatorartigen Struktur in dem Speichermaterial an den Überkreuzungen bzw. Überschneidungen zwischen Wortleitungen und Bitleitungen definiert wird, wobei die Speicherzellen der Speichereinrichtung die Elemente einer passiven Matrix bilden, wobei jede Speicherzelle für einen Schreib/Lese-Vorgang über eine Wortleitung und eine Bitleitung selektiv adressiert werden kann, wobei ein Schreibvorgang an eine Speicherzelle stattfindet, indem ein gewünschter Polarisationszustand in der Zelle mit Hilfe einer Spannung, die an die Zelle über die jeweilige Wortleitung und die Bitleitung, die die Zelle definieren, angelegt wird, eingerichtet wird, wobei die angelegte Spannung entweder einen bestimmten Polarisationszustand in der Speicherzelle einrichtet oder in der Lage ist zwischen den Polarisationszuständen davon umzuschalten, und wobei ein Lesevorgang stattfindet, indem eine Schaltspannung  $V_s$  größer als die Koerzitivspannung  $V_c$  an die Speicherzelle angelegt wird und wenigstens ein elektrischer Parameter eines Ausgangstroms auf den Bitleitungen erfasst wird.

**[0002]** Die Erfindung betrifft weiter ein Verfahren gemäß des angehängten unabhängigen Verfahrensanspruchs.

**[0003]** Die Erfindung betrifft auch die Verwendung einer nicht-flüchtigen passiven Matrixspeichereinrichtung in einer volumetrischen Datenspeichervorrichtung.

**[0004]** Ferroelektrische integrierte Schaltungen haben revolutionäre Eigenschaften im Vergleich mit der herkömmlichen Technologie. Anwendungen umfassen nicht-flüchtige Informationsspeichereinrichtungen, insbesondere Matrixspeicher mit Vorteilen wie einer hohen Geschwindigkeit, einer im Grunde genommen unbegrenzten Haltbarkeit und einer hohen Schreibgeschwindigkeit; Eigenschaften von denen man vor kurzem nur geträumt hat.

**[0005]** Ferroelektrische Matrixspeicher können in zwei Typen aufgeteilt werden, ein Typ, der aktive Ele-

mente enthält, die mit den Speicherzellen verknüpft sind, und ein Typ ohne aktive Elemente. Diese zwei Typen werden nachstehend beschrieben.

**[0006]** Ein ferroelektrischer Matrixspeicher mit Speicherzellen in der Form von ferroelektrischen Kondensatoren ohne aktive Zugriffselemente, wie einen Zugriffstransistor, umfasst einen dünnen ferroelektrischen Film mit einem Satz von parallel leitenden Elektroden („Wortleitungen“), die auf einer Seite aufgebracht sind, und einen im Wesentlichen orthogonalen Satz von leitenden Elektroden („Bitleitungen“), die auf der anderen Seite aufgebracht sind, wobei diese Konfiguration nachstehend als ein „passiver Matrixspeicher“ bezeichnet wird. In dem passiven Matrixspeicher werden individuelle ferroelektrische Speicherzellen an den Überschneidungspunkten der gegenüberliegenden Elektroden gebildet, wobei eine Speichermatrix geschaffen wird, die Speicherzellen umfasst, auf die durch eine selektive Anregung der geeigneten Elektroden von der Kante der Matrix individuell elektrisch zugegriffen werden kann.

**[0007]** Ein anderer Ansatz zum Bereitstellen eines Matrixspeichers besteht darin jede ferroelektrische Speicherzelle durch Einbau eines aktiven Elements, typischerweise eines Zugriffstransistors in Reihe zu dem ferroelektrischen Kondensator, zu modifizieren. Der Zugriffstransistor steuert den Zugriff auf den Kondensator und blockt unerwünschte Störungssignale, zum Beispiel von benachbarten Speicherzellen, ab. Die Speicherzelle kann typischerweise einen ferroelektrischen Kondensator und einen n-Kanal Metall-Oxid-Halbleiter-Feldeffekttransistor (nachstehend generisch als „MOSFET“ abgekürzt, aber ohne einen n-Typ oder p-Typ der Einfachheit halber anzuzeigen) umfassen, dessen Gate mit einer Wortleitung verbunden ist. Ein Source-Drain-Bereich des MOSFET ist mit einer Bitleitung verbunden. Eine Elektrode des ferroelektrischen Kondensators ist mit dem Source-Drain-Bereich des MOSFET verbunden und die andere Elektrode des Kondensators ist mit einer so genannten „Ansteuerleitung“ verbunden. Dies ist das herkömmliche Konzept bis heute und es wird oft als Speicherzellen mit einem Transistor und einem Kondensator (1T-1C) bereitgestellt. Andere Konzepte sind ebenfalls altbekannt, mit zwei Transistoren oder mehr. Jedoch erhöhen all diese Konzepte die Anzahl von Transistoren im Vergleich mit dem passiven Matrixspeicher, was eine Anzahl von Nachteilen mit sich bringt, wie die Verringerung der Anzahl von Speicherzellen innerhalb eines gegebenen Gebiets, mit einer Erhöhung der Komplexität und einem hohen Stromverbrauch. Hier werden diese Typen von Einrichtungen nachstehend als „aktive“ Matrixspeicher wegen des „aktiven“ Elements, d.h. dem Transistor in jeder Speicherzelle, bezeichnet.

**[0008]** Die vorliegende Erfindung ist jedoch ausschließlich auf passive Matrixspeicher ohne aktive

Elemente, wie Dioden oder Transistoren, die lokal zu der Speicherzelle gehören, gerichtet.

**[0009]** Lese- und Schreibvorgänge in passiven Matrixspeichern können mit Hilfe einer so genannten „Parzellenwortadressierung“ ausgeführt werden, bei der nur ein Teil, typischerweise eine der Speicherzellen auf einer gegebenen Wortleitung, gelesen oder beschrieben wird. Um einen derartigen Parzellenles- oder Schreibvorgang durchzuführen werden die nicht-adressierten Zellen auf nicht-aktivierten Wortleitungen oder Bitleitungen mit einer Spannung vorgespannt, und zwar in Übereinstimmung mit einem so genannten „Pulsierungsprotokoll“ („pulsing protocol“), um eine partielle Umschaltung der nicht-adressierten Zellen zu vermeiden. Die Wahl des Pulsierungsprotokolls hängt von einer Anzahl von Faktoren ab und unterschiedliche Vorgehensweisen sind in der Literatur für Anwendungen vorgeschlagen worden, die ferroelektrische Speichermaterialien beinhalten, die eine Hysterese aufzeigen. Dies ist zum Beispiel in der gleichzeitig anhängigen norwegischen Patentanmeldung Nr. 20003508 des Patentinhabers, eingereicht am 7. Juli 2000, beschrieben. Diese Anmeldung beschreibt ein Protokoll für einen passiven Matrixspeicher. Andererseits verursacht die Vorspannung der nicht-adressierten Zellen normalerweise Störspannungen, die zu einem Verlust des Speicherinhalt füren können oder Leckströme oder andere parasitäre Ströme hervorrufen können, die hier als „Kriechströme“ bezeichnet werden und die den Strom einer adressierten Speicherzelle während eines Lesebetriebs maskieren können und dadurch den Dateninhalt während des Lesevorgangs maskieren können. In Abhängigkeit von dem Typ von Einrichtung, der in Frage steht, können unterschiedliche Kriterien definiert werden, um eine Störung der nicht-adressierten Speicherzellen zu vermeiden oder wenigstens zu verringern, wie beispielsweise Verfahren für eine Kriechstrom-Auslösung. Eine andere Vorgehensweise besteht darin die Empfindlichkeit von jeder Zelle in der Matrix auf Kleinsignal-Störungen herabzusetzen, was durch Zellen erreicht werden kann, die eine nicht-lineare Spannungs-Stromantwort aufzeigen, die z.B. eine Schwellwertfunktion, eine Gleichrichtung und/oder verschiedene Formen einer Hysterese beinhalten.

**[0010]** Um das Betriebsverhalten von sowohl aktiven als auch passiven ferroelektrischen Speichereinrichtungen zu verbessern kann die Speichermatrix intern in kleinere Blöcke unterteilt bzw. „segmentiert“ werden, nämlich in so genannte „Segmente“, um zum Beispiel Energie- bzw. Leistungsanforderungen zu verringern. Normalerweise ist diese Segmentierung für den Benutzer transparent. Ein anderer Grund für eine Segmentierung ist das Problem mit ferroelektrischen Kondensatoren, die den Nachteil einer so genannten „Ermüdung“ aufweisen, was bedeutet, dass ein ferroelektrischer Kondensator nach-

dem er oft umgeschaltet worden ist, zum Beispiel mehrere Millionen Male, eine bleibende Polarisation nicht halten kann und deshalb die Funktion stoppt. Eine Lösung für dieses bestimmte Problem können kleinere Matrixelemente sein, um ein Umschalten einer gesamten Zeile von Kondensatoren zu vermeiden. Dies ist zum Beispiel in der US-A-5 567 636 offenbart. Ein anderes Dokument, das eine segmentierte Speichermatrix beschreibt, ist Gary F. Derbenwick et al., „Non-volatile Ferroelectric Memory for Space Applications“, Celis Semiconductor Corporation, Colorado Springs. Dieses Dokument beschreibt eine segmentierte Speichermatrix, die in der Lage ist, Energie- bzw. Leistungsanforderungen in einer aktiven Matrix unter Verwendung einer Speicherzellenarchitektur (1T, 1C) mit einem Transistor und einem Kondensator zu verringern.

**[0011]** Beispiele von passiven Matrixspeichern, die ein ferroelektrisches Speichermaterial verwenden, können in der Literatur gefunden werden, die 40–50 Jahre zurückliegt. Zum Beispiel haben W. J. Merz und J. R. Anderson einen Speicher auf Basis von Bariumtitanat im Jahr 1955 beschrieben (W. J. Merz und J. R. Anderson, „Ferroelectric storage devices“, Bell. Lab. Record. 1, Seiten 335–342 (1955)), und ähnliche Arbeiten wurden auch durch andere prompt danach berichtet (siehe z.B. C. F. Pulvari „Ferroelectrics and their memory applications“, IRE Transactions CP-3, Seiten 3–11 (1956) und D. S. Campbell, „Barium titanate and its use as a memory store“, J. Brit. IRE 17 (7), Seiten 385–395 (1957)). Ein anderes Beispiel eines passiven Matrixspeichers findet man in dem IBM Technical Disclosure Bulletin, Vol. 37, Nr. 11, November 1994. Jedoch beschreibt keines von diesen Dokumenten eine Lösung für das Problem mit gestörten nicht-adressierten Zellen.

**[0012]** Ein anderer Ansatz zum Beseitigen des Problems würde darin bestehen das ferroelektrische Material zu modifizieren, um eine quadratartige Hystereseschleife zu schaffen. Jedoch ist auch dies bislang nicht ausführlich beschrieben worden.

**[0013]** Demzufolge besteht ein Bedarf für einen passiven Matrixspeicher ohne die obigen negativen Attribute, wie gestörte nicht-adressierte Zellen.

**[0014]** Im Hinblick auf die obigen Ausführungen ist es eine Aufgabe der Erfindung eine passive Matrixspeichereinrichtung bereitzustellen, die das Problem mit gestörten nicht-adressierten Speicherzellen löst. Eine andere Aufgabe der Erfindung besteht darin eine passive Matrixspeichereinrichtung bereitzustellen, die den Einfluss von kumulativen Signalen von nicht-adressierten Zellen während eines Lesevorgangs von gespeicherten Daten minimiert. Schließlich ist es auch eine Aufgabe der Erfindung ein Ausleseverfahren in einer passiven Matrixspeichereinrichtung und kompatibel der voranstehend erwähn-

ten Aufgaben bereitzustellen.

**[0015]** Die obigen Aufgaben, sowie weitere Vorteile und Merkmale, werden mit einer nicht-flüchtigen passiven Speichermatrixeinrichtung gemäß der Erfindung realisiert, die dadurch gekennzeichnet ist, dass die Wortleitungen in eine Anzahl von Segmenten aufgeteilt sind, wobei jedes Segment eine Vielzahl von angrenzenden Bitleitungen in der Matrix umfasst und durch diese definiert wird, und dass eine Einrichtung zum Verbinden jeder Bitleitung, die zu einem Segment zugewiesen ist, mit einer zugehörigen Erfassungseinrichtung versehen ist, sodass eine gleichzeitige Verbindung von sämtlichen Speicherzellen, die einer Wortleitung auf einem Segment für eine Auslesung über die entsprechenden Bitleitungen des Segments zugewiesen sind, ermöglicht wird, wobei jede Erfassungseinrichtung zum Erfassen des Ladungsflusses in der Bitleitung, die damit verbunden ist, ausgelegt ist, um einen logischen Wert zu bestimmen, der in der Speicherzelle gespeichert ist, die durch die Bitleitung definiert wird.

**[0016]** In einer ersten vorteilhaften Ausführungsform der Speichereinrichtung gemäß der Erfindung ist die Einrichtung für eine gleichzeitige Verwendung von jeder Bitleitung eines Segments mit einer zugehörigen Erfassungseinrichtung während einer Adressierung Multiplexer. In diesem Fall können die Anzahl von Multiplexern der größten Anzahl von Bitleitungen, die ein Segment definieren, entsprechen, wobei jede Bitleitung eines Segments mit einem spezifischen Multiplexer verbunden ist. Es wird dann bevorzugt, dass der Ausgang von jedem Multiplexer mit einer einzelnen Erfassungseinrichtung verbunden ist, und insbesondere kann dann die einzelne Erfassungseinrichtung ein Erfassungsverstärker bzw. ein Leseverstärker sein.

**[0017]** In einer zweiten vorteilhaften Ausführungsform der Speichereinrichtung gemäß der Erfindung ist die Einrichtung für eine gleichzeitige Verbindung von jeder Bitleitung eines Segments mit einer zugehörigen Erfassungseinrichtung während einer Adressierung eine Gattereinrichtung. In diesem Fall können sämtliche Bitleitungen eines Segments mit einer spezifischen Gattereinrichtung verbunden werden, wobei jede Gattereinrichtung eine Anzahl von Ausgängen entsprechend zu der Anzahl von Bitleitungen in dem jeweiligen Segment aufweist, und jeder Ausgang von jeder Gattereinrichtung mit einer spezifischen Busleitung eines Ausgangsdatenbusses verbunden ist, wobei die Anzahl von Busleitungen somit einer größten Anzahl von Bitleitungen in einem Segment entspricht, wobei jede Busleitung mit einer einzelnen Erfassungseinrichtung verbunden ist.

**[0018]** Vorzugsweise umfasst die Gattereinrichtung Weitergabegatter und vorzugsweise ist die Erfassungseinrichtung ein Erfassungs- bzw. Leseverstär-

ker.

**[0019]** Die obigen Aufgaben und andere Vorteile und Merkmale werden auch mit einem Ausleseverfahren für eine Speichereinrichtung gemäß der Erfindung realisiert, wobei das Verfahren gekennzeichnet ist durch Aufteilen der Wortleitungen in eine Anzahl von Segmenten, wobei jedes Segment eine Anzahl von angrenzenden Bitleitungen in der Matrix umfasst und durch diese definiert wird, Verbinden jeder Bitleitung innerhalb eines Wortleitungssegments mit einer zugehörigen Erfassungseinrichtung, Aktivieren einer Wortleitung eines Segments in Übereinstimmung mit dem Protokoll zu einer Zeit durch Einstellen des Potentials der einen Wortleitung des Segments auf eine Schaltspannung  $V_s$  während wenigstens eines Abschnitts des Lesezyklus, während sämtliche Bitleitungen des Segments auf einem Null-Potential gehalten werden, und Bestimmen des logischen Werts, der in den individuellen Speicherzellen gespeichert wird, die durch die Erfassungseinrichtung während des Lesezyklus erfasst werden.

**[0020]** In einer vorteilhaften Ausführungsform des Ausleseverfahrens gemäß der Erfindung werden sämtliche Wortleitungen und Bitleitungen, wenn keine Speicherzelle gelesen oder beschrieben wird, auf einer Ruhespannung von ungefähr 1/3 der Schaltspannung  $V_s$  gehalten, eine Wortleitung zu einer Zeit wird in Übereinstimmung mit dem Protokoll durch Einstellen des Potentials der einen Wortleitung des Segments auf die Schaltspannung  $V_s$  während wenigstens eines Abschnitts des Lesezyklus aktiviert, während sämtliche Bitleitungen des Segments auf einem Null-Potential gehalten werden, und der logische Wert, der in den individuellen Speicherzellen gespeichert ist, die durch die Erfassungseinrichtung während des Lesezyklus erfasst werden, wird bestimmt.

**[0021]** Schließlich werden die obigen Aufgaben und andere Merkmale und Vorteile in Übereinstimmung mit der Erfindung auch mit der Verwendung der erfindungsgemäßen nicht-flüchtigen passiven Speicher- einrichtung und dem erfindungsgemäßen Verfahren zum Auslesen in einer volumetrischen Datenspeicher- vorrichtung mit einer Vielzahl von gestapelten Schichten erreicht, wobei jede Schicht eine der nicht-flüchtigen passiven Matrixspeichereinrichtungen umfasst.

**[0022]** Die Erfindung soll nun ausführlicher auf Grundlage der Diskussionen von ihrem allgemeinen Hintergrund und von nachstehend angegebenen bevorzugten Ausführungsformen, wenn diese in Verbindung mit den angehängten Zeichnungsfiguren gelesen werden, beschrieben werden. In den Zeichnungen zeigen:

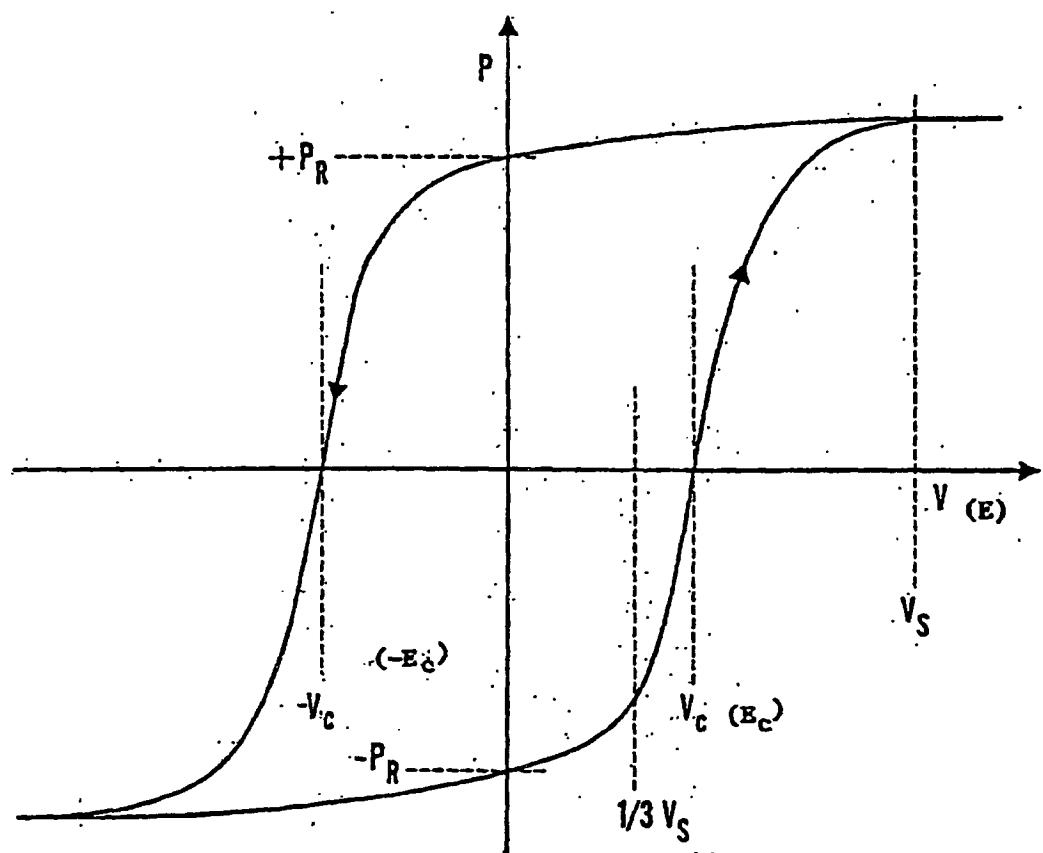

**[0023]** [Fig. 1](#) eine Prinzipzeichnung einer Hystere-

sekurve für ein ferroelektrisches Speichermaterial;

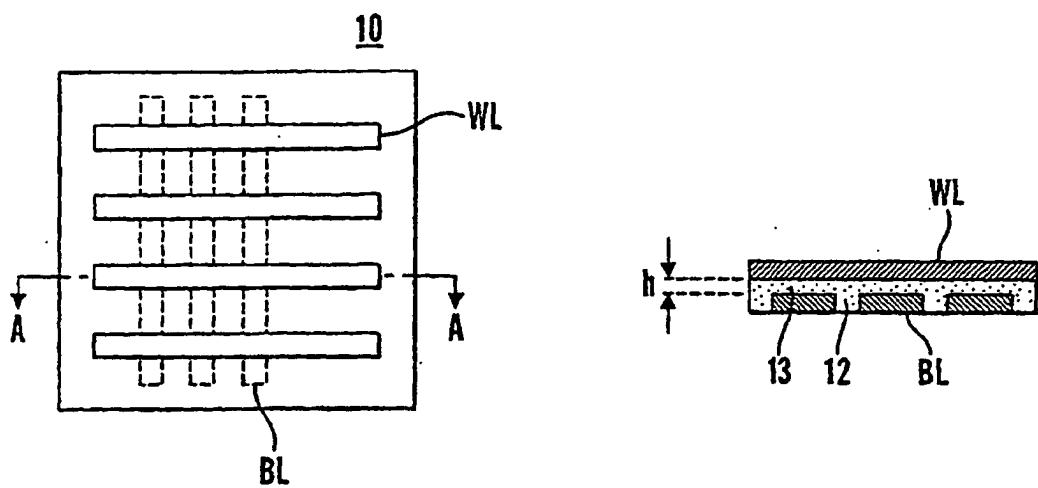

[0024] [Fig. 2](#) ein schematisches Diagramm eines Abschnitts einer passiven Speichermatrix mit überquerenden Elektrodenleitungen, wobei die Speicherzellen ein ferroelektrisches Material umfassen, welches zwischen diesen Elektroden lokalisiert ist, wenn sie überlappen;

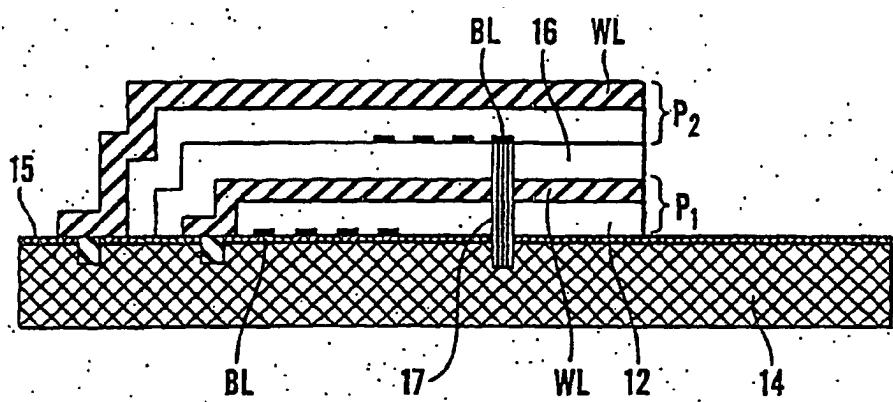

[0025] [Fig. 3](#) eine vergrößerte Querschnittsansicht entlang der Linie A-A in [Fig. 2](#);

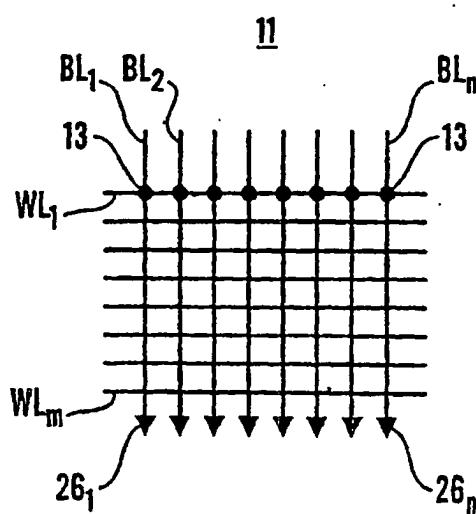

[0026] [Fig. 4](#) ein Funktionsblockdiagramm, das einen vollständigen Wortlesevorgang in einem ferroelektrischen Matrixspeicher darstellt;

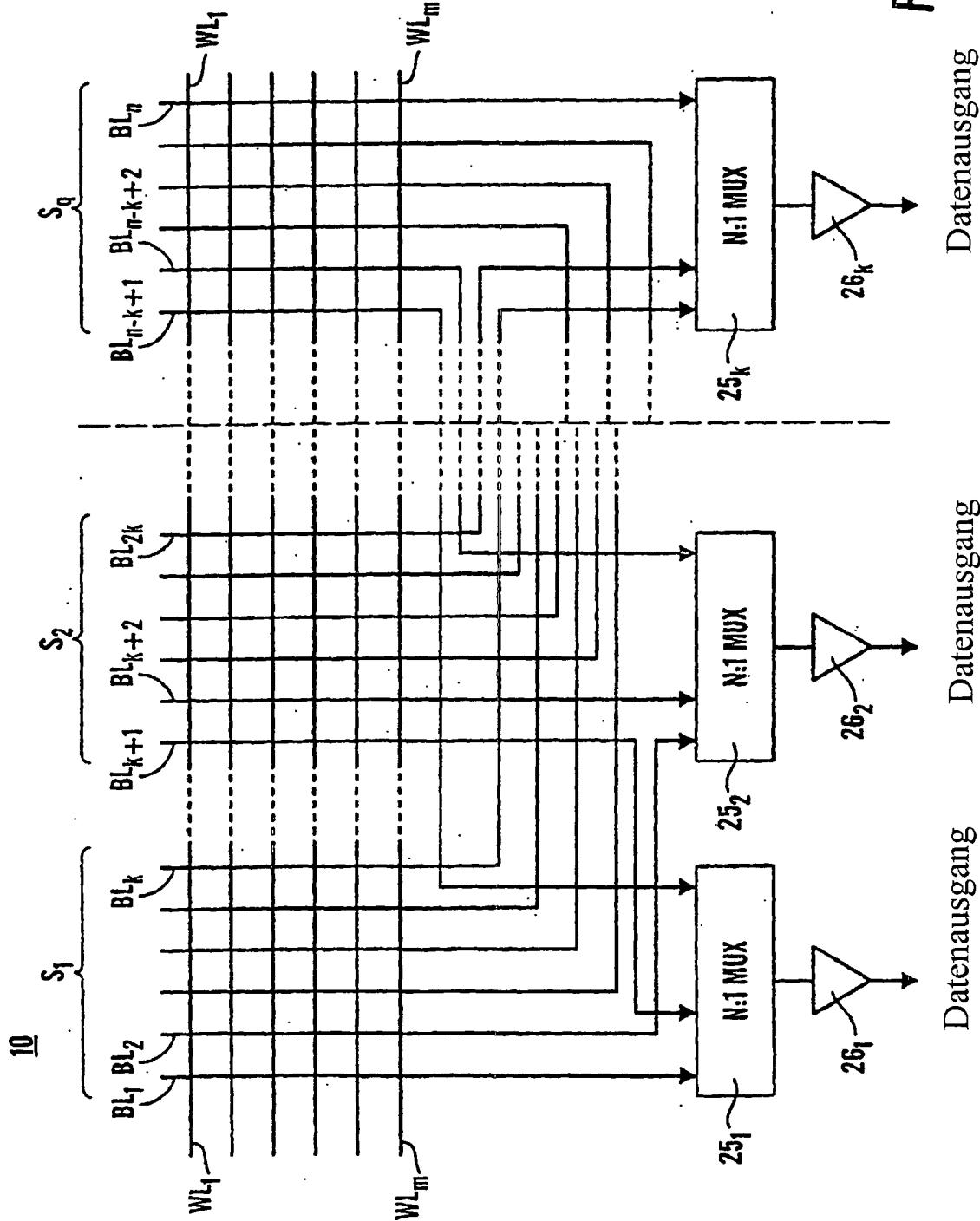

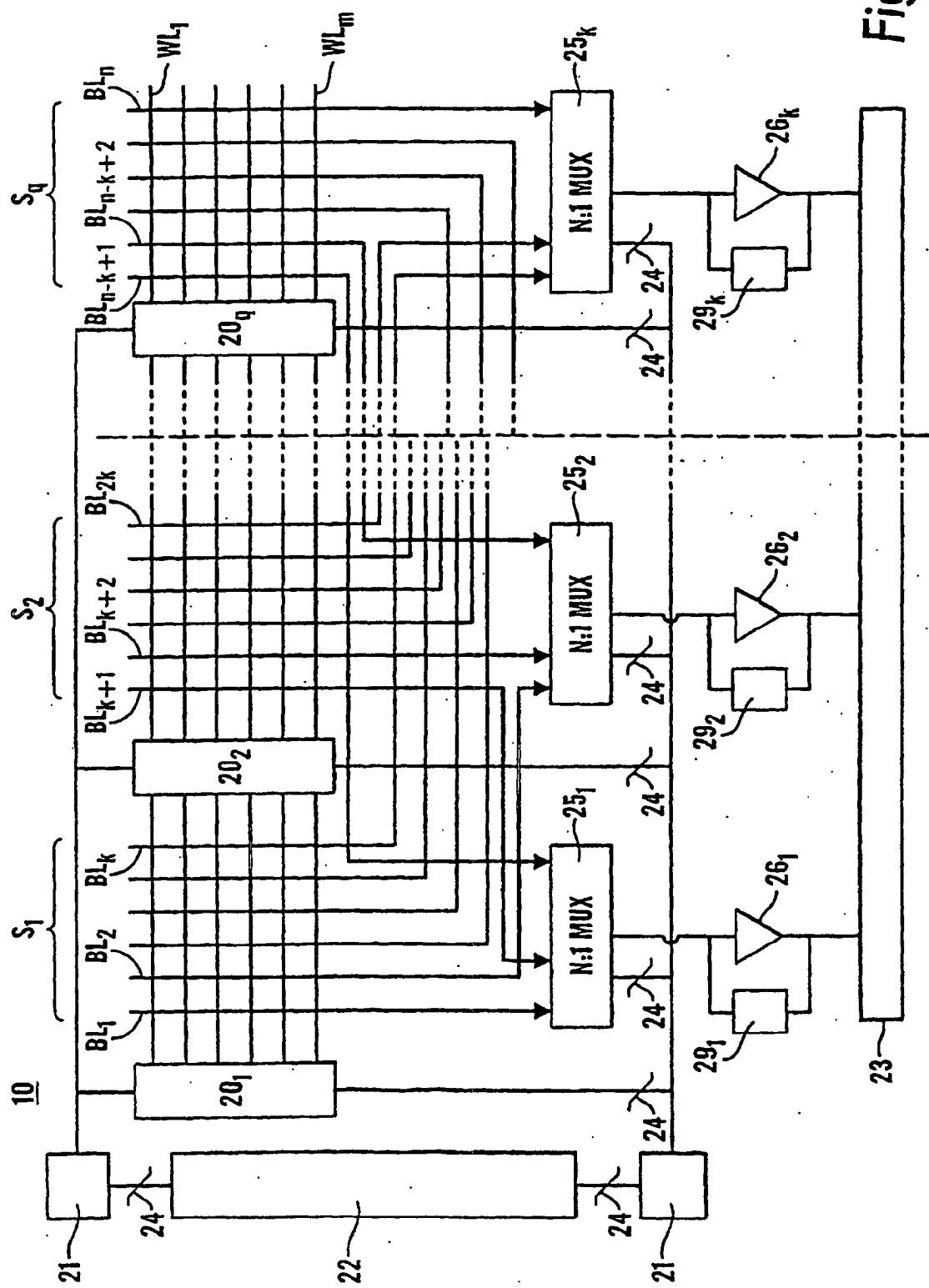

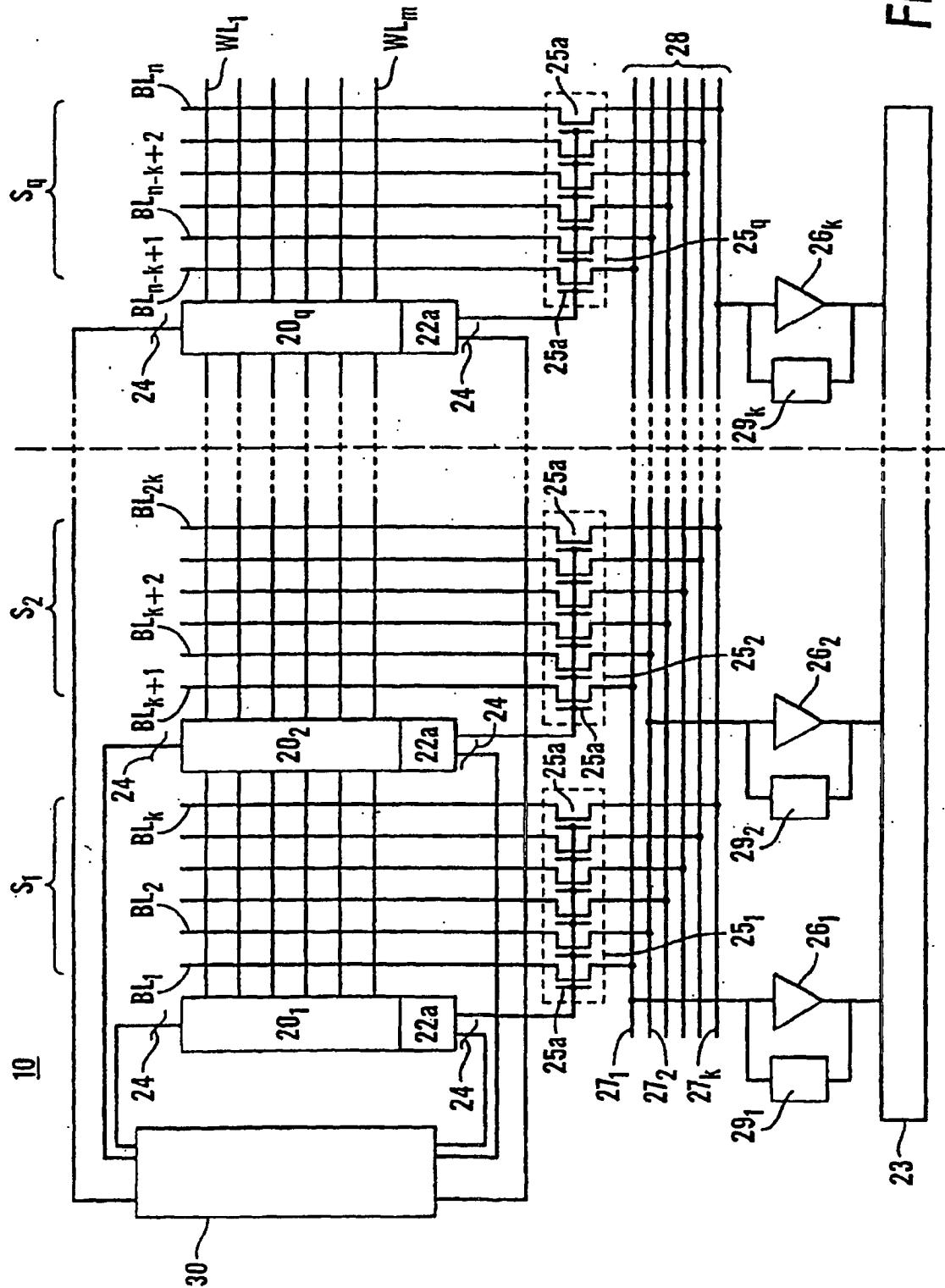

[0027] [Fig. 5](#) ein Funktionsblockdiagramm, das einen passiven Matrixspeicher gemäß einer bevorzugten Ausführungsform der Erfindung und mit segmentierten Wortleitungen darstellt;

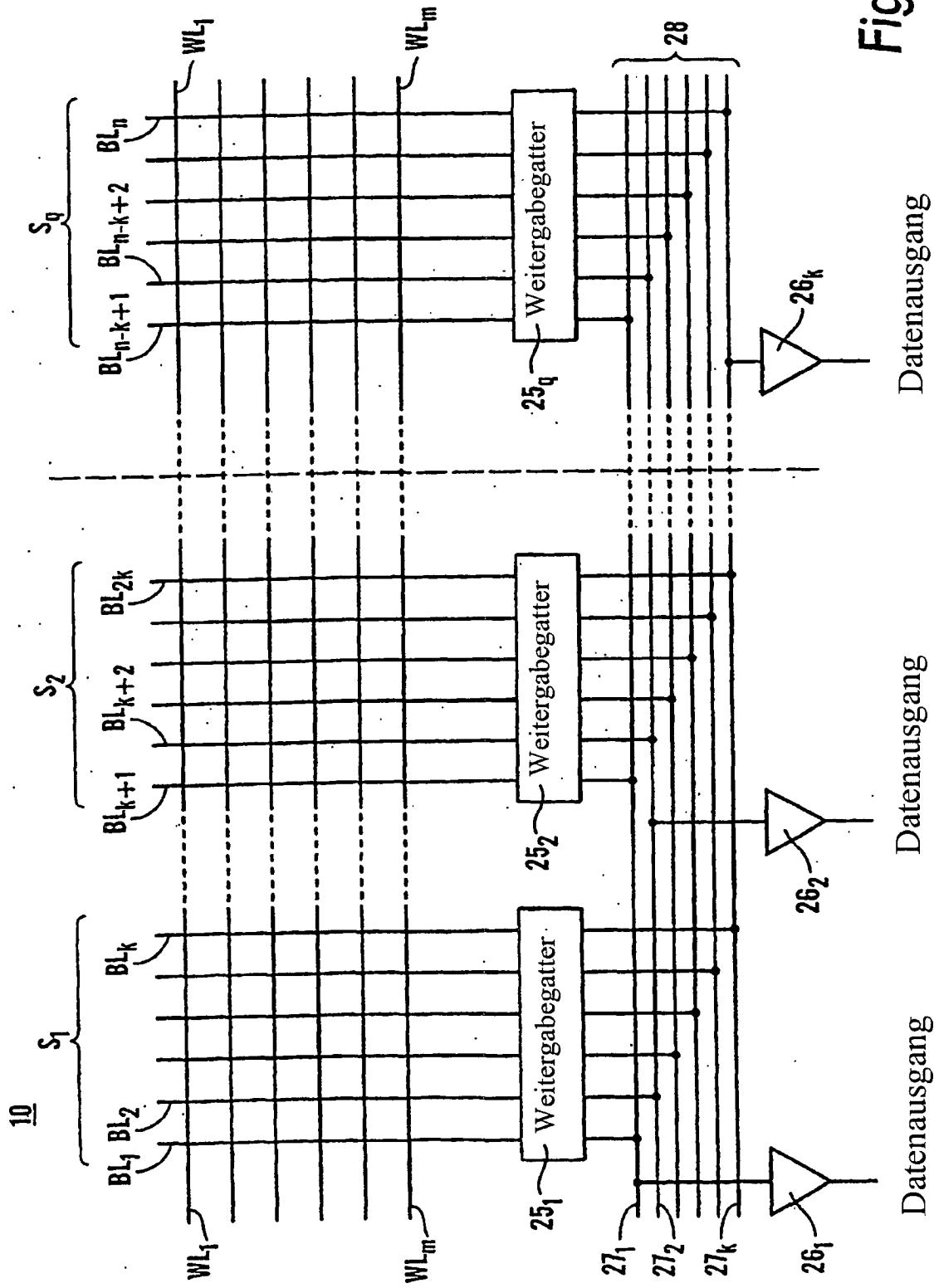

[0028] [Fig. 6](#) ein Funktionsblockdiagramm, das einen passiven Matrixspeicher gemäß einer bevorzugten Ausführungsform der Erfindung und mit segmentierten Wortleitungen darstellt;

[0029] [Fig. 7a](#) ein einfaches Timingdiagramm zum Lesen eines vollständigen Worts mit einem folgenden Schreib/Wiederauffrischungszyklus, der zum Adressieren einer Wortleitung eines Segments der Speichermatrix in einem „Lesevorgang für ein vollständiges Wort“ bereitgestellt wird;

[0030] [Fig. 7b](#) eine Variante des Timingdiagramms in [Fig. 7a](#); und

[0031] [Fig. 8](#) die gleiche Ausführungsform wie in [Fig. 5](#), aber mit einer elektrischen Segmentierung der Wortleitungen; und

[0032] [Fig. 9](#) die Ausführungsform wie in [Fig. 6](#), aber mit einer elektrischen Segmentierung der Wortleitungen; und

[0033] [Fig. 10](#) schematisch, wie die Speichermatrix in [Fig. 5](#) oder [Fig. 6](#) in einer volumetrischen Speichereinrichtung implementiert werden kann.

[0034] Bevor eine ausführliche Beschreibung von bevorzugten Ausführungsformen angegeben wird, soll der allgemeine Hintergrund der vorliegenden Erfindung diskutiert werden, um ein besseres Verständnis darüber zu geben, wie eine passive Speichereinrichtung oder sogar eine einzelne Speicherzelle in einem derartigen Speicher arbeitet. In diesem Zusammenhang wird auf [Fig. 1](#) verwiesen, die eine typische so genannte „Hystereseschleife“ eines ferroelektrischen Materials zeigt, wobei die Polarisation  $P$  des ferroelektrischen Materials über dem elektrischen Feld  $E$  und/oder in Bezug auf eine Potentialdifferenz

$V$  aufgetragen werden kann. Der Wert der Polarisationsrichtung wird sich um die Schleife in der angezeigten Richtung bewegen. Ein ferroelektrisches Material mit einer Hystereseschleife, wie in [Fig. 1](#) gezeigt, wird seine Nettopolarisationsrichtung („Schalten“) auf die Anlegung eines elektrischen Felds (einer Spannung  $V_s$ ), die ein so genanntes elektrisches Koerzitivfeld  $E_c$  (Spannung  $V_c$ ) übersteigt, ändern. Wenn das elektrische Feld  $E$  (die Spannung  $V$ ) das elektrische Koerzitivfeld  $E_c$  ( $V_c$ ) übersteigt, dann ändert sich die Polarisation  $P$  abrupt auf einen großen positiven Wert  $+P_r$  (unter der Annahme eines Starts bei einer negativen Polarisation, bei einem elektrischen Null-Feld (Potential)). Diese positive Polarisation  $+P_r$  bleibt, bis ein negatives elektrisches Feld (Spannung  $-V_s$ ), das das negative elektrische Koerzitivfeld  $E_c$  (Spannung  $-V_c$ ) übersteigt, die Polarisation wieder zurück auf eine negative Polarisation ändert. In dieser Weise werden Speichereinrichtungen, die mit Kondensatoren versehen sind, die ein ferroelektrisches Material umfassen, einen Speichereffekt bei Abwesenheit eines angelegten externen elektrischen Felds aufzeigen, sodass ermöglicht wird nicht-flüchtige Daten dadurch zu speichern, dass eine Potentialdifferenz über dem ferroelektrischen Material angelegt wird, was eine Polarisationsantwort hervorruft. Die Richtung (und Größe) davon kann somit eingestellt und in einem gewünschten Zustand gelassen werden. Genauso kann der Polarisationsstatus bestimmt werden. Eine Speicherung und Bestimmung von Daten wird nachstehend mit näheren Einzelheiten beschrieben.

[0035] In Abhängigkeit von der erforderlichen Schaltgeschwindigkeit etc. wird typischerweise eine nominelle Spannung  $V_s$ , die zum Ansteuern des Polarisationszustands des ferroelektrischen Materials verwendet wird, beträchtlich höher als die Koerzitivspannung  $E_c$  gewählt. Die nominelle Spannung  $V_s$  ist allgemein mit einer gestrichelten Linie in [Fig. 1](#) dargestellt, ist aber keineswegs auf diesen bestimmten Wert beschränkt. Andere Werte können zutreffend sein.

[0036] [Fig. 2](#) zeigt einen Teil einer  $m \cdot n$  Speichermatrix **11** eines passiven Matrixspeichers **10**, wobei zwei zueinander gegenüber liegende Sätze von parallelen Elektroden, nämlich Wortleitungs-Elektroden WL und Bitleitungs-Elektroden BL, gezeigt sind. Die Wortleitungs- und die Bitleitungs-Elektroden WL; BL sind senkrecht zueinander angeordnet, wodurch sie an den überschneidenden Gebieten Seitenwände von spezifischen Volumenelementen eines isolierenden ferroelektrischen Materials (welches nachstehend noch näher beschrieben wird) definieren und die wiederum das Volumen von kondensatorartigen Speicherzellen in der Speichermatrix **11** definieren. [Fig. 3](#) offenbart eine Querschnittsansicht entlang der Schnittlinie A-A in [Fig. 2](#). Das Dielektrikum von jedem „Kondensator“ ist das ferroelektrische Material in einer ferroelektrischen Schicht **12**, wobei die Dicke des

Materials die Höhe  $h$  der Volumenelemente definiert, die wiederum die Speicherzellen **13** definieren. – Der Einfachheit halber sind in [Fig. 2](#) nur drei Überschneidungspunkte zwischen den Wortleitungs- und Bitleitungen-Elektroden WL; BL gezeigt.

**[0037]** Durch Anlegung einer Potentialdifferenz  $V_s$  zwischen zwei gegenüber liegenden Elektroden, der Wortleitung WL und der Bitleitung BL in einer Zelle **13**, wird das ferroelektrische Material in der Zelle **13** einem elektrischen Feld E ausgesetzt, das eine Polarisationsantwort mit einer Richtung hervorruft, die in einem von zwei stabilen Zuständen eingestellt und belassen werden kann, nämlich einer positiven oder negativen Polarisation, gemäß der Offenbarung zum Beispiel in [Fig. 1](#). Die zwei Zustände stellen die binären Zustände „1“ und „0“ dar. Genauso kann der Polarisationsstatus der Zelle **13** durch eine erneute Anlegung einer Potentialdifferenz zwischen die zwei gegenüber liegenden Elektroden WL und BL, die diese Zelle **13** adressieren, verändert oder abgeleitet werden, was entweder bewirkt, dass die Polarisation nach Entfernung der Potentialdifferenz unverändert bleibt oder auf die entgegengesetzte Richtung umkippt. In dem ersten Fall wird ein kleiner Strom im Ansprechen auf die angelegte Spannung fließen, während in dem letzteren Fall die Polarisationsänderung einen großen Strom verursacht. Der Strom wird mit einer Referenz verglichen, die in einer Anzahl von Vorgehensweisen (nicht gezeigt) bereitgestellt werden kann, um in der Lage zu sein zu entscheiden, ob eine „0“ oder eine „1“ vorhanden ist. Wenn der Lesevorgang ein destruktiver Lesevorgang ist, dann wird der Polarisationszustand in einigen Zellen auf den entgegengesetzten Zustand umgeschaltet. Zum Beispiel kann der Polarisationszustand der Zelle auf „0“ geschaltet werden, und zwar unabhängig davon ob sie in dem Zustand „1“ oder dem Zustand „0“ ist, der gerade gelesen wird. Der anfängliche Zustand muss an eine Zelle in dem Speicher zurückgeschrieben werden, um die Information in dem Speicher, d.h. den ausgelesenen Wert, zu halten. Eine ausführlichere Beschreibung darüber, wie ein passiver Matrixspeicher arbeitet wird nachstehend bei der Beschreibung einer bevorzugten Ausführungsform der Erfindung angegeben.

**[0038]** Um auch das Verständnis der vorliegenden Erfindung zu verbessern kann auf die [Fig. 4](#) Bezug genommen werden, die ein anderes Ausleseverfahren für passive Matrixspeicher darstellt, das nachstehend als „Lesevorgang für ein vollständiges Wort“ bezeichnet wird, bei dem eine aktive Wortleitung, hier die erste Wortleitung WL<sub>1</sub>, die eine gewünschte Speicherzelle **13** umfasst, über ihrer gesamten Wortlänge, das heißt jeder der Speicherzellen **13**, die durch die Bitleitungen BL<sub>1</sub> ... BL<sub>n</sub> definiert sind, erfasst wird. Ein Lesevorgang eines vollständigen Worts per se ist ein bekanntes Konzept, welches zum Beispiel in der US-A-6 157 578 beschrieben ist. In dem Dokument

ist die Lösung jedoch auf eine aktive Matrixspeicher-einrichtung mit dem Zweck der Erhöhung der Geschwindigkeit zum Transferieren von Daten, die in einem relativ großen Block einer Speichermatrix gespeichert sind, gerichtet. Die vorliegende Erfindung bezieht sich im Gegensatz dazu auf passive Matrixspeicher, wobei Kenntnisse des Standes der Technik in Bezug auf aktive Matrizen, wie in der US-A-6 157 578 beschrieben, nicht relevant sind, da aktive Einrichtungen das Problem mit störenden nicht-adressierten Zellen nicht aufweisen.

**[0039]** Es ist wichtig darauf hinzuweisen, dass gemäß dem Pulsierungsprotokoll für einen Lesevorgang eines vollständigen Worts in einem passiven Matrixspeicher nicht verwendete Wortleitungen, in diesem Fall die Wortleitungen WL<sub>2,...m</sub> auf dem gleichen Potential oder im Wesentlichen dem gleichen Potential wie die Bitleitungen BL<sub>1,...n</sub> gehalten werden können. Demzufolge gibt es kein störendes Signal auf irgendeiner der nicht-adressierten Zellen der Speichermatrix **10**. Für eine Auslesung der Daten (eine Erfassung) wird die aktive Wortleitung, in diesem Fall die erste Wortleitung BL<sub>1</sub>, auf ein Potential gebracht, das einen Strom I veranlasst durch die Zellen auf den kreuzenden Bitleitungen BL<sub>1,...n</sub> zu fließen. Die Größe des Stroms I hängt von dem Polarisationszustand jeder Zelle **13** ab und wird durch eine Erfassungseinrichtung **26**, eine für jede Bitleitung BL, wie in [Fig. 4](#) gezeigt, bestimmt. Die Erfassungseinrichtungen können zum Beispiel Leseverstärker sein.

**[0040]** Das Leseverfahren für ein vollständiges Wort bietet mehrere Vorteile. Zum Beispiel kann die Auslesespannung viel höher als die Koerativspannung gewählt werden, ohne dass eine teilweise Umschaltung in nicht-adressierten Zellen auftritt, und das Verfahren ist mit einer großen Matrix kompatibel.

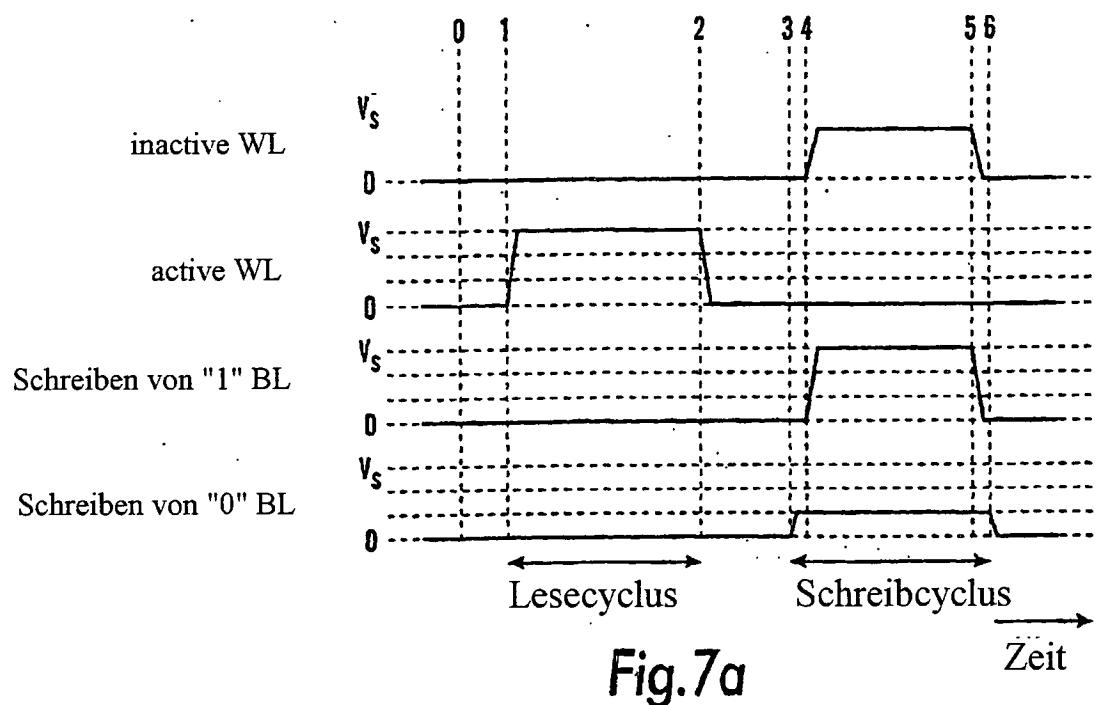

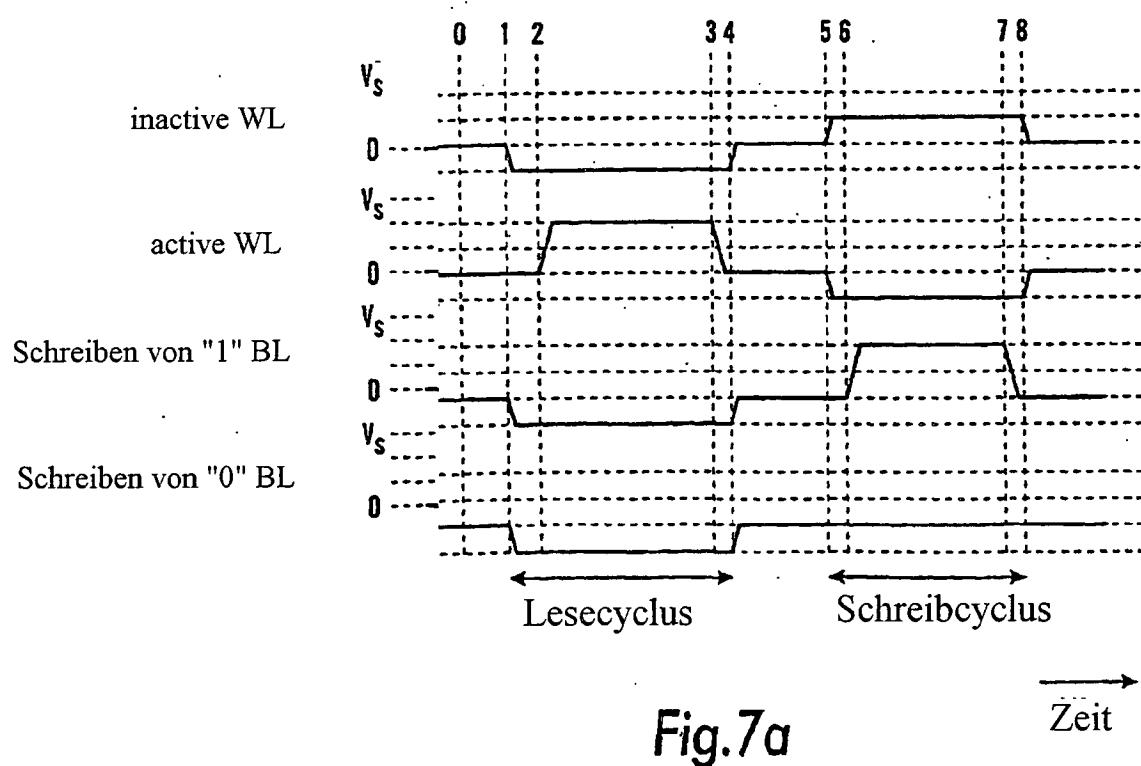

**[0041]** Die bevorzugten Ausführungsformen der vorliegenden Erfindung sind in den [Fig. 5–7](#) der Zeichnungen dargestellt. Ein beiliegendes Timingdiagramm berichtet eine Null-Volt-Störung von nicht-adressierten Speicherzellen ein, während eine Schaltspannung  $V_s$  an sämtliche Zellen der aktiven Wortleitung WL, während einer Auslesung von sämtlichen Zellen in einem aktiven Element angewendet wird. Ein bevorzugtes Timingdiagramm ist in [Fig. 7a](#) gezeigt und ein alternatives Timingdiagramm ist in [Fig. 7b](#) offenbart.

**[0042]** Unter Bezugnahme auf [Fig. 5](#), die eine bevorzugte Ausführungsform der passiven Speicher-einrichtung gemäß der vorliegenden Erfindung zeigt, wird die Matrixeigenschaft als eine m·n Matrix verkörpert, die durch m Wortleitungen WL<sub>1,...m</sub> und n Bitleitungen BL<sub>1,...n</sub> gebildet ist. Die Wortleitungen sind in q Segmente S unterteilt, wobei jedes Segment S durch eine Anzahl k von angrenzenden Bitleitungen BL in der Matrix BL definiert ist. Vorzugsweise ist k das

Gleiche für sämtliche Segmente, sodass  $q \cdot k = n$  ist. Für eine Auslesung kann die erste Bitleitung in jedem Segment S nun durch einen ersten Multiplexer **25**, mit einer ersten Erfassungseinrichtung **26**, gekoppelt werden. Die zweite Bitleitung in jedem Segment soll entsprechend mit einem anderen Multiplexer **25<sub>2</sub>**, gekoppelt werden, sodass die  $k$ -te Leitung in jedem Segment mit einem letzten Multiplexer **25<sub>k</sub>** gekoppelt sein wird. Die Anzahl von Multiplexern (MUX) **25** soll mit anderen Worten gleich zu der größten Anzahl von Bitleitungen BL sein, die ein Segment definiert. Dies schließt natürlich nicht aus, dass die Anzahl von Bitleitungen in jedem Segment S unterschiedlich sein kann, wenn aber die Speicherzellen auf den Bitleitungen auf dem Segment Datenworte mit der gleichen Länge enthalten, wird  $k$  das Gleiche für sämtliche Segmente sein. Jeder Multiplexer **25** ist mit einer Erfassungseinrichtung **26** zum Auslesen von Daten verbunden und die Anzahl von Erfassungseinrichtungen **26** wird ebenfalls gleich zu der größten Anzahl  $k$  von den Bitleitungen BL sein, die ein Segment definiert. Unterschiedlich zu herkömmlichen passiven Matrixspeichern, die einen partiellen Wortlesevorgang verwenden, sind sämtliche Speicherzellen **13** in einem Wortleitungssegment  $n$  gleichzeitig mit der Erfassungseinrichtung **26** verbunden, sodass sämtliche Bit-Spots auf einem Wortleitungssegment parallel ausgelesen werden können. Insbesondere können die Erfassungseinrichtungen Leseverstärker sein. – Der Einfachheit halber sind nur die zwei ersten Segmente  $S_1$ ,  $S_2$  und das letzte Segment  $S_q$  in [Fig. 5](#) herausgestellt und das Gleiche trifft auf die zugehörigen Multiplexer **25** und die Leseverstärker **26** zu. Auf Daten, die gespeichert sind und/oder die in der Speichermatrix **11** gespeichert werden sollen, kann mit Hilfe eines zugehörigen Zeilendecoders und eines Spaltendecoders, der in [Fig. 5](#) nicht gezeigt ist, zugegriffen werden und die Daten, die in den Speicherzellen **13** in der Speichermatrix **11** gespeichert sind, können mit einem Impulsprotokoll, z.B. wie in Verbindung mit [Fig. 7a](#) diskutiert, über die Leseverstärker **26** ausgelesen werden, die mit den Bitleitungen über die Multiplexer **25** verbunden sind. Sämtliche Bitleitungen, die ein Wortleitungssegment S definieren, werden an Multiplexer **25** geführt und werden nur dann gewählt, wenn eine gegebene Wortleitung WL in diesem Segment aktiv ist. In dieser Weise werden sämtliche Bitleitungen in der aktiven Wortleitung WL in dem Segment S parallel in einer „Konfiguration eines vollständigen Worts“ ausgelesen und sämtliche Bitleitungen sind unter den Leseverstärkern **26** verteilt.

**[0043]** In einer praktischen Ausführungsform kann die passive Speichereinrichtung zum Beispiel ein 16 Mbit Speicher, aufgeteilt in 8 Segmente S, d.h. mit  $q = 8$ , sein und 256000 Wortleitungen WL von jeweils 64 Bits umfassen. Dann werden 8 Bitleitungen BL in jedem Segment S vorhanden sein, mit anderen Worten  $k = 8$ . Andere Architekturen sind natürlich auch

möglich, z.B. mit 9, 16 oder 32 Bitleitungen in jedem Segment S.

**[0044]** In einer anderen bevorzugten Ausführungsform der Erfindung werden wenigstens 256 Speicherzellen **13** in jedem Segment S verwendet. Mit der Verwendung von 32:1 Multiplexern **25** bildet dies einen 8192 Bits breiten Speicher mit einer nur 32 Duplikation von Wortleitungs-Treibern. Jede Wortleitung wird dann natürlich in Übereinstimmung mit der Anzahl von vorgesehenen Leseverstärkern **26** segmentiert sein.

**[0045]** In [Fig. 6](#) ist eine alternative Ausführungsform der Speichereinrichtung gemäß der vorliegenden Erfindung gezeigt, wobei die Multiplexer durch eine Gattereinrichtung **25** ersetzt sind. Die Gattereinrichtungen **25** aktivieren die Bitleitungen BL in der gleichen Weise wie die Multiplexer.

**[0046]** Vorzugsweise werden die Gattereinrichtungen **25** als Weitergabegatter (pass gates) realisiert, die mit jeder Bitleitung BL in einem Segment S verbunden sind. Während die Anzahl von Multiplexern **25** in der Ausführungsform in [Fig. 5](#) gleich zu der Anzahl von Bitleitungen BL in dem Segment S sein sollte, nämlich  $k$ , sollte die Anzahl von Weitergabegattern **25** in der Ausführungsform in [Fig. 6](#) der Anzahl  $q$  von Segmenten S entsprechen. Die Anzahl von Ausgängen auf jedem Weitergabegatter **25** entspricht der Anzahl von Bitleitungen BL in dem jeweiligen Segment S. Um eine parallele Auslesung von Speicherzellen **13** der aktiven Wortleitung WL in dem Segment S aufrecht zu erhalten wird ein Leseverstärker **26** für jede Bitleitung BL in dem Segment verwendet, wobei jeder Leseverstärker **26** mit einer der Leitungen **27** auf einem Datenbus **28** verbunden ist. Ein erster Ausgang des Weitergabegatters ist mit der ersten Busleitung **27<sub>1</sub>** und der zweite mit der zweiten Busleitung **27<sub>2</sub>** etc. verbunden und die Anzahl von Busleitungen **27** und Leseverstärkern wird natürlich die größte Anzahl von Bitleitungen BL, die ein Segment S definiert, sein.

**[0047]** Die [Fig. 7a](#) und [Fig. 7b](#) heben alternative Timingdiagramme für einen Lesezyklus eines vollständigen Worts hervor.

**[0048]** Die [Fig. 7a](#) zeigt ein Timingdiagramm für einen Lesevorgang eines vollständigen Worts mit einem folgenden Schreib/Lese-Zyklus („Wiederauffrischung“, „Zurückschreiben“ („refresh“, „write back“)) für ein Wortleitungssegment. Dieses Timingdiagramm ist auf ein Spannungsprotokoll mit vier Ebenen gestützt. Gemäß dieses Timingdiagramms werden sämtliche Wortleitungen und sämtliche Bitleitungen, wenn keine Zelle in der Matrix gelesen oder beschrieben wird, auf einer Ruhespannung gehalten, die gleich zu Null-Volt ist. Sämtliche Speicherzellen weisen eine Adresse auf, die den Überkreuzungen

entspricht, die aus einer aktiven Wortleitung WL und durch sämtliche Bitleitungen BL innerhalb dieses Segments, welches gelesen werden soll, gebildet sind. Die inaktiven Wortleitungen WL und sämtliche Bitleitungen BL folgen den gleichen Potentialkurven während des Lesezyklus. Während des Lesezyklus wird die Wortleitung, die die zu lesenden Zellen kontaktiert, auf eine Schaltspannung  $V_s$  gesetzt. In dem gleichen Zeitintervall werden sämtliche Bitleitungen auf einer Null-Spannung gehalten. In dem Timingdiagramm, welches gezeigt ist, ist vorgesehen, dass eine Anlegung der Spannung  $V_s$  auf der Wortleitungsseite einer Zelle und einer Null-Spannung auf der Bitleitungsseite der gleichen Zelle impliziert, dass eine „0“ in die Zelle eingeschrieben wird. Dementsprechend werden in beiden Timingdiagrammen, die gezeigt sind, sämtliche Zellen auf den aktiven Wortleitungen auf den Null-Zustand eingestellt, nachdem der Lesebetrieb ausgeführt worden ist. Um deshalb Daten wiederherzustellen, die in dem Speicher gespeichert sind, wird es erforderlich sein eine „1“ nur auf den Bitleitungen zurückzuschreiben, die Zellen aufweisen, die „1“ enthalten sollten. Dies ist in beiden Beispielen in den [Fig. 7a](#) und [Fig. 7b](#) gezeigt, wo eine Spannung mit einer umgekehrten Polarität an die Zelle angelegt wird, die mit einer „1“ während des Lesezyklus, wie in dem Diagramm angedeutet, beschrieben werden soll.

**[0049]** [Fig. 7b](#) zeigt ein alternatives Timingdiagramm auf Grundlage eines Spannungsprotokolls mit vier Ebenen. Gemäß dieser Ausführungsform werden sämtliche Wortleitungen und Bitleitungen, wenn keine Zelle in der Matrix gelesen oder beschrieben wird, auf einer Ruhespannung  $V_s/3$  gehalten.

**[0050]** Die exakten Werte für sämtliche Timingpunkte, die als Beispiel in den [Fig. 7a](#) und [Fig. 7b](#) dargestellt sind, sind von den Materialien der Speicherzellen und den Einzelheiten der Konstruktion abhängig.

**[0051]** In den Ausführungsformen der [Fig. 5](#) und [Fig. 6](#) könnten die Wortleitungen im Prinzip nicht unterbrochen sein, d.h. sie erstrecken sich kontinuierlich zu den getrennten Segmenten, wobei die Segmente nur durch die Bitleitungen, die in Frage stehen, definiert sind. Eine Multiplexierung und Protokolle für einen Lesevorgang und einen Schreibvorgang müssen dann darauf angepasst werden. Es ist jedoch kein Vorteil, dass die Wortleitungen zu lang werden. Mit einer begrenzten Anzahl von Segmenten und einer begrenzten Anzahl von Bitleitungen in jedem Segment wird dies vermieden, z.B. wie in dem voranstehend erwähnten Beispiel, bei dem 256000 Wortleitungen und 8 Segmente mit 8 Bitleitungen in jedem Segment verwendet werden. Der Speicher erhält dann, wie angegeben, eine Speicherkapazität von 16 Mbits. Es gibt jedoch auch andere Nachteile mit kontinuierlichen Wortleitungen. Wenn die Bit-Spots der Speicherzellen in dem Segment S mit einer hohen

Spannung auf der aktiven Wortleitung gelesen werden, wird die gleiche hohe Spannung auf die aktiven Wortleitungen in sämtlichen Segmenten aufgeprägt und, obwohl sogar nur die Bitleitungen in den adressierten Segmenten verbunden sind, können kapazitive Kopplungen und Kriechströme gebildet werden und beeinflussen z.B. die Speicherzellen in angrenzenden nicht-aktiven Wortleitungen in dem Segment, etwas, was zu unechten Auslesevorgängen oder Rauschbeiträgen führen kann. In einer praktischen Ausführungsform der Speichereinrichtung gemäß der Erfindung wird es somit auch relevant sein in der Lage zu sein die Wortleitungen elektrisch derart zu segmentieren, dass nur die aktive Wortleitung innerhalb des adressierten Segments elektrisch mit dem Treiber verbunden ist, wo hingegen die entsprechenden Wortleitungssegmente in den übrigen Segmenten getrennt sind. Dies wird besonders relevant sein, wenn das Protokoll in [Fig. 7](#) verwendet wird, und kann mit einer Ausführungsform der Speichereinrichtung, wie in [Fig. 8](#) gezeigt, stattfinden, die im Prinzip derjenigen in [Fig. 5](#) entspricht. Ein nicht gezeigter Treiber in einer Treibergruppe **20** wird mit Hilfe eines Segmentwählers **22** gewählt, der z.B. als ein Wählerbus realisiert werden kann, sodass die Wortleitung WL in dem gewählten Segment S für einen Lese- oder Schreibzyklus aktiviert wird. Die Multiplexer **25**, die durch die Segmentwählereinrichtung **22** gesteuert werden, können mit einem gewählten Treiber in der Gruppe **20** über Schalter **24** verbunden und über die Wählereinrichtungen **22** über einen schaltbaren Casche-Speicher **21** gesteuert werden. Der spezifische Multiplexer **25** wird gleichzeitig adressiert zum Verbinden der Bitleitungen BL in dem adressierten Segment mit dem Leseverstärker **26**. In rein praktischer Hinsicht kann jede Wortleitung WL in einem Segment mit einem UND Gatter, z.B. einem CMOS Logikgatter oder einem Weitergabegatter, verbunden werden und das Segment kann von einer Wortleitung oder einem Adressendecoder adressiert werden. Zum Beispiel würde die Wortleitung WL<sub>1</sub> in dem Segment S<sub>1</sub> gewählt und ist dann nur Spannung auf der Wortleitung innerhalb des Segments S<sub>1</sub>. Mit einer destruktiven Auslesung werden nun alle Speicherzellen und die Wortleitungen WL<sub>1</sub> in dem Segment S<sub>1</sub> auf einen Null-Zustand umgeschaltet, während der Multiplexer **25** sämtliche Bitleitungen in dem Segment S<sub>1</sub> mit den jeweiligen Leseverstärkern **26<sub>1</sub>** ... **26<sub>k</sub>** verbindet. Sämtliche Zellen auf der aktivierte Wortleitung können somit ausgelesen werden, d.h. ein Lesevorgang eines vollständigen Worts wird erhalten, wenn die Wortleitung des Segments definiert ist, um ein Datenwort zu enthalten. Während der Zustand von sämtlichen Zellen auf der gewählten Wortleitung WL, dann erfasst ist, werden die verbleibenden Wortleitungen WL<sub>2</sub> ... WL<sub>m</sub> und die Bitleitungen BL<sub>1</sub>-BL<sub>k</sub> auf einer Ruhespannung in der Nähe der Vorspannpunkte der Leseverstärker **26** gehalten und im Prinzip wird dann kein Störungsbeitrag von den übrigen Zellen des Segments vorhanden sein. Außerdem wird kei-

nerlei Vorspannung auf den Zellen auf der Bitleitung vorhanden sein, sodass störende Signale an dem Eingang der Leseverstärker **26** erzeugt werden können. Der Datenausgang des Leseverstärkers **26** wird an einen Zweiweg-Datenbus **23** weitergeleitet, während eine Schreiblogik **29** parallel mit dem Ausgang der Multiplexer zum Schreiben von Daten an die Bit-Spots der Zellen auf einer aktiven Wortleitung in dem Segment verbunden ist, wobei die Wortleitungen in den Segmenten in entsprechenden Vorgehensweisen über die Wählereinrichtung **22** gewählt werden, wie für den Fall eines Auslesevorgangs. Vorzugsweise sind Pufferspeicher **21** auf den schaltbaren Ausgängen der Wählereinrichtung **22** vorgesehen und die Letzteren verbinden Treiber und Multiplexer **25** über eine Anzahl von Leitungsschaltern **24**, die durch die Wählereinrichtungen **22** gesteuert wird (werden).

**[0052]** [Fig. 9](#) zeigt eine Ausführungsform, die funktional äquivalent zu denjenigen der [Fig. 8](#) ist, die aber zusätzlich der Ausführungsform in [Fig. 6](#) entspricht, bei der Multiplexer durch Weitergabegatter **25** ersetzt worden sind. Jede Weitergabeeinrichtung **25** kann z.B. Schalttransistoren **25a** umfassen, die als Weitergabegatter funktionieren, und zwar einer für jede Leitung, sodass insgesamt  $k$  Schalttransistoren **25a** in einer Weitergabeeinrichtung **25** vorhanden sein werden. Wie in dem Fall mit der Ausführungsform in [Fig. 8](#) sind Treibergruppen **20** vorgesehen, eine für jedes Segment, während die Wählereinrichtung **22** nun durch einen Treibergruppen-Wähler **22a** ersetzt ist. Die Adressierung der getrennten Wortleitung WL findet über den Ausgang in einem Wortleitungs-Adressenbus **30** unter der Steuerung durch den Gruppenwähler **22a** statt. Bei der Auslesung sind die Bitleitungen **25a** mit der Busleitung **27** in dem Datenbus **28** verbunden und der Datenausgang des Leseverstärkers ist mit einem Zweiweg-Datenbus **23** verbunden. Wie in [Fig. 8](#) ist die Schreiblogik **29** parallel über den Leseverstärkern **26** vorgesehen und wenn ein Schreibvorgang stattfindet wird das Wortleitungssegment über die Gruppenwähler **22a** und mit einer Adressierung über den Wortleitungs-Adressenbus **30** gewählt.

**[0053]** Grundlegend sind die erforderlichen Einrichtungen und Mittel für eine Auswahl, Decodierung und Adressierung, genauso wie die nicht gezeigte Timelogik, in dem technischen Gebiet altbekannt und werden üblicherweise in Matrix-adressierbaren Speichern verwendet, unabhängig davon ob sie aktiv oder passiv sind, und sie werden somit hier nicht mit näheren Einzelheiten diskutiert.

**[0054]** Die Anzahl von Spannungspegeln und die Spannungspegel selbst in dem Pulsierungsprotokoll können beliebig gewählt werden, vorausgesetzt dass die Anforderungen zum Ausführen eines Lesevorgangs eines vollständigen Worts erfüllt werden. Fer-

ner kann die Polarität der Spannungen gemäß der dargestellten Protokolle genauso umgekehrt sein.

**[0055]** In einer praktischen Schaltungstechnologie für die Realisation der Speichereinrichtung gemäß der vorliegenden Erfindung kann die Speichermatrix auf einem Substrat vorgesehen werden und Wortleitungs-Treiber können dort integriert werden, sodass die Gesamtfläche der Einrichtung nicht zunimmt.

**[0056]** Die segmentierten Wortleitungen könnten genauso auf gestapelten Speicherebenen implementiert werden, wobei die Bitleitungen BL vertikal mit den Multiplexern oder den Gattereinrichtungen **25** verbunden sind. Dies ist in [Fig. 10](#) dargestellt, die schematisch und in einem Querschnitt eine Ausführungsform zeigt, bei der Speichereinrichtungen **10** gemäß der Erfindung in einer gestapelten Anordnung vorgesehen sind. Dies realisiert eine volumetrische Datenspeichervorrichtung, bei der jede Schicht oder Speicherebene  $P$  eine Speichereinrichtung **10** umfasst. Durch Bereitstellen der Speichereinrichtungen in einer gestaffelten Anordnung können die jeweiligen Wortleitungen und Bitleitungen über so genannte abgestaffelte Kontaktierungslöcher, d.h. abwechselnden horizontalen und vertikalen „über-die-Kante-Verbindungen“ mit einer Treiber- und Steuerungs-Schaltungsanordnung in dem Substrat **14** verbunden werden. Das Substrat **14** kann anorganisch, d.h. gestützt auf Silizium, sein und somit kann die Schaltungsanordnung in z.B. einer kompatiblen CMOS Technologie implementiert werden. Die [Fig. 10](#) zeigt nur zwei Speicherebenen  $P_1$ ,  $P_2$  (es sei darauf hingewiesen, dass nur eine begrenzte Anzahl von Bitleitungen gezeigt sind), aber in der Praxis kann die volumetrische Datenspeichervorrichtung eine sehr große Anzahl von Speicherebenen, von 8 und weit über 100 oder mehr, umfassen, wobei ein Speicher mit einer sehr hohen Kapazität und Speicherdicthe realisiert wird, da jede Speicherebene nur ungefähr  $1 \mu\text{m}$  dick oder sogar weniger sein wird.

**[0057]** Vorteile der passiven Matrixspeichereinrichtung, die voranstehend beschrieben wurde, umfassen die Einfachheit einer Herstellung und eine hohe Dichte von Zellen. Weitere Vorteile sind:

- Wenn die Wortleitungen elektrisch segmentiert werden, werden nicht-adressierte Speicherzellen während des Lesezyklus einem Null-Volt-Potential (oder einem kleinen Potential) ausgesetzt, unter der Voraussetzung, dass das Protokoll gemäß [Fig. 7a](#) verwendet wird. Dies wird die Anzahl von Störsignalen verringern, die zu einem Verlust in dem Speicherinhalt führen könnten, sowie sämtliche Störungen während eines Lesebetriebs, die Kriechströme hervorrufen, beseitigen.

- Die Datentransferrate wird bei der maximalen Rate, wie durch die Anzahl von Bitleitungen innerhalb eines Segments zugelassen, sein.

- Die Auslesespannung  $V_s$  kann viel höher als die

Koerzitivspannung gewählt werden, ohne dass ein partielles Umschalten in nicht-adressierten Zellen hervorgerufen wird. Dies erlaubt, dass sich Schaltgeschwindigkeiten der höchstmöglichen Geschwindigkeit des polarisierbaren Materials in den Zellen annähert.

d) Das Ausleseverfahren ist mit großen Matrizen kompatibel.

**[0058]** Zusätzlich kann die Speichereinrichtung der Erfindung mit einer verringerten Anzahl von Leseverstärkern realisiert werden, was ein Vorteil ist, wenn der Speicher groß ist und auch in Bezug auf den Energie- bzw. Leistungsverbrauch der Leseverstärker. Dieser kann hoch sein, er kann aber zu einem gewissen Ausmaß durch eine geeignete Energie- bzw. Leistungsverwaltung der Ansteuerungs- und Adressierungs-Schaltungsanordnung verringert werden. Ferner bedeutet eine Verringerung in der Anzahl von Leseverstärkern, dass Grundstücke, die für die Leseeinrichtungen speziell vorgesehen sind, balanciert sein können, um eine Gesamtflächenoptimierung in der Speichereinrichtung zu erzielen. Schließlich impliziert die Segmentierung der Wortleitungen, dass Fehler während einer Auslesung oder Adressierung in einem einzelnen Wort für den Fall eines einzelnen Wortleitungsfehlers angeordnet sein werden.

### Patentansprüche

1. Nicht-flüchtige passive Matrixspeichereinrichtung (**10**), umfassend ein elektrisch polarisierbares dielektrisches Speichermaterial (**12**), das eine Hysterese, insbesondere ein ferromagnetisches Material, wobei das Speichermaterial (**12**) in einer Schicht zwischen einem ersten Satz und einem zweiten Satz (**14; 15**) von jeweiligen parallelen Adressierungselektroden eingebettet ist, wobei die Elektroden des ersten Satzes (**14**) Wortleitungen (**WL<sub>1,...,m</sub>**) der Speichereinrichtung bilden und in einer im Wesentlichen orthogonalen Beziehung zu den Elektroden des zweiten Satzes (**15**) sind, wobei die letzteren Bitleitungen (**BL<sub>1,...,n</sub>**) der Speichereinrichtung bilden, wobei eine Speicherzelle (**13**) mit einer Kondensator-artigen Struktur in dem Speichermaterial (**12**) an den Überschneidungen zwischen Wortleitungen und Bitleitungen definiert wird, wobei die Speicherzellen (**13**) der Speichereinrichtung die Elemente einer passiven Matrix (**11**) bilden, wobei jede Speicherzelle (**13**) selektiv für einen Schreib/Lese-Betrieb über eine Wortleitung (**WL**) und eine Bitleitung (**BL**) gewählt werden kann, wobei ein Schreibbetrieb an eine Speicherzelle (**13**) stattfindet, indem ein gewünschter Polarisationszustand in der Zelle mit Hilfe einer Spannung eingerichtet wird, die an die Zelle über die jeweilige Wortleitung (**WL**) und die Bitleitung (**BL**), die die Zelle definieren, angelegt wird, wobei die angelegte Spannung entweder einen bestimmten Polarisationszustand in der Speicherzelle (**13**) einrichtet oder in der Lage ist zwischen den Polarisationszuständen davon

umzuschalten, und wobei ein Lesebetrieb dadurch stattfindet, dass eine Spannung, die größer als die Koerzitivspannung (**V<sub>c</sub>**) ist, an die Speicherzelle (**13**) angelegt wird und wenigstens ein elektrischer Parameter eines Ausgangsstroms der Bitleitungen (**BL**) erfasst wird, dadurch gekennzeichnet, dass die Wortleitungen (**WL**) in eine Anzahl von Segmenten (**S<sub>1,...,q</sub>**) aufgeteilt sind, wobei jedes Segment eine Vielzahl von angrenzenden Bitleitungen (**BL**) in der Matrix (**11**) umfasst und durch diese definiert wird, und dass eine Einrichtung (**25**) zum Verbinden jeder Bitleitung (**BL**), die zu einem Segment (**S**) zugewiesen ist, mit einer zugehörigen Erfassungseinrichtung (**26**) vorgesehen ist, sodass eine gleichzeitige Verbindung von sämtlichen Speicherzellen (**13**), die einer Wortleitung (**WL**) auf einem Segment (**S**) für eine Auslesung über die entsprechenden Bitleitungen (**BL**) des Segments (**S**) zugewiesen sind, ermöglicht wird, wobei jede Erfassungseinrichtung (**26**) zum Erfassen des Ladungsflusses in der Bitleitung (**BL**), die damit verbunden ist, ausgelegt ist, um einen logischen Wert zu bestimmen, der in der Speicherzelle (**13**) gespeichert ist, die durch die Bitleitung definiert wird.

2. Nicht-flüchtige passive Matrixspeichereinrichtung (**10**) nach Anspruch 1, dadurch gekennzeichnet, dass die Einrichtung (**25**) für eine gleichzeitige Verbindung von jeder Bitleitung (**BL**) eines Segments (**S**) mit einer zugehörigen Erfassungseinrichtung (**26**) während einer Adressierung Multiplexer sind.

3. Nicht-flüchtige passive Matrixspeichereinrichtung (**10**) nach Anspruch 2, dadurch gekennzeichnet, dass die Anzahl von Multiplexern (**25**) der größten Anzahl von Bitleitungen (**BL**), die ein Segment (**S**) definieren, entspricht, wobei jede Bitleitung eines Segments mit einem spezifischen Multiplexer verbunden ist.

4. Nicht-flüchtige passive Matrixspeichereinrichtung (**10**) nach Anspruch 3, dadurch gekennzeichnet, dass der Ausgang von jedem Multiplexer (**25**) mit einer einzelnen Erfassungseinrichtung (**26**) verbunden ist.

5. Nicht-flüchtige passive Matrixspeichereinrichtung nach Anspruch 4, dadurch gekennzeichnet, dass die einzelne Erfassungseinrichtung (**26**) ein Erfassungsverstärker ist.

6. Nicht-flüchtige passive Matrixspeichereinrichtung nach Anspruch 1, dadurch gekennzeichnet, dass die Einrichtung (**25**) für eine gleichzeitige Verbindung von jeder Bitleitung (**BL**) eines Segments (**S**) mit einer zugehörigen Erfassungseinrichtung (**26**) während einer Adressierung eine Gattereinrichtung ist.

7. Nicht-flüchtige passive Matrixspeichereinrichtung nach Anspruch 6, dadurch gekennzeichnet,

dass alle Bitleitungen ( $BL_{1,\dots,n}$ ) eines Segments (S) mit einer spezifischen Gattereinrichtung verbunden sind, wobei jede Gattereinrichtung eine Anzahl von Ausgängen entsprechend zu der Anzahl von Bitleitungen (BL) in dem jeweiligen Segment (S) aufweist, dass jeder Ausgang jeder Gattereinrichtung (25) mit einer spezifischen Busleitung (27) eines Ausgangsbusses (28) verbunden ist, wobei die Anzahl von Busleitungen (27) somit der größten Anzahl von Bitleitungen (BL) in einem Segment (S) entspricht, und dass jede Busleitung (27) mit einer einzelnen Erfassungseinrichtung (26) verbunden ist.

8. Nicht-flüchtige passive Matrixspeichereinrichtung nach Anspruch 6, dadurch gekennzeichnet, dass die Gattereinrichtung (25) Weitergabegatter umfassen.

9. Nicht-flüchtige passive Matrixspeichereinrichtung nach Anspruch 6, dadurch gekennzeichnet, dass die Erfassungseinrichtung (26) ein Erfassungsverstärker ist.

10. Verfahren zum Auslesen einer nicht-flüchtigen passiven Matrixspeichereinrichtung (10), die ein elektrisch polarisierbares dielektrisches Speichermaterial (12), das eine Hysterese aufzeigt, insbesondere ein ferroelektrisches Material, umfasst, wobei das Speichermaterial (12) in einer Schicht zwischen einem ersten Satz und einem zweiten Satz (14; 15) von jeweiligen parallelen Adressierungselektroden eingebettet ist, wobei die Elektroden des ersten Satzes (14) Wortleitungen (WL) der Speichereinrichtung (10) bilden und in einer im Wesentlichen orthogonalen Beziehung zu den Elektroden des zweiten Satzes (15) vorgesehen sind, wobei die letzteren Bitleitungen ( $BL_{1,\dots,n}$ ) der Speichereinrichtung (10) bilden, wobei eine Speicherzelle (13) mit einem Kondensator-ähnlichen Aufbau in dem Speichermaterial (12) an Überschneidungen zwischen Wortleitungen (WL) und Bitleitungen (BL) definiert wird, wobei die Speicherzellen (13) der Speichereinrichtung (10) die Elemente einer passiven Matrix (11) bilden, wobei jede Speicherzelle (13) für einen Schreib/Lesebetrieb über eine Wortleitung (WL) und Bitleitung (BL) selektiv adressiert werden kann, wobei ein Schreibbetrieb an eine Speicherzelle (13) stattfindet, indem ein gewünschter Polarisationszustand in der Zelle mit Hilfe einer Spannung eingerichtet wird, die an die Zelle über die jeweilige Wortleitung (WL) und Bitleitung (BL) angelegt wird, die die Zelle definieren, wobei die angelegte Spannung entweder einen gegebenen Polarisationszustand in der Zelle einrichtet oder in der Lage ist die Zelle zwischen ihren Polarisationszuständen zu schalten, wobei ein Lesebetrieb stattfindet, indem eine Spannung größer als die Koerzitivspannung ( $V_c$ ) an die Speicherzelle (13) angelegt wird und wenigstens ein dielektrischer Parameter eines Ausgangstroms auf seinen Bitleitungen (BL) erfasst wird, und wobei das Verfahren Schritte zum

Steuern von elektrischen Potentialen auf sämtlichen Wortleitungen (WL) und Bitleitungen (BL) in einer zeitlich koordinierten Weise in Übereinstimmung mit einem Protokoll, welches elektrische Timingsequenzen für sämtliche Wortleitungen und Bitleitungen umfasst, Anordnen des Protokolls, um einen Lesezyklus zu umfassen, und ermöglichen, dass die Erfassungseinrichtung während des Lesezyklus Ladungen erfassst, die in den Bitleitungen fließen, umfasst und wobei das Verfahren gekennzeichnet ist durch Aufteilen der Wortleitungen (WL) in eine Anzahl von Segmenten ( $S_1, \dots S_q$ ), wobei jedes Segment eine Anzahl von angrenzenden Bitleitungen (BL) in der Matrix (11) umfasst und durch diese definiert wird, Verbinden jeder Bitleitung (BL) innerhalb eines Wortleitungssegments (S) mit einer zugehörigen Erfassungseinrichtung (26), Aktivieren einer Wortleitung (WL) eines Segments (S) in Übereinstimmung mit dem Protokoll zu einer Zeit durch Einstellen des Potentials der einen Wortleitung (WL) des Segments (S) auf die Schaltspannung  $V_s$  während wenigstens eines Abschnitts des Lesezyklus, während sämtliche Bitleitungen des Segments (S) auf einem Null-Potential gehalten werden, und Bestimmen des logischen Werts, der in den individuellen Speicherzellen (13) gespeichert wird, die durch die Erfassungseinrichtung (26) während des Lesezyklus erfasst werden.

11. Verfahren zum Auslesen nach Anspruch 10, gekennzeichnet durch ein Halten von sämtlichen Wortleitungen (WL) und Bitleitungen (BL), wenn keine Speicherzelle (13) gelesen oder beschrieben wird, auf einer Ruhespannung von ungefähr 1/3 der Schaltspannung ( $V_s$ ), Aktivieren einer Wortleitung (WL) in Übereinstimmung mit dem Protokoll zu einer Zeit durch Einstellen des Potentials der einen Wortleitung (WL) des Segments (S) auf die Schaltspannung ( $V_s$ ) während wenigstens eines Abschnitts des Lesezyklus, während sämtliche Bitleitungen (BL) des Segments (S) auf einem Null-Potential gehalten werden, und Bestimmen des logischen Werts, der in den individuellen Speicherzellen (13) gespeichert ist, die durch die Erfassungseinrichtung (26) während des Lesezyklus erfasst werden.

12. Verwendung einer nicht-flüchtigen passiven Matrixspeichereinrichtung (10) nach Anspruch 1 und eines Verfahrens zum Auslesen nach Anspruch 10 in einer volumetrischen Datenspeichervorrichtung mit einer Vielzahl von gestapelten Schichten ( $P_1, P_2, \dots$ ), wobei jede Schicht (P) eine der Nicht-flüchtigen passiven Matrixspeichereinrichtungen (10) umfasst.

Es folgen 8 Blatt Zeichnungen

## Anhängende Zeichnungen

Fig. 1

Fig.2

Fig.3

Fig.4

Fig.6

Datenausgang

Datenausgang

Datenausgang

Fig.7a

Fig.7a

Fig. 8

Fig. 9

Fig. 10