(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5034797号

(P5034797)

(45) 発行日 平成24年9月26日(2012.9.26)

(24) 登録日 平成24年7月13日(2012.7.13)

|              |                          |

|--------------|--------------------------|

| (51) Int.Cl. | F 1                      |

| H04L 25/02   | (2006.01) H04L 25/02 J   |

| G06F 3/00    | (2006.01) G06F 3/00 F    |

| H03K 17/00   | (2006.01) H03K 17/00 F   |

| G09G 5/00    | (2006.01) G09G 5/00 555D |

| G09G 3/20    | (2006.01) G09G 5/00 510X |

請求項の数 16 (全 30 頁) 最終頁に続く

(21) 出願番号 特願2007-232502 (P2007-232502)

(22) 出願日 平成19年9月7日 (2007.9.7)

(65) 公開番号 特開2009-65508 (P2009-65508A)

(43) 公開日 平成21年3月26日 (2009.3.26)

審査請求日 平成22年9月6日 (2010.9.6)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 米澤 岳美

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】シリアルインターフェース回路及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

その各々が、差動信号線を介して差動信号のシリアルデータ又はクロックを受信して受信シリアルデータ又は受信クロックを出力する、第1～第Nのレシーバ回路と、

受信クロックに基づいてサンプリングクロックを生成するサンプリングクロック生成回路と、

生成されたサンプリングクロックに基づいて、受信シリアルデータをサンプリングして、パラレルデータに変換するシリアル／パラレル変換回路と、

前記第1～第Nのレシーバ回路と前記シリアル／パラレル変換回路、前記サンプリングクロック生成回路との間に設けられる接続切り替え回路と、

前記シリアル／パラレル変換回路の後段側に設けられるマッピング変更回路と、

を含み、

差動信号線に対するシリアルデータ、クロックのマッピングが変更された場合に、

前記接続切り替え回路が、クロックとシリアルデータを入れ替えるための信号線の接続の切り替えを行い、

前記マッピング変更回路が、前記シリアル／パラレル変換回路から出力されるパラレルデータに対するデータチャネルのマッピングの変更を行うことを特徴とするシリアルインターフェース回路。

## 【請求項 2】

請求項1において、

10

20

前記第1～第Nのレシーバ回路は、

第1のマッピングモードではシリアルデータを受信し、第2のマッピングモードではクロックを受信する第iのレシーバ回路と、

前記第1のマッピングモードではクロックを受信し、前記第2のマッピングモードではシリアルデータを受信する第jのレシーバ回路を含み、

前記接続切り替え回路は、

前記第1のマッピングモードから前記第2のマッピングモードに切り替わった場合に、前記第iのレシーバ回路の出力ポートの接続先を、前記シリアル／パラレル変換回路のデータ入力ポートから前記サンプリングクロック生成回路のクロック入力ポートに切り替えると共に、前記第jのレシーバ回路の出力ポートの接続先を、前記サンプリングクロック生成回路のクロック入力ポートから前記シリアル／パラレル変換回路のデータ入力ポートに切り替え、10

前記マッピング変更回路は、

前記第1のマッピングモードから前記第2のマッピングモードに切り替わった場合に、前記シリアル／パラレル変換回路が有する第1～第mのシリアル／パラレル変換部から出力されるパラレルデータに対するデータチャネルのマッピングを変更することを特徴とするシリアルインターフェース回路。

#### 【請求項3】

請求項2において、

前記接続切り替え回路は、20

前記第1～第Nのレシーバ回路のうちシリアルデータを受信したレシーバ回路からの出力信号の非反転信号又は反転信号のいずれかを、前記第1、第2のマッピングモードの切り替えに応じて選択して、前記シリアル／パラレル変換回路のデータ入力ポートに対して出力するデータセレクタと、

前記第1～第Nのレシーバ回路のうちクロックを受信したレシーバ回路からの出力信号の非反転信号又は反転信号のいずれかを、前記第1、第2のマッピングモードの切り替えに応じて選択して、前記サンプリングクロック生成回路のクロック入力ポートに対して出力するクロックセレクタを含むことを特徴とするシリアルインターフェース回路。

#### 【請求項4】

請求項3において、30

前記接続切り替え回路は、

前記データセレクタと前記シリアル／パラレル変換回路の間に設けられ、受信シリアルデータの遅延時間を調整するためのデータ遅延回路と、

前記クロックセレクタと前記サンプリングクロック生成回路の間に設けられ、受信クロックの遅延時間を調整するためのクロック遅延回路を含むことを特徴とするシリアルインターフェース回路。

#### 【請求項5】

請求項1乃至4のいずれかにおいて、

前記第1～第Nのレシーバ回路として、第1、第2、第3、第4、第5のレシーバ回路が設けられ、40

前記第1のマッピングモードでは、前記第1、第2、第3、第5のレシーバ回路が、各自、第1、第2、第3、第4のデータチャネルのシリアルデータを受信し、前記第4のレシーバ回路がクロックを受信し、

前記第2のマッピングモードでは、前記第1、第3、第4、第5のレシーバ回路が、各自、第4、第3、第2、第1のデータチャネルのシリアルデータを受信し、前記第2のレシーバ回路がクロックを受信することを特徴とするシリアルインターフェース回路。

#### 【請求項6】

請求項5において、

前記接続切り替え回路は、

前記第1のマッピングモードでは、前記第1、第2、第3、第5のレシーバ回路の出力50

ポートを、前記シリアル／パラレル変換回路が有する第1、第2、第3、第4のシリアル／パラレル変換部の第1、第2、第3、第4のデータ入力ポートに接続すると共に、前記第4のレシーバ回路の出力ポートを、前記サンプリングクロック生成回路のクロック入力ポートに接続し、

前記第2のマッピングモードでは、前記第2のレシーバ回路の出力ポートを、前記サンプリングクロック生成回路のクロック入力ポートに接続し、

前記マッピング変更回路は、

前記第1のマッピングモードでは、前記第1、第2、第3、第4のシリアル／パラレル変換部から出力されるパラレルデータを、第1、第2、第3、第4のデータチャネルのパラレルデータとして出力し、

前記第2のマッピングモードでは、前記第1のシリアル／パラレル変換部から出力されるパラレルデータを第4のデータチャネルにマッピングし、前記第4のシリアル／パラレル変換部から出力されるパラレルデータを第1のデータチャネルにマッピングすることを特徴とするシリアルインターフェース回路。

#### 【請求項7】

請求項6において、

前記接続切り替え回路は、

前記第2のマッピングモードでは、前記第1、第3、第4、第5のレシーバ回路の出力ポートを、各々、前記第1、第2、第3、第4のシリアル／パラレル変換部の前記第1、第2、第3、第4のデータ入力ポートに接続し、

前記マッピング変更回路は、

前記第2のマッピングモードでは、前記第2のシリアル／パラレル変換部から出力されるパラレルデータを第3のデータチャネルにマッピングし、前記第3のシリアル／パラレル変換部から出力されるパラレルデータを第2のデータチャネルにマッピングすることを特徴とするシリアルインターフェース回路。

#### 【請求項8】

請求項5乃至7のいずれかにおいて、

前記接続切り替え回路は、

前記第1のマッピングモードでは、シリアルデータを受信した前記第1のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、前記第1のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第1のデータセレクタと、

前記第1のマッピングモードでは、シリアルデータを受信した前記第2のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、シリアルデータを受信した前記第3のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第2のデータセレクタと、

前記第1のマッピングモードでは、前記第3のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、シリアルデータを受信した前記第4のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第3のデータセレクタと、

前記第1のマッピングモードでは、シリアルデータを受信した前記第5のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、前記第5のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第4のデータセレクタを含むことを特徴とするシリアルインターフェース回路。

#### 【請求項9】

請求項8において、

前記接続切り替え回路は、

前記第1のデータセレクタと前記第1のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第1のデータ遅延回路と、

前記第2のデータセレクタと前記第2のシリアル／パラレル変換部の間に設けられ、受

10

20

30

40

50

信シリアルデータの遅延時間を調整するための第2のデータ遅延回路と、

前記第3のデータセレクタと前記第3のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第3のデータ遅延回路と、

前記第4のデータセレクタと前記第4のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第4のデータ遅延回路を含むことを特徴とするシリアルインターフェース回路。

#### 【請求項10】

請求項5乃至9のいずれかにおいて、

前記接続切り替え回路は、

前記第1のマッピングモードでは、クロックを受信した前記第4のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、クロックを受信した前記第2のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力するクロックセレクタを含むことを特徴とするシリアルインターフェース回路。

10

#### 【請求項11】

請求項10において、

前記接続切り替え回路は、

前記クロックセレクタと前記サンプリングクロック生成回路の間に設けられ、受信クロックの遅延時間を調整するためのクロック遅延回路を含むことを特徴とするシリアルインターフェース回路。

20

#### 【請求項12】

請求項5乃至11のいずれかにおいて、

前記第4のレシーバ回路に接続される差動信号線を構成する第1、第2の信号線のハイインピーダンス状態を、前記第1のマッピングモードにおいて検出する第1のハイインピーダンス状態検出回路と、

前記第2のレシーバ回路に接続される差動信号線を構成する第1、第2の信号線のハイインピーダンス状態を、前記第2のマッピングモードにおいて検出する第2のハイインピーダンス状態検出回路を含むことを特徴とするシリアルインターフェース回路。

#### 【請求項13】

請求項12において、

30

前記第1のハイインピーダンス状態検出回路は、前記第4のレシーバ回路に隣接して配置され、

前記第2のハイインピーダンス状態検出回路は、前記第2のレシーバ回路に隣接して配置されることを特徴とするシリアルインターフェース回路。

#### 【請求項14】

請求項12又は13において、

前記第1、第2のハイインピーダンス状態検出回路の各々は、

前記第1の信号線に接続される第1のブルアップ抵抗と、

前記第2の信号線に接続される第2のブルアップ抵抗と、

レシーバ回路のコモンモードの入力電圧範囲の最小電圧をV\_Lとし、最大電圧をV\_Hとした場合に、前記第1、第2の信号線の電圧が、前記最大電圧V\_Hよりも高くなつたか否かを検出する電圧検出回路を含むことを特徴とするシリアルインターフェース回路。

40

#### 【請求項15】

請求項12乃至14のいずれかにおいて、

前記第1又は第2のハイインピーダンス状態検出回路によりハイインピーダンス状態が検出された場合に、前記シリアル／パラレル変換回路及び前記マッピング変更回路を含むロジック回路ブロックの出力信号を、後段の回路に伝達されないようにマスクする出力マスク回路を含むことを特徴とするシリアルインターフェース回路。

#### 【請求項16】

請求項1乃至15のいずれかに記載のシリアルインターフェース回路と、

50

前記シリアルインターフェース回路により受信されたデータ又はクロックに基づき動作するデバイスと、

を含むことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シリアルインターフェース回路及び電子機器に関する。

【背景技術】

【0002】

近年、EMIノイズの低減などを目的としたインターフェースとしてLVDS (Low Voltage Differential Signaling)などの高速シリアル転送が脚光を浴びている。この高速シリアル転送では、トランスミッタ回路がシリアル化されたデータを差動信号により送信し、レシーバ回路が差動信号を差動増幅することでデータ転送を実現する。10

【0003】

このような高速シリアル転送の従来技術としては例えば特許文献1に開示される技術がある。

【0004】

しかしながら、特許文献1等の従来技術では、差動信号線に対するシリアルデータやクロックのマッピングが変更された場合におけるマッピングモード（端子配列）の切り替え機能については、何ら提案されていなかった。20

【0005】

そして、このようなマッピングモードの切り替え機能を、信号配線の接続の切り替えだけで実現しようとすると、レイアウト面積が大幅に増加したり、信号配線の引き回しに起因する寄生遅延により回路特性が悪化するなどの問題が生じる。

【特許文献1】特開2006-276221

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明に係る幾つかの態様によれば、レイアウト面積の増加や回路特性の悪化を最小限に抑えながらマッピングモードの切り替えを実現できるシリアルインターフェース回路及びこれを含む電子機器を提供できる。30

【課題を解決するための手段】

【0007】

本発明は、その各々が、差動信号線を介して差動信号のシリアルデータ又はクロックを受信して受信シリアルデータ又は受信クロックを出力する、第1～第Nのレシーバ回路と、受信クロックに基づいてサンプリングクロックを生成するサンプリングクロック生成回路と、生成されたサンプリングクロックに基づいて、受信シリアルデータをサンプリングして、パラレルデータに変換するシリアル／パラレル変換回路と、前記第1～第Nのレシーバ回路と前記シリアル／パラレル変換回路、前記サンプリングクロック生成回路との間に設けられる接続切り替え回路と、前記シリアル／パラレル変換回路の後段側に設けられるマッピング変更回路とを含み、差動信号線に対するシリアルデータ、クロックのマッピングが変更された場合に、前記接続切り替え回路が、クロックとシリアルデータを入れ替えるための信号線の接続の切り替えを行い、前記マッピング変更回路が、前記シリアル／パラレル変換回路から出力されるパラレルデータに対するデータチャネルのマッピングの変更を行うシリアルインターフェース回路に係る。

【0008】

本発明によれば、第1～第Nのレシーバ回路によりシリアルデータやクロックが受信され、受信クロックに基づいてサンプリングクロックが生成される。そして受信シリアルデータが、サンプリングクロックに基づいてサンプリングされて、パラレルデータに変換される。この場合に本発明では接続切り替え回路とマッピング変更回路が設けられる。そし4050

て、差動信号線に対するシリアルデータやクロックのマッピングが変更されると、接続切り替え回路により、クロックとシリアルデータの入れ替えが行われ、マッピング変更回路により、データチャネルのマッピングの変更が行われる。従って、接続切り替え回路での配線の切り替えが最小限で済むため、信号配線の引き回しに起因するレイアウト面積の増加や回路特性の悪化を最小限に抑えることが可能になる。

#### 【0009】

また本発明では、前記第1～第Nのレシーバ回路は、第1のマッピングモードではシリアルデータを受信し、第2のマッピングモードではクロックを受信する第iのレシーバ回路と、前記第1のマッピングモードではクロックを受信し、前記第2のマッピングモードではシリアルデータを受信する第jのレシーバ回路を含み、前記接続切り替え回路は、前記第1のマッピングモードから前記第2のマッピングモードに切り替わった場合に、前記第iのレシーバ回路の出力ポートの接続先を、前記シリアル／パラレル変換回路のデータ入力ポートから前記サンプリングクロック生成回路のクロック入力ポートに切り替えると共に、前記第jのレシーバ回路の出力ポートの接続先を、前記サンプリングクロック生成回路のクロック入力ポートから前記シリアル／パラレル変換回路のデータ入力ポートに切り替え、前記マッピング変更回路は、前記第1のマッピングモードから前記第2のマッピングモードに切り替わった場合に、前記シリアル／パラレル変換回路が有する第1～第mのシリアル／パラレル変換部から出力されるパラレルデータに対するデータチャネルのマッピングを変更してもよい。

#### 【0010】

このようにすれば、例えば第iのレシーバ回路がシリアルデータを受信する第1のマッピングモードから、第iのレシーバ回路がクロックを受信する第2のマッピングモードに切り替わると、第iのレシーバ回路の出力ポートの接続先が、シリアル／パラレル変換回路のデータ入力ポートから、サンプリングクロック生成回路のクロック入力ポートに切り替わる。従って、第iのレシーバ回路が受信したクロックを、サンプリングクロック生成回路に対して適正に入力できるようになる。

#### 【0011】

また本発明では、前記接続切り替え回路は、前記第1～第Nのレシーバ回路のうちシリアルデータを受信したレシーバ回路からの出力信号の非反転信号又は反転信号のいずれかを、前記第1、第2のマッピングモードの切り替えに応じて選択して、前記シリアル／パラレル変換回路のデータ入力ポートに対して出力するデータセレクタと、前記第1～第Nのレシーバ回路のうちクロックを受信したレシーバ回路からの出力信号の非反転信号又は反転信号のいずれかを、前記第1、第2のマッピングモードの切り替えに応じて選択して、前記サンプリングクロック生成回路のクロック入力ポートに対して出力するクロックセレクタを含んでもよい。

#### 【0012】

このようにすれば、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、シリアル／パラレル変換回路に入力されるシリアルデータの極性やサンプリングクロック生成回路に入力されるクロックの極性が反転してしまうなどの事態を防止できる。

#### 【0013】

また本発明では、前記接続切り替え回路は、前記データセレクタと前記シリアル／パラレル変換回路の間に設けられ、受信シリアルデータの遅延時間を調整するためのデータ遅延回路と、前記クロックセレクタと前記サンプリングクロック生成回路の間に設けられ、受信クロックの遅延時間を調整するためのクロック遅延回路を含んでもよい。

#### 【0014】

このようにすれば、例えば第1のマッピングモードから第2のマッピングモードに切り替わった場合に、信号極性については変化させない状態で、クロックやデータを遅延させる調整が可能になる。

#### 【0015】

10

20

30

40

50

また本発明では、前記第1～第Nのレシーバ回路として、第1、第2、第3、第4、第5のレシーバ回路が設けられ、前記第1のマッピングモードでは、前記第1、第2、第3、第5のレシーバ回路が、各々、第1、第2、第3、第4のデータチャネルのシリアルデータを受信し、前記第4のレシーバ回路がクロックを受信し、前記第2のマッピングモードでは、前記第1、第3、第4、第5のレシーバ回路が、各々、第4、第3、第2、第1のデータチャネルのシリアルデータを受信し、前記第2のレシーバ回路がクロックを受信してもよい。

#### 【0016】

また本発明では、前記接続切り替え回路は、前記第1のマッピングモードでは、前記第1、第2、第3、第5のレシーバ回路の出力ポートを、前記シリアル／パラレル変換回路が有する第1、第2、第3、第4のシリアル／パラレル変換部の第1、第2、第3、第4のデータ入力ポートに接続すると共に、前記第4のレシーバ回路の出力ポートを、前記サンプリングクロック生成回路のクロック入力ポートに接続し、前記第2のマッピングモードでは、前記第2のレシーバ回路の出力ポートを、前記サンプリングクロック生成回路のクロック入力ポートに接続し、前記マッピング変更回路は、前記第1のマッピングモードでは、前記第1、第2、第3、第4のシリアル／パラレル変換部から出力されるパラレルデータを、第1、第2、第3、第4のデータチャネルのパラレルデータとして出力し、前記第2のマッピングモードでは、前記第1のシリアル／パラレル変換部から出力されるパラレルデータを第4のデータチャネルにマッピングし、前記第4のシリアル／パラレル変換部から出力されるパラレルデータを第1のデータチャネルにマッピングしてもよい。

#### 【0017】

このようにすれば、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、受信したクロックについてはサンプリングクロック生成回路のクロック入力ポートに入力し、受信したシリアルデータについてはシリアル／パラレル変換回路のデータ入力ポートに入力できるようになり、クロックとシリアルデータの適正な入れ替えを実現できる。また第1、第4のデータチャネル間の入れ替えはマッピング変更回路により行われ、接続切り替え回路ではこれらの入れ替えを行わなくても済むため、回路を小規模化できる。

#### 【0018】

また本発明では、前記接続切り替え回路は、前記第2のマッピングモードでは、前記第1、第3、第4、第5のレシーバ回路の出力ポートを、各々、前記第1、第2、第3、第4のシリアル／パラレル変換部の前記第1、第2、第3、第4のデータ入力ポートに接続し、前記マッピング変更回路は、前記第2のマッピングモードでは、前記第2のシリアル／パラレル変換部から出力されるパラレルデータを第3のデータチャネルにマッピングし、前記第3のシリアル／パラレル変換部から出力されるパラレルデータを第2のデータチャネルにマッピングしてもよい。

#### 【0019】

このようにすれば、第2、第3のデータチャネル間の入れ替えはマッピング変更回路により行われ、接続切り替え回路ではこれらの入れ替えを行わなくても済むため、回路を小規模化できる。

#### 【0020】

また本発明では、前記接続切り替え回路は、前記第1のマッピングモードでは、シリアルデータを受信した前記第1のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、前記第1のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第1のデータセレクタと、前記第1のマッピングモードでは、シリアルデータを受信した前記第2のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、シリアルデータを受信した前記第3のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第2のデータセレクタと、前記第1のマッピングモードでは、前記第3のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマ

10

20

30

40

50

ツピングモードでは、シリアルデータを受信した前記第4のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第3のデータセレクタと、前記第1のマッピングモードでは、シリアルデータを受信した前記第5のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、前記第5のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力する第4のデータセレクタを含んでもよい。

#### 【0021】

このような第1～第4のデータセレクタを設ければ、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、シリアル／パラレル変換回路に入力されるデータの極性が反転してしまうなどの事態を防止できる。 10

#### 【0022】

また本発明では、前記接続切り替え回路は、前記第1のデータセレクタと前記第1のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第1のデータ遅延回路と、前記第2のデータセレクタと前記第2のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第2のデータ遅延回路と、前記第3のデータセレクタと前記第3のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第3のデータ遅延回路と、前記第4のデータセレクタと前記第4のシリアル／パラレル変換部の間に設けられ、受信シリアルデータの遅延時間を調整するための第4のデータ遅延回路を含んでもよい。

#### 【0023】

このような第1～第4の遅延回路を設ければ、データの信号極性については変化させないままで、データの遅延調整が可能になる。 20

#### 【0024】

また本発明では、前記接続切り替え回路は、前記第1のマッピングモードでは、クロックを受信した前記第4のレシーバ回路からの出力信号の非反転信号を選択して後段の回路に出力し、前記第2のマッピングモードでは、クロックを受信した前記第2のレシーバ回路からの出力信号の反転信号を選択して後段の回路に出力するクロックセレクタを含んでもよい。

#### 【0025】

このようなクロックセレクタを設ければ、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、サンプリングクロック生成回路に入力されるクロックの極性が反転してしまうなどの事態を防止できる。 30

#### 【0026】

また本発明では、前記接続切り替え回路は、前記クロックセレクタと前記サンプリングクロック生成回路の間に設けられ、受信クロックの遅延時間を調整するためのクロック遅延回路を含んでもよい。

#### 【0027】

このようなクロック遅延回路を設ければ、クロックの信号極性については変化させないままで、クロックの遅延調整が可能になる。

#### 【0028】

また本発明では、前記第4のレシーバ回路に接続される差動信号線を構成する第1、第2の信号線のハイインピーダンス状態を、前記第1のマッピングモードにおいて検出する第1のハイインピーダンス状態検出回路と、前記第2のレシーバ回路に接続される差動信号線を構成する第1、第2の信号線のハイインピーダンス状態を、前記第2のマッピングモードにおいて検出する第2のハイインピーダンス状態検出回路を含んでもよい。 40

#### 【0029】

このようにすれば、第1、第2の信号線がハイインピーダンス状態になった場合に、このハイインピーダンス状態を検出することが可能になり、高速シリアルインターフェース回路やその後段の回路の動作が不安定になるなどの事態を防止できる。

#### 【0030】

10

20

30

40

50

また本発明では、前記第1のハイインピーダンス状態検出回路は、前記第4のレシーバ回路に隣接して配置され、前記第2のハイインピーダンス状態検出回路は、前記第2のレシーバ回路に隣接して配置されてもよい。

【0031】

このようにすれば、レシーバ回路とハイインピーダンス状態検出回路の間の配線の引き回しを減らすことができるため、安定した検出動作を実現できる。

【0032】

また本発明では、前記第1、第2のハイインピーダンス状態検出回路の各々は、前記第1の信号線に接続される第1のプルアップ抵抗と、前記第2の信号線に接続される第2のプルアップ抵抗と、レシーバ回路のコモンモードの入力電圧範囲の最小電圧をVLとし、最大電圧をVHとした場合に、前記第1、第2の信号線の電圧が、前記最大電圧VHよりも高くなつたか否かを検出する電圧検出回路を含んでもよい。

10

【0033】

このようにすれば、第1、第2の信号線の電圧が最大電圧VHよりも高くなつたか否かを検出するだけで、ハイインピーダンス状態を検出できるようになる。

【0034】

また本発明では、前記第1又は第2のハイインピーダンス状態検出回路によりハイインピーダンス状態が検出された場合に、前記シリアル／パラレル変換回路及び前記マッピング変更回路を含むロジック回路ブロックの出力信号を、後段の回路に伝達されないようにマスクする出力マスク回路を含んでもよい。

20

【0035】

このようにすれば、差動信号線のハイインピーダンス状態に起因する不安定な出力信号が、後段の回路に伝達されるのを防止できる。

【0036】

また本発明は、上記のいずれかに記載の高速シリアルインターフェース回路と、前記高速シリアルインターフェース回路により受信されたデータ又はクロックに基づき動作するデバイスとを含む電子機器に関係する。

【発明を実施するための最良の形態】

【0037】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

30

【0038】

1. 第1の構成例

さて、高速シリアルインターフェース回路を有する集積回路装置では、その実装形態が、回路基板や表示パネルに対して表面実装になったり裏面実装になることで、パッドに対するシリアルデータやクロックのマッピングが変更される場合がある。例えば第1のマッピングモードではシリアルデータに割り当てられていたパッドが、第2のマッピングモードではクロックに割り当てられたり、第1のマッピングモードでは第1のデータチャネルのシリアルデータに割り当てられていたパッドが、第2のマッピングモードでは第2のデータチャネルのシリアルデータに割り当てられる場合がある。或いは第1のマッピングモードでは、正極性側のシリアルデータやクロックに割り当てられていたパッドが、第2のマッピングモードでは、負極性側のシリアルデータやクロックに割り当てられる場合がある。

40

【0039】

このようなマッピングモード（端子配列）の切り替え時に、集積回路装置の接続切り替え領域において全ての信号線の配線を一挙に入れ替えてしまうと、配線の引き回しが原因となって、接続切り替え領域のレイアウト面積が大幅に増加し、集積回路装置の大規模化や高コスト化を招く。また配線の引き回しによる寄生遅延時間が要因となって、サンプリングタイミングの設計等が困難になるおそれがある。

50

**【 0 0 4 0 】**

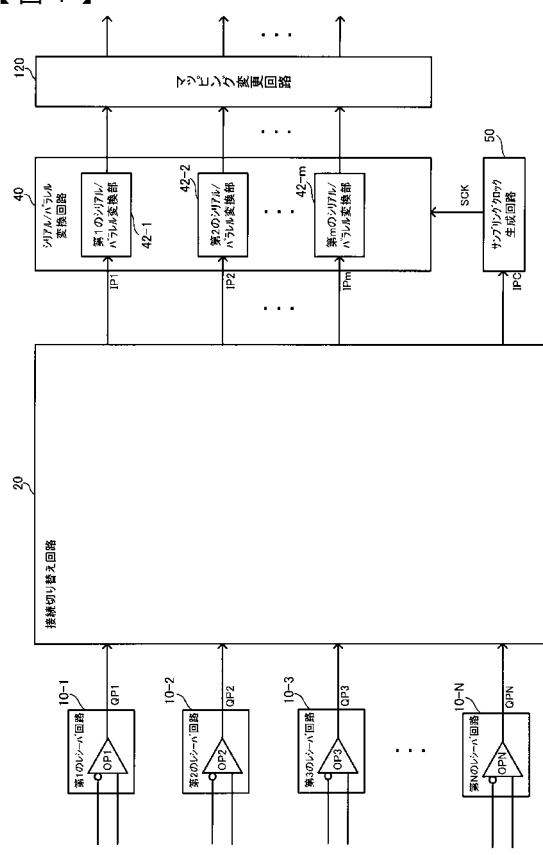

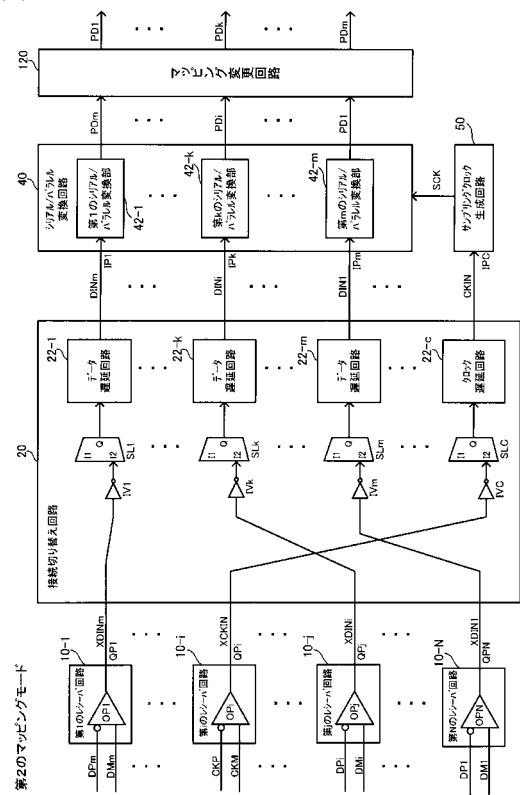

このような課題を解決できる本実施形態の高速シリアルインターフェース回路（データ転送制御装置、シリアルインターフェース回路）の第1の構成例を図1に示す。この高速シリアルインターフェース回路は、第1～第N（Nは2以上の整数）のレシーバ回路10-1～10-N、接続切り替え回路20、シリアル／パラレル変換回路40、サンプリングクロック生成回路50、マッピング変更回路120を含む。なお本実施形態の高速シリアルインターフェース回路は図1の構成に限定されず、その構成要素の一部を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

**【 0 0 4 1 】**

第1～第Nのレシーバ回路10-1～10-Nは、シリアルデータやクロックを受信するための回路である。具体的には、第1～第Nのレシーバ回路10-1～10-Nの各々は、差動信号線（シリアルバス）を介して差動信号のシリアルデータ又はクロックを受信して、受信シリアルデータ又は受信クロックを出力する。例えば第1～第Nのレシーバ回路10-1～10-Nは、差動増幅器OP1～OPN（コンパレータ）を含む。そして差動増幅器OP1～OPNの各々は、差動データ信号（DP、DM）又は差動クロック信号（CKP、CKM）を差動増幅して、例えばシングルエンド（CMOSレベル）の受信シリアルデータ（DIN）又は受信クロック（CKIN）を出力する。10

**【 0 0 4 2 】**

接続切り替え回路20（接続切り替え領域）は、第1～第Nのレシーバ回路10-1～10-Nとシリアル／パラレル変換回路40、サンプリングクロック生成回路50との間に設けられる。そして、これらの回路間での信号配線の接続の切り替えを行う。具体的には、端子配列のマッピングモードの切り替えに応じて、第1～第Nのレシーバ回路10-1～10-Nの出力ポートQ<sub>P1</sub>～Q<sub>PN</sub>と、シリアル／パラレル変換回路40のデータ入力ポートI<sub>P1</sub>～I<sub>Pm</sub>やサンプリングクロック生成回路50のクロック入力ポートI<sub>PC</sub>との間の接続の切り替えを行う。20

**【 0 0 4 3 】**

シリアル／パラレル変換回路40（データサンプリング回路）は、受信シリアルデータをパラレルデータに変換するための回路である。具体的には、クロックを受信したレシーバ回路からの受信クロックにより生成されるサンプリングクロックSCKを、サンプリングクロック生成回路50から受ける。そしてサンプリングクロックSCKに基づいて、受信シリアルデータをサンプリングして、パラレルデータに変換する。このシリアル／パラレル変換回路40は、例えばそのクロック端子にサンプリングクロックSCK（多相クロック）が入力され、そのデータ端子に受信シリアルデータが入力されるフリップフロップ回路などにより実現できる。30

**【 0 0 4 4 】**

シリアル／パラレル変換回路40は、各データチャネル毎に設けられる第1～第m（mはm<Nとなる整数）のシリアル／パラレル変換部42-1～42-mを含む。そしてシリアル／パラレル変換部42-1～42-mは、データ入力ポートI<sub>P1</sub>～I<sub>Pm</sub>から入力される各データチャネルの受信シリアルデータをパラレルデータに変換して、マッピング変更回路120などの後段の回路に出力する。40

**【 0 0 4 5 】**

サンプリングクロック生成回路50はサンプリングクロックSCKを生成するための回路である。具体的には、第1～第Nのレシーバ回路10-1～10-Nのうち、クロックを受信したレシーバ回路から受信クロックを受け、受信シリアルデータをサンプリングするためのサンプリングクロックSCKを生成して出力する。このサンプリングクロック生成回路50は、例えば、多相のサンプリングクロックを生成するDLL（Delayed Locked Loop）回路などにより実現できる。

**【 0 0 4 6 】**

マッピング変更回路120は、シリアル／パラレル変換回路40の後段側に設けられ、データチャネルのマッピングの変更を行う。50

**【0047】**

そして本実施形態では、差動信号線（パッド）に対するシリアルデータやクロックのマッピング（端子配列のマッピング）が変更された場合に、接続切り替え回路20が、クロックとシリアルデータを入れ替えるための信号線の接続の切り替えを行う。

**【0048】**

例えば、シリアルデータを受信していたレシーバ回路が、マッピングモード（端子配列）の切り替えによりクロックを受信するようになった場合には、そのレシーバ回路の出力ポート（Q P 1 ~ Q P N）の接続先を、シリアル／パラレル変換回路40のデータ入力ポート（I P 1 ~ I P m）から、サンプリングクロック生成回路50のクロック入力ポート（I P C）に切り替える。また、クロックを受信していたレシーバ回路が、マッピングモードの切り替えによりシリアルデータを受信するようになった場合には、そのレシーバ回路の出力ポート（Q P 1 ~ Q P N）の接続先を、サンプリングクロック生成回路50のクロック入力ポート（I P C）から、シリアル／パラレル変換回路40のデータ入力ポート（I P 1 ~ I P m）に切り替える。

10

**【0049】**

一方、マッピング変更回路120は、差動信号線に対するシリアルデータやクロックのマッピングが変更された場合に、シリアル／パラレル変換回路40から出力されるパラレルデータに対するデータチャネルのマッピングの変更を行う。

**【0050】**

例えば、データ入力ポートI P 1から入力される第1のデータチャネルの受信シリアルデータをパラレルデータに変換していた第1のシリアル／パラレル変換回路42-1に対して、マッピングモードの変更により第mのデータチャネルの受信シリアルデータが入力されたとする。この場合にはマッピング変更回路120は、第1のシリアル／パラレル変換回路42-1から出力されるパラレルデータを、例えば第mのデータチャネルにマッピングする（第1のデータチャネルから第mのデータチャネルにマッピングを変更する）。

20

**【0051】**

一方、データ入力ポートI P mから入力される第mのデータチャネルの受信シリアルデータをパラレルデータに変換していた第mのシリアル／パラレル変換回路42-mに対して、マッピングモードの変更により第1のデータチャネルの受信シリアルデータが入力されたとする。この場合にはマッピング変更回路120は、第mのシリアル／パラレル変換回路42-mから出力されるパラレルデータを、第1のデータチャネルにマッピングする（第mのデータチャネルから第1のデータチャネルにマッピングを変更する）。

30

**【0052】**

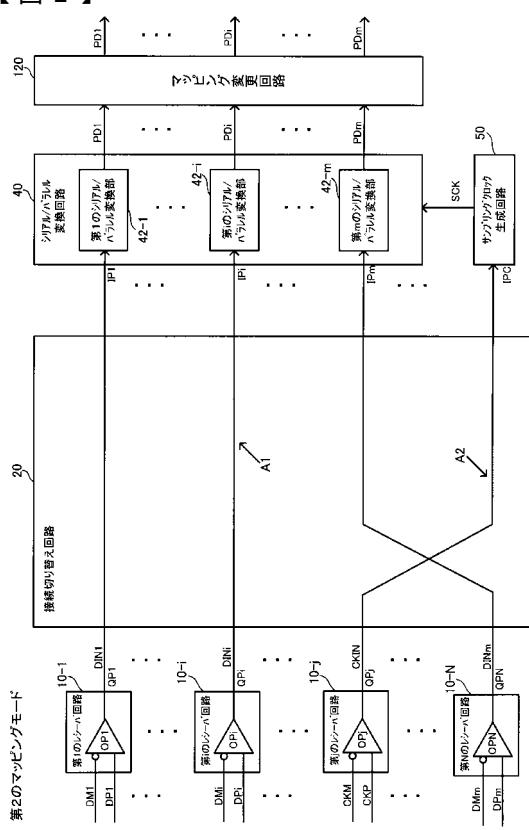

次に、図1の高速シリアルインターフェース回路の動作について、図2、図3を用いて更に詳細に説明する。図2、図3は、第1のマッピングモードから第2のマッピングモードに切り替わった場合の例である。

**【0053】**

図2、図3では、第1～第Nのレシーバ回路10-1～10-Nが、第iのレシーバ回路10-iと第jのレシーバ回路10-jを含む（1 i N。1 j N。iとjは異なる整数）。

40

**【0054】**

そして第iのレシーバ回路10-iは、図2の第1のマッピングモードではD P i、D M iのシリアルデータ（差動データ信号）を受信し、図3の第2のマッピングモードではC K P、C K Mのクロック（差動クロック信号）を受信する。

**【0055】**

一方、第jのレシーバ回路10-jは、図2の第1のマッピングモードではC K P、C K Mのクロックを受信し、図3の第2のマッピングモードではD P i、D M iのシリアルデータを受信する。

**【0056】**

なお第1、第2のマッピングモードでは信号極性の順番も入れ替わる。例えば図2の第

50

1のマッピングモードでは第jのレシーバ回路 $10-j$ に対して、図2の下から順番にCKP、CKMが入力されているが、図3の第2のマッピングモードでは第iのレシーバ回路 $10-i$ に対して、図3の上から順番にCKP、CKMが入力されている。

#### 【0057】

そして図2の第1のマッピングモードから図3の第2のマッピングモードに切り替わった場合に、接続切り替え回路20は、第iのレシーバ回路 $10-i$ の出力ポートQPiの接続先を、シリアル／パラレル変換回路40のデータ入力ポートIPiからサンプリングクロック生成回路50のクロック入力ポートIPCに切り替える。即ち第1のマッピングモードでは、図2のA1に示すように出力ポートQPiとデータ入力ポートIPiを接続していたのに対して、第2のマッピングモードでは、図3のB1に示すように出力ポートQPiとクロック入力ポートIPCを接続する。これによりシリアルデータとクロックの入れ替えが実現される。10

#### 【0058】

また接続切り替え回路20は、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、第jのレシーバ回路 $10-j$ の出力ポートQPjの接続先を、サンプリングクロック生成回路50のクロック入力ポートIPCからシリアル／パラレル変換回路40のデータ入力ポートIPkに切り替える。即ち第1のマッピングモードでは、図2のA2に示すように出力ポートQPjとクロック入力ポートIPCを接続していたのに対して、第2のマッピングモードでは、図3のB2に示すように出力ポートQPjとデータ入力ポートIPkを接続する。これによりクロックとシリアルデータの入れ替えが実現される。20

#### 【0059】

そしてマッピング変更回路120は、第1のマッピングモードから第2のマッピングモードに切り替わった場合に、第1～第mのシリアル／パラレル変換部 $42-1 \sim 42-m$ から出力される各パラレルデータに対するデータチャネルのマッピングを変更する。

#### 【0060】

即ちマッピング変更回路120は、図2の第1のマッピングモードでは、第1、第i、第mのシリアル／パラレル変換部 $42-1, 42-i, 42-m$ から出力されるパラレルデータPD1、PDi、PDmに対するデータチャネルのマッピングの変更は行わずに、そのまま後段の回路に出力する。30

#### 【0061】

一方、図3の第2のマッピングモードでは、第1、第k、第mのシリアル／パラレル変換部 $42-1, 42-k, 42-m$ からはパラレルデータPDm、PDi、PD1が出力される。そこでマッピング変更回路120は、パラレルデータPDm、PDi、PD1に対するデータチャネルのマッピングを、各々、第m、第i、第1のデータチャネルから第1、第k、第mのデータチャネルに変更する。これによりマッピング変更回路120からは、入力されたパラレルデータPDm、PDi、PD1に対して、各々、パラレルデータPD1、PDk、PDmが出力されるようになる。

#### 【0062】

以上のように本実施形態では、クロックとデータの入れ替えは接続切り替え回路20において行われ、データチャネル間の入れ替えはマッピング変更回路120において行われる。従って、接続切り替え回路20での配線の切り替えが最小限で済むため、配線を引き回す面積を最小限に抑えることができる。従って、レイアウト面積の増加や回路特性の悪化を最小限に抑えながらマッピングモードの切り替えを実現できる。40

#### 【0063】

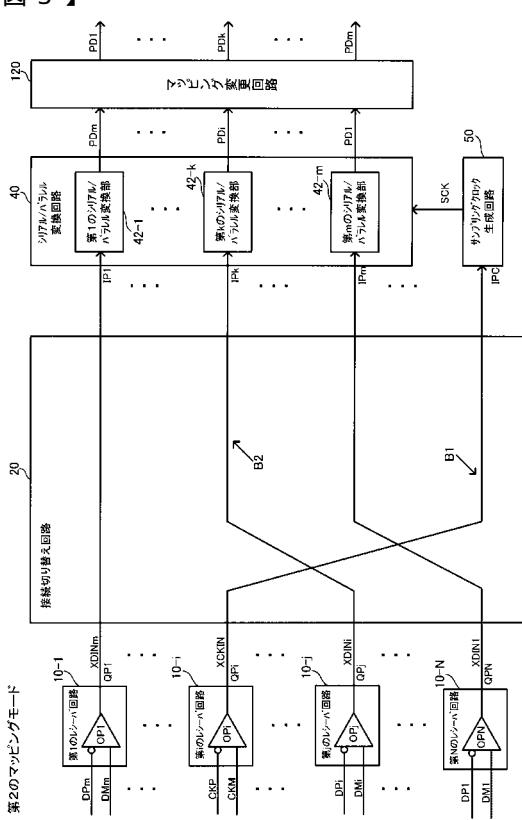

##### 2. 第2の構成例

図4、図5に高速シリアルインターフェース回路の第2の構成例を示す。図4、図5では、接続切り替え回路20が、データセレクタSL1～SLmやクロックセレクタSLCを含む。またデータ遅延回路 $22-1 \sim 22-m$ やクロック遅延回路 $22-c$ を含む。

#### 【0064】

50

例えば図4、図5のデータセレクタSL1は、DP1、DM1のシリアルデータを受信した第1のレシーバ回路10-1からの出力信号の非反転信号又は反転信号のいずれかを、第1、第2のマッピングモードの切り替えに応じて選択し、シリアル／パラレル変換回路40のデータ入力ポートIP1に対して出力する。

#### 【0065】

例えば図4の第1のマッピングモードでは、データセレクタSL1は、第1のレシーバ回路10-1の出力信号の非反転信号を選択して、データ入力ポートIP1に出力する。一方、図5の第2のマッピングモードでは、データセレクタSL1は、第1のレシーバ回路10-1の出力信号をインバータ回路IV1により反転した信号を選択して、データ入力ポートIP1に出力する。

10

#### 【0066】

即ち図4の第1のマッピングモードと図5の第2のマッピングモードでは、第1のレシーバ回路10-1に入力されるシリアルデータのデータチャネルのみならず、その極性も変更されている。

#### 【0067】

例えば図4の第1のマッピングモードでは、第1のレシーバ回路10-1の差動増幅器OP1の非反転入力端子に対して、第1のデータチャネルの正極性側のシリアルデータDP1が入力され、差動増幅器OP1の反転入力端子に対して、第1のデータチャネルの負極性側のシリアルデータDM1が入力される。これにより、第1のレシーバ回路10-1からは正極性（正論理）の受信シリアルデータDIN1が出力されることになる。従って、この場合にはデータセレクタSL1は、第1のレシーバ回路10-1からのDIN1の非反転信号が入力される第1の入力端子I1側を選択して、後段の回路に出力する。これにより、第1のシリアル／パラレル変換部42-1に対して、正極性の受信シリアルデータDIN1を入力できるようになる。

20

#### 【0068】

これに対して図5の第2のマッピングモードでは、差動増幅器OP1の非反転入力端子に対して、第mのデータチャネルの負極性側のシリアルデータDMmが入力され、差動増幅器OP1の反転入力端子に対して、第mのデータチャネルの正極性側のシリアルデータDPmが入力される。従って、第1のレシーバ回路10-1からは負極性（負論理）の受信シリアルデータXDINmが出力されることになる。従って、この場合にはデータセレクタSL1は、第1のレシーバ回路10-1からのXDINmの反転信号が入力される第2の入力端子I2側を選択して、後段の回路に出力する。これにより、第1のシリアル／パラレル変換部42-1に対して、正極性の受信シリアルデータDINmを入力できるようになる。

30

#### 【0069】

同様に図4、図5では、クロックセレクタSLCは、クロックを受信した第jのレシーバ回路10-j又は第iのレシーバ回路10-iからの出力信号の非反転信号又は反転信号のいずれかを、第1、第2のマッピングモードの切り替えに応じて選択して、サンプリングクロック生成回路50のクロック入力ポートIPCに対して出力する。

#### 【0070】

40

例えば図4の第1のマッピングモードでは、クロックセレクタSLCは、第jのレシーバ回路10-jの出力信号の非反転信号を選択して、クロック入力ポートIPCに出力する。一方、図5の第2のマッピングモードでは、クロックセレクタSLCは、第iのレシーバ回路10-iの出力信号をインバータ回路IVCにより反転した信号を選択して、クロック入力ポートIPCに出力する。

#### 【0071】

更に具体的には、図4の第1のマッピングモードでは、第jのレシーバ回路10-jの差動増幅器OPjの非反転入力端子に対して、正極性側のクロックCKPが入力され、差動増幅器OPjの反転入力端子に対して、負極性側のクロックCKMが入力される。これにより、第jのレシーバ回路10-jからは正極性（正論理）の受信クロックCKINが出力

50

されることになる。従って、この場合にはクロックセレクタ SLC は、第 j のレシーバ回路 10-j からの CKIN の非反転信号が入力される第 1 の入力端子 I1 側を選択して、後段の回路に出力する。これにより、サンプリングクロック生成回路 50 に対して正極性の受信クロック CKIN を入力できるようになる。

#### 【0072】

これに対して図 5 の第 2 のマッピングモードでは、第 i のレシーバ回路 10-i の差動増幅器 OPi の非反転入力端子に対して、負極性側のクロック CKM が入力され、差動増幅器 OPi の反転入力端子に対して、正極性側のクロック CKP が入力される。従って、第 i のレシーバ回路 10-i からは負極性（負論理）の受信クロック XCKIN が出力されることになる。従って、この場合にはクロックセレクタ SLC は、第 i のレシーバ回路 10-i からの XCKIN の反転信号が入力される第 2 の入力端子 I2 側を選択して、後段の回路に出力する。これにより、サンプリングクロック生成回路 50 に対して正極性の受信クロック CKIN を入力できるようになる。10

#### 【0073】

また図 4、図 5 では、接続切り替え回路 20 が含むデータ遅延回路 22-1 ~ 22-m が、データセレクタ SL1 ~ SLm とシリアル／パラレル変換回路 40（第 1 ~ 第 m のシリアル／パラレル変換部 42-1 ~ 42-m）の間に設けられる。そして受信シリアルデータの遅延時間を調整する。

#### 【0074】

また接続切り替え領域 20 が含むクロック遅延回路 22-c は、クロックセレクタ SLC とサンプリングクロック生成回路 50 の間に設けられる。そして受信クロックの遅延時間を調整する。20

#### 【0075】

このようなデータ遅延回路 22-1 ~ 22-m やクロック遅延回路 22-c を設ければ、例えば受信シリアルデータの中央付近にサンプリングポイントを設定する調整を容易化できる。

#### 【0076】

また図 5 では、負極性（負論理）のシリアルデータ XDINm ~ XDIN1 や負極性（負論理）のクロック XCKIN を、インバータ回路 IV1 ~ IVm、IVC で反転して、正極性（正論理）にした後の信号に対して、データ遅延回路 22-1 ~ 22-m やクロック遅延回路 22-c による遅延処理が行われる。従って、信号の立ち上がりや立ち下がりの遅延時間について、第 1、第 2 のマッピングモード間で整合を取りることが可能になり、適正な遅延処理を実現できる。30

#### 【0077】

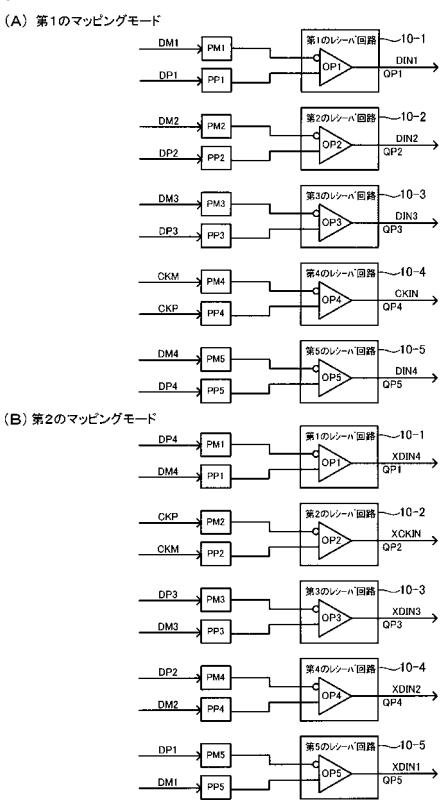

##### 3. 第 1、第 2 のマッピングモード

図 6 (A)、図 6 (B) に第 1、第 2 のマッピングモードの具体例を示す。図 6 (A)、図 6 (B) では、第 1 ~ 第 N のレシーバ回路 10-1 ~ 10-N として、第 1、第 2、第 3、第 4、第 5 のレシーバ回路 10-1、10-2、10-3、10-4、10-5 が設けられる。

#### 【0078】

そして図 6 (A) の第 1 のマッピングモードでは、第 1、第 2、第 3、第 5 のレシーバ回路 10-1、10-2、10-3、10-5 が、各々、第 1、第 2、第 3、第 4 のデータチャネルのシリアルデータ DP1 / DM1、DP2 / DM2、DP3 / DM3、DP4 / DM4 を受信する。即ちこれらのシリアルデータを、差動パッドペア PP1 / PM1、PP2 / PM2、PP3 / PM3、PP5 / PM5 を介して受信して、受信シリアルデータ DIN1、DIN2、DIN3、DIN4 を出力する。40

#### 【0079】

また第 1 のマッピングモードでは、第 4 のレシーバ回路 10-4 がクロック CKP / CKM を受信する。即ちクロック CKP / CKM を差動パッドペア PP4 / PM4 を介して受信して、受信クロック CKIN を出力する。

#### 【0080】

50

20

30

40

50

一方、図6(B)の第2のマッピングモードでは、第1、第3、第4、第5のレシーバ回路10-1、10-3、10-4、10-5が、各々、第4、第3、第2、第1のデータチャネルのシリアルデータDP4/DM4、DP3/DM3、DP2/DM2、DP1/DM1を受信する。即ちこれらのシリアルデータを、差動パッドペアPP1/PM1、PP3/PM3、PP4/PM4、PP5/PM5を介して受信して、受信シリアルデータXDIN4、XDIN3、XDIN2、XDIN1を出力する。このように第1、第2のマッピングモードでは、シリアルデータやクロックのマッピングが、例えば第3の受信回路10-3を中心線として線対称にミラー反転されている。

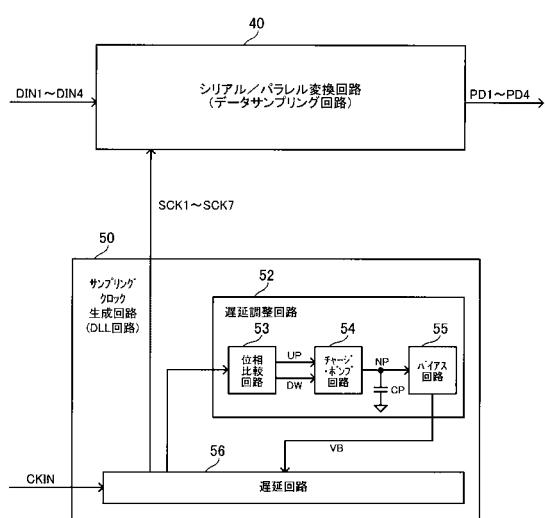

## 【0081】

4.サンプリングクロック生成回路、シリアル／パラレル変換回路

10

次にサンプリングクロック生成回路50の具体例について図7、図8を用いて説明する。なお本実施形態のサンプリングクロック生成回路50の構成は図7に限定されず、その構成要素の一部を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば多相ではないサンプリングクロックを生成する構成のサンプリングクロック生成回路50を採用してもよい。

## 【0082】

図7のサンプリングクロック生成回路50(DLL回路)は、遅延調整回路52と遅延回路56を含む。

## 【0083】

遅延回路56は、受信クロックCKINを受け、CKINを遅延させる回路である。そして図8に示すように、位相が互いに異なる多相のサンプリングクロックSCK1～SCK7を生成する。具体的には、この遅延回路56は、カスケード接続された複数段の遅延バッファ(遅延ユニット)を含む。そして、これらの複数段の遅延バッファにより、クロックCKINを遅延させて、各遅延バッファの出力ノードからバッファ等を介して多相のサンプリングクロックSCK1～SCK7を出力する。

20

## 【0084】

遅延調整回路52は、遅延回路56での遅延時間の調整を行う。具体的には、クロック遅延時間がロックされた多相のサンプリングクロックSCK1～SCK7を生成するための位相比較処理を行う。この遅延調整回路52は、位相比較回路53、チャージ・ポンプ回路54、バイアス回路55を含む。

30

## 【0085】

位相比較回路53は、遅延回路56での多相クロックのクロック遅延時間をロックするための位相比較処理を行う。即ち、サンプリングクロックの例えば立ち上がりエッジ間の位相差が固定されるように遅延時間をロックする。また、この際に、ハーモニック・ロックが発生しないように遅延時間のロックを行う。

## 【0086】

更に具体的には位相比較回路53には、遅延回路56の各遅延バッファが出力するクロック(多相クロック、中間出力クロック)のうちの何本かのクロックが入力される。そしてこれらのクロックに基づいて、内部信号を生成し、これらの内部信号に基づいて信号UP、DWを生成して、チャージ・ポンプ回路54に出力する。

40

## 【0087】

チャージ・ポンプ回路54は、位相比較回路53からの信号UP、DWに基づいて、チャージ・ポンプノードNPへのチャージ・ポンプ動作を行う。またバイアス回路55は、ノードNPのチャージ・ポンプ電圧に基づいて、遅延調整用のバイアス電圧VBを生成して、遅延回路56に出力する。そして遅延回路56は、バイアス回路55からのバイアス電圧VBに応じたクロック遅延時間で、クロックCKINを遅延させて、多相のサンプリングクロックSCK1～SCK7を生成して、シリアル／パラレル変換回路40に出力する。

## 【0088】

シリアル／パラレル変換回路40は、多相のサンプリングクロックSCK1～SCK7

50

の例えは立ち上がりエッジで、各データチャネルの受信シリアルデータDIN1～DIN4の各ビットをサンプリングする。そして例えは7ビットの各パラレルデータPD1～PD4に変換して、後段の回路に出力する。

#### 【0089】

例えは図8において、DIN1、DIN2、DIN3、DIN4は、第1、第2、第3、第4のデータチャネルの受信シリアルデータである。

#### 【0090】

そして第1のデータチャネルの受信シリアルデータDIN1は、RT7、RT6、RT4、RT3、RT2、RT1、RT0のビットにより構成され、第1のマッピングモードでは図9の第1のシリアル／パラレル変換部42-1により7ビットのパラレルデータPD1に変換される（第2のマッピングモードでは第4のシリアル／パラレル変換部42-4により変換される）。第2のデータチャネルの受信シリアルデータDIN2は、RT18、RT15、RT14、RT13、RT12、RT9、RT8のビットにより構成され、第1のマッピングモードでは第2のシリアル／パラレル変換部42-2により7ビットのパラレルデータPD2に変換される。第3のデータチャネルの受信シリアルデータDIN3は、RT26、RT25、RT24、RT22、RT21、RT20、RT19のビットにより構成され、第1のマッピングモードでは第3のシリアル／パラレル変換部42-3により7ビットのパラレルデータPD3に変換される。第4のデータチャネルの受信シリアルデータDIN4はRT23、RT17、RT16、RT11、RT10、RT5、RT27により構成され、第1のマッピングモードでは第4のシリアル／パラレル変換部42-4により7ビットのパラレルデータPD4に変換される。

10

#### 【0091】

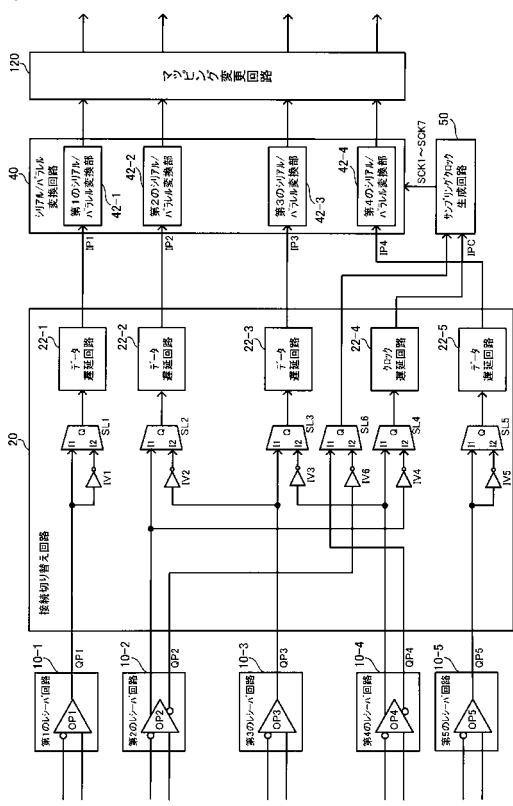

##### 5. 第3の構成例

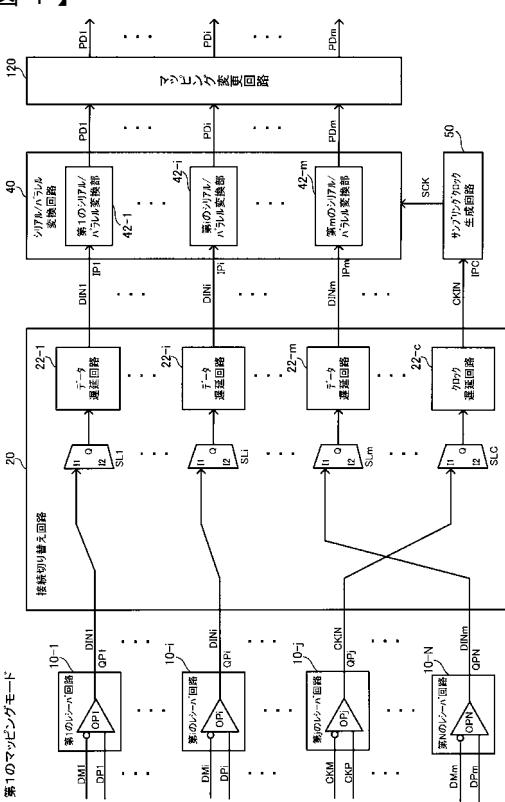

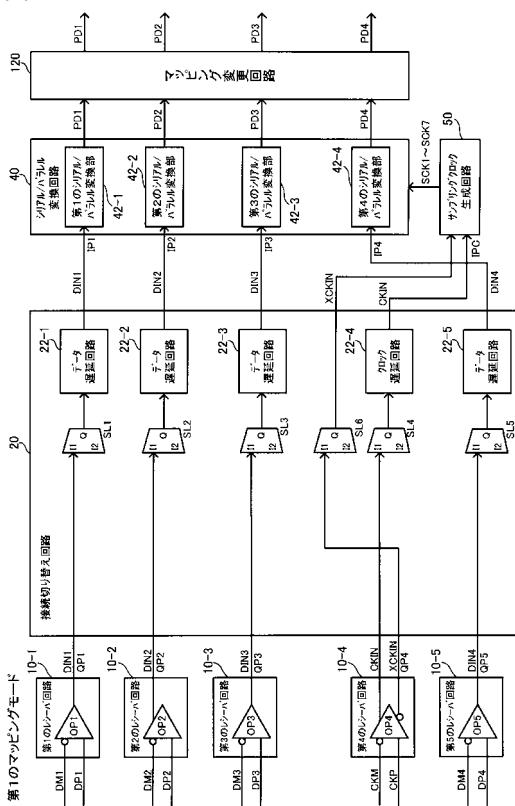

図9に本実施形態の高速シリアルインターフェース回路の具体例である第3の構成例を示し、図10、図11に第1、第2のマッピングモードでの動作説明図を示す。

#### 【0092】

図9の高速シリアルインターフェース回路は、第1～第5のレシーバ回路10-1～10-5、接続切り替え回路20、シリアル／パラレル変換回路40、サンプリングクロック生成回路50、マッピング変更回路120を含む。

#### 【0093】

図9に示すように接続切り替え回路20は、データセレクタSL1、SL2、SL3、SL5や、クロックセレクタSL4、SL6や、反転信号を生成するためのインバータ回路IV1～IV6を含む。またデータ遅延回路22-1、22-2、22-3、22-5やクロック遅延回路22-4を含む。

30

#### 【0094】

接続切り替え回路20は、図10の第1のマッピングモードでは、第1、第2、第3、第5のレシーバ回路10-1、10-2、10-3、10-5の出力ポートQ<sub>P</sub>1、Q<sub>P</sub>2、Q<sub>P</sub>3、Q<sub>P</sub>5を、第1、第2、第3、第4のシリアル／パラレル変換部42-1、42-2、42-3、42-4のデータ入力ポートIP1、IP2、IP3、IP4に接続する。即ち、セレクタSL1、SL2、SL3、SL5やデータ遅延回路22-1、22-2、22-3、22-5を介して、出力ポートQ<sub>P</sub>1、Q<sub>P</sub>2、Q<sub>P</sub>3、Q<sub>P</sub>5をデータ入力ポートIP1、IP2、IP3、IP4に接続する。また第4のレシーバ回路10-4の出力ポートQ<sub>P</sub>4を、サンプリングクロック生成回路50のクロック入力ポートIPCに接続する。即ち、セレクタSL4、SL6やクロック遅延回路22-4を介して、出力ポートQ<sub>P</sub>4をクロック入力ポートIPCに接続する。

40

#### 【0095】

なおサンプリングクロック生成回路50には、正極性（立ち上がりエッジ）と負極性（立ち下がりエッジ）のクロック入力ポートが設けられている。そして正極性側のクロック入力ポートはクロック遅延回路22-4を介してクロックセレクタSL4の出力に接続され、負極性側のクロック入力ポートはクロックセレクタSL6の出力に接続される。

50

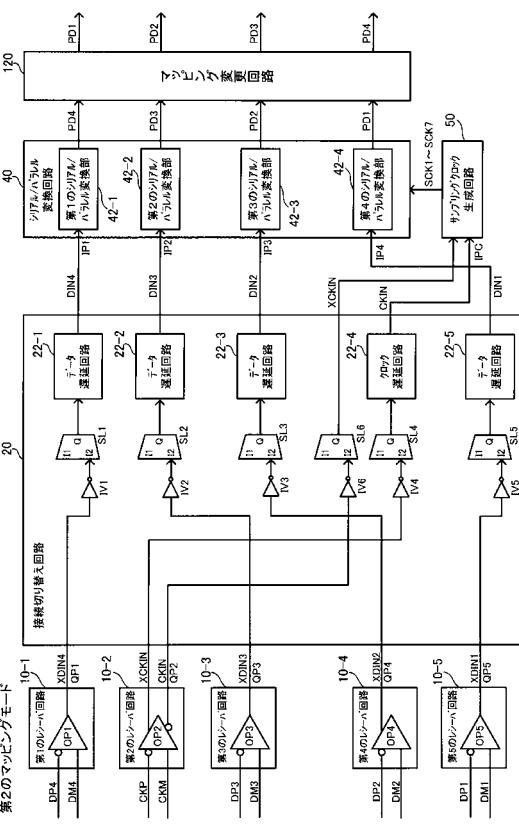

**【0096】**

接続切り替え回路20は、図11の第2のマッピングモードでは、第2のレシーバ回路10-2の出力ポートQ P 2を、サンプリングクロック生成回路50のクロック入力ポートI P Cに接続する。即ち、セレクタS L 4、S L 6やクロック遅延回路22-4を介して、出力ポートQ P 2をクロック入力ポートI P Cに接続する。

**【0097】**

更に具体的には接続切り替え回路20は、図11の第2のマッピングモードでは、第1、第3、第4、第5のレシーバ回路10-1、10-3、10-4、10-5の出力ポートQ P 1、Q P 3、Q P 4、Q P 5を、各々、第1、第2、第3、第4のシリアル／パラレル変換部42-1、42-2、42-3、42-4のデータ入力ポートI P 1、I P 2、I P 3、I P 4に接続する。即ちセレクタS L 1、S L 2、S L 3、S L 5やデータ遅延回路22-1、22-2、22-3、22-5を介して、出力ポートQ P 1、Q P 3、Q P 4、Q P 5をデータ入力ポートI P 1、I P 2、I P 3、I P 4に接続する。

10

**【0098】**

マッピング変更回路120は、図10の第1のマッピングモードでは、第1、第2、第3、第4のシリアル／パラレル変換部42-1、42-2、42-3、42-4から出力されるパラレルデータP D 1、P D 2、P D 3、P D 4を、第1、第2、第3、第4のデータチャネルのパラレルデータとして、そのまま出力する。

**【0099】**

一方、マッピング変更回路120は、図11の第2のマッピングモードでは、第1のシリアル／パラレル変換部42-1から出力されるパラレルデータP D 4を、第4のデータチャネルにマッピングする（第4のデータチャネルにマッピングを変更して出力する）。また第4のシリアル／パラレル変換部42-4から出力されるパラレルデータP D 1を、第1のデータチャネルにマッピングする（第1のデータチャネルにマッピングを変更して出力する）。

20

**【0100】**

更に具体的にはマッピング変更回路120は、図11の第2のマッピングモードでは、第2のシリアル／パラレル変換部42-2から出力されるパラレルデータP D 3を第3のデータチャネルにマッピングし、第3のシリアル／パラレル変換部42-3から出力されるパラレルデータP D 2を第2のデータチャネルにマッピングする。

30

**【0101】**

このようにすれば、第1のマッピングモードから第2のマッピングモードに切り替わった場合にも、常にマッピング変更回路120の同じポートから同じデータチャネルのパラレルデータが出力されるようになり、後段の回路の処理を簡素化できる。

**【0102】**

また図9の第3の構成例では、接続切り替え回路20が第1、第2、第3、第4のデータセレクタS L 1、S L 2、S L 3、S L 5やクロックセレクタS L 4、S L 6を含む。

**【0103】**

そして第1のデータセレクタS L 1は、図10の第1のマッピングモードでは、シリアルデータを受信した第1のレシーバ回路10-1からの出力信号の非反転信号を選択して後段の回路（データ遅延回路22-1、第1のシリアル／パラレル変換部42-1）に出力する。一方、図11の第2のマッピングモードでは、第1のレシーバ回路10-1からの出力信号の反転信号（I V 1で反転した信号）を選択して後段の回路に出力する。

40

**【0104】**

また第2のデータセレクタS L 2は、第1のマッピングモードでは、シリアルデータを受信した第2のレシーバ回路10-2からの出力信号の非反転信号を選択して後段の回路（データ遅延回路22-2、第2のシリアル／パラレル変換部42-2）に出力する。一方、第2のマッピングモードでは、シリアルデータを受信した第3のレシーバ回路10-3からの出力信号の反転信号を選択して後段の回路に出力する。

**【0105】**

また第3のデータセレクタS L 3は、第1のマッピングモードでは、シリアルデータを受信した第3のレシーバ回路10-3からの出力信号の非反転信号を選択して後段の回路（データ遅延回路22-3、第3のシリアル／パラレル変換部42-3）に出力する。一方、第2のマッピングモードでは、シリアルデータを受信した第4のレシーバ回路10-4からの出力信号の反転信号を選択して後段の回路に出力する。

#### 【0106】

また第4のデータセレクタS L 5は、第1のマッピングモードでは、シリアルデータを受信した第5のレシーバ回路10-5からの出力信号の非反転信号を選択して後段の回路（データ遅延回路22-5、第4のシリアル／パラレル変換部42-4）に出力する。一方、第2のマッピングモードでは、第5のレシーバ回路10-5からの出力信号の反転信号を選択して後段の回路に出力する。10

#### 【0107】

またクロックセレクタS L 4は、図10の第1のマッピングモードでは、クロックを受信した第4のレシーバ回路10-4からの出力信号の非反転信号を選択して後段の回路に出力する。一方、図11の第2のマッピングモードでは、クロックを受信した第2のレシーバ回路10-2からの出力信号の反転信号を選択して後段の回路に出力する。

#### 【0108】

また図9～図11の第3の構成例では、接続切り替え回路20は、データ遅延回路22-1、22-2、22-3、22-5やクロック遅延回路22-4を含む。

#### 【0109】

データ遅延回路22-1は、第1のデータセレクタS L 1と第1のシリアル／パラレル変換部42-1の間に設けられ、受信シリアルデータの遅延時間を調整する。データ遅延回路22-2は、第2のデータセレクタS L 2と第2のシリアル／パラレル変換部42-2の間に設けられ、受信シリアルデータの遅延時間を調整する。データ遅延回路22-3は、第3のデータセレクタS L 3と第3のシリアル／パラレル変換部42-3の間に設けられ、受信シリアルデータの遅延時間を調整する。データ遅延回路22-5は、第4のデータセレクタS L 5と第4のシリアル／パラレル変換部42-4の間に設けられ、受信シリアルデータの遅延時間を調整する。20

#### 【0110】

クロック遅延回路22-4は、クロックセレクタS L 4とサンプリングクロック生成回路50の間に設けられ、受信クロックの遅延時間を調整する。30

#### 【0111】

これらのデータ遅延回路22-1、22-2、22-3、22-5やクロック遅延回路22-4によりシリアルデータやクロックの遅延時間を調整することで、図8の受信シリアルデータDIN1～DIN4の各ビットの中央付近で、データをサンプリングしてパラレルデータに変換することが可能になる。

#### 【0112】

##### 6. 第4の構成例

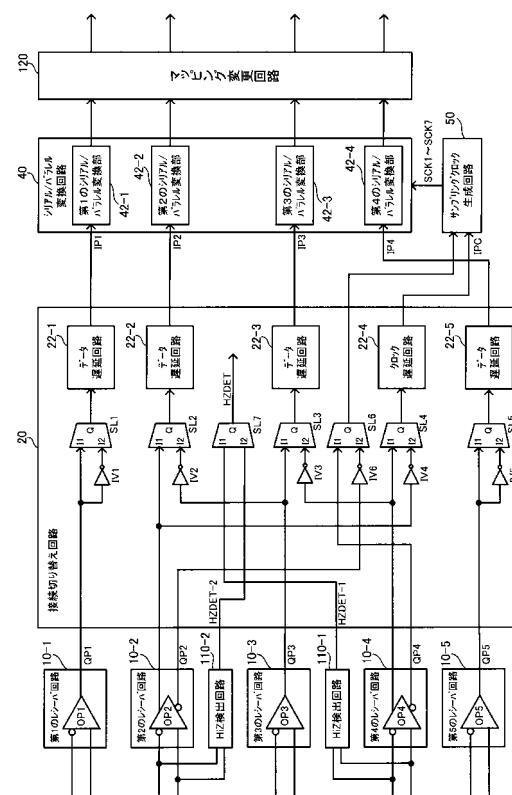

図12に本実施形態の第4の構成例を示す。図12では図9の構成に対して、HIZ検出回路110-1、110-2や、これらのHIZ検出回路110-1、110-2の出力が接続されるセレクタS L 7が更に設けられている。40

#### 【0113】

具体的には、HIZ検出回路110-1（第1のハイインピーダンス状態検出回路）は、第4のレシーバ回路10-4に接続される差動信号線を構成する第1、第2の信号線（第1のマッピングモードでのCKP、CKMの信号線）のハイインピーダンス状態を、第1のマッピングモードにおいて検出する。例えばトランスマッタ回路がこれらの第1、第2の信号線を駆動しないことで、これらの第1、第2の信号線がハイインピーダンス状態になった場合に、この状態を検出する。そして第1の検出信号HZDET-1をアクティブ（Hレベル）にする。

#### 【0114】

一方、HiZ検出回路110-2(第2のハイインピーダンス状態検出回路)は、第2のレシーバ回路10-2に接続される差動信号線を構成する第1、第2の信号線(第2のマッピングモードでのCKP、CKMの信号線)のハイインピーダンス状態を、第2のマッピングモードにおいて検出する。例えばトランスマッタ回路がこれらの第1、第2の信号線を駆動しないことで、これらの第1、第2の信号線がハイインピーダンス状態になった場合に、この状態を検出する。そして第2の検出信号HZDET-2をアクティブ(Hレベル)にする。

#### 【0115】

セレクタSL7は、第1のマッピングモードでは、HiZ検出回路110-1からの第1の検出信号HZDET-1を選択して、検出信号HZDETとして出力する。一方、第2のマッピングモードでは、HiZ検出回路110-2からの第2の検出信号HZDET-2を選択して、検出信号HZDETとして出力する。10

#### 【0116】

なお図12に示すように、HiZ検出回路110-1は第4のレシーバ回路10-4に隣接して配置される。一方、HiZ検出回路110-2は第2のレシーバ回路10-2に隣接して配置される。このような配置にすれば、ハイインピーダンス状態の検出信号線を引き回さなくて済むため、ハイインピーダンス状態の適正な検出が可能になる。また無駄な配線の引き回しが減るため、レイアウト面積を縮小化できる。

#### 【0117】

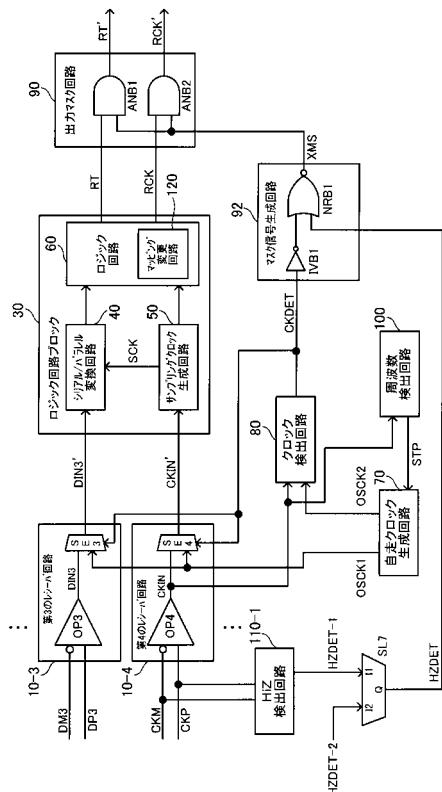

図13に、図12の更に詳細な構成例を示す。なお以下では説明の簡素化のためにマッピングモードが第1のマッピングモードである場合について主に例により説明する。20

#### 【0118】

図13においてロジック回路ブロック30は、シリアル/パラレル変換回路40やサンプリングクロック生成回路50やロジック回路60を含み、ロジック回路60はマッピング変更回路120などを含む。

#### 【0119】

自走クロック生成回路70は、外部供給クロックではない自走のクロックOSC1、OSC2を生成して出力する。具体的には、リングオシレータなどの自走の発振回路を内蔵し、電源投入後に開始する発振動作により、自走の発振クロックを生成する。また必要であれば、発振クロックを分周して、所望の周波数の自走クロックを出力する。30

#### 【0120】

クロック検出回路80は、差動信号線を介してクロックが転送されているか否かを検出するための回路である。具体的には、例えば第1のマッピングモードでは、第4のレシーバ回路20-4からの受信クロックCKINと自走クロック生成回路70からの自走クロックOSC2を比較して、差動信号線でのクロックの転送・非転送を検出する。そしてクロックが転送されていると判定した場合には、クロックの検出信号CKDETをアクティブ(例えばHレベル)にする。

#### 【0121】

更に具体的にはクロック検出回路80は、受信クロックCKINの周波数と自走クロックOSC2の周波数を比較する。そして受信クロックCKINの周波数の方が自走クロックOSC2の周波数よりも低い場合に、差動信号線を介してクロックが転送されていないと判定し、検出信号CKDETを非アクティブ(例えばLレベル)にする。40

#### 【0122】

周波数検出回路100は、受信クロックCKINの周波数を検出する。そして受信クロックCKINの周波数が所与の周波数よりも高くなった場合に、自走クロック生成回路70の動作停止信号STOPをアクティブにする。これにより自走クロック生成回路70が含む発振回路が発振動作を停止し、自走クロックの生成が停止する。

#### 【0123】

マスク信号生成回路92は、インバータ回路INV1とNOR回路NRB1を含み、クロック検出信号80からの検出信号CKDETと、HiZ検出回路110-1のセレクタS50

L 7 からの検出信号 H Z D E T が入力される。そして検出信号 C K D E T が非アクティブ (L レベル) になった場合や、検出信号 H Z D E T がアクティブ (H レベル) になった場合に、マスク信号 X M S (負論理) をアクティブ (L レベル) にする。

#### 【 0 1 2 4 】

出力マスク回路 9 0 は、ロジック回路ブロック 3 0 の出力信号 R T (パラレルデータ) 、 R C K (クロック) のマスクを行う。具体的には、クロック検出回路 8 0 により、差動信号線でのクロックの非転送が検出された場合や、 H i Z 検出回路 1 1 0 -1 (1 1 0 -2) により差動信号線のハイインピーダンス状態が検出された場合に、ロジック回路ブロック 3 0 の出力信号 R T 、 R C K を、後段の回路に伝達されないようにマスクする。

#### 【 0 1 2 5 】

例えれば出力マスク回路 9 0 は、 A N D 回路 A N B 1 、 A N B 2 (論理積回路) を含み、 A N B 1 、 A N B 2 の第 1 の入力端子にはロジック回路ブロック 3 0 の出力信号 R T 、 R C K が入力され、 A N B 1 、 A N B 2 の第 2 の入力端子にはマスク信号 X M S (負論理) が入力される。従って、差動信号線でのクロックの非転送が検出されたり、差動信号線のハイインピーダンス状態が検出されて、マスク信号 X M S が L レベルになると、 A N D 回路 A N B 1 、 A N B 2 の出力信号 R T ' 、 R C K ' は L レベルに固定される。これにより、ロジック回路ブロック 3 0 の出力信号 R T 、 R C K はマスクされて、後段の回路に伝達されないようにになる。

#### 【 0 1 2 6 】

例えればクロックの非転送時に C K P 、 C K M の信号線が共に L レベル等に固定されると、第 4 のレシーバ回路 2 0 -4 の差動増幅器 O P 4 の非反転入力端子及び反転入力端子が共に L レベルに固定されてしまう。そしてこのように C K P 、 C K M の信号線が L レベルに固定された状態で C K P 、 C K M にノイズが重畠されると、差動増幅器 O P 4 によりノイズが増幅されてクロックのように振る舞い、高速シリアルインターフェース回路やその後段の回路が誤動作してしまう事態が生じる。

#### 【 0 1 2 7 】

一方、 C K P 、 C K M の信号線に、小振幅の差動のクロック信号が存在しない場合には、クロックが転送されていない状況であり、このような状況では、高速シリアルインターフェース回路からの出力信号 R T 、 R C K を後段の回路に出力することは望ましくなく、出力する必要もない。

#### 【 0 1 2 8 】

そこで図 1 3 では、このような C K P 、 C K M のクロックの非転送時には、ロジック回路ブロック 3 0 の出力信号 R T 、 R C K 自体を、出力マスク回路 9 0 によりマスクしてしまう。このようにすれば、例えは C K P 、 C K M の信号線のノイズが増幅されてクロックのように振る舞い、高速シリアルインターフェース回路が予期しない動作を行った場合にも、不安定な出力信号 R T 、 R C K は後段の回路には伝達されないようになり、 C K P 、 C K M のノイズ等に起因する誤動作の発生を効果的に防止できる。

#### 【 0 1 2 9 】

そして図 1 3 では、このようなクロックの転送・非転送の検出を、受信クロック C K I N と自走クロック O S C K 2 の比較により実現している。

#### 【 0 1 3 0 】

例えればクロックの転送・非転送の検出を、クロックの包絡線等を抽出することで検出する手法も考えられる。しかしながら、この手法によると、複雑な回路構成のアナログ回路が必要になり、回路の大規模化や消費電力の増加や回路設計の複雑化を招く。

#### 【 0 1 3 1 】

この点、図 1 3 のように受信クロック C K I N と自走クロック O S C K 2 を比較する手法によれば、クロックの包絡線を抽出する手法に比べて、簡素な構成の回路でクロックの転送・非転送を検出できるため、回路の小規模化や低消費電力化を実現できる。

#### 【 0 1 3 2 】

また、クロック検出回路 8 0 によりクロックの非転送を検出する手法のみでは、トラン

10

20

30

40

50

スミック回路側がCKP、CKMの信号線を駆動しないことでこれらの信号線がハイインピーダンス状態になった場合に、不安定状態になった出力信号RT、RCKをマスクできないおそれがある。

#### 【0133】

この点、図13のようなHIZ検出回路110-1を設ければ、クロックの非転送時のみならず、トランスマッタ回路側の非駆動によりCKP、CKMの信号線がハイインピーダンス状態になった場合にも、出力信号RT、RCKをマスクでき、後段の回路が誤動作するのを防止できる。

#### 【0134】

また図13では、第4のレシーバ回路20-4はセレクタSE4を含む。このセレクタSE4は、その第1の入力端子に受信クロックCKINが入力され、その第2の入力端子に自走クロックOSCK1が入力される。そしてクロック検出回路80からの検出信号CKDETに基づいて、受信クロックCKIN又は自走クロックOSCK1のいずれかを選択して出力する。即ち、検出信号CKDETがアクティブ(Hレベル)である場合には受信クロックCKINの方を選択して、CKIN'として出力し、検出信号CKDETが非アクティブ(Lレベル)である場合には、自走クロックOSCK1の方を選択して、CKIN'としてロジック回路ブロック30に出力する。

#### 【0135】

同様に、第3のレシーバ回路10-3はセレクタSE3を含む。このセレクタSE3は、その第1の入力端子に受信シリアルデータDIN3が入力され、その第2の入力端子に自走クロックOSCK1が入力される。そしてクロック検出回路80からの検出信号CKDETに基づいて、受信シリアルデータDIN3又は自走クロックOSCK1のいずれかを選択して出力する。即ち、検出信号CKDETがアクティブである場合には受信シリアルデータDIN3の方を選択して、DIN3'として出力し、検出信号が非アクティブである場合には、自走クロックOSCK1の方を選択して、DIN3'としてロジック回路ブロック30に出力する。

#### 【0136】

図13の構成によれば、差動信号線でのクロックが停止して、CKP、CKMのクロックの非転送がクロック検出回路80により検出されると、自走クロック生成回路70からの自走クロックOSCK1が、受信クロックCKINや受信シリアルデータDIN3の代わりにロジック回路ブロック30に入力される。このため、高速シリアルインターフェース回路のイネーブル信号がアクティブになった後に、CKP、CKMのクロックやDP3、DM3のデータが、長時間、非転送状態のままになった場合にも、自走クロックOSCK1が擬似的なクロック、データとしてロジック回路ブロック30に供給されるようになる。この時、検出信号CKDETが非アクティブになると出力マスク回路90により出力信号RT、RCKがマスクされるため、不適切な出力信号が後段の回路に伝達されることもない。従って図13の構成によれば、ロジック回路ブロック30のトランジスタのしきい値が、トランジスタの負バイアス温度不安定性(NBTI: Negative Bias Temperature Instability)等によりシフトしてしまうのを低減でき、信頼性や設計マージンの向上を図れる。

#### 【0137】

特に図13では、出力信号のマスクのために設けられた自走クロック生成回路70やクロック検出回路80を有効活用して、NBTIの低減に利用している点に特徴がある。即ち図13では、自走クロック生成回路70からの自走クロックOSCK2とクロック検出回路80により、CKP、CKMの非転送を検出して出力信号RT、RCKをマスクすると共に、このようにCKP、CKMの非転送が検出された時に、自走クロックOSCK1をセレクタSE4、SE3を介してロジック回路ブロック30に供給することで、NBTIの低減を実現している。従って、小規模で簡素な回路構成で、出力信号のマスクとNBTIの低減の両方を実現できる。

#### 【0138】

10

20

30

40

50

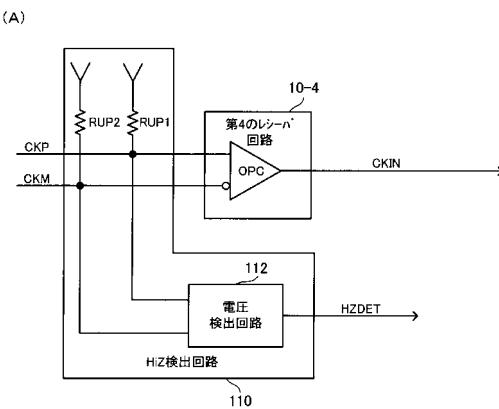

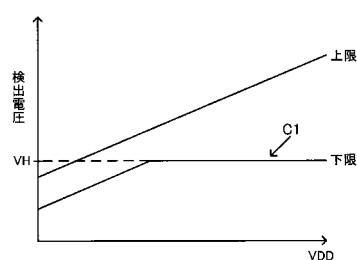

図14(A)にHiZ検出回路110(110-1、110-2)の構成例を示す。このHiZ検出回路110は、CKPの信号線に接続される第1のプルアップ抵抗RUP1と、CKMの信号線に接続される第2のプルアップ抵抗RUP2を含む。これらのプルアップ抵抗RUP1、RUP2は、VDDとCKP、CKMのクロック信号線の間に設けられる。

#### 【0139】

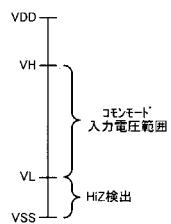

HiZ検出回路110は電圧検出回路112を含む。この電圧検出回路112は、レシーバ回路のコモンモードの入力電圧範囲(同相入力電圧範囲)の最小電圧をVLとし、最大電圧をVHとした場合に、CKP、CKMの信号線の電圧が、最大電圧VHよりも高くなつたか否かを検出する。例えば図14(B)に示すように、VL～VHがコモンモード入力電圧範囲である場合に、CKP、CKMの信号線の電圧がVHよりも高い場合(VH～VDDの間である場合)に、検出信号HZDET(HZDET-1、HZDET-2)をアクティブにする。

#### 【0140】

即ち、CKP、CKMのクロックが転送されている状態では、コモンモード入力電圧範囲VL～VH内の小振幅の差動信号がレシーバ回路に入力される。従って、CKP、CKMの電圧が最大電圧VHよりも高い場合には、クロックが転送されている状態ではないと判断できる。そしてトランスマッタ回路側が信号線を駆動していない状態では、これらの信号線はプルアップ抵抗RUP1、RUP2によりVDD側にプルアップされているため、このプルアップされた電圧を電圧検出回路112により検出することで、CKP、CKMのハイインピーダンス状態を検出できる。

#### 【0141】

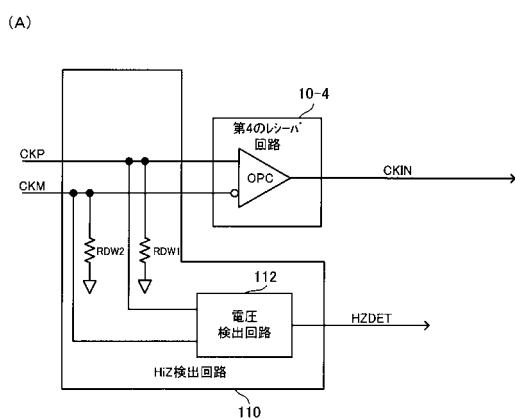

なおHiZ検出回路110は図14(A)の構成に限定されず、種々の変形実施が可能である。例えば図15(A)にHiZ検出回路110の他の構成例を示す。

#### 【0142】

図15(A)のHiZ検出回路110は、CKPの信号線に接続される第1のプルダウン抵抗RDW1と、CKMの信号線に接続される第2のプルダウン抵抗RDW2を含む。これらのプルダウン抵抗RDW1、RDW2は、CKP、CKMの信号線とVSSの間に設けられる。

#### 【0143】

また図15(A)のHiZ検出回路110では、電圧検出回路112は、CKP、CKMのクロック信号線の電圧が、コモンモードの入力電圧範囲の最小電圧をVLよりも低くなつたか否かを検出する。例えば図15(B)に示すように、VL～VHがコモンモード入力電圧範囲である場合に、CKP、CKMの電圧がVLよりも低い場合(VSS～VLの間である場合)に、検出信号HZDETをアクティブにする。

#### 【0144】

即ち、コモンモード入力電圧範囲はVL～VHであるため、CKP、CKMの信号線の電圧がVLよりも低い場合には、CKP、CKMのクロックが転送されている状態ではないと判断できる。そしてトランスマッタ回路側がCKP、CKMの信号線を駆動しない場合には、これらの信号線はプルダウン抵抗RDW1、RDW2によりVSS側にプルダウンされているため、このプルダウンされた電圧を電圧検出回路112により検出することで、CKP、CKMのハイインピーダンス状態を検出できる。

#### 【0145】

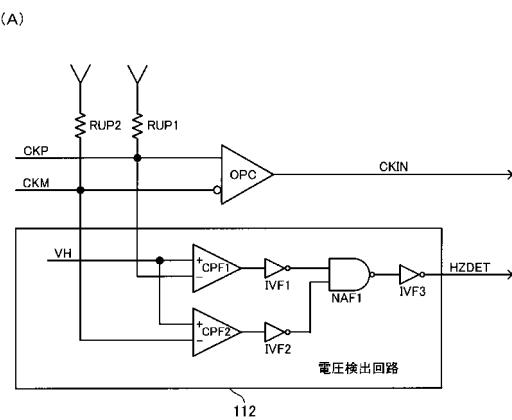

図16(A)に電圧検出回路112の構成例を示す。なお電圧検出回路112の構成は図16(A)に限定されず、種々の変形実施が可能である。

#### 【0146】

図16(A)の電圧検出回路112は、コンパレータCPF1、CPF2、インバータ回路IVF1、IVF2、IVF3、NAND回路NAF1を含む。コンパレータCPF1は、コモンモード入力電圧範囲の最大電圧VHと、CKPの電圧を比較し、CKPの電圧がVHよりも大きくなつた場合にLレベルを出力する。コンパレータCPF2は、最大

10

20

30

40

50

電圧VHと、CKMの電圧を比較し、CKMの電圧がVHよりも大きくなった場合にLレベルを出力する。従って、CKP、CKMの電圧が共に最大電圧VHよりも大きくなると、NAND回路NAF1の第1、第2の入力端子の電圧が共にHレベルになり、検出信号HZDETがHレベル(アクティブ)になる。これにより、CKP、CKMのハイインピーダンス状態を検出できる。

#### 【0147】

図16(A)の電圧検出回路112によれば、図16(B)に示すように電源電圧が変動した場合にも、C1に示すように検出電圧の下限値が一定になるため、ハイインピーダンス状態の適正な検出が可能になる。

#### 【0148】

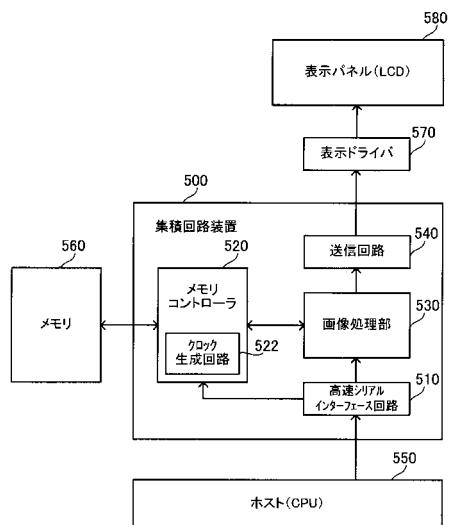

##### 7. 電子機器

図17に本実施形態の高速シリアルインターフェース回路510を用いた電子機器の一例を示す。図17は、LCD等の表示パネル580を備えた大型テレビや携帯電話機などの電子機器の構成例である。

#### 【0149】

ホスト550からのシリアルデータやクロックは、LVD\\$の差動信号線(シリアルバス)を介して集積回路装置500に送信され、高速シリアルインターフェース回路510(LVD\\$受信回路)が受信する。そして高速シリアルインターフェース回路510は、ホスト550から転送されたクロック(或いは当該クロックを遅延したクロック)を、メモリコントローラ520に供給する。またホスト550から転送された受信シリアルデータである画像データを、画像処理部530に供給する。

#### 【0150】

画像処理部530は、ホスト550から受信した画像データに対して、例えばガンマ補正等の種々の画像処理を施す。そして、この画像処理のためにメモリ560(広義には、高速シリアルインターフェース回路により受信されたデータ又はクロックに基づき動作するデバイス)を使用して、画像処理前や画像処理後の画像データをメモリ560に書き込んだり、メモリ560から読み出す。このメモリ560としては、例えばSDRAMやDDR SDRAMなどの高速メモリを使用できる。このようなメモリ560へのデータの書き込みや、メモリ560からのデータの読み出しは、メモリコントローラ520(SDRAM)の制御により実現される。

#### 【0151】

メモリコントローラ520のクロック生成回路522は、例えば高速シリアルインターフェース回路510からのクロックに基づいて、メモリ560からのリードデータをサンプリングするためのクロックを生成する。或いはメモリ560へのデータの書き込みに必要なクロックを生成してもよい。

#### 【0152】

画像処理部530により画像処理が施された後の画像データは、送信回路540により表示ドライバ570(高速シリアルインターフェース回路により受信されたデータ又はクロックに基づき動作するデバイス)に送信される。そして表示ドライバ570は、受信した画像データに基づいて、LCD等の表示パネル580を駆動して、画像データに対応する画像を表示するための制御を行う。

#### 【0153】

なお本実施形態の高速シリアルインターフェース回路が適用される電子機器は図17の構成には限定されず、少なくとも高速シリアルインターフェース回路により受信されたデータ又はクロックに基づき動作するデバイス(例えばメモリ、表示ドライバ、表示パネル等)を含むものであればよい。具体的には本実施形態が適用できる電子機器としては、情報処理装置、携帯情報端末、AV機器、携帯型AV機器、ゲーム装置又は携帯型ゲーム装置等の種々のものが考えられる。

#### 【0154】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効

10

20

30

40

50

果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また高速シリアルインターフェース回路、電子機器の構成、動作も本実施形態で説明したものに限定に限定されず、種々の変形実施が可能である。

#### 【図面の簡単な説明】

##### 【0155】

- 【図1】本実施形態の高速シリアルインターフェース回路の第1の構成例。

- 【図2】本実施形態の第1の構成例の第1のマッピングモードでの動作説明図。 10

- 【図3】本実施形態の第1の構成例の第2のマッピングモードでの動作説明図。

- 【図4】本実施形態の第2の構成例の第1のマッピングモードでの動作説明図。

- 【図5】本実施形態の第2の構成例の第2のマッピングモードでの動作説明図。

- 【図6】図6(A)、図6(B)は第1、第2のマッピングモードの具体例。

- 【図7】サンプリングクロック生成回路の構成例。

- 【図8】サンプリングクロック生成回路及びシリアル／パラレル変換回路の動作を説明するための信号波形。

- 【図9】本実施形態の高速シリアルインターフェース回路の第3の構成例。

- 【図10】本実施形態の第3の構成例の第1のマッピングモードでの動作説明図。

- 【図11】本実施形態の第3の構成例の第2のマッピングモードでの動作説明図。 20

- 【図12】本実施形態の高速シリアルインターフェース回路の第4の構成例。

- 【図13】図12の詳細な構成例。

- 【図14】図14(A)、図14(B)はHiZ検出回路の構成例及びその説明図。

- 【図15】図15(A)、図15(B)はHiZ検出回路の他の構成例及びその説明図。

- 【図16】図16(A)、図16(B)はHiZ検出回路が含む電圧検出回路の構成例及びその説明図。

- 【図17】電子機器の構成例。

#### 【符号の説明】

##### 【0156】

- S L 1 ~ S L m データセレクタ、S L C クロックセレクタ、 30

- 1 0 -1 ~ 1 0 -N 第1 ~ 第Nのレシーバ回路、2 0 接続切り替え回路、

- 2 2 -1 ~ 2 2 -m データ遅延回路、2 2 -c クロック遅延回路、

- 3 0 ロジック回路ブロック、4 0 シリアル／パラレル変換回路、

- 4 2 -1 ~ 4 2 -m シリアル／パラレル変換部 5 0 サンプリングクロック生成回路、

- 5 2 遅延調整回路、5 3 位相比較回路、5 4 チャージ・ポンプ回路、

- 5 5 バイアス回路、5 6 遅延回路、6 0 ロジック回路、

- 7 0 自走クロック生成回路、8 0 クロック検出回路、

- 9 0 出力マスク回路、9 2 マスク信号生成回路、1 0 0 周波数検出回路、

- 1 1 0 HiZ検出回路、1 1 2 電圧検出回路、1 2 0 マッピング変更回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

(B)

【図15】

(B)

【図16】

(B)

【図17】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 6 1 1 A

G 09 G 3/20 6 2 3 J

G 09 G 3/20 6 3 3 B

G 09 G 3/20 6 1 2 P

G 06 F 3/00 P

H 04 L 25/02 V

(56)参考文献 特開2000-078027(JP,A)

特開2006-080877(JP,A)

特開昭63-121344(JP,A)

特開2000-059684(JP,A)

特開平08-116272(JP,A)

特開2008-219813(JP,A)

特開2008-011396(JP,A)

特表2010-503256(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 04 L 25/00 - 25/66